(19)日本国特許庁(JP)

## (12)特許公報(B2)

(11)特許番号

特許第7110357号

(P7110357)

(45)発行日 令和4年8月1日(2022.8.1)

(24)登録日 令和4年7月22日(2022.7.22)

(51)国際特許分類

|         |                  |     |         |         |

|---------|------------------|-----|---------|---------|

| G 0 6 F | 30/3308(2020.01) | F I | G 0 6 F | 30/3308 |

| G 0 6 F | 30/367(2020.01)  |     | G 0 6 F | 30/367  |

請求項の数 20 (全30頁)

(21)出願番号 特願2020-537468(P2020-537468)

(86)(22)出願日 平成31年1月11日(2019.1.11)

(65)公表番号 特表2021-512387(P2021-512387)

A)

(43)公表日 令和3年5月13日(2021.5.13)

(86)国際出願番号 PCT/EP2019/050608

(87)国際公開番号 WO2019/149503

(87)国際公開日 令和1年8月8日(2019.8.8)

審査請求日 令和3年6月23日(2021.6.23)

(31)優先権主張番号 15/883,652

(32)優先日 平成30年1月30日(2018.1.30)

(33)優先権主張国・地域又は機関

米国(US)

(73)特許権者 3900009531

インターナショナル・ビジネス・マシンズ・コーポレーション

INTERNATIONAL BUSINESS MACHINES CORPORATION

アメリカ合衆国10504 ニューヨーク州 アーモンク ニュー オーチャード ロード

New Orchard Road, Armonk, New York 10504, United States of America

(74)代理人 100112690

弁理士 太佐 種一

最終頁に続く

(54)【発明の名称】 量子コンピューティング・デバイス設計

## (57)【特許請求の範囲】

## 【請求項1】

量子コンピューティング・デバイス設計ツールのシステムであって、

コンピュータ実行可能コンポーネントを格納するメモリと、

前記メモリに格納されたコンピュータ実行可能コンポーネントを実行するプロセッサと

を備えており、前記コンピュータ実行可能コンポーネントが、

量子コンピューティング・デバイスの量子デバイス素子を電磁回路素子としてモデル化

し、前記量子コンピューティング・デバイスの電磁回路データを生成するモデル化コンポ

ーネントと、

前記電磁回路データを使用して前記量子コンピューティング・デバイスをシミュレート

し、前記量子コンピューティング・デバイスの応答関数を示す応答関数データを生成する

シミュレーション・コンポーネントと

を含んでいる、システム。

## 【請求項2】

前記量子デバイス素子が、前記量子コンピューティング・デバイスの第1の量子デバイ

ス素子であり、前記モデル化コンポーネントが、前記量子コンピューティング・デバイス

の前記第1の量子デバイス素子と第2の量子デバイス素子の間の接続に関連付けられた情

報を示す接続データを生成する、請求項1に記載のシステム。

## 【請求項3】

前記モデル化コンポーネントが、前記接続データに基づいて前記量子コンピューティン

グ・デバイスの前記電磁回路データを生成する、請求項 2 に記載のシステム。

【請求項 4】

前記シミュレーション・コンポーネントが前記応答関数データに基づいてハミルトニアン・データを生成する、請求項 1 に記載のシステム。

【請求項 5】

定義された基準を前記ハミルトニアン・データが満たすということの決定に応答して、前記シミュレーション・コンポーネントが、前記電磁回路データを使用して前記量子コンピューティング・デバイスを再シミュレートする、請求項 4 に記載のシステム。

【請求項 6】

前記コンピュータ実行可能コンポーネントが、

前記ハミルトニアン・データに基づいて、前記量子コンピューティング・デバイスのレイアウトを示す設計データを生成する設計コンポーネントを含んでいる、請求項 4 に記載のシステム。

【請求項 7】

前記モデル化コンポーネントが、電磁回路素子のライブラリに基づいて、前記量子コンピューティング・デバイスの前記量子デバイス素子を前記電磁回路素子としてモデル化する、請求項 1 に記載のシステム。

【請求項 8】

前記シミュレーション・コンポーネントによって生成された前記応答関数データが、前記量子コンピューティング・デバイスの品質の改善を促進する、請求項 1 に記載のシステム。

10

【請求項 9】

前記ハミルトニアン・データが、前記量子コンピューティング・デバイスのエネルギーに関連付けられた情報を示す、請求項 4 に記載のシステム。

【請求項 10】

コンピュータ実装方法であって、

プロセッサに動作可能なように結合されたシステムによって、量子コンピューティング・デバイスの量子デバイス素子を電磁回路素子としてモデル化し、前記量子コンピューティング・デバイスの電磁回路データを生成することと、

前記システムによって、前記電磁回路データを使用して前記量子コンピューティング・デバイスをシミュレートし、前記量子コンピューティング・デバイスのパラメータのセットを示すパラメータ・データを生成することと、

前記システムによって、前記パラメータ・データに基づいて、前記量子コンピューティング・デバイスのレイアウトを示す設計データを生成することとを含んでいる、コンピュータ実装方法。

20

【請求項 11】

前記量子コンピューティング・デバイスを前記シミュレートすることが、前記電磁回路データを使用して前記量子コンピューティング・デバイスをシミュレートし、前記量子コンピューティング・デバイスの応答関数を示す応答関数データを生成することを含んでいる、請求項 10 に記載のコンピュータ実装方法。

30

【請求項 12】

前記量子コンピューティング・デバイスを前記シミュレートすることが、前記応答関数データに基づいてハミルトニアン・データを生成することを含んでいる、請求項 11 に記載のコンピュータ実装方法。

40

【請求項 13】

前記設計データを前記生成することが、前記ハミルトニアン・データに基づいて前記設計データを生成することを含んでいる、請求項 12 に記載のコンピュータ実装方法。

【請求項 14】

定義された基準を前記ハミルトニアン・データが満たすということの決定に応答して、前記システムによって、前記電磁回路データを使用して前記量子コンピューティング・デ

50

バイスを再シミュレートすることをさらに含んでいる、請求項1\_2に記載のコンピュータ実装方法。

【請求項15】

前記システムによって、前記量子コンピューティング・デバイスの量子デバイス素子間の1つまたは複数の接続に関連付けられた情報を示す接続データを生成することをさらに含んでいる、請求項1\_0に記載のコンピュータ実装方法。

【請求項16】

前記量子デバイス素子を前記モデル化することが、前記接続データに基づいて前記量子コンピューティング・デバイスの前記電磁回路データを生成することを含んでいる、請求項1\_5に記載のコンピュータ実装方法。

10

【請求項17】

前記量子デバイス素子を前記モデル化することが、電磁回路素子のライブラリに基づいて、前記量子コンピューティング・デバイスの前記量子デバイス素子を前記電磁回路素子としてモデル化することを含んでいる、請求項1\_0に記載のコンピュータ実装方法。

【請求項18】

前記設計データを前記生成することが、前記量子コンピューティング・デバイスを改良することを含んでいる、請求項1\_0に記載のコンピュータ実装方法。

【請求項19】

量子コンピューティング・デバイス設計のためのコンピュータ・プログラムであって、

プロセッサに、

20

量子コンピューティング・デバイスの1つまたは複数の量子デバイス素子を1つまたは複数の電磁回路素子としてモデル化することと、

前記1つまたは複数の電磁回路素子に基づいて前記量子コンピューティング・デバイスの等価電磁回路を生成することと、

前記等価電磁回路をシミュレートし、前記量子コンピューティング・デバイスのパラメータのセットを示すパラメータ・データを生成することと、

前記パラメータ・データに基づいて、前記量子コンピューティング・デバイスのレイアウトを示す設計データを生成することと

を実行させるためのコンピュータ・プログラム。

【請求項20】

30

コンピュータ実装方法であって、

プロセッサに動作可能なように結合されたシステムによって、量子コンピューティング・デバイスの1つまたは複数の量子デバイス素子を1つまたは複数の電磁回路素子としてモデル化することと、

前記システムによって、前記1つまたは複数の電磁回路素子に基づいて前記量子コンピューティング・デバイスの等価電磁回路を生成することと、

前記システムによって、前記等価電磁回路をシミュレートし、前記量子コンピューティング・デバイスの応答関数を示す応答関数データを生成することと、

前記システムによって、前記応答関数を使用して前記量子コンピューティング・デバイスのハミルトニアン・パラメータのセットを生成することと、

前記ハミルトニアン・パラメータのセットに基づいて、前記システムによって、前記量子コンピューティング・デバイスのレイアウトを生成することと

を含んでいる、コンピュータ実装方法。

40

【発明の詳細な説明】

【技術分野】

【0001】

本開示は、量子コンピューティング・デバイスに関し、より詳細には、量子コンピューティング・デバイス設計に関する。

【背景技術】

【0002】

50

量子コンピューティングは、トランジスタに基づく2進デジタル手法ではなく、量子物理学を採用して情報をエンコードする。例えば、量子コンピューティング・デバイスは、量子物理学の重ね合わせの原理および量子物理学のエンタングルメント原理に従って動作する量子のビット（quantum bits）（例えば、量子ビット（qubits））を採用することができる。量子物理学の重ね合わせの原理は、各量子ビットが「1」の値と「0」の値の両方を同時に表すことができるようとする。量子物理学のエンタングルメント原理の状態は、量子ビットが、重ね合わせにおいて互いに相関関係を持つことができるようとする。例えば、第1の値（例えば、「1」の値または「0」の値）の状態は、第2の値の状態によって決まることができる。そのため、量子コンピューティング・デバイスは、トランジスタに基づく2進デジタル手法ではなく、量子ビットを採用して情報をエンコードすることができる。しかし、量子コンピューティング・デバイスの設計は、従来の2進デジタル・デバイスと比較して、通常、困難であるか、または時間がかかるか、あるいはその両方である。例えば、Svore, et al., "Toward a Software Architecture for Quantum Computing Design Tools"は、「量子コンピューティング・アルゴリズムを表す高水準言語プログラムをテクノロジー固有の実装に変換するコンピュータ支援設計フロー」を開示している。Svore他は、「この設計フロー（図1）は、量子アルゴリズムを表す高水準プログラムをテクノロジー固有の実装またはシミュレーションにマッピングする4段階のプロセスである」ということも開示している。さらに、Svore他は、「設計フローの最初の3つの段階は、量子コンピュータ・コンパイラ（QCC：quantum computer compiler）の一部であり、・・・最後の段階は、量子デバイス上の量子アルゴリズムのシミュレーションまたは実装である」と述べている。そのため、量子コンピューティング・デバイスの設計プロセスまたは量子コンピューティング・デバイスの設計あるいはその両方が改善され得る。

【先行技術文献】

【非特許文献】

【0003】

【文献】Svore, et al., "Toward a Software Architecture for Quantum Computing Design Tools"

【発明の概要】

【発明が解決しようとする課題】

【0004】

本発明は、量子コンピューティング・デバイスのモデル化および設計のための手法およびシステムを提供することを目的とする。

【課題を解決するための手段】

【0005】

以下に、本発明の1つまたは複数の実施形態の基本的理解を可能にするための概要を示す。この概要は、主要な要素または重要な要素を特定するよう意図されておらず、特定の実施形態の範囲または特許請求の範囲を正確に説明するよう意図されていない。この概要の唯一の目的は、後で提示されるより詳細な説明のための前置きとして、概念を簡略化された形態で提示することである。本明細書に記載された1つまたは複数の実施形態では、量子コンピューティング・デバイス設計を容易にするためのデバイス、システム、コンピュータ実装方法、装置、またはコンピュータ・プログラム製品、あるいはその組み合わせが説明される。

【0006】

一実施形態によれば、量子コンピューティング・デバイス設計ツールのシステムは、モデル化コンポーネントおよびシミュレーション・コンポーネントを備えることができる。モデル化コンポーネントは、量子コンピューティング・デバイスの量子デバイス素子を電磁回路素子としてモデル化し、量子コンピューティング・デバイスの電磁回路データを生成することができる。シミュレーション・コンポーネントは、電磁回路データを使用して量子コンピューティング・デバイスをシミュレートし、量子コンピューティング・デバイ

10

20

30

40

50

スの応答関数を示す応答関数データを生成することができる。一実施形態では、このシステムは、量子コンピューティング・デバイスを設計する時間を最小限に抑えることができ、または量子コンピューティング・デバイスを設計するために採用される計算リソースの量を減らすことができ、あるいはその両方を行うことができる。特定の実施形態では、量子デバイス素子が、量子コンピューティング・デバイスの第1の量子デバイス素子であることができ、モデル化コンポーネントが、量子コンピューティング・デバイスの第1の量子デバイス素子と第2の量子デバイス素子の間の接続に関連付けられた情報を示す接続データを生成することができる。別の実施形態では、モデル化コンポーネントが、接続データに基づいて量子コンピューティング・デバイスの電磁回路データを生成することができる。特定の実施形態では、シミュレーション・コンポーネントが、量子コンピューティング・デバイスに関連付けられた情報を示す応答関数データを生成することができる。さらに、特定の実施形態では、シミュレーション・コンポーネントが、応答関数データに基づいて、ハミルトニアンまたはハミルトニアン・データあるいはその両方を構築することができる。追加的または代替的に、定義された基準をハミルトニアン・データが満たすということの決定に応答して、シミュレーション・コンポーネントが、電磁回路データを使用して量子コンピューティング・デバイスを再シミュレートすることができる。追加的または代替的に、設計コンポーネントが、ハミルトニアン・データに基づいて、量子コンピューティング・デバイスのレイアウトを示す設計データを生成することができる。特定の実施形態では、モデル化コンポーネントが、電磁回路素子のライブラリに基づいて、量子コンピューティング・デバイスの量子デバイス素子を電磁回路素子としてモデル化することができる。特定の実施形態では、シミュレーション・コンポーネントによって生成された応答関数データが、量子コンピューティング・デバイスの品質の改善を促進することができる。

#### 【 0 0 0 7 】

別の実施形態によれば、コンピュータ実装方法が提供される。コンピュータ実装方法は、プロセッサに動作可能なように結合されたシステムによって、量子コンピューティング・デバイスの量子デバイス素子を電磁回路素子としてモデル化し、量子コンピューティング・デバイスの電磁回路データを生成することを含むことができる。コンピュータ実装方法は、システムによって、電磁回路データを使用して量子コンピューティング・デバイスをシミュレートし、量子コンピューティング・デバイスのパラメータのセットを示すパラメータ・データを生成することを含むこともできる。一実施形態では、コンピュータ実装方法は、量子コンピューティング・デバイスを設計する時間を最小限に抑えることができ、または量子コンピューティング・デバイスを設計するために採用される計算リソースの量を減らすことができ、あるいはその両方を行うことができる。特定の実施形態では、コンピュータ実装方法は、シミュレートされた量子コンピューティング・デバイスの応答関数に基づいて、システムによって、ハミルトニアンを構築することを含むこともできる。さらに、コンピュータ実装方法は、パラメータ・データに基づいて、システムによって、量子コンピューティング・デバイスのレイアウトを示す設計データを生成することを含むことができる。一実施形態では、量子コンピューティング・デバイスをシミュレートすることが、電磁回路データを使用して量子コンピューティング・デバイスをシミュレートし、量子コンピューティング・デバイスの応答関数を示す応答関数データを生成することを含むことができる。別の実施形態では、量子コンピューティング・デバイスをシミュレートすることが、量子コンピューティング・デバイスに関連付けられた情報を示す応答関数データを生成することを含むことができる。別の実施形態では、量子コンピューティング・デバイスをシミュレートすることが、応答関数データに基づいて量子コンピューティング・デバイスのハミルトニアンまたはハミルトニアン・データあるいはその両方を構築することを含むことができる。さらに別の実施形態では、設計データを生成することができ、ハミルトニアン・データに基づいて設計データを生成することを含むことができる。特定の実施形態では、コンピュータ実装方法は、定義された基準をハミルトニアン・データが満たすということの決定に応答して、システムによって、電磁回路データを使用して量子コ

10

20

30

40

50

ンピューティング・デバイスを再シミュレートすることをさらに含むことができる。特定の実施形態では、コンピュータ実装方法は、システムによって、量子コンピューティング・デバイスの量子デバイス素子間の1つまたは複数の接続に関連付けられた情報を示す接続データを生成することをさらに含むことができる。一実施形態では、量子デバイス素子をモデル化することが、接続データに基づいて量子コンピューティング・デバイスの電磁回路データを生成することを含むことができる。別の実施形態では、量子デバイス素子をモデル化することが、電磁回路素子のライブラリに基づいて、量子コンピューティング・デバイスの量子デバイス素子を電磁回路素子としてモデル化することを含むことができる。さらに別の実施形態では、設計データを生成することが、量子コンピューティング・デバイスを改良することを含むことができる。

10

#### 【0008】

さらに別の実施形態によれば、量子コンピューティング・デバイス設計のためのコンピュータ・プログラム製品が、プログラム命令が具現化されたコンピュータ可読記憶媒体を含むことができる。プログラム命令は、プロセッサによって実行可能であり、プロセッサによって量子コンピューティング・デバイスの1つまたは複数の量子デバイス素子を1つまたは複数の電磁回路素子としてモデル化することを、プロセッサに実行させることができる。プログラム命令は、プロセッサによって、1つまたは複数の電磁回路素子に基づいて量子コンピューティング・デバイスの等価電磁回路を生成することを、プロセッサに実行させることもできる。さらに、プログラム命令は、プロセッサによって、等価電磁回路をシミュレートし、量子コンピューティング・デバイスのパラメータのセットを示すパラメータ・データを生成することを、プロセッサに実行させることができる。一実施形態では、コンピュータ・プログラム製品が、量子コンピューティング・デバイスを設計する時間を最小限に抑えることができ、または量子コンピューティング・デバイスを設計するために採用される計算リソースの量を減らすことができ、あるいはその両方を行うことができる。プログラム命令は、パラメータ・データに基づいて、プロセッサによって量子コンピューティング・デバイスのレイアウトを示す設計データを生成することを、プロセッサに実行させることもできる。特定の実施形態では、プログラム命令は、プロセッサによって、等価電磁回路をシミュレートし、量子コンピューティング・デバイスの応答関数を示す応答関数データを生成することを、プロセッサに実行させることもできる。特定の実施形態では、プログラム命令は、応答関数データに基づいて、プロセッサによってハミルトニアン・データを生成することを、プロセッサに実行させることもでき、ハミルトニアン・データは、量子コンピューティング・デバイスのエネルギーに関連付けられた情報を示す。

20

#### 【0009】

さらに別の実施形態によれば、量子コンピューティング・デバイス設計ツールのシステムは、モデル化コンポーネント、シミュレーション・コンポーネント、および設計コンポーネントを備えることができる。モデル化コンポーネントは、量子コンピューティング・デバイスの量子デバイス素子を電磁回路素子としてモデル化し、量子コンピューティング・デバイスの電磁回路データを生成することができる。シミュレーション・コンポーネントは、電磁回路データを使用して量子コンピューティング・デバイスをシミュレートし、量子コンピューティング・デバイスの応答関数を示す応答関数データを生成することができる。シミュレーション・コンポーネントは、応答関数データに基づいてハミルトニアン・データを生成することもでき、ハミルトニアン・データは、量子コンピューティング・デバイスのエネルギーに関連付けられた情報を示す。設計コンポーネントは、ハミルトニアン・データに基づいて、量子コンピューティング・デバイスのレイアウトを示す設計データを生成することができる。一実施形態では、このシステムは、量子コンピューティング・デバイスを設計する時間を最小限に抑えることができ、または量子コンピューティング・デバイスを設計するために採用される計算リソースの量を減らすことができ、あるいはその両方を行うことができる。特定の実施形態では、量子デバイス素子が、量子コンピューティング・デバイスの第1の量子デバイス素子であり、モデル化コンポーネントが、

30

40

50

量子コンピューティング・デバイスの第1の量子デバイス素子と第2の量子デバイス素子の間の接続に関する情報を示す接続データを生成することができる。特定の実施形態では、モデル化コンポーネントが、接続データに基づいて量子コンピューティング・デバイスの電磁回路データを生成することができる。

【0010】

さらに別の実施形態によれば、コンピュータ実装方法が提供される。コンピュータ実装方法は、プロセッサに動作可能なように結合されたシステムによって、量子コンピューティング・デバイスの1つまたは複数の量子デバイス素子を1つまたは複数の電磁回路素子としてモデル化することを含むことができる。コンピュータ実装方法は、システムによって、1つまたは複数の電磁回路素子に基づいて量子コンピューティング・デバイスの等価電磁回路を生成することを含むことができる。さらに、コンピュータ実装方法は、システムによって、等価電磁回路をシミュレートし、量子コンピューティング・デバイスの応答関数を示す応答関数データを生成することを含むことができる。一実施形態では、コンピュータ実装方法は、量子コンピューティング・デバイスを設計する時間を最小限に抑えることができ、または量子コンピューティング・デバイスを設計するために採用される計算リソースの量を減らすことができ、あるいはその両方を行うことができる。コンピュータ実装方法は、システムによって、応答関数を使用して量子コンピューティング・デバイスのハミルトニアンおよびハミルトニアン・パラメータのセットを生成することを含むことができる。さらに、コンピュータ実装方法は、ハミルトニアン・パラメータのセットに基づいて、システムによって、量子コンピューティング・デバイスのレイアウトを生成することを含むことができる。特定の実施形態では、コンピュータ実装方法は、定義された基準を、ハミルトニアン・パラメータのセットからのハミルトニアン・パラメータが満たしているということの決定に応答して、システムによって、等価電磁回路を再シミュレートすることを含むことができる。

10

【図面の簡単な説明】

【0011】

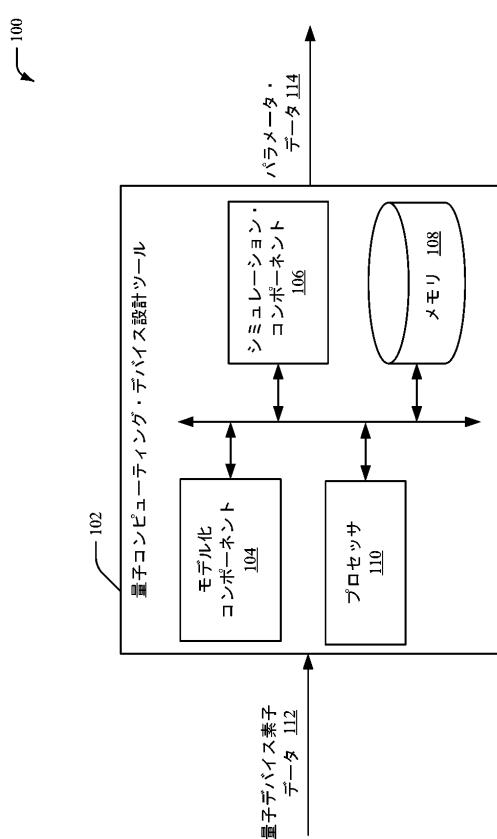

【図1】本明細書に記載された1つまたは複数の実施形態に従って、量子コンピューティング・デバイスのコンポーネントを含んでいる、例示的な非限定的システムのブロック図である。

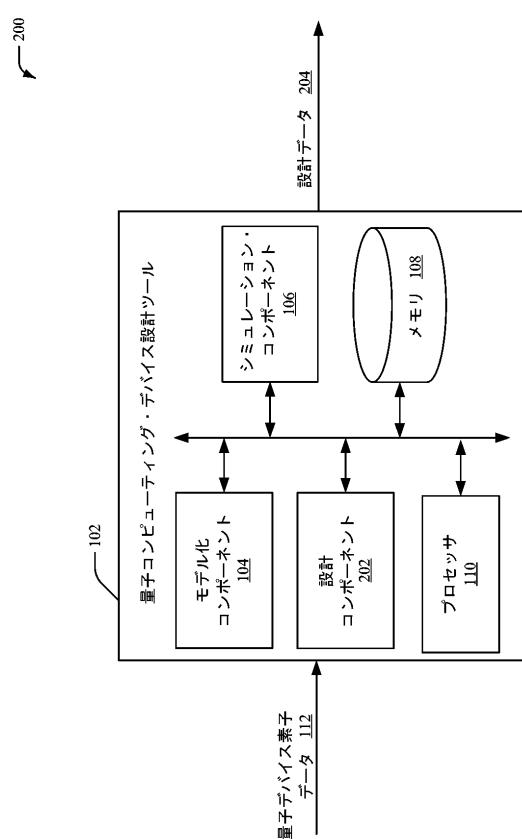

【図2】本明細書に記載された1つまたは複数の実施形態に従って、量子コンピューティング・デバイスのコンポーネントを含んでいる、別の例示的な非限定的システムのブロック図である。

30

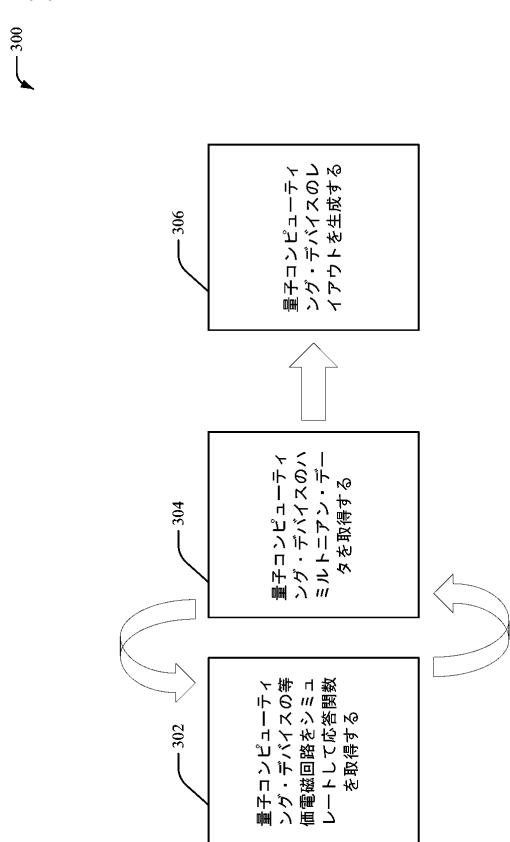

【図3】本明細書に記載された1つまたは複数の実施形態に従って、量子コンピューティング・デバイス設計を容易にする、例示的な非限定的システムを示す図である。

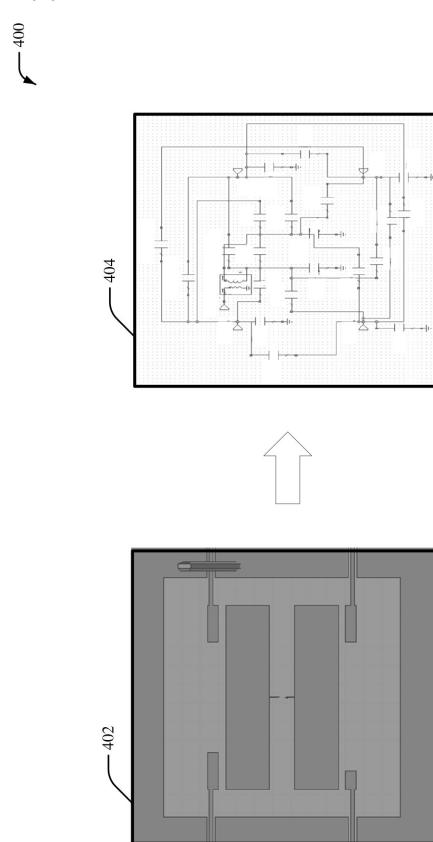

【図4】本明細書に記載された1つまたは複数の実施形態に従って、量子デバイス素子および電磁回路素子を含んでいる、例示的な非限定的システムを示す図である。

【図5】本明細書に記載された1つまたは複数の実施形態に従って、量子デバイス素子、電磁回路素子、および概略素子を含んでいる、例示的な非限定的システムを示す図である。

【図6】本明細書に記載された1つまたは複数の実施形態に従って、量子デバイス素子、電磁回路素子、および概略素子を含んでいる、別の例示的な非限定的システムを示す図である。

40

【図7】本明細書に記載された1つまたは複数の実施形態に従って、量子デバイス素子および電磁回路素子を含んでいる、別の例示的な非限定的システムを示す図である。

【図8】本明細書に記載された1つまたは複数の実施形態に従って、等価電磁回路に接続された例示的な非限定的システムを示す図である。

【図9】本明細書に記載された1つまたは複数の実施形態に従って、応答関数に接続された例示的な非限定的グラフである。

【図10】本明細書に記載された1つまたは複数の実施形態に従って、例示的な非限定的量子コンピューティング・デバイスを示す図である。

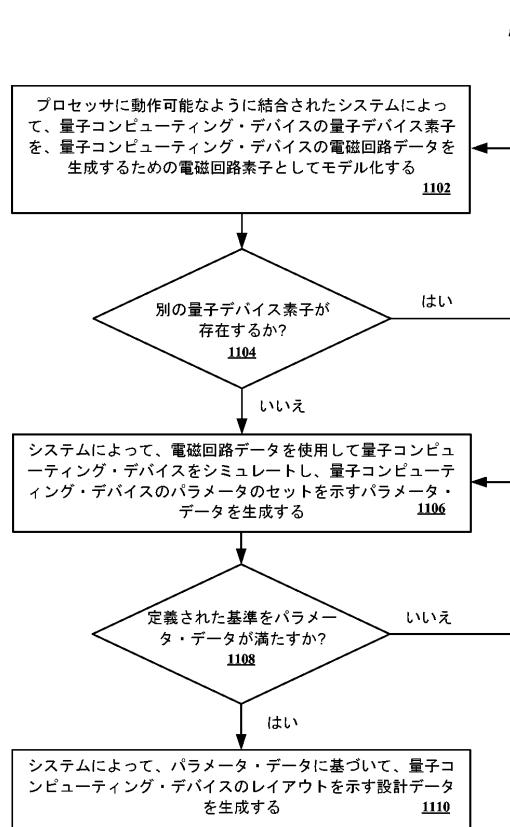

【図11】本明細書に記載された1つまたは複数の実施形態に従って、量子コンピューテ

50

イング・デバイス設計を容易にするための、例示的な非限定的コンピュータ実装方法のフロー図である。

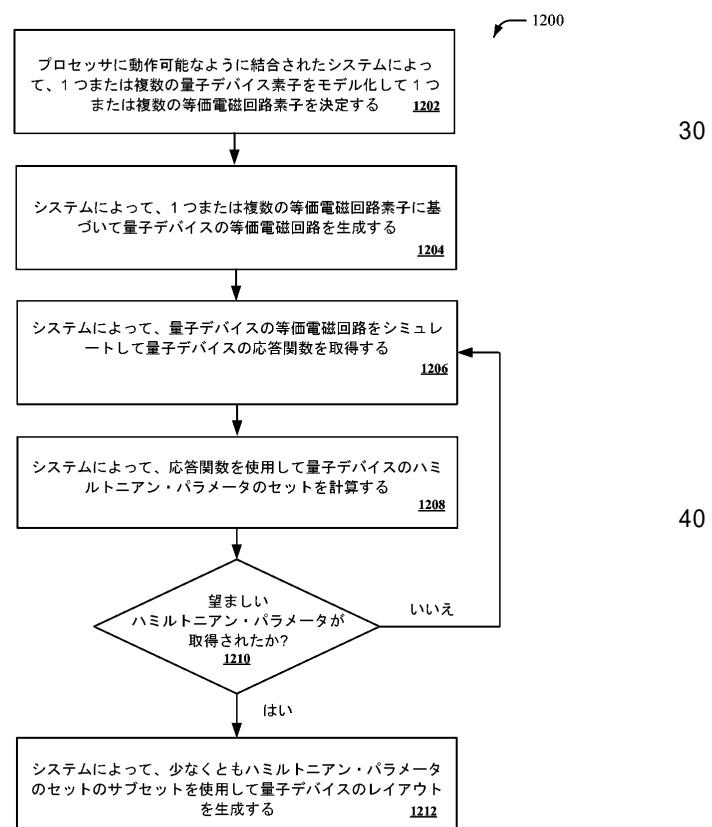

【図12】本明細書に記載された1つまたは複数の実施形態に従って、量子コンピューティング・デバイス設計を容易にするための、別の例示的な非限定的コンピュータ実装方法のフロー図である。

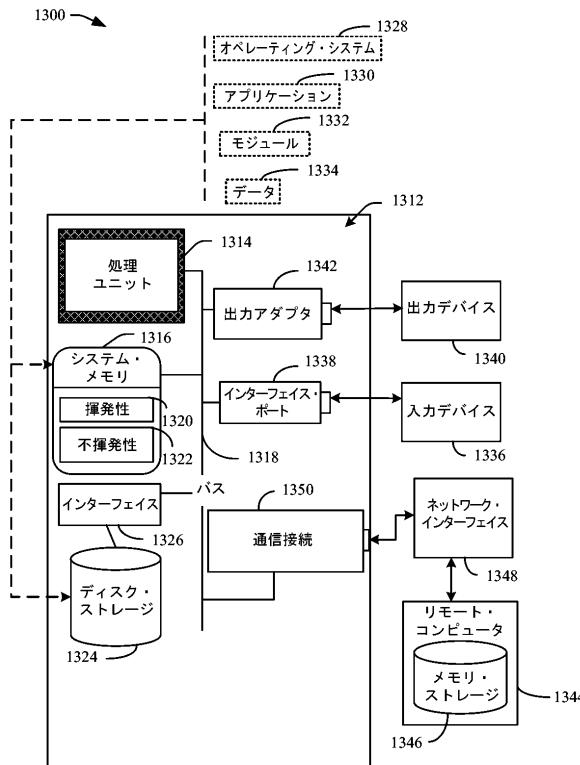

【図13】本明細書に記載された1つまたは複数の実施形態を容易にすることができる例示的な非限定的動作環境のブロック図である。

【発明を実施するための形態】

【0012】

以下の詳細な説明は、例にすぎず、実施形態、または実施形態の適用もしくは使用、あるいはその両方を制限するよう意図されていない。さらに、先行する「背景技術」または「発明の概要」のセクション、あるいは「発明を実施するための形態」のセクションで提示された、いずれかの明示されたか、または暗示された情報によって制約されるという意図はない。

【0013】

ここで、図面を参照して1つまたは複数の実施形態が説明され、図面全体を通じて、類似する参照番号が、類似する要素を参照するために使用されている。以下の説明では、説明の目的で、1つまたは複数の実施形態を十分に理解できるように、多数の特定の詳細が示されている。しかし、これらの特定の詳細がなくても、さまざまな事例において、1つまたは複数の実施形態が実践され得るということは明らかである。

【0014】

量子コンピューティングは、トランジスタに基づく2進デジタル手法ではなく、量子物理学を採用して情報をエンコードする。例えば、量子コンピューティング・デバイスは、量子物理学の重ね合わせの原理および量子物理学のエンタングルメント原理に従って動作する量子のビット (quantum bits) (例えば、量子ビット (qubits)) を採用することができる。量子物理学の重ね合わせの原理は、各量子ビットが「1」の値と「0」の値の両方を同時に表すことができるようになる。量子物理学のエンタングルメント原理の状態は、量子ビットが、重ね合わせにおいて互いに相関関係を持つことができるようになる。例えば、第1の値 (例えば、「1」の値または「0」の値) の状態は、第2の値の状態によって決まることができる。そのため、量子コンピューティング・デバイスは、トランジスタに基づく2進デジタル手法ではなく、量子ビットを採用して情報をエンコードすることができる。しかし、量子コンピューティング・デバイスの設計は、従来の2進デジタル・デバイスと比較して、通常、困難であるか、または時間がかかるか、あるいはその両方である。例えば、Svore, et al., "Toward a Software Architecture for Quantum Computing Design Tools"は、「量子コンピューティング・アルゴリズムを表す高水準言語プログラムをテクノロジー固有の実装に変換するコンピュータ支援設計フロー・・・この設計フロー (図1) は、量子アルゴリズムを表す高水準プログラムをテクノロジー固有の実装またはシミュレーションにマッピングする4段階のプロセスである。設計フローの最初の3つの段階は、量子コンピュータ・コンパイラ (QCC) の一部である。最後の段階は、量子デバイス上の量子アルゴリズムのシミュレーションまたは実装である。」ということを開示している (Svore他の要約、図1、および3ページを参照)。そのため、量子コンピューティング・デバイスの設計プロセスまたは量子コンピューティング・デバイスの設計あるいはその両方が改善され得る。

【0015】

これらの問題またはその他の問題あるいはその両方に對処するために、本明細書に記載された実施形態は、改良された量子コンピューティング・デバイス設計のためのシステム、コンピュータ実装方法、およびコンピュータ・プログラム製品を含んでいる。1つの態様では、量子コンピューティング・デバイスは、等価電磁回路を採用することによって設計され得る。例えば、量子コンピューティング・デバイスの1つまたは複数の量子デバイス素子と同等である電磁回路に基づいて、量子コンピューティング・デバイスを設計する

10

20

30

40

50

ための回路設計またはハミルトニアン計算あるいはその両方が決定され得る。ハミルトニアン計算は、例えば、量子コンピューティング・デバイスのエネルギーまたは電磁特性あるいはその両方に関連付けられた情報を示すことができる。そのため、回路設計と回路設計のためのハミルトニアン計算との間の改良された転換が実現され得る。一実施形態では、等価電磁回路素子を決定するために、量子コンピューティング・デバイスの1つまたは複数の量子デバイス素子がモデル化され得る。1つまたは複数の量子デバイス素子に関連付けられた1つまたは複数の接続に基づいて、量子コンピューティング・デバイスの等価電磁回路が生成され得る。量子コンピューティング・デバイスの応答関数を示す応答関数データを取得するために、(例えば、量子コンピューティング・デバイスのレイアウトをシミュレートするのではなく)等価電磁回路がシミュレートされ得る。応答関数データ(例えば、量子コンピューティング・デバイスの応答関数)は、例えば、インピーダンス、アドミッタンス、または量子コンピューティング・デバイスの別の電気的パラメータ、あるいはその組み合わせを含むことができる。1つの態様では、量子コンピューティング・デバイスの応答関数から1つまたは複数のパラメータを計算するために、モデル化ツールが採用され得る。例えば、量子コンピューティング・デバイスの応答関数から1つまたは複数のハミルトニアン・パラメータを計算するために、ハミルトニアン・モデル化ツールが採用され得る。1つの例では、量子コンピューティング・デバイスの応答関数から1つまたは複数のハミルトニアン・パラメータを計算するために、量子情報処理用の非線形素子に関連付けられたブラックボックス量子化手法(black-box quantization technique)が採用され得る。そのため、量子コンピューティング・デバイスを設計する時間が短縮され得る。例えば、量子コンピューティング・デバイスを準備するか、またはシミュレートするか、あるいはその両方を行う時間が短縮され得る。さらに、量子コンピューティング・デバイスを設計するために採用される計算リソース量が削減され得る。量子コンピューティング・デバイスの設計も最適化され得る。さらに、量子コンピューティング・デバイス設計システムの精度または量子コンピューティング・デバイス設計システムの効率あるいはその両方が改善され得る。さらに、量子コンピューティング・デバイスの品質を改善することができ、量子コンピューティング・デバイスの性能を改善することができ、量子コンピューティング・デバイスの効率を改善することができ、量子コンピューティング・デバイスのタイミング特性を改善することができ、量子コンピューティング・デバイスの電力特性を改善することができ、または量子コンピューティング・デバイスの別の特性を改善することができ、あるいはその組み合わせを行うことができる。

#### 【0016】

図1は、本明細書に記載された1つまたは複数の実施形態に従って、量子コンピューティング・デバイス設計のための例示的な非限定的システム100のブロック図を示している。さまざまな実施形態では、システム100は、量子コンピューティング・デバイス技術、量子コンピューティング設計技術、量子ビット技術、量子コンピューティング・デバイス・モデル化技術、量子回路技術、量子コンピューティング・デバイス・シミュレーション技術、量子プロセッサ技術、人工知能技術、医薬および材料技術、サプライ・チェーンおよび物流技術、金融サービス技術、またはその他のデジタル技術、あるいはその組み合わせなどの、ただしこれらに限定されない技術に関連付けられた、量子コンピューティング・デバイス設計システムであることができる。システム100は、抽象的ではない、人間による一連の精神的活動として実行され得ない本質的に高度に技術的な問題を解決するためのハードウェアまたはソフトウェアあるいはその両方を採用することができる。さらに、特定の実施形態では、実行されるプロセスの一部は、機械学習に関連する定義されたタスクを実行するために、1つまたは複数の特殊なコンピュータ(例えば、1つまたは複数の特殊な処理ユニット、量子コンピューティング・デバイス設計ツールを含む特殊なコンピュータなど)によって実行されてよい。前述の技術、コンピュータ・アーキテクチャ、または同様のもの、あるいはその組み合わせにおける進歩を通じて生じる新しい問題を解決するために、一部の実施形態では、システム100またはシステム100のコンポーネントあるいはその両方が採用され得る。システム100の1つまたは複数の実施形態

10

20

30

40

50

は、量子コンピューティング・デバイス・システム、量子コンピューティング設計システム、量子ビット・システム、量子コンピューティング・デバイス・モデル化システム、量子回路システム、量子コンピューティング・デバイス・シミュレーション・システム、量子プロセッサ・システム、人工知能システム、医薬および材料システム、サプライ・チェーンおよび物流システム、金融サービス・システム、またはその他のシステム、あるいはその組み合わせに、技術的改善を提供できる。システム 100 の 1 つまたは複数の実施形態は、量子コンピューティング・デバイスの処理性能を改善すること、量子コンピューティング・デバイスの処理効率を改善すること、量子コンピューティング・デバイスのタイミング特性を改善すること、または量子コンピューティング・デバイスの電力効率を改善すること、あるいはその組み合わせによって、量子コンピューティング・デバイス（例えば、量子プロセッサ）に技術的改善を提供することもできる。

#### 【 0 0 1 7 】

図 1 に示された実施形態では、システム 100 は、量子コンピューティング・デバイス設計ツール 102 を含むことができる。図 1 に示されているように、量子コンピューティング・デバイス設計ツール 102 は、モデル化コンポーネント 104 およびシミュレーション・コンポーネント 106 を含むことができる。量子コンピューティング・デバイス設計ツール 102 の態様は、マシン内で具現化された（例えば、1 つまたは複数のマシンに関連付けられた 1 つまたは複数のコンピュータ可読媒体内で具現化された）機械実行可能コンポーネントを構成できる。そのようなコンポーネントは、1 つまたは複数のマシン（例えば、コンピュータ、コンピューティング・デバイス、仮想マシンなど）によって実行された場合に、マシンに、説明された動作を実行させることができる。1 つの態様では、量子コンピューティング・デバイス設計ツール 102 は、コンピュータ実行可能コンポーネントおよび命令を格納するメモリ 108 を含むこともできる。さらに、量子コンピューティング・デバイス設計ツール 102 は、量子コンピューティング・デバイス設計ツール 102 による命令（例えば、コンピュータ実行可能コンポーネントおよび対応する命令）の実行を容易にするために、プロセッサ 110 を含むことができる。図に示されているように、1 つまたは複数の実施形態では、モデル化コンポーネント 104、シミュレーション・コンポーネント 106、メモリ 108、またはプロセッサ 110、あるいはその組み合わせは、電気的に、または通信によって、あるいはその両方によって、互いに結合され得る。

#### 【 0 0 1 8 】

量子コンピューティング・デバイス設計ツール 102（例えば、量子コンピューティング・デバイス設計ツール 102 のモデル化コンポーネント 104）は、量子デバイス素子データ 112 を受信できる。量子デバイス素子データ 112 は、例えば、量子コンピューティング・デバイスの 1 つまたは複数の量子デバイス素子の機械可読記述であることができる。追加的または代替的に、量子デバイス素子データは、量子コンピューティング・デバイスの 1 つまたは複数の量子デバイス素子の 1 つまたは複数のモデルに関連付けられる。量子コンピューティング・デバイスは、例えば、量子回路、量子プロセッサ、量子ビット・デバイス、量子ビット単位セル、または量子ビットを採用する別の種類のコンピューティング・デバイス、あるいはその組み合わせであることができる。1 つまたは複数の量子デバイス素子からの量子デバイス素子は、例えば、量子コンピューティング・デバイスの量子ビット素子、量子コンピューティング・デバイスの結合器、量子コンピューティング・デバイスの読み出し、量子コンピューティング・デバイスのバス、または量子コンピューティング・デバイスの別の素子を含むことができる。一実施形態では、量子デバイス素子データ 112 は、量子コンピューティング・デバイスのモデルに関連付けられる。例えば、量子コンピューティング・デバイスのモデルはコンピュータ・シミュレータによって生成され得る。コンピュータ・シミュレータは、例えば、量子コンピューティング・デバイスに関連付けられた 1 つまたは複数の電磁場シミュレーションを実行する静的な場のシミュレータであることができる。1 つの例では、量子コンピューティング・デバイ

スのモデルは、2次元モデルであることができる。別の例では、量子コンピューティング・デバイスのモデルは、3次元モデルであることができる。

【0019】

モデル化コンポーネント104は、量子デバイス素子データ112に関連付けられた量子デバイス素子を電磁回路素子としてモデル化し、量子コンピューティング・デバイスの電磁回路データを生成することができる。例えば、モデル化コンポーネント104は、量子コンピューティング・デバイスの量子デバイス素子を電磁回路素子としてモデル化し、量子コンピューティング・デバイスの電磁回路データを生成することができる。電磁回路素子は、例えば、インダクタ、コンデンサ、抵抗器、インダクタ コンデンサ回路網、インダクタ 抵抗器回路網、インダクタ コンデンサ 抵抗器回路網、コンデンサ 抵抗器回路網、共振器、マイクロ波共振器、別の種類の電磁回路素子などであることができる。一実施形態では、モデル化コンポーネント104は、量子コンピューティング・デバイスの量子デバイス素子間の1つまたは複数の接続に関連付けられた情報を示す接続データを生成することができる。例えば、モデル化コンポーネント104は、量子コンピューティング・デバイスの第1の量子デバイス素子と量子コンピューティング・デバイスの第2の量子デバイス素子の間の接続に関連付けられた情報を示す接続データを生成することができる。1つの態様では、モデル化コンポーネント104が、接続データに基づいて量子コンピューティング・デバイスの電磁回路データを生成することができる。特定の実施形態では、モデル化コンポーネント104が、電磁回路素子のライブラリに基づいて、量子コンピューティング・デバイスの量子デバイス素子を電磁回路素子としてモデル化することができる。例えば、電磁回路素子のライブラリは、量子デバイス素子に対応する既定の電磁回路素子のセットを含むことができる。追加的または代替的に、特定の実施形態では、量子デバイス素子データ112は、量子コンピューティング回路内の量子デバイス素子に関連付けられた1つまたは複数の位置に関する情報を示す位置データをさらに含むことができる。例えば、この位置データは、量子コンピューティング回路内の1つまたは複数の量子デバイス素子の位置にタグ付けする1つまたは複数のタグを含むことができる。

【0020】

シミュレーション・コンポーネント106は、電磁回路データを使用して量子コンピューティング・デバイスをシミュレートし、量子コンピューティング・デバイスのパラメータ・データ114を生成することができる。一実施形態では、このパラメータ・データは、応答関数データを含むことができる。例えば、シミュレーション・コンポーネント106は、電磁回路データを使用して量子コンピューティング・デバイスをシミュレートし、量子デバイスの応答関数データを生成することができる。応答関数データは、量子コンピューティング・デバイスの応答関数を示すことができる。1つの例では、この応答関数は、量子コンピューティング・デバイスの多次元応答関数 (multi-dimensional response function) であることができる。別の実施形態では、このパラメータ・データは、ハミルトニアン・データを含むことができる。例えば、シミュレーション・コンポーネント106は、応答関数データに基づいてハミルトニアン・データを生成することができる。1つの例では、ハミルトニアン・データは応答関数から計算され得る。ハミルトニアン・データは、量子コンピューティング・デバイスのエネルギーまたは量子コンピューティング・デバイスの電磁特性あるいはその両方に関連付けられた情報を示すことができる。1つの態様では、ハミルトニアン・データは、量子コンピューティング・デバイスに関連するクロストーク、相互接続、コネクタ、プリント基板レイアウト、電気的バス、またはその他の電気的特性、あるいはその組み合わせの理解を促進することができる。特定の実施形態では、定義された基準をハミルトニアン・データが満たすということの決定に応答して、シミュレーション・コンポーネント106が、電磁回路データを使用して量子コンピューティング・デバイスを再シミュレートすることができる。例えば、シミュレーション・コンポーネント106は、ハミルトニアン・データに関連付けられた望ましいハミルトニアン値が取得されるまで、電磁回路データを使用して量子コンピューティング・デバイスを再シミュレートすることができる。

10

20

30

40

50

## 【0021】

特定の実施形態では、モデル化コンポーネント104は、人工知能の原理に関連する分類、相関関係、推論、または式、あるいはその組み合わせに基づいて、電磁回路データを生成することができる。例えば、モデル化コンポーネント104は、1つまたは複数の量子デバイス素子を分類するため、または電磁回路データを生成するため、あるいはその両方のために、自動分類システムまたは自動分類プロセスあるいはその両方を採用できる。1つの例では、モデル化コンポーネント104は、1つまたは複数の量子デバイス素子に関する推論を学習するため、または生成するため、あるいはその両方のために、確率または統計あるいはその両方に基づく（例えば、有用性およびコストを考慮して解析を行う）解析を採用できる。1つの態様では、モデル化コンポーネント104は推論コンポーネント（図示されていない）を含むことができ、推論コンポーネントは、1つまたは複数の量子デバイス素子に関連する推論を学習すること、または生成すること、あるいはその両方を容易にするために、推論に基づく方式を一部分において利用して、モデル化コンポーネント104の態様をさらに強化できる。モデル化コンポーネント104は、任意の適切な機械学習に基づく手法、統計に基づく手法、または確率に基づく手法、あるいはその組み合わせを採用できる。例えば、モデル化コンポーネント104は、エキスパート・システム、ファジー論理、SVM、隠れマルコフ・モデル（HMM: Hidden Markov Model）、欲張り検索アルゴリズム、ルールに基づくシステム、ベイジアン・モデル（例えば、ベイジアン・ネットワーク）、ニューラル・ネットワーク、その他の非線形トレーニング手法、データ融合、有用性に基づく解析システム、ベイジアン・モデルを採用するシステムなどを採用することができる。別の態様では、モデル化コンポーネント104は、電磁回路データの生成に関連する一連の機械学習計算を実行できる。例えば、モデル化コンポーネント104は、一連のクラスタリング機械学習計算、一連のロジスティック回帰機械学習計算、一連の決定木機械学習計算、一連のランダム・フォレスト機械学習計算、一連の回帰ツリー機械学習計算、一連の最小二乗機械学習計算、一連のインスタンスに基づく機械学習計算、一連の回帰機械学習計算、一連のサポート・ベクター回帰機械学習計算、一連のK平均機械学習計算、一連のスペクトル・クラスタリング機械学習計算、一連のルール学習機械学習計算、一連のベイジアン機械学習計算、一連のディープ・ボルツマン機械計算、一連のディープ・ビリーフ・ネットワーク計算、または電磁回路データを決定するための一連のさまざまな機械学習計算、あるいはその組み合わせを実行することができる。

## 【0022】

量子コンピューティング・デバイス設計ツール102（例えば、モデル化コンポーネント104またはシミュレーション・コンポーネント106あるいはその両方）が、人間によって実行できない（例えば、1人の人間の知性の能力を上回る）量子コンピューティング・デバイス設計プロセスを実行するということが、理解されるべきである。例えば、特定の期間にわたって量子コンピューティング・デバイス設計ツール102（例えば、モデル化コンポーネント104またはシミュレーション・コンポーネント106あるいはその両方）によって処理されるデータの量、処理されるデータの速度、または処理されるデータのデータ型、あるいはその組み合わせは、同じ期間にわたって1人の人間の知性によって処理され得る量より多く、速度より速く、かつデータ型とは異なるデータ型ができる。量子コンピューティング・デバイス設計ツール102（例えば、モデル化コンポーネント104またはシミュレーション・コンポーネント106あるいはその両方）は、上で参照された量子コンピューティング・デバイス設計プロセスを実行しながら、1つまたは複数の他の機能を実行することに向けて完全に動作可能であることもできる（例えば、完全に電源が投入される、完全に実行されるなど）。さらに、量子コンピューティング・デバイス設計ツール102（例えば、モデル化コンポーネント104またはシミュレーション・コンポーネント106あるいはその両方）によって生成されるパラメータ・データまたは設計データあるいはその両方は、ユーザによって手動で取得するが不可能な情報を含むことができる。例えば、パラメータ・データ114に含まれる情報の種類、

10

20

30

40

50

パラメータ・データ 114 に含まれる情報の多様性、またはパラメータ・データ 114 の最適化、あるいはその組み合わせは、ユーザによって手動で取得される情報より複雑であることができる。

#### 【0023】

さらに、量子コンピューティング・デバイスの従来の設計ツールと比較して、システム 100 がさまざまな利点を提供できるということが、理解されるべきである。例えば、システム 100 を採用することによって、量子コンピューティング・デバイスを設計する時間が短縮され得る。さらに、システム 100 を採用することによって、量子コンピューティング・デバイスを準備するか、またはシミュレートするか、あるいはその両方を行う時間が短縮され得る。また、システム 100 を採用することによって、量子コンピューティング・デバイスを設計するために採用される計算リソース量が削減され得る。システム 100 を採用することによって、量子コンピューティング・デバイスの設計も最適化され得る。さらに、量子コンピューティング・デバイス設計システムの精度または量子コンピューティング・デバイス設計システムの効率あるいはその両方が改善され得る。さらに、システム 100 を採用することによって、量子コンピューティング・デバイスの品質を改善することができ、量子コンピューティング・デバイスの性能を改善することができ、量子コンピューティング・デバイスの効率を改善することができ、量子コンピューティング・デバイスのタイミング特性を改善することができ、量子コンピューティング・デバイスの電力特性を改善することができ、または量子コンピューティング・デバイスの別の特性を改善することができ、あるいはその組み合わせを行うことができる。

10

#### 【0024】

図 2 は、本明細書に記載された 1 つまたは複数の実施形態に従って、例示的な非限定的システム 200 のブロック図を示している。本明細書に記載された他の実施形態で採用されている類似する要素の説明の繰り返しは、簡潔にするために省略されている。

20

#### 【0025】

システム 200 は、量子コンピューティング・デバイス設計ツール 102 を含んでいる。図 2 に示されている量子コンピューティング・デバイス設計ツール 102 は、モデル化コンポーネント 104、シミュレーション・コンポーネント 106、メモリ 108、プロセッサ 110、または設計コンポーネント 202、あるいはその組み合わせを含むことができる。設計コンポーネント 202 は、パラメータ・データ 114 に基づいて設計データ 204 を生成することができる。設計データ 204 は、量子コンピューティング・デバイスのレイアウトを示すことができる。例えば、設計データ 204 は、量子コンピューティング・デバイス内の 1 つまたは複数のコンポーネントの位置を含むことができる。追加的または代替的に、設計データ 204 は、量子コンピューティング・デバイス内の 1 つまたは複数のコンポーネントの電気的パラメータを含むことができる。追加的または代替的に、設計データ 204 は、量子コンピューティング・デバイス内の 1 つまたは複数のコンポーネントの値または設定あるいはその両方を含むことができる。追加的または代替的に、設計データ 204 は、量子コンピューティング・デバイス内の 1 つまたは複数のコンポーネントのサイズ、形状、または配置、あるいはその組み合わせを含むことができる。一実施形態では、量子コンピューティング・デバイスのレイアウトは、パラメータ・データに基づいて変更され得る。別の実施形態では、設計コンポーネント 202 は、応答関数データに基づいて設計データ 204 を生成することができる。別の実施形態では、設計コンポーネント 202 は、ハミルトニアン・データに基づいて設計データ 204 を生成することができる。特定の実施形態では、量子コンピューティング・デバイスのレイアウトは、応答関数データまたはハミルトニアン・データあるいはその両方にに基づいて変更され得る。

30

#### 【0026】

量子コンピューティング・デバイスの従来の設計ツールと比較して、システム 200 がさまざまな利点を提供できるということが、理解されるべきである。例えば、システム 200 を採用することによって、量子コンピューティング・デバイスを設計する時間が短縮され得る。さらに、システム 200 を採用することによって、量子コンピューティング・

40

50

デバイスを準備するか、またはシミュレートするか、あるいはその両方を行う時間が短縮され得る。また、システム 200 を採用することによって、量子コンピューティング・デバイスを設計するために採用される計算リソース量が削減され得る。システム 200 を採用することによって、量子コンピューティング・デバイスの設計も最適化され得る。さらに、量子コンピューティング・デバイス設計システムの精度または量子コンピューティング・デバイス設計システムの効率あるいはその両方が改善され得る。さらに、システム 200 を採用することによって、量子コンピューティング・デバイスの品質を改善することができ、量子コンピューティング・デバイスの性能を改善することができ、量子コンピューティング・デバイスの効率を改善することができ、量子コンピューティング・デバイスのタイミング特性を改善することができ、量子コンピューティング・デバイスの電力特性を改善することができ、または量子コンピューティング・デバイスの別の特性を改善することができ、あるいはその組み合わせを行うことができる。

#### 【 0 0 2 7 】

図 3 は、本明細書に記載された 1 つまたは複数の実施形態に従って、例示的な非限定的システム 300 のブロック図を示している。本明細書に記載された他の実施形態で採用されている類似する要素の説明の繰り返しは、簡潔にするために省略されている。

#### 【 0 0 2 8 】

システム 300 は、量子コンピューティング・デバイスの等価電磁回路をシミュレートして応答関数を取得する設計プロセス 302 と、応答関数に基づいて量子コンピューティング・デバイスのハミルトニアン・データを取得するための設計プロセス 304 と、ハミルトニアン・データに基づいて量子コンピューティング・デバイスのレイアウトを生成するための設計プロセス 306 とを含んでいる。一実施形態では、ハミルトニアン・データは、設計プロセス 302 を介して取得された応答関数に基づいて（例えば、設計プロセス 304 を介して）取得され得る。ハミルトニアン・データは、例えば、量子コンピューティング・デバイスの電磁特性または量子コンピューティング・デバイスの 1 つまたは複数の位置でのエネルギーに関連付けられた情報あるいはその組み合わせに、関連付けられ得る。別の実施形態では、定義された基準を、設計プロセス 304 を介して取得されたハミルトニアン・データが満たしているということの決定に応答して、設計プロセス 302 を介して、等価電磁回路のシミュレーションが繰り返され得る。量子コンピューティング・デバイスのレイアウトは、設計プロセス 304 を介して取得されたハミルトニアン・データに基づいて、設計プロセス 306 を介して生成され得る。従来は、量子コンピューティング・デバイスの設計を容易にするために、量子コンピューティング・デバイスのレイアウトが描画され、量子コンピューティング・デバイスのレイアウトがシミュレートされるということが、理解されるべきである。これに対して、量子コンピューティング・デバイス設計ツール 102 は、シミュレーションのコストの削減またはシミュレーション時の計算能力の低減あるいはその両方を促進するために、設計プロセスを 302 介して等価電磁回路をシミュレートして応答関数を取得し、設計プロセス 304 を介して量子コンピューティング・デバイスのハミルトニアン・データを取得し、設計プロセス 306 を介して、ハミルトニアン・データに基づいて量子コンピューティング・デバイスのレイアウトを生成することができる。

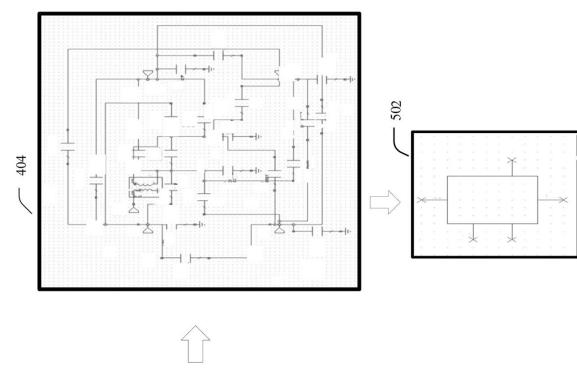

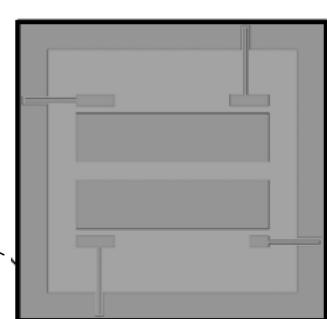

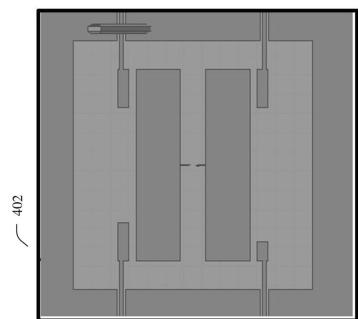

#### 【 0 0 2 9 】

図 4 は、本明細書に記載された 1 つまたは複数の実施形態に従って、例示的な非限定的システム 400 のブロック図を示している。本明細書に記載された他の実施形態で採用されている類似する要素の説明の繰り返しは、簡潔にするために省略されている。

#### 【 0 0 3 0 】

システム 400 は、量子デバイス素子 402 および電磁回路素子 404 を含んでいる。一実施形態では、モデル化コンポーネント 104 は、量子デバイス素子 402 から電磁回路素子 404 を生成することができる。量子デバイス素子 402 は、例えば、量子コンピューティング・デバイスの量子ビット素子、量子コンピューティング・デバイスの結合器、量子コンピューティング・デバイスの読み出し、量子コンピューティング・デバイスの

10

20

30

40

50

バス、または量子コンピューティング・デバイスの別の素子であることができる。量子デバイス素子 402 は、量子コンピューティング・デバイスの特定の部分（例えば、量子コンピューティング・デバイスの特定の領域）にも関連付けられ得る。1つの例では、量子デバイス素子 402 は、接合点のない超伝導トランズモン量子ビット・レイアウトであることができる。トランズモンは、電荷に関連するノイズに対する感受性の減少を備えるように設計された量子ビットであることができる。電磁回路素子 404 は、例えば、静電容量ネットワークであることができる。一実施形態では、1つまたは複数の静電容量値が、量子デバイス素子 402 の静的シミュレーションから決定され得る。

#### 【0031】

図 5 は、本明細書に記載された1つまたは複数の実施形態に従って、例示的な非限定的システム 500 のブロック図を示している。本明細書に記載された他の実施形態で採用されている類似する要素の説明の繰り返しは、簡潔にするために省略されている。

10

#### 【0032】

システム 500 は、量子デバイス素子 402、電磁回路素子 404、および概略素子 502 を含んでいる。一実施形態では、モデル化コンポーネント 104 が概略素子 502 を生成できる。概略素子 502 は、量子デバイス素子 402 に関連付けられた電磁回路素子 404 に基づいて生成され得る。一実施形態では、概略素子 502 は、電磁回路素子のライブラリに格納され得る。別の実施形態では、概略素子 502 は、量子デバイス素子 402 または量子デバイス素子 402 に関連付けられた量子デバイスあるいはその両方のシミュレーションを容易にするために、シミュレーション・ツールによって採用され得る。さらに、特定の実施形態では、モデル化コンポーネント 104 は、概略素子 502 に基づいて量子デバイス素子を識別するか、モデル化するか、あるいはその両方を行うことができる。1つの態様では、概略素子 502 は、電磁回路素子 404 の機能を表すことができる。例えば、概略素子 502 は、電磁回路素子 404 に対応する機能を有するブラック・ボックス・コンポーネントであることができる。

20

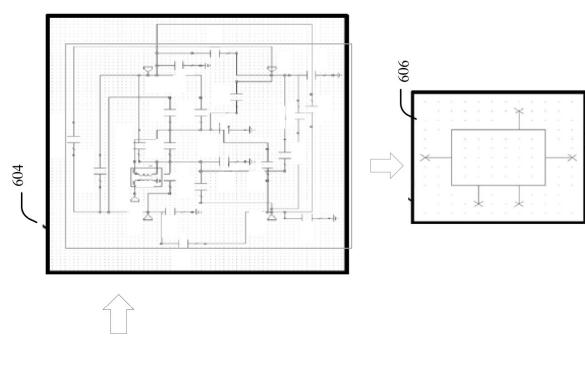

#### 【0033】

図 6 は、本明細書に記載された1つまたは複数の実施形態に従って、例示的な非限定的システム 600 のブロック図を示している。本明細書に記載された他の実施形態で採用されている類似する要素の説明の繰り返しは、簡潔にするために省略されている。

30

#### 【0034】

システム 600 は、量子デバイス素子 602、電磁回路素子 604、および概略素子 606 を含んでいる。一実施形態では、モデル化コンポーネント 104 は、電磁回路素子 604 または概略素子 606 あるいはその両方を生成することができる。1つの例では、量子デバイス素子 602 は、量子ビット・レイアウトであることができる。電磁回路素子 604 は、例えば、静電容量ネットワークであることができる。概略素子 606 は、量子デバイス素子 602 に関連付けられた電磁回路素子 604 に基づいて生成され得る。一実施形態では、概略素子 606 は、電磁回路素子のライブラリに格納され得る。別の実施形態では、概略素子 606 は、量子デバイス素子 602 または量子デバイス素子 602 に関連付けられた量子デバイスあるいはその両方のシミュレーションを容易にするために、シミュレーション・ツールによって採用され得る。さらに、特定の実施形態では、モデル化コンポーネント 104 は、概略素子 606 に基づいて量子デバイス素子を識別するか、モデル化するか、あるいはその両方を行うことができる。

40

#### 【0035】

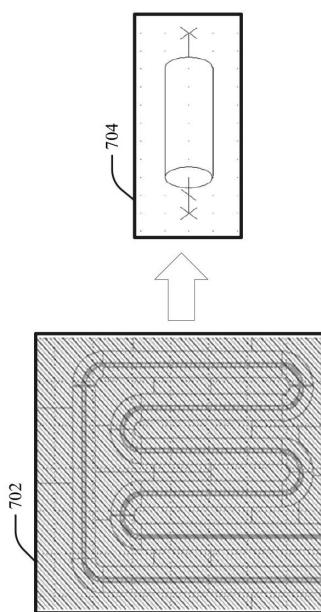

図 7 は、本明細書に記載された1つまたは複数の実施形態に従って、例示的な非限定的システム 700 のブロック図を示している。本明細書に記載された他の実施形態で採用されている類似する要素の説明の繰り返しは、簡潔にするために省略されている。

#### 【0036】

システム 700 は、量子デバイス素子 702 および電磁回路素子 704 を含んでいる。一実施形態では、モデル化コンポーネント 104 が電磁回路素子 704 を生成できる。特定の実施形態では、電磁回路素子 704 は概略素子であることもできる。1つの例では、

50

量子デバイス素子 702 は、量子コンピューティング・デバイスの一部であることができる。電磁回路素子 704 は、例えば、共振器素子であることができる。電磁回路素子 704 は、量子デバイス素子 702 から生成され得る。一実施形態では、電磁回路素子 704 は、電磁回路素子のライブラリに格納され得る。別の実施形態では、電磁回路素子 704 は、量子デバイス素子 702 または量子デバイス素子 702 に関連付けられた量子デバイスあるいはその両方のシミュレーションを容易にするために、シミュレーション・ツールによって採用され得る。さらに、特定の実施形態では、モデル化コンポーネント 104 は、電磁回路素子 704 に基づいて量子デバイス素子を識別するか、モデル化するか、あるいはその両方を行うことができる。

#### 【0037】

10

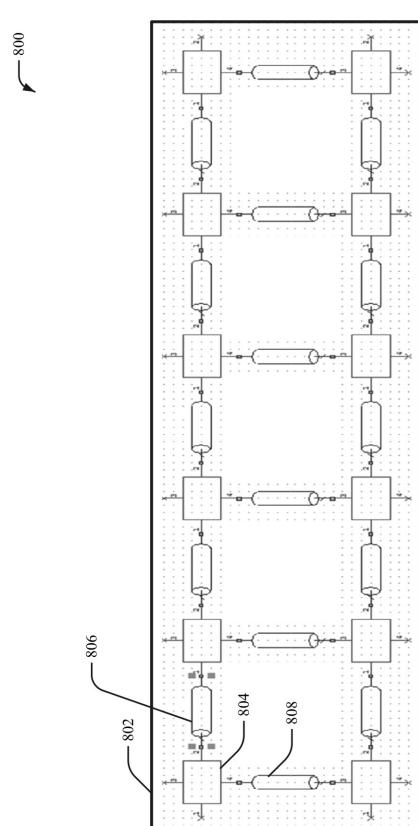

図 8 は、本明細書に記載された 1 つまたは複数の実施形態に従って、例示的な非限定的システム 800 のブロック図を示している。本明細書に記載された他の実施形態で採用されている類似する要素の説明の繰り返しは、簡潔にするために省略されている。

#### 【0038】

システム 800 は、量子コンピューティング・デバイスの等価電磁回路 802 を含んでいる。等価電磁回路 802 は、概略素子のセットとして形式設定された電磁回路素子のセットを含むことができる。例えば、等価電磁回路 802 は、第 1 の概略素子 804 として形式設定された第 1 の電磁回路素子、第 2 の概略素子 806 として形式設定された第 2 の電磁回路素子、第 3 の概略素子 808 として形式設定された第 3 の電磁回路素子などを含むことができる。1 つの例では、第 1 の概略素子 804 ( 例えば、第 1 の電磁回路素子 ) を、第 2 の電磁概略素子 806 ( 例えば、第 2 の電磁回路素子 ) および第 3 の概略素子 808 ( 例えば、第 3 の電磁回路素子 ) に接続することができる。1 つの態様では、等価電磁回路 802 の機能は、等価電磁回路 802 に関連付けられた量子コンピューティング・デバイスの機能に対応することができる。例えば、モデル化コンポーネント 104 は、量子コンピューティング・デバイスの 1 つまたは複数の量子デバイス素子をモデル化し、電磁回路素子のセットを等価電磁回路 802 内に生成することができる。

20

#### 【0039】

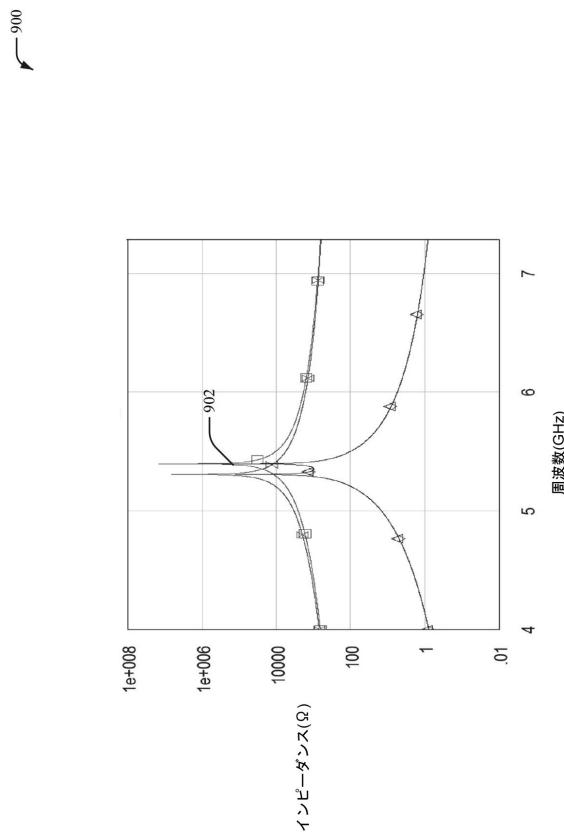

図 9 は、本明細書に記載された 1 つまたは複数の実施形態に従って、例示的な非限定的グラフ 900 のブロック図を示している。本明細書に記載された他の実施形態で採用されている類似する要素の説明の繰り返しは、簡潔にするために省略されている。

30

#### 【0040】

グラフ 900 は、本明細書に記載された 1 つまたは複数の実施形態に従って、応答関数 902 を示している。グラフ 900 の横軸は、周波数 ( G H z ) を示している。グラフ 900 の縦軸は、インピーダンス ( ) を示している。一実施形態では、応答関数 902 は、量子コンピューティング・デバイスのシミュレーション・コンポーネント 106 によって生成された応答関数であることができる。1 つの態様では、応答関数 902 に基づいて、量子コンピューティング・デバイスのハミルトニアン・データが決定され得る。応答関数 902 は、量子コンピューティング・デバイス内の 1 つまたは複数の位置でインピーダンスまたはアドミッタンスあるいはその両方に対応することができる。

#### 【0041】

40

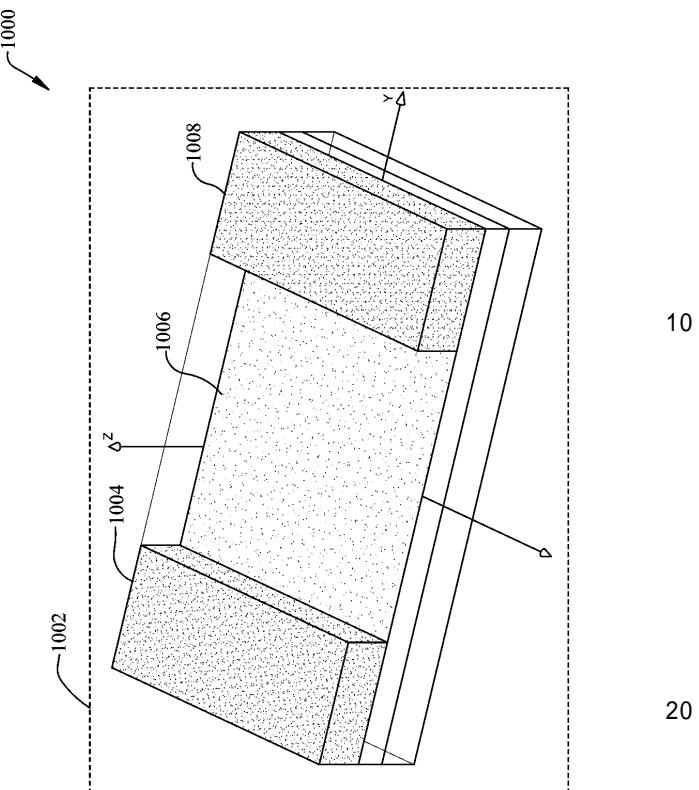

図 10 は、本明細書に記載された 1 つまたは複数の実施形態に従って、例示的な非限定的システム 1000 のブロック図を示している。本明細書に記載された他の実施形態で採用されている類似する要素の説明の繰り返しは、簡潔にするために省略されている。

#### 【0042】

システム 1000 は、量子コンピューティング・デバイス 1002 を含むことができる。例えば、量子コンピューティング・デバイス 1002 は、量子コンピューティング・デバイス 1002 の 1 つまたは複数の量子デバイス素子をモデル化するためにモデル化コンポーネント 104 によって採用された量子コンピューティング・デバイスのモデルであることができる。一実施形態では、量子コンピューティング・デバイス 1002 のモデルはコンピュータ・シミュレータによって生成され得る。コンピュータ・シミュレータは、例

50

えば、量子コンピューティング・デバイス 1002 に関連付けられた 1 つまたは複数の電磁場シミュレーションを実行する静的な場のシミュレータであることができる。量子コンピューティング・デバイス 1002 は、例えば、量子回路、量子プロセッサ、量子ビット・デバイス、量子ビット単位セル、または量子ビットを採用する別の種類のコンピューティング・デバイス、あるいはその組み合わせであることができる。1 つの態様では、量子コンピューティング・デバイス 1002 は、例えば、量子ビット素子、結合器素子、読み出し素子、バス素子、または量子コンピューティング・デバイス 1002 の別の素子などの、1 つまたは複数の量子デバイス素子を含むことができる。さらに、量子コンピューティング・デバイス 1002 は、量子物理学の原理に基づいて一連の計算を実行するマシンであることができる。例えば、量子コンピューティング・デバイス 1002 は、量子ビットを使用して情報をエンコードすることができる。1 つの実施形態では、量子コンピューティング・デバイス 1002 は、ハードウェア量子プロセッサ (hardware quantum processor) (例えば、ハードウェア超伝導量子プロセッサ (hardware superconducting quantum processor) ) であることができる。例えば、量子コンピューティング・デバイス 1002 は、量子ビットを使用して一連の命令スレッドを実行するハードウェア量子プロセッサであることができる。非限定的な例では、量子コンピューティング・デバイス 1002 の部分 1004 が第 1 の量子デバイス素子に対応することができ、量子コンピューティング・デバイス 1002 の部分 1006 が第 2 の量子デバイス素子に対応することができ、量子コンピューティング・デバイス 1002 の部分 1008 が第 3 の量子デバイス素子に対応することができる。

#### 【0043】

図 11 は、本明細書に記載された 1 つまたは複数の実施形態に従って、量子コンピューティング・デバイス設計を容易にするための、例示的な非限定的コンピュータ実装方法 1100 のフロー図を示している。1102 で、プロセッサに動作可能なように結合されたシステムによって (例えば、モデル化コンポーネント 104 によって)、量子コンピューティング・デバイスの量子デバイス素子が、量子コンピューティング・デバイスの電磁回路データを生成するための電磁回路素子としてモデル化される。量子デバイス素子データは、例えば、量子コンピューティング・デバイスの 1 つまたは複数の量子デバイス素子の機械可読記述であることができる。追加的または代替的に、量子デバイス素子データは、量子コンピューティング・デバイスの 1 つまたは複数の量子デバイス素子の 1 つまたは複数のモデルに関連付けられ得る。量子コンピューティング・デバイスは、例えば、量子回路、量子プロセッサ、量子ビット・デバイス、量子ビット単位セル、または量子ビットを採用する別の種類のコンピューティング・デバイス、あるいはその組み合わせであることができる。1 つまたは複数の量子デバイス素子からの量子デバイス素子は、例えば、量子コンピューティング・デバイスの量子ビット素子、量子コンピューティング・デバイスの結合器、量子コンピューティング・デバイスの読み出し、量子コンピューティング・デバイスのバス、または量子コンピューティング・デバイスの別の素子を含むことができる。一実施形態では、量子コンピューティング・デバイスの量子デバイス素子間の 1 つまたは複数の接続に関連付けられた情報を示す接続データが生成され得る。さらに、接続データに基づいて、量子コンピューティング・デバイスの電磁回路データが生成され得る。特定の実施形態では、電磁回路素子のライブラリに基づいて、量子コンピューティング・デバイスの量子デバイス素子が、電磁回路素子としてモデル化され得る。

#### 【0044】

1104 で、別の量子デバイス素子が存在するかどうかが判定され得る。「はい」である場合、コンピュータ実装方法 1100 が 1102 に戻る。「いいえ」である場合、コンピュータ実装方法 1100 が 1106 に進む。

#### 【0045】

1106 で、システムによって (例えば、シミュレーション・コンポーネント 106 によって)、電磁回路データを使用して量子コンピューティング・デバイスがシミュレートされ、量子コンピューティング・デバイスのパラメータのセットを示すパラメータ・デー

10

20

30

40

50

タを生成する。一実施形態では、電磁回路データを使用して量子コンピューティング・デバイスをシミュレートし、量子コンピューティング・デバイスの応答関数を示す応答関数データを生成することができる。さらに別の実施形態では、応答関数データに基づいて、ハミルトニアン・データが生成され得る。ハミルトニアン・データは、量子コンピューティング・デバイスのエネルギーまたは量子コンピューティング・デバイスの電磁特性あるいはその両方に関連付けられた情報を示すことができる。1つの態様では、ハミルトニアン・データは、量子コンピューティング・デバイスに関連するクロストーク、相互接続、コネクタ、プリント基板レイアウト、電気的バス、またはその他の電気的特性、あるいはその組み合わせの理解を促進することができる。

#### 【0046】

1108で、定義された基準をパラメータ・データが満たすかどうかが判定される。「いいえ」である場合、コンピュータ実装方法1100が1106に戻る。「はい」である場合、コンピュータ実装方法1100が1108に進む。

#### 【0047】

1110で、システムによって（例えば、設計コンポーネント202によって）、パラメータ・データに基づいて、量子コンピューティング・デバイスのレイアウトを示す設計データが生成される。一実施形態では、量子コンピューティング・デバイスのレイアウトは、パラメータ・データに基づいて変更され得る。設計データは、量子コンピューティング・デバイスのレイアウトを示すことができる。例えば、設計データは、量子コンピューティング・デバイス内の1つまたは複数のコンポーネントの位置を含むことができる。追加的または代替的に、設計データは、量子コンピューティング・デバイス内の1つまたは複数のコンポーネントの電気的パラメータを含むことができる。追加的または代替的に、設計データは、量子コンピューティング・デバイス内の1つまたは複数のコンポーネントの値または設定あるいはその両方を含むことができる。追加的または代替的に、設計データは、量子コンピューティング・デバイス内の1つまたは複数のコンポーネントのサイズ、形状、または配置、あるいはその組み合わせを含むことができる。一実施形態では、ハミルトニアン・データに基づいて設計データが生成され得る。特定の実施形態では、コンピュータ実装方法1100は、定義された基準をハミルトニアン・データが満たすということの決定に応答して、システムによって、電磁回路データを使用して量子コンピューティング・デバイスを再シミュレートすることを含むことができる。

#### 【0048】

図12は、本明細書に記載された1つまたは複数の実施形態に従って、量子コンピューティング・デバイス設計を容易にするための、例示的な非限定的コンピュータ実装方法1200のフロー図を示している。1202で、プロセッサに動作可能なように結合されたシステムによって（例えば、モデル化コンポーネント104によって）、1つまたは複数の量子デバイス素子がモデル化されて1つまたは複数の等価電磁回路素子を決定する。1204で、システムによって（例えば、モデル化コンポーネント104によって）、1つまたは複数の等価電磁回路素子に基づいて量子デバイスの等価電磁回路が生成される。1206で、システムによって（例えば、シミュレーション・コンポーネント106によって）、量子デバイスの等価電磁回路がシミュレートされて量子デバイスの応答関数を取得する。1208で、システムによって（例えば、シミュレーション・コンポーネント106によって）、応答関数を使用して量子デバイスのハミルトニアン・パラメータのセットが計算される。1210で、望ましいハミルトニアン・パラメータが取得されたかどうかが判定される。「いいえ」である場合、コンピュータ実装方法1200が1206に戻る。「はい」である場合、コンピュータ実装方法1200が1108に進む。1212で、システムによって（例えば、設計コンポーネント202によって）、少なくともハミルトニアン・パラメータのセットのサブセットを使用して量子デバイスのレイアウトが生成される。

#### 【0049】

説明を簡単にするために、一連の動作としてコンピュータ実装方法が示され、説明され

10

20

30

40

50

る。本革新技術が、示された動作によって、または動作の順序によって、あるいはその両方によって制限されず、例えば動作が、本明細書において提示されておらず、説明されていない他の動作と共に、さまざまな順序で、または同時に、あるいはその両方で発生できるということが、理解されるべきである。さらに、開示される対象に従ってコンピュータ実装方法を実装するために、示されているすべての動作が必要でなくてもよい。加えて、当業者は、コンピュータ実装方法が、代替として、状態図を介して相互に関連する一連の状態またはイベントとして表され得るということを理解するであろう。そのようなコンピュータ実装方法をコンピュータに輸送または転送するのを容易にするために、以下および本明細書全体を通じて開示されたコンピュータ実装方法を製品に格納できるということが、さらに理解されるべきである。製品という用語は、本明細書において使用されるとき、任意のコンピュータ可読記憶デバイスまたはコンピュータ可読記憶媒体からアクセスできるコンピュータ・プログラムを包含するよう意図されている。

#### 【0050】

さらに、少なくとも、量子デバイス（例えば、量子コンピューティング・デバイス）の設計データまたはレイアウトあるいはその両方を生成すること、電磁回路素子または等価電磁回路あるいはその両方をシミュレートすることなどが、電気的および機械的コンポーネントおよび回路の組み合わせから確立されるため、人間は、本明細書で開示された量子コンピューティング・デバイス設計ツール 102（例えば、モデル化コンポーネント 104、シミュレーション・コンポーネント 106、または設計コンポーネント 202、あるいはその組み合わせ）によって実行される処理を複製することも実行することもできない。例えば、人間は、設計データを生成すること、電磁回路素子または等価電磁回路あるいはその両方をシミュレートすることなどを、実行することができない。

#### 【0051】

開示される対象のさまざまな態様の背景を提供するために、図 13 および以下の説明は、開示される対象のさまざまな態様が実装され得る適切な環境の概要を示すよう意図されている。図 13 は、本明細書に記載された 1 つまたは複数の実施形態を容易にすることができる例示的な非限定的動作環境のブロック図を示している。本明細書に記載された他の実施形態で採用されている類似する要素の説明の繰り返しは、簡潔にするために省略されている。

#### 【0052】

図 13 を参照すると、本開示のさまざまな態様を実装するための適切な動作環境 1300 は、コンピュータ 1312 を含むこともできる。コンピュータ 1312 は、処理ユニット 1314、システム・メモリ 1316、およびシステム・バス 1318 を含むこともできる。システム・バス 1318 は、システム・メモリ 1316 を含むが、これに限定されないシステム・コンポーネントを、処理ユニット 1314 に結合する。処理ユニット 1314 は、さまざまな使用可能なプロセッサのいずれかができる。デュアル・マイクロプロセッサおよびその他のマルチプロセッサ・アーキテクチャが、処理ユニット 1314 として採用されてもよい。システム・バス 1318 は、ISA (Industry Standard Architecture)、MCA (Micro Channel Architecture)、EISA (Extended ISA)、IDE (Intelligent Drive Electronics)、VESA ローカル・バス (VLB : VESA Local Bus)、PCI (Peripheral Component Interconnect)、カードバス、ユニバーサル・シリアル・バス (USB : Universal Serial Bus)、AGP (Advanced Graphics Port)、FireWire (IEEE 1394)、および小型コンピュータ・システム・インターフェイス (SCSI : Small Computer Systems Interface) を含むが、これらに限定されない、任意のさまざまな使用可能なバス・アーキテクチャを使用する、メモリ・バスもしくはメモリ・コントローラ、ペリフェラル・バスもしくは外部バス、またはローカル・バス、あるいはその組み合わせを含む、複数の種類のバス構造のいずれかができる。

#### 【0053】

システム・メモリ 1316 は、揮発性メモリ 1320 および不揮発性メモリ 1322 を

10

20

30

40

50

含むこともできる。起動中などにコンピュータ 1312 内の要素間で情報を転送するための基本ルーチンを含んでいる基本入出力システム (BIOS : basic input/output system) が、不揮発性メモリ 1322 に格納される。コンピュータ 1312 は、取り外し可能 / 取り外し不可能な揮発性 / 不揮発性のコンピュータ記憶媒体を含むこともできる。例えば図 13 は、ディスク・ストレージ 1324 を示している。ディスク・ストレージ 1324 は、磁気ディスク・ドライブ、フロッピー (R) ・ディスク・ドライブ、テープ・ドライブ、Jaz ドライブ、Zip ドライブ、LS-100 ドライブ、フラッシュ・メモリ・カード、またはメモリ・スティックなどの、ただしこれらに限定されない、デバイスを含むこともできる。ディスク・ストレージ 1324 は、記憶媒体を、別々に、または他の記憶媒体と組み合わせて、含むことができる。システム・バス 1318 へのディスク・ストレージ 1324 の接続を容易にするために、インターフェイス 1326 などの、取り外し可能または取り外し不可能なインターフェイスが通常は使用される。図 13 は、ユーザと、適切な動作環境 1300 において説明された基本的なコンピュータ・リソースとの間の仲介として機能するソフトウェアも示している。そのようなソフトウェアは、例えば、オペレーティング・システム 1328 を含むこともできる。ディスク・ストレージ 1324 に格納できるオペレーティング・システム 1328 は、コンピュータ 1312 のリソースを制御し、割り当てるように動作する。

#### 【0054】

システムのアプリケーション 1330 は、プログラム・モジュール 1332 を介して、オペレーティング・システム 1328 によるリソースの管理を利用し、例えばシステム・メモリ 1316 またはディスク・ストレージ 1324 のいずれかに格納されたデータ 1334 をプログラムする。さまざまなオペレーティング・システムまたはオペレーティング・システムの組み合わせを使用して本開示が実装され得るということが、理解されるべきである。ユーザは、1つまたは複数の入力デバイス 1336 を介して、コマンドまたは情報をコンピュータ 1312 に入力する。入力デバイス 1336 は、マウス、トラックボール、スタイラス、タッチ・パッド、キーボード、マイクロホン、ジョイスティック、ゲーム・パッド、衛星放送受信アンテナ、スキャナ、TV チューナー・カード、デジタル・カメラ、デジタル・ビデオ・カメラ、Web カメラなどのポインティング・デバイスを含むが、これらに限定されない。これらおよびその他の入力デバイスは、インターフェイス・ポート 1338 を介してシステム・バス 1318 を通り、処理ユニット 1314 に接続する。インターフェイス・ポート 1338 は、例えば、シリアル・ポート、パラレル・ポート、ゲーム・ポート、およびユニバーサル・シリアル・バス (USB) を含む。出力デバイス 1340 は、入力デバイス 1336 と同じ種類のポートの一部を使用する。このようにして、例えば、USB ポートを使用して、入力をコンピュータ 1312 に提供し、コンピュータ 1312 から出力デバイス 1340 に情報を出力できる。出力アダプタ 1342 は、特殊なアダプタを必要とする出力デバイス 1340 の中でも特に、モニタ、スピーカ、およびプリンタのような何らかの出力デバイス 1340 が存在することを示すために提供される。出力アダプタ 1342 の例としては、出力デバイス 1340 とシステム・バス 1318 の間の接続の手段を提供するビデオ・カードおよびサウンド・カードが挙げられるが、これらに限定されない。リモート・コンピュータ 1344 などの、他のデバイスまたはデバイスのシステムあるいはその両方が、入力機能および出力機能の両方を提供するということに、注意するべきである。

#### 【0055】

コンピュータ 1312 は、リモート・コンピュータ 1344 などの1つまたは複数のリモート・コンピュータへの論理接続を使用して、ネットワーク環境内で動作できる。リモート・コンピュータ 1344 は、コンピュータ、サーバ、ルータ、ネットワーク PC、ワークステーション、マイクロプロセッサベースの機器、ピア・デバイス、またはその他の一般的なネットワーク・ノードなどであることができ、通常は、コンピュータ 1312 に関連して説明された要素の多くまたはすべてを含むこともできる。簡潔にするために、メモリ・ストレージ・デバイス 1346 のみが、リモート・コンピュータ 1344 と共に示

されている。リモート・コンピュータ 1344 は、ネットワーク・インターフェイス 1348 を介してコンピュータ 1312 に論理的に接続されてから、通信接続 1350 を介して物理的に接続される。ネットワーク・インターフェイス 1348 は、ローカル・エリア・ネットワーク (LAN : local-area networks)、広域ネットワーク (WAN : wide-area networks)、セルラー・ネットワークなどの、有線通信ネットワークまたは無線通信ネットワークあるいはその両方を包含する。LAN 技術は、光ファイバ分散データ・インターフェイス (FDDI : Fiber Distributed Data Interface)、銅線分散データ・インターフェイス (CDDI : Copper Distributed Data Interface)、トークン・リングなどを含む。WAN 技術は、ポイントツーポイント・リンク、総合デジタル通信網 (ISDN : Integrated Services Digital Networks) およびその変形などの回路交換網、パケット交換網、およびデジタル加入者回線 (DSL : Digital Subscriber Lines) を含むが、これらに限定されない。通信接続 1350 は、ネットワーク・インターフェイス 1348 をシステム・バス 1318 に接続するために採用されたハードウェア / ソフトウェアのことを指す。通信接続 1350 は、説明を明確にするために、コンピュータ 1312 内に示されているが、コンピュータ 1312 の外部に存在することもできる。ネットワーク・インターフェイス 1348 に接続するためのハードウェア / ソフトウェアは、単に例示の目的で、通常の電話の等級のモデム、ケーブル・モデム、および DSL モデムを含むモデム、ISDN アダプタ、およびイーサネット (R) ・カードなどの、内部および外部の技術を含むこともできる。

#### 【0056】

本発明は、任意の可能な統合の技術的詳細レベルで、システム、方法、装置、またはコンピュータ・プログラム製品、あるいはその組み合わせであってよい。コンピュータ・プログラム製品は、プロセッサに本発明の態様を実行させるためのコンピュータ可読プログラム命令を含んでいるコンピュータ可読記憶媒体を含むことができる。コンピュータ可読記憶媒体は、命令実行デバイスによって使用するための命令を保持および格納できる有形のデバイスであることができる。コンピュータ可読記憶媒体は、例えば、電子ストレージ・デバイス、磁気ストレージ・デバイス、光ストレージ・デバイス、電磁ストレージ・デバイス、半導体ストレージ・デバイス、またはこれらの任意の適切な組み合わせであることができるが、これらに限定されない。コンピュータ可読記憶媒体のさらに具体的な例の非網羅的リストは、ポータブル・コンピュータ・ディスクケット、ハード・ディスク、ランダム・アクセス・メモリ (RAM : random access memory)、読み取り専用メモリ (ROM : read-only memory)、消去可能プログラマブル読み取り専用メモリ (EPROM : erasable programmable read-only memory またはフラッシュ・メモリ)、静态・ランダム・アクセス・メモリ (SRAM : static random access memory)、ポータブル・コンパクト・ディスク読み取り専用メモリ (CD-ROM : compact disc read-only memory)、デジタル多用途ディスク (DVD : digital versatile disk)、メモリ・スティック、フロッピー (R) ・ディスク、パンチカードまたは命令が記録されている溝の中の隆起構造などの機械的にエンコードされるデバイス、およびこれらの任意の適切な組み合わせを含むことができる。本明細書において使用されるとき、コンピュータ可読記憶媒体は、それ自体が、電波またはその他の自由に伝搬する電磁波、導波管またはその他の送信媒体を伝搬する電磁波 (例えば、光ファイバ・ケーブルを通過する光パルス)、あるいはワイヤを介して送信される電気信号などの一過性の信号であると解釈されるべきではない。

#### 【0057】

本明細書に記載されたコンピュータ可読プログラム命令は、コンピュータ可読記憶媒体から各コンピューティング・デバイス / 処理デバイスへ、またはネットワーク (例えば、インターネット、ローカル・エリア・ネットワーク、広域ネットワーク、または無線ネットワーク、あるいはその組み合わせ) を介して外部コンピュータまたは外部ストレージ・デバイスへダウンロードされ得る。このネットワークは、銅伝送ケーブル、光伝送ファイバ、無線送信、ルータ、ファイアウォール、スイッチ、ゲートウェイ・コンピュータ、ま

10

20

30

40

50

たはエッジ・サーバ、あるいはその組み合わせを備えることができる。各コンピューティング・デバイス/処理デバイス内のネットワーク・アダプタ・カードまたはネットワーク・インターフェイスは、コンピュータ可読プログラム命令をネットワークから受信し、それらのコンピュータ可読プログラム命令を各コンピューティング・デバイス/処理デバイス内のコンピュータ可読記憶媒体に格納するために転送する。本発明の動作を実行するためのコンピュータ可読プログラム命令は、アセンブラー命令、命令セット・アーキテクチャ (ISA : instruction-set-architecture) 命令、マシン命令、マシン依存命令、マイクロコード、ファームウェア命令、状態設定データ、集積回路のための構成データ、あるいは、Smalltalk (R)、C++などのオブジェクト指向プログラミング言語、および「C」プログラミング言語または同様のプログラミング言語などの手続き型プログラミング言語を含む1つまたは複数のプログラミング言語の任意の組み合わせで記述されたソース・コードまたはオブジェクト・コードであることができる。コンピュータ可読プログラム命令は、ユーザのコンピュータ上で全体的に実行すること、ユーザのコンピュータ上でスタンドアロン・ソフトウェア・パッケージとして部分的に実行すること、ユーザのコンピュータ上およびリモート・コンピュータ上でそれぞれ部分的に実行すること、あるいはリモート・コンピュータ上またはサーバ上で全体的に実行することができる。後者のシナリオでは、リモート・コンピュータは、ローカル・エリア・ネットワーク (LAN) または広域ネットワーク (WAN) を含む任意の種類のネットワークを介してユーザのコンピュータに接続することができ、または接続は、( 例えは、インターネット・サービス・プロバイダを使用してインターネットを介して ) 外部コンピュータに対して行われ得る。一部の実施形態では、本発明の態様を実行するために、例えはプログラマブル論理回路、フィールドプログラマブル・ゲート・アレイ (FPGA : field-programmable gate arrays)、またはプログラマブル・ロジック・アレイ (PLA : programmable logic arrays) を含む電子回路は、コンピュータ可読プログラム命令の状態情報を利用することによって、電子回路をカスタマイズするためのコンピュータ可読プログラム命令を実行することができる。

#### 【 0058 】

本発明の態様は、本明細書において、本発明の実施形態に従って、方法、装置 (システム)、およびコンピュータ・プログラム製品のフローチャート図またはブロック図あるいはその両方を参照して説明される。フローチャート図またはブロック図あるいはその両方の各ブロック、ならびにフローチャート図またはブロック図あるいはその両方に含まれるブロックの組み合わせが、コンピュータ可読プログラム命令によって実装され得るということが理解されるであろう。これらのコンピュータ可読プログラム命令は、コンピュータまたはその他のプログラム可能なデータ処理装置のプロセッサを介して実行される命令が、フローチャートまたはブロック図あるいはその両方のブロックに指定される機能 / 動作を実施する手段を作り出すべく、汎用コンピュータ、専用コンピュータ、または他のプログラム可能なデータ処理装置のプロセッサに提供されてマシンを作り出すものであることができる。これらのコンピュータ可読プログラム命令は、命令が格納されたコンピュータ可読記憶媒体がフローチャートまたはブロック図あるいはその両方のブロックに指定される機能 / 動作の態様を実施する命令を含んでいる製品を備えるように、コンピュータ可読記憶媒体に格納され、コンピュータ、プログラム可能なデータ処理装置、または他のデバイス、あるいはその組み合わせに特定の方式で機能するように指示できるものであることもできる。コンピュータ可読プログラム命令は、コンピュータ上、その他のプログラム可能な装置上、またはその他のデバイス上で実行される命令が、フローチャートまたはブロック図あるいはその両方のブロックに指定される機能 / 動作を実施するように、コンピュータ実装プロセスを作り出すべく、コンピュータ、その他のプログラム可能なデータ処理装置、またはその他のデバイスに読み込まれ、コンピュータ上、その他のプログラム可能な装置上、またはその他のデバイス上で一連の操作可能な動作を実行させるものであることもできる。

#### 【 0059 】

10

20

30

40

50

図内のフローチャートおよびブロック図は、本発明のさまざまな実施形態に従って、システム、方法、およびコンピュータ・プログラム製品の可能な実装のアーキテクチャ、機能、および動作を示す。これに関連して、フローチャートまたはブロック図内の各ブロックは、規定された論理機能を実装するための1つまたは複数の実行可能な命令を含んでいる、命令のモジュール、セグメント、または部分を表すことができる。一部の代替の実装では、ブロックに示された機能は、図に示された順序とは異なる順序で発生することができる。例えば、連続して示された2つのブロックは、実際には、含まれている機能に応じて、実質的に同時に実行されるか、または場合によっては逆の順序で実行され得る。ブロック図またはフローチャート図あるいはその両方の各ブロック、ならびにブロック図またはフローチャート図あるいはその両方に含まれるブロックの組み合わせは、規定された機能または動作を実行するか、または専用ハードウェアとコンピュータ命令の組み合わせを実行する専用ハードウェアベースのシステムによって実装され得るということにも注意する。

#### 【0060】

上記では、1つのコンピュータまたは複数のコンピュータあるいはその両方で実行されるコンピュータ・プログラム製品のコンピュータ実行可能命令との一般的な関連において、対象が説明されたが、当業者は、本開示がその他のプログラム・モジュールと組み合わせられるか、またはその他のプログラム・モジュールと組み合わせて実装され得るということを認識するであろう。通常、プログラム・モジュールは、特定のタスクを実行するか、または特定の抽象データ型を実装するか、あるいはその両方を行うルーチン、プログラム、コンポーネント、データ構造などを含む。さらに、当業者は、本発明のコンピュータ実装方法が、シングルプロセッサ・コンピュータ・システムまたはマルチプロセッサ・コンピュータ・システム、ミニコンピューティング・デバイス、メインフレーム・コンピュータ、コンピュータ、ハンドヘルド・コンピューティング・デバイス（例えば、PDA、電話）、マイクロプロセッサベースまたはプログラム可能な家庭用電化製品または産業用電子機器などを含む、その他のコンピュータ・システム構成を使用して実践され得るということを理解するであろう。示された態様は、通信ネットワークを介してリンクされたりモード処理デバイスによってタスクが実行される、分散コンピューティング環境内で実践されてもよい。ただし、本開示の態様の全部ではないとしても一部は、スタンドアロン・コンピュータ上で実践され得る。分散コンピューティング環境において、プログラム・モジュールは、ローカルおよびリモートの両方のメモリ・ストレージ・デバイスに配置され得る。

#### 【0061】

本出願において使用されるとき、「コンポーネント」、「システム」、「プラットフォーム」、「インターフェイス」などの用語は、1つまたは複数の特定の機能を含むコンピュータ関連の実体または操作可能なマシンに関連する実体を指すことができるか、またはそれらの実体を含むことができるか、あるいはその両方が可能である。本明細書で開示された実体は、ハードウェア、ハードウェアとソフトウェアの組み合わせ、ソフトウェア、または実行中のソフトウェアのいずれかであることができる。例えば、コンポーネントは、プロセッサ上で実行されるプロセス、プロセッサ、オブジェクト、実行ファイル、実行のスレッド、プログラム、またはコンピュータ、あるいはその組み合わせであることができるが、これらに限定されない。例として、サーバ上で実行されるアプリケーションおよびサーバの両方が、コンポーネントであることができる。1つまたは複数のコンポーネントが、プロセス内または実行のスレッド内あるいはその両方に存在することができ、コンポーネントは、コンピュータ上に局在するか、または2つ以上のコンピュータ間で分散されるか、あるいはその両方が可能である。別の例では、各コンポーネントは、さまざまなデータ構造が格納されているさまざまなコンピュータ可読媒体から実行できる。コンポーネントは、1つまたは複数のデータ・パケット（例えば、ローカル・システム内または分散システム内の別のコンポーネントと情報をやりとりするか、またはインターネットなどのネットワークを経由して、信号を介して他のシステムと情報をやりとりするか、あるいは

10

20

30

40

50

はその両方によって情報をやりとりする、1つのコンポーネントからのデータ)を含んでいる信号などに従って、ローカルまたはリモートあるいはその両方のプロセスを介して通信できる。別の例として、コンポーネントは、電気または電子回路によって操作される機械的部品によって提供される特定の機能を有する装置であることができ、プロセッサによって実行されるソフトウェア・アプリケーションまたはファームウェア・アプリケーションによって操作される。そのような場合、プロセッサは、装置の内部または外部に存在することができ、ソフトウェア・アプリケーションまたはファームウェア・アプリケーションの少なくとも一部を実行できる。さらに別の例として、コンポーネントは、機械的部品を含まない電子コンポーネントを介して特定の機能を提供する装置であることができ、それらの電子コンポーネントは、電子コンポーネントの機能の少なくとも一部を与えるソフトウェアまたはファームウェアを実行するためのプロセッサまたはその他の手段を含むことができる。1つの態様では、コンポーネントは、例えばクラウド・コンピューティング・システム内で、仮想マシンを介して電子コンポーネントをエミュレートすることができる。

#### 【0062】

加えて、「または」という用語は、排他的論理和ではなく、包含的論理和を意味するよう意図されている。すなわち、特に指定されない限り、または文脈から明らかでない限り、「XがAまたはBを採用する」は、自然な包含的順列のいずれかを意味するよう意図されている。すなわち、XがAを採用するか、XがBを採用するか、またはXがAおよびBの両方を採用する場合、「XがAまたはBを採用する」が、前述の事例のいずれかにおいて満たされる。さらに、本明細書および添付の図面において使用される冠詞「a」および「a n」は、単数形を対象にすることが特に指定されない限り、または文脈から明らかでない限り、「1つまたは複数」を意味すると一般に解釈されるべきである。本明細書において使用されるとき、「例」または「例示的」あるいはその両方の用語は、例、事例、または実例となることを意味するために使用される。誤解を避けるために、本明細書で開示された対象は、そのような例によって限定されない。加えて、「例」または「例示的」あるいはその両方として本明細書に記載された任意の態様または設計は、他の態様または設計よりも好ましいか、または有利であると必ずしも解釈されず、当業者に知られている同等の例示的な構造および技術を除外するよう意図されていない。

#### 【0063】

本明細書において使用されるとき、「プロセッサ」という用語は、シングルコア・プロセッサと、ソフトウェアのマルチスレッド実行機能を備えるシングルプロセッサと、マルチコア・プロセッサと、ソフトウェアのマルチスレッド実行機能を備えるマルチコア・プロセッサと、ハードウェアのマルチスレッド技術を備えるマルチコア・プロセッサと、並列プラットフォームと、分散共有メモリを備える並列プラットフォームとを含むが、これらに限定されない、実質的に任意の計算処理ユニットまたはデバイスを指すことができる。さらに、プロセッサは、集積回路、特定用途向け集積回路 (ASIC : application specific integrated circuit)、デジタル信号プロセッサ (DSP : digital signal processor)、フィールド・プログラマブル・ゲート・アレイ (FPGA : field programmable gate array)、プログラマブル・ロジック・コントローラ (PLC : programmable logic controller)、複合プログラム可能論理デバイス (CPLD : complex programmable logic device)、個別のゲートまたはトランジスタ論理、個別のハードウェア・コンポーネント、あるいは本明細書に記載された機能を実行するように設計されたこれらの任意の組み合わせを指すことができる。さらに、プロセッサは、空間利用を最適化し、ユーザ機器の性能を向上するために、分子および量子ドットベースのトランジスタ、スイッチ、およびゲートなどの、ただしこれらに限定されない、ナノスケール・アーキテクチャを利用することができる。プロセッサは、計算処理ユニットの組み合わせとして実装されてもよい。本開示では、コンポーネントの動作および機能に関連する「ストア」、「ストレージ」、「データ・ストア」、「データ・ストレージ」、「データベース」、および実質的に任意のその他の情報格納コンポーネントなどの用語は、「メモリ・コンポーネン

ト」、「メモリ」内に具現化された実体、またはメモリを備えているコンポーネントを指すために使用される。本明細書に記載されたメモリまたはメモリ・コンポーネントあるいはその両方が、揮発性メモリまたは不揮発性メモリのいずれかであることができ、あるいは揮発性メモリおよび不揮発性メモリの両方を含むことができるということが、理解されるべきである。不揮発性メモリの例としては、読み取り専用メモリ (ROM)、プログラマブルROM (PROM)、電気的プログラマブルROM (EPROM)、電気的消去可能ROM (EEPROM)、フラッシュ・メモリ、または不揮発性ランダム・アクセス・メモリ (RAM) (例えば、強誘電体RAM (FeRAM)) が挙げられるが、これらに限定されない。揮発性メモリは、例えば外部キャッシュ・メモリとして機能できる、RAMを含むことができる。例えばRAMは、シンクロナスRAM (SRAM)、ダイナミックRAM (DRAM)、シンクロナスDRAM (SDRAM)、ダブル・データ・レートSDRAM (DDR SDRAM)、拡張SDRAM (ESDRAM)、シンクリングDRAM (SLDRAM)、ダイレクト・ラムバスRAM (DRRAM)、ダイレクト・ラムバス・ダイナミックRAM (DRDRAM)、およびラムバス・ダイナミックRAM (RDRAM : Rambus dynamic RAM) などの、ただしこれらに限定されない、多くの形態で利用可能である。さらに、本明細書において開示されたシステムまたはコンピュータ実装方法のメモリ・コンポーネントは、これらおよび任意のその他の適切な種類のメモリを含むが、これらに限定されない、メモリを含むよう意図されている。

#### 【0064】

前述した内容は、システムおよびコンピュータ実装方法の単なる例を含んでいる。当然ながら、本開示を説明する目的で、コンポーネントまたはコンピュータ実装方法の考えられるすべての組み合わせについて説明することは不可能であるが、当業者は、本開示の多くのその他の組み合わせおよび並べ替えが可能であるということを認識できる。さらに、「含む」、「有する」、「所有する」などの用語が、発明を実施するための形態、特許請求の範囲、付録、および図面において使用される範囲では、それらの用語は、「備えている」が特許請求における暫定的な用語として使用されるときに解釈されるような、用語「備えている」と同様の方法で、包含的であるよう意図されている。

#### 【0065】

さまざまな実施形態の説明は、例示の目的で提示されているが、網羅的であることは意図されておらず、開示された実施形態に限定されない。記載された実施形態の範囲および思想を逸脱することなく多くの変更および変形が可能であることは、当業者にとって明らかであろう。本明細書で使用された用語は、実施形態の原理、実際の適用、または市場で見られる技術を超える技術的改良を最も適切に説明するため、または他の当業者が本明細書で開示された実施形態を理解できるようにするために選択されている。

10

20

30

40

50

## 【図面】

### 【図 1】

【 図 2 】

【 义 3 】

【 4 】

10

20

30

40

50

【図 5】

【図 6】

10

20

【図 7】

【図 8】

30

40

50

【図 9】

【図 10】

【図 11】

【図 12】

【図 1 3】

10

20

30

40

50

---

フロントページの続き

(72)発明者 バイク、ハンマー

アメリカ合衆国 10598 ニューヨーク州ヨークタウン・ハイツ キッチャワン・ロード 1101

(72)発明者 ソルグン、フィラット

アメリカ合衆国 10598 ニューヨーク州ヨークタウン・ハイツ キッチャワン・ロード 1101

(72)発明者 オリヴァデーセ、サルヴァトーレ、ベルナルド

アメリカ合衆国 10598 ニューヨーク州ヨークタウン・ハイツ キッチャワン・ロード 1101

(72)発明者 サンドバーグ、マーティン

アメリカ合衆国 10598 ニューヨーク州ヨークタウン・ハイツ キッチャワン・ロード 1101

(72)発明者 ガンベッタ、ジェイ

アメリカ合衆国 10598 ニューヨーク州ヨークタウン・ハイツ キッチャワン・ロード 1101

審査官 松浦 功

(56)参考文献

米国特許出願公開第 2017/0228483 (U.S., A1)

国際公開第 2017/078731 (WO, A1)

特開 2017-059071 (JP, A)

特開 2000-348082 (JP, A)

国際公開第 2005/117127 (WO, A1)

NIGG, S.E. et al. , Black-Box Superconducting Circuit Quantization , Physical Review Letters [online] , American Physical Society , 2012年06月12日 , Vol. 108, No. 24 , pp. 240502-1 - 240502-5 , [検索日 2022.06.30] , インターネット , U R L : <https://journals.aps.org/prl/abstract/10.1103/PhysRevLett.108.240502>

(58)調査した分野 (Int.Cl. , DB名)

G 06 F 30/30 - 30/398

G 06 N 10/00 - 10/80

Google Scholar