(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6647285号

(P6647285)

(45) 発行日 令和2年2月14日(2020.2.14)

(24) 登録日 令和2年1月16日(2020.1.16)

(51) Int.Cl.

F 1

|                    |                  |             |      |

|--------------------|------------------|-------------|------|

| <b>G06F 15/78</b>  | <b>(2006.01)</b> | G06F 15/78  | 517  |

| <b>G06F 11/30</b>  | <b>(2006.01)</b> | G06F 11/30  | 140H |

| <b>G06F 11/07</b>  | <b>(2006.01)</b> | G06F 11/07  | 140H |

| <b>G06F 1/3206</b> | <b>(2019.01)</b> | G06F 1/3206 |      |

請求項の数 12 (全 24 頁)

(21) 出願番号 特願2017-511288 (P2017-511288)

(86) (22) 出願日 平成27年9月4日 (2015.9.4)

(65) 公表番号 特表2017-533493 (P2017-533493A)

(43) 公表日 平成29年11月9日 (2017.11.9)

(86) 國際出願番号 PCT/US2015/048707

(87) 國際公開番号 WO2016/040192

(87) 國際公開日 平成28年3月17日 (2016.3.17)

審査請求日 平成30年8月16日 (2018.8.16)

(31) 優先権主張番号 14/484,125

(32) 優先日 平成26年9月11日 (2014.9.11)

(33) 優先権主張国・地域又は機関

米国(US)

(73) 特許権者 507364838

クアルコム、インコーポレイテッド

アメリカ合衆国 カリフォルニア 921

21 サンディエゴ モアハウス ドラ

イブ 5775

(74) 代理人 100108453

弁理士 村山 靖彦

(74) 代理人 100163522

弁理士 黒田 晋平

(72) 発明者 ジェフリー・デイヴィッド・シャベル

アメリカ合衆国・カリフォルニア・921

21・サン・ディエゴ・モアハウス・ドラ

イブ・5775

最終頁に続く

(54) 【発明の名称】システムオンチップのサブシステムの外部アクセス検出および回復のためのシステムおよび方法

## (57) 【特許請求の範囲】

## 【請求項 1】

ポータブルコンピューティングデバイス(PCD)におけるシステムオンチップ(SoC)内の複数の処理サブシステムのうちの少なくとも1つの処理サブシステムでの外部アクセス検出および回復のための方法であって、

メモリ、センサ、およびモニタモジュールと通信しているプロセッサを備えた、前記SoCの少なくとも2つの処理サブシステムの各々を、前記SoCが低電力状態である間、互いおよび前記SoCの残部とは独立しておよび電気的に絶縁されて第1のモードで動作させるステップと、

前記SoCの前記少なくとも2つの処理サブシステムの各々において、

10

前記モニタモジュールを用いて、当該処理サブシステムの外部の構成要素への前記プロセッサによるアクセス要求を検出するステップと、

前記検出されたアクセス要求に応答して、前記モニタモジュールから前記プロセッサに、当該処理サブシステムの外部の構成要素への前記プロセッサによるアクセス要求が検出されたことを通知する通知信号を送るステップと、

前記通知信号に応答して、当該処理サブシステムの外部の前記構成要素への前記検出されたアクセス要求が、当該処理サブシステムのプロセッサ上または当該処理サブシステム内で動作している何らかのコードまたはルーチンにおけるエラーの結果であるかどうかを、前記プロセッサによって決定するステップと、

前記検出されたアクセス要求が前記エラーの結果ではないと決定した場合に、前記SoC

20

を全電力状態に入らせるとともに、当該処理サブシステムを、当該処理サブシステムが当該処理サブシステムの外部の前記構成要素にアクセスすることを可能にする第2のモードで動作させるステップと、

前記検出されたアクセス要求が前記エラーの結果であると決定した場合に、当該処理サブシステムの前記プロセッサを用いてエラーを訂正しようと努めるためにエラー処理ルーチンを起動するステップと

を含む、方法。

#### 【請求項 2】

前記SoCを全電力状態に入らせることが、

当該処理サブシステムの前記モニタモジュールから前記SoCの電力マネージャに信号を送って、前記電力マネージャをアクティブにすること

をさらに含む、請求項1に記載の方法。

10

#### 【請求項 3】

前記モニタモジュールが、状態機械と通信しているハードウェアモニタを備え、当該処理サブシステムを前記第2のモードで動作させるステップが、前記モニタモジュールが前記状態機械をアクティブにして、当該処理サブシステムの絶縁ハードウェアを無効にするステップをさらに含む、請求項1に記載の方法。

#### 【請求項 4】

前記状態機械が、前記モニタモジュールの外部にある、請求項3に記載の方法。

#### 【請求項 5】

当該処理サブシステムの外部の前記構成要素がメモリである、請求項1に記載の方法。

20

#### 【請求項 6】

前記センサが、前記PCDの加速度計またはジャイロスコープのうちの少なくとも1つと通信している、請求項1に記載の方法。

#### 【請求項 7】

請求項1～6のいずれか一項に記載の方法を実施するための命令を含むコンピュータプログラム。

#### 【請求項 8】

ポータブルコンピューティングデバイス(PCD)におけるシステムオンチップ(SoC)内の複数の処理サブシステムのうちの少なくとも1つの処理サブシステムでの外部アクセス検出および回復のためのコンピュータシステムであって、

30

メモリ、およびセンサと通信しているプロセッサを備えた、前記SoCの少なくとも2つの処理サブシステムの各々を、前記SoCが低電力状態である間、互いおよび前記SoCの残部とは独立しておよび電気的に絶縁されて第1のモードで動作させるための手段を備え、

前記SoCの前記少なくとも2つの処理サブシステムの各々が、

当該処理サブシステムの外部の構成要素への前記プロセッサによるアクセス要求を検出するための手段と、

前記検出されたアクセス要求に応答して、当該処理サブシステムの外部の構成要素への前記プロセッサによるアクセス要求が検出されたことを通知する通知信号を前記プロセッサに送るための手段と、

40

前記通知信号に応答して、当該処理サブシステムの外部の前記構成要素への前記検出されたアクセス要求が、当該処理サブシステムのプロセッサ上または当該処理サブシステム内で動作している何らかのコードまたはルーチンにおけるエラーの結果であるかどうかを、前記プロセッサによって決定するための手段と、

前記検出されたアクセス要求が前記エラーの結果ではないと決定した場合に、前記SoCを全電力状態に入らせるための手段と、

前記検出されたアクセス要求が前記エラーの結果ではないと決定した場合に、当該処理サブシステムを、当該処理サブシステムが当該処理サブシステムの外部の前記構成要素にアクセスすることを可能にする第2のモードで動作させるための手段と、

前記検出されたアクセス要求が前記エラーの結果であると決定した場合に、当該処理サ

50

システムの前記プロセッサを用いてエラーを訂正しようと努めるためにエラー処理ルーチンを起動するための手段と

を備える、システム。

【請求項 9】

前記SoCを全電力状態に入らせるための前記手段が、

当該処理サブシステムから前記SoCの電力マネージャに信号を送って、前記電力マネージャをアクティブにするための手段

をさらに含む、請求項8に記載のシステム。

【請求項 10】

当該処理サブシステムを前記第2のモードで動作させるための前記手段が、当該処理サブシステムの絶縁ハードウェアを無効にするための手段をさらに含む、請求項8に記載のシステム。 10

【請求項 11】

当該処理サブシステムの外部の前記構成要素がメモリである、請求項8に記載のシステム。

【請求項 12】

前記センサが、前記PCDの加速度計またはジャイロスコープのうちの少なくとも1つと通信している、請求項8に記載のシステム。

【発明の詳細な説明】

【技術分野】

20

【0001】

本発明は、システムオンチップのサブシステムの外部アクセス検出および回復のためのシステムおよび方法に関する。

【背景技術】

【0002】

ワイヤレス信号を含めた様々な通信媒体を介して他のデバイスと通信する、プロセッサを備えたデバイスが至る所にある。ポータブルコンピューティングデバイス(PCD)を含めてモバイルデバイスは、ワイヤレス、アナログ、デジタル、および他の手段により、様々な他のデバイスと通信するために使用される場合がある。これらのモバイルデバイスは、モバイル電話、携帯情報端末(PDA)、ポータブルゲームコンソール、パームトップコンピュータ、タブレットコンピュータ、および他のポータブル電子デバイスを含む場合がある。

30

【0003】

主要機能に加えて、PCDは、ゲームのダウンロードおよびプレイ、音楽のダウンロードおよび再生、ビデオのダウンロードおよび視聴、全地球測位システム(GPS)ナビゲーション、ウェブブラウジング、ならびに予定表およびアドレス帳アプリケーションなどのアプリケーション、電子財布ソフトウェア、その他の実行のために、使用される場合もある。

【0004】

これらのますます増加する用途およびより高い性能の要求に応えるために、現代のPCDは一般に、PCDの様々な機能を制御または実行するための、1つまたは複数のサブシステムまたはコア(たとえば、中央処理ユニット、グラフィックス処理ユニットなど)を備えたシステムオンチップ(SoC)を含んでいる。しかしながら、各コア/CPUおよびSoC自体を動作させると、PCD上の電力消費を増大させ、バッテリー寿命を減らす、PCDのタッチ温度を上げる、サービスを低下させる、その他となる。 40

【0005】

SoCおよび/またはそのサブシステムもしくはコアによって消費される電力を減らすために、様々な低電力または省電力モード戦略が実施してきた。たとえば、PCDがエンドユーザーによってアクティブに使用されていないとき、いくつかのSoCは、SoCがオフにされる期間を含むことができる省電力または低電力モードで動作する。

【0006】

50

そのような省電力または低電力モードでは、SoCは、PCDの状態および/またはSoCの様々な機能を決定するために、定期的に電源が入る、または「ウェイクアップする」ことが可能である。しかしながら、SoCがどの機能の状態をチェックまたは決定する必要があるかに応じて、SoC全体の電源を入れると、依然としてかなりの電力コストを生じるおそれがある。加えて、電力を節約するためにSoCの一部のみを動作させようとすると、一部で動作がストールするという結果になる、および/またはその部分がSoCの他の、電源を切断された部分へのアクセスを必要とする場合、ハングアップになる可能性がある。

#### 【発明の概要】

#### 【発明が解決しようとする課題】

#### 【0007】

10

したがって、SoCの主要部分が電源を切断されている、および/または低電力もしくは省電力モードであるとき、SoC内のサブシステムが、効果的に動作することを可能にするための改善されたシステムおよび方法の必要がある。

#### 【課題を解決するための手段】

#### 【0008】

20

ポータブルコンピューティングデバイス(PCD)におけるシステムオンチップ(SoC)のサブシステムによる外部アクセス検出および回復を可能にするシステムおよび方法が開示される。動作時、SoCのサブシステムは、SoCが機能しないまたはゼロ電力の状態またはモードなど、低電力状態である間、SoCとは独立して内部モードで動作する。サブシステムは、メモリ、センサ、およびモニタモジュールと通信しているプロセッサを備える。モニタモジュールは、サブシステムのプロセッサが、サブシステムの外部の構成要素へのアクセスを要求するときを検出する。この検出された要求に応答して、SoCは、全電力(full power)状態またはモードに入るようにされ、サブシステムは、内部動作モードを終了するようになれる。

#### 【0009】

30

例示的な一実施形態は、ポータブルコンピューティングデバイス(PCD)におけるシステムオンチップ(SoC)のためのコンピュータシステムであり、システムは、内部モードで独立して動作するように構成されたSoCのサブシステムを備え、サブシステムは、センサおよびメモリと通信しているプロセッサと、プロセッサと通信しているメモリモニタとを備え、モニタモジュールは、サブシステムの外部の構成要素へのプロセッサによるアクセス要求を検出し、検出されたアクセス要求に応答してSoCを全電力状態に入れさせ、検出されたアクセス要求に応答してサブシステムに内部モードを終了させるように構成される。

#### 【0010】

40

別の例示的な実施形態は、コンピュータ可読プログラムコードがその中で実施される非一時的コンピュータ使用可能媒体を備えたコンピュータプログラム製品であり、上記コンピュータ可読プログラムコードは、ポータブルコンピューティングデバイス(PCD)におけるシステムオンチップ(SoC)のサブシステムでの外部アクセス検出および回復のための方法を実施するために実行されるように適合され、本方法は、メモリ、センサ、およびモニタモジュールと通信しているプロセッサを備えた、SoCのサブシステムを、SoCが低電力状態である間、SoCとは独立して内部モードで動作させるステップと、モニタモジュールを用いて、サブシステムの外部の構成要素へのプロセッサによるアクセス要求を検出するステップと、サブシステムの外部の構成要素への検出されたアクセス要求に応答して、SoCを全電力状態に入れさせ、サブシステムに内部モードを終了させるステップとを含む。

#### 【0011】

図面における同様の参照番号は、特に示されていない限り、様々な図を通して同様の部分を参照している。「102A」または「102B」などの文字指定を伴う参照番号について、文字指定は、同じ図内に存在する2つの同様の部分または要素を区別することができる。参照番号がすべての図において同じ参照番号を有するすべての部分を含むことを意図するとき、参照番号に対する文字指定は省略される場合がある。同様に、「102」などの'指定を伴う参照番号について、「指定は、同じ参照番号を有する(ただし、「指定のない」)下位要素に

50

に対する代替実施形態を示すことができる。

【図面の簡単な説明】

【0012】

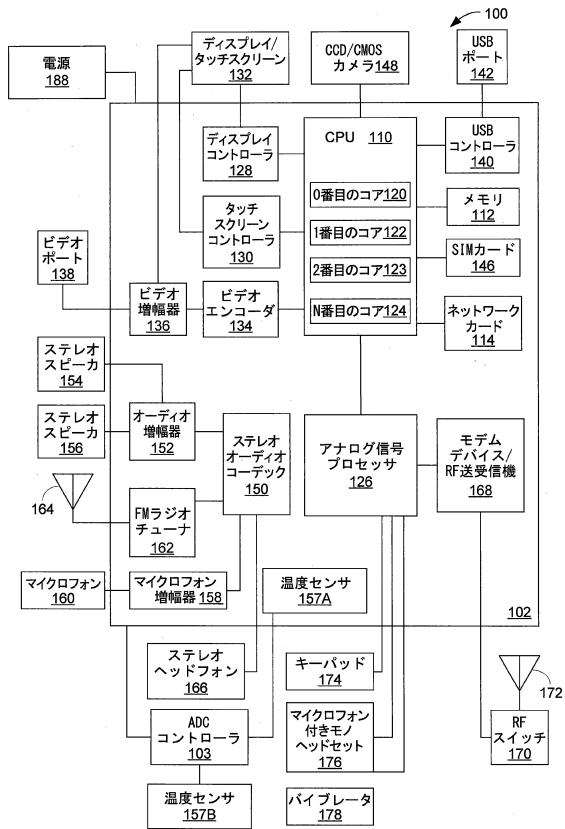

【図1】本発明を実装することができるポータブルコンピューティングデバイス(PCD)のある例示的な実施形態のブロック図である。

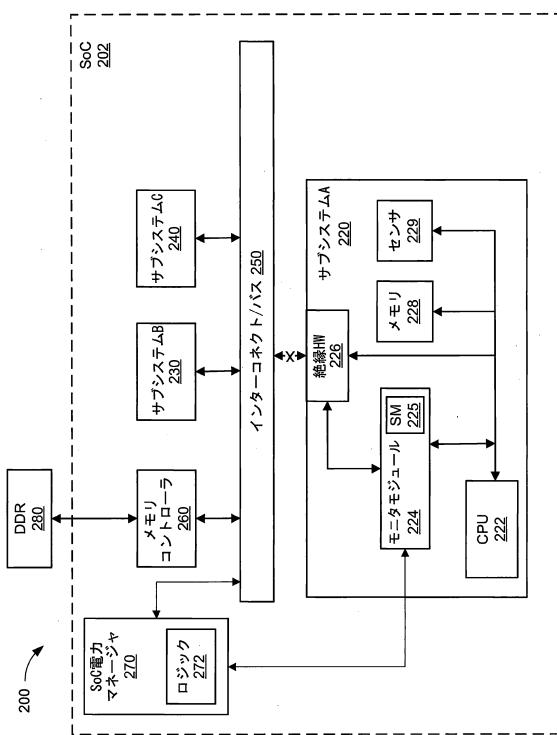

【図2A】図1に示すPCD実施形態など、PCDにおけるSoCのサブシステムによる外部アクセス検出および回復のためのシステムの例示的な実施形態を示すブロック図である。

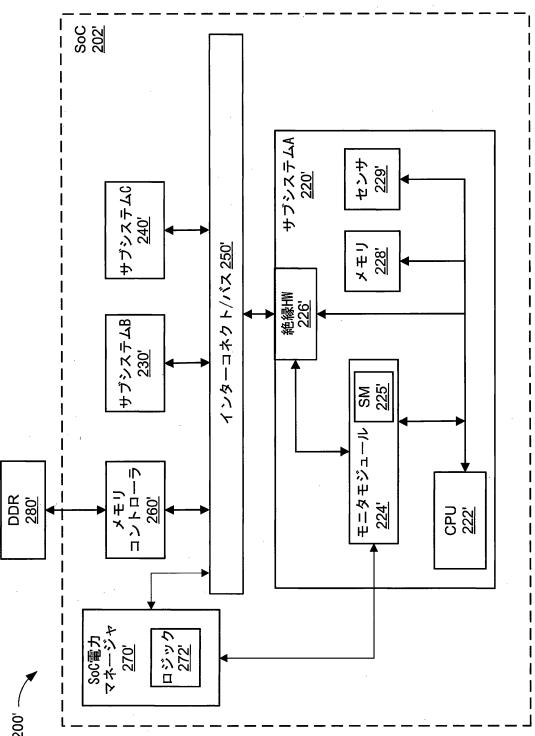

【図2B】図2Aの例示的なシステムの構造を示すブロック図である。

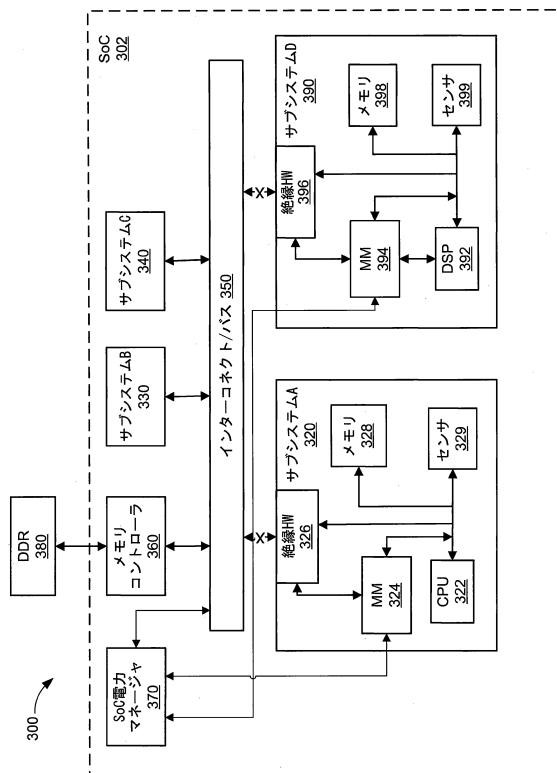

【図3】図1に示すPCD実施形態など、PCDにおけるSoCのサブシステムによる外部アクセス検出および回復のためのシステムの別の例示的な実施形態を示すブロック図である。 10

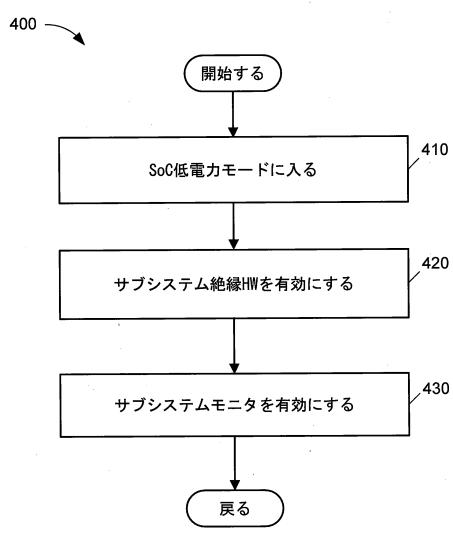

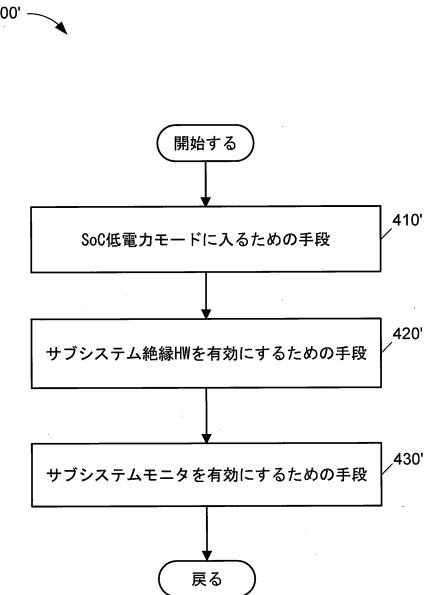

【図4A】PCDにおけるSoCのサブシステムを実装するための方法の例示的な実施形態の構造を説明するフローチャートである。

【図4B】図4Aに示した方法の構造を実行することが可能な例示的な構成要素を示す図である。

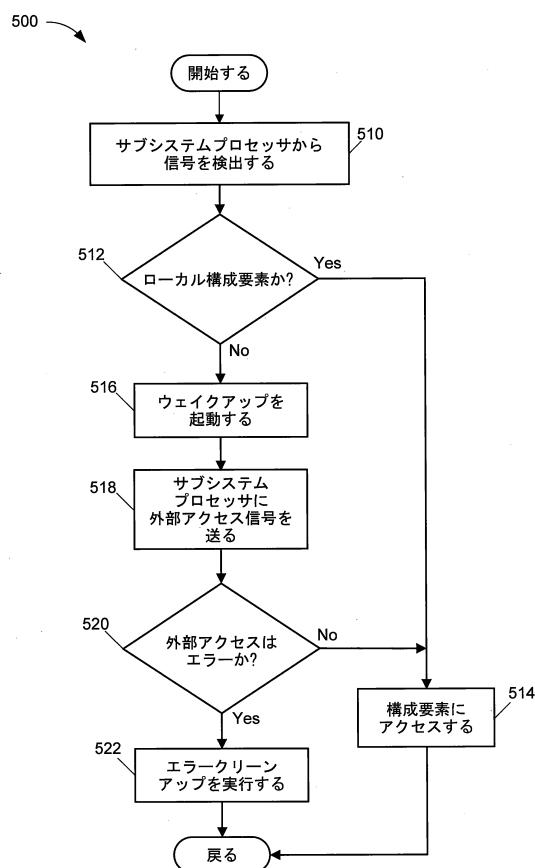

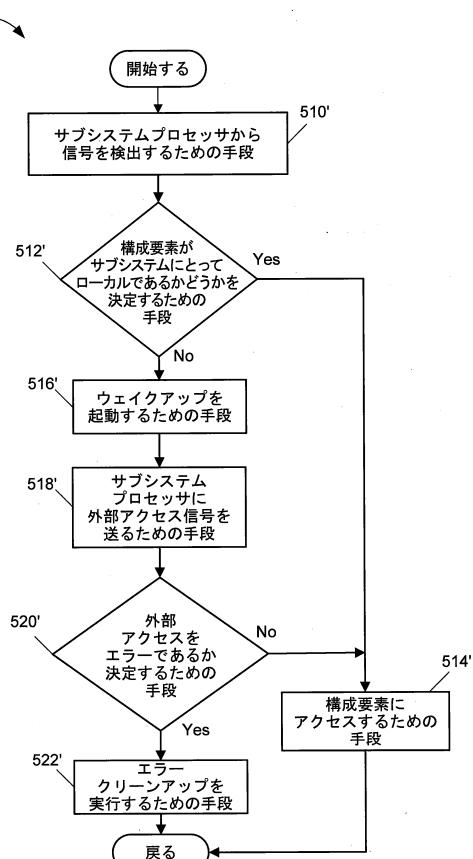

【図5A】SoCのサブシステムによる外部アクセス検出および回復を提供するための方法の例示的な実施形態の構造を説明するフローチャートである。

【図5B】図5Aに示した方法の構造を実行することが可能な例示的な構成要素を示す図である。

【発明を実施するための形態】

【0013】

「例示的」という語は、本明細書では、「例、事例、または例示として役に立つ」ことを意味するために使用される。「例示的」として本明細書で説明するいずれの構造も、他の構造よりも好ましい、または有利であるものとして必ずしも解釈されるとは限らない。 20

【0014】

本明細書では、「アプリケーション」という用語は、オブジェクトコード、スクリプト、バイトコード、マークアップ言語ファイル、およびパッチのような実行可能コンテンツを有するファイルをも含んでもよい。さらに、本明細書で参照される「アプリケーション」は、開かれることが必要な場合があるドキュメント、またはアクセスされる必要がある他のデータファイルなどの、本質的に実行可能ではないファイルを含む場合もある。

【0015】

「コンテンツ」という用語はまた、オブジェクトコード、スクリプト、バイトコード、マークアップ言語ファイル、およびパッチなどの、実行可能コンテンツを有するファイルを含む場合もある。さらに、本明細書において参照される「コンテンツ」は、開くことが必要な場合があるドキュメント、またはアクセスされる必要がある他のデータファイルやデータ値などの、本質的に実行可能ではないファイルを含む場合もある。 30

【0016】

「構成要素」、「データベース」、「モジュール」、「システム」などの用語は、本明細書で使用されるとき、ハードウェア、ファームウェア、ハードウェアとソフトウェアの組合せ、ソフトウェア、または実行中のソフトウェアのいずれかであるコンピュータ関連エンティティを指すものとする。たとえば、構成要素は、限定はしないが、プロセッサ上で実行されているプロセス、プロセッサ、オブジェクト、実行可能ファイル、実行のスレッド、プログラム、および/またはコンピュータであってもよい。例として、コンピューティングデバイス上で実行されるアプリケーションとコンピューティングデバイスの両方が構成要素であってもよい。1つまたは複数の構成要素は、プロセスおよび/または実行のスレッド内に存在してもよく、構成要素は、1つのコンピュータ上に局在化され、および/または2つ以上のコンピュータ間で分散されてもよい。さらに、これらの構成要素は、様々なデータ構造が記憶された様々なコンピュータ可読媒体から実行されてもよい。構成要素は、たとえば1つまたは複数のデータパケット(たとえば、ローカルシステム、分散システム内の別の構成要素とやりとりし、および/または信号によってインターネットなどのネットワークを介して他のシステムとやりとりする、ある構成要素からのデータ)を有す 40

る信号に従って、ローカルプロセスおよび/またはリモートプロセスによって通信してもよい。

#### 【0017】

本明細書では、「ポータブルコンピューティングデバイス」(「PCD」)という用語は、バッテリーおよび/またはキャパシタなど、制限された容量の再充電可能な電源において動作するデバイスを記述するために使用される。充電式電源を備えるPCDが、数十年にわたって使用してきたが、第3世代(「3G」)および第4世代(「4G」)のワイヤレス技術の出現に結び付けられる、充電式バッテリーにおける技術的な進歩により、複数の能力を有する数多くのPCDが可能になった。したがってPCDは、とりわけ、セルラー電話、衛星電話、ページャ、PDA、スマートフォン、ナビゲーションデバイス、スマートブックすなわちリーダ、メディアプレーヤ、上記デバイスの組合せ、ワイヤレス接続を有するラップトップコンピュータまたはタブレットコンピュータであってもよい。10

#### 【0018】

本明細書では、「中央処理ユニット(「CPU」)」、「デジタル信号プロセッサ(「DSP」)」、「グラフィックス処理ユニット(「GPU」)」、「チップ」、「ビデオコーデック」、「システムバス」、「画像プロセッサ」、および「メディアディスプレイプロセッサ(「MDP」)」という用語は、SoC上に実装することができる処理構成要素の非限定的な例である。処理構成要素についてのこれらの用語は、別段に規定されているときを除いて、互換的に使用される。その上、下で論じるように、上記またはそれらの均等物のいずれも、「コア」および/または「サブコア」と本明細書では全般的に呼ばれる1つまたは複数の別個の処理構成要素内で実装され得るか、またはそれらからなり得る。20

#### 【0019】

本明細書では、「作業負荷」、「処理負荷」、「処理作業負荷」および「グラフィカル作業負荷」という用語は互換的に使用され、全般的に、所与の実施形態の所与の処理構成要素に関連付けられるか、または割り当てられ得る処理負担または処理負担の割合を対象にする場合がある。加えて、「フレーム」、「コードブロック」、および「コードのブロック」という関連用語は、所与の作業負荷の部分またはセグメントを指すために交換可能に使用される場合がある。上で定義されるものに加えて、「処理構成要素」などは、限定はしないが、中央処理装置、グラフィカル処理ユニット、コア、メインコア、サブコア、処理エリア、ハードウェアエンジンなど、またはポータブルコンピューティングデバイス内の集積回路内またはその外にある任意の構成要素とすることができます。30

#### 【0020】

「MIPS」という用語が、プロセッサが所与の電力周波数において処理することが可能である百万命令毎秒の数を表すことは、当業者には認識されよう。本明細書では、この用語は、例示的な実施形態におけるプロセッサ性能の相対的なレベルを示すための尺度の一般的な単位として使用され、本開示の範囲内に入る任意の所与の実施形態が任意の特定のドライストーン評価または処理能力を有するプロセッサを含むべきであること、または含むべきではないことを示唆するものと、解釈されることはない。加えて、当業者によって理解されるように、プロセッサのMIPS設定は、プロセッサに供給されている電力、周波数、または動作周波数と直接的に相關する。40

#### 【0021】

PCDにおけるSoCのサブシステムによる外部アクセス検出および回復のための本システムおよび方法は、SoCのサブシステムを実装するためのコスト効果的な方法を提供する。サブシステムは、SoCの残部が、機能しない、スリープ、またはゼロ電力の状態またはモードなど、低電力モードであるときを含めて、SoCの残部とは独立して、内部モードで動作するように構成される。サブシステムは、センサおよびメモリと通信しているプロセッサと、プロセッサと通信しているメモリモニタとを備える。モニタモジュールは、サブシステムの外部の構成要素へのプロセッサによるアクセス要求を検出するように構成される。外部構成要素へのアクセス要求を検出することに応答して、モニタモジュールは、他のアクションとして、SoCを全電力状態に入らせ、サブシステムに内部モードを終了させるこ50

とができる。

#### 【0022】

本システムおよび方法では、SoCがひとたび低電力モードに入ると、サブシステムは、SoCとは電気的に絶縁された、その独立した動作を始める。「内部モード」でのこの動作中に、サブシステムのプロセッサから送られる信号または通信は、サブシステムモニタモジュールによって監視される。プロセッサが、正しくまたは誤って、サブシステムの外のメモリなどのいずれかの構成要素にアクセスしようと試みる場合、モニタモジュールは、アクセスの試みを検出する。

#### 【0023】

この検出に応答して、モニタモジュールは、SoCを「ウェイクアップ」させて完全動作モードにするために、SoCの電力マネージャに通信を送ることができる。モニタモジュールは、サブシステムを、サブシステムがSoCの残部と通信する/再び関与することができる状態またはモードにすることもできる。モニタモジュールは、サブシステムプロセッサに通信を送り、アクセスの試みが外部構成要素に対するものであることをプロセッサに通知することもできる。外部構成要素へのアクセスが誤っていた場合、プロセッサは、エラーから回復しようと努めるために、エラー処理ルーチンまたはコードを起動するまたは実行することができる。

#### 【0024】

本システムおよび方法は、SoCを完全に動作可能に維持する必要なく、および/またはSoCを低電力/省電力モードもしくは状態から引き上げる必要なく、SoCセンサのルーチンチェックのためなどに、SoCの残部とは独立したSoCのサブシステムのロバストで柔軟な動作を可能にする。本システムおよび方法は、そのようなサブシステムが、独立して動作し、そのような独立して、絶縁されたサブシステムがサブシステムの外の構成要素にアクセスしようと試みるとき引き起こしたエラーから回復することを可能にする。

#### 【0025】

そのような外部アクセスは、サブシステムのプロセッサがセンサからの入力に応答して作動しているなど、適切である場合がある。これらの場合、本システムおよび方法は、サブシステムが外部構成要素にアクセスするためのパスを提供するように、SoCをウェイクアップさせ、サブシステムを内部/独立モードから抜けさせることによって、エラーメッセージ、サブシステムのクラッシュ、または他の問題を防ぐ。一方でそのような外部アクセスは、サブシステムの何らかのコードにおけるエラーの結果である場合がある。このような場合、外部アクセスの試みをサブシステムに通知することにより、エラーを訂正しようと努めるためにエラー処理ルーチンを実施することが可能になり、サブシステムが動作を続けることが可能になり、プロセッサまたはサブシステムがストールするまたは「ハングアップする」ことを防ぐことができる。

#### 【0026】

一実施形態では、モニタモジュールは、少なくとも1つのモニタと、状態機械からなる單一ハードウェアデバイスで実装されてよく、または状態機械と通信している少なくとも1つのモニタを含んだ別個の構成要素もしくはデバイスであってよい。これらの実施形態でモニタモジュールに(1つまたは複数の)ハードウェアデバイスを使用することによって、プロセッサによる外部アクセスの試みが検出されると、そのような外部アクセスの試みに起因して、サブシステムプロセッサが、アクセスの完了を待つ間にストールした、またはハングアップになったとしても、割込み信号を送ることが可能である。他の実施形態では、モニタモジュールは、ハードウェアでまたはファームウェアで部分的に実装されるにすぎない場合がある。絶縁されたサブシステムによる、外部構成要素にアクセスしようとする試みを自動的に検出し、そこから回復できることは、SoCが低電力モードである間、SoC上でのそのようなサブシステムの改善された動作を可能にし、SoCの動作が減ることからコスト効果的な方法で電力節約をもたらす。

#### 【0027】

本明細書で説明するPCDにおけるSoCのサブシステムによる外部アクセス検出および回復

10

20

30

40

50

を提供するためのシステム、またはシステムの一部は、ハードウェアまたはソフトウェアで実装されてよい。ハードウェアで実装する場合、すべてが当技術分野でよく知られている、以下の技術のいずれか、またはそれらの組合せを含み得る：すなわち、適切に構成された半導体デバイスおよび抵抗要素を有する、個別電子構成要素、集積回路、特定用途向け集積回路などである。これらのハードウェアデバイスのうちのいずれも、単独で動作しようと、他のデバイス、またはメモリなどの他の構成要素とともに動作しようと、開示する方法の様々な動作またはステップを実行するための構成要素または手段を形成するかまたは備えることがやはり可能である。

#### 【0028】

本明細書で説明するPCDまたは他のシステムが、ソフトウェアで実装される、または部分的に実装されるとき、ソフトウェア部分は、本明細書で説明する方法の様々なステップを実行するために使用されることがある。様々な要素を表す際に使用されるソフトウェアおよびデータは、メモリ内に記憶され、適切な命令実行システム(マイクロプロセッサ)によって実行されることがある。ソフトウェアは、論理機能を実装するために実行可能な命令の順位リストを備えてよく、シングルコアプロセッサもしくはマルチコアプロセッサまたはプロセッサ包含システム(processor-containing system)など、命令実行システム、装置、またはデバイスによって、またはそれらとともに使用するために任意の「プロセッサ可読媒体」内で実施されることがある。そのようなシステムは、一般に、命令実行システム、装置、またはデバイスから命令にアクセスし、それらの命令を実行することになる。

10

#### 【0029】

図1は、1つまたは複数のワイヤレス通信システムと通信することができるワイヤレス電話の形態で本システムおよび本方法を実装することができるPCD100の例示的な非限定的な態様のブロック図である。そのようなワイヤレス通信システムは、ロングタームエボリューション(LTE)システム、符号分割多元接続(CDMA)システム、周波数分割多元接続(FDMA)システム、モバイル通信用グローバルシステム(GSM(登録商標):Global System for Mobile Communications)システム、ワイヤレスローカルエリアネットワーク(WLAN)システム、いくつかの他のワイヤレスシステム、またはそれらのうちのいずれかの組合せを含めて、広帯域ワイヤレス通信システムであり得る。CDMAシステムは、広帯域CDMA(WCDMA(登録商標))、CDMA 1X、エボリューションデータオプティマイズド(EVDO)、時分割同期CDMA(TD-SCDMA)、またはCDMAの何らかの他のバージョンを実装してもよい。

20

#### 【0030】

図示するように、PCD100は、互いに結合された異種マルチコア中央処理装置(「CPU」)10およびアナログ信号プロセッサ126を含むオンチップシステム(またはSoC)102を含む。当業者によって理解されるように、CPU110は、0番目のコア120、1番目のコア122、2番目のコア123、およびN番目のコア124を備えてもよい。さらに、当業者によって理解されるように、CPU110の代わりにデジタル信号プロセッサ(「DSP」)も採用され得る。その上、異種マルチコアプロセッサの技術分野で理解されるように、コア120、122、123、124の各々は、同様の動作条件の下で異なる効率で作業負荷を処理することができる。コア120、122、123、124の各々は、PCD100の1つまたは複数の機能を制御することができる。たとえば、第1のコア120は、PCD100内のグラフィックスを制御するためのグラフィックス処理ユニット(GPU)であってよい。そのようなGPU/第1のコア120は、GPUコア120と(バッファを含む)メモリ112との間の通信を制御することを含めて、PCD100内のグラフィックスを制御するために必要なドライバおよび/または他の構成要素をさらに含むことができる。別の例については、N番目のコア124などの異なるコアが、ハイレベルオペレーティングシステム(HLOS)などのPCDオペレーティングシステムを実行する場合がある。そのようなN番目/HLOSのコア124は、さらにドライバ、ハードウェアインターフェース、および/または、コア124とメモリ112(ラッシュメモリを含むことができる)との通信を含めて、HLOSを実行するために必要な他の構成要素を含む場合がある。

30

#### 【0031】

40

50

コア120、122、123、124のいずれも、CPUなどの別個のプロセッサ、またはデジタル信号プロセッサであってよい。加えて、コアの各々は、以下で説明するサブシステムを形成するために、メモリ112、センサ、またはPCD100の他のハードウェアなどの他の構成要素と、機能的にグループ化されてよい。そのようなサブシステムは、オーディオサブシステム、GPSサブシステム、センササブシステムなど、PCDのある機能を実行するために実装されてよい。そのようなサブシステムの1つまたは複数は、たとえばSoC102が、電力オフ状態またはモードを含めて、低電力または省電力状態またはモードに置かれているときに、動作を続けるためなどに、SoC102とは独立して動作するように構成されてもよい。

#### 【0032】

図1に示されるように、ディスプレイコントローラ128およびタッチスクリーンコントローラ130がマルチコアCPU110に結合される。次に、オンチップシステム102の外部のディスプレイ/タッチスクリーン132が、ディスプレイコントローラ128およびタッチスクリーンコントローラ130に結合される。デジタルカメラ148も、マルチコアCPU110に結合されてよい。そのような実施形態では、デジタルカメラ148は、マルチコアCPU110のコアのうちの1つによって制御されてよい。例示的な態様において、デジタルカメラ148は、電荷結合デバイス(CCD:charge-coupled device)カメラまたは相補型金属酸化物半導体(CMOS:complementary metal-oxide semiconductor)カメラである。

#### 【0033】

図1のPCD100は、ビデオエンコーダ134、たとえば、マルチコアCPU110に結合された、位相反転線(PAL:phase alternating line)エンコーダ、順次式カラーメモリ(SECAM:sequential couleur a memoire)エンコーダ、もしくは全国テレビジョン方式委員会(NTSC:national television system(s) committee)エンコーダ、または任意の他のタイプのビデオエンコーダ134をさらに含む場合がある。さらに、ビデオ増幅器136が、ビデオエンコーダ134およびディスプレイ/タッチスクリーン132に結合される。ビデオポート138は、ビデオ増幅器136に結合される。図1に示すように、ユニバーサルシリアルバス(USB)コントローラ140がマルチコアCPU110に結合される。同様に、USBポート142は、USBコントローラ140に結合される。メモリ112もまた、マルチコアCPU110に結合されて図示されている。そのようなメモリ112は、たとえば、ランダムアクセスメモリ(RAM)、読み取り専用メモリ(ROM)、フラッシュメモリ、またはそれらの任意の組合せであってよい。加入者識別モジュール(SIM)カード146も、マルチコアCPU110に結合されてよい。他の実施形態では、複数のSIMカード146が実装される場合がある。

#### 【0034】

図1にさらに示すように、ステレオオーディオコーデック150がマルチコアCPU110に結合されてよい。さらに、オーディオ増幅器152が、ステレオオーディオコーデック150に結合されてよい。例示的な態様では、第1のステレオスピーカ154および第2のステレオスピーカ156が、オーディオ増幅器152に結合される。図1は、マイクロフォン増幅器158もステレオオーディオコーデック150に結合される場合があることを示す。加えて、マイクロフォン160が、マイクロフォン増幅器158に結合される場合がある。特定の態様では、周波数変調('FM')ラジオチューナ162が、ステレオオーディオコーデック150に結合される場合がある。また、FMアンテナ164がFMラジオチューナ162に結合される。さらに、ステレオヘッドフォン166が、ステレオオーディオコーデック150に結合される場合がある。

#### 【0035】

図1は、モデムデバイス/高周波('RF')送受信機168がマルチコアCPU110に結合される場合があることをさらに示す。モデムデバイス168は、GSM(登録商標)、CDMA、W-CDMA、TD-SCDMA、LTE、および、FDD/LTEワイヤレスプロトコルおよびPDD/LTEワイヤレスプロトコルに限定されないが、これらなど、LTEの変形体など、ワイヤレス通信プロトコルのうちの1つまたは複数をサポートし得る。加えて、複数のモデムデバイス168が存在する場合があり、そのような実施形態では、異なるモデムデバイス168が、上に記載したワイヤレス通信プロトコルおよび/または技術のうちのいくつかまたはすべてをサポートし得る。

#### 【0036】

10

20

30

40

50

いくつかの実装形態では、モデムデバイス168はさらに、別個のプロセッサ、メモリ、および/またはRF送受信機を含めて、様々な構成要素からなり得る。他の実装形態では、モデムデバイス168は単なるRF送受信機であり得る。さらに、モデムデバイス168は集積回路に組み込まれる場合がある。すなわち、モデムデバイス168を備える構成要素は、チップにおいてフルソリューションであって、本明細書で説明するシステムおよび方法によって監視され得るそれ自体のプロセッサおよび/またはコアを含む場合がある。代替的には、モデムデバイス168を備える様々な構成要素が、マルチコアCPU110に結合され、CPU110のコア120、122、124のうちの1つによって制御される場合がある。RFスイッチ170が、モデムデバイス168およびRFアンテナ172に結合される場合がある。様々な実施形態では、複数のRFアンテナ172が存在する場合があり、そのようなRFアンテナ172の各々は、RFスイッチ170を介してモデムデバイス168に結合される場合がある。10

#### 【0037】

図1に示すように、キーパッド174が、直接的に、またはアナログ信号プロセッサ126を介してのいずれかで、マルチコアCPU110に結合される場合がある。また、マイクロフォン付きモノヘッドセット176が、マルチコアCPU110および/またはアナログ信号プロセッサ126に結合される場合がある。さらに、バイブレータデバイス178が、マルチコアCPU110および/またはアナログ信号プロセッサ126に結合される場合もある。図1はまた、電源188がオンチップシステム102に結合されてよいことを示し、いくつかの実装形態では、電源188は、USBコントローラ140を介して結合される。特定の態様では、電源188は電力を必要とするPCD100の様々な構成要素に電力を供給する直流(DC)電源である。さらに、特定の態様では、電源188は、充電式DCバッテリーまたは、交流(AC)電源に接続されたAC-DC変換器から得られるDC電源であってよい。20

#### 【0038】

マルチコアCPU110は、1つまたは複数の内部のオンチップ熱センサ157A、ならびに、1つまたは複数の外部のオフチップ熱センサ157Bにも結合される場合もある。オンチップ熱センサ157Aは、縦型PNP構造に基づき、通常は相補型金属酸化膜半導体('CMOS')の超大規模集積('VLSI:very large-scale integration')回路に専用の、1つまたは複数の絶対温度比例('PTAT:proportional to absolute temperature')の温度センサを備えることができる。オフチップ熱センサ157Bは、1つまたは複数のサーミスタを備えることができる。熱センサ157は、アナログデジタル変換器('ADC')コントローラ103を用いてデジタル信号に変換される、電圧降下を生じさせる場合がある。しかしながら、本開示の範囲から逸脱することなく、他のタイプの熱センサ157が採用されてよい。30

#### 【0039】

図1はさらに、PCD100がまた、データネットワーク、たとえば、ローカルエリアネットワーク、パーソナルエリアネットワーク、または任意の他のネットワークにアクセスするために使用される場合がある、ネットワークカード114を含んでもよいことを示す。ネットワークカード114は、Bluetooth(登録商標)ネットワークカード、WiFiネットワークカード、パーソナルエリアネットワーク(PAN)カード、または当技術分野でよく知られている任意の他のネットワークカードとすることができます。さらに、ネットワークカード114は集積回路に組み込まれる場合がある。すなわち、ネットワークカード114は、チップ内のフルソリューションとすることができます、別個のネットワークカード114でなくてもよい。40

#### 【0040】

図1に示すように、ディスプレイ/タッチスクリーン132、ビデオポート138、USBポート142、カメラ148、第1のステレオスピーカ154、第2のステレオスピーカ156、マイクロフォン160、FMアンテナ164、ステレオポートヘッドフォン166、RFスイッチ170、RFアンテナ172、キーパッド174、モノヘッドセット176、バイブレータ178および電源180は、SoC102の外部にある。

#### 【0041】

SoC102はまた、様々なバスコントローラ(図示せず)を含むことができる。たとえば、第1の例は、ビデオエンコーダ134を含めて、マルチメディアサブシステムの構成要素にCPU150

10を通信可能に結合するバスインターフェース内の信号に応答するものであってよい。任意の数の同様に構成されたバスコントローラが、オンチップシステム102内に配置されたバスインターフェースを監視するように配置され得ることを理解されよう。代替的には、必要に応じてCPU110とPCD100の様々なサブシステムとの間で信号を通信する2つ以上のバスインターフェースを監視するように配置された入力を備えた、単一のバスコントローラが構成されることがある。

#### 【0042】

特定の態様では、本明細書で説明する方法ステップのうちの1つまたは複数は、メモリ12内および/またはCPU110に配置されたメモリに記憶されたデータおよびプロセッサ命令の組合せを介して使用可能にされる場合がある。これらの命令は、本明細書で説明する方法を実行するために、マルチコアCPU110内の1つもしくは複数のコア120、122、123、124および/またはSoC102のサブシステムによって実行される場合がある。さらに、マルチコアCPU110、コア120、122、123、124のうちの1つまたは複数、メモリ112、PCD100の他の構成要素、またはこれらの組合せは、SoC102のサブシステムによる外部アクセス検出および回復を可能にするために本明細書で説明する方法ステップの1つまたは複数を実行するための手段として機能することができる。10

#### 【0043】

図2Aおよび図2Bは、図1に示すPCD実施形態など、PCDにおけるSoCのサブシステムによる外部アクセス検出および回復のためのシステムの例示的な実施形態を示すブロック図である。図2Aおよび図2Bは、以下で説明する異なる動作状態において例示的なシステム200/200'の同じ実施形態を示す。図2Aは、SoC202が機能しない/低電力またはゼロ電力のモードまたは状態であって、サブシステムA220が独立して動作しているときの例示的なシステム200を示す。図2Bは、SoC202が完全に機能する/電力供給されるときの、例示的なシステム200'を示す。20

#### 【0044】

図2Aをはじめとして、例示的なシステム200は、システムオンチップ(SoC)集積回路202を含み、SoC集積回路202は、(図1のSoC102と同様の)PCDに実装することができる。図2AのSoC202は、SoC202のインターフェクトまたはバス250にすべて接続された、SoC202のサブシステムA220、サブシステムB230、およびサブシステムC240を含む。SoC202のインターフェクト/バス250は、SoC202のアーキテクチャおよび/またはSoC202もしくはPCDが対象とする用途によって決まり得る任意の所望のタイプのバスまたはインターフェクトであってよい。30

#### 【0045】

SoC202はまた、インターフェクト/バス250と通信し、SoC202の外部のメモリ、DDR280とも通信しているメモリコントローラ260を含む。メモリコントローラ260は、SoC202の様々なメモリへのアクセスを制御することができ、また、SoC202が電源投入される、および/または機能する状態もしくはモードであるとき、サブシステムA220、サブシステムB230、およびサブシステムC240を含めて、SoC202の様々な構成要素が、外部DDR280メモリにアクセスすることを可能にすることもできる。

#### 【0046】

SoC202はまた、SoC202が、機能する/全電力モードおよび状態、ならびに機能しない低電力モードおよび状態を含めて、様々な電力モードまたは状態に入るおよびそれらを終了することを可能にする内部ロジック272を有する電力マネージャ270を含む。SoC202の機能状態にかかわらず、電力マネージャ270は、常時オンに/電源を供給され、PCDの要求に従って必要に応じてSoC202をウェイクアップするまたはSoC202の電源を切断することができる。40

#### 【0047】

図2Aに示す実施形態では、サブシステムA220は、SoC202が低電力および/または機能しないモードまたは状態であるとき動作することを含めて、SoC202の他の部分とは独立して動作することができるように構成される。対照的に、図示の実施形態のサブシステムB23050

およびサブシステムC240は、SoC202の他の部分とは独立して動作するように構成されていない。したがって、サブシステムB230およびC240は、SoC202が低電力および/または機能しないモードまたは状態であるとき、機能しないことになる。

#### 【0048】

サブシステムA220は、プロセッサCPU222を含み、プロセッサCPU222は、図1のコア120、122、123、124のうちの1つとして実装されることがある。いくつかの実施形態では、CPU222は、汎用処理ユニットとして実装されることがあり、他の実施形態では、CPU222は、DSPなど、専用プロセッサとして実装される場合がある。サブシステムA220のCPU222は、メモリ228およびセンサ229と通信しており、メモリ228およびセンサ229もまた、SoC202が低電力および/または機能しないモードまたは状態であるとき動作することを含めて、SoC202の他の部分とは独立して機能し、動作する。10

#### 【0049】

様々な実施形態では、サブシステムA220は、図2Aに示すよりも多いまたは少ない構成要素を含む場合がある。加えて、いくつかの実施形態では、サブシステムA220の構成要素は、物理的にSoC202上で互いの近くにあって、SoC202の物理的サブシステムを形成する場合がある。他の実施形態では、図2Aに示すサブシステムA220が、SoC202上の様々な位置にある構成要素からなるサブシステムを表すように、サブシステムA220の構成要素は、物理的にSoC202上で互いから離れて位置している場合がある。加えて、SoC202の残部が低電力またはゼロ電力状態またはモードであるとき、動作を可能にするために、サブシステムA220は、ローカル母線(図示せず)および/またはローカルデータバス(サブシステムA220の構成要素間のコネクタ線で部分的に図示)を含む場合もある。20

#### 【0050】

図2Aに示すセンサ229は、いくつかの実施形態では、PCDの加速度計および/またはジャイロに関係する場合がある。他の実施形態では、センサ229は、必要に応じて、オーディオ、ワイヤレス、GPS、またはPCDの他の機能に関係する場合がある。加えて、サブシステムA220は、図2Aに示す単一のセンサ229よりも多くを含むことができる。たとえば、サブシステムA220は、異なるタイプのセンサ、またはSoC202および/もしくはPCDの異なる機能に関係するセンサを含めて、2つ以上のセンサを含むことができる。

#### 【0051】

図2Aに示すメモリ228は、任意の所望のタイプのメモリであってよいが、一般に、フラッシュまたは他のコードが多い(code-intensive)タイプのメモリではない。以下で説明するように、メモリ228は、サブシステムA220のローカルメモリとして働く。したがって、CPU222は、SoC202が完全に動作するときも、SoC202が低電力またはゼロ電力モードまたは状態であるときも、メモリ228からデータを読み取り、メモリ228にデータを書き込むことができる。様々な実施形態では、サブシステムA220は、図2Aに示す単一のメモリ228よりも多くを含む場合がある。たとえば、サブシステムA220は、2つ以上のメモリを含む場合があり、そのような各メモリは、必要に応じて同じタイプまたは異なるタイプ(またはそれらの任意の組合せ)である場合がある。30

#### 【0052】

図2Aに示すように、サブシステムA220は、CPU222からの信号/通信を監視するためにCPU222と通信しているモニタモジュール224を含む。図示したモニタモジュール224は、ハードウェアで実装され、ハードウェアモニタと、状態機械225とを備える。様々な実施形態では、モニタモジュール224および状態機械225は、図2Aに示す単一の構成要素ではなく別個の構成要素であってよい。たとえば、モニタモジュール224および状態機械225は、互いおよび/またはCPU222と通信している別個のハードウェア構成要素であってよい。モニタモジュール224および/または状態機械225は、サブシステムA220が、以下で説明するようにSoC202の残部とは独立して動作しているとき、外部アクセス検出および回復を提供するように動作する。40

#### 【0053】

サブシステムA220はまた、図2Aの絶縁HWブロック226によって表される様々な絶縁ハー

50

ドウェアを含む。絶縁HW226は、SoC202が低電力またはゼロ電力モードまたは状態に入るとき、サブシステムAが動作し続けることができるよう、サブシステムA220をSoC202の残部から絶縁する働きをする。たとえば、図2Aに示すように、SoC202が機能しない/低電力のモードまたは状態であるとき、絶縁HW226は、インターフェクト/バス250との接続を絶縁することによって、サブシステムA220(およびその構成要素)をSoC202の残部から電気的に絶縁するように動作することができる。絶縁HW226は、SoC202のインターフェクト/バス250、母線などからの絶縁を含めて、SoC202の残部からの絶縁を実現するために必要な、クランプおよび他のハードウェア構成要素を含むことができる。

#### 【0054】

動作時、SoC202は、電力節約ルーチンの部分など、機能しないおよび/または低電力もしくはゼロ電力モードまたは状態に入る場合がある。サブシステムA220の絶縁HW226は、サブシステムA220をSoC202の残部から電気的におよびそれ以外に絶縁することに関与し、サブシステムA220がSoC202の残部とは独立して動作を続けることを可能にする。たとえば、SoC202は、PCDの不活動により、スリープまたは機能しないモードに入っている場合がある。

10

#### 【0055】

しかしながら、SoC202が、ワイヤレス接続、GPS接続または測位に関係するセンサ、ユーザがPCDを動かしている/操作していると決定するためのPCDの加速度計またはジャイロ、PCDのユーザからなどのウェイクアップ音またはコマンドを検出するためのオーディオセンサ、その他のセンサを、定期的にチェックすることが望ましいまたは必要とされる場合がある。そのようなチェックを実行するためにSoC202全体を定期的にウェイクアップさせるのではなく、サブシステムA220は、SoC202がスリープ、省電力、または機能しないモードである間、SoC202の残部とは電気的に絶縁された「孤立モード(island mode)」または「内部モード」で独立して動作し続けることができる。そのような孤立モードで動作する間、サブシステムA220またはサブシステムAのCPU222などのプロセッサは、必要に応じて、ローカルセンサ229(および任意の追加センサ)を監視するおよび/またはローカルメモリ228にアクセスすることができる。サブシステムA220のためのこの孤立動作モードは、センサ229をチェックするまでSoC202をウェイクアップさせ続けるよりもはるかに低い電力コスト/消費で、センサ229の所望のまたは必要なチェックを可能にする。

20

#### 【0056】

SoC202のサブシステムA220が、この孤立モードで動作している間、モニタモジュール224は、CPU222への通信/信号、およびCPU222からの通信/信号を監視する。たとえば、センサ229からの信号に基づいてCPU222が、サブシステムA220の外部の構成要素にアクセスしようと試みる場合、モニタモジュール224は、アクセスの試みを検出する。たとえば、サブシステムA220が孤立モードで動作している間に、CPU222が、DDR280などの外部メモリにアクセスしようと試みる場合、モニタモジュール224は、アクセスの試みを検出することになる。モニタモジュール224は、次いで、SoC電力マネージャ270に、CPU222がDDR280にアクセスできるように、SoC202をウェイクアップさせることを始めるように伝える、割込みまたは他の通信などの信号を、SoC電力マネージャ270に送ることになる。

30

#### 【0057】

SoC電力マネージャ270は、SoC電力マネージャ270がモニタモジュール224からの信号または通信を解釈することを可能にするロジック272を含むことができる。いくつかの実施形態では、信号を受信すると、SoC電力マネージャ270は、CPU222によるアクセスを完了するためには必要なSoC202の部分のみが電力を供給される/動作する状態になるようにするために、動作することができる。これらの実施形態では、モニタモジュール224からの信号または通信は、SoC電力マネージャ270が、アクセスを完了するために必要とされるSoC202の構成要素を決定するために、ロジック272を使用するなどして、解釈する情報を含むことができる。他の実施形態では、モニタモジュール224から信号を受信すると、SoC電力マネージャ270は、SoC202全体を機能するおよび/または電力供給される状態またはモードに復元させるように動作する。

40

50

**【 0 0 5 8 】**

モニタモジュール224はまた、サブシステムA220がSoC202の残部と通信することができるよう、サブシステムA220を孤立しない/通常機能モードに移行させるために状態機械225をトリガることができる。モニタモジュール224および状態機械225が別個の構成要素である実施形態では、モニタモジュール224は、状態機械225をトリガするために、割込みなどの信号を送ることができる。状態機械225がモニタモジュール224の一部である実施形態では、モニタモジュール224は、状態機械225の動作を直接制御することができる。

**【 0 0 5 9 】**

CPU222がDDR280にアクセスしようと試みている上記の例を続けると、モニタモジュール224は、CPU222が外部メモリDDR280へのアクセスを完了することができるように、絶縁HW226にインターフェクト/バス250との通信を再有効化するために状態機械225をトリガすることができる。他の例は、サブシステムA220および/またはCPU222などサブシステムA220の構成要素の増大した活動をサポートするために、状態機械225が他のハードウェアにサブシステムA220をSoC202母線に再接続させることを含むことができる。10

**【 0 0 6 0 】**

要約すれば、上記の例では、モニタモジュール224は、DDR280など、サブシステムA220の外部にある構成要素にアクセスしようとするCPU222による試みを検出する。モニタモジュール224は、それだけで、または状態機械225と組み合わせてのいずれかで、この検出されたアクセスの試みを、SoC202の残部をウェイクアップさせるためのトリガとして使用して、CPU222がアクセスしようとしている構成要素へのパスを提供するおよび/またはその構成要素をウェイクアップさせる。モニタモジュール224はまた、やはりそれだけで、または状態機械225と組み合わせてのいずれかで、サブシステムA220が、サブシステムA(およびCPU222など、その構成要素)が状態に、ならびにサブシステムAがSoC202の残部と通信するおよび/または対話することができる状態またはモードに、入るようにする。20

**【 0 0 6 1 】**

別の例では、SoC202は、機能しない/低電力またはゼロ電力モードであり、サブシステムA220は、たとえば孤立モードまたは内部モードで、動作し続けている。この例では、CPU222は、センサ229からの信号により、またはCPU222によって実行されている何らかのコードもしくはルーチンのエラーにより、DDR280など、サブシステムA220の外部の構成要素にアクセスしようと試みる場合がある。上述のように、サブシステムA220の外部のアクセスの試みを検出した後、モニタモジュール224は、(この例ではDDR280の)アクセスの試みがサブシステムA220の外部であることをCPU222に通知する信号をCPU222に送ることもできる。30

**【 0 0 6 2 】**

様々な実施形態では、モニタモジュール224は、上述の様々な「ウェイクアップ」機能を実行する前に、実行した後に、または実行する代わりに、CPU222にこの信号/通信を送ることができる。モニタモジュール224からCPU222への信号または通信は、CPU222への割込みなど、任意の所望の形であってよい。いくつかの実施形態では、モニタモジュール224は、CPU222による外部アクセスの試みが正しかったか、誤っていたかを考慮せずに、常にCPU222に信号/通信を送る場合がある。そのような実施形態では、モニタモジュール224から信号を受信すると、CPU222が、アクセスの試みはエラーではないと決定する場合、CPU222は信号を無視することができ、外部アクセスの試みがエラーである場合、CPU222は、1つまたは複数のエラー処理ルーチンまたはコードを起動または開始することができる。40

**【 0 0 6 3 】**

これらの実施形態では、モニタモジュール224をハードウェアで実装することによって、外部構成要素へのアクセスが完了できるようにすることによって、および外部アクセスの通知とともにCPU222に割込みも送ることによって、モニタモジュール224は、サブシステムA220がSoC202の残部から離れて孤立モードで動作している(または孤立モードに入っている、もしくは孤立モードから抜け出している)間に、CPU222が外部構成要素にアクセスしようと試みることから発生する場合があるエラーから、CPU222および/またはサブシ50

システムA220が回復するためのチャンスをより大きくするまたは高めることができる。

#### 【0064】

様々な実施形態では、モニタモジュール224がSoC202および/またはサブシステムA220に対して他の「ウェイクアップ」機能を実行する前に、モニタモジュール224がCPU222に信号/割込みを送ることが好ましい場合がある。他の実施形態では、CPU222が信号/割込みを受信し、モニタモジュール224に応答するまで、モニタモジュール224が「ウェイクアップ」機能を実行しないことが好ましい場合がある。

#### 【0065】

図2Bを参照すると、システム200'は、SoC202'が覚醒した後に図示されている、および/または全電力で動作している。図2Bに示すように、サブシステムA220'とSoC202'との間の接続は、絶縁HW226'を無効にすることなどによって、復元されている。SoC202'とサブシステムA220'との間の復元された接続は、CPU222'が外部メモリDDR280'など、サブシステムA220'の外の構成要素にアクセスするためのパスを与える、CPU222'とインターフェクト/バス250'との間の通信を含む。

10

#### 【0066】

いくつかの実施形態では、SoC202'が全電力/機能する状態に戻ったとき、モニタモジュール224'は、たとえばSoC電力マネージャ270'もしくはSoC202'の他の構成要素からの信号または確認応答から、またはモニタモジュール224'が「ウェイクアップ」信号/通信をSoC電力マネージャ270'に送るととき、モニタモジュール224'を無効にするように動作する、モニタモジュール224'の内部のトリガもしくはロジックから、無効にされてよい。

20

#### 【0067】

他の実施形態では、モニタモジュール224'は、SoC202'が全電力/機能する状態に戻ったとき、CPU222'を監視し続けることができる。そのような実施形態では、モニタモジュール224'は、CPU222'が、サブシステムA220'の外部にあるDDR280'などの構成要素にアクセスしようと試みることを検出するとき、もはやいかなるアクションもとらなくてよい。たとえば、モニタモジュール224'は、もはやSoC電力マネージャ270'に「ウェイクアップ」信号/通信を送らなくてよい、および/または、サブシステムA220'の外部の構成要素へのアクセスの試みをCPU222'に警告する信号/通信をCPU222'にもはや送らなくてよい。

#### 【0068】

図3は、図1に示すPCD実施形態など、PCDにおけるSoCのサブシステムによる外部アクセス検出および回復のためのシステムの第2の例示的な実施形態を示すブロック図である。図2Aおよび図2Bに示す実施形態と同様に、図3のシステム300は、SoC302のインターフェクトまたはバス350にすべて接続されたサブシステムA320、サブシステムB330、およびサブシステムC340を有するSoC302を含む。図3の実施形態はまた、やはりインターフェクト/バス350に接続されたサブシステムD390を含む。SoC302のインターフェクト/バス350は、SoC302のアーキテクチャおよび/またはSoC302もしくはPCDが対象とする用途によって決まり得る任意の所望のタイプのバスまたはインターフェクトであってよい。

30

#### 【0069】

SoC302はまた、インターフェクト/バス350と通信し、SoC302の外部のメモリ、DDR380とも通信しているメモリコントローラ360を含む。メモリコントローラ360は、SoC302の様々なメモリへのアクセスを制御することができ、また、SoC302が電源投入される、および/または機能する状態もしくはモードであるとき、サブシステムA320、B330、C340、およびD390を含めて、SoC302の様々な構成要素が、外部DDR380メモリにアクセスすることを可能にすることもできる。SoC302はまた、図2A～図2Bに関して上記で説明した電力マネージャ270と同様に動作する電力マネージャ370を含む。

40

#### 【0070】

図3に示す実施形態では、サブシステムA320およびサブシステムD390はともに、SoC302が低電力および/または機能しないモードまたは状態であるとき動作することを含めて、SoC302の他の部分(および互い)とは独立して動作することができるよう構成される。対照的に、図示の実施形態のサブシステムB330およびサブシステムC340は、SoC302の他の部

50

分とは独立して動作するように構成されていない。したがって、サブシステムB330およびC340は、SoC302が低電力および/または機能しないモードまたは状態であるとき、機能しないことになる。

#### 【0071】

図2A～図2Bにおいて上記で説明したサブシステムA220のように、図3のサブシステムA320は、プロセッサ、CPU322を含み、CPU322は、図1のコア120、122、123、124のうちの1つとして実装されることがある。いくつかの実施形態では、CPU322は、汎用処理ユニットとして実装されることがある、他の実施形態では、CPU322は、専用プロセッサとして実装される場合がある。サブシステムA320のCPU322は、メモリ328およびセンサ329と通信しており、メモリ328およびセンサ329もまた、SoC302が低電力および/または機能しないモードまたは状態であるときに動作することを含めて、SoC302の他の部分とは独立して機能し、動作することができる。上記で説明したように、図3には1つのメモリ328および1つのセンサ329しか示していないが、サブシステムA320は、複数の、異なるタイプのメモリおよび/またはセンサを含むことがある。

#### 【0072】

サブシステムA320は、図3では絶縁HWブロック326で表す様々な絶縁ハードウェアを含む。絶縁HW326は、上記で説明したように、SoC302が低電力またはゼロ電力モードまたは状態に入るとき、サブシステムA320が動作し続けることができるよう、サブシステムA320をSoC302の残部から分離する働きをする。絶縁HW326は、SoC302のインターフェクト/バス350、母線などからの絶縁を含めて、SoC302の残部からの絶縁を実現するために必要な、クランプおよび他のハードウェア構成要素を含むことができる。

#### 【0073】

図3に示すように、サブシステムA320はまた、CPU322からの信号/通信を監視するためにCPU322と通信しているモニタモジュール324を含む。図示したモニタモジュール324は、ハードウェアで実装され、ハードウェアモニタ、ならびに状態機械(図示せず)を備える。様々な実施形態では、モニタモジュール324および状態機械は、図3に示す単一の構成要素ではなく別個の構成要素であってよい。モニタモジュール324および/または状態機械は、サブシステムA320が上記で説明したようにSoC302の残部とは独立して動作しているとき、外部アクセス検出および回復を提供するように動作する。

#### 【0074】

図3の実施形態は、上記で説明した孤立モードなど、サブシステムAを含めて、SoC302の残部とは独立して動作するようにやはり構成された、サブシステムD390を含む。サブシステムD390は、サブシステムD390が処理ユニットとしてDSP392を実装することを除いて、サブシステムA320と同様である。絶縁HW396、モニタモジュール394、メモリ398、およびセンサ399を含めて、サブシステムD390の様々な他の構成要素は、サブシステムA320に対して上記で説明した構成要素と同様である。

#### 【0075】

サブシステムA320とサブシステムD390の両方に対して図示した構成要素は、例示であることに留意されたい。サブシステムA320および/またはサブシステムD390の各々が、追加の構成要素または異なる構成要素を含む場合がある。たとえば、サブシステムA320および/またはサブシステムD390の各々が、それぞれのサブシステムがSoC302の残部とは独立して動作することを可能にするために、ローカル通信バス、ローカル母線などを含む場合がある。同様に、システム300は、図3に示すサブシステムA320およびサブシステムD390に加えて、SoC302の残部とは独立して動作するように構成された追加のサブシステムを含む場合がある。

#### 【0076】

互いと同様の構成要素を有して図示されているが、サブシステムA320は、サブシステムDとは異なる構成要素、および異なるように構成された構成要素を有する場合がある。たとえば、サブシステムA320は、図示したセンサ329に加えて複数のセンサを含む場合があり、サブシステムD390は、1つのセンサ399のみを含む場合がある。同様に、サブシステム

10

20

30

40

50

A320のセンサ329は、サブシステムD390のセンサ399とは異なる種類のセンサである、および/またはPCDの異なる機能領域に関係している場合がある。たとえば、サブシステムA320のセンサ329は、オーディオ機能に関係する場合があり、PCDのユーザからの「ウェイクアップ」コマンドまたは音を検知するように動作する場合があり、サブシステムD390のセンサ399は、上記で説明したようにPCDの加速度計および/またはジャイロに関係する場合がある。センサの他の構成および/またはタイプもまた、図示したサブシステムのいずれかまたは両方で実装される場合がある。

#### 【 0 0 7 7 】

運用上、サブシステムA320およびサブシステムD390の各々は、図2A～図2BのサブシステムA220に関して上記で説明したように動作することになる。したがって、SoC302が、機能しないおよび/または低電力もしくはゼロ電力モードまたは状態であるとき、サブシステムA320またはサブシステムD390のいずれかまたは両方は、孤立モードで動作する場合がある。各サブシステムのモニタモジュール324および394は、それらのそれぞれのCPU322またはDSP392による、それらのそれぞれのサブシステムの外のSoC302の構成要素にアクセスしようとする試みを検出するように動作することになる。そのような外部アクセスが検出される場合、各モニタモジュール324または394は、そのそれぞれのサブシステムに対して、図2A～図2Bのモニタモジュール220に対して上記で説明したアクションの1つまたは複数をとることができる。このようにして、SoC302が機能しない状態であるとき、SoC302は、複数のシステムが、上記で説明した孤立モードを含めて、機能し続け、各サブシステムがそれ自体の割り当てられた機能を実行し、各サブシステムが上記で説明したようにSoC302を覚醒させる能力を有するようになることができる。10

#### 【 0 0 7 8 】

図4Aは、PCDにおけるSoCのサブシステムを実装するための方法400の例示的な実施形態の態様を説明するフロー・チャートである。ブロック410において、図2A～図2BのSoC202または図3の302などのSoCが、省電力またはゼロ電力状態またはモードなどの、低電力モードに入る。SoCは、PCDがエンドユーザによってアクティブに操作されていないときなどに、SoCまたはPCDの電力節約ルーチンまたはプログラムの一部として低電力モードに入ることができる。

#### 【 0 0 7 9 】

SoCは、上記で説明したサブシステムA220/320など、SoCの残部とは独立して動作するよう構成された少なくとも1つのサブシステムを含む。ブロック420では、上記で説明したサブシステムA220/320の絶縁HW226/326など、サブシステムのための絶縁ハードウェアが、SoCの残部からサブシステムを電気的におよびそれ以外に隔離するように関与する。30

#### 【 0 0 8 0 】

方法400のブロック430において、サブシステムのサブシステムモニタが有効にされる。サブシステムモニタは、図2A～図2Bおよび図3に対して上記で説明したサブシステムA220/320のモニタモジュール224/324を含むことができる。サブシステムモニタは、プロセッサからの通信/信号を監視し、以下で図5A～図5Bにおいて述べるようにサブシステムのために外部アクセス検出および回復を実行するように動作する。

#### 【 0 0 8 1 】

図5Aを参照すると、SoCのサブシステムによる外部アクセス検出および回復を提供するための方法500の例示的な実施形態の態様を説明するフロー・チャートが示されている。方法500は、上記で説明した方法400のサブシステム監視ブロック430として実装されてよい。方法500は、サブシステムプロセッサからの信号が検出されるブロック510から始まる。サブシステムは、図2Aの例示的なサブシステムA220など、SoCの残部とは独立して動作することができ、独立して動作している。例としてサブシステムA220を使用すると、動作中、プロセッサ、CPU222からの信号または通信は、ハードウェアモニタを含むことができるモニタモジュール224によって監視される、および/または検出される。40

#### 【 0 0 8 2 】

上記で説明したように、CPU222からのそのような信号または通信は、サブシステムA220

10

20

30

40

50

のメモリ228またはセンサ229などの様々な構成要素、または他の構成要素にアクセスしようとする試みを含むことができる。CPU222からの信号/通信が検出されると、ブロック512において、アクセスされる構成要素はローカルであるかどうか、またはCPU222はサブシステムの外部の構成要素にアクセスしようとしているかどうか、決定が行われる。たとえば、CPU222は、サブシステムA220の外部のSoC202上の別の構成要素にアクセスしようとしている場合があり、またはCPU222は、SoC202の外部にあるDDR280などの構成要素にアクセスしようとしている場合がある。

#### 【 0 0 8 3 】

CPU222がアクセスしたい構成要素がローカルである、すなわち、SoCの残部とは独立して動作しているサブシステムA220の一部である場合、CPU222は、ブロック514において構成要素にアクセスし、方法500は戻り、これは、CPU222からの信号/通信を監視することに戻ることを含めることができる。10

#### 【 0 0 8 4 】

ブロック512における決定が、CPU222がアクセスしたい構成要素はサブシステムA220にとってローカルではないということである場合、ブロック516においてウェイクアップが起動される。図2Aのモニタモジュール224の例を続けると、ブロック516のウェイクアップは、上述のように、SoC202をウェイクアップさせる/機能する状態またはモードに入らせるなどを含むことができる。一実施形態では、ブロック516のウェイクアップは、モニタモジュール224が割込みなどの信号または通信を、SoC202の常時オンのSoC電力マネージャ270に送ることによって遂行されてよい。SoC電力マネージャ270は次いで、受信された信号/通信または割込みに従って、CPU222によって望まれるアクセスのための経路を作成するために、SoC202の一部または全体に電源を入れるおよび/またはこれらを機能する状態にするように作動することができる。20

#### 【 0 0 8 5 】

ブロック516のウェイクアップは、代わりに、または追加として、サブシステムA220自体が、SoC202の残部と通信または対話することができる状態またはモードに入るようになることを含むことができる。たとえば、一実施形態では、ブロック516のウェイクアップのこのサブシステムA220部分は、モニタモジュール224が信号または通信を(必要に応じてモニタモジュール224とは別個とする、またはモニタモジュール224に組み込むことができる)状態機械225に送ることによって遂行されてよい。状態機械225は次いで、絶縁HW226を無効にすること、および/またはSoC202のインターフェクト/バス250とCPU222との間の通信を確立することなどによって、サブシステムA220が再びSoC202の残部とともに動作するように、サブシステムA220が孤立モードから抜け出すようにすることができる。様々な実施形態では、ブロック516は、サブシステムA220が、必要に応じてSoC202のウェイクアップと同時に、その前に、またはその後に行われるよう、SoC202と通信/対話することができる状態またはモードに入るようになることができる。30

#### 【 0 0 8 6 】

方法のブロック518において、外部アクセス信号が、外部構成要素にアクセスしようとしているサブシステムプロセッサに送られる。再び図2Aのシステム200の例を続けると、ブロック518の信号は、一実施形態では、モニタモジュール224からCPU222への割込みなどの、信号または通信であってよい。この信号は、CPU222がサブシステムA220の外部にあるメモリなどの構成要素にアクセスしようと試みていることを、CPU222に通知するまたは警告する。40

#### 【 0 0 8 7 】

方法は次いで、ブロック520において、外部アクセスの試みがエラーであったかどうかを決定することになる。たとえば、CPU222は、モニタモジュール224からの信号または割込みを受信すると、外部構成要素にアクセスしようとする試みが、CPU222上でまたはサブシステムA320内で動作しているコードまたはルーチンにおけるエラーの結果であったかどうかを決定することができる。外部アクセスがエラーではなかった場合、CPUはその決定を行う、または単にモニタモジュール224からの信号/割込みを無視し、ブロック514にお50

いて外部構成要素にアクセスすることができ、方法500は、SoC202が覚醒された/機能する状態またはモードに戻ったとき、終了し、サブシステムA220はもはや孤立モードおよび/またはSoC202とは独立して動作していない。

#### 【0088】

外部アクセスの試みが何らかのエラーの結果であった場合、方法は、エラーを訂正するためにエラークリーンアップを実行しようと試みることができる。そのようなクリーンアップは、上記の例のCPU222が、上記で説明した外部アクセスを引き起こしたエラーに対処しようと努めるためにエラー処理ルーチン/コードを動作させるまたは起動することを含むことができる。次いで、方法500は戻ることになる。

#### 【0089】

当業者によって理解されるように、図4Aおよび図5Aは、開示する方法400および500の例示的な実施形態を表しているにすぎない。他の実施形態では、図4Aに示す方法400または図5Aに示す方法500に追加のブロックまたはステップを加えることができる。同様に、いくつかの実施形態では、図4Aまたは図5Aに示す様々なブロックまたはステップを結合する、または省略することができる。方法400または方法500のそのような変形体は本開示の範囲内である。

#### 【0090】

加えて、本発明が説明した実施形態で機能するように、図4Aまたは図5Aを含めて、本明細書で説明したプロセスまたはプロセスフロー内のいくつかのステップが、他のステップよりも先行する場合があるのは当然である。しかしながら、そのような順序またはシーケンスが本発明の機能を変更しない場合、本開示は、説明したステップの順序に限定されない。さらに、いくつかのステップが、本開示の範囲から逸脱することなく、他のステップの前、後、またはそれと並行して(実質的に同時に)実行される場合があることを認識されたい。たとえば、上記で説明したように図5Aにおいては、ブロック516で起動されるウェイクアップのいずれかまたは全部が、ブロック518の外部アクセス信号の送信の前に実行されることは必要ではない。代わりに、ブロック516のウェイクアップのいくつかまたは全部が、ブロック518の外部アクセス信号の送信の後で、またはさらに、様々な実施形態において必要な場合、ブロック522のエラークリーンアップ実行の後でも、実行されることがある。

#### 【0091】

その上、場合によっては、本発明から逸脱することなく、いくつかのステップは、省略される場合もあり、または実行されない場合もある。方法400および方法500のそのような変形体は本開示の範囲内である。さらに、「それ以降」、「次いで」、「次に」、「後に」などの語は、ステップの順序を制限することは意図していない。これらの言葉は単に、例示的な方法の説明を理解できるように読者を導くために使用される。

#### 【0092】

方法400と方法500の両方について上述した様々な動作、方法、または機能は、様々なハードウェアおよび/またはソフトウェア構成要素/モジュールによって実行される場合がある。そのような構成要素および/またはモジュールは、上述した様々な動作、方法、または機能を実行するための手段を提供することができる。概して、対応する等価物であるミーンズプラスファンクションを有する、図に示した方法が存在する場合、動作ブロックは類似に番号付けされたミーンズプラスファンクションに対応する。たとえば、図4Aに示したブロック410～430は、図4Bに示したミーンズプラスファンクションブロック410'～430'に対応する。同様に、図5Aに示したブロック510～522は、図5Bに示したミーンズプラスファンクションブロック510'～522'に対応する。

#### 【0093】

さらに、プログラミングに関する当業者は、たとえば、本明細書におけるフローチャートおよび関連する説明に基づいて、難なく、開示した発明を実装するコンピュータコードを書くことができるか、または実装するのに適したハードウェアおよび/もしくは回路を特定することができる。したがって、特定の1つのセットのプログラムコード命令または

10

20

30

40

50

詳細なハードウェアデバイスの開示は、本発明の作製方法および使用方法を十分に理解するのに必要であるとは見なされない。特許請求されるプロセッサ実施プロセスの本発明の機能性は、種々のプロセスフローを例示する場合がある図面とともに、上述の説明において、より詳細に説明されている。

#### 【0094】

先に示したような1つまたは複数の例示的な態様では、説明した機能は、ハードウェア、ソフトウェア、ファームウェア、またはそれらの任意の組合せで実装することができる。ソフトウェアにおいて実装される場合には、その機能は、非一時的プロセッサ可読媒体のようなコンピュータ可読媒体上に1つまたは複数の命令またはコードとして記憶すること、または送信することができる。コンピュータ可読媒体は、ある場所から別の場所へのプログラムの転送を容易にする任意の媒体を含む、コンピュータ記憶媒体とコンピュータ通信媒体との両方を含む。10

#### 【0095】

記憶媒体は、コンピュータまたはプロセッサによってアクセスすることができる任意の利用可能な媒体とすることができます。限定はしないが、例として、そのようなコンピュータ可読媒体は、RAM、ROM、EEPROM、CD-ROMもしくは他の光ディスク記憶装置、磁気ディスク記憶装置もしくは他の磁気記憶デバイス、または命令もしくはデータ構造の形態で所望のプログラムコードを搬送または記憶するために使用することができ、コンピュータによってアクセスすることができる任意の他の媒体を含むことができる。ディスク(disk)およびディスク(disc)は、本明細書で使用するとき、コンパクトディスク(disc)(CD)、レーディスク(登録商標)(disc)、光ディスク(disc)、デジタル多用途ディスク(disc)(DVD)、フロッピー(登録商標)ディスク(disk)、およびブルーレイディスク(disc)を含み、ディスク(disk)は通常、データを磁気的に再生し、ディスク(disc)は、レーザーを用いてデータを光学的に再生する。上記の組合せも、非一時的コンピュータ可読媒体の範囲内に含まれるべきである。20

#### 【0096】

選択された態様が詳細に図示および説明されたが、以下の特許請求の範囲によって規定されるような本発明から逸脱することなく、本明細書において様々な置換および改変がなされる場合があることは理解されよう。

#### 【符号の説明】

#### 【0097】

- 100 ポータブルコンピューティングデバイス(PCD)

- 102 SoC

- 110 CPU

- 112 メモリ

- 120 コア

- 122 コア

- 123 コア

- 124 コア

- 126 アナログ信号プロセッサプロセッサ

- 128 ディスプレイコントローラ

- 130 タッチスクリーンコントローラ

- 132 ディスプレイ/タッチスクリーン

- 134 ビデオエンコーダ

- 136 ビデオ増幅器

- 138 ビデオポート

- 140 ユニバーサルシリアルバス(USB)コントローラ

- 142 USBポート

- 146 加入者識別モジュール(SIM)カード

- 148 デジタルカメラ

30

40

50

|      |                     |    |

|------|---------------------|----|

| 150  | ステレオオーディオコーデック      |    |

| 152  | オーディオ増幅器            |    |

| 154  | ステレオスピーカ            |    |

| 156  | ステレオスピーカ            |    |

| 157A | オンチップ熱センサ           |    |

| 157B | オフチップ熱センサ           |    |

| 158  | マイクロフォン増幅器          |    |

| 160  | マイクロフォン             |    |

| 162  | 周波数変調(FM)ラジオチューナ    | 10 |

| 164  | FMアンテナ              |    |

| 166  | ステレオヘッドフォン          |    |

| 168  | モデムデバイス/高周波(RF)送受信機 |    |

| 170  | RFスイッチ              |    |

| 172  | RFアンテナ              |    |

| 174  | キーパッド               |    |

| 176  | マイクロフォン付きモノヘッドセット   |    |

| 178  | バイブレータデバイス          |    |

| 188  | 電源                  |    |

| 200  | 例示的なシステム            |    |

| 202  | SoC                 | 20 |

| 220  | サブシステムA             |    |

| 222  | CPU                 |    |

| 224  | モニタモジュール            |    |

| 225  | 状態機械                |    |

| 226  | 絶縁HW                |    |

| 228  | メモリ                 |    |

| 229  | センサ                 |    |

| 230  | サブシステムB             |    |

| 240  | サブシステムC             |    |

| 250  | インターフェクト/バス         | 30 |

| 260  | メモリコントローラ           |    |

| 270  | 電力マネージャ             |    |

| 272  | 内部ロジック              |    |

| 280  | DDR                 |    |

| 300  | サブシステム              |    |

| 302  | SoC                 |    |

| 320  | サブシステムA             |    |

| 322  | CPU                 |    |

| 324  | モニタモジュール            |    |

| 326  | 絶縁HW                | 40 |

| 329  | センサ                 |    |

| 330  | サブシステムB             |    |

| 340  | サブシステムC             |    |

| 350  | インターフェクト/バス         |    |

| 360  | メモリコントローラ           |    |

| 370  | 電力マネージャ             |    |

| 380  | DDR                 |    |

| 390  | サブシステムD             |    |

| 392  | DSP                 |    |

| 394  | モニタモジュール            | 50 |

【図1】

【図2 A】

【図2 B】

【図3】

【図4A】

【図4B】

【図5A】

【図5B】

---

フロントページの続き

(72)発明者 フィリップ・ミュラー・ジュニア

アメリカ合衆国・カリフォルニア・92121・サン・ディエゴ・モアハウス・ドライブ・577

5

(72)発明者 ジュラン・ジャオ

アメリカ合衆国・カリフォルニア・92121・サン・ディエゴ・モアハウス・ドライブ・577

5

(72)発明者 カール・ヴィクター・ストリーター

アメリカ合衆国・カリフォルニア・92121・サン・ディエゴ・モアハウス・ドライブ・577

5

(72)発明者 ラシュミ・クルカルニ

アメリカ合衆国・カリフォルニア・92121・サン・ディエゴ・モアハウス・ドライブ・577

5

審査官 清木 泰

(56)参考文献 米国特許出願公開第2013/0262903(US,A1)

米国特許出願公開第2012/0100895(US,A1)

特開2013-003911(JP,A)

(58)調査した分野(Int.Cl., DB名)

G 06 F 15 / 78

G 06 F 15 / 16 - 15 / 177

G 06 F 15 / 80

G 06 F 9 / 38

G 06 F 1 / 26 - 1 / 3296

G 06 F 1 / 04 - 1 / 14

G 06 F 12 / 00 - 12 / 06

G 06 F 13 / 16 - 13 / 18

G 06 F 11 / 07

G 06 F 11 / 28 - 11 / 36

G 06 F 9 / 455 - 9 / 54