**(19) 대한민국특허청(KR)**

**(12) 등록특허공보(B1)**

(51) Int. Cl.

*G01R 19/00* (2006.01)

(45) 공고일자

2006년09월22일

(11) 등록번호

10-0627000

(24) 등록일자

2006년09월15일

(21) 출원번호

10-2003-0020776

(65) 공개번호

10-2003-0079761

(22) 출원일자

2003년04월02일

(43) 공개일자

2003년10월10일

(30) 우선권주장

02392004.4

2002년04월02일

유럽특허청(EPO)(EP)

(73) 특허권자

다이얼로그 세미컨덕터 게엠베하

독일, 키르하임-나베른, 디-73230, 노이에 스트라세 95

(72) 발명자

크뇌트겐호어스트

독일, 뮌헨80997, 히틀스트라세 64

(74) 대리인

이병호

정상구

신현문

이범래

심사관 : 한충희

**(54) 전류 감지용 연료 게이지 파워 스위치****요약**

새로운 전류 감지 회로가 달성된다. 첫 번째, 이 회로는 게이트, 소스 및 드레인을 가진 출력 트랜지스터를 포함한다. 드레인은 부하에 결합되고, 소스는 파워 레일(power rail)에 결합되며, 게이트는 출력 트랜지스터가 출력 전류를 도통시키도록 제어 전압에 결합된다. 두 번째, 감지 트랜지스터는 게이트, 소스, 및 드레인을 가진다. 소스는 파워 레일에 결합되고 게이트는 제어 전압에 결합된다. 감지 인자(sensing factor)는 감지 트랜지스터 크기에 의해 나누어지는 출력 트랜지스터 크기를 포함한다. 세 번째, 감지 트랜지스터 드레인-소스(drain-to-source) 전압과 출력 트랜지스터 드레인-소스 전압을 등화하는(equalizing) 수단이 감지 트랜지스터 드레인 전류가 감지 인자에 의해 나누어지는 출력 전류를 포함하도록 이용된다. 마지막으로, 전류 제어 발진기가 구비된다. 전류 제어 발진기는 입력과 출력을 가진다. 입력은 감지 트랜지스터 드레인 전류를 포함한다. 출력은 출력 전류에 비례하는 주파수를 가지는 주기적 신호(cyclical signal)를 포함한다.

**대표도**

도 1

**색인어**

전류 감지 회로, 게이트, 소스, 드레인, 트랜지스터.

**명세서**

## 도면의 간단한 설명

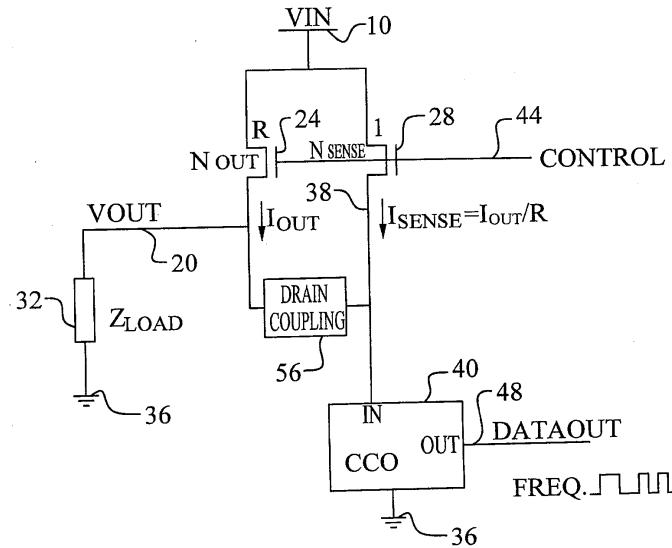

도 1은 본 발명의 양호한 실시예를 도시한 도면.

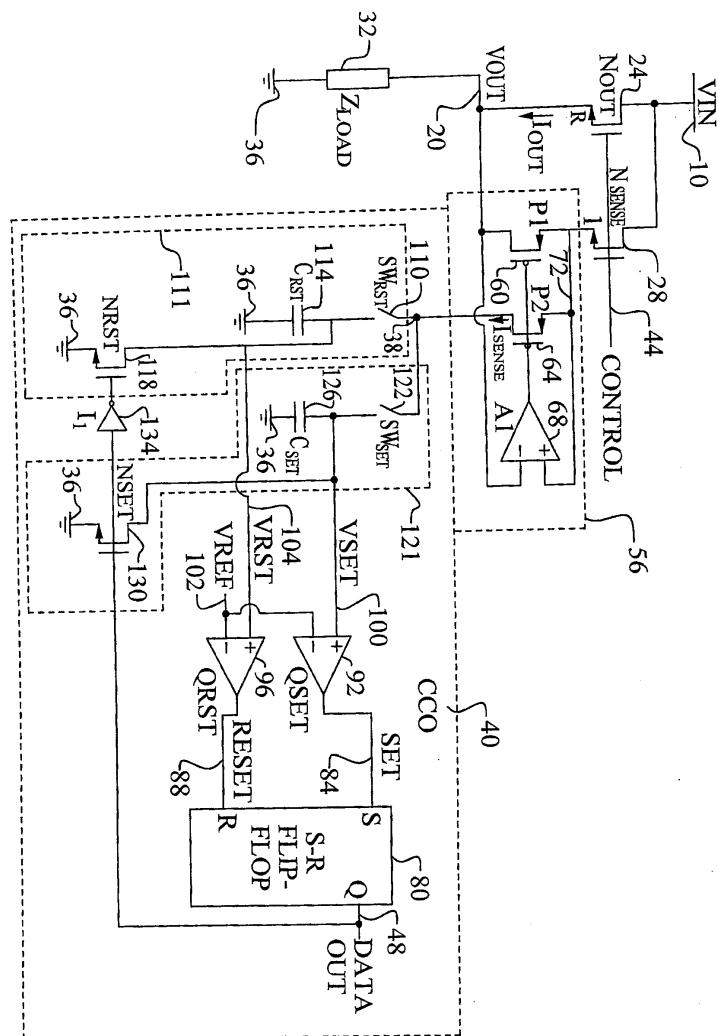

도 2는 본 발명의 양호한 실시예의 더 상세한 버전을 도시한 도면.

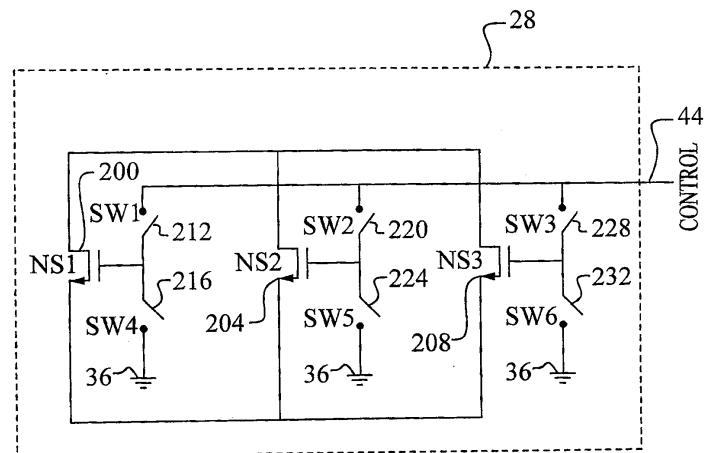

도 3은 조정 가능한 감지 인자를 얻기 위한 방법을 도시한 도면.

\*도면의 주요 부분에 대한 부호의 설명\*

10: 파워 24: 출력 트랜지스터

28: 감지 트랜지스터 32: 부하

40: 전류 제어 발진기

## 발명의 상세한 설명

### 발명의 목적

#### 발명이 속하는 기술 및 그 분야의 종래기술

##### (1) 발명의 분야

본 발명은 파워 출력에 대한 전류 감지 회로에 관한 것으로, 특히 출력 전류에 비례하는 주파수를 발생시키기 위해 감지 전류 매칭 회로와 전류 제어 발진기(oscillator)를 이용하는 신규한 전류 감지 회로에 관한 것이다.

##### (2) 종래 기술의 설명

전류 감지 회로들에는 많은 응용들(applications)이 있다. 파워 스위칭 회로들에 있어서, 과전류(over-current) 보호가 행해 질 수 있도록 부하 전류를 아는 것이 바람직하다. 또한, 전류 레벨이 제어되어야 하는, 연료 게이지 회로(fuel gauge circuit)들과 같은, 일부 응용들에서 부하 전류를 아는 것이 유용하다. 부하 전류 경로에서 감지 저항의 추가 없이 부하 전류를 정확히 결정하는 것이 또한 바람직하다.

몇 개의 종래 기술 발명들이 전류 감지 회로들을 설명한다. 호드긴스(Hodgins) 등에 의한 미국특허 제5,821,740호는 출력 구동기에 병렬하는 감지 트랜지스터를 이용하는 DC-DC 변환기(DC-to-DC converter)를 설명한다. 감지 레지스터는 감지 트랜지스터에 의해 구동되고 과전류 상태들을 검출하는데 이용된다. 레들(Reed)에 의한 미국특허 제5,680,034호 및 블럼(Blum) 등에 의한 미국특허 제6,201,417호는 전류 감지 레지스터를 이용하는 펄스폭 변조(pulse width modulation:PWM) 제어기들 및 전류를 제한하기 위한 S-R 래치(S-R latch)를 교시한다.

#### 발명이 이루고자 하는 기술적 과제

### 발명의 요약

본 발명의 주 목적은 파워 스위치 출력에 대한 효율적이고 매우 제조 가능한 전류 감지 회로를 제공하는 것이다.

본 발명의 다른 목적은 감지 전류가 감지 트랜지스터를 이용하여 생성되는 전류 감지 회로를 제공하는 것이다.

본 발명의 또 다른 목적은 파워 트랜지스터와 감지 트랜지스터에 대한 드레인 대 소스 전압을 등화함으로써 감지 전류의 정확성(accuracy)을 개선하는 것이다.

본 발명의 또 다른 목적은 전류 제어 발진기를 이용하여 파워 스위치 출력 전류에 비례하는 디지털 주파수 신호를 제공하는 것이다.

본 발명의 또 다른 목적은 높은 동적 범위와 우수한 선형성(linearity)을 갖는 전류 감지 회로를 제공하는 것이다.

본 발명의 또 다른 목적은 조정 가능한 감지 인자를 갖는 감지 회로를 제공하는 것이다.

### 발명의 구성 및 작용

본 발명의 목적들에 따라, 전류 감지 회로가 달성된다. 첫 번째로, 이 회로는 게이트, 소스 및 드레인을 갖는 출력 트랜지스터를 포함한다. 드레인은 부하에 결합되고, 소스는 파워 레일에 결합되며, 게이트는 출력 트랜지스터가 출력 전류를 도통시키도록 제어 전압에 결합된다. 두 번째, 감지 트랜지스터는 게이트, 소스, 및 드레인을 갖는다. 소스는 파워 레일에 결합되고, 게이트는 제어 전압에 결합된다. 감지 인자는 감지 트랜지스터 크기에 의해 나누어지는 출력 트랜지스터 크기를 포함한다. 세 번째, 감지 트랜지스터 드레인-소스(drain-to-source) 전압과 출력 트랜지스터 드레인-소스 전압을 등화하는 수단이 감지 트랜지스터 드레인 전류가 감지 인자에 의해 나누어지는 출력 전류를 포함하도록 이용된다. 마지막으로, 전류 제어 발진기가 구비된다. 전류 제어 발진기는 입력과 출력을 가진다. 입력은 감지 트랜지스터 드레인 전류를 포함한다. 출력은 출력 전류에 비례하는 주파수를 갖는 주기적 신호를 포함한다.

본 발명은 본 명세서의 주요 부분을 형성하는 첨부된 도면들을 참조하여 설명한다.

#### (바람직한 실시예들의 설명)

바람직한 실시예들은 파워 스위칭 출력을 위한 신규한 전류 감지 회로를 개시한다. 본 발명은 전류 감지 FET를 이용하는 전류 감지 회로, 파워 스위치 FET와 감지 FET의 드레인-소스 전압들을 등화하는 회로, 및 감지 전류를 비례 주파수 (proportional frequency)로 변환하는 전류 제어 발진기를 개시하고 있다. 본 발명이 본 발명의 범위를 벗어나지 않고서 적용 및 확장될 수 있음이 이 분야의 숙련된 자들에게는 명백하다.

이하, 도 1을 참조하여, 본 발명의 바람직한 실시예가 예시된다. 본 발명의 몇몇 중요한 특징들이 도시된다. 회로는 우선 게이트, 소스, 및 드레인을 갖는 출력 트랜지스터 NOUT(24)를 포함한다. 출력 트랜지스터는 바람직하게는 NMOS FET 장치를 포함한다. PMOS 장치를 포함하는 임의의 FET 장치들이 이용될 수 있다. 출력 트랜지스터 NOUT의 드레인은 출력 노드 VOUT(20)에서 외부 부하  $Z_{LOAD}$ (32)에 결합된다. NOUT(24)의 소스는 파워 레일에 결합되고, 이 경우에는 VIN 파워(10)에 결합된다. NOUT(24)의 게이트는 제어 전압 CONTROL(44)에 결합되어, NOUT은 CONTROL이 NOUT의 임계값 위의 전압으로 어서트(assert)될 때 출력 전류를 도통시킨다. 이러한 배열에서, 출력은 높은 측 구동기 회로(hight side driver circuit)이며, 여기서 CONTROL 신호(44)는 출력 전압 VOUT보다 실질적으로 더 높아야 하고, 전하 펌프를 요구할 수 있다. 다른 바이어싱 배열들(biasing arrangements)이 이용될 수 있다. 이것은 본 발명의 필수적인 특징은 아니다.  $Z_{LOAD}$ (32)가 코일과 같은 유도성 부하 또는 저항성 부하를 포함할 수 있다는 것에 유의해야 한다. 또한, 이러한 회로는 DC-DC 변환기의 일부분을 포함할 수 있다,

둘째로, 감지 트랜지스터 NSENSE(28)는 게이트, 소스, 및 드레인을 가진다. NSENSE의 소스는 파워 레일 VIN(10)에 결합되고, NSENSE의 게이트는 제어 전압 CONTROL(44)에 결합된다. 감지 트랜지스터 NSENSE는 NOUT(24)과 동일한 유형의 장치를 포함해야 한다. NOUT이 NMOS 장치라면, 이때 NSENSE는 동일한 프로세스 파라미터들의 NMOS 장치여야 한다. 출력 트랜지스터 NOUT는 R의 상대적인 크기를 가지며, 한편 감지 트랜지스터는 1의 상대적인 크기를 가진다는 것에 유의해야 하며, 여기서  $R > 1$ 이다. 예컨대, NOUT(24)는 약 500 킬로마이크론(kilomicrons)의 폭과 약 0.5 마이크론의 길이를 갖는 매우 큰 구동 트랜지스터일 수 있다. 감지 트랜지스터 NSENSE(28)는 훨씬 작을 것이다. 예컨대, NSENSE는 약 500 마이크론의 폭과 약 0.5 마이크론의 길이를 수도 있다. 감지 인자(R)는 감지 트랜지스터 크기에 의해 나누어진 출력 트랜지스터 크기를 포함한다. 이러한 예의 경우에, R은 1000과 동일하다. 바람직한 실시예에서, 감지 인자(R)는 약 1과 10,000사이의 범위를 포함한다. 또한, 선택적 특징으로서, 감지 인자(R)는 가변으로 될 수 있다. 가변 감지 인자(R)를 생성하는 바람직한 수단은 도 3에 도시되며, 하기에 논의된다.

도 1을 다시 참조하면, 등화 수단(56) 또는 드레인 커플링(56), 감지 트랜지스터 NSENSE(28) 드레인-소스 전압, 출력 트랜지스터 NOUT(24) 드레인-소스 전압이 이용되어, 감지 트랜지스터 NSENSE 드레인 전류  $I_{SENSE}$ 는 감지 인자(R)에 의해 나누어진 출력 전류  $I_{OUT}$ 를 포함한다. 드레인 커플링(56)의 바람직한 실시예가 도 2에 도시되며, 하기에 논의된다. 도 1을 다시 참조하면, 전류 제어 발진기(current controlled oscillator: CCO)(40)가 포함된다. 전류 제어 발진기(40)는 입력

(38)과 출력 DATAOUT(48)을 갖는다. CCO(40)로의 입력은 감지 트랜지스터 드레인 전류  $I_{SENSE}$ 를 포함한다. 출력 DATAOUT(48)은 출력 전류에 비례하는 주파수를 갖는 주기적 신호(cyclical signal)를 포함한다. CCO(40)의 바람직한 구현은 도 2에 도시되며, 하기에 논의된다.

도 2를 참조하면, 본 발명의 바람직한 실시예의 더 상세한 버전이 도시된다. 본 발명의 몇몇 중요한 특징들이 예시된다. 도 1과 도 2사이의 같은 특징이 예시된 곳에서, 요소들은 동일한 번호가 붙여진다. 도 2에서, NOUT(24)과 NSENSE(28)의 드레인 전압들을 등화하는 수단(56)이 상세히 도시된다. 등화 회로(56)의 수단은 NOUT(24)과 NSENSE(28)의 동작 조건들을 거의 등화하는데 이용된다. 특히, 설계에 의해, NOUT(24)과 NSENSE(28)의 게이트-소스 전압들은 동일하다. 드레인-소스 전압들을 동일하게 함으로써, 두 장치들의 드레인 전류는  $I_{SENSE} = I_{OUT} / R$ 에 의해 주어진 식에 맞추어진다.

NOUT(24)과 NSENSE(28)의 드레인 전압들을 등화하는 수단(56)은 바람직하게는 우선 게이트, 드레인, 및 소스를 갖는 제 1 트랜지스터 P1(60)를 포함한다. P1(60)의 소스는 NSENSE(28)의 드레인에 결합된다. P1(60)의 드레인은 NOUT(28)의 드레인에 결합된다. 둘째로, 제 2 트랜지스터 P2(64)는 게이트, 드레인, 및 소스를 갖는다. P2(64)의 소스는 감지 트랜지스터 NSENSE 드레인에 결합된다. P2(64)의 드레인은 전류 제어 발진기 CCO(40) 입력에 결합된다. P1(60) 및 P2(64)는 모두 바람직하게 PMOS 장치들을 포함한다.

두개의 입력들과 출력을 갖는 증폭기 A1(68)은 등화 수단(56)을 완성한다. 한 입력은 NSENSE(28)의 드레인에 결합된다. 다른 입력은 NOUT(24)의 드레인에 결합된다. A1(68)의 출력은 P1(60) 및 P2(64) 게이트들에 결합된다. 이러한 새로운 구성에서, 회로(56)는 감지 전류  $I_{SENSE}$ 가 CCO 회로(40)로 흐르게 하는 동안 NOUT(24)과 NSENSE(28)의 드레인 전압들이 거의 동일한 전압이 되게 한다.

전류 제어 발진기 회로(40)의 바람직한 실시예의 중요한 상세부분들이 도 2에 도시된다. 회로(40)는 바람직하게는 우선 S-R 플립-플롭(80)을 포함한다. S-R 플립-플롭(80)은 세트(set) 입력과 리세트(reset) 입력 및 출력을 갖는다. S-R 플립-플롭(80) 출력은 전류 제어 발진기 출력 DATAOUT(48)을 포함한다. 둘째로, 세트 비교기(set comparator) QSET(92)는 두개의 입력들과 출력을 갖는다. 하나의 QSET(92) 입력은 전압 기준 VREF(102)에 결합된다. QSET(92)의 출력은 S-R 플립-플롭(80) SET 입력에 결합된다. 세째로, 리세트 비교기 QRST(96)는 두개의 입력들과 출력을 갖는다. 하나의 QRST(96) 입력이 전압 기준에 결합된다. QRST(96) 출력은 S-R 플립-플롭(80) RESET 입력에 결합된다.

넷째로, 세트 전류-전압 변환기(121)는 제 1 스위치 SW<sub>SET</sub>(122), 커패시터 C<sub>SET</sub>(126), 및 제 2 스위치 NSET(130)를 포함한다. 세트 전류-전압 변환기(121)는 입력(38) 및 출력 VSET(100)를 구비한다. 세트 전류-전압 변환기(121)에 대한 입력은 감지 전류  $I_{SENSE}$ 이다.  $I_{SENSE}$ 는 제 1 스위치 SW<sub>SET</sub>(122)에 의해 CCO(40) 입력에 스위칭 가능하게 결합된다. SW<sub>SET</sub>(122)가 ON일 때,  $I_{SENSE}$ 는 CSET(126)을 충전시키고 그에 의해 전류가 전압 VSET(100)로 변환된다. VSET(100)은 세트 비교기 QSET(92)에 결합된다.

마지막으로, 리세트 전류-전압 변환기(111)는 제 1 스위치 SW<sub>RST</sub>(110), 커패시터 C<sub>RST</sub>(114), 및 제 2 스위치 NRST(118)를 포함한다. 리세트 전류-전압 변환기(111)는 입력(38) 및 출력 VRST(104)를 구비한다. 리세트 전류-전압 변환기(111)에 대한 입력은 또한 감지 전류  $I_{SENSE}$ 이다.  $I_{SENSE}$ 는 제 1 스위치 SW<sub>RST</sub>(110)에 의해 CCO(40) 입력에 스위칭 가능하게 결합된다. SW<sub>RST</sub>(110)가 ON일 때,  $I_{SENSE}$ 는 CRST(114)를 충전시키고, 그에 의해 전류는 전압 VRST(104)로 전환된다. VRST(104)는 리세트 비교기 QRST(96)에 결합된다.

CCO 회로(40)는 세트 또는 리세트 모드 중 어느 하나에서 동작한다. 세트 모드에 있어서, S-R 플립플롭(80)은 세트되고 DATAOUT 신호(48)는 하이(high)가 된다. 이러한 상태에서, 세트 제 2 스위치 NSET(130)은 ON이 되고 세트 제 1 스위치 SW<sub>SET</sub>(122)는 OFF가 된다. 따라서, VSET(100) 노드는 NSET(130)을 통해 접지(36)에 접속된다. 한편, 반전기 I<sub>1</sub>(134)로 인해, 리세트 제 2 스위치 NRST(118)은 OFF가 되고 리세트 제 1 스위치 SW<sub>RST</sub>(110)은 ON이 된다. 이러한 상태에서, 감지 전류  $I_{SENSE}$ 는 C<sub>RST</sub>(114)를 충전시키고, 그에 의해 전류는 전압 VRST(104)로 변환된다. VRST(104)가 전압 기준 VREF(102)을 초과할 때, 리세트 비교기 QRST(96)는 S-R 플립플롭(80)의 RESET(88) 라인을 어서트하기( assert) 위해 하이로 스위칭한다. SET 라인(84)이 NSET(130)에 의해 로우(low)로 이미 구동되었을 때, S-R 플립플롭(80)의 상태는 RESET로 변하고 DATAOUT(48)은 로우로 구동된다.

RESET 상태 동안, 리세트 전류-전압 변환기(111)는 OFF 상태에 있으며, 여기서, NRST(118)은 ON이 되고 SW<sub>RST</sub>(110)은 OFF가 된다. SW<sub>SET</sub>(122)는 ON이 되고 NSET(130)은 OFF가 된다. 따라서, 감지 전류 I<sub>SENSE</sub>는 세트 커패시터 CSET(126)을 충전시키고, VSET(100)은 전압을 증가시킨다. VSET(100)가 값 VREF(102)를 초과할 때, 세트 비교기 QSET(92)는 토클링(toggling)된다. SET 신호(84)가 어서트된다. RESET(88)가 NRST(118)에 의해 로우로 구동되기 때문에, S-R 플립플롭(80)은 다시 강제로 SET 상태가 된다.

S-R 플립플롭(80)은 I<sub>SENSE</sub> 전류에 정비례하는 주파수에서 하이와 로우 사이를 주기적으로 토클링 할 것이다. I<sub>SENSE</sub>의 값이 크면 클수록, 커패시터들은 더 빨리 바뀌게 되고 DATAOUT(48)은 더 빨리 순환한다. I<sub>SENSE</sub>의 더 작은 값들은 사이클 주파수를 감소시킨다. 주파수가 모니터링된다면, 파워 스위치 NOUT(24)의 에너지가 모니터링될 수 있다.

상당히, 새로운 설계는 조정되어야 하는 전압 기준 VREF(102)만을 포함한다. VREF(102)를 조정함으로써, 예를 들면 저항기 값의 트리밍을 통해 커패시터 값들에서의 변경을 처리하기 위한 보정이 행해질 수 있다. 또한, 이러한 단순 CCO 회로(40)를 이용함으로써, 회로의 선형성이 매우 높다. 커패시터들 CSET(126) 및 CRST(114)의 온도 편류(drift)만이 중요하다. 그러나, 이러한 편류는 단지 30ppm이다. 따라서 시스템은 온도에 대해 매우 안정하다.

부가적인 특징들로서, 감지 인자(R)가 조정될 수 있고, 그에 의해 전류의 동적 범위를 조정한다. 예를 들면, 상대적으로 작은 출력 전류들 I<sub>OUT</sub>에 대해, 감지 전류 I<sub>SENSE</sub>가 양호한 노이즈 내성 및 주파수 출력을 위해 충분히 크게 되도록 감지 인자(R)를 감소시키는 것이 바람직할 수 있다. 대안적으로, 출력 전류 I<sub>OUT</sub>가 매우 클 때 감지 인자(R)를 증가시키는 것이 바람직할 수 있다.

이제 도 3을 참조하면, 가변하는 감지 인자를 제공하는 단순하고 양호한 수단이 도시되어 있다. 감지 트랜지스터(28)는 복수의 감지 트랜지스터들 NS1(200), NS2(204), 및 NS3(208)으로 나누어진다. 일련의 스위치들 SW1(212) 내지 SW6(232)은 감지 장치들의 임의의 것 또는 감지 장치들의 조합 중 어느 것이 사용되는가를 선택하는데 사용된다. 이러한 유형의 회로는, 예를 들면 약 10마이크로 암페어에서 약 3암페어까지의 출력 전류의 동적 범위가 동일한 회로를 이용하여 비례 주파수들로 변환될 수 있도록 감지 인자들의 범위를 생성하는데 이용될 수 있다.

본 발명은 파워 스위치 출력을 위한 효과적이고 충분히 제조 가능한 전류 감지 회로를 제공한다. 전류 감지 회로는 감지 트랜지스터를 이용하여 감지 전류를 발생시킨다. 감지 전류의 정확성은 파워 트랜지스터 및 감지 트랜지스터에 대한 드레인-소스 전압을 등화함으로써 개선된다. 전류 제어 발진기를 이용하여 파워 스위치 출력 전류에 비례하는 주파수를 갖는 주기적 출력 신호가 발생된다. 전류 감지 회로는 높은 동적 범위 및 우수한 선형성을 나타낸다. 최종적으로, 감지 회로는 조정 가능한 감지 인자를 가질 수 있다.

양호한 실시예들에 나타낸 바와 같이, 파워 스위치를 위한 새로운 전류 감지 회로는 종래 기술에 대한 효과적이고 제조 가능한 대안을 제공한다.

본 발명은 특히 그 양호한 실시예들을 참조하여 도시되고 기술되었지만, 본 기술 분야의 숙련된 기술자들은 본 발명의 정신 및 범위를 벗어나지 않고 형태 및 세부 사항들에서의 다양한 변경들이 이루어질 수 있음을 이해할 것이다.

### 발명의 효과

본 발명은 파워 스위치 출력에 대한 효율적이고 매우 제조 가능한 전류 감지 회로를 제공한다.

### (57) 청구의 범위

#### 청구항 1.

전류 감지 회로(current sense circuit)에 있어서,

게이트, 소스, 및 드레인을 갖는 출력 트랜지스터로서, 상기 드레인은 부하(load)에 결합되고, 상기 소스는 파워 레일(power rail)에 결합되고, 상기 게이트는 상기 출력 트랜지스터가 출력 전류를 도통시키도록 제어 전압에 결합되는, 상기 출력 트랜지스터와;

게이트, 소스, 및 드레인을 갖는 감지 트랜지스터로서, 상기 소스는 상기 파워 레일에 결합되고, 상기 게이트는 상기 제어 전압에 결합되고, 감지 인자(sensing factor)가 상기 감지 트랜지스터 크기에 의해 나누어지는 상기 출력 트랜지스터 크기를 포함하는, 상기 감지 트랜지스터와;

상기 감지 트랜지스터 드레인 전류가 상기 감지 인자에 의해 나누어지는 상기 출력 전류를 포함하도록 상기 감지 트랜지스터 드레인-소스 전압과 상기 출력 트랜지스터 드레인-소스 전압을 등화하는(equalizing) 수단과;

입력 및 출력을 갖는 전류 제어 발진기로서, 상기 입력은 상기 감지 트랜지스터 드레인 전류를 포함하고, 상기 출력은 상기 출력 전류에 비례하는 주파수를 갖는 주기적 신호(cyclical signal)를 포함하는, 상기 전류 제어 발진기를 포함하는, 전류 감지 회로.

## 청구항 2.

제 1 항에 있어서, 상기 출력 트랜지스터 및 상기 감지 트랜지스터는 NMOS 트랜지스터들을 포함하는, 전류 감지 회로.

## 청구항 3.

제 1 항에 있어서, 상기 감지 인자값은 약 1과 10,000 사이의 범위를 포함하는, 전류 감지 회로.

## 청구항 4.

제 1 항에 있어서, 상기 감지 인자값은 조정 가능한, 전류 감지 회로.

## 청구항 5.

제 1 항에 있어서, 상기 등화하는 수단은:

게이트, 드레인, 및 소스를 갖는 제 1 트랜지스터로서, 상기 소스는 상기 감지 트랜지스터 드레인에 결합되고, 상기 드레인은 상기 출력 트랜지스터 드레인에 결합되는, 상기 제 1 트랜지스터와;

게이트, 드레인, 및 소스를 갖는 제 2 트랜지스터로서, 상기 소스는 상기 감지 트랜지스터 드레인에 결합되고, 상기 드레인은 상기 전류 제어 발진기 입력에 결합되는, 상기 제 2 트랜지스터와;

두개의 입력들 및 출력을 갖는 증폭기로서, 하나의 상기 입력은 상기 감지 트랜지스터 드레인에 결합되고, 다른 하나의 상기 입력은 상기 출력 트랜지스터 드레인에 결합되며, 상기 출력은 상기 제 1 및 제 2 트랜지스터 게이트들에 결합되는, 상기 증폭기를 포함하는, 전류 감지 회로.

## 청구항 6.

제 5 항에 있어서, 상기 제 1 및 제 2 트랜지스터들은 PMOS 트랜지스터들을 포함하는, 전류 감지 회로.

## 청구항 7.

제 1 항에 있어서, 상기 전류 제어 발진기는:

세트(set) 및 리세트(reset) 입력들 및 출력을 갖는 S-R 플립-플롭으로서, 상기 출력은 상기 전류 제어 발진기 출력을 포함하는, 상기 S-R 플립-플롭과;

두개의 입력들과 출력을 갖는 세트 비교기(set comparator)로서, 하나의 상기 입력은 전압 기준(voltage reference)에 결합되고, 상기 출력은 상기 S-R 플립-플롭 세트 입력에 결합되는, 상기 세트 비교기와;

두개의 입력들과 출력을 갖는 리세트 비교기로서, 하나의 상기 입력은 상기 전압 기준에 결합되고, 상기 출력은 상기 S-R 플립-플롭 리세트 입력에 결합되는, 상기 리세트 비교기와;

입력 및 출력을 갖는 세트 전류-전압 변환기(set current-to-voltage converter)로서, 상기 입력은 상기 전류 제어 발진기 입력에 스위칭 가능하게 결합되고 상기 출력은 상기 세트 비교기에 결합되는, 상기 세트 전류-전압 변환기와;

입력 및 출력을 갖는 리세트 전류-전압 변환기로서, 상기 입력은 상기 전류 제어 발진기 입력에 스위칭 가능하게 결합되고, 상기 출력은 상기 리세트 비교기에 결합되는, 상기 리세트 전류-전압 변환기를 포함하는, 전류 감지 회로.

## 청구항 8.

제 7 항에 있어서, 상기 세트 및 리세트 전류-전압 변환기들은:

두개의 단자들을 갖는 커패시터와;

상기 전류 제어 발진기 입력과 제 1의 상기 커패시터 단자 사이에 결합되는 제 1 스위치와;

제 2의 상기 커패시터 단자와 접지 사이에 결합되는 제 2 스위치를 포함하는, 전류 감지 회로.

## 청구항 9.

전류 감지 회로에 있어서,

게이트, 소스, 및 드레인을 갖는 출력 트랜지스터로서, 상기 드레인은 부하에 결합되고, 상기 소스는 파워 레일에 결합되고, 상기 게이트는 상기 출력 트랜지스터가 출력 전류를 도통시키도록 제어 전압에 결합되는, 상기 출력 트랜지스터와;

게이트, 소스, 및 드레인을 갖는 감지 트랜지스터로서, 상기 소스는 상기 파워 레일에 결합되고, 상기 게이트는 상기 제어 전압에 결합되며, 감지 인자가 상기 감지 트랜지스터 크기에 의해 나누어지는 상기 출력 트랜지스터 크기를 포함하는, 상기 감지 트랜지스터와;

상기 감지 트랜지스터 드레인 전류가 상기 감지 인자에 의해 나누어지는 상기 출력 전류를 포함하도록 상기 감지 트랜지스터 드레인-소스 전압과 상기 출력 트랜지스터 드레인-소스 전압을 등화하는 수단으로서, 상기 등화하는 수단은:

게이트, 드레인, 및 소스를 갖는 제 1 트랜지스터로서, 상기 소스는 상기 감지 트랜지스터 드레인에 결합되고, 상기 드레인은 상기 출력 트랜지스터 드레인에 결합되는, 상기 제 1 트랜지스터와;

게이트, 드레인, 및 소스를 갖는 제 2 트랜지스터로서, 상기 소스는 상기 감지 트랜지스터 드레인에 결합되고, 상기 드레인은 상기 전류 제어 발진기 입력에 결합되는, 상기 제 2 트랜지스터와;

두개의 입력들과 출력을 갖는 증폭기로서, 하나의 상기 입력은 상기 감지 트랜지스터 드레인에 결합되고, 다른 하나의 상기 입력은 상기 출력 트랜지스터 드레인에 결합되며, 상기 출력은 상기 제 1 및 제 2 트랜지스터 게이트들에 결합되는, 상기 증폭기를 포함하는, 상기 등화하는 수단과;

입력 및 출력을 갖는 전류 제어 발진기로서, 상기 입력은 상기 감지 트랜지스터 드레인 전류를 포함하고, 상기 출력은 상기 출력 전류에 비례하는 주파수를 갖는 주기적 신호를 포함하는, 상기 발진기를 포함하는, 전류 감지 회로.

### 청구항 10.

제 9 항에 있어서, 상기 출력 트랜지스터 및 상기 감지 트랜지스터는 NMOS 트랜지스터들을 포함하는, 전류 감지 회로.

### 청구항 11.

제 9항에 있어서, 상기 감지 인자값은 약 1과 10,000 사이의 범위를 포함하는, 전류 감지 회로.

### 청구항 12.

제 9항에 있어서, 상기 감지 인자값은 조정가능한, 전류 감지 회로.

### 청구항 13.

제 9항에 있어서, 상기 제 1 및 제 2 트랜지스터들은 PMOS 트랜지스터들을 포함하는, 전류 감지 회로.

### 청구항 14.

제 9항에 있어서, 상기 전류 제어 발진기는:

세트 및 리세트 입력들 및 출력을 갖는 S-R 플립-플롭으로서, 상기 출력은 상기 전류 제어 발진기 출력을 포함하는, 상기 S-R 플립-플롭과;

두개의 입력들 및 출력을 갖는 세트 비교기로서, 하나의 상기 입력은 전압 기준에 결합되고, 상기 출력은 상기 S-R 플립-플롭 세트 입력에 결합되는, 상기 세트 비교기와;

두개의 입력들 및 출력을 갖는 리세트 비교기로서, 하나의 상기 입력은 상기 전압 기준에 결합되고, 상기 출력은 상기 S-R 플립-플롭 리세트 입력에 결합되는, 상기 리세트 비교기와;

입력과 출력을 갖는 세트 전류-전압 변환기로서, 상기 입력은 상기 전류 제어 발진기 입력에 스위칭 가능하게 결합되고, 상기 출력은 상기 세트 비교기에 결합되는, 상기 세트 전류-전압 변환기와;

입력과 출력을 갖는 리세트 전류-전압 변환기로서, 상기 입력은 상기 전류 제어 발진기 입력에 스위칭 가능하게 결합되고, 상기 출력은 상기 리세트 비교기에 결합되는, 상기 리세트 전류-전압 변환기를 포함하는, 전류 감지 회로.

### 청구항 15.

제 14항에 있어서, 상기 세트 및 리세트 전류-전압 변환기들은:

두개의 단자들을 갖는 커패시터와;

상기 전류 제어 발진기 입력과 제 1의 상기 커패시터 단자 사이에 결합되는 제 1 스위치와;

제 2의 상기 커패시터 단자와 접지 사이에 결합되는 제 2 스위치를 포함하는, 전류 감지 회로.

## 청구항 16.

전류 감지 회로에 있어서,

게이트, 소스, 및 드레인을 갖는 출력 트랜지스터로서, 상기 드레인은 부하에 결합되고, 상기 소스는 파워 레일에 결합되고, 상기 게이트는 상기 출력 트랜지스터가 출력 전류를 도통시키도록 제어 전압에 결합되는, 상기 출력 트랜지스터와;

게이트, 소스, 및 드레인을 갖는 감지 트랜지스터로서, 상기 소스는 상기 파워 레일에 결합되고, 상기 게이트는 상기 제어 전압에 결합되고, 상기 감지 인자는 상기 감지 트랜지스터 크기에 의해 나누어지는 상기 출력 트랜지스터 크기를 포함하는, 상기 감지 트랜지스터와;

상기 감지 트랜지스터 드레인 전류가 상기 감지 인자에 의해 나누어지는 상기 출력 전류를 포함하도록 상기 감지 트랜지스터 드레인-소스 전압 및 상기 출력 트랜지스터 드레인-소스 전압을 등화하는 수단으로서, 상기 등화하는 수단은:

게이트, 소스, 및 드레인을 갖는 제 1 트랜지스터로서, 상기 소스는 상기 감지 트랜지스터 드레인에 결합되고, 상기 드레인은 상기 출력 트랜지스터 드레인에 결합되는, 상기 제 1 트랜지스터와;

게이트, 소스, 및 드레인을 갖는 제 2 트랜지스터로서, 상기 소스는 상기 감지 트랜지스터 드레인에 결합되고, 상기 드레인은 상기 전류 제어 발진기 입력에 결합되는, 상기 제 2 트랜지스터와;

두개의 입력들 및 출력을 갖는 증폭기로서, 하나의 상기 입력은 상기 감지 트랜지스터 드레인에 결합되고, 다른 하나의 상기 입력은 상기 출력 트랜지스터 드레인에 결합되고, 상기 출력은 상기 제 1 및 제 2 트랜지스터 게이트들에 결합되는, 상기 증폭기를 포함하는, 상기 등화 수단과;

입력과 출력을 갖는 전류 제어 발진기로서, 상기 입력은 상기 감지 트랜지스터 드레인 전류를 포함하고, 상기 출력은 상기 출력 전류에 비례하는 주파수를 갖는 주기적 신호를 포함하는, 상기 전류 제어 발진기를 포함하고,

상기 전류 제어 발진기는:

세트 및 리세트 입력들 및 출력을 갖는 S-R 플립-플롭으로서, 상기 출력은 상기 전류 제어 발진기 출력을 포함하는, 상기 S-R 플립-플롭과;

두개의 입력들과 출력을 갖는 세트 비교기로서, 하나의 상기 입력은 전압 기준에 결합되고, 상기 출력은 상기 S-R 플립-플롭 세트 입력에 결합되는, 상기 세트 비교기와;

두개의 입력들과 출력을 갖는 리세트 비교기로서, 하나의 상기 입력은 상기 전압 기준에 결합되고, 상기 출력은 상기 S-R 플립-플롭 리세트 입력에 결합되는, 상기 리세트 비교기와;

입력과 출력을 갖는 세트 전류-전압 변환기로서, 상기 입력은 상기 전류 제어 발진기 입력에 스위칭 가능하게 결합되고, 상기 출력은 상기 세트 비교기에 결합되는, 상기 세트 전류-전압 변환기와;

입력과 출력을 갖는 리세트 전류-전압 변환기로서, 상기 입력은 상기 전류 제어 발진기 입력에 스위칭 가능하게 결합되고, 상기 출력은 상기 리세트 비교기에 결합되는, 상기 리세트 전류-전압 변환기를 포함하는, 전류 감지 회로.

## 청구항 17.

제 16항에 있어서, 상기 출력 트랜지스터 및 상기 감지 트랜지스터는 NMOS 트랜지스터들을 포함하는, 전류 감지 회로.

### 청구항 18.

제 16항에 있어서, 상기 감지 인자값은 조정가능한, 전류 감지 회로.

### 청구항 19.

제 16항에 있어서, 상기 제 1 및 제 2 트랜지스터들은 PMOS 트랜지스터들을 포함하는, 전류 감지 회로.

### 청구항 20.

제 16항에 있어서, 상기 세트 및 리세트 전류-전압 변환기들은:

두개의 단자들을 갖는 커패시터와;

상기 전류 제어 발진기 입력과 제 1의 상기 커패시터 단자 사이에 결합되는 제 1 스위치와;

제 2의 상기 커패시터 단자와 접지에 결합되는 제 2 스위치를 포함하는, 전류 감지 회로.

### 청구항 21.

효과적이고 제조가능한 전류 감지 회로를 제조하는 방법에 있어서,

출력 트랜지스터, 조정가능한 감지 인자를 갖는 감지 회로, 및 전류 제어 발진기를 제공하는 단계와;

상기 출력 트랜지스터 및 상기 감지 회로에 결치는 전압들을 등화하는 단계와;

상기 감지 인자에 따라서, 상기 출력 트랜지스터를 통과하는 전류에 비례하는 상기 감지 회로를 통과하는 전류를 발생시키는 단계와;

상기 감지 회로를 통과하는 상기 전류를 상기 출력 트랜지스터를 통과하는 상기 전류에 비례하는 주파수로 변환하는 단계를 포함하는, 전류 감지 회로 제조 방법.

### 청구항 22.

제 21항에 있어서, 상기 출력 트랜지스터는 FET 장치인, 전류 감지 회로 제조 방법.

### 청구항 23.

제 22항에 있어서, 상기 출력 트랜지스터는 NMOS FET인, 전류 감지 회로 제조 방법.

### 청구항 24.

제 21항에 있어서, 상기 감지 회로는 상기 출력 트랜지스터와 같은 타입의 감지 트랜지스터를 포함하고, 상기 출력 트랜지스터의 소스와 같은 전압에 접속된 소스를 가지며, 상기 출력 트랜지스터의 게이트와 같은 제어 전압에 접속된 게이트를 갖는, 전류 감지 회로 제조 방법.

### 청구항 25.

제 24항에 있어서, 상기 감지 인자는 상기 출력 트랜지스터의 크기에 대한 상기 감지 트랜지스터들의 상대적인 크기의 비에 관한 것인, 전류 감지 회로 제조 방법.

### 청구항 26.

제 24항에 있어서, 상기 출력 트랜지스터와 상기 감지 트랜지스터에 대해 거의 동일한 동작 조건들을 확립하도록 상기 출력 트랜지스터와 상기 감지 트랜지스터의 드레인들을 결합시킴으로써, 상기 출력 트랜지스터와 상기 감지 회로에 걸치는 전압들이 등화되는, 전류 감지 회로 제조 방법.

### 청구항 27.

제 26항에 있어서, 상기 출력 트랜지스터와 상기 감지 트랜지스터의 드레인들의 결합은, 상기 감지 트랜지스터의 드레인에 결합되는 제 1 입력과, 상기 출력 트랜지스터의 드레인에 결합되는 제 2 입력과, 전류 미러의 게이트들에 결합된 출력을 갖는 차동 증폭기를 포함하는 회로에 의해 수행되고,

상기 전류 미러의 제 1 트랜지스터의 드레인은 상기 출력 트랜지스터의 드레인에 접속되고, 상기 전류 미러의 제 2 트랜지스터의 드레인은 상기 전류 제어 발진기의 입력에 접속되고, 상기 전류 미러의 상기 제 1 및 제 2 트랜지스터의 소스들은 상기 감지 트랜지스터의 드레인에 접속되는, 전류 감지 회로 제조 방법.

### 청구항 28.

제 21항에 있어서, 상기 전류 구동 발진기는 캘리브레이션(calibration)을 위해 하나의 전압만을 필요로 하는, 전류 감지 회로 제조 방법.

### 청구항 29.

제 21항에 있어서, 상기 감지 인자는 가변적(variable)인, 전류 감지 회로 제조 방법.

### 청구항 30.

제 29항에 있어서, 상기 감지 인자는 상기 감지 트랜지스터를 복수의 병렬 감지 트랜지스터들로 나눔으로써 변하고, 스위치들의 구성이 상기 감지 트랜지스터들 중 임의의 감지 트랜지스터 또는 이들의 조합을 선택하는, 전류 감지 회로 제조 방법.

### 청구항 31.

제 21항에 있어서, 상기 전류 감지 회로는 파워 스위칭 회로를 용으로 사용되는, 전류 감지 회로 제조 방법.

도면

도면1

도면2

도면3