(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2011-24004

(P2011-24004A)

(43) 公開日 平成23年2月3日(2011.2.3)

(51) Int.Cl.

|      |       |           |

|------|-------|-----------|

| H04N | 1/036 | (2006.01) |

| B41J | 2/44  | (2006.01) |

| B41J | 2/45  | (2006.01) |

| B41J | 2/455 | (2006.01) |

F 1

|      |       |

|------|-------|

| H04N | 1/036 |

| B41J | 3/21  |

A

テーマコード (参考)

2 C 1 6 2

5 C 0 5 1

審査請求 未請求 請求項の数 10 O L (全 37 頁)

(21) 出願番号

特願2009-167723 (P2009-167723)

(22) 出願日

平成21年7月16日 (2009.7.16)

(71) 出願人 591044164

株式会社沖データ

東京都港区芝浦四丁目11番22号

(71) 出願人 500002571

株式会社沖デジタルイメージング

群馬県高崎市西横手町1番地1

(74) 代理人 100086807

弁理士 柿本 恒成

(74) 代理人 100091362

弁理士 阿仁屋 節雄

(74) 代理人 100145872

弁理士 福岡 昌浩

(72) 発明者 南雲 章

東京都八王子市東浅川町550番地の1

株式会社沖デジタルイメージング内

最終頁に続く

(54) 【発明の名称】光プリントヘッド及び画像形成装置

## (57) 【要約】

【課題】スタンバイ時の低消費電力化を図ると共に、不良品の検出を可能にする。

【解決手段】LEDヘッドは、複数のLEDアレイ200と、印刷駆動信号HD-STB-Nに基づきLEDアレイ200をオン／オフ駆動する複数のドライバIC100と、前記印刷駆動信号HD-STB-Nとは異なる論理状態に設定されたスタンバイ信号STBYに基づき、基準電圧VREFを生成する基準電圧発生回路70等とを備えている。ドライバIC100は、スタンバイ信号STBYを生成するモード変換指令手段と、前記スタンバイ信号STBY及び基準電圧VREFに基づき、LEDアレイ200に対する駆動量を指令する制御電圧を出力する制御電圧発生回路と、印刷駆動信号HD-STB-N及び前記制御電圧に基づき、前記LEDアレイ200をオン／オフ駆動するドライバと、前記スタンバイ信号STBYを基準電圧発生回路70へ出力するSTBY端子とを有している。

【選択図】図1

**【特許請求の範囲】****【請求項 1】**

複数の発光素子と、

駆動オン／オフ指令信号に基づき前記発光素子をオン／オフ駆動する駆動回路と、

前記駆動オン／オフ指令信号とは異なる論理状態に任意に設定されたモード変換指令信号に基づき、基準信号を生成する付帯回路と、

を備えた光プリントヘッドであって、

前記駆動回路は、

前記モード変換指令信号を生成するモード変換指令手段と、

前記モード変換指令手段により生成された前記モード変換指令信号、及び前記付帯回路

により生成された前記基準信号に基づき、前記発光素子に対する駆動量を指令する駆動量

指令信号を出力する駆動量指令手段と、

前記駆動オン／オフ指令信号、及び前記駆動量指令信号に基づき、前記発光素子をオン

／オフ駆動する駆動手段と、

前記モード変換指令手段により生成された前記モード変換指令信号を前記付帯回路へ出

力する出力端子と、

を有することを特徴とする光プリントヘッド。

**【請求項 2】**

前記モード変換指令信号は、前記駆動回路の静的消費電流を略ゼロとするスタンバイ信

号であり、

前記付帯回路は、

前記スタンバイ信号を入力して前記付帯回路の静的消費電流を切り替え可能とする切り

替え回路を有することを特徴とする請求項 1 記載の光プリントヘッド。

**【請求項 3】**

前記付帯回路は、

前記基準信号として基準電圧を生成して前記駆動量指令手段へ与える基準電圧発生回路

であることを特徴とする請求項 1 又は 2 記載の光プリントヘッド。

**【請求項 4】**

複数の発光素子と、

第 1 の電源電圧の印加により動作し、駆動オン／オフ指令信号に基づき前記発光素子を

オン／オフ駆動する駆動回路と、

前記第 1 の電源電圧とは異なる第 2 の電源電圧が印加されると動作し、前記第 2 の電源

電圧に基づいて基準信号を生成する基準信号生成手段と、

前記第 2 の電源電圧が印加されると動作し、前記駆動オン／オフ指令信号に基づき前記

駆動回路に対する付帶的な処理を行う付帯回路と、

を備えた光プリントヘッドであって、

前記駆動回路は、

前記駆動オン／オフ指令信号とは異なる論理状態に任意に設定されたモード変換指令信号

を生成するモード変換指令手段と、

前記モード変換指令手段により生成された前記モード変換指令信号、及び前記基準信号

生成手段により生成された前記基準信号に基づき、前記発光素子に対する駆動量を指令す

る駆動量指令信号を出力する駆動量指令手段と、

前記駆動オン／オフ指令信号、及び前記駆動量指令信号に基づき、前記発光素子をオン

／オフ駆動する駆動手段と、

を有することを特徴とする光プリントヘッド。

**【請求項 5】**

前記付帯回路の第 1 の信号入力端子と前記駆動回路の第 2 の信号入力端子とが接続され

て、コネクタ端子ピンが共有化されていることを特徴とする請求項 4 記載の光プリントヘ

ッド。

**【請求項 6】**

10

20

30

40

50

前記付帯回路は、

前記第1の信号入力端子、前記第2の電源電圧が印加される電源端子、及びグランド端子と、

前記第1の信号入力端子と前記グラン端子との間に接続された静電気保護素子を有する入力回路と、

を備えたことを特徴とする請求項5記載の光プリントヘッド。

#### 【請求項7】

前記付帯回路は、不揮発性メモリであることを特徴とする請求項6記載の光プリントヘッド。

#### 【請求項8】

前記モード変換指令信号は、前記駆動回路の静的消費電流を略ゼロとするスタンバイ信号であることを特徴とする請求項4～7のいずれか1項に記載の光プリントヘッド。

#### 【請求項9】

前記駆動量指令手段は、

前記駆動量指令信号として制御電圧を生成して出力する制御電圧発生回路であることを特徴とする請求項1～8のいずれか1項に記載の光プリントヘッド。

#### 【請求項10】

請求項1～9のいずれか1項に記載の光プリントヘッドを備えたことを特徴とする画像形成装置。

#### 【発明の詳細な説明】

#### 【技術分野】

#### 【0001】

本発明は、被駆動素子の群、例えば、光源に発光素子（発光ダイオード（以下「LED」という。）、発光サイリスタ等）を用いた電子写真プリンタにおけるLEDの列等を選択的に且つサイクリックに駆動する光プリントヘッドと、これを用いた画像形成装置に関するものである。

#### 【背景技術】

#### 【0002】

従来、例えば、下記の特許文献1等に記載されているように、電子写真プリンタ等の画像形成装置には、発光素子を多数配列させて露光部を形成したものがある。発光素子としては、LED他、有機エレクトロルミネセンス（以下「有機EL」という。）、発光サイリスタ等が用いられる。

#### 【0003】

LEDを用いたものでは、駆動回路とLEDとが1対1、もしくは1対N（N>1）に対応するように設けられ、LEDのアノード端子（以下単に「アノード」という。）・カソード端子（以下単に「アノード」という。）間に電流を流すか否かにより、発光／非発光の状態を切り替えている。発光状態におけるLEDの光出力は、駆動電流値により決まるものであり、この駆動電流値を調整することで、露光部への露光エネルギー量を調整している。

#### 【0004】

前記駆動回路として、MOSトランジスタを飽和領域で動作させることで定電流特性を持たせ、LEDの定電流駆動を行うと共に、LEDの駆動電流値をドット毎に調整可能とすることで、LEDの光量ばらつきを補正する構成が知られている。

#### 【0005】

前記MOSトランジスタを飽和領域で動作させるため、ゲート端子（以下単に「ゲート」という。）及びソース端子（以下単に「ソース」という。）間に所定の電圧を印加させ、この制御電圧値を演算増幅器（以下「オペアンプ」という。）を含む制御回路により発生させることができる。そのため、制御回路に対する駆動電流値を指令するための基準電圧を与えることを目的として、画像形成装置には基準電圧発生回路を備えている。

#### 【0006】

10

20

30

40

50

更に、基準電圧発生回路からの出力電圧に正の温度係数を与えることで、LEDの温度補償を行う構成も知られている。しかし、この構成では、基準電圧発生回路が駆動回路チップとは別の素子として構成されているので、定常的に静的消費電流が生じる。

#### 【0007】

又、発光素子アレイと、これを駆動するためのモノリシック集積回路（以下「IC」という。）で構成されたドライバIC等とが搭載されたLEDヘッド等の光プリントヘッド内には、前記LED光量補正のための補正データを格納するために、EEPROM（Electrically Erasable and Programmable Read Only Memory）等の不揮発性メモリを備えることが通例である。しかし、この不揮発性メモリにおいても、電気的な状態により静的な消費電流を生る。

10

#### 【先行技術文献】

#### 【特許文献】

#### 【0008】

#### 【特許文献1】特開2000-108407号公報

#### 【発明の概要】

#### 【発明が解決しようとする課題】

#### 【0009】

しかしながら、従来の光プリントヘッド及びこれを用いた画像形成装置では、次のような課題があった。

#### 【0010】

高密度に配列された発光素子アレイと接続するために、ドライバICは、いわゆるペアチップの状態でプリント配線板に実装されているため、実装時の故障が起きやすい。

20

#### 【課題を解決するための手段】

#### 【0011】

本発明のうちの第1の発明の光プリントヘッドは、複数の発光素子と、駆動オン／オフ指令信号に基づき前記発光素子をオン／オフ駆動する駆動回路と、前記駆動オン／オフ指令信号とは異なる論理状態に任意に設定されたモード変換指令信号に基づき、基準信号を生成する付帯回路とを備えている。

#### 【0012】

ここで、前記駆動回路は、前記モード変換指令信号を生成するモード変換指令手段と、前記モード変換指令手段により生成された前記モード変換指令信号、及び前記付帯回路により生成された前記基準信号に基づき、前記発光素子に対する駆動量を指令する駆動量指令信号を出力する駆動量指令手段と、前記駆動オン／オフ指令信号、及び前記駆動量指令信号に基づき、前記発光素子をオン／オフ駆動する駆動手段と、前記モード変換指令手段により生成された前記モード変換指令信号を前記付帯回路へ出力する出力端子とを有している。

30

#### 【0013】

本発明のうちの第2の発明の光プリントヘッドは、複数の発光素子と、第1の電源電圧の印加により動作し、駆動オン／オフ指令信号に基づき前記発光素子をオン／オフ駆動する駆動回路と、前記第1の電源電圧とは異なる第2の電源電圧が印加されると動作し、前記第2の電源電圧に基づいて基準信号を生成する基準信号生成手段と、前記第2の電源電圧が印加されると動作し、前記駆動オン／オフ指令信号に基づき前記駆動回路に対する付帯的な処理を行う付帯回路とを備えている。

40

#### 【0014】

ここで、前記駆動回路は、前記駆動オン／オフ指令信号とは異なる論理状態に任意に設定されたモード変換指令信号を生成するモード変換指令手段と、前記モード変換指令手段により生成された前記モード変換指令信号、及び前記基準信号生成手段により生成された前記基準信号に基づき、前記発光素子に対する駆動量を指令する駆動量指令信号を出力する駆動量指令手段と、前記駆動オン／オフ指令信号、及び前記駆動量指令信号に基づき、前記発光素子をオン／オフ駆動する駆動手段とを有している。

50

## 【0015】

第3の発明の画像形成装置は、前記第1又は第2の発明の光プリントヘッドを備えている。

## 【発明の効果】

## 【0016】

第1の発明の光プリントヘッドによれば、駆動回路内で生成したモード変換指令信号等に基づき、駆動量指令手段から駆動量指令信号を出力し、更に、駆動回路内で生成したモード変換指令信号を出力端子から外部へ出力する構成にしたので、駆動回路、及び付帯回路の静的消費電流を遮断することが可能となる。そのため、光プリントヘッドの実装組立て時に、駆動回路に損傷を与えたとしても、損傷された駆動回路を内在した光プリントヘッドを不良として検出することができ、光プリントヘッドの品質レベルを向上させることができ可能になる。

10

## 【0017】

第2の発明の光プリントヘッドによれば、第2の電源電圧の印加／遮断により付帯回路の動作／停止を切り替える構成にし、更に、駆動回路内で生成したモード変換指令信号等に基づき、駆動量指令手段から駆動量指令信号を出力する構成にしたので、第1の発明と同様に、駆動回路、及び付帯回路の静的消費電流を遮断することが可能となる。そのため、光プリントヘッドの実装組立て時に、駆動回路に損傷を与えたとしても、損傷された駆動回路を内在した光プリントヘッドを不良として検出することができ、光プリントヘッドの品質レベルを向上させることができ可能になる。

20

## 【0018】

第3の発明の画像形成装置によれば、前記発明の光プリントヘッドを備えているので、待機時消費電力を略ゼロとすることができます、大幅な省エネルギーが実現できる。

## 【図面の簡単な説明】

## 【0019】

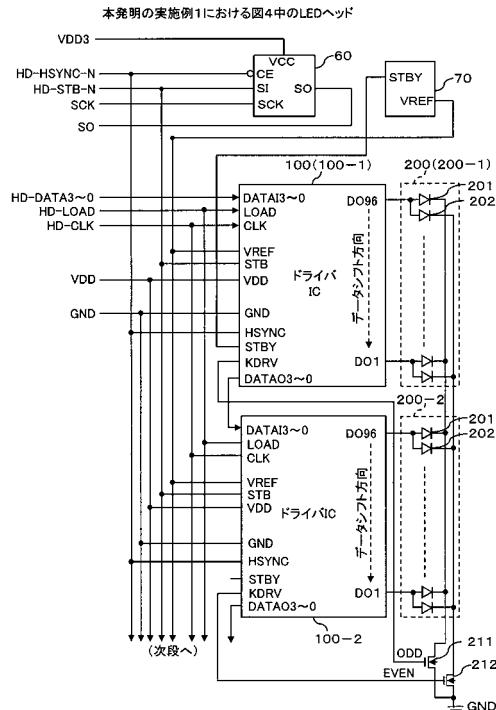

【図1】図1は本発明の実施例1における図4中のLEDヘッド13を示す構成図である。

30

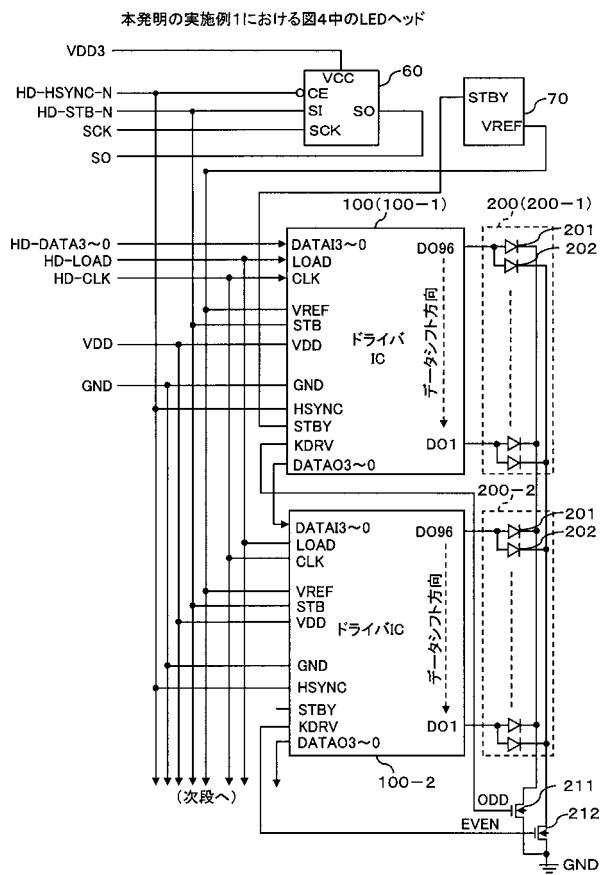

【図2】図2は本発明の実施例1における画像形成装置を示す概略の構成図である。

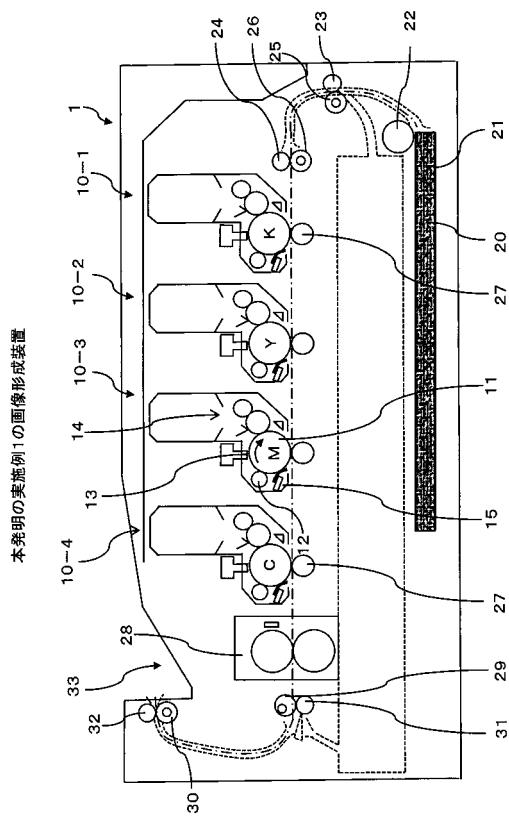

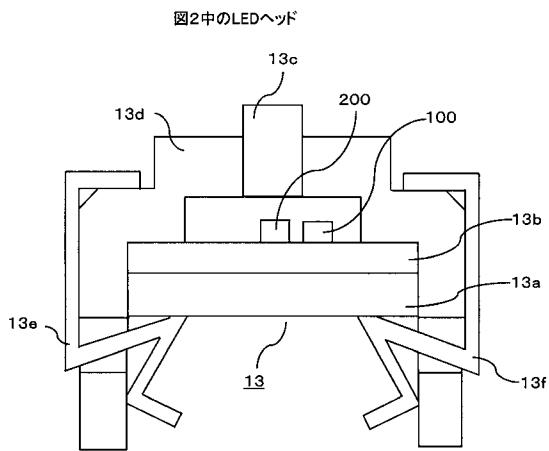

【図3】図3は図2中のLEDヘッド13の構成を示す概略の断面図である。

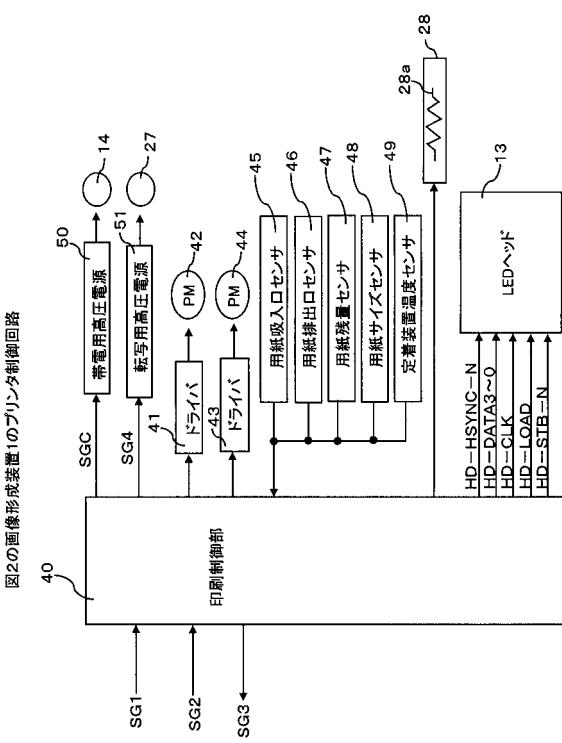

【図4】図4は図2の画像形成装置1におけるプリンタ制御回路の構成を示すブロック図である。

40

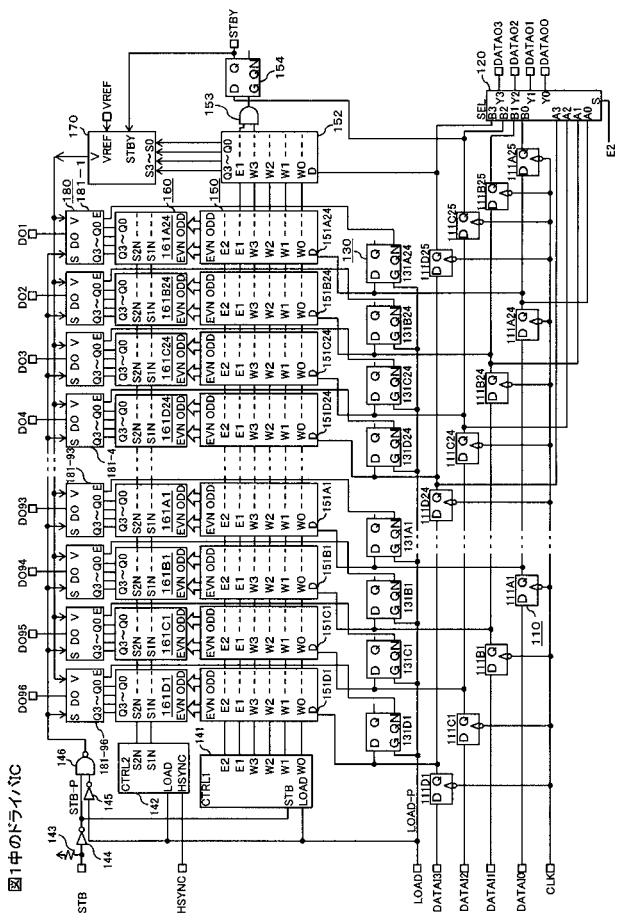

【図5】図5は図1中のドライバIC100の詳細な構成を示すブロック図である。

【図6】図6は図5中のメモリ回路151の構成を示す回路図である。

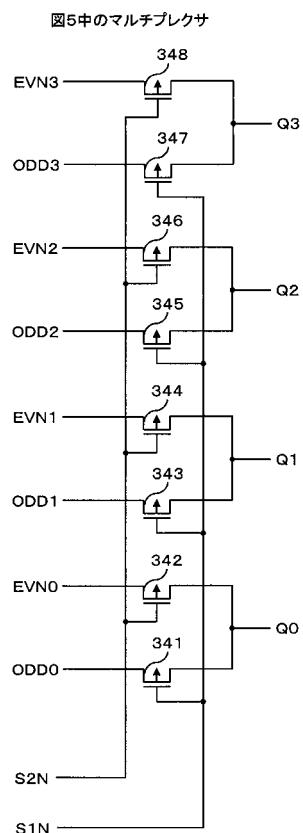

【図7】図7は図5中のマルチプレクサ161の構成を示す回路図である。

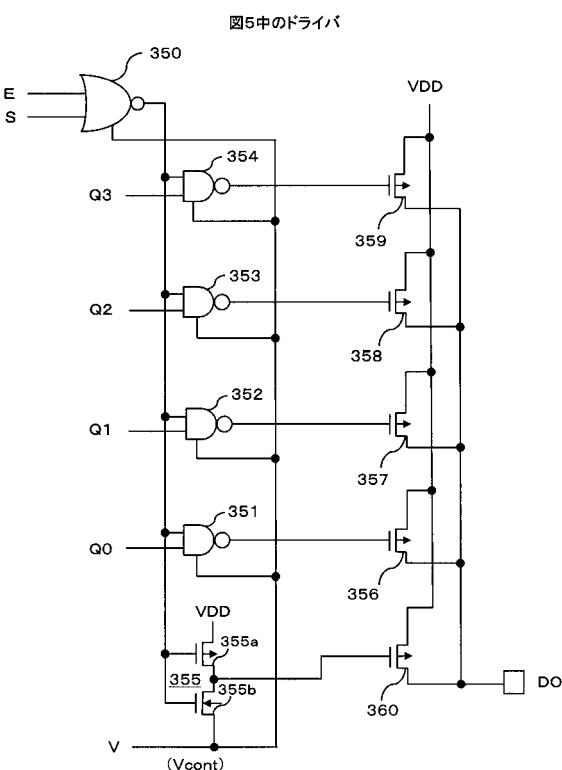

【図8】図8は図5中のドライバ181の構成を示す回路図である。

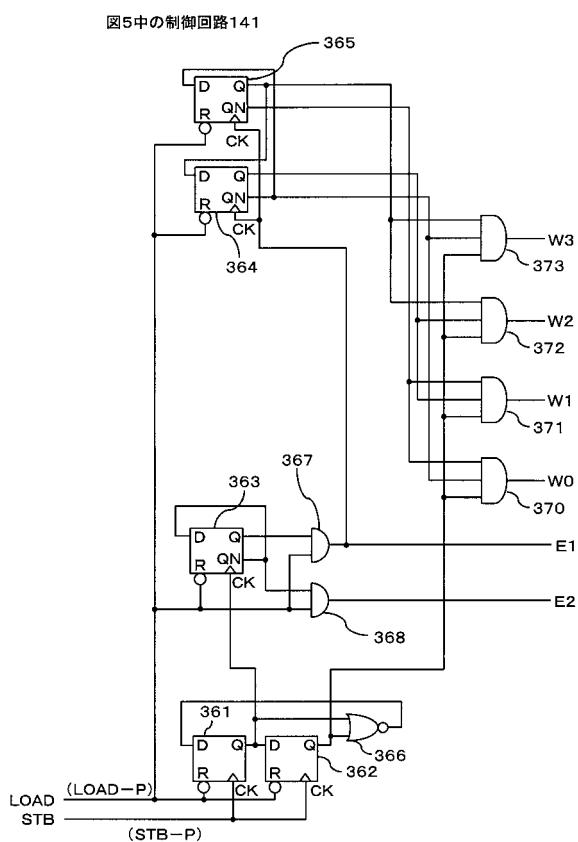

【図9】図9は図5中の制御回路141の構成を示す回路図である。

【図10】図10は図5中の制御回路142の構成を示す回路図である。

【図11】図11は図5中の制御電圧発生回路170の構成を示す回路図である。

【図12】図12は図1中の基準電圧発生回路70の構成を示す回路図である。

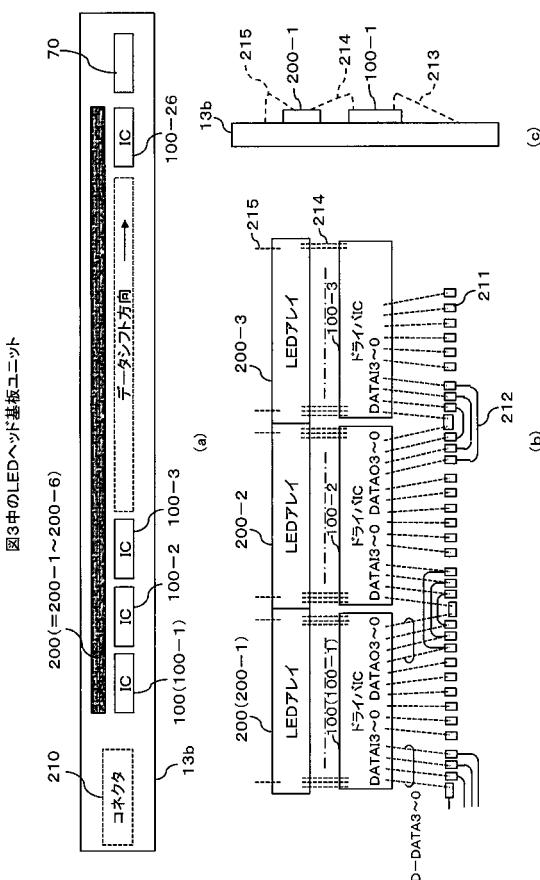

【図13】図13は図3中のLEDヘッド基板ユニットを示す構成図である。

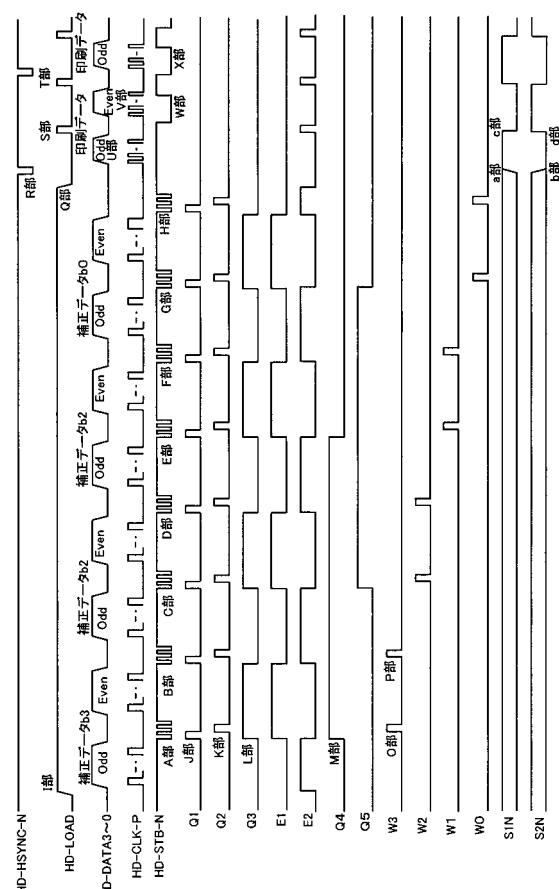

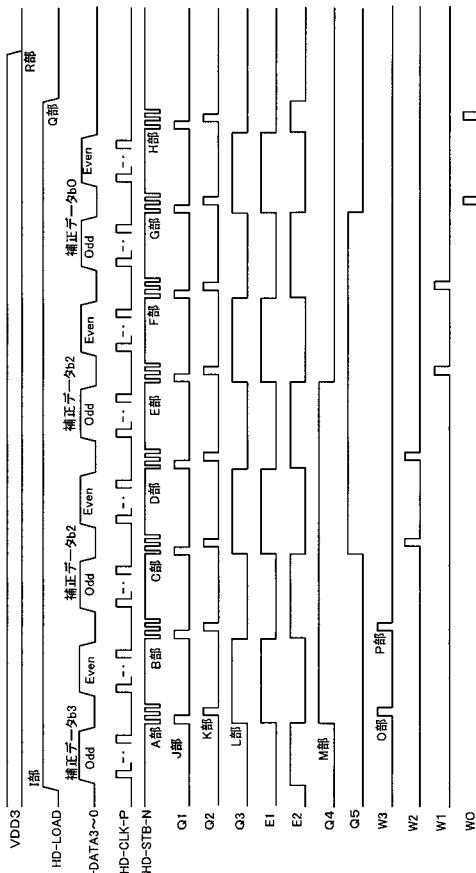

【図14】図14は本発明の実施例1のLEDヘッド13に対して行われる補正データ転送処理と、その後に行われる印刷データ転送の様子を示すタイムチャートである。

50

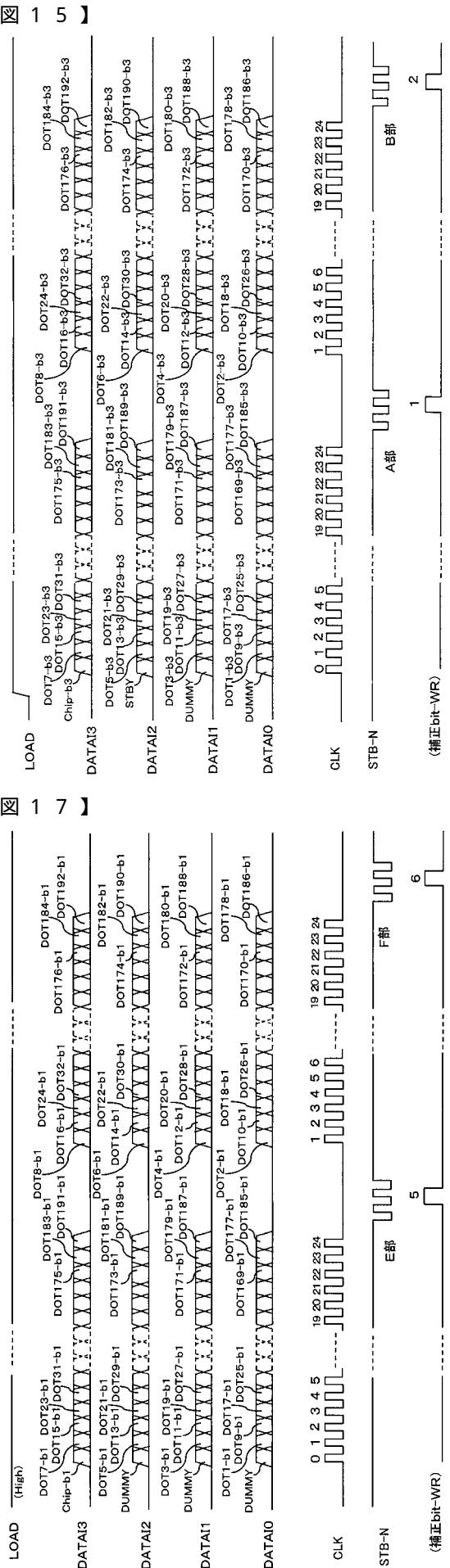

【図15】図15は図14のA部とB部の詳細を示すタイムチャートである。

【図16】図16は図14のC部とD部の詳細を示すタイムチャートである。

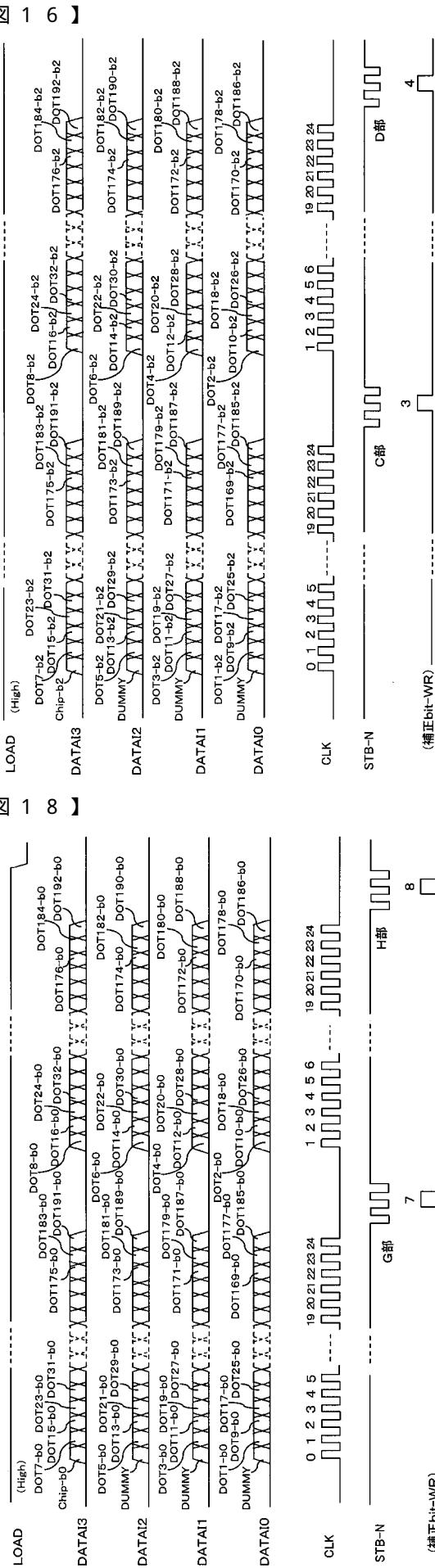

【図17】図17は図14のE部とF部の詳細を示すタイムチャートである。

【図18】図18は図14のG部とH部の詳細を示すタイムチャートである。

【図19】図19は図12の基準電圧発生回路70の変形例を示す回路図である。

【図20】図20は本発明の実施例2におけるLEDヘッド13Bを示す構成図である。

【図21】図21は図20中のEEPROM60Bの構成を従来構成と対して示す回路図である。

50

【図22】図22は図20中の基準電圧発生回路70Bの構成を示す回路図である。

【図23】図23は本発明の実施例2のLEDヘッド13Bに対して行われる補正データ転送処理とスタンバイ状態の設定シーケンスを示すタイムチャートである。

【発明を実施するための形態】

【0020】

本発明を実施するための形態は、以下の好ましい実施例の説明を添付図面と照らし合わせて読むと、明らかになるであろう。但し、図面はもっぱら解説のためのものであって、本発明の範囲を限定するものではない。

【実施例1】

【0021】

(実施例1の画像形成装置)

図2は、本発明の実施例1における画像形成装置を示す概略の構成図である。

【0022】

この画像形成装置1は、被駆動素子である発光素子（例えば、LED）を用いた光プリントヘッド（例えば、LEDヘッド）が搭載された電子写真カラープリンタであり、ブラック（K）、イエロー（Y）、マゼンタ（M）及びシアン（C）の各色の画像を各自に形成する4個のプロセスユニット10-1～10-4を有し、これらが記録媒体（例えば、用紙）20の搬送経路の上流側から順に配置されている。各プロセスユニット10-1～10-4の内部構成は共通しているため、例えば、マゼンタのプロセスユニット10-3を例にとり、これらの内部構成を説明する。

【0023】

プロセスユニット10-3には、像担持体としての感光体ドラム11が図2中の矢印方向に回転可能に配置されている。感光体ドラム11の周囲には、この回転方向上流側から順に、感光体ドラム11の表面に電荷を供給して帯電させる帯電装置12と、帯電された感光体ドラム11の表面に選択的に光を照射して静電潜像を形成する露光装置（例えば、光プリントヘッドであるLEDヘッド）13が配設されている。更に、静電潜像が形成された感光体ドラム11の表面に、マゼンタ（所定色）のトナーを付着させて顕像を発生させる現像器14と、感光体ドラム11上のトナーの顕像を記録媒体20に転写した後に残留したトナーを除去するクリーニング装置15が配設されている。なお、これら各装置に用いられているドラム又はローラは、図示しない駆動源からギア等を経由して動力が伝達され回転する。

【0024】

画像形成装置1の下部には、用紙20を堆積した状態で収納する用紙カセット21が装着され、その上方に、用紙20を1枚ずつ分離させて搬送するためのホッピングローラ22が配設されている。用紙20の搬送方向におけるホッピングローラ22の下流側には、ピンチローラ23、24と共に用紙20を挟持することによってこの用紙20を搬送する搬送ローラ25と、用紙20の斜行を修正し、プロセスユニット10-1に搬送するレジストローラ26とが配設されている。これらのホッピングローラ22、搬送ローラ25及びレジストローラ26は、図示しない駆動源からギア等を経由して動力が伝達され回転する。

【0025】

プロセスユニット10-1～10-4の各感光体ドラム11に対向する位置には、それぞれ半導電性のゴム等によって形成された転写器27が配設されている。各転写器27には、感光体ドラム11上に付着されたトナーによる顕像を用紙20に転写する転写時に、各感光体ドラム11の表面電位とこれら各転写器27の表面電位に電位差を持たせるための電位が印加されている。

【0026】

プロセスユニット10-4の下流には、定着器28が配設されている。定着器28は、ヒータが内蔵された加熱ローラとバックアップローラとを有し、用紙20上に転写されたトナーを加圧・加熱することによって定着する装置であり、この下流に、排出ローラ29

10

20

30

40

50

, 30、排出部のピンチローラ31, 32、及び用紙スタッカ部33が設けられている。排出口ーラ29, 30は、定着器28から排出された用紙20を、排出部のピンチローラ31, 32と共に挟持し、用紙スタッカ部33に搬送する。これら定着器28及び排出口ーラ29等は、図示しない駆動源からギア等を経由して動力が伝達されて回転する。

## 【0027】

このように構成される画像記録装置1は、次のように動作する。

先ず、用紙カセット21に堆積した状態で収納されている用紙20が、ホッピングローラ22によって、上から1枚ずつ分離されて搬送される。続いて、この用紙20は、搬送ローラ25、レジストローラ26及びピンチローラ23, 24に挟持されて、プロセスユニット10-1の感光体ドラム11と転写器27の間に搬送される。その後、用紙20は、感光体ドラム61及び転写器27に挟持され、その記録面にトナー像が転写されると同時に感光体ドラム10-1の回転によって搬送される。同様にして、用紙20は、順次プロセスユニット10-2~10-4を通過し、その通過過程で、各LEDヘッド13により形成された静電潜像を各現像器14によって現像した各色のトナー像が、その記録面に順次転写されて重ね合わされる。

10

## 【0028】

このようにして記録面上に各色のトナー像が重ね合わされた後、定着器28によってトナー像が定着された用紙20は、排出口ーラ29, 30及びピンチローラ31, 32に扶持されて、画像形成装置1の外部の用紙スタッカ部33に排出される。以上の過程を経て、カラー画像が用紙20上に形成される。

20

## 【0029】

(LEDヘッド)

図3は、図2中のLEDヘッドの構成を示す概略の断面図である。

## 【0030】

このLEDヘッド13は、ベース部材13aを有し、このベース部材13a上にプリント配線板13bが固定されている。プリント配線板13b上には、駆動回路等が集積された複数個のチップ状のドライバIC100と複数個のチップ状のLEDアレイ200とが熱硬化性樹脂等により固着され、それらの複数個のドライバIC100と複数個のLEDアレイ200とが、図示しないボンディングワイヤ等により相互に接続されている。複数個のLEDアレイ100上には、柱状の光学素子を多数配列してなるロッドレインズアレイ13cが配置され、このロッドレインズアレイ13cがホルダ13dにより固定されている。ベース部材13a、プリント配線板13b及びホルダ13dは、クランプ部材13e, 13fにより固定されている。

30

## 【0031】

(プリンタ制御回路)

図4は、図2の画像形成装置1におけるプリンタ制御回路の構成を示すブロック図である。

## 【0032】

このプリンタ制御回路は、画像形成装置1における印字部の内部に配設された印刷制御部40を有している。印刷制御部40は、マイクロプロセッサ、読み出し専用メモリ(ROM)、隨時読み書き可能なメモリ(RAM)、信号の入出力を行う入出力ポート、タイマ等によって構成され、図示しない画像処理部からの制御信号SG1、及びビデオ信号(ドットマップデータを一次元的に配列したもの)SG2等によって画像形成装置全体をシーケンス制御して印刷動作を行う機能を有している。印刷制御部40には、プロセスユニット10-1~10-4の4個のLEDヘッド13、定着器28のヒータ28a、ドライバ41, 43、用紙吸入口センサ45、用紙排出口センサ46、用紙残量センサ47、用紙サイズセンサ48、定着器用温度センサ49、帯電用高圧電源50、及び転写用高圧電源51等が接続されている。ドライバ41には現像・転写プロセス用モータ(PM)42が、ドライバ43には用紙送りモータ(PM)44G、帯電用高圧電源50には現像器14が、転写用高圧電源51には転写器27が、それぞれ接続されている。

40

50

## 【0033】

このような構成のプリンタ制御回路では、次のような動作を行う。

印刷制御部40は、画像処理部からの制御信号SG1によって印刷指示を受信すると、先ず、温度センサ49によって定着器28内のヒータ28aが使用可能な温度範囲にあるか否かを検出し、温度範囲になければヒータ28aに通電し、使用可能な温度まで定着器28を加熱する。次に、ドライバ41を介して現像・転写プロセス用モータ42を回転させ、同時にチャージ信号SGCによって帯電用高圧電源50をオンにし、現像器14の帯電を行う。

## 【0034】

そして、セットされている図2中の用紙20の有無及び種類が用紙残量センサ47、用紙サイズセンサ48によって検出され、その用紙20に合った用紙送りが開始される。ここで、用紙送りモータ44はドライバ43を介して双方向に回転させることが可能であり、最初に逆転させて、用紙吸入口センサ45が検知するまで、セットされた用紙20を予め設定された量だけ送る。続いて、正回転させて用紙20を画像形成装置内部の印刷機構内に搬送する。

10

## 【0035】

印刷制御部40は、用紙20が印刷可能な位置まで到達した時点において、図示しない画像処理部に対してタイミング信号SG3（主走査同期信号、副走査同期信号を含む）を送信し、ビデオ信号SG2を受信する。画像処理部においてページ毎に編集され、印刷制御部40に受信されたビデオ信号SG2は、印刷データ信号HD-DATA3～HD-DATA0として各LEDヘッド13に転送される。各LEDヘッド13は、それぞれ1ドット（ピクセル）の印字のために設けられたLEDを複数個線上に配列したものである。

20

## 【0036】

印刷制御部40は1ライン分のビデオ信号SG2を受信すると、各LEDヘッド13にラッチ信号HD-LOADを送信し、印刷データ信号HD-DATAを各LEDヘッド13内に保持させる。又、印刷制御部40は、画像処理部から次のビデオ信号SG2を受信している最中においても、各LEDヘッド13に保持した印刷データ信号HD-DATA3～HD-DATA0について印刷することができる。

## 【0037】

なお、印刷制御部40から各LEDヘッド13に送信されるクロック信号HD-CLK、主走査同期信号HD-HSYNC-N（但し、「-N」は負論理信号を意味する。）、及び駆動オン／オフ指令信号（例えば、印刷駆動信号）HD-STB-Nの内、クロック信号HD-CLKは、印刷データ信号HD-DATA3～HD-DATA0をLEDヘッド13へ送信するための信号である。

30

## 【0038】

ビデオ信号SG2の送受信は、印刷ライン毎に行われる。各LEDヘッド13によって印刷される情報は、マイナス電位に帯電された図示しない各感光体ドラム11上において電位の上昇したドットとして潜像化される。そして、現像器14において、マイナス電位に帯電された画像形成用のトナーが、電気的な吸引力によって各ドットに吸引され、トナー像が形成される。

40

## 【0039】

その後、トナー像は転写器27へ送られ、一方、転写信号SG4によってプラス電位に転写用高圧電源51がオン状態になり、転写器27は感光体ドラム11と転写器27との間隔を通過する用紙20上にトナー像を転写する。転写されたトナー像を有する用紙20は、ヒータ28aを内蔵する定着器28に当接して搬送され、この定着器28の熱によって用紙20に定着される。この定着された画像を有する用紙20は、更に搬送されて画像形成装置1の印刷機構から用紙排出口センサ46を通過して画像形成装置外部へ排出される。

## 【0040】

印刷制御部40は、用紙サイズセンサ48、及び用紙吸入口45の検知に対応して、用

50

紙20が転写器27を通過している間だけ転写用高圧電源51からの電圧を転写器27に印加する。印刷が終了し、用紙20が用紙排出口センサ46を通過すると、帶電用高圧電源50による現像器14への電圧の印加を終了し、同時に現像・転写プロセス用モータ42の回転を停止させる。以後、上記の動作を繰り返す。

#### 【0041】

(LEDヘッド)

図1は、本発明の実施例1における図4中のLEDヘッド13を示す構成図である。

#### 【0042】

このLEDヘッド13は、例えば、A4サイズの用紙に1インチ当たり600ドットの解像度で印刷可能な構成になっている。

10

#### 【0043】

LEDヘッド13は、コネクタ端子VDD3に接続された付帯回路である不揮発性メモリ(例えば、EEPROM)60と、付帯回路である基準電圧生成手段(例えば、基準電圧発生回路)70とを有し、これらのEEPROM60及び基準電圧発生回路70に、駆動回路である複数のドライバIC100(=100-1, 100-2, ...)が接続されている。更に、各ドライバIC100には、LEDアレイ200(=200-1, 200-2, ...)がそれぞれ接続されている。なお、EEPROM60の入力端子の一部は、ドライバIC100の入力端子の一部とも接続され、LEDヘッド13とコネクタ端子を共用している。

20

#### 【0044】

EEPROM60は、LEDヘッド13のコネクタ端子VDD3に接続された電源電圧VCC用のVCC端子、主走査同期信号HD-HSYNC-N端子への入力信号を負論理チップイネーブル信号CEとして入力するCE端子、ストローブ信号である印刷駆動信号HD-STB-N端子への信号をシリアルデータSIとして入力するSI端子、シリアルクロック信号SCKを入力するSCK端子、及びシリアルデータSOを出力するSO端子を有し、CE端子から入力される主走査同期信号HD-HSYNC-Nにより活性化され、シリアルクロック信号SCKに同期して印刷駆動信号HD-STB-NをシリアルデータSIとして入力して格納するための半導体メモリである。主走査同期信号HD-HSYNC-Nは、時分割駆動において奇数(ODD)番目のLED駆動であるか偶数(EVE)番目のLED駆動であるかの初期状態を設定するための信号である。

30

#### 【0045】

基準電圧発生回路70は、ドライバIC100-1から供給されるモード変換指令信号(例えば、スタンバイ信号)STBYを入力するSTBY端子と、LED駆動のための駆動電流値を指令するための基準信号(例えば、基準電圧)VREFを出力するVREF端子とを有し、STBY端子から入力されるスタンバイ信号STBYにより活性化され(即ち、内部の動作状態がオン/オフ動作され)、基準電圧VREFを発生してVREF端子から出力し、各ドライバIC100へ供給する回路である。

30

#### 【0046】

本実施例では、被駆動素子であるLED201, 201, ...の総数は4992ドットであり、これを構成するために26個のLEDアレイ200(=200-1, 200-2, ...)が配列されている。各LEDアレイ200は、各々192個のLED201, 202, ...を有し、各LEDアレイ200内の各LED200-1, 200-2, ...において、奇数番目のLED201, ...のカソード同士、偶数番目のLED202, ...のカソード同士が接続され、隣接して配置される2個のLED201, 202, ...のアノード端子同士が接続されており、奇数番目のLED201, ...と偶数番目のLED202, ...とは時分割に駆動される。

40

#### 【0047】

26個のLEDアレイ200(=200-1, 200-2, ...)に対応して、駆動回路である26個のドライバIC100(=100-1, 100-2, ...)が配列されている。これらの26個のドライバICは、同一の回路により構成され、隣接するドラ

50

イバIC100-1, 100-2, . . . がカスケード接続（継続接続）されている。

#### 【0048】

各ドライバIC100は、印刷データ信号HD-DATA3～HD-DATA0を入力するDATAI3～DATA0端子、ラッチ信号HD-LOADを入力するLOAD端子、クロック信号HD-CLKを入力するCLK端子、基準電圧発生回路70から供給される基準電圧VREFを入力するVREF端子、印刷駆動信号HD-STB-Nを入力するSTB端子、第1の電源電圧VDDを入力するVDD端子、グランドGNDに接続されるGND端子、主走査同期信号HD-HSYNC-Nを入力するHSYNC端子、スタンバイ信号STBYを基準電圧発生回路70へ出力する出力端子であるSTBY端子、制御信号KDRVを出力するKDRV端子、データDATAO3～DATAO0を次段のドライバIC100へ出力するDATAO3～DATAO0端子、及び各LEDアレイ200内のLED201, 202, . . . に対して駆動電流D01～D096を供給するD01端子～D096端子を有している。10

#### 【0049】

ここで、EEPROM60の第1の信号入力端子であるCE端子及びSI端子と、各ドライバIC100の第2の信号入力端子であるHSYNC端子及びSTB端子とが接続されて、コネクタ端子ピンが共有化されている。このように接続することにより、EEPROM60とドライバIC100とが独立に動作可能となると共に、コネクタ端子ピンの数を削減することができる。20

#### 【0050】

LEDアレイ200-1, 200-2, . . . の近傍には、奇数(ODD)側と偶数(EVEN)側の2個のパワーMOSトランジスタ（例えば、NチャネルMOSトランジスタ（以下「NMOS」という。）が設けられている。奇数(ODD)側のNMOS211のドレイン端子（以下単に「ドレイン」という。）は、奇数側のLED201, . . . のカソードと共に接続され、偶数(EVEN)側のNMOS212のドレインは、偶数側のLED202, . . . のカソードと共に接続されている。各NMOS211, 212のソースは、グランドGNDに接続されている。NMOS211のゲートは、ドライバIC100-1のKDRV端子から供給される制御信号KDRVによりゲート制御（即ち、オン／オフ制御）され、NMOS212のゲートは、ドライバIC100-2のKDRV端子から供給される制御信号KDRVによりゲート制御（即ち、オン／オフ制御）される構成になっている。30

#### 【0051】

このように構成される図1のLEDヘッド13における動作を説明する。

図1に示す構成においては、印刷データ信号HD-DATA3～HD-DATA0は4本であり、隣接するLED8個のうち、奇数番目同士あるいは偶数番目同士の4画素分のデータをクロック信号HD-CLK毎に同時に送出する構成になっている。このため、図4の印刷制御部40から出力される印刷データ信号HD-DATA3～HD-DATA0は、クロック端子CLKに入力されるクロック信号HD-CLKと共に、全ドライバIC100のDATAI3端子～DATAI0端子に入力される。ここで印刷データは、前述の総数が4992のLEDのうち、奇数側のLED201, . . . に対応する2496ドット分の印刷データが、印刷データ信号HD-DATA3～HD-DATA0として後述する各ドライバIC100内のフリップフロップ回路（以下「FF」という。）からなるシフトレジスタ中を順次転送される。40

#### 【0052】

次に、ラッチ信号HD-LOADが全ドライバIC100のLOAD端子に入力され、シフトレジスタ内に格納された前述の2496ドット分の印刷データが、各ドライバIC100内のシフトレジスタを構成する各FFに対応して設けられたラッチ回路にラッチされる。続いて、ラッチ回路にラッチされた印刷データ信号と、印刷駆動信号HD-STB-Nとによって、2496ドットの奇数側のLED201, . . . のうち、高レベル（以下「Hレベル」という。）であるD01, D02, . . . 端子に対応するものが点灯50

される。

【0053】

偶数側のLED202, . . . に対応する残り2496ドット分の印刷データについても、奇数側のLED201, . . . と同様にして順次、転送、ラッチおよび点灯される。

【0054】

ここで、前記各ドライバ1C100において、VDD端子に印加される電源電圧はVDDであり、典型的な例では5Vである。これに対し、前記EEPROM60のVCC端子に印加される電源電圧はVCCであり、典型的な例では3、3Vが用いられる。このようにする理由は、以下の(1)、(2)の通りである。

【0055】

(1) 各ドライバ1C100の電源電圧VDD

各LED201, 202, . . . の点灯時の順電圧が略1.6Vであり、この定電流駆動を行う各ドライバ1C100の駆動電源電圧VDDとして通常のロジックLSI(大規模集積回路)の多くで採用されている3.3Vでは電圧が不足してしまう。そのため、これより高い5Vが選ばれている。

【0056】

(2) EEPROM60の電源電圧VCC

不揮発性メモリ(例えば、EEPROM60)の電源電圧VCCは、典型例では3.3Vが選ばれており、LEDヘッド13を制御する図4の印刷制御部40内の制御回路の電源電圧も、通常のロジックLSIの多くで採用されている電源電圧と同様の3.3Vとされ、同じ電源系統に属するように構成されている。このようにするのは、下記の理由による。

【0057】

EEPROM60においては、この記憶保持されているデータの誤書き込みを防止するため、内部に自身の電源電圧が正常動作範囲内にあるか否かを判定するリセット回路を備えている。

【0058】

LEDヘッド搭載装置の電源投入や電源断時におけるこの素子の電源電圧の立ち上がり、立ち下がり時において、電源電圧が正常動作範囲外にある時は、これを制御している図示しない上位装置(例えば、画像処理部)が誤動作して誤った書き込み指令が入力されるおそれがある。このような場合でも、EEPROM60内に前記リセット回路を備えることで、書き込み動作は禁止されており、その記憶内容を保持することができる。又、EEPROM60の電源電圧VCCが正常動作範囲にある時、図4の印刷制御部40内の制御回路の電源電圧も同じ電源系統に属するように構成されているので、その電源電圧VCCも正常動作範囲にあり、誤った書き込み指令信号が発せられるおそれがない。

【0059】

このように、図1の構成とすることで、LEDヘッド搭載装置の電源投入や電源断時において、EEPROM60の記憶データが破壊されることを防止できるように工夫されている。

【0060】

(ドライバICの全体構成)

図5は、図1中のドライバIC100の詳細な構成を示すブロック図である。

【0061】

このドライバIC100は、カスケード接続された複数のFF111(=FF111A1~FF111A25, FF111B1~FF111B25, FF111C1~FF111C25, FF111D1~FF111D25)からなるシフトレジスタ110を有している。シフトレジスタ110は、クロック入力用端子CLKから入力されるクロック信号HD-CLKに同期して、データ入力用DATA3~DATA0端子から入力される印刷データ信号HD-DATA3~HD-DATA0を取り込んでシフトする回路である。

10

20

30

40

50

## 【0062】

ここで、FF111A1～FF111A25は、カスケード接続されており、ドライバIC100のデータ入力用DATAI0端子はFF111A1のデータ入力用D端子に接続され、FF111A24とFF111A25のデータ出力用Q端子はセレクタ120のデータ入力用端子A0,B0に接続され、セレクタ120のデータ出力用Y0端子がドライバIC100のデータ出力用DATAO0端子に接続されている。同様に、FF111B1～FF111B25、FF111C1～FF111C25、及びFF111D1～FF111D25も、それぞれカスケード接続されており、ドライバIC100のデータ入力用DATAI1端子、DATAI2端子、DATAI3端子が、FF111B1、FF111C1、及びFF111D1のデータ入力用D端子にそれぞれ接続されている。FF111B24とFF111B25、FF111C24とFF111C25、FF111D24とFF111D25のデータ出力用Q端子も、セレクタ120のデータ入力用A1端子、A2端子、A3端子、B1端子、B2端子、及びB3端子にそれぞれ接続され、セレクタ120のデータ出力用Y1端子、Y2端子、及びY3端子が、ドライバIC100のデータ出力用DATAO1端子、DATAO2端子、及びDATAO3端子にそれぞれ接続されている。10

## 【0063】

これにより、FF111A1～FF111A25、FF111B1～FF111B25、FF111C1～FF111C25、及びFF111D1～FF111D25は、それぞれ25段のシフトレジスタ110を構成しており、セレクタ120により、シフトレジスタ110のシフト段数を24段と25段とに切り替えることが可能な構成になっている。そのため、各ドライバIC100-1, … のデータ出力用DATAO0端子～DATAO3端子は、次段のドライバIC100-2, … のデータ入力用DATAI0端子～DATAI3端子にそれぞれ接続されることになる。従って、ドライバIC100-1～100-26の全てで構成されるシフトレジスタ110, … は、図4の印刷制御部40から初段のドライバIC100-1中のドライバ181-1に入力される印刷データ信号HD-DATA3を、クロック信号HD-CLKに同期してシフトさせる24×26段あるいは25×26段のシフトレジスタを構成している。20

## 【0064】

シフトレジスタ110の出力側には、ラッチ回路部130及びメモリ回路部150の入力側が接続されている。ラッチ回路部130の出力側にはドライバ部180が接続され、メモリ回路部150の入力側に制御回路141が接続され、そのメモリ回路部150の出力側にマルチプレクサ部160が接続されている。マルチプレクサ部160の入力側には、制御回路142が接続されている。ドライバIC100の駆動信号入力用STB端子には、プルアップ抵抗143及び論理反転用のインバータ144が接続され、更に、ドライバIC100のラッチ信号入力用LOAD端子に、論理反転用のインバータ145が接続されている。インバータ144, 145の出力端子には、2入力の否定論理積回路（以下「NAND回路」という。）146の入力端子が接続され、このNAND回路146の出力端子に、ドライバ部180の入力側が接続されている。ドライバ部180の入力側には、駆動量指令手段（例えば、制御電圧発生回路）170も接続されている。30

## 【0065】

ここで、ラッチ回路部130は、ラッチ信号入力用LOAD端子から入力されるラッチ信号LOAD-P（但し、「-P」は正論理信号を意味する。）により、シフトレジスタ110の出力信号をラッチする回路であり、複数のラッチ回路131（=131A1, 131B1, 131C1, 131D1～131A24, 131B24, 131C24, 131D24）により構成されている。各ラッチ回路131は、データ入力用D端子、ラッチ信号入力用G端子、及び反転データ出力用QN端子をそれぞれ有し、これらの出力側に、ドライバ部180が接続されている。40

## 【0066】

メモリ回路部150は、制御回路141によりアクセス制御され、LEDの光量ばらつ50

き補正のための補正データ（即ち、ドット補正データ）や各LEDアレイ200毎の光量補正データ（即ち、チップ補正データ）、もしくは各ドライバ1C100毎の固有データを格納するものである。このメモリ回路部150は、複数のメモリ回路151（=151A1, 151B1, 151C1, 151D1～151A24, 151B24, 151C24, 151D24）とメモリ回路152により構成されている。各メモリ回路151は、データ入力用D端子、信号入力用W0端子～W3、信号入力用E1端子、E2端子、データ出力用EVN端子、及びODD端子をそれぞれ有している。更に、メモリ回路152は、データ入力用D端子、信号入力用W0端子～W3、信号入力用E1端子、データ出力用Q0端子～Q3端子を有している。このメモリ回路部150の出力側には、マルチプレクサ部160及び制御電圧発生回路170が接続されている。

10

## 【0067】

メモリ回路部150を制御する制御回路141は、ラッチ信号入力用LOAD端子、駆動信号入力用STB端子、信号出力用W0端子～W3端子、E1端子、及びE2端子を有し、前記補正データを複数のメモリ回路151（=151A1, 151B1, 151C1, 151D1～151A24, 151B24, 151C24, 151D24）やメモリ回路152に対して書き込みする時の書き込み指令信号をW0端子～W3端子、E1端子及びE2端子から出力する回路である。

## 【0068】

更に、制御回路141の信号出力用W3端子及びE1端子には、モード変換指令信号であるスタンバイ信号を生成するモード変換指令手段（例えば、2入力の論理積回路（以下「AND回路」という。）153とこの出力端子に接続されたラッチ回路154）が接続されている。ラッチ回路154は、FF111C26の出力データを入力するD端子、AND回路153の出力信号を入力するG端子、及びスタンバイ信号STBYを出力するQ端子を有し、AND回路153の出力信号に基づき、FF111C26の出力データをラッピングしてスタンバイ信号STBYをQ端子から出力し、制御電圧発生回路170及びSTBY端子へ供給する回路である。

20

## 【0069】

マルチプレクサ部160は、制御回路142により制御され、メモリ回路部150中の複数のメモリ回路151（=151A1, 151B1, 151C1, 151D1～151A24, 151B24, 151C24, 151D24）から出力されるドット補正データにおいて、隣接したLEDドットのうち、奇数番目ドットの補正データと偶数番目ドットの補正データとを切り替えるものであり、複数のマルチプレクサ161（=161A1, 161B1, 161C1, 161D1～161A24, 161B24, 161C24, 161D24）により構成されている。各マルチプレクサ161は、データ入力用EVN端子、ODD端子、信号入力用S1N端子、S2N端子、及びデータ出力用Q0端子～Q3端子をそれぞれ有し、これらの出力側に、ドライバ部180が接続されている。

30

## 【0070】

マルチプレクサ部160を制御する制御回路142は、主走査同期信号入力用HSYN端子、ラッチ信号入力用LOAD端子、信号出力用S1N端子、及びS2N端子を有し、マルチプレクサ部160に対し奇数ドットデータと偶数ドットデータとの切り替え指令信号をS1N端子及びS2N端子から出力する回路である。

40

## 【0071】

ドライバ部180の入力側に接続された制御電圧発生回路170は、データ入力用S0～S3端子、基準電圧入力用VREF端子、スタンバイ信号入力用STBY端子、及び制御電圧出力用V端子を備え、例えば、図示しないレギュレータ回路から発生された基準電圧VREFを入力し、LED駆動のための駆動量指令信号（例えば、制御電圧）VをV端子から発生してドライバ部180へ供給する機能と、スタンバイ信号STBYを入力すると、内部の動作状態をオフする機能とを有している。この制御電圧発生回路170は、LEDの全点灯駆動時のように電源電圧VDDが一瞬降下するような状況においても、基準電圧VREFを所定値のままで、LED駆動電流の低下を発生させない構成になって

50

いる。

**【0072】**

ドライバ部180は、ラッチ回路部130、NAND回路146、マルチプレクサ部160、及び制御電圧発生回路170の出力信号に基づき、LEDアレイ200を駆動するための駆動電流を複数のD01端子～D096端子から出力する回路であり、駆動手段である複数のドライバ181(=181-1～181-96)により構成されている。各ドライバ181は、データ入力用Q0端子～Q3端子、E端子、信号入力用S端子、及び制御電圧入力用V端子をそれぞれ有している。

**【0073】**

このドライバ部180の各信号入力用S端子に接続されたNAND回路146には、STB端子に入力される印刷駆動信号HD-STB-Nと、LOAD端子に入力されるラッチ信号LOAD-Pとが、インバータ144, 145を介して入力され、ドライバ部180に対する駆動のオン／オフを制御する信号を生成する機能を有している。

**【0074】**

(図6中のメモリ回路)

図6は、図5中のメモリ回路151の構成を示す回路図である。

**【0075】**

図6のメモリ回路151(例えば、151A1)では、LED光量補正のためのドット補正データは4ビットであり、LED駆動電流をドット毎に16段階に調整することで光量補正を行うものとしている。

**【0076】**

このメモリ回路151A1には、隣接する2個(2ドット)のメモリセル回路300-1, 300-2が示されている。左側のメモリセル回路300-1は、奇数番目のドット(例えば、ドットNo.1)の補正データを格納するものであり、右側のメモリセル回路300-2は、偶数番目のドット(例えば、ドットNo.2)の補正データを格納するためのものである。

**【0077】**

メモリ回路151A1は、シフトレジスタ110中のFFF111A1のデータ出力用Q端子から出力される補正データを入力するD端子と、制御手段である制御回路141の端子E1から出力される奇数番目ドットの側のデータ書き込みを許可する書き込みイネーブル信号を入力するE1端子と、制御回路141のE2端子から出力される偶数番目ドットの側のデータ書き込みを許可する書き込みイネーブル信号を入力するE2端子と、制御回路141のW0端子～W3端子から出力される書き込み制御信号を入力するW0端子～W3端子と、奇数番目ドットに関する補正データを出力するODD0端子～ODD3端子と、偶数番目ドットに関する補正データを出力するEVN0端子～EVN3端子とを有している。

**【0078】**

補正データ入力用D端子には、入力された補正データを駆動するバッファ301が接続され、このバッファ301に、前記補正データの論理を反転して反転補正データを生成するインバータ302が接続されている。バッファ301の出力端子及びインバータ302の出力端子には、メモリセル回路300-1, 300-2が接続されている。

**【0079】**

メモリセル回路300-1は、メモリ手段(例えば、メモリセル)311～314と、バッファ301の出力データをメモリセル311～314へ伝送するスイッチ手段(例えば、NMOS)321～328と、インバータ302の出力データをメモリセル311～314へ伝送するスイッチ手段(例えば、NMOS)331～338とを有している。

**【0080】**

メモリセル311は、リング状に直列接続された第1及び第2のインバータ311a, 311bにより構成されている。同様に、メモリセル312は、リング状に直列接続されたインバータ312a, 312bにより、メモリセル313は、リング状に直列接続され

10

20

30

40

50

たインバータ 313a, 313b により、メモリセル 314 は、リング状に直列接続されたインバータ 314a, 314b により、それぞれ構成されている。各インバータ 311a, 311b, 312a, 312b, 313a, 313b, 314a, 314b の電源端子は、電源電圧 VDD (例えば、一定の略 5V) が印加される VDD 端子に接続されている。

#### 【0081】

NMOS 321, 323, 325, 327 のゲートは、書き込みイネーブル信号入力用端子 E1 に共通に接続され、NMOS 322, 324, 326, 328 のゲートは、書き込み制御信号入力用 W0 端子、W1 端子、W2 端子及び W3 端子にそれぞれ接続されている。バッファ 301 の出力端子には、NMOS 321, 322、補正データ端子 ODD0 及びメモリセル 311 の直列回路と、NMOS 323, 324、補正データ端子 ODD1 及びメモリセル 312 の直列回路と、NMOS 325, 326、補正データ端子 ODD2 及びメモリセル 313 の直列回路と、NMOS 327, 328、補正データ端子 ODD3 及びメモリセル 314 の直列回路とが、共通に接続されている。10

#### 【0082】

NMOS 331, 333, 335, 337 のゲートは、書き込み制御信号入力用 W0 端子、W1 端子、W2 端子及び W3 端子にそれぞれ接続され、NMOS 332, 334, 336, 338 のゲートは、書き込みイネーブル信号入力用端子 E1 に共通に接続されている。インバータ 302 の出力端子には、NMOS 332, 331 及びメモリセル 311 の直列回路と、NMOS 334, 333 及びメモリセル 312 の直列回路と、NMOS 336, 335 及びメモリセル 313 の直列回路と、NMOS 338, 337 及びメモリセル 314 の直列回路とが、共通に接続されている。20

#### 【0083】

メモリセル回路 300-2 は、メモリセル回路 300-1 の書き込みイネーブル信号入力用端子 E1 に代えて、書き込みイネーブル信号入力用端子 E2 に接続され、更に、メモリセル回路 300-1 の補正データ出力用 ODD0 端子～ODD3 端子に代えて、補正データ出力用 EVN0 端子～EVN3 端子に接続されている他は、メモリセル回路 300-1 と同様の構成である。

#### 【0084】

(図 6 中のマルチプレクサ)

30

図 7 は、図 5 中のマルチプレクサ 161 の構成を示す回路図である。

#### 【0085】

図 7 のマルチプレクサ 161 (例えば、161A1) は、メモリ回路 151A1 の ODD0 端子～ODD3 端子から出力される補正データ ODD0～ODD3 を入力する ODD0 端子～ODD3 端子と、メモリ回路 151A1 の EVN0 端子～EVN3 端子から出力される補正データ EVN0～EVN3 を入力する EVN0 端子～EVN3 端子と、制御回路 142 の S1N 端子及び S2N 端子から出力される奇数ドットデータと偶数ドットデータとの切り替え指令信号 S1N, S2N を入力する S1N 端子及び S2N 端子と、補正データ Q0～Q3 を出力する Q0 端子～Q3 端子と、入力データ切り替え用の P チャネル MOS トランジスタ (以下「PMOS」という。) 341～348 とを有している。40

#### 【0086】

PMOS 341, 343, 345, 347 は、S1N 端子から入力される切り替え指令信号 S1N によりゲート制御され、入力側の ODD0 端子～ODD3 端子と出力側の Q0 端子～Q3 端子との間をそれぞれオン／オフする構成になっている。更に、PMOS 342, 344, 346, 348 は、S2N 端子から入力される切り替え指定信号 S2N によりゲート制御され、入力側の EVN0 端子～EVN3 端子と出力側の Q0 端子～Q3 端子との間をそれぞれオン／オフする構成になっている。

#### 【0087】

(図 6 中のドライバ)

50

図 8 は、図 5 中のドライバ 181 の構成を示す回路図である。

## 【0088】

図8のドライバ181(例えば、181-93)は、ラッチ回路131A1の反転出力用端子QNから出力される負論理の印刷データ信号を入力する端子Eと、NAND回路146から出力される負論理のLED駆動オン／オフ指令信号を入力するS端子と、マルチブレクサ161A1の端子Q0～端子Q3から出力される補正データQ0～Q3を入力するQ0端子～Q3端子と、制御電圧発生回路170のV端子から出力される制御電圧V<sub>cont</sub>を入力するV端子と、電源電圧VDDが入力されるVDD端子と、図示しないボンディングワイヤを介して接続されたLEDのアノードに対して駆動電流DOを供給するDO端子(=DO93端子)とを有している。

## 【0089】

E端子及びS端子は、2入力の否定論理回路(以下「NOR回路」という。)350の入力端子に接続されている。NOR回路350は、電源端子がVDD端子に接続され、グランド端子がV端子に接続されて制御電圧V<sub>cont</sub>に保持されている。NOR回路350の出力端子とQ0端子～Q3端子とは、2入力NAND回路351～354の入力端子にそれぞれ接続されている。各NAND回路351～354は、電源端子がVDD端子に接続され、グランド端子がV端子に接続されて制御電圧V<sub>cont</sub>に保持されている。更に、NOR回路350の出力端子は、相補形MOSインバータ(以下「CMOSインバータ」という。)355を構成するPMOS355a及びNMOS355bの各ゲートに共通に接続されている。PMOS355a及びNMOS355bは、VDD端子とV端子との間に直列に接続されている。

10

20

## 【0090】

NAND回路351～354の出力端子には、PMOS356～359のゲートがそれぞれ接続され、更に、CMOSインバータ355の出力端子に、PMOS360のゲートが接続されている。各PMOS356～360のソース・ドレインは、VDD端子とDO端子との間に並列に接続されている。PMOS360は、LEDに主たる駆動電流DOを供給する主駆動トランジスタであり、PMOS356～359は、LEDの駆動電流DOをドット毎に調整して光量補正するための補助駆動トランジスタである。

30

## 【0091】

ここで、VDD端子の電位と、V端子から入力される制御電圧V<sub>cont</sub>の電位との電位差は、PMOS356～360がオンする時のゲート・ソース間電圧に略等しく、この電圧を変化させることで、PMOS356～360のドレン電流を調整することが可能となる。制御電圧V<sub>cont</sub>を供給するための図5中の制御電圧発生回路170は、基準電圧VREFを受けて、PMOS356～360等のドレン電流が所定値となるように制御電圧V<sub>cont</sub>を制御するために設けられている。

40

## 【0092】

このように構成されるドライバ181-93は、次のように動作する。

E端子に入力される印刷データ信号がオン(=低レベル、以下「“L”レベル」という。)であり、S端子に入力されるLED駆動オン／オフ指令信号がオン(=“L”レベル)の時、NOR回路350の出力信号が“H”レベルとなる。この時、Q3端子～Q0端子の補正データQ3～Q0に従い、NAND回路351～354の出力レベル、及びCMOSインバータ355の出力レベルが、電源電圧VDDあるいは制御電圧V<sub>cont</sub>となる。

50

## 【0093】

主駆動用のPMOS360は、E端子に入力される印刷データ信号に従って駆動される。図6のメモリ回路151A1には、LED各ドットの発光ばらつきを補正するための補正データQ0～Q3が格納されているので、この補正データQ0～Q3が、マルチブレクサ161A1のQ0端子～Q3端子から出力される。補助駆動用のPMOS356～359は、NOR回路350の出力レベルが“H”レベルである時に、マルチブレクサ161A1のQ0端子～Q3端子から出力される補正データQ0～Q3に従って選択的に駆動される。

50

## 【0094】

つまり、主駆動用のPMOS360と共に、補正データQ0～Q3に従って補助駆動用のPMOS356～359が選択的に駆動され、PMOS360のドレイン電流に対し、選択されたPMOS356～359の各ドレイン電流が加算された駆動電流DOが、DO93端子からLEDに供給される。

## 【0095】

PMOS356～359が駆動されている時、NAND回路351～354の出力レベルは“H”レベル（制御電圧Vcont）であるので、PMOS356～359のゲート電位は、略制御電圧Vcontに等しくなる。この時、PMOS355aはオフ状態にあり、NMOS355bはオン状態にあって、PMOS360のゲート電位もまた略制御電圧Vcontに等しくなる。そのため、PMOS356～360のドレイン電流値を、制御電圧Vcontにより一括して調整することができる。この際、NAND回路351～354は、電源端子に電源電圧VDD、及びグランド端子に制御電圧Vcontが印加されて動作しているので、その入力信号の電位も電源電圧VDDと制御電圧Vcontに即したものであってよく、“L”レベルは必ずしも0Vであることを必要としないという利点を有する。

10

## 【0096】

（図6中の制御回路141）

図9は、図5中の制御回路141の構成を示す回路図である。

20

## 【0097】

この制御回路141は、正論理のラッチ信号LOAD-Pを入力するLOAD端子と、図5中のインバータ144から出力される正論理の印刷駆動信号STB-Pを入力するSTB端子と、書き込み制御信号W0～W3を図5中のメモリ回路部150へ出力するW0端子～W3端子と、書き込みイネーブル信号E1, E2をメモリ回路部150へ出力するE1端子及びE2端子と、FF361～365と、2入力のNOR回路366と、2入力の論理積回路（以下「AND回路」という。）367, 368と、3入力のAND回路370～373とを備えている。

30

## 【0098】

各FF361, 362は、LOAD端子から入力されるラッチ信号LOAD-Pを入力する負論理リセット用R端子と、STB端子から入力される印刷駆動信号STB-Pを入力するクロック入力用CK端子と、データ入力用D端子と、非反転データ出力用Q端子とを有している。各FF363～365は、LOAD端子から入力されるラッチ信号LOAD-Pを入力する負論理リセット用R端子と、クロック入力用CK端子と、データ入力用D端子と、非反転データ出力用QN端子とを有している。

40

## 【0099】

FF361, 362のQ端子は、NOR回路366の入力端子と接続され、このNOR回路366の出力端子がFF361のD端子に接続されている。FF361のQ端子は、FF363のCK端子に接続され、このFF363のQN端子がD端子に接続されている。FF363のQ端子とLOAD端子とは、AND回路367の入力端子に接続され、このAND回路367の出力端子がE1端子に接続されている。FF363のQN端子とLOAD端子とは、AND回路368の入力端子に接続され、このAND回路368の出力端子がE2端子に接続されている。

## 【0100】

AND回路367の出力端子は、FF364, 365のCK端子に接続され、このFF364, 365のR端子が、LOAD端子に接続されている。FF364のQN端子は、FF365のD端子に接続されている。FF364, 365のQ端子及びQN端子とFF362のQ端子とには、AND回路370～373の入力端子が接続され、このAND回路370～373の出力端子が、W0端子～W3端子に接続されている。

## 【0101】

即ち、AND回路373の第1入力端子はFF365のQ端子、及び第2入力端子はF

50

F 3 6 4 の Q N 端子にそれぞれ接続され、A N D 回路 3 7 2 の第 1 入力端子は F F 3 6 5 の Q 端子、及び第 2 入力端子は F F 3 6 4 の Q 端子にそれぞれ接続され、A N D 回路 3 7 1 の第 1 入力端子は F F 3 6 5 の Q N 端子、及び第 2 入力端子は F F 3 6 4 の Q 端子にそれぞれ接続され、A N D 回路 3 7 0 の第 1 入力端子は F F 3 6 5 の Q N 端子、及び第 2 入力端子は F F 3 6 4 の Q N 端子にそれぞれ接続されている。

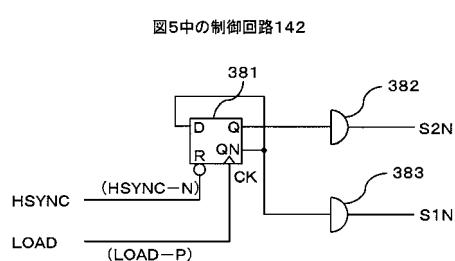

#### 【0102】

(図 5 中の制御回路 142)

図 10 は、図 5 中の制御回路 142 の構成を示す回路図である。

#### 【0103】

この制御回路 142 は、F F 3 8 1 及びバッファ 3 8 2 , 3 8 3 を有している。F F 3 8 1 は、H S Y N C 端子からの負論理の主走査同期信号 H S Y N C - N を入力する負論理のリセット用 R 端子と、L O A D 端子からの正論理のラッチ信号 L O A D - P を入力するクロック入力用 C K 端子と、相互に接続されたデータ入力用 D 端子及び反転データ出力用 Q N 端子と、非反転データ出力用 Q 端子とを有し、これらの Q 端子及び Q N 端子が、バッファ 3 9 2 , 3 9 3 を介して切り替え指令信号用 S 2 N 端子及び S 1 N 端子にそれぞれ接続されている。

10

#### 【0104】

この制御回路 142 では、C K 端子に入力されるラッチ信号 L O A D - P に同期して、“H”又は“L”的切り替え指令信号 S 1 N , S 2 N を S 1 N 端子及び S 2 N 端子から出力する構成になっている。

20

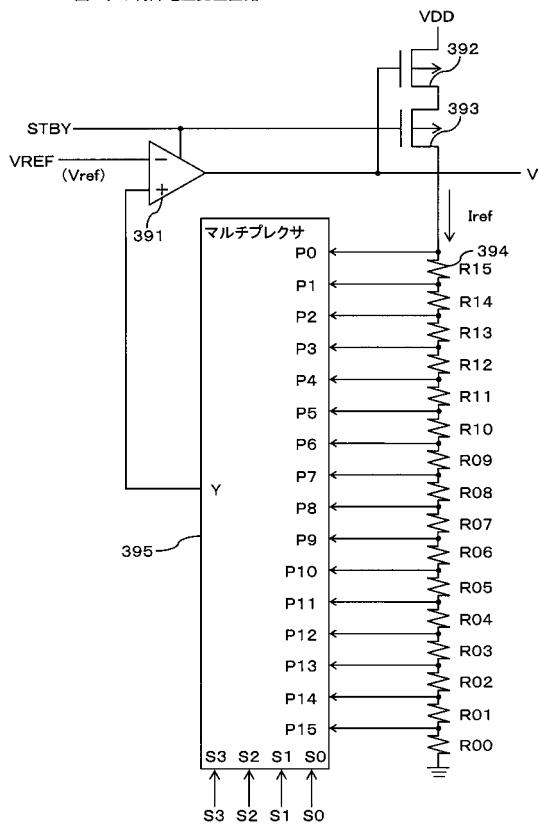

#### 【0105】

(図 6 中の制御電圧発生回路)

図 11 は、図 5 中の制御電圧発生回路 170 の構成を示す回路図である。

#### 【0106】

この制御電圧発生回路 170 は、ドライバ I C 1 0 0 毎に 1 回路ずつ設けられ、演算増幅器(以下「オペアンプ」という。) 3 9 1 と、P M O S 3 9 2 , 3 9 3 と、直列接続された分圧抵抗 R 0 0 ~ R 1 5 からなる分圧回路 3 9 4 と、アナログ形のマルチプレクサ 3 9 5 により構成されている。

20

#### 【0107】

オペアンプ 3 9 1 は、反転入力端子が基準電圧入力用 V R E F 端子に接続され、非反転入力端子がマルチプレクサ 3 9 5 の出力用 Y 端子に接続され、出力端子が P M O S 3 9 2 のゲート及び制御電圧出力用 V 端子に接続され、スタンバイ端子がスタンバイ信号入力用 S T B Y 端子に接続されている。オペアンプ 3 9 1 は、端子 S T B Y から入力されるスタンバイ信号 S T B Y が“L”レベルの時に動作状態になり、スタンバイ信号 S T B Y が“H”レベルの時に非動作状態になって消費電流が略ゼロとなる。

30

#### 【0108】

P M O S 3 9 2 は、図 8 中の各 P M O S 3 5 6 ~ 3 6 0 とゲート長が等しく、ソースが V D D 端子に接続され、ゲートがオペアンプ 3 9 1 の出力端子及び端子 V に接続され、ドレインが P M O S 3 9 3 のソースに接続されている。P M O S 3 9 3 は、ゲートが S T B Y 端子に接続され、ドレインが分圧回路 3 9 4 を介してグランド G N D に接続されている。P M O S 3 9 3 は、S T B Y 端子から入力されるスタンバイ信号 S T B Y が“L”レベルの時にオン状態になり、スタンバイ信号 S T B Y が“H”レベルの時にオフ状態になるスイッチ素子である。そのため、スタンバイ信号 S T B Y が“L”レベルの時には、オペアンプ 3 9 1 が動作状態になると共に P M O S 3 9 3 がオン状態になり、P M O S 3 9 2 , 3 9 3 にドレイン電流 I r e f が流れる。一方、スタンバイ信号 S T B Y が“H”レベルとなってスタンバイ状態が指令されると、オペアンプ 3 9 1 が非動作状態、及び P M O S 3 9 3 がオフ状態になり、オペアンプ 3 9 5 の消費電流が略ゼロになると共に、前記ドレイン電流 I r e f も遮断される。

40

#### 【0109】

マルチプレクサ 3 9 5 は、直列接続された分圧抵抗 R 1 5 ~ R 0 0 における各接続点か

50

らのアナログ電圧が入力される 16 個の入力用 P0 端子～P15 端子と、アナログ電圧を出力する出力用 Y 端子と、図 5 中のメモリ回路 152 の出力用 Q0 端子～Q3 端子から供給される論理信号 Q0～Q3 が入力される 4 個の入力用 S0 端子～S3 端子とを有し、この 4 本の論理信号 S0～S3 により設定される 16 通りの信号論理の組み合わせによって、入力用 P0 端子～P15 端子のうちの何れか 1 つの端子を選択し、この端子に印加されるアナログ電圧を Y 端子からオペアンプ 391 の非反転入力端子へ出力する回路である。換言すれば、マルチプレクサ 395 における入力用 S3 端子～S0 端子の論理信号レベルによって、入力用 P0 端子～P15 端子のうち何れか 1 つの端子が選択され、出力用 Y 端子との間に電流経路が形成される。

## 【0110】

10

オペアンプ 391 と分圧抵抗 R00～R15 及び PMOS392 とで構成される回路により、フィードバック制御回路が構成され、オペアンプ 391 の非反転入力端子の電位が、略基準電圧 VREF と等しくなるように制御される。このため、PMOS392 のドレンイン電流  $I_{ref}$  は、分圧抵抗 R00～R15 のうち、マルチプレクサ 395 により選択される部位の合成抵抗値と、オペアンプ 391 に入力される基準電圧 VREF とから決定されることになる。

## 【0111】

20

例えば、マルチプレクサ 395 の入力用 S3 端子～S0 端子の論理値が “1111” となっていて、補正状態の最大が指令されている時、マルチプレクサ 395 の入力用 P15 端子と出力用 Y 端子とが導通状態になり、入力用 P15 端子の電圧が基準電圧 VREF と略等しくなるように制御される。この結果、PMOS392 のドレンイン電流  $I_{ref}$  は、

$$I_{ref} = VREF / R00$$

となる。

## 【0112】

30

一方、入力用 S3 端子～S0 端子の論理値が “0111” となっていて、補正状態の中間が指令されている時、マルチプレクサ 395 の入力用 P7 端子と出力用 Y 端子とが導通状態になり、入力用 P7 端子の電圧が基準電圧 VREF と略等しくなるように制御される。この結果、PMOS392 のドレンイン電流  $I_{ref}$  は、

$$I_{ref} = VREF / (R00 + R01 + \dots + R07 + R08)$$

となる。

## 【0113】

40

更に、入力用 S3 端子～S0 端子の論理値が “0000” となっていて、補正状態の最小が指令されている時、マルチプレクサ 395 の入力用 P0 端子と出力用 Y 端子とが導通状態となり、入力用 P0 端子の電圧が前記基準電圧 VREF と略等しくなるように制御される。この結果、PMOS392 のドレンイン電流  $I_{ref}$  は、

$$I_{ref} = VREF / (R00 + R01 + \dots + R14 + R15)$$

となる。

## 【0114】

このように、図 8 中の PMOS356～360 と図 11 中の PMOS392 とは、ゲート長が相等しく構成され、これら PMOS が飽和領域で動作するように制御されているので、各 PMOS はカレントミラーの関係となり、PMOS356～360 がオン状態となる時、基準電圧 VREF に比例するドレンイン電流  $I_{ref}$  を生じる。この結果、マルチプレクサ 395 の入力用 S3 端子～S0 端子に与える論理値状態により、ドレンイン電流  $I_{ref}$  を 16 段階に調整することができ、図 8 中の PMOS356～360 のドレンイン電流もまた 16 段階に調整可能とすることができる。

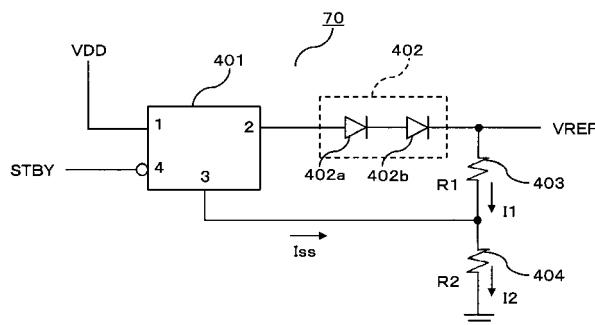

## 【0115】

(図 1 中の基準電圧発生回路)

図 12 は、図 1 中の基準電圧発生回路 70 の構成を示す回路図である。

## 【0116】

50

この基準電圧発生回路 70 は、電源電圧 VDD が印加される VDD 端子、スタンバイ信

号 S T B Y が入力される S T B Y 端子、基準電圧 V R E F を出力する V R E F 端子、及び G N D 端子を有し、その V D D 端子及び S T B Y 端子に、切り替え回路（例えば、定電圧発生用レギュレータ）401が接続されている。レギュレータ401は、略記して示す4つの端子1, 2, 3, 4を有し、端子1は電源端子であって V D D 端子と接続され、端子2はGND端子との間に所定の出力電圧を出力する出力端子、端子3はグランド端子、端子4はチップイネーブル入力端子であって S T B Y 端子と接続されている。このレギュレータ401は、端子4に入力されるスタンバイ信号 S T B Y が“L”レベルの時に、端子2から定電圧を出力し、スタンバイ信号 S T B Y が“H”レベルの時に、端子2の出力がオフすると共に、消費電流もまた略ゼロとなる低消費電力モードに移行する切り替え回路である。

10

## 【0117】

レギュレータ401の端子2には、ダイオード部402が接続されている。ダイオード部402は、2つのダイオード402a, 402bを有し、これらが順方向に直列に接続されている。ダイオード402bのカソードには、V R E F 端子が接続されると共に、抵抗R1の抵抗403及び抵抗R2の抵抗404を介して GND 端子に接続されている。抵抗403及び404の接続点は、レギュレータ401の端子3に接続されている。

## 【0118】

図12において、抵抗R1の抵抗403に流れる電流をI1、抵抗R2の抵抗404に流れる電流をI2、レギュレータ401の端子3から流れるグランド電流をI<sub>ss</sub>とする。更に、レギュレータ401の端子2, 3間に生じる出力電圧をV<sub>o</sub>、抵抗403の両端電圧をV1、ダイオード402a, 402bの順電圧をV<sub>f</sub>とすると、

$$V_1 = V_o - 2 \times V_f$$

となる。この時、電流I1は、

$$I_1 = V_1 / R_1 = (V_o - 2 \times V_f) / R_1$$

となる。一方、レギュレータ401のグランド電流I<sub>ss</sub>は、電流I1, I2と比べて無視できる程小さいので、

$$I_2 = I_1 + I_{ss} - I_1$$

である。抵抗R2の抵抗403における両端電圧V2は、

$$V_2 = R_2 \times I_2 = R_2 \times (I_1 + I_{ss}) = (V_o - 2 \times V_f) \times (R_2 / R_1)$$

と求まる。

30

## 【0119】

基準電圧発生回路70のV R E F 端子から出力される基準電圧 V R E F は、(V1 + V2)であるので、これより基準電圧 V R E F は、

$$V R E F = (1 + R_2 / R_1) \times (V_o - 2 \times V_f)$$

として求めることができる。

## 【0120】

次に、基準電圧 V R E F の温度係数を求めてみる。抵抗R1の抵抗403と、抵抗R2の抵抗404の温度係数は小さく、レギュレータ自体の温度係数も小さいので、これらの温度係数は無視することができる。そのため、基準電圧 V R E F の温度係数Tcは、

$$T_c = (1 / V R E F) \times V R E F / T = 2 / (V_o - 2 \times V_f) \times (-V_f / T)$$

となる。

## 【0121】

ここで、ダイオード402a, 402bの順電圧V<sub>f</sub>はマイナスの温度係数を持つので、出力する基準電圧 V R E F として正の温度係数のものが得られ、この数値はレギュレータ401の出力電圧V<sub>o</sub>の設定により、種々に変えることが可能であることが判る。又、基準電圧 V R E F 値もまた、抵抗403, 404における抵抗比 R2 / R1 を変えることで、前記温度係数Tcの設定とは独立して任意に設定可能である、という設計上の利点を有している。

40

## 【0122】

50

(LEDヘッド基板ユニット)

図13(a)～(c)は、図3中のLEDヘッド基板ユニットを示す構成図であり、同図(a)は平面図、同図(b)はその平面図の一部の拡大図、及び、同図(c)は同図(b)に対比するように描かれた断面図である。

【0123】

図13(a)において、長方形のプリント配線板13bの平面(即ち、上面)上には、複数(例えば、26個)のドライバIC100(=100-1～100-26)がそのプリント配線板13bの長辺方向に沿って配置されると共に、これらのドライバIC100に隣接して、複数(例えば、26個)のLEDアレイ200(=200-1～200-26)がプリント配線板13bの長辺方向に沿って配置されている。更に、プリント配線板13bの両短辺付近には、LEDヘッド13を制御する制御信号端子や図1中のコネクタ端子VDD3等の電源端子、及びGND端子等を含んだコネクタ210と、基準電圧発生回路70とが搭載されている。

10

【0124】

図13(b)において、プリント配線板13bの上面上には、ドライバIC100-1, 100-2, 100-3, …に隣接して、端子パッド列211が形成され、この端子パッド列211における所要所間が、プリント配線板13b上に形成された配線パターン212により接続されている。

【0125】

図13(c)において、例えば、ドライバIC100-1のDATAO3端子パッド～DATAO0端子パッドは、ボンディングワイヤ213を介して、プリント配線板13bの端子パッド列211に接続され、この端子パッド列211が配線パターン212を介して、他の端子パッド列211に接続され、この他の端子パッド列211が、ボンディングワイヤ213を介して、他のドライバIC100-2のDATAO3端子パッド～DATAO0端子パッドに接続されている。各ドライバIC100-1, …のLED駆動端子パッドと各LEDアレイ200-1, …のアノードパッドとが、ボンディングワイヤ214により接続され、各LEDアレイ200-1, …の共通カソードとプリント配線板13b上の図示しないカソードパッドとが、ボンディングワイヤ215により接続されている。

20

【0126】

30

(LEDヘッドの全体の動作)

図14は、本発明の実施例1における画像形成装置1の電源投入後に、図1のLEDヘッド13に対して行われる補正データ転送処理と、その後に行われる印刷データ転送の様子を示すタイムチャートである。

【0127】

補正データの転送開始に先立ち、引き続くデータ転送が補正データであることを示すため、ラッチ信号HD-LOADを“H”とする(I部)。

【0128】

次いで、奇数番目に属するドットについて1ドット当たり4ビットからなる補正データのうち、bit3のものを印刷データ信号HD-DATA3～HD-DATA0からクロック信号HD-CLKに同期して入力して、図5のFF111A1～FF111D24で構成されるシフトレジスタ110中へシフト入力する。シフト入力が完了すると、A部に示すように、印刷駆動信号HD-STB-Nが3パルス入力され、図9の制御回路141の動作が行われる。

40

【0129】

図14中のQ1, Q2, Q3, Q4, Q5は、図9のFF361, 362, 363, 365, 364の各出力端子、E1, E2は、AND回路367, 368から出力される書き込みイネーブル信号、W3～W0は、AND回路370～373から出力される書き込み制御信号である。更に、S1N, S2Nは、図10中のバッファ382, 383から出力される奇数ドットデータと偶数トッドデータとの切り替え指令信号である。

50

## 【0130】

図14のA部において、印刷駆動信号HD-STB-Nの1パルス目が入力されると、J部に示すように、Q1端子の信号が発生し、次いで印刷駆動信号HD-STB-Nの2パルス目で、K部に示すように、Q2端子の信号が発生する。又、Q1端子の信号が立ち上がる毎にQ3端子の信号が状態反転し、L部に示すように、Q3端子の信号が“H”レベルに遷移する。Q3端子の信号の遷移に引き続き、書き込みイネーブル信号E1,E2が発生する。

## 【0131】

書き込みイネーブル信号E1の立ち上がりエッジに引き続き、M部に示すように、Q4端子の信号が立ち上がり、書き込みイネーブル信号E1の次の立ち上がりで、Q5端子の信号が立ち上がり、更に、書き込みイネーブル信号E1の次の立ち上がりで、Q4端子の信号が立ち下がり、書き込みイネーブル信号E1の次の立ち上がりで、Q5端子の信号が立ち下がる。

10

## 【0132】

書き込み制御信号W3～W0は、Q2端子の信号に引き続いて発生するものであるが、O部、P部に示すように、書き込み制御信号W3が2回に亘って出力され、次いで、各書き込み制御信号W2,W1,W0においても、それぞれ2パルスずつ発生する。

## 【0133】

各書き込み制御信号W3～W0のパルスが発生する毎に、図6のメモリ回路151にデータの書き込みが行われ、書き込み制御信号W3～W0の1パルス目で、メモリセル回路300-1内の奇数ドット用メモリセル311～314へのデータ書き込みが行われ、2パルス目で、メモリセル回路300-1内の偶数ドット用メモリセルへのデータ書き込みが行われる。

20

## 【0134】

前記1パルス目の書き込み制御信号W3～W0(O部等)は、A部、C部、E部、G部について入力された印刷駆動信号HD-STB-Nを基に発生されるものであり、前記2パルス目の書き込み制御信号W3～W0(P部等)は、B部、D部、F部、H部について入力された印刷駆動信号HD-STB-Nを基に発生されるものである。

## 【0135】

以上の過程を経て、補正データb3～b0(Odd=ODD3～ODD0, Even=EVN3～EVN0)のbit3～bit0の全てのデータ書き込みが完了すると、Q部に示すように、ラッチ信号HD-LOADを“L”レベルにして、印刷データ信号HD-DATA3～HD-DATA0の転送が可能な状態に遷移する。1ラインの印刷開始に際し、引き続くデータ転送が奇数ドットのものであることを示すため、主走査同期信号HD-HSYNC-Nが入力される(R部)。

30

## 【0136】

次いで、U部で奇数ドットの印刷データ信号HD-DATA3～HD-DATA0が転送され、S部のラッチ信号HD-LOADのパルスにより、シフトレジスタ110にシフト入力された印刷データ信号HD-DATA3～HD-DATA0が、ラッチ部130にラッチされる。

40

## 【0137】

更に、W部に示すように、印刷駆動信号HD-STB-Nが“L”レベルへと遷移して、LED201,202,・・・の発光駆動が行われる。印刷データ信号HD-DATA3～HD-DATA0がオン状態であると、“L”レベルとなる期間、LED201,202,・・・が発光駆動されることになる。同様にV部では、偶数ドットのデータ転送が行われ、このデータはT部のパルスによりラッチされ、同様にX部において、LED201,202,・・・が発光駆動される。

## 【0138】

(補正データ転送の詳細)

図15～図18は、図14のタイムチャートにおいてドライバ1C100(=100-

50

1, 100-2, . . .) を 1 チップのみに簡略化した場合における補正データ転送の詳細波形を示すタイムチャートである。

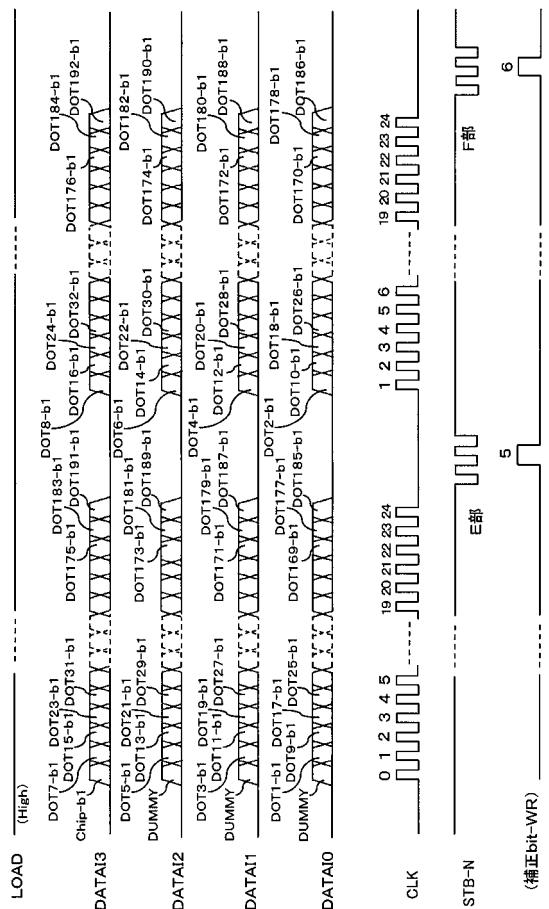

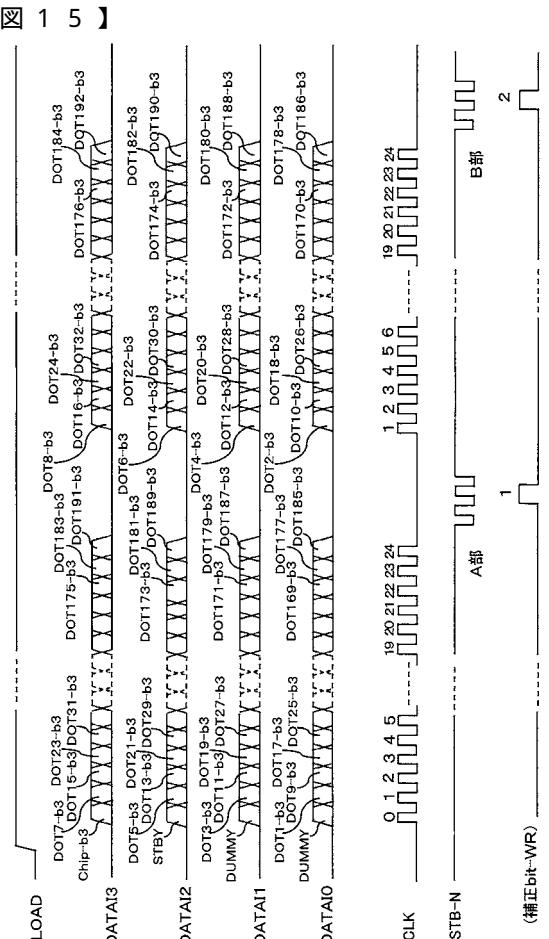

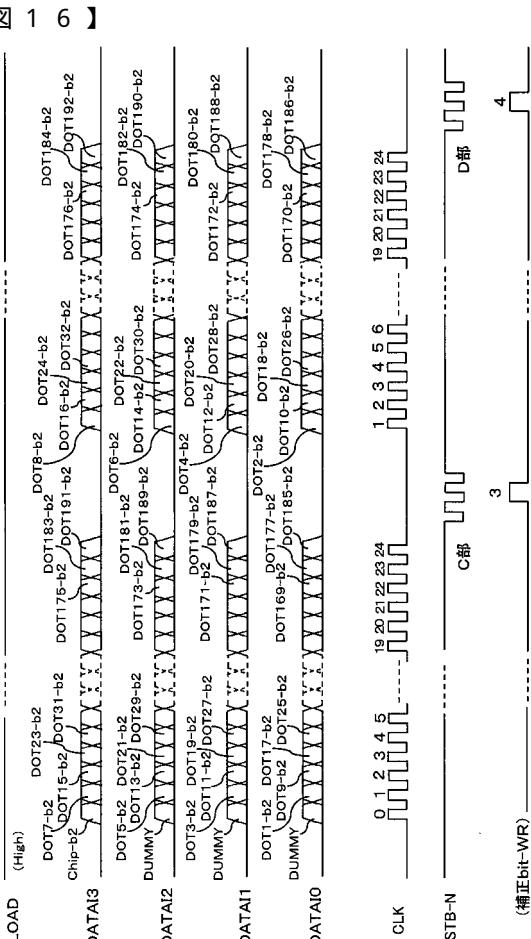

#### 【0139】

ここで、図 15 は図 14 の A 部と B 部の詳細を示すタイムチャート、図 16 は図 14 の C 部と D 部の詳細を示すタイムチャート、図 17 は図 14 の E 部と F 部の詳細を示すタイムチャート、更に、図 18 は図 14 の G 部と H 部の詳細を示すタイムチャートである。

#### 【0140】

図 15において、各ドライバ 1 C 100 毎に設定されるチップ補正データ b3 ~ b0 は、奇数ドット転送(例えば、A 部)と偶数ドット転送(例えば、B 部)の内、1 回のみ行えれば十分である。

10

#### 【0141】

このため、図 15 ~ 図 18においては、A 部、C 部、E 部、G 部等の奇数ドットの補正データ転送時に、シフトレジスタ 110 の段数を 1 段多くなるように切り替えて、送出データ列の先頭位置にチップ補正データ(Chip - b3, Chip - b2, Chip - b1, Chip - b0 等)を割り当てて送出するように工夫されている。

20

#### 【0142】

併せて、図 15 に示すように、補正データ列の先頭には、チップ補正データ(Chip - b3, Chip - b2, Chip - b1, Chip - b0 等)の bit3 (Chip - b3) の他、データ入力信号 DATAI2 の先頭部にスタンバイ信号 STBY ビットを割り当てており、この信号によって図 5 中のラッチ回路 154 のスタンバイ信号 STBY によるデータを次のシーケンスによって格納することができる。

20

#### 【0143】

先ず、図 15 の A 部で示す補正データ(Chip - b3 等)の書き込み制御信号(“1”で示す箇所)により、図 5 中の AND 回路 153 の出力端子には正極性のパルス信号を生じて、このパルス信号がラッチ回路 154 の G 端子に入力され、その時、ラッチ回路 154 の D 端子に印加されている FF111C26 の Q 端子の信号レベルをそのラッチ回路 154 の内部に取り込んで、記憶保持する。

30

#### 【0144】

ここで、図 5 中のラッチ回路 154 の Q 端子から出力されるスタンバイ信号 STBY が“L”レベルであったとする。

#### 【0145】

このスタンバイ信号 STBY の“L”レベルは、制御電圧発生回路 170 に入力され、この制御信号発生回路 170 が動作可能状態になる。又、スタンバイ信号 STBY の“L”レベルは、図 12 の基準電圧発生回路 70 内におけるレギュレータ 401 の端子 4(負論理のチップイネーブル入力端子)にも印加される。そのため、レギュレータ 401 が動作可能状態になり、ダイオード部 402 から所定の基準電圧 VREF が発生する。

40

#### 【0146】

即ち、スタンバイ信号 STBY の“L”レベルが入力されると、レギュレータ 401 が動作モードになり、この端子 2 からダイオード部 402 及び抵抗 403, 404 を通してグランド GND へ至る電流 I2 を生じる。この結果、レギュレータ 401 の端子 1 には、それに応じた電源電流を生じることになる。この電源電流は、主としてダイオード部 402 及び抵抗 403, 404 に流れる電流 I1 に略等しく、典型的な設計例では 10mA と大きなものとなる。

#### 【0147】

別の場合として、図 5 中のラッチ回路 154 の Q 端子から出力されるスタンバイ信号 STBY が“H”レベルとなる場合を考える。

#### 【0148】

スタンバイ信号 STBY の“H”レベルは、制御信号発生回路 170 に入力される。そのため、制御信号発生回路 170 の動作が停止し、この制御信号発生回路 170 の電源電流は略ゼロになる。又、スタンバイ信号 STBY の“H”レベルは、図 12 の基準電圧発

50

生回路 70 内におけるレギュレータ 401 の端子 4 (負論理のチップイネーブル入力端子) にも印加される。そのため、レギュレータ 401 が動作禁止状態になり、このレギュレータ 401 からの電流出力がオフする。そのため、レギュレータ 401 の端子 2 からダイオード部 402 及び抵抗 403, 404 を通してグランド GND へ至る電流 I2 は遮断され、レギュレータ 401 の端子 1 に生じる電流も略ゼロとなる。この結果、制御信号発生回路 170 のみならず、基準電圧発生回路 70 全体としても、電源電流を略ゼロにできる。

#### 【0149】

(実施例 1 の効果)

本実施例 1 によれば、次の (a)、(b) のような効果がある。

10

#### 【0150】

(a) 従来の LED ヘッドにおいては、多数のドライバ IC を搭載して、このドライバ IC の端子パッドとプリント配線板の端子パッドとの間をワイヤボンディングにより接続している。LED ヘッドの基板ユニットに搭載されるドライバ IC は多数であり、ボンディングワイヤの数も多数に及ぶので、この製造過程において、ごく稀にではあるがワイヤボンディングを行うときに実装位置ずれを生じて、ボンディングワイヤの接続部がドライバ IC 側の端子パッドからはみ出してしまい、前記端子パッドに隣接配置されている回路素子を押し潰し、損傷を与える可能性がある。

#### 【0151】

このようにして生じる損傷チップの有無を検出するためには、前記損傷箇所を通じて電流が流れることによる電源電流 (IDDq 電流) を測定することが有効であり、特許文献 1 には、そのための好適な構成が開示されている。

20

#### 【0152】

ところが、LED の温度補償のために、基準電圧発生回路を用いようとすると、これに用いる三端子レギュレータ IC によって静的な電源電流 (典型的な例では 10 mA) を生じてしまい、前記の損傷により生じる微小な IDDq 電流 (典型例では 1 μA 以下) の有無により生じる差異を検出することができない。

#### 【0153】

このような不都合を解決するために、本実施例 1 の構成においては、LED ヘッド 13 に用いられる各ドライバ IC 100 内に、外部からの制御信号により論理状態が任意に設定可能な出力用 STBY 端子を設け、この STBY 端子から出力されるスタンバイ信号 STBY により、基準電圧発生回路 70 の動作状態をオン / オフ切り替えることを可能にしている。これにより、基準電圧発生回路 70 により生じていた静的消費電流が遮断され、LED ヘッド全体での消費電流を略ゼロにすることができる。この結果、LED ヘッド 13 の実装組立て後の試験工程において、実装不具合による損傷チップの有無を、電源電流 (IDDq 電流) を測定することで、高精度に判別することができる、LED ヘッド 13 の品質レベルを格段に向上させることができる。

30

#### 【0154】

更に、電源電流を遮断して消費電流を略ゼロにできる構成としたことで、LED ヘッド 13 を用いた画像形成装置 1 の待機時消費電力を低減することも可能となり、大幅な省エネルギーが図れるという効果も得られる。

40

#### 【0155】

(b) 本実施例 1 の画像形成装置 1 によれば、前記 LED ヘッド 13 を採用するため、スペース効率及び光取り出し効率に優れた高品質の画像形成装置 (プリンタ、複写機、ファクシミリ装置、複合機等) を提供することができる。即ち、前記 LED ヘッド 13 を用いることにより、上述したフルカラーの画像形成装置 1 に限らず、モノクロ、マルチカラーの画像形成装置においても効果が得られるが、特に露光装置を数多く必要とするフルカラーの画像形成装置において一層大きな効果が得られる。

#### 【0156】

(実施例 1 の変形例)

50

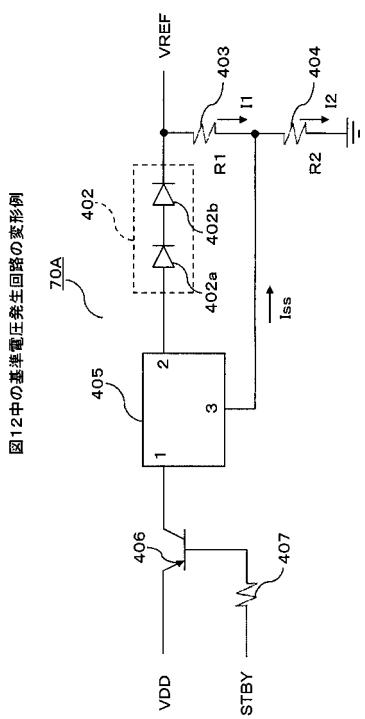

図19は、図12の基準電圧発生回路70の変形例を示す回路図である。

#### 【0157】

この変形例の基準電圧発生回路70Aでは、図12の基準電圧発生回路70におけるレギュレータ401に代えて、これとは構成の異なるレギュレータ405、PNPトランジスタ406、及び抵抗407が設けられている。

#### 【0158】

レギュレータ405は、略記して示す3つの端子1, 2, 3を有し、端子1は電源端子、端子2は所定の出力電圧を出力する出力端子であってダイオード402aのアノードに接続され、端子3はグランド端子であって抵抗403及び404の接続点に接続されている。このレギュレータ405は、端子1に電源電圧VDDが印加された時に、端子2から定電圧を出力し、端子1への印加電圧が0Vの時に、端子2の出力がオフすると共に、消費電流もまたゼロとなる低消費電力モードに移行する回路である。10

#### 【0159】

レギュレータ405の端子1には、PNPトランジスタ406のコレクタ端子（以下単に「コレクタ」という。）が接続され、エミッタ端子（以下単に「エミッタ」という。）に電源電圧VDDが印加され、ベース端子（以下単に「ベース」という。）に抵抗407を介してスタンバイ信号STBYが入力される。その他の構成は、図12の基準電圧発生回路70と同様である。

#### 【0160】

このような構成の基準電圧発生回路70Aでは、入力されるスタンバイ信号STBYが“L”レベルの時に、トランジスタ406がオン状態になって電源電圧VDDがレギュレータ405の端子1に印加され、このレギュレータ405が動作する。入力されるスタンバイ信号STBYが“H”レベルの時には、トランジスタ406がオフ状態になり、レギュレータ405の端子1が0Vになるので、このレギュレータ405が非動作状態になる。そのため、レギュレータ405の端子2の出力がオフすると共に、消費電流もまたゼロとなる低消費電力モードに移行する。従って、図12の基準電圧発生回路70とほぼ同様の効果が得られる。20

#### 【実施例2】

#### 【0161】

本発明の実施例2における画像形成装置の全体構成は、実施例1と同様であるが、この画像形成装置に設けられるLEDヘッドの構成及び動作が実施例1と異なるので、この異なる箇所を以下説明する。30

#### 【0162】

(LEDヘッド)

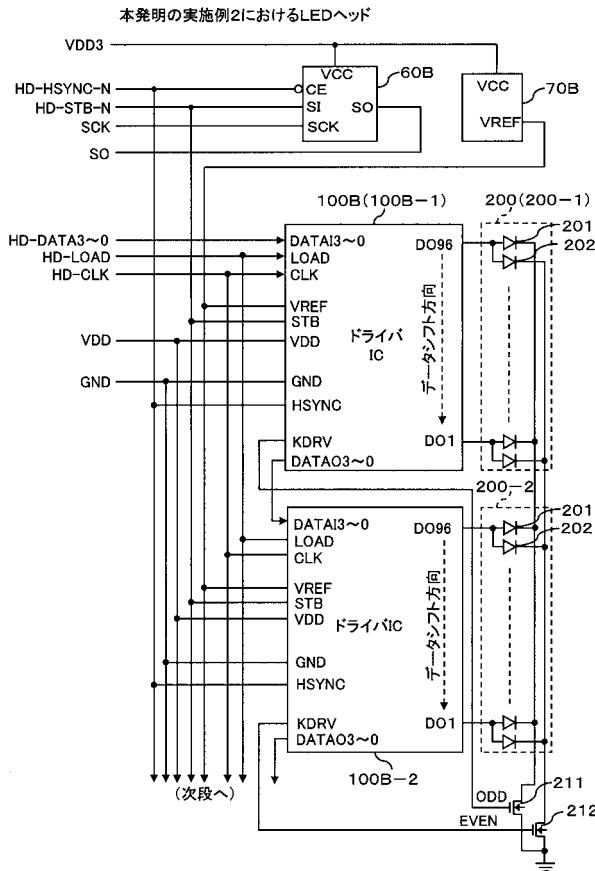

図20は、本発明の実施例2におけるLEDヘッド13Bを示す構成図であり、実施例1のLEDヘッド13を示す図1中の要素と共に通の要素には共通の符号が付されている。

#### 【0163】

本実施例2のLEDヘッド13Bでは、実施例1のLEDヘッド13におけるEEPROM60、基準電圧発生回路70及び複数のドライバIC100(=100-1, 100-2, ...)に代えて、これらとは機能あるいは構成の異なる付帯回路であるEEPROM60B、基準信号生成手段である基準電圧発生回路70B、及び駆動回路である複数のドライバIC100B(=100-1B, 100-2B, ...)が設けられている。40

#### 【0164】

EEPROM60Bは、実施例1のEEPROM60に対して内部回路が異なる。即ち、EEPROM60は、実施例1のEEPROM60と同様に、LEDヘッド13Bのコネクタ端子VDD3に接続された第2の電源電圧VCC用のVCC端子、主走査同期信号HD-HSYNC-Nを負論理チップイネーブル信号CEとして入力するCE端子、印刷駆動信号HD-STB-NをシリアルデータSIとして入力するSI端子、シリアルクロック信号SCKを入力するSCK端子、及びシリアルデータSOを出力するSO端子を有し、CE端子から入力される主走査同期信号HD-HSYNC-Nにより活性化され、シ50

リアルクロック信号 SCK に同期して印刷駆動信号 HD-STB-N をシリアルデータ SI として入力して格納するための半導体メモリであるが、実施例 1 の EEPROM60 に対して内部回路が異なる。なお、第 2 の電源電圧 VCC は、第 1 の電源電圧 VDD とは異なる電源系統である。

#### 【0165】

基準電圧発生回路 70B は、コネクタ端子 VDD3 から供給される電源電圧 VCC を入力する VCC 端子と、LED 駆動のための駆動電流値を指令するための基準電圧 VREF を出力する VREF 端子とを有し、電源電圧 VCC が VCC 端子に入力されると活性化され（即ち、内部回路が動作し）、基準電圧 VREF を発生して VREF 端子から出力し、各ドライバ IC100B へ供給する回路である。電源電圧 VCC が基準電圧発生回路 70B の VCC 端子に入力されないと（即ち、VCC 端子への電源電圧 VCC の入力が停止されると）、この基準電圧発生回路 70B の内部回路における動作が停止し、基準電圧 VREF の出力が停止される。10

#### 【0166】

このように、本実施例 3 では、コネクタ端子 VDD3 に印加される電源電圧 VCC を遮断することで、EEPROM60B 及び基準電圧発生回路 70B の電源電流を遮断する構成になっている。

#### 【0167】

各ドライバ IC100B は、実施例 1 の各ドライバ IC100 と同様に、複数の端子を有しているが、スタンバイ信号 STBY 出力用の STBY 端子のみが削除され、内部回路は、実施例 1 の各ドライバ IC100 と同様の構成である。ここで、EEPROM60B の第 1 の信号入力端子である CE 端子及び SI 端子と、各ドライバ IC100B の第 2 の信号入力端子である HSYNC 端子及び STB 端子とが接続されて、コネクタ端子ピンが共有化されている。20

その他の構成は、実施例 1 の LED ヘッド 13 と同様である。

#### 【0168】

（図 20 中の EEPROM）

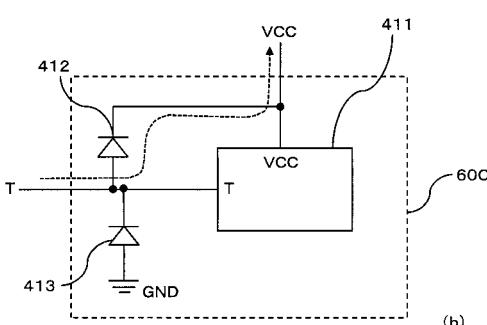

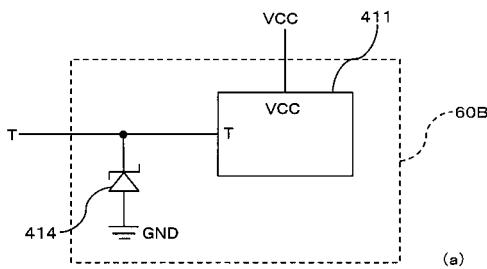

図 21 (a)、(b) は、図 20 中の EEPROM60B の構成を示す概略の回路図であり、同図 (a) は本実施例 2 の EEPROM60B の回路図、及び、同図 (b) は同図 (a) と対比するように図示した従来構成の EEPROM60C の回路図である。30

#### 【0169】

図 21 (b) に示す EEPROM60C は、電源電圧 VCC を入力する VCC 端子と、図 20 中の CE 端子、SI 端子、及び SCK 端子等を総称した端子 T とを有し、これらの VCC 端子及び T 端子に、EEPROM 本体である内部のコア部 411 と、このコア部 411 の入力回路を構成する 2 つのダイオード 411, 412 とが接続されている。

#### 【0170】

EEPROM60C 内のコア部 411 は、EEPROM60C の VCC 端子及び T 端子に接続された VCC 端子及び T 端子とを有している。ダイオード 412 は、アノードが端子 T に接続され、カソードが VCC 端子に接続されている。ダイオード 413 は、アノードがグランド GND に接続され、カソードが T 端子に接続されている。ダイオード 412, 413 は、静電気放電 (Electro Static Discharge、以下「ESD」という。) 保護のための静電気保護素子であって、ESD 等により正極性や負極性の過大電圧が T 端子に印加された時に、電源側やグランド GND 側に放電させ、コア部 411 の T 端子に過大電圧が印加されるのを防止している。40

#### 【0171】

これに対し、図 21 (a) に示す EEPROM60B は、図 21 (b) の EEPROM60C と同様のコア部 411 と、EEPROM60C のダイオード 413 に対応したダイオード 414 とを有しているが、EEPROM60C における T 端子から VCC 端子に向かう方向のダイオード 412 が削除された構成になっている。

#### 【0172】

なお、本実施例3のEEPROM60Bにおいて、前記ダイオード412を削除する代わりに、ダイオード414においては、ブレークダウン電圧を低めに設定して、ツェナーダイオードに類似の電圧・電流特性を備えるようにすることで、T端子に正極性の過大電圧が印加された時には、ダイオード414に逆方向に電圧が印加されるが、前記ブレークダウンによりこのダイオード414のカソードからアノードへ向けて電流が流れることで、コア部411のT端子に過大な電圧が印加されることを防止することができる。

#### 【0173】

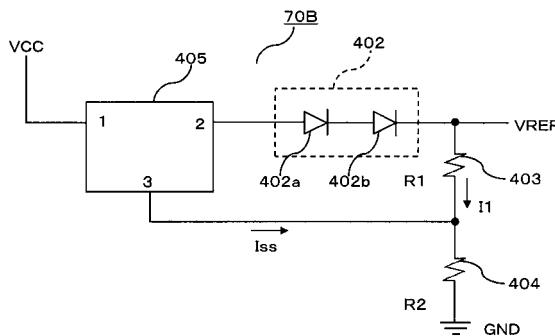

(図20中の基準電圧発生回路)

図22は、図20中の基準電圧発生回路70Bの構成を示す回路図であり、図19に示す基準電圧発生回路70A中の要素と共に共通の要素には共通の符号が付されている。

10

#### 【0174】

本実施例2の基準電圧発生回路70Bでは、図19の基準電圧発生回路70AにおけるPNPトランジスタ406及びSTBY端子が削除され、VDD端子がレギュレータ405の端子1に直接接続された構成になっている。その他の構成は、図19の基準電圧発生回路70Aと同様である。

#### 【0175】

(LEDヘッドのスタンバイ状態の動作)

本実施例2における図20のLEDヘッド13Bにおいて、図21(a)のEEPROM60Bを備えることの動作を、図21(b)のEEPROM60Cを備える場合と対比しつつ、以下説明する。

20

#### 【0176】

図20のLEDヘッド13Bでは、LEDヘッド組立て後の完成試験において、実装工程不具合による損傷チップの有無を検出するために、複数のドライバIC100B(=100-1B, 100-2B, ...)をスタンバイ状態に設定して、消費電流を略ゼロにする。

#### 【0177】

同時に、基準電圧発生回路70BのVCC端子に接続されたコネクタ端子VDD3の電圧を略ゼロに設定することで、この基準電圧発生回路70Bによる消費電流を略ゼロとすることができる。またこの時、EEPROM60BのCE端子を“H”レベルとすることで、このEEPROM60Bもまたスタンバイ状態とされ、その消費電流を略ゼロとすることができるはずである。

30

#### 【0178】

ところが、図20中のEEPROM60Bの入力回路が、図21(b)に示すEEPROM60Cのような入力回路の構成であったとすると、図21(b)中に破線矢印で示す向きの回り込み電流を生じてしまう。

#### 【0179】

例えば、図21(b)のEEPROM60Cにおいて、T端子がシリアルデータ入力用SI端子であったとすると、このSI端子には主走査同期信号HD-STB-Nが入力されており、この時の主走査同期信号HD-STB-Nのレベルは“H”であるが、図21(b)のVCC端子の電位がゼロであると、ダイオード412のアノード・カソード間に電流が流れてしまい、端子T(この場合は印刷駆動信号HD-STB-Nが入力されている。)の“H”レベルを低下させる。そのため、図5のドライバIC内部のブルアップ抵抗143に電流を生じてしまい、本来ゼロとなるように設定していたドライバIC100Bに電源電流を生じることになる。この結果、図21(b)の構成のままでは、図20のLEDヘッド13Bにおいて所望の作用効果を奏することができない。

40

#### 【0180】

そこで、本実施例2では、図21(a)に示すEEPROM60Bの構成にすることで、図21(b)における破線矢印の電流を生じなくすることができる。従って、スタンバイ状態におけるドライバIC100Bの電源電流ゼロの状態を実現することが可能となる。

50

## 【0181】

(LEDヘッドの全体の動作)

図23は、本発明の実施例2における画像形成装置1の電源投入後に、図20のLEDヘッド13Bに対して行われる補正データ転送処理と、これと同時に行われるスタンバイ状態の設定シーケンスを示すタイムチャートである。この図23では、実施例1の図14中の要素と共に共通の要素には共通の符号が付されている。

## 【0182】

補正データ $b_3 \sim b_0$  ( $Odd = Odd_3 \sim Odd_0$ ,  $Even = Even_3 \sim Even_0$ ) の転送開始に先立ち、引き続くデータ転送が補正データ $b_3 \sim b_0$  であることを示すため、ラッチ信号HD-LOADを“H”にする(I部)。次いで、奇数番目に属するドットについて1ドット当たり4ビットからなる補正データ $b_3 \sim b_0$  のうち、 $b_{it3}$  の補正データ $b_3$  をHD-DATA3端子～HD-DATA0端子からクロック信号HD-CLK-Pに同期して入力し、図5中のシフトレジスタ110内へシフト入力する。シフト入力が完了すると、A部に示すように、印刷駆動信号HD-STB-Nが3パルス入力され、図9に示す制御回路141の動作が行われる。

10

## 【0183】

図23のA部において、印刷駆動信号HD-STB-Nの1パルス目が入力されると、J部に示すように、図9中のFF361のQ端子(=Q1端子)の信号が発生し、次いで、印刷駆動信号HD-STB-Nの2パルス目で、K部に示すように、図9中のFF362のQ端子(=Q2端子)の信号が発生する。又、Q1端子の信号が立ち上がる毎に、図9中のFF363のQ端子(=Q3端子)の信号が状態反転し、L部に示すように、Q3端子の信号は“H”レベルに遷移している。

20

## 【0184】

Q3端子の信号の遷移に引き続き、書き込みイネーブル信号E1, E2が発生する。書き込みイネーブル信号E1の立ち上がりエッジに引き続き、M部に示すように、図9中のFF365のQ端子(=Q4端子)の信号が立ち上がり、書き込みイネーブル信号E1の次の立ち上がりで、図9中のFF364のQ端子(=Q5端子)の信号が立ち上がり、更に、書き込みイネーブル信号E1の次の立ち上がりで、Q4端子の信号が立ち下がり、書き込みイネーブル信号E1の次の立ち上がりで、Q5端子の信号が立ち下がる。

30

## 【0185】

書き込み制御信号W3～W0はQ2端子の信号に引き続いて発生するものであるが、O部、P部のように、書き込み制御信号W3が2回に亘って出力され、次いで、書き込み制御信号W2, W1, W0の各信号においても、それぞれ2パルスずつ発生する。

## 【0186】

書き込み制御信号W3～W0の各パルスが発生する毎に、図6のメモリ回路151にデータの書き込みが行われ、書き込み制御信号W3～W0の1パルス目で奇数ドット用メモリセル回路300-1内のメモリセル311～314へのデータ書き込みが、2パルス目で偶数ドット用メモリセル回路300-2内のメモリセルへのデータ書き込みが行われる。

40

## 【0187】

前記1パルス目の書き込み制御信号W3(O部等)は、A部、C部、E部、G部において入力された印刷駆動信号HD-STB-Nを基に発生されるものであり、前記2パルス目の書き込み制御信号W3(P部等)は、B部、D部、F部、H部について入力された印刷駆動信号HD-STB-Nを基に発生されるものである。

## 【0188】

以上の過程を経て、補正データ $b_3 \sim b_0$  の $b_{it3} \sim b_{it0}$  の全てのデータ書き込みが完了すると、Q部に示すように、ラッチ信号HD-LOADを“L”として、補正データ $b_3 \sim b_0$  の格納処理が完了する。これにより、図5のAND回路153及びラッチ回路154の動作において説明したように、各ドライバIC100Bのスタンバイ信号STBYを選択的に設定することができ、LEDヘッド全体としてスタンバイモード(消費

50

電流を略ゼロとする状態)に設定することができる。

#### 【0189】

次いで、R部に示すように、コネクタ端子VDD3の電源電圧VCCを立ち下げて、電位を略ゼロにする。これにより、図20中のEEPROM60B及び基準電圧発生回路70Bの電源電流をゼロとすることができる。そのため、図21(a)を用いて説明したように、LEDヘッド13Bに入力されている“H”レベル信号(例えば、印刷駆動信号HD-STB-N)に生じる電流流入が生じることがなく、その電位状態にも影響を与えることがない。

#### 【0190】

(実施例2の効果)

本実施例2によれば、実施例1の(a)の効果で説明したような従来の課題を解決できる以下のような効果があり、更に、以下のような効果があるので、実施例1の(b)の効果とほぼ同様の効果がある。

#### 【0191】

本実施例2の構成においては、従来の課題を解決するために、LEDヘッド13Bに用いられる各ドライバIC100B内で、外部からの制御信号により静止時消費電流を略ゼロにすると共に、LEDヘッド13Bの付帯回路である基準電圧発生回路70Bの電源を切断可能とすることで、その消費電流を切断可能として、LEDヘッド全体での消費電流を略ゼロにすることができる。この結果、LEDヘッド13Bの実装組立て後の試験工程において、実装不具合による損傷チップの有無を、電源電流(I<sub>DDQ</sub>電流)を測定することで、高精度に判別することが可能となり、LEDヘッド13Bの品質レベルを格段に向上させることができる。

#### 【0192】

更に、電源電流を遮断して消費電流を略ゼロにできる構成としたことで、LEDヘッド13Bを用いた画像形成装置1の待機時消費電力を低減することも可能となり、大幅な省エネルギーが図れるという効果も得られる。

#### 【0193】

(実施例の他の変形例)

本発明は、上記実施例1、2やこれらの変形例に限定されず、その他の利用形態や変形が可能である。この利用形態や変形例としては、例えば、次の(a)~(c)のようなものがある。

#### 【0194】

(a) LEDが光源として用いられる発光素子に適用した場合について説明したが、本発明はこれに限らず、他の被駆動素子(例えば、有機EL素子等)への電圧印加制御を行う場合にも適用可能である。例えば、有機EL素子のアレイで構成される有機ELヘッドを供えたプリンタにおいて利用することができる。

#### 【0195】

(b) 本発明は、2端子構造を備えたLED等の被駆動素子に限らず、3端子構造を備えた発光サイリスタの他、第1と第2の2個のゲート端子を備えた4端子サイリスタSCS(Silicon Semiconductor Controlled Switch)を駆動する場合にも適用可能である。又、EEPROM60,60Bは、他の不揮発性メモリに置換してもよい。

#### 【0196】

(c) 本発明の趣旨及び技術思想を考察して明らかなように、本発明は同一構成要素の連続的配置からなる被駆動素子列のドライバに限定されるものではなく、複数若しくは単数の駆動端子出力を備えた任意形状のICチップや、これらを搭載してなるユニット装置等に広く応用することが可能である。

#### 【符号の説明】

#### 【0197】

- |    |        |

|----|--------|

| 1  | 画像形成装置 |

| 13 | LEDヘッド |

10

20

30

40

50

6 0 , 6 0 B                E E P R O M

7 0 , 7 0 A , 7 0 B      基準電圧発生回路

1 0 0 , 1 0 0 B , 1 0 0 - 1 , 1 0 0 - 1 B , 1 0 0 - 2 , 1 0 0 - 2 B

ドライバ I C

1 1 0                シフトレジスタ

1 2 0                セレクタ

1 3 0                ラッチ回路部

1 4 1 , 1 4 2      制御回路

1 5 0                メモリ回路部

1 6 0                マルチプレクサ部

1 7 0                制御電圧発生回路

1 8 0                ドライバ部

2 0 0 , 2 0 0 - 1 , 2 0 0 - 2      L E D アレイ

3 0 0 - 1 , 3 0 0 - 1 A ~ 3 0 0 - 1 C , 3 0 0 - 2 , 3 0 0 - 2 A ~ 3 0 0 - 2 C

メモリセル回路

10

【図1】

【図2】

【図3】

【図4】

【図5】

【図7】

【図8】

【図9】

【図10】

【図11】

図5中の制御電圧発生回路

【図12】

図1中の基準電圧発生回路

【図13】

【図14】

本発明の実施例1の補正データ転送処理とその後に行われる印刷データ転送

図14のA部とB部の詳細

図14のC部とD部の詳細

図14のG部とH部の詳細

【図 1 5】

【図 1 6】

【図 19】

【図 20】

【図 21】

図20中のEEPROMの構成を従来構成と対して示す回路図

【図 22】

図20中の基準電圧発生回路

【図 2 3】

本発明の実施例2の補正データ転送処理ヒスタンバイ状態の設定シーケンス

---

フロントページの続き

F ターム(参考) 2C162 AE03 AE21 AE28 AE40 AE47 FA04 FA16 FA17

5C051 AA02 CA08 DA03 DB02 DB08 DB29 DC02 DC03 DC05 DE03

DE12 DE30 EA01