(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6649890号

(P6649890)

(45) 発行日 令和2年2月19日(2020.2.19)

(24) 登録日 令和2年1月21日(2020.1.21)

|                        |             |

|------------------------|-------------|

| (51) Int.Cl.           | F 1         |

| HO1L 21/8234 (2006.01) | HO1L 27/088 |

| HO1L 27/088 (2006.01)  | HO2M 3/155  |

| HO2M 3/155 (2006.01)   | HO2M 7/21   |

| HO2M 7/21 (2006.01)    | HO1L 29/78  |

| HO1L 21/336 (2006.01)  | HO1L 29/78  |

請求項の数 14 (全 9 頁) 最終頁に続く

|                    |                               |                                            |

|--------------------|-------------------------------|--------------------------------------------|

| (21) 出願番号          | 特願2016-549475 (P2016-549475)  | (73) 特許権者 390020248                        |

| (86) (22) 出願日      | 平成27年1月30日 (2015.1.30)        | 日本テキサス・インスツルメンツ合同会社                        |

| (65) 公表番号          | 特表2017-510062 (P2017-510062A) | 東京都新宿区西新宿六丁目24番1号                          |

| (43) 公表日           | 平成29年4月6日 (2017.4.6)          | (73) 特許権者 507107291                        |

| (86) 國際出願番号        | PCT/US2015/013989             | テキサス インスツルメンツ インコーポ<br>レイテッド               |

| (87) 國際公開番号        | W02015/117038                 | アメリカ合衆国 テキサス州 75265                        |

| (87) 國際公開日         | 平成27年8月6日 (2015.8.6)          | -5474 ダラス メイル ステイショ<br>ン 3999 ピーオーボックス 655 |

| 審査請求日              | 平成30年1月23日 (2018.1.23)        | 474                                        |

| (31) 優先権主張番号       | 14/608,391                    | (74) 上記1名の代理人 100098497                    |

| (32) 優先日           | 平成27年1月29日 (2015.1.29)        | 弁理士 片寄 恒三                                  |

| (33) 優先権主張国・地域又は機関 | 米国(US)                        |                                            |

| (31) 優先権主張番号       | 61/933,717                    |                                            |

| (32) 優先日           | 平成26年1月30日 (2014.1.30)        |                                            |

| (33) 優先権主張国・地域又は機関 | 米国(US)                        |                                            |

最終頁に続く

(54) 【発明の名称】バックコンバータのためのモノリシックに集積されたトランジスタ

## (57) 【特許請求の範囲】

## 【請求項1】

集積回路であつて、

第1の面と前記第1の面と対向する第1の面とを有する基板と、

横方向拡散された金属酸化物半導体(LDMOS)トランジスタを含むハイサイドトランジスタと、

前記基板の第1の面に沿ったドレインと、前記基板の第2の面に沿ったソースと、前記基板の第1の面と第2の面との間の垂直区分に沿ったチャネル領域とを含むローサイドトランジスタと、

前記ハイサイドトランジスタと前記ローサイドトランジスタのソースとの間に位置するnドープされたウェルと、

前記ローサイドトランジスタのドレインと前記ハイサイドトランジスタのソースとをスイッチノードで結合する金属層と、

を含む、集積回路。

## 【請求項2】

請求項1に記載の集積回路であつて、

前記ローサイドトランジスタのドレインが前記基板の第1の面に沿ったLDD領域を含む、集積回路。

## 【請求項3】

請求項2に記載の集積回路であつて、

10

20

前記基板の第1の面から前記基板の中に延在して前記LDD領域と前記nドープされたウェルとの間に介在するフィールドプレートを更に含む、集積回路。

**【請求項4】**

請求項1に記載の集積回路であって、

前記LDMOSトランジスタが、前記nドープされたウェル内のpドープされた領域と、前記pドープされた領域内のnドープされたソース領域とを含む、集積回路。

**【請求項5】**

請求項4に記載の集積回路であって、

前記pドープされた領域と前記nドープされたウェルと前記基板とが、前記ハイサイドトランジスタのソースと前記ローサイドトランジスタのソースとの間にp-n-p構造を形成する、集積回路。

10

**【請求項6】**

請求項1に記載の集積回路であって、

前記nドープされたウェルと前記基板の第2の面との間に分離層を更に含む、集積回路。

。

**【請求項7】**

請求項1に記載の集積回路であって、

前記金属層を前記ローサイドトランジスタのドレインに接続する第1のビアと、

前記金属層を前記ハイサイドトランジスタのソースに接続する第2のビアと、

を更に含む、集積回路。

20

**【請求項8】**

バックコンバータであって、

集積回路であって、

第1の面と前記第1の面と対向する第1の面とを有する基板と、

横方向拡散された金属酸化物半導体(LDMOS)トランジスタを含むハイサイドトランジスタと、

前記基板の第1の面に沿ったドレインと、前記基板の第2の面に沿ったソースと、前記基板の第1の面と第2の面との間の垂直区分に沿ったチャネル領域とを含むローサイドトランジスタと、

前記ハイサイドトランジスタと前記ローサイドトランジスタのソースとの間に位置するnドープされたウェルと、

前記ローサイドトランジスタのドレインと前記ハイサイドトランジスタのソースとをスイッチノードで結合する金属層と、

を含む、

前記集積回路を含む、バックコンバータ。

30

**【請求項9】**

請求項8に記載のバックコンバータであって、

前記ローサイドトランジスタのドレインが前記基板の第1の面に沿ったLDD領域を含む、バックコンバータ。

**【請求項10】**

請求項9に記載のバックコンバータであって、

前記集積回路が、前記基板の第1の面から前記基板の中に延在して前記LDD領域と前記nドープされたウェルとの間に介在するフィールドプレートを更に含む、バックコンバータ。

40

**【請求項11】**

請求項8に記載のバックコンバータであって、

前記LDMOSトランジスタが、前記nドープされたウェル内のpドープされた領域と、前記pドープされた領域内のnドープされたソース領域とを含む、バックコンバータ。

**【請求項12】**

請求項11に記載のバックコンバータであって、

50

前記 p ドープされた領域と前記 n ドープされたウェルと前記基板とが、前記ハイサイドトランジスタのソースと前記ローサイドトランジスタのソースとの間に p - n - p 構造を形成する、バックコンバータ。

**【請求項 13】**

請求項 8 に記載のバックコンバータであって、

前記集積回路が、前記 n ドープされたウェルと前記基板の第 2 の面との間に分離層を更に含む、バックコンバータ。

**【請求項 14】**

請求項 8 に記載のバックコンバータであって、

前記集積回路が、前記金属層を前記ローサイドトランジスタのドレインに接続する第 1 のビアと、前記金属層を前記ハイサイドトランジスタのソースに接続する第 2 のビアとを更に含む、バックコンバータ。

**【発明の詳細な説明】**

**【背景技術】**

**【0001】**

同期バック電圧コンバータは、ポータブルコンピュータ、サーバー、テレコミュニケーションデバイス、コンピューティング用途、及び種々のその他のポータブルシステムのための電源において広く用いられる。残念なことに、多くのバックコンバータは、それらが高スイッチング周波数で高電流レベルを扱うことが可能であり、且つ、一層低いスイッチング効率でも高電流レベルを扱い得るように、かなり大きい。

10

**【発明の概要】**

**【0002】**

記載される例において、バックコンバータにおいて用いるための集積半導体トランジスタチップがハイサイドトランジスタを含み、ハイサイドトランジスタは、集積半導体トランジスタチップ上に形成され、横方向拡散された金属酸化物半導体 (LDMOS) トランジスタを含む。また、集積半導体トランジスタチップはローサイドトランジスタを含み、ローサイドトランジスタは、集積半導体トランジスタチップ上に形成され、ソースダウン金属酸化物半導体電界効果トランジスタ (MOSFET) を含む。更に、集積半導体トランジスタチップは、ローサイドトランジスタのためのソースとして用いるための基板と、ハイサイドトランジスタのローサイドトランジスタのソースからの隔離のための n ドープされたウェルとを含む。

20

**【図面の簡単な説明】**

**【0003】**

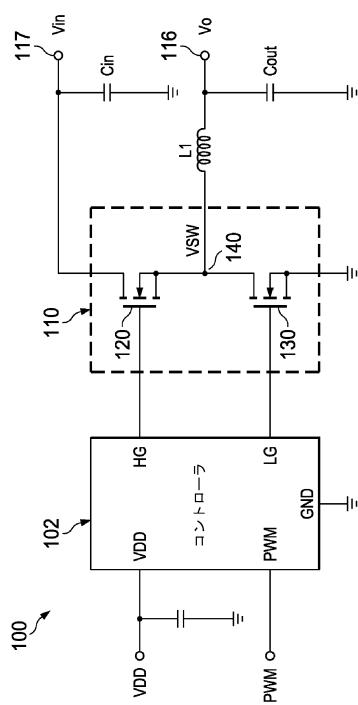

【図 1】 様々な実装に従った、一対のモノシリックに形成されたトランジスタを含むバックコンバータの概略である。

**【0004】**

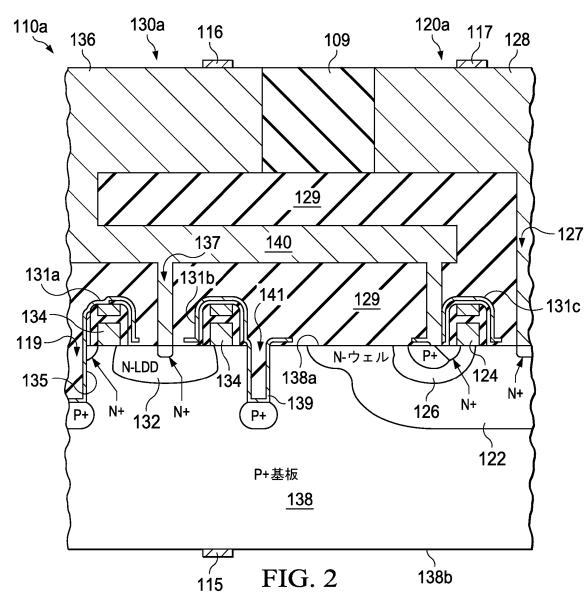

【図 2】 図 1 のモノシリックに形成されたトランジスタの実装の一例を示す。

**【0005】**

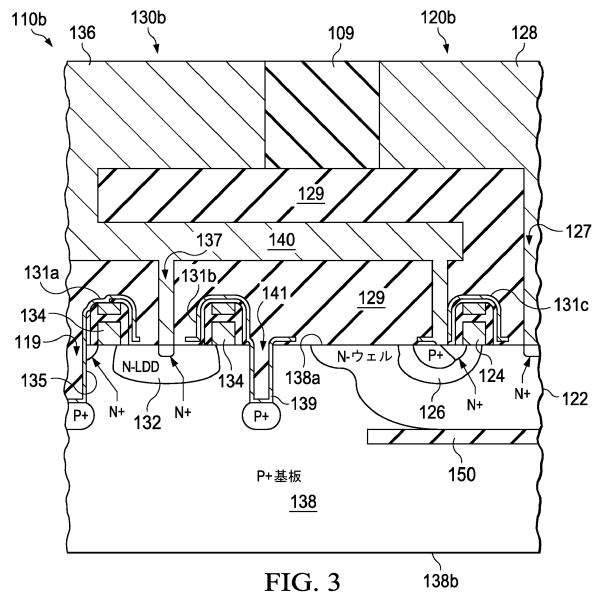

【図 3】 付加的な絶縁層を含む、図 1 のモノシリックに形成されたトランジスタの実装を示す別の例である。

30

**【0006】**

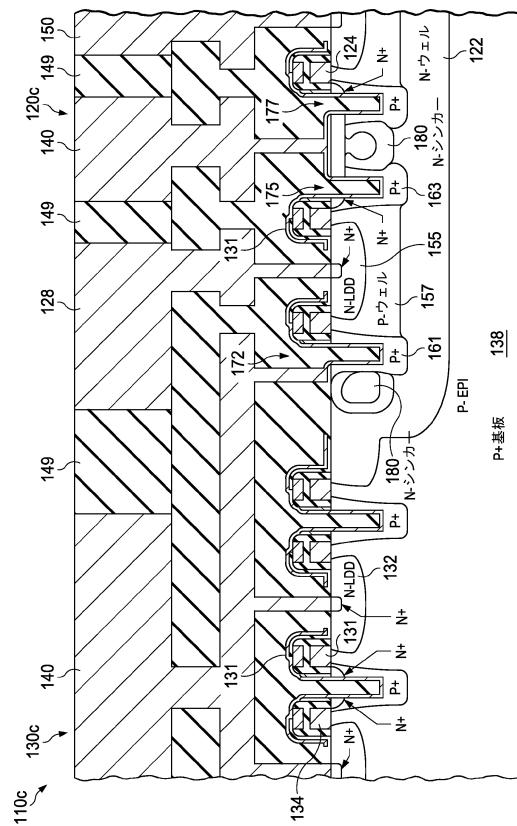

【図 4】 図 1 のモノシリックに形成されたトランジスタの実装の更に別の例を示す。

**【発明を実施するための形態】**

**【0007】**

高電流処理能力を備えた既存の同期バックコンバータは、ディスクリートパワー金属酸化物半導体電界効果トランジスタ (MOSFET) を用いる。一つのトランジスタはローサイドトランジスタと呼ばれ、別のトランジスタはハイサイドトランジスタと呼ばれる。このようなディスクリート解決策は、大きな寄生インダクタンス及び抵抗を導入し得、これは、一層低い変換効率につながる。幾つかのコンバータはパッケージ集積MOSFET を用いるが、このような解決策ではパッケージコストが一層高くなり得る。他の解決策は

40

50

、モノリシックに集積されたトランジスタをバックコンバータに用いるが、ローサイド及びハイサイドトランジスタ両方として、横方向拡散された金属酸化物半導体（LDMOS）トランジスタを用いる。横方向電流フローと金属の拡がり抵抗の制約のため、許容可能な程度に高い変換効率で充分に高い電流処理能力をこのような解決策が達成することは困難となり得る。本明細書に記載される実施例はこれらの問題に対処する。

#### 【0008】

図1は、本明細書に記載される様々な実装に従ったバックコンバータ100の一例を示す。図示するように、コンバータ100は、コントローラ102、一对のトランジスタ110、インダクタL1、及び出力キャパシタCoutを含む。付加的な構成要素も可能である。例えば、入力キャパシタCin、及びコントローラ102へのVDD入力上のキャパシタが示されている。入力電圧VinがVin入力端子に提供され、パルス幅変調された信号が、コントローラのPWM入力に提供される。PWM入力信号は、出力電圧Voの電圧レベルを制御するためコントローラ102により用いられる。PWM入力信号を調節することにより、異なる出力電圧レベルが入力電圧Vinに基づいて可能とされる。従って、Vin入力電圧は、異なる（典型的に、一層低い）出力電圧Voに変換される。

#### 【0009】

トランジスタ100はトランジスタ対110を含み、トランジスタ対110は、「ハイサイド」トランジスタ120（「制御FET」と称されることもある）及び「ローサイド」トランジスタ130（「同期FET」と称されることもある）を含む。トランジスタ120、130は、スイッチとして機能し、コントローラ102による制御下でオン及びオフにされる。コントローラは、ハイサイドトランジスタ120のゲートを制御するハイサイドゲート制御出力信号（HG）、及びローサイドトランジスタ130のゲートを制御するローサイドゲート制御出力信号（LG）をアサートする。コントローラは、PWM入力信号のレベルに従って、ハイ及びローサイドトランジスタ120、130の各々を相互にオン及びオフにする。これら2つのトランジスタ120、130は、概して両方同時にオンにされることではなく、従って、一つがオンである間、他方がオフであり、その逆も同様であるが、両方のトランジスタは同時にオフにされ得る。トランジスタのデューティサイクルは、出力電圧Voの出力電圧レベルを指示する。

#### 【0010】

本明細書において提供される様々な例に従って、トランジスタ対110（ハイサイドトランジスタ120及びローサイドトランジスタ130を含む）は、单一半導体基板上に形成される。従って、トランジスタ120、130は、单一の半導体チップ上にモノリシックに集積される。図2は、バックコンバータ100に用いるためのモノリシックに集積されたトランジスタ対110aの一例を示す。ローサイドトランジスタ130は半導体構造の左側に示されており、ハイサイドトランジスタ120は半導体構造の右側に示されている。エッジ領域109（例えば、誘電体）が、2つのトランジスタ120、130を分離する。ローサイドトランジスタ130は、ソースダウンMOSFETとして実装され得る。ハイサイドトランジスタ120は、LDMOSトランジスタとして実装され得る。

#### 【0011】

この例では、ローサイドトランジスタ130はnドープされたドレインを含み、nドープされたドレインは、必要とされる降伏電圧を維持するために充分に長い軽くドープされたドレイン領域（N-LDD）132、基板138によって形成されるソース、及びゲート134を含む。N-LDD132への電気的接続が金属136を通して提供され、これがバイア137を下へN-LDD132に提供される。ソースは、P+ドープされた基板138により提供され、そのドーピング濃度は概して、頂部表面138aから、反対の底部表面138bに向かって増大する。ゲート134及びN-LDD132はシリコン基板138の一つの側に提供され、ソース接続115は基板138上のシリコンの裏側にある。

#### 【0012】

ハイサイドトランジスタ120は、nドープされたウェル領域（N-ウェル）122に

10

20

30

40

50

形成されるドレイン、pドープされた(P+)領域126に形成されるソース、及びゲート124を含む。N-ウェル122(ドレイン)への電気的接続が金属128により提供され、これがバイア127を下へN-ウェル/ドレインに提供される。そのため、ハイサイドトランジスタ120のソースはP+領域126の一部として形成され、ドレインはN-ウェル122に形成される。ローサイドトランジスタ130のN-LDD132におけるドレインは、ハイサイドトランジスタ120のP+領域126におけるソースに金属を介して電気的に接続され、これがスイッチノードVSW140を形成する。領域129は誘電性材料である。ハイサイドトランジスタ120のN-ウェル122(ドレイン)はバックコンバータ(図1も参照)の入力ノードVinを形成し、バックコンバータへの接続が電気的コンタクト117において成され得る。バックコンバータの出力ノードVoは、インダクタL1(図1に図示するように)を介してVSWノード140によりコンタクト116を介して提供される。

#### 【0013】

図2の例(及び、図3及び図4)におけるローサイドトランジスタ130はソースダウンMOSFETであり、そのため、電流は概して、構造をN-LDD132(ドレイン)からゲート制御チャネルを介して垂直に下に、そして基板138(ソース)を介して下に、及び、構造の裏側(即ち、基板138のN-LDD132とは反対側)を出て流れる。この集積トランジスタ対110におけるハイサイドトランジスタ120は、LD MOSトランジスタであり、電流がVinノードからN-ウェル122におけるドレインへのバイア127を下方に、デバイスに形成されるチャネル(具体的には図示せず)を横切ってP+領域126(ソース)へ、そして金属VSWノード140を横切ってローサイドトランジスタ130のN-LDD領域132のドレインへ流れる。

#### 【0014】

ハイサイドトランジスタ120とローサイドトランジスタ130との間の隔離が、少なくとも部分的に、N-ウェル122により提供され、N-ウェル122は、基板138とハイサイドトランジスタのソースとの間に形成される。N-ウェル122及びP+領域126はPN接合を形成し、これは、nドープされたウェル(N-ウェル122)への入力電圧Vinの印加に起因して逆バイアスされる。逆バイアスされたPN接合として、電流はN-ウェル122を介してハイサイドトランジスタ120のP+領域126から、ローサイドトランジスタ130のソースでもある基板138へ流れることができない。そのため、2つのトランジスタ120、130のソースは、互いから隔離される。

#### 【0015】

図2の例はまた、種々のゲート134及び124の上に形成されるフィールドプレート131a、131b、及び131cを含む。フィールドプレート131a～cは、金属であり、接地された基板138に接続される。フィールドプレート131a～cは、トランジスタゲートに対して電気的遮蔽を提供する。フィールドプレート131aは、トレチ119内に提供されるポイント135で基板に接続される。フィールドプレート131bは、トランジスタ間のエッジ領域における基板に形成されるトレチ141内の基板138に接続される。フィールドプレート131a及びbの金属は、接地された基板138との充分なコンタクトエリアを介して良好に接地される。トレチ139の深さは、改善された接地性能のために基板の一層高いドープされたエリアへのコンタクトポイントを提供する。ハイサイドゲート124はまた、金属VSWノード140の一部であるフィールドプレート131cにより遮蔽される。

#### 【0016】

図3は、図2のものに類似して、モノリシックに集積されたトランジスタ対100bを提供する。図2及び図3の構造間の違いは、図3の構造が絶縁層150を含むという点である。様々な実装において、絶縁層150は、ハイサイドトランジスタ120のN-ウェル122(ドレイン)と基板138の少なくとも一部との間に提供される。絶縁層150は、例えば、酸素注入又はその他の絶縁性ドーピングにより形成され得る。絶縁層150は、P+基板138からのハイサイドN-ウェル122の付加的な切り離しを提供し、ま

10

20

30

40

50

た、別の状況ではハイサイドP+領域126、N-ウェル122、及び基板138によって形成され得る寄生p/n/pバイポーラトランジスタを更にディセーブルするように機能する。

#### 【0017】

図4は、バックコンバータ100のためのモノシリックに形成されたトランジスタ対110cの更に別の実装を示す。図4の例において、ローサイドトランジスタ130cは、付加的なゲート(LG)が示されているが、図2及び3の実装と概して同じである。但し、ハイサイドトランジスタ120cは、前の実施例におけるものとは異なる。図4において、N-LDD領域155はハイサイドトランジスタのドレインを表し、P-ウェル157はハイサイドトランジスタのソースを表す。P-ウェル領域は、pドープされた領域であり、概して隣接のP+領域161及び163と同じ電圧電位である。P+領域161及び163は、P-ウェル157より高いドーピング濃度を有する。電圧スイッチノード(VSW)140が、N-LDD領域132(ローサイドトランジスタ130cのドレイン)をハイサイドトランジスタ130cのソースに接続する。より具体的には、VSWノード140の金属は、トレンチ172を下方に提供され、それにより、P+領域161に接する。また、P+領域163は、トレンチ175におけるVSWノード140からの金属により接触される。図4は、VSWノード140の2つの異なるインスタンスを示すよう見えるが、これら2つのVSWノード140のインスタンスは、部分的にトレンチ172、175、及び177内の金属を介して及びP+領域161、163、及びP-ウェルを介して、また、図4には示していない構造における別個の金属接続によっても、共に接続される。同様に、図4に示すVinノード128の2つのインスタンスは、図4において金属(図示せず)により共に電気的に接続される。図4における領域149は、Voutノード140からVinノード128を電気的に隔離するための誘電性材料を表す。

#### 【0018】

図4の構造は、ハイサイドトランジスタ120c及びローサイドトランジスタ130cとの間の改善された隔離のためにN-ウェル122内のP-ウェル157を含む。また、Vout(VSWノード140)からN-ウェル122への低抵抗経路を提供するためハイサイドトランジスタ120cとともに個別のN-シンカー180が含まれる。N-シンカーは、重くnドープされた領域であり、N-ウェル電位が、電流フローに起因して構造を水平方向に介する最小電圧変動を有するVout(VSW)電位であることを確実にすることを助ける。

#### 【0019】

図2及び図3の構造の場合とは異なり、図4の構造におけるN-ウェル122は、ハイサイドトランジスタのドレインを表わさない。しかし、前述の構造と同様に、図4のN-ウェル122は、ローサイドトランジスタ130からハイサイドトランジスタ120を隔離することを助ける。

#### 【0020】

上述したように、図4における種々のゲート134及び124は、その金属が種々のトレンチにおけるP+領域と接する、フィールドプレート131で遮蔽される。

#### 【0021】

本明細書に記載される実施例は概して、他の解決策が達成し得るより小さな寄生インダクタンス及び高い変換効率を達成する。バックコンバータが一対のディスクリートパワートランジスタにより構成される場合、トランジスタパッケージング及び印刷回路基板(PCB)トレースに関連付けられる寄生ソースインダクタンスは、コンバータのスイッチング性能及びコスト付加的な電力損失に影響を与える。上記の開示された例において、ローサイドトランジスタ130のN-LDD132におけるドレインは、金属を介して直接的にハイサイドトランジスタ120のP+領域126におけるソースに電気的に接続される。(別の状況ではディスクリートトランジスタ実装において存在し得るトランジスタパッケージング及びPCBトレースに関連付けられる)ハイサイドトランジスタの寄生ソースインダクタンスが、回路から取り除かれる。従って、上述の付加的な電力損失が回避さ

10

20

30

40

50

れる。

【0022】

本発明の特許請求の範囲内で、説明した例示の実施例に変形が成され得、多くの他の実施例が可能である。

【図1】

FIG. 1

【図2】

FIG. 2

【図3】

FIG. 3

【 図 4 】

FIG. 4

---

フロントページの続き

(51)Int.Cl. F I

H 01 L 29/78 (2006.01) H 01 L 27/06 102Z

H 01 L 27/06 (2006.01)

(72)発明者 ジュン ワン

アメリカ合衆国 18055 ペルシルベニア州 ヘラータウン, マティス ストリート 19

82

(72)発明者 フランク バイオッキ

アメリカ合衆国 18104 ペルシルベニア州 アレンタウン, ドーセット ロード 732

(72)発明者 ハイアン リン

アメリカ合衆国 18020 ペルシルベニア州 ベスレヘム, ブリークネス プレース 50

19

審査官 辻 勇貴

(56)参考文献 米国特許出願公開第2010/0155836(US, A1)

国際公開第2013/002129(WO, A1)

特開2012-238741(JP, A)

特開2005-203766(JP, A)

特開2001-250870(JP, A)

特表2006-509360(JP, A)

米国特許第7566931(US, B2)

(58)調査した分野(Int.Cl., DB名)

H 01 L 21/336

H 01 L 27/06

H 01 L 21/8234

H 01 L 27/088

H 01 L 29/78

H 02 M 3/155

H 02 M 7/21