**(12) STANDARD PATENT**

**(19) AUSTRALIAN PATENT OFFICE**

**(11) Application No. AU 2001287791 B2**

(54) Title

**Hall-effect sensor**

(51) International Patent Classification(s)

**H01L 43/06** (2006.01)

(21) Application No: **2001287791** (22) Date of Filing: **2001.08.30**

(87) WIPO No: **WO02/19442**

(30) Priority Data

(31) Number

**00 11087** (32) Date

**2000.08.30** (33) Country

**FR**

(43) Publication Date: **2002.03.13**

(43) Publication Journal Date: **2002.06.06**

(44) Accepted Journal Date: **2006.04.27**

(71) Applicant(s)

**Centre National De La Recherche Scientifique -CNRS-**

(72) Inventor(s)

**Camassel, Jean;Contreras, Sylvie;Robert, Jean-Louis;Pernot, Julien**

(74) Agent / Attorney

**Griffith Hack, 509 St Kilda Road, Melbourne, VIC, 3004**

(56) Related Art

**US 5536953**

**US 4315273**

**EP 458466**

(12) DEMANDE INTERNATIONALE PUBLIÉE EN VERTU DU TRAITÉ DE COOPÉRATION

EN MATIÈRE DE BREVETS (PCT)

(19) Organisation Mondiale de la Propriété

Intellectuelle

Bureau international

(43) Date de la publication internationale

7 mars 2002 (07.03.2002)

PCT

(10) Numéro de publication internationale

WO 02/19442 A1

(51) Classification internationale des brevets<sup>7</sup> : H01L 43/06

(21) Numéro de la demande internationale :

PCT/FR01/02703

(71) Déposant (pour tous les États désignés sauf US) :

CENTRE NATIONAL DE LA RECHERCHE SCIENTIFIQUE -CNRS- [FR/FR]; 3, rue Michel-Ange, F-75794 Paris Cedex 16 (FR).

(22) Date de dépôt international : 30 août 2001 (30.08.2001)

(25) Langue de dépôt :

français

(26) Langue de publication :

français

(30) Données relatives à la priorité :

00/11087 30 août 2000 (30.08.2000) FR

(72) Inventeurs; et

(75) Inventeurs/Déposants (pour US seulement) : ROBERT, Jean-Louis [FR/FR]; 12, impasse du Romarin, F-34920 Le Cres (FR). PERNOT, Julien [FR/FR]; 250 Route de Mende, Résidence Le Pré aux Clercs, Bâtiment Florian, F-34090 MONTPELLIER (FR). CAMASSEL, Jean [FR/FR]; 840, avenue de Rouargues, F-34980 Saint-Clément-de-Rivière (FR). CONTRERAS, Sylvie [FR/FR]; 440, impasse Chemin Vieux, F-34150 Gignac (FR).

[Suite sur la page suivante]

(54) Title: HALL-EFFECT SENSOR

(54) Titre : CAPTEUR A EFFET HALL

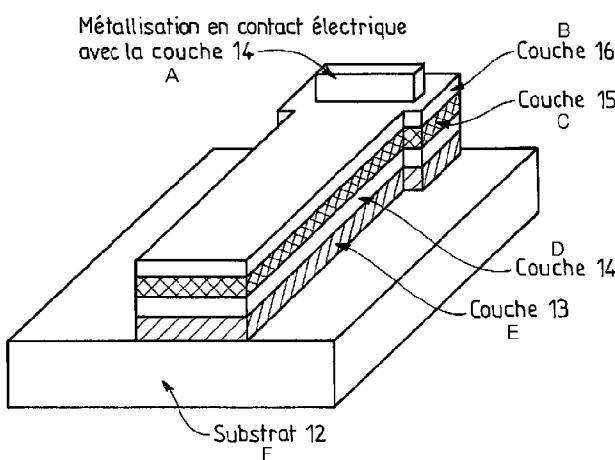

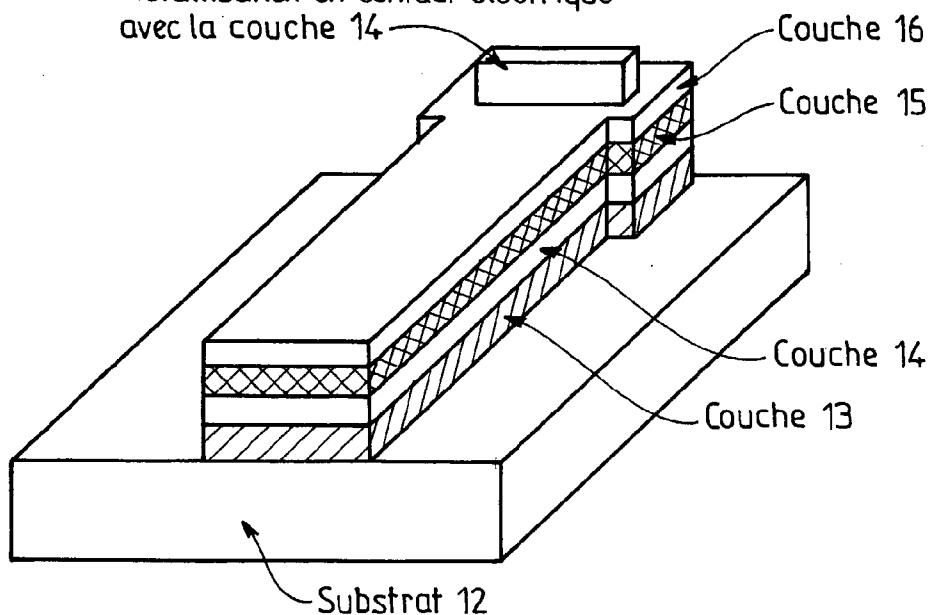

A...METAL PLATING IN CONTACT WITH LAYER 14

B...LAYER 16

C...LAYER 15

D...LAYER 14

E...LAYER 13

F...SUBSTRATE 12

G...VIEW ALONG SECTION PLANE AA' OF SAID SENSOR

(57) Abstract: The invention concerns a Hall-effect sensor consisting of a multilayer structure comprising a thin semiconductor material layer deposited on a semiconductor substrate (12), the two layers being electrically insulated with an insulation. The invention is characterised in that the substrate (12) is a n+-type semiconductor material whereon is deposited an insulating material consisting of a p-type semiconductor layer (13), and the thin active layer (14) is of the n-type doped in exhaustion mode. Preferably, the active layer consists of a silicon carbide or a gallium nitride layer.

(57) Abrégé : La présente invention concerne un capteur à effet Hall constitué par une structure multicoche comprenant une couche mince d'un matériau semi-conducteur déposé sur un substrat (12) semi-conducteur, les deux couches étant isolées électriquement par un isolant, caractérisé en ce que le substrat (12) est un matériau semi-conducteur de type n+ sur lequel est déposé un matériau d'isolation constitué par une couche semi-conductrice de p-, et en ce que la couche mince active (14) est de type n- dopé en régime d'exhaustion. De préférence, la couche active est constitué par une couche de carbure de silicium ou de niture de gallium.

WO 02/19442 A1

(74) **Mandataires :** BREESE, Pierre etc.; Breese-Majerowicz, 3, avenue de l'Opéra, F-75001 Paris (FR).

(81) **États désignés (national) :** AE, AG, AL, AM, AT, AU, AZ, BA, BB, BG, BR, BY, BZ, CA, CH, CN, CO, CR, CU, CZ, DE, DK, DM, DZ, EC, EE, ES, FI, GB, GD, GE, GI, GM, HR, HU, ID, IL, IN, IS, JP, KE, KG, KP, KR, KZ, LC, LK, LR, LS, LT, LU, LV, MA, MD, MG, MK, MN, MW, MX, MZ, NO, NZ, PII, PL, PT, RO, RU, SD, SE, SG, SI, SK, SL, TJ, TM, TR, TT, TZ, UA, UG, US, UZ, VN, YU, ZA, ZW.

(84) **États désignés (régional) :** brevet ARIPO (GII, GM, KE, LS, MW, MZ, SD, SL, SZ, TZ, UG, ZW), brevet eurasien (AM, AZ, BY, KG, KZ, MD, RU, TJ, TM), brevet européen

(AT, BE, CH, CY, DE, DK, ES, FI, FR, GB, GR, IE, IT, LU, MC, NL, PT, SE, TR), brevet OAPI (BF, BJ, CF, CG, CI, CM, GA, GN, GQ, GW, ML, MR, NE, SN, TD, TG).

**Publiée :**

- avec rapport de recherche internationale

- avant l'expiration du délai prévu pour la modification des revendications, sera republiée si des modifications sont reçues

*En ce qui concerne les codes à deux lettres et autres abréviations, se référer aux "Notes explicatives relatives aux codes et abréviations" figurant au début de chaque numéro ordinaire de la Gazette du PCT.*

## HALL EFFECT SENSOR

The present invention pertains to the field of Hall sensors intended for the quantitative measurement of magnetic fields.

The general principle of Hall effect sensors is well known. In particular, sensors are known which are constituted by a multilayer structure comprising a thin layer of a semiconductor material deposited on a substrate which is itself a semiconductor, with the two layers being electrically isolated from each other.

As an example, European patent EP 572,298 describes a "two-dimensional electron gas" Hall effect sensor comprising, on an isolating substrate, a quantum well structure, a carrier supply layer adjacent to the quantum well structure, of a thickness less than 250 angstroms and possessing a surface density of donors integrated over the entire surface of the supply layer of carriers lower than a threshold value, an isolating burial layer deposited on the carrier supply layer, possessing an energy conduction band greater than the fermi energy of the sensor and of a thickness greater than 200 angstroms.

European patent EP 458,466 describes a Hall effect device comprising a substrate, an active layer formed by a diamond semiconductor deposited on the substrate, a pair of electrodes deposited on the opposite sides of the active layer, for introducing a current in the active layer in one direction and another pair of electrodes deposited on the other opposite sides of the active layer for detecting a tension or a tension component which is induced in a direction which is generally orthogonal to the direction of the current.

US patent 5,536,953 describes a broad-band semiconductor comprising multiple dopants at low concentrations.

The problem that characterizes the sensors is that of the operating domain. In fact, the metrological performances of the sensors degrade (decrease in sensitivity, nonlinearity, etc.) at temperatures higher than 200°C.

This degradation is linked to the performance of the structure (deficiencies in the electric isolation of the active/substrate layer) and/or the active layer (change in the conduction mechanisms, etc.).

The goal of examples of the present invention is to propose a Hall effect sensor 5 exhibiting a low sensitivity to temperature, typically of less than 250 ppm/°C for operating temperatures greater than 200°C, and presenting a high Hall KH coefficient on the order of several hundreds of volt/ampere/tesla. KH is inversely proportional to the surface carrier density and the electron charge.

According to one aspect of the present invention there is provided a Hall effect 10 sensor with a multilayer structure comprising a thin active layer deposited on a substrate, said substrate being of a monocrystalline silicon carbide (SiC) and wherein the thin active layer is made of a semiconductor material of type n<sup>-</sup> or p<sup>-</sup> doped with a doping level lower than  $5 \cdot 10^{15}$  per cm<sup>3</sup> in an exhaustion regime.

The active layer is preferably covered by an insulator (for example, silicon oxide or 15 nitride) or by a passivation insulator. The doping level of the active layer is selected such that the sensor operates in exhaustion regime (total ionization of the dopants) over the entire temperature range corresponding to use.

According to a first mode of implementation, the active layer and/or the insulating layer and/or the substrate are constituted by a hexagonal silicon carbide layer. The 20 doping level of the n<sup>-</sup> active layer is advantageously lower than  $5 \cdot 10^{15}$  per cm<sup>3</sup>.

According to a variant, the active layer is a cubic silicon carbide layer. According to a variant, the active layer is a layer of nitrides based on GaN and/or its alloys.

According to a variant, the active layer is made from a material with a weaker forbidden band than that of the above materials (the case, e.g., of silicon).

25 The temperature range corresponding to the exhaustion regime is, in this case, shifted toward low temperatures (below 200°C) and is limited toward high temperatures (> 200°C). The sensitivity to temperature can be higher than in the preceding cases and

not constant over the entire temperature interval corresponding to the exhaustion regime and to use.

The materials forming the substrate and the active layer are preferably of the same substance with different dopings.

5 According to a variant, the active layer can be transferred onto a substrate of a different substance. It can be adhered by molecular adhesion.

According to a particular variant, the Hall effect sensor is made by a multilayer structure comprising a thin active layer of a semiconductor material deposited on a semiconductor substrate, the two layers being isolated electrically by an insulating 10 layer. The overall structure is a type  $n^+$  semiconductor material on which is deposited an insulating material constituted by a type  $p^-$  semiconductor material and in that the thin active layer is of type  $n^-$ .

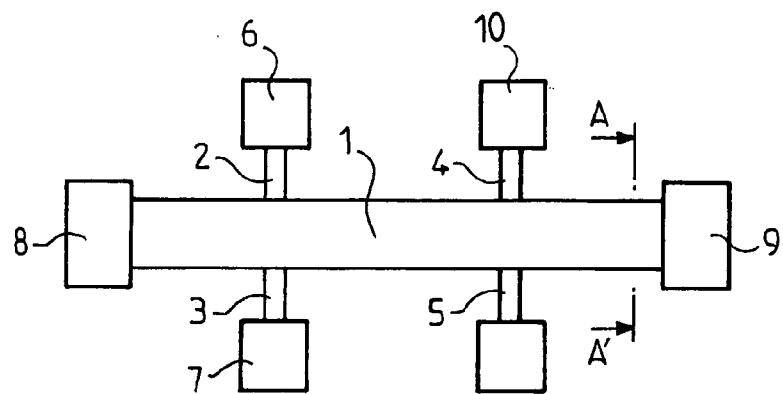

According to a particular mode of implementation, the sensor is constituted by a bar presenting a body extended by two pairs of lateral arms, with the body presenting at 15 each of its ends an electrode for electric power, two opposed lateral arms comprising electrodes for acquisition of the Hall signal and two adjacent arms presenting electrodes for measuring the resistance.

Better comprehension of the invention will be obtained from the description below of a nonlimitative example of an embodiment which refers to the attached drawings in 20 which:

- figure 1 represents a top view of a sensor according to an example of an embodiment of the invention,

- figure 2 represents a view along a cross-sectional plane of said sensor.

The Hall sensor according to the example presents a general shape of a “cross of Lorraine” with a body (1), a first pair of lateral arms (2, 3) and a second pair of lateral 25 arms (4, 5) with the unit being designed to measure a magnetic field perpendicular to the plane formed by the median axis of the body (1) and by the median axis of at least one pair of arms (e.g., 2, 3).

One of the pairs of arms (2, 3) presents electrodes (6, 7) for acquisition of the Hall signal.

The body also presents two electrodes (8, 9) positioned at opposite ends for powering with an excitation tension or a current feed. Moreover, two adjacent arms (2, 5 4) present electrodes (6, 10) for measuring the resistance of the structure, a measurement which allows deduction of the temperature of the Hall sensor.

Figure 2 represents a view along a cross-sectional plane. The Hall sensor according to a first mode of implementation of the invention is designed to present an impedance of several kilo-ohms, typically on the order of 10 kilo-ohms, a thermal sensitivity on the 10 order of 200 ppm/°C and a KH factor on the order of multiple hundreds of volt/ampere/tesla.

In order to attain these performance levels, the Hall sensor is made by a substrate (12) made of an n<sup>+</sup> doped semiconductor. The semiconductor is monocrystalline of the silicon carbide (SiC) type, preferably of the 4H-SiC type.

15 An insulating layer (13) is deposited on this substrate, e.g., by epitaxial growth. This layer is constituted by a semiconductor material identical to that of the p<sup>+</sup> doped substrate.

On this insulating layer (13) is deposited a thin active layer (14) constituted by an n<sup>-</sup> 20 doped semiconductor. The semiconductor is monocrystalline of the silicon carbide SiC type, of type 4H-SiC.

The active layer is itself optionally covered by an insulating layer (15) and a passivation layer (16), e.g., of silicon oxide (SiO<sub>2</sub>).

The sensor can employ large-gap semiconductors working in exhaustion regime.

According to a variant, the active layer can be deposited in the form of nitrides 25 (GaN and/or alloys). The substrate can be sapphire on which is deposited a buffer layer, or silicon carbide with a buffer layer, or a nitride or any other substrate.

It is to be understood that, if any prior art publication is referred to herein, such reference does not constitute an admission that the publication forms a part of the common general knowledge in the art, in Australia or any other country.

In the claims which follow and in the preceding description, except where the context requires otherwise due to express language or necessary implication, the word "comprise" or variations such as "comprises" or "comprising" is used in an inclusive sense, i.e. to specify the presence of the stated features but not to preclude the presence or addition of further features in various embodiments of the invention.

## CLAIMS

1. A Hall effect sensor with a multilayer structure comprising a thin active layer deposited on a substrate, said substrate being of a monocrystalline silicon carbide (SiC) and wherein the thin active layer is made of a semiconductor material of type n<sup>-</sup> or p<sup>-</sup> 5 doped with a doping level lower than 5·10<sup>15</sup> per cm<sup>3</sup> in an exhaustion regime.

2. A Hall effect sensor according to claim 1, wherein the type n<sup>-</sup> active layer (14) is deposited on a type p<sup>-</sup> electric insulating layer in order to electrically isolate the active layer from the substrate.

3. A Hall effect sensor according to claim 1 or 2, wherein the type n<sup>-</sup> active layer is 10 covered by a thermal oxide and by a passivation insulator.

4. A Hall effect sensor according to any one of the preceding claims, wherein the active layer is a layer of hexagonal silicon carbide.

5. A Hall effect sensor according to any one of the preceding claims, wherein the insulating layer is a layer of type p<sup>-</sup> hexagonal silicon carbide.

- 15 6. A Hall effect sensor according to any one of the preceding claims, wherein the substrate is a layer of hexagonal silicon carbide.

7. A Hall effect sensor according to any one of the preceding claims, wherein the active layer is a layer of cubic silicon carbide.

8. A Hall effect sensor according to any one of the preceding claims, wherein the 20 active layer is a layer of nitrides based on GaN and/or its alloys.

9. A Hall effect sensor according to any one of the preceding claims, wherein the active layer is a layer of silicon.

10. A Hall effect sensor according to any one of the preceding claims, wherein the semiconductor materials forming the substrate, the insulating layer and the active layer are made of the same substance.

11. A Hall effect sensor according to any one of claims 1 to 8, wherein the active 5 layer is mounted on a support [insulating layer or buffer layer and substrate] and in that the substrate and the active layer are made of different substances.

12. A Hall effect sensor according to any one of the preceding claims, constituted by a bar presenting a body extended by two pairs of lateral arms, with the body presenting at each of its ends an electrode for electric power, two opposed lateral arms 10 comprising electrodes for acquisition of the Hall signal and two adjacent arms presenting electrodes for measuring the resistance.

13. A Hall effect sensor as claimed in any one for the preceding claims, and substantially as herein described with reference to the accompanying drawings.

15 Dated this 24th day of March 2006

CENTRE NATIONAL DE LA RECHERCHE SCIENTIFIQUE -CNRS-

By their Patent Attorneys

GRIFFITH HACK

Fellows Institute of Patent and

20 Trade Mark Attorneys of Australia

1/1

**FIG.1** Capteur vue de dessus

Méttallisation en contact électrique

avec la couche 14

**FIG.2** Vue suivant le plan de coupe A A' dudit capteur