(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5547878号

(P5547878)

(45) 発行日 平成26年7月16日(2014.7.16)

(24) 登録日 平成26年5月23日(2014.5.23)

|               |                     |

|---------------|---------------------|

| (51) Int.Cl.  | F 1                 |

| H 01 L 21/305 | (2006.01)           |

| H 01 L 21/304 | (2006.01)           |

| H 01 L 21/027 | (2006.01)           |

| G 03 F 7/42   | (2006.01)           |

|               | HO 1 L 21/302 104 H |

|               | HO 1 L 21/302 104 C |

|               | HO 1 L 21/304 645 C |

|               | HO 1 L 21/30 572 A  |

|               | GO 3 F 7/42         |

請求項の数 4 (全 8 頁)

(21) 出願番号 特願2008-170629 (P2008-170629)

(22) 出願日 平成20年6月30日 (2008.6.30)

(65) 公開番号 特開2010-10573 (P2010-10573A)

(43) 公開日 平成22年1月14日 (2010.1.14)

審査請求日 平成23年5月11日 (2011.5.11)

前置審査

(73) 特許権者 501387839

株式会社日立ハイテクノロジーズ

東京都港区西新橋一丁目24番14号

(74) 代理人 110000442

特許業務法人 武和国際特許事務所

(72) 発明者 小野 哲郎

山口県下松市大字東豊井794番地 株式

会社 日立ハイテクノロジーズ 笠戸事業

所内

(72) 発明者 斎藤 剛

山口県下松市大字東豊井794番地 株式

会社 日立ハイテクノロジーズ 笠戸事業

所内

審査官 山本 雄一

最終頁に続く

(54) 【発明の名称】半導体加工方法

## (57) 【特許請求の範囲】

## 【請求項 1】

H f または Z r を含む絶縁膜と T i 、 T a または R u を含み前記絶縁膜上に形成された導体膜と前記導体膜上に形成されたレジストとが積層された半導体基板をプラズマを用いて加工する半導体加工方法において、

前記レジストを用いてプラズマにより前記導体膜を 65 nm 以下の寸法に加工し、

前記導体膜の加工後、前記半導体基板にバイアス電力を供給した状態のもとにおける、H<sub>2</sub> ガスと Ar ガスとの混合ガスからなり前記混合ガスの全ガス量に対する前記 Ar ガスの混合割合が 50 % を超えないプラズマにより、前記レジストの除去と、前記導体膜の側壁に生じる堆積膜の除去と、を行うことを特徴とする半導体加工方法。

10

## 【請求項 2】

請求項 1 記載の半導体加工方法において、

前記 H<sub>2</sub> ガスと Ar ガスとの混合ガスは、 CF<sub>4</sub> ガス、 CHF<sub>3</sub> ガス、 SF<sub>6</sub> ガスまたは NF<sub>3</sub> ガスがさらに混合されることを特徴とする半導体加工方法。

## 【請求項 3】

請求項 1 記載の半導体加工方法において、

前記導体膜は仕事関数制御金属からなり、前記導体膜上には W からなる電極層を備えることを特徴とする半導体加工方法。

## 【請求項 4】

請求項 1 記載の半導体加工方法において、

20

前記バイアス電力は、15W以上80W以下であることを特徴とする半導体加工方法。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体加工方法に係り、特に高誘電率絶縁膜上に金属を堆積した構造の半導体を加工する半導体加工方法に関する。

【背景技術】

【0002】

例えば、特許文献1には、半導体素子の層間絶縁膜に用いられているlow-k膜と呼ばれる誘電率が低い絶縁膜上に形成されたレジスト除去に際して、水素と希ガスの混合ガスのプラズマから取り出した水素原子あるいは水素分子の中性ラジカルを用いることが示されている。ここでは、通常の酸素プラズマを用いたレジスト除去方法ではlow-k膜が酸化等の劣化により誘電率が上昇するために、酸素を用いないでレジストを除去する方法を採用することが開示されている。また、この文献には、基板の温度を200℃から400℃に上昇させてレジスト除去速度を増加する技術、NH<sub>3</sub>プラズマあるいはCF<sub>4</sub>プラズマを照射してレジスト表面の変性層を除去する技術も開示されている。

【0003】

特許文献2には、Wなどの高融点金属電極を備えるメタルゲートと呼ばれる半導体素子において、Wの劣化を防ぎながら汚染を除去する洗浄方法が記載されている。ここでは、水素および水蒸気を含む雰囲気中でウエハを熱酸化し、その後、過酸化水素を含まない液によりウエハを洗浄する技術が開示されている。この方法ではW層が酸化されないので洗浄によりW酸化層が除去されてしまうことはない。またこの文献の0055、0056段落には素子のドライエッチング後のレジスト除去には酸素プラズマを用いることが記載されている。

【特許文献1】特開2005-268312号公報

【特許文献2】特開2005-229130号公報

【発明の開示】

【発明が解決しようとする課題】

【0004】

特許文献2に示すように、従来技術においては、メタルゲート構造の素子のレジスト除去に酸素プラズマが用いられる。しかし、素子の微細化が進み加工線幅が65nm以下の領域になると、レジスト除去時に用いる酸素により、Ti、Ta、Ruなどの金属電極の側壁が酸化されてその抵抗が増加して素子が劣化するという問題が生じる。

【0005】

素子の加工線幅が大きい場合には、前記側壁における酸化層の厚さの全体に占める割合は小さいため、前記抵抗の増大は問題とはならない。このため、従来技術では、この点に関する解決方法について言及するところはない。

【0006】

本発明は、このような問題点に鑑みてなされたもので、高誘電率絶縁膜上に金属導体を堆積した構造の半導体に対する微細加工に適した加工方法を提供するものである。

【課題を解決するための手段】

【0007】

本発明は上記課題を解決するため、次のような手段を採用した。

【0008】

HfまたはZrを含む絶縁膜とTi、TaまたはRuを含み前記絶縁膜上に形成された導体膜と前記導体膜上に形成されたレジストとが積層された半導体基板をプラズマを用いて加工する半導体加工方法において、前記レジストを用いてプラズマにより前記導体膜を65nm以下の寸法に加工し、前記導体膜の加工後、前記半導体基板にバイアス電力を供給した状態のもとにおける、H<sub>2</sub>ガスとArガスとの混合ガスからなり前記混合ガスの全ガス量に対する前記Arガスの混合割合が50%を超えないプラズマにより、前記レジス

10

20

30

40

50

トの除去と、前記導体膜の側壁に生じる堆積膜の除去と、を行う。

【発明の効果】

【0009】

本発明は、以上の構成を備えるため、高誘電率絶縁膜上に金属導体を堆積した構造の半導体において、素子を劣化させることなく微細加工を施すことができる。

【発明を実施するための最良の形態】

【0010】

以下、最良の実施形態を添付図面を参照しながら説明する。

【0011】

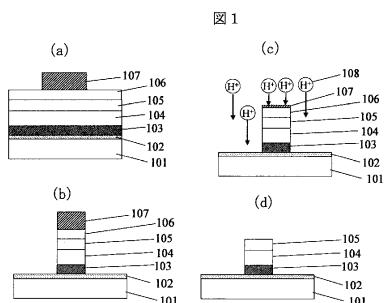

図1は、第1の実施形態にかかる半導体加工方法を説明する図であり、図1(a)は加工対象となる半導体素子の断面図である。半導体素子は、図1(a)に示すようにSi基板101、Si基板101上に順次形成した高誘電率絶縁膜としてのHfSiON膜102、仕事関数制御金属の導体膜としてのTiN膜103、電極材料としてのW膜104、キャップとしてのSiN膜105、反射防止膜106を備える。ここで、高誘電率のHfSiON膜102をFETのゲート絶縁膜(high-k膜)として利用し、TiN膜103をメタルゲートとして利用することにより、high-k膜/メタルゲート構造を備えるFETを形成することができる。10

【0012】

なお、それぞれの膜厚はHfSiON膜102が2nm、TiN膜103が10nm、W膜104が50nm、SiN膜105が50nm、反射防止膜106が80nm、レジスト107が200nmである。20

【0013】

図1(a)は、処理の初期状態を表し、リソグラフィーによりパタニングされたレジスト107が最上層にある。

【0014】

図1(b)は、レジスト107をトリミングして線幅を細らせる工程を施した後、細らせたレジスト107を用いて、反射防止膜106、SiN膜105、W膜104、TiN膜103にドライエッティングを施した後の形状を表す。

【0015】

トリミングはAr/O<sub>2</sub>混合ガスのプラズマ雰囲気で行い、SiN膜105のエッティングにはSF<sub>6</sub>/CHF<sub>3</sub>/Arの混合ガスのプラズマを用いた。またW膜104とTiNのエッティングには、SF<sub>2</sub>ガスを5ml/min、Cl<sub>2</sub>ガスを20ml/min、CHF<sub>3</sub>ガスを40ml/min、N<sub>2</sub>ガスを100ml/minの流量で供給し、圧力1Paのプラズマを用いた。30

【0016】

図1(c)は、水素プラズマによるレジスト除去工程を表している。ここでは、基板温度を30℃に設定し、H<sub>2</sub>ガスを50ml/min、N<sub>2</sub>ガスを50ml/minの流量で供給し、圧力1Paのプラズマを用いた。この工程により、レジスト107と反射防止膜106を除去することができる。

【0017】

図1(c)は、レジスト除去終了後の形状を表す図である。なお、仕事関数制御金属の導体膜103としては、TiNの外にTaN、TaSiN、Ru、RuOなどを用いることができる。

【0018】

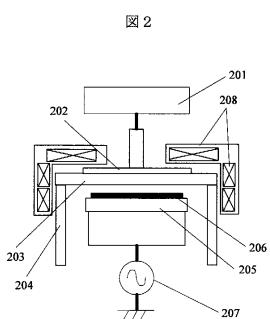

図2は、半導体素子を加工する加工装置(プラズマエッティング装置)を説明する図である。この装置は電子スピニ共鳴(ECR)方式と呼ばれる装置であり、プラズマ電源201から放出された電磁波をアンテナ202、石英などの電磁波を透過する窓203を通して真空チャンバ(減圧処理室)204内に導入する。チャンバ204内はエッティングガスが一定の圧力で保持されており、前記電磁波によりガスをプラズマ化し、反応性イオンをウェハ206に入射させることでエッティングあるいはレジスト除去作用が進行する。50

## 【0019】

ウエハ206を保持する試料台205には入射イオンを加速するためのバイアス電源207が接続されている。この装置では電磁コイル208によりチャンバ204内に磁場を発生する。プラズマ中の電子スピニ周波数と、プラズマ電源201の周波数が一致するよう磁場強度を設定すると、電力が効率よくプラズマに吸収されて、低圧にて高いプラズマ密度を維持することができる。電磁コイル208に流す電流値を変えることにより磁場強度をECRが生じるように設定することができる。なお、エッティングあるいはレジスト除去に用いる加工装置は、ECR方式に限らず、例えば誘導結合型(ICP)プラズマ処理装置などを用いることができる。

## 【0020】

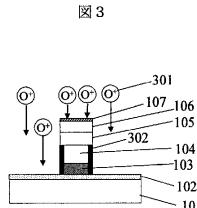

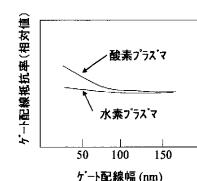

10

図3、4は本発明による効果を説明する図であり、図3は従来技術である酸素プラズマを用いたレジスト除去の様子を表す図、図4は水素プラズマおよび酸素プラズマを用いてレジストを除去した後のゲート配線の抵抗率(単位断面積あたりの抵抗)を比較して示す図である。なお、図において図1に示される部分と同一部分については同一符号を付してその説明を省略する。

## 【0021】

図3に示すように酸素プラズマ301を用いたレジスト除去では、金属の導体膜、すなわちW膜104、TiN膜103のプラズマに晒される側壁に酸化層302が生じる。このため、ゲート配線幅が100nm以下、特に65nm以下になると、図4に示すように酸化層302の影響が大きくなり、配線の抵抗率が上昇する。

20

## 【0022】

一方、酸素プラズマに代えて水素プラズマを用いると、金属の導体膜は酸化されないため、配線抵抗率の増加はほとんどない。なお、配線抵抗が増加すると素子の消費電力が増加し、また、素子の高速動作の妨げになる。

## 【0023】

基板温度は高いほどレジスト除去速度は大きくなるが、メタル材料の変質などを考慮すると、200以下が好ましい。また、30ないし100がより好ましい。

## 【0024】

このように、high-k膜およびメタル材料(メタルゲート)を備える半導体素子のレジスト除去に際して水素プラズマを用いることにより、素子(メタルゲート)の劣化を抑制することができる

30

図5、6は、第2の実施形態を説明する図である。この例では、水素プラズマによるレジスト除去に際して、シリコン基板(ウエハ)にバイアスを印加することにより処理速度を向上している。

## 【0025】

図2に示すように、プラズマエッティング装置はウエハ206に入射するイオンを加速するためのバイアス電源207を備えている。バイアス電源207の周波数は通常400KHzから20MHzくらいの高周波である。このバイアス電源によりウエハ206に入射するイオンを加速することにより、レジスト除去速度を向上できる。

## 【0026】

40

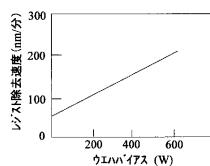

図5は、H<sub>2</sub>/Arの混合ガスプラズマ(1Pa)における、ウエハバイアス電力(400KHz)とレジスト除去速度の関係を示す図である。バイアス電力の増大に伴いレジスト除去速度が増加することが分かる。

## 【0027】

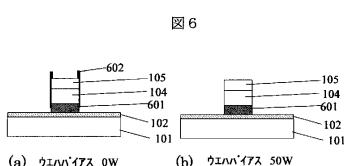

図6は、ウエハバイアス電力の有無によるゲート電極側壁の堆積物の除去性を示す図であり、図6(a)はウエハバイアスを印加しない場合、図6(b)はウエハバイアスを印加(50W)した場合を表している。

## 【0028】

メタルゲート601を形成する金属として、TaSiNなどの、ハロゲンとの化合物の蒸気圧が比較的低い材料を選択した場合は、エッティング中に電極側壁に堆積物602が生

50

じる。

#### 【0029】

ウエハバイアスを印加しないでレジスト除去を行うと、図6(a)のようにレジスト除去後に堆積物602が残ってしまう。ウエハバイアスとして50Wを印加すると、図6(b)のように堆積物602を除去することができる。これは加速されたイオンのエネルギーにより堆積物602の分解反応が促進されると同時に物理的なスパッタにより堆積物602が除去されるからである。

#### 【0030】

なお、イオンエネルギーはウエハバイアス電圧の振幅Vpp(V)にほぼ比例する。図5に示す例ではバイアス電力50Wの場合Vppは350V、バイアス電力100Wの場合Vppは600Vとなる。

10

#### 【0031】

Vppが大きいほどレジスト除去速度は大きくなるが、Vppの増加に伴いゲート絶縁膜であるHfSiON膜102およびその下層のSi基板101がイオン照射により損傷を受ける。素子特性の測定結果およびレジストの除去速度を考慮すると、バイアス電圧の振幅Vppは1500V以下が好ましい。また、500V(80W)ないし100V(15W)がより好ましい。

#### 【0032】

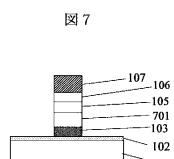

図7は、第3の実施形態を説明する図である。図7の例では、ゲート電極として、メタルゲート金属TiN膜107の上にpoly-Si膜701を堆積した電極を用いる。この電極構造によれば、poly-Si膜701は図1に示すWよりも酸化されにくいために、酸素プラズマによる劣化は比較的小さい、しかしTiN膜107の金属部分は酸化されるため、やはり素子の劣化が生じる。したがって、この構造素子においても水素プラズマによるレジスト除去は素子の特性劣化を抑える効果がある。

20

#### 【0033】

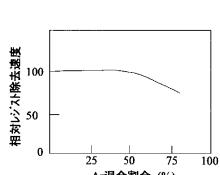

図8は、エッチングに用いるH<sub>2</sub>/Arの混合ガスにおけるArの割合とレジスト除去速度の関係を表す図である

酸素を用いないでレジストを除去するには、前記特許文献1に記載されている方法、すなわち水素原子あるいは水素分子の中性ラジカルを用いる方法がある。しかし、この方法はプラズマを用いる方法よりレジスト除去能力が低く、メタルゲート加工後のレジスト除去では、残渣が出やすくなる。

30

#### 【0034】

また、レジスト除去に用いるガスはH<sub>2</sub>、H<sub>2</sub>/N<sub>2</sub>、H<sub>2</sub>/希ガスに加えてNH<sub>3</sub>などの水素を含むガスのプラズマでも同様に効果がある。なお、水素とN<sub>2</sub>あるいは希ガスとを混合するときの混合比は主に安全性を考慮した水素の希釈である。

#### 【0035】

図8は前述のようにH<sub>2</sub>/Arの混合ガスにおけるArの割合とレジスト除去速度の関係を表す図であり、Arの割合が50%を超えるとレジスト除去速度が低下する。したがって、希ガスあるいはN<sub>2</sub>の混合割合は50%以下が好ましい。

#### 【0036】

40

なお、水素を含むガスにCF<sub>4</sub>、CHF<sub>3</sub>、NF<sub>3</sub>、SF<sub>6</sub>などのハロゲンを含むガスを混合すると金属を含む堆積物の除去性が向上する。ハロゲンガスの混合割合が増加するとエッチングが生じてしまうので、混合比は30%以下が好ましい。また、5%ないし10%がより好ましい。

#### 【0037】

以上説明したように、本発明の実施形態によれば、トランジスタの高速化のために提案されているhigh-k/Metal Gateと呼ばれる構造を持つ半導体素子の微細加工に適した加工方法を提供することができる。

#### 【0038】

特に、high-k膜と呼ばれるHfO<sub>x</sub>やZrO<sub>x</sub>などの誘電率が高いゲート絶縁膜上に

50

TiN、TaN、RuあるいはRuOなどの仕事関数の制御を目的とした金属を堆積した構造のゲート電極を備える半導体素子の製造における、ドライエッチング後のレジスト除去に際して、水素を含み酸素を含まないガスのプラズマを用いることにより、前記TiN、TaN、RuあるいはRuOなどの金属を堆積した構造のゲート電極を酸化せることなくレジストを除去することができる。

【図面の簡単な説明】

【0039】

【図1】第1の実施形態にかかる半導体加工方法を説明する図である。

【図2】半導体素子を加工する加工装置（プラズマエッチング装置）を説明する図である。

10

【図3】図3は酸素プラズマを用いたレジスト除去の様子を表す図である。

【図4】水素プラズマおよび酸素プラズマを用いてレジストを除去した後のゲート配線の抵抗率を比較して示す図である。プラント監視制御装置を説明する図である。

【図5】第2の実施形態を説明する図である。

【図6】第2の実施形態を説明する図である。

【図7】第3の実施形態を説明する図である。

【図8】混合ガスにおけるArの割合とレジスト除去速度の関係を表す図である。

【符号の説明】

【0040】

|     |          |    |

|-----|----------|----|

| 101 | Si基板     | 20 |

| 102 | HfSiON膜  |    |

| 103 | TiN膜     |    |

| 104 | W膜       |    |

| 105 | SiN膜     |    |

| 106 | 反射防止膜    |    |

| 107 | レジスト     |    |

| 108 | 水素イオン    |    |

| 201 | プラズマ電源   |    |

| 202 | アンテナ     |    |

| 203 | 窓        | 30 |

| 204 | 真空チャンバ   |    |

| 205 | 試料台      |    |

| 206 | ウエハ      |    |

| 207 | バイアス電源   |    |

| 208 | 電磁コイル    |    |

| 301 | 酸素イオン    |    |

| 302 | 酸化層      |    |

| 601 | TaSiN膜   |    |

| 602 | 堆積物      |    |

| 701 | poly-Si膜 | 40 |

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

---

フロントページの続き

(56)参考文献 特開2007-088238(JP,A)

特開2007-095784(JP,A)

特開平07-078829(JP,A)

特開平11-068095(JP,A)

(58)調査した分野(Int.Cl., DB名)

H01L 21/3065

H01L 21/027

H01L 21/304

H01L 21/336

H01L 29/78