(19)

Bundesrepublik Deutschland

Deutsches Patent- und Markenamt

(10) DE 600 36 083 T2 2008.05.08

(12)

## Übersetzung der europäischen Patentschrift

(97) EP 1 153 403 B1

(51) Int Cl.<sup>8</sup>: **H01H 35/00** (2006.01)

(21) Deutsches Aktenzeichen: 600 36 083.0

(86) PCT-Aktenzeichen: PCT/US00/01258

(96) Europäisches Aktenzeichen: 00 903 348.1

(87) PCT-Veröffentlichungs-Nr.: WO 2000/042628

(86) PCT-Anmeldetag: 18.01.2000

(87) Veröffentlichungstag

der PCT-Anmeldung: 20.07.2000

(97) Erstveröffentlichung durch das EPA: 14.11.2001

(97) Veröffentlichungstag

der Patenterteilung beim EPA: 22.08.2007

(47) Veröffentlichungstag im Patentblatt: 08.05.2008

(30) Unionspriorität:

234150 19.01.1999 US

(84) Benannte Vertragsstaaten:

AT, BE, CH, CY, DE, DK, ES, FI, FR, GB, GR, IE, IT,

LI, LU, MC, NL, PT, SE

(73) Patentinhaber:

TouchSensor Technologies, L.L.C., Wheaton, Ill.,

US

(72) Erfinder:

CALDWELL, David W., Naperville, IL 60563, US

(74) Vertreter:

derzeit kein Vertreter bestellt

(54) Bezeichnung: **BERÜHRUNGSSCHALTER MIT INTEGRIERTEM KONTROLLSCHATKREIS**

Anmerkung: Innerhalb von neun Monaten nach der Bekanntmachung des Hinweises auf die Erteilung des europäischen Patents kann jedermann beim Europäischen Patentamt gegen das erteilte europäische Patent Einspruch einlegen. Der Einspruch ist schriftlich einzureichen und zu begründen. Er gilt erst als eingelebt, wenn die Einspruchsgebühr entrichtet worden ist (Art. 99 (1) Europäisches Patentübereinkommen).

Die Übersetzung ist gemäß Artikel II § 3 Abs. 1 IntPatÜG 1991 vom Patentinhaber eingereicht worden. Sie wurde vom Deutschen Patent- und Markenamt inhaltlich nicht geprüft.

**Beschreibung****GEBIET DER ERFINDUNG**

**[0001]** Die vorliegenden Erfindung betrifft Touchfeldsysteme und insbesondere Touchschalter (d. h. Schalter, die betätigt werden, indem beispielsweise ein Touchpad oder dessen Umkreis mit einem Finger berührt wird) und zugehörige Kontrollschatzkreise zur Verwendung als Ersatz für mechanische Schalter.

**HINTERGRUND DER ERFINDUNG**

**[0002]** Mechanische Schalter werden seit langem zur Kontrolle von Geräten aller Art einschließlich von Haushaltsgeräten, Werkzeugmaschinen und anderer häuslicher und industrieller Ausrüstung verwendet. Mechanische Schalter werden normalerweise auf ein Substrat montiert und erfordern eine Art von Durchdringung durch das Substrat. Diese Durchdringungen sowie Durchdringungen im Schalter selbst können es zulassen, dass Schmutz, Wasser und andere Verunreinigungen durch das Substrat dringen oder sich im Schalter sammeln, was zu elektrischen Kurzschlüssen und anderen Fehlfunktionen führt.

**[0003]** Touchschalter werden oft verwendet, um konventionelle mechanische Schalter zu ersetzen. Anders als mechanische Schalter enthalten Touchschalter keine beweglichen Teile, die zerbrechen oder verschleißt können. Weiterhin können Touchschalter auf eine durchgängige Substratplatte, d. h. ein Schalterfeld, montiert oder gebildet werden, ohne dass Öffnungen im Substrat erforderlich sind. Die Verwendung von Touchschaltern anstelle von mechanischen Schaltern kann daher vorteilhaft sein, insbesondere in Umgebungen, in denen wahrscheinlich Verunreinigungen vorhanden sind. Touchschalterfelder sind außerdem einfacher zu reinigen als typische Felder mit mechanischen Schaltern, weil sie ohne Öffnungen im Substrat hergestellt werden können, die das Eindringen von Verschmutzungen zulassen würden.

**[0004]** Bekannte Touchschalter umfassen normalerweise ein Touchpad mit einer oder mehr Elektroden. Die Touchpads kommunizieren mit Kontroll- oder Schnittstellen-Schaltkreisen, die oft kompliziert und entfernt von den Touchpads sind. Ein Signal wird gewöhnlich an eine oder mehr der Elektroden, die das Touchpad umfasst, gelegt, das ein elektrisches Feld im Umkreis der betroffenen Elektroden erzeugt. Die Kontroll-/Schnittstellen-Schaltkreise erfassen Störungen in den elektrischen Feldern und bewirken, dass eine Reaktion zur Verwendung durch eine kontrollierte Vorrichtung erzeugt wird.

**[0005]** Obwohl Touchschalter viele Probleme lösen, die mit mechanischen Schaltern assoziiert sind, sind bekannte Touchschalter-Konstruktionen nicht per-

fekt. Beispielsweise können viele bekannte Touchschalter falsch funktionieren, wenn Verunreinigungen wie Wasser oder andere Flüssigkeiten auf dem Substrat vorhanden sind. Die Verunreinigung kann als ein Leiter für die elektrischen Felder, die um die Touchpads erzeugt werden, wirken und nicht beabsichtigte Schaltbetätigungen verursachen. Dies stellt ein Problem in Bereichen dar, in denen derartige Verunreinigungen häufig vorkommen, wie in einer Küche oder einigen Werksumgebungen.

**[0006]** Existierende Touchschalter-Konstruktionen können auch unter Problemen leiden, die mit Übersprechen assoziiert sind, d. h. Interferenzen zwischen den elektrischen Feldern um aneinander angrenzende Touchpads. Übersprechen kann bewirken, dass der falsche Touchschalter aktiviert wird, oder kann bewirken, dass zwei Schalter gleichzeitig durch eine Berührung in der Nähe eines einzelnen Touchpads aktiviert werden.

**[0007]** Viele existierende Touchschalter-Konstruktionen sind auch anfällig gegenüber unbeabsichtigte Aktivierungen aufgrund von elektrischem Rauschen oder anderen Interferenzen, die ein Touchpad selbst oder die Leitungen, die von dem Touchpad zu seinem assoziierten Kontrollschatzkreis führen, beeinträchtigen. Dieses Problem kann verstärkt in Anwendungen vorkommen, in denen das Touchpad eine relativ große Distanz von den kontrollierten Schaltkreisen entfernt ist, wie es häufig bei konventionellen Touchschalter-Konstruktionen der Fall ist.

**[0008]** Existierende Touchschalter-Konstruktionen erfordern gewöhnlich komplizierte Kontrollschatzkreise, um mit den Vorrichtungen zusammenzuwirken, die sie kontrollieren. Es ist wahrscheinlich, dass diese Kontrollschatzkreise eine große Zahl von diskreten Bauteilen umfassen, die beträchtlichen Raum auf einer Leiterplatte belegen. Aufgrund ihrer physikalischen Größe sind die Kontrollschatzkreise gewöhnlich in einer beträchtlichen Entfernung von den Touchpads selbst angeordnet. Die physikalische Größe der Kontroll-/Schnittstellen-Schaltkreise und ihre Entfernung von den Touchpads kann viele der oben diskutierten Probleme wie Übersprechen und Anfälligkeit gegenüber elektrischem Rauschen und Interferenzen verstärken. Die Größe und Entfernung verkomplizieren außerdem die gesamte Konstruktion, was in erhöhten Produktionskosten und mehr Komplexität resultiert.

**[0009]** Einige bestehende Touchschalter-Konstruktionen erfordern eine separate Masseleitung von dem Touchpad zum Schnittstellen-/Kontrollschatzkreis oder zur kontrollierten Vorrichtung. Bestimmte Geräte, die konventionelle mechanische Schalter verwenden, erfordern derartige Massekabel nicht und nehmen diese unter Umständen nicht problemlos auf. Die Anpassung derartiger Geräte für Verwen-

dung mit derartigen Touchschaltern kann es erforderlich machen, spezielle Masseverbindungsverkehrungen vorzusehen, wodurch Konstruktion- und Produktionsdauern, Komplexität und Kosten erhöht werden. Dieses Erfordernis von Masseleitungen kann das einfache, direkte Ersetzen von konventionellen mechanischen Schalterfeldern durch Touchschalterfelder unmöglich machen.

**[0010]** Kürzliche Verbesserungen in der Konstruktion von Touchschaltern enthalten Techniken, die die Eingangs- und Ausgangsimpedanz des Touchschalters selbst senken, wodurch er in hohem Maße immun gegenüber falschen Aktivierungen durch Verunreinigungen und externe Störquellen wird. US-Patent Nr. 5594222 beschreibt eine Touchschalter-Konstruktion mit niedriger Impedanz, die bei Vorhandensein von Verunreinigungen und elektrischem Rauschen weniger anfällig für Fehlfunktionen als viele frühere Konstruktionen ist. Obwohl dieses Konzept viele Vorteile gegenüber dem Stand der Technik bietet, sind einige Attribute vorhanden, die seine Anwendung beschränken können. Beispielsweise kann der resultierende Schalter empfindlich gegenüber Temperaturschwankungen sein. Solange die Temperaturschwankungen am Ausgang klein relativ zu zulässigen Signaländerungen sind und klein relativ zu Signalvariationen sind, die durch Transistorvariationen induziert werden, wird ein einzelner Transistor oder eine andere Verstärkungsvorrichtung zufrieden stellend sein. Diese Technik kann jedoch die Verwendung von zusätzlichen Schaltkreisen zur Anbindung an die kontrollierte Vorrichtung erfordern, wodurch die Kosten und Komplexität der gesamten Touchschalter-Konstruktion erhöht werden. In Anwendungen, in denen nur ein geringer dynamischer Bereich für Ausgleichung besteht und in denen Temperaturänderungen relativ zu zulässigen Signaländerungen beträchtlich sind, ist ein anderes Konzept unter Umständen besser imstande, die Auswirkungen der Temperatur zu eliminieren oder zu reduzieren.

**[0011]** Obwohl das Niederimpedanz-Konzept dieser Technik zwischen Verunreinigungen mit gewissen finiten Impedanzbeträgen und einer menschlichen Berührung mit gewissen finiten Impedanzbeträgen unterscheiden kann, ist diese Technik außerdem unter Umständen nicht ausreichend, um zwischen extrem niedrigen Impedanzpegeln zu unterscheiden. Eine derartige Situation könnte bestehen, wenn ein gesamter Touchschalter (d. h. sowohl die innere als auch die äußere Elektrode) von einer großen Menge Verunreinigung bedeckt ist. Eine ähnliche Situation mit im Wesentlichen einer Impedanz von null könnte bestehen, wenn ein leitendes Material wie eine Metallwanne einen Touchschalter vollständig bedeckt.

**[0012]** Die US-Patenanmeldung mit der laufenden Nr. 08/986927, jetzt US-Patent Nr. 6310611, das demselben Rechtsnachfolger der vorliegenden An-

meldung zugeteilt ist, offenbart eine Touchschaltervorrichtung mit einem Differenzial-Messschaltkreis, der viele der Probleme hinsichtlich von Gleichtaktstörungen, die Touchschalter beeinträchtigen, behandelt. Beispielsweise kann ein Touchschalter mit einem Zwei-Elektroden-Touchpad konfiguriert werden, um ein elektrisches Feld um jede Elektrode zu erzeugen. Eine Gleichtaktstörung wie eine Verunreinigung, die beide Elektroden im Wesentlichen abdeckt, wird das elektrische Feld um jede der Elektroden wahrscheinlich im Wesentlichen in gleichem Maße beeinflussen. Jede Elektrode liefert ein Signal, das proportional zur Störung ist, an den Differenzial-Messschaltkreis. Da die Signale von den Elektroden als im Wesentlichen gleich angesehen werden, erfasst der Differenzial-Messschaltkreis keine Differenz und reagiert nicht auf die Gleichtaktstörung. Wenn andererseits nur das Feld um eine der Elektroden gestört wird, wird das von dieser Elektrode an den Differenzial-Messschaltkreis gelieferte Signal im Wesentlichen von dem, das von der anderen, nicht betroffenen Elektrode geliefert wird, verschieden sein. Der Differenzialschaltkreis kann durch Bereitstellung eines Ausgangs, der eine Schalteraktivierung verursacht, reagieren.

**[0013]** Obwohl das Konzept des Differenzial-Messschaltkreises viele nach dem Stand der Technik bekannte Probleme anspricht, ist es relativ komplex und kann kostspielig in der Konstruktion und Herstellung sein. Ein Differenzial-Messschaltkreis umfasst normalerweise viel mehr Teile als ein konventioneller Kontrollschatlkreis. Die zusätzlichen Teile werden wahrscheinlich mehr Raum auf einem Touchschalterfeld einnehmen. Als solcher wird der Kontrollschatlkreis wahrscheinlich noch weiter von dem Touchpad entfernt sein, als es bei einer Nicht-Differenzial-Schaltkreiskonstruktion wäre, wodurch lange Leitungen zwischen dem Touchpad und seinem Kontrollschatlkreis erforderlich sind. Dadurch können Probleme hinsichtlich von elektrischen Interferenzen tatsächlich noch verstärkt werden. Weiterhin wird beim Bilden eines Differenzial-Messschaltkreises die gegenseitige Anpassung der Komponenten wichtig. Richtige Anpassung der Komponenten stellt eine zusätzliche Belastung bei der Fertigung dar und wird wahrscheinlich höhere Kosten verursachen.

**[0014]** Obwohl die vorstehenden Verbesserungen unbeabsichtigte Schalteraktivierungen aufgrund von Übersprechen zwischen Schaltern und die Auswirkungen von elektrischen Interferenzen auf ihre Kontrollschatlkreise reduzieren können, beseitigen sie diese Probleme nicht vollständig. Außerdem berücksichtigen sie weder das Erfordernis nach separaten Masseschaltkreisen in bestimmten Touchschalter-Anwendungen noch lösen sie die damit in Beziehung stehenden Probleme. Ein anderes Beispiel eines Touchschalters wird in WO-A-9826506 offenbart, wobei ein Differenzialschaltkreis fungiert, um einen

Ausgang proportional zu einer Differenz, falls vorhanden, zwischen den Stimuli zu erzeugen, die auf erste und zweite Elektroden ausgeübt werden. In dieser Schrift wird kein Entscheidungsschaltkreis offenbart.

## ZUSAMMENFASSUNG DER ERFINDUNG

**[0015]** Es ist eine Aufgabe der Erfindung, eine zuverlässige Touchschaltervorrichtung bereitzustellen, die im Wesentlichen durch das Vorhandensein von Verunreinigungen, elektrischen Interferenzen und anderen Störungen in der Nähe des Touchschalters und seiner assoziierten Kontrollschatlkreise nicht beeinträchtigt wird, um eine unbeabsichtigte Schalteraktivierung zu verhindern, wenn der Touchschalter durch derartige Störungen beeinträchtigt wird.

**[0016]** Außerdem ist es eine Aufgabe der Erfindung, die Schnittstellen-Anforderungen zwischen Touchschaltern und den vielen verschiedenen Anwendungen, in denen sie verwendet werden können, zu vereinfachen, so dass Touchschalterfelder auf einfache Weise als direkte Einstech-Ersetzungen für Felder mit mechanischen Schaltern dienen können.

**[0017]** Die vorliegende Erfindung stellt eine Touchschaltervorrichtung bereit, die ein Touchpad und einen in der Nähe des Touchpads angeordneten Kontrollschatlkreis umfasst. Das Touchpad und der Kontrollschatlkreis können auf einem dielektrischen Substrat montiert werden. Der Kontrollschatlkreis ist im Vergleich zur gesamten Größe der Vorrichtung klein. In einer bevorzugten Ausführungsform ist der Kontrollschatlkreis im Wesentlichen auf einen oder mehr integrierte Schaltkreise reduziert. Die physikalische Kompaktheit des Kontrollschatlkreises in der Ausführungsform mit integriertem Schaltkreis reduziert die Anfälligkeit des Touchschalters gegenüber Gleichtaktinterferenzen sowie gegenüber Übersprechen und Interferenzen zwischen angrenzend angeordneten Touchschaltern. Das Konzept mit integriertem Schaltkreis gestattet außerdem eine bessere Anpassung und Übereinstimmung der Komponenten des Kontrollschatlkreises.

**[0018]** Der Touchschalter der vorliegenden Erfindung kann in einer Reihe von bevorzugten Ausführungsformen konfiguriert werden. In einigen Ausführungsformen kann der Touchschalter einen konventionellen mechanischen Schalter in Dauerkontaktausführung emulieren. In anderen Ausführungsformen kann der Touchschalter einen mechanischen Schalter in Wischkontaktausführung emulieren.

**[0019]** In einer bevorzugten Ausführungsform hat das Touchpad eine erste Elektrode und eine zweite Elektrode nahe an der ersten Elektrode. Mindestens eine der Elektroden ist elektrisch mit dem lokalen Kontrollschatlkreis verbunden. Die erste und zweite Elektrode und der lokale Kontrollschatlkreis sind nor-

malerweise auf derselben Oberfläche eines Substrats angeordnet, gegenüber der Seite des Substrats, die als Berührungsfläche zu verwenden ist. Sie müssen jedoch nicht koplanar sein und können an gegenüberliegenden Seiten des Substrats angeordnet sein.

**[0020]** In einer alternativen Ausführungsform hat das Touchpad eine einzelne Elektrode, die elektrisch mit dem lokalen Kontrollschatlkreis verbunden ist. In anderen alternativen Ausführungsformen kann das Touchpad mehr als zwei Elektroden haben.

**[0021]** In einer bevorzugten Ausführungsform enthält der Kontrollschatlkreis Mittel zum Erzeugen eines Signals und zur Bereitstellung dieses für das Touchpad, um ein elektrisches Feld um eine oder mehr der Elektroden, die das Touchpad umfasst, zu erzeugen. Alternativ kann ein derartiges Signal woanders erzeugt und für eine oder mehr der Elektroden bereitgestellt werden, um dieses eine oder mehr elektrische Felder zu erzeugen. Der Kontrollschatlkreis erfasst Störungen des elektrischen Felds als Reaktion auf darauf ausgeübte Stimuli, wie wenn der Benutzer mit seiner Fingerspitze das an den Touchschalter angrenzende Substrat berührt oder seine Fingerspitze daran nähert. Der Kontrollschatlkreis reagiert selektiv auf derartige Feldstörungen durch Erzeugen eines Kontrollschatlsignals zur Verwendung durch eine kontrollierte Vorrichtung wie ein Haushaltsgerät oder eine industrielle Maschine.

**[0022]** In einer bevorzugten Ausführungsform erfasst der Kontrollschatlkreis Differenzen im elektrischen Potenzial zwischen den ersten und zweiten Elektroden als Reaktion auf die Einführung eines Stimulus nahe der ersten Elektrode, der zweiten Elektrode oder beider und reagiert darauf. Ein derartiger Differenz-Messschaltkreis ermöglicht die Zurückweisung von Gleichtaktsignalen (d. h. Signale, die dahn tendieren, beide Elektroden ungefähr gleich zu beeinflussen) wie Temperatur, elektrisches Rauschen, Schwankungen der Stromversorgung und andere Eingänge. Der Differenz-Messschaltkreis ermöglicht außerdem die Zurückweisung von Gleichtaktsignalen, die aus der Anwendung von Verunreinigungen des Substrats angrenzend an den Touchschalter resultieren.

**[0023]** In einer bevorzugten Ausführungsform wird ein Signal an eine erste Elektrode und an eine zweite Elektrode angelegt. Ein elektrisches Potenzial wird an jeder Elektrode entwickelt und infolgedessen wird an jeder der Elektroden ein elektrisches Feld erzeugt. Zwei aneinander angepasste Transistoren sind in einem Differenz-Messschaltkreis angeordnet, wobei der erste Transistor mit der ersten Elektrode verbunden ist und der zweite Transistor mit der zweiten Elektrode verbunden ist. Der Ausgang jedes Transistors ist mit einem Spitzendetektions-Schaltkreis verbunden, und der Ausgang jedes Spitzendetektions-Schaltkreises ist mit dem lokalen Kontrollschatlkreis verbunden.

ons-Schaltkreises wird einem Entscheidungsschaltkreis zugeführt.

**[0024]** Der Ausgang jedes Transistors wird geändert, wenn das elektrische Feld um seine korrespondierende Elektrode geändert wird, wie wenn die Elektrode von einem Benutzer berührt wird oder ein Benutzer sich ihrer nähert. Der Spitzendetektions-Schaltkreis reagiert auf Änderungen in den Ausgängen der Transistoren und liefert Signale, die mit den Spitzenzonen von den Transistoren korrespondieren, an den Entscheidungsschaltkreis. Der Entscheidungsschaltkreis verwendet die Spitzenzonen in einer vorbestimmten Weise zur Bereitstellung eines Ausgangs zur Nutzung durch andere Bereiche des Kontrollschatlkreises.

**[0025]** In einer bevorzugten Ausführungsform sind die inneren und äußeren Elektroden betriebsfähig mit den Eingängen des Entscheidungsschaltkreises derart assoziiert, dass der Entscheidungsschaltkreis einen hochpegeligen Ausgang bereitstellt, wenn eine Störung eines elektrischen Felds um eine erste Elektrode größer ist als der Grad der Störung eines elektrischen Felds um eine zweite Elektrode. Umgekehrt stellt der Entscheidungsschaltkreis einen niedrigpegeligen Ausgang bereit, wenn eine Störung des elektrischen Felds um die zweite Elektrode größer ist als der Grad der Störung eines elektrischen Felds um die erste Elektrode. Wenn die Felder um beide Elektroden mehr oder weniger gleich gestört werden, stellt der Entscheidungsschaltkreis einen niedrigpegeligen Ausgang bereit.

**[0026]** Die erste Bedingung kann beispielsweise erzeugt werden, wenn eine Fingerspitze die erste Elektrode im Wesentlichen bedeckt, aber nicht die zweite Elektrode. Die zweite Bedingung kann beispielsweise erzeugt werden, wenn eine Fingerspitze oder Verunreinigung die zweite Elektrode im Wesentlichen bedeckt, aber nicht die erste Elektrode. Die dritte Bedingung kann erzeugt werden, wenn beispielsweise eine Verunreinigung oder ein Gegenstand wie eine Metallwanne sowohl die erste als auch die zweite Elektrode bedeckt.

**[0027]** Der Ausgang des Entscheidungsschaltkreises wird für andere Schaltkreiskomponenten wie ein elektrisches Latch bereitgestellt, das selektiv bewirkt, dass ein Kontrollsignal von dem Kontrollschatlkreis in Abhängigkeit von dem Ausgangszustand des Entscheidungsschaltkreises ausgegeben wird. In einer bevorzugten Ausführungsform bewirkt ein hochpegeliger Ausgang vom Entscheidungsschaltkreis schließlich die Ausgabe eines Kontrollssignals von dem Kontrollschatlkreis, während kein Kontrollsignal als Reaktion auf einen niedrigpegeligen Ausgang ausgegeben wird. In einer alternativen Ausführungsform bewirkt ein niedrigpegeliger Ausgang von dem Entscheidungsschaltkreis, dass ein Kontrollsignal

von dem Kontrollschatlkreis ausgegeben wird, während kein Kontrollsignal als Reaktion auf einen hochpegeligen Ausgang ausgegeben wird.

**[0028]** Die Touchschaltervorrichtung der vorliegenden Erfindung kann verwendet werden, um fast jede Funktion auszuführen, die von einem mechanischen Schalter ausgeführt werden kann, wie Ein- oder Ausschalten einer Vorrichtung, Anpassen der Temperatur oder Einstellen einer Uhr oder eines Timers. Sie kann anstelle von existierenden Touchschaltern verwendet werden und damit assoziierte Probleme lösen. Sie kann außerdem als direkter Ersatz für mechanische Schalter in Membranausführung verwendet werden. Die Touchschaltervorrichtung der vorliegenden Erfindung ist gut geeignet zur Verwendung in Umgebungen, in denen extreme Temperaturschwankungen vorkommen, in denen beträchtliche Mengen von Verunreinigungen vorhanden sein können oder in denen Metallgegenstände auf oder über das Touchpad angeordnet werden können.

#### KURZE BESCHREIBUNG DER ZEICHNUNGEN

**[0029]** Die verschiedenen Merkmale, Vorteile und anderen Verwendungen der vorliegenden Erfindung werden besser ersichtlich durch Bezugnahme auf die folgende ausführliche Beschreibung und die Zeichnungen, von denen:

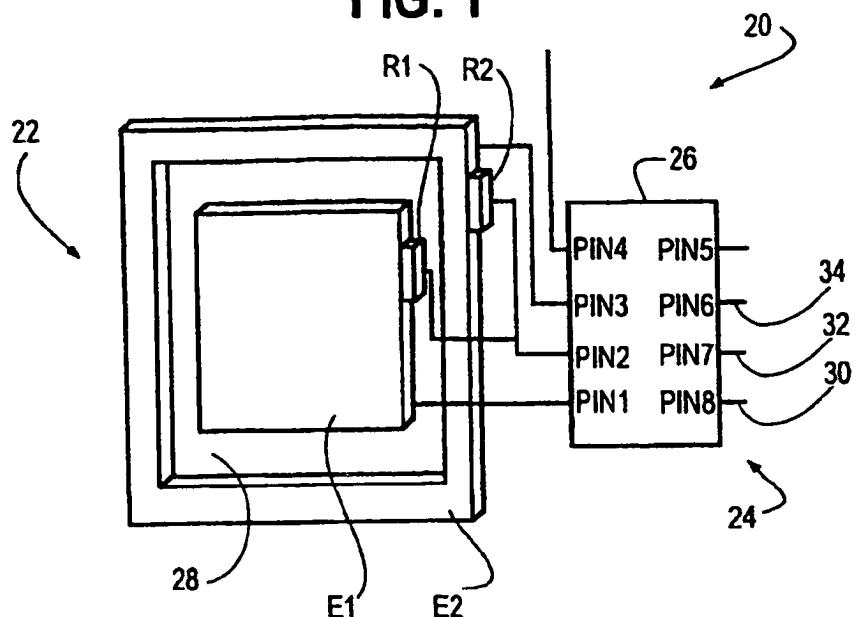

**[0030]** [Fig. 1](#) eine perspektivische Zeichnung einer bevorzugten Ausführungsform eines Touchschalters der vorliegenden Erfindung zeigt;

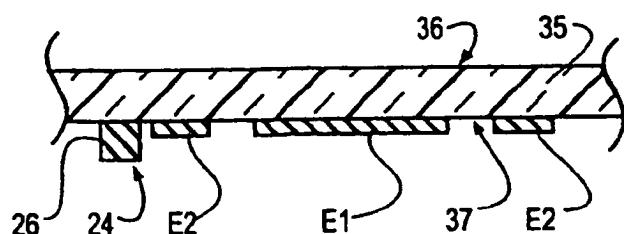

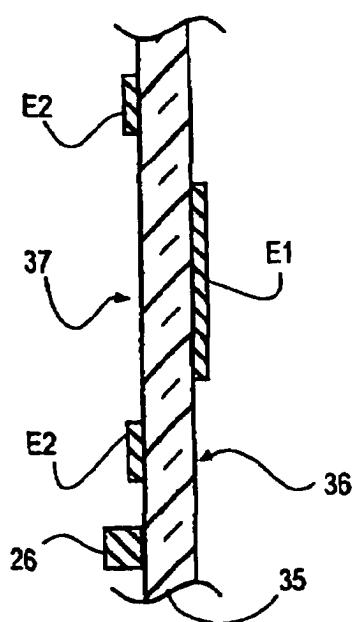

**[0031]** [Fig. 2](#) eine Querschnittsansicht eines Zwei-Elektroden-Touchpads und integrierten Schaltkreischips der vorliegenden Erfindung zeigt;

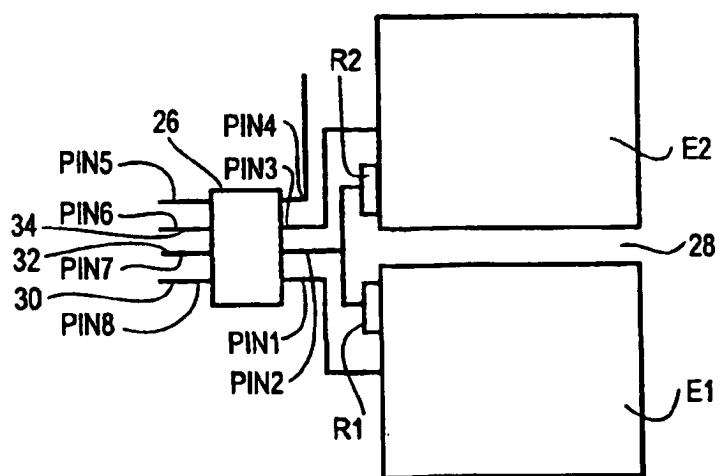

**[0032]** [Fig. 3](#) eine Planansicht einer Ausführungsform einer Touchschaltervorrichtung der vorliegenden Erfindung zeigt;

**[0033]** [Fig. 4](#) eine elektrische schematische Repräsentation eines Touchschalter-Kontrollschatlkreises zeigt, der für einen bevorzugten Operationsmodus konfiguriert ist;

**[0034]** [Fig. 5](#) eine elektrische schematische Repräsentation eines Touchschalter-Kontrollschatlkreises zeigt, der für einen alternativen bevorzugten Operationsmodus konfiguriert ist;

**[0035]** [Fig. 6](#) eine elektrische schematische Repräsentation eines Touchschalter-Kontrollschatlkreises zeigt, der für einen anderen alternativen bevorzugten Operationsmodus konfiguriert ist;

**[0036]** [Fig. 7](#) eine elektrische schematische Repräsentation eines Touchschalter-Kontrollschatlkreises zeigt, der für einen wieder anderen alternativen be-

vorzugten Operationsmodus konfiguriert ist;

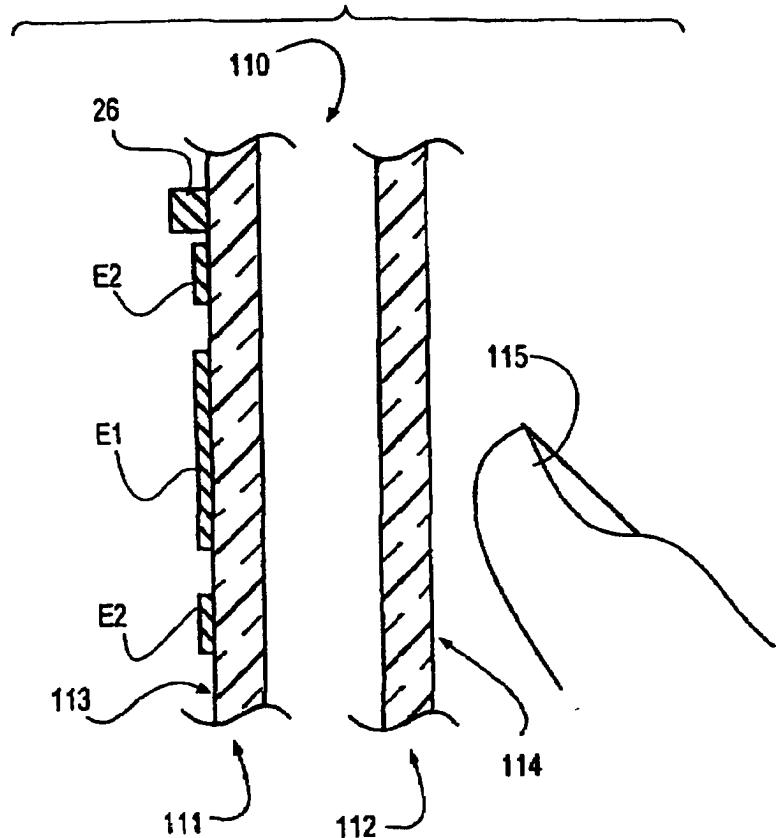

[0037] [Fig. 8](#) eine Querschnittsansicht einer alternativen Ausführungsform eines Touchpads der vorliegenden Erfindung zeigt;

[0038] [Fig. 9](#) eine Querschnittsansicht einer anderen alternativen Ausführungsform eines Touchpads der vorliegenden Erfindung zeigt; und

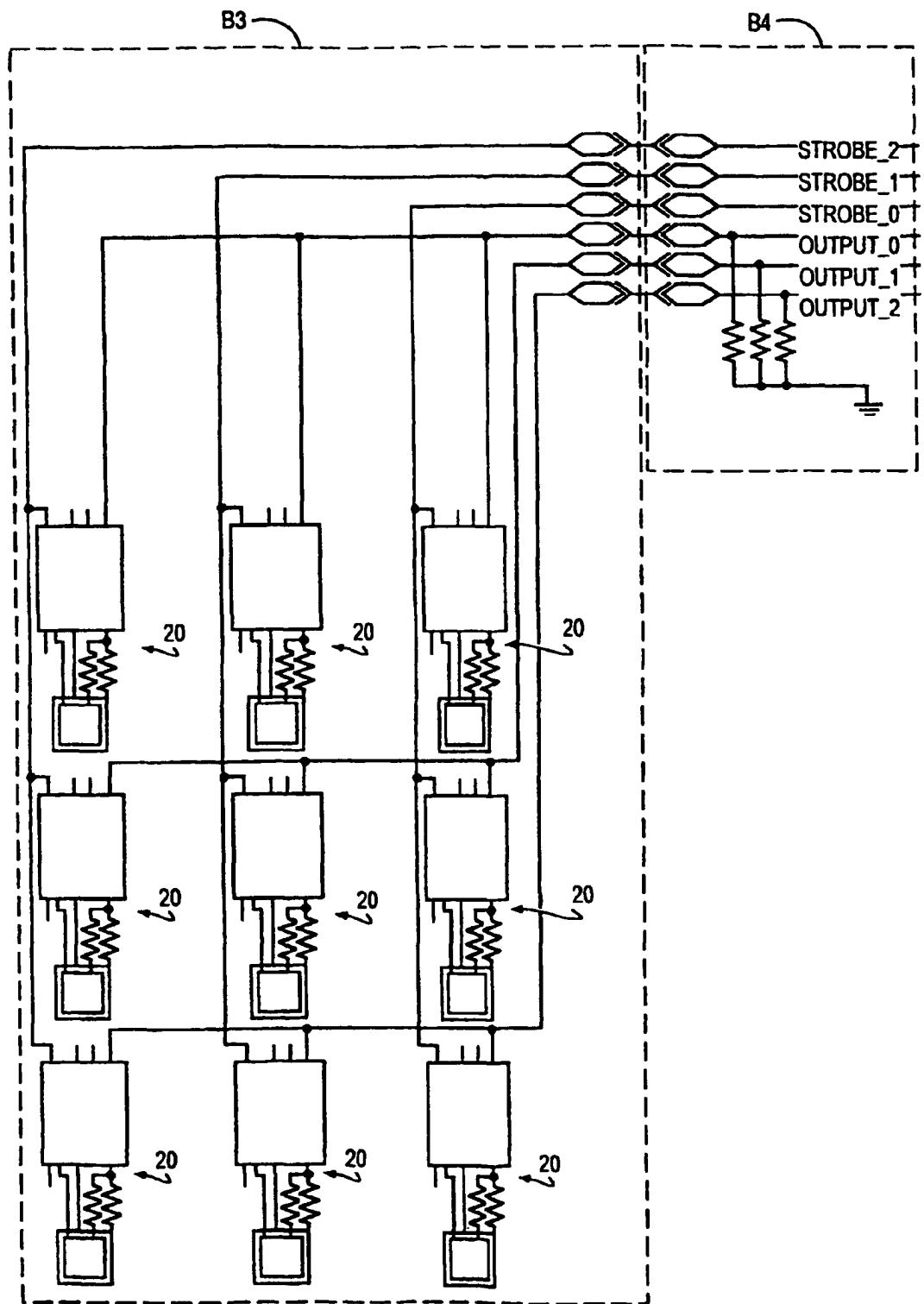

[0039] [Fig. 10](#) eine diagrammatische Repräsentation einer Ausführungsform eines Touchschalterfelds zeigt, das eine Vielzahl von Touchschaltern in Matrixanordnung zeigt.

[0040] Ähnliche Bezugsnummern in den verschiedenen Figuren beziehen sich auf ähnliche Elemente.

## BESCHREIBUNG DER BEVORZUGTEN AUSFÜHRUNGSFORMEN

[0041] Die Erfindung betrifft eine Touchschaltervorrichtung, die ein Touchpad mit einer oder mehr Elektroden und einem Kontrollschatzkreis umfasst. Viele der Zeichnungsfiguren, die den Kontrollschatzkreis darstellen, zeigen den Schaltkreis im Verhältnis zum Touchpad zur Verdeutlichung groß. In typischen Anwendungen kann der Kontrollschatzkreis jedoch im Vergleich zum Touchpad klein sein und hat vorzugsweise die Form von einem oder mehr integrierten Schaltkreischips.

[0042] [Fig. 1](#) zeigt eine perspektivische Repräsentation einer bevorzugten Ausführungsform einer Touchschaltervorrichtung **20** der vorliegenden Erfindung. Die Touchschaltervorrichtung **20** umfasst ein Touchpad **22**, einen Kontrollschatzkreis **24**, der einen integrierten Schaltkreis-(IC)-Chip **26** mit acht Ausgangsanschlüssen PIN1–PIN8 umfasst, und erste und zweite Widerstände R1 und R2. In der dargestellten Ausführungsform umfasst das Touchpad **22** eine erste Elektrode E1 und eine zweite Elektrode E2, obwohl das Touchpad auch mehr oder weniger als zwei Elektroden umfassen kann. Obwohl der Kontrollschatzkreis **24** unter Verwendung von diskreten elektronischen Komponenten hergestellt werden könnte, ist es vorzuziehen, den Kontrollschatzkreis **24** in einem einzelnen integrierten Schaltkreischip wie IC-Chip **26** auszuführen.

[0043] Der Kontrollschatzkreis **24** ist über die Anschlüsse PIN1–PIN8 des IC-Chips **26** elektrisch mit ersten und zweiten Widerständen R1 und R2, ersten und zweiten Elektroden E1 und E2 und einer Eingangsleitung **30**, die zur Zuführung eines Kontroll- und/oder Energiesignals von einer entfernten Vorrichtung (nicht dargestellt) konfiguriert ist, verbunden und kommuniziert damit. Der Kontrollschatzkreis **24** kommuniziert außerdem mit einer entfernten Vorrichtung (nicht dargestellt) unter Verwendung einer ers-

ten Ausgangsleitung **32**. In einigen Ausführungsformen wird außerdem eine zweite Ausgangsleitung **34** für Kommunikation mit der entfernten Vorrichtung (nicht dargestellt) verwendet.

[0044] [Fig. 2](#) zeigt eine partielle Querschnittsansicht eines typischen Touchschalters **20** der vorliegenden Erfindung, in dem die Komponenten, die die Touchschaltervorrichtung **20** umfasst, auf einem dielektrischen Substrat **35** montiert sind, das eine vordere Oberfläche **36** und eine gegenüberliegende hintere Oberfläche **37** hat. In der dargestellten Ausführungsform sind erste und zweite Elektroden E1 und E2 auf der hinteren Oberfläche **37** des Substrats **35** montiert. Der IC-Chip **26** ist auch auf der hinteren Oberfläche **37** des Substrats **35** nahe an den ersten und zweiten Elektroden E1 und E2 montiert. Wie sowohl aus [Fig. 1](#) als auch aus [Fig. 2](#) ersichtlich, wird in der bevorzugten Ausführungsform in Betracht gezogen, dass der IC-Chip **26**, der den Kontrollschatzkreis **24** umfasst, in großer Nähe zum Touchpad **22** montiert ist.

[0045] Das Substrat **35** besteht normalerweise aus einem relativ starren dielektrischen Material wie Glas, Kunststoff, Keramik oder einem anderen geeigneten dielektrischen Material. Das Substrat **35** kann jedoch auch aus einem anderen geeigneten dielektrischen Material bestehen, einschließlich von flexiblen Materialien. Consolidated Graphics No. HS-500, Type 561, Level 2, ein 0,005 Zoll dickes Polyestermaterial, ist ein Beispiel eines geeigneten flexiblen Substrats. In Ausführungsformen, in denen die Komponenten der Touchschaltervorrichtung auf ein flexibles Substrat montiert werden, wird der flexible Träger häufig auf einen anderen, im Allgemeinen starreren Substrat aufgebracht.

[0046] In einer bevorzugten Ausführungsform ist das Substrat **35** aus Glas mit einer gleichförmigen Dicke von etwa 3 mm hergestellt. In anderen Ausführungsformen kann die Dicke des Substrats **35** variieren, abhängig von der Art des verwendeten Materials, seinen mechanischen und elektrischen Eigenschaften und der physikalischen Festigkeit und elektrischen Empfindlichkeit, die für eine bestimmte Anwendung erforderlich sind. Die maximale funktionale Dicke von Glas- und Kunststoff-Substraten liegt in der Größenordnung von mehreren Zoll. In den meisten Anwendungen reichen Glas-Substrate in der Dicke von etwa 1,1 bis etwa 5 mm, während Kunststoff-Substrate noch dünner sein können.

[0047] In einer bevorzugten Ausführungsform, wie in [Fig. 1](#) und [Fig. 2](#) dargestellt, umgibt die zweite Elektrode E2 im Wesentlichen die erste Elektrode E1. Ein Freiraum **28** befindet sich zwischen der ersten Elektrode E1 und der zweiten Elektrode E2. Die erste Elektrode E1 kann so dimensioniert sein, dass sie von der Fingerspitze eines Benutzers oder einem an-

deren menschlichen Anhangsgebilde „bedeckt“ wird, wenn der Benutzer den korrespondierenden Abschnitt der vorderen Oberfläche **36** des Substrats **35** berührt. In einer bevorzugten Ausführungsform ist die erste Elektrode E1 quadratisch und die zweite Elektrode E2 ist in einem quadratischen Muster um und entsprechend der Form der ersten Elektrode E1 angeordnet.

**[0048]** Obwohl die in [Fig. 1](#) und [Fig. 2](#) dargestellte Touchpad-Geometrie eine bevorzugte Anordnung der ersten und zweiten Elektroden E1 und E2 repräsentiert, sollte es anerkannt werden, dass die Anordnung der Elektroden in einem großen Ausmaß zur Anpassung an eine große Vielzahl von Anwendungen variiert werden kann. Beispielsweise können die Größe, Form und Anordnung der Elektroden zur Anpassung an die Größe des Anhangsgebildes oder anderen Stimulus, das zum Aktivieren des Touchschalters **20** vorgesehen ist, variiert werden. Beispielsweise kann eine bestimmte Anwendung erfordern, dass eine Hand anstelle eines Fingers den Stimulus zur Aktivierung des Touchschalters **20** bereitstellt. In einer derartigen Anwendung würden die ersten und zweiten Elektroden E1 und E2 viel größer und weiter voneinander entfernt angeordnet sein.

**[0049]** Die erste Elektrode E1 kann jede Zahl von verschiedenen geometrischen Formen annehmen einschließlich von, aber nicht darauf begrenzt, Rechtecken, Trapezoiden, Kreisen, Ellipsen, Dreiecken, Sechsecken und Achtecken. Unabhängig von der Form der ersten Elektrode E1 kann die zweite Elektrode E2 so konfiguriert werden, dass sie die erste Elektrode E1 zumindest teilweise in einer davon entfernten Beziehung umgibt. Es ist jedoch nicht erforderlich, dass die zweite Elektrode E1 die erste Elektrode auch nur teilweise umgibt, um die Vorteile der Erfindung zu realisieren. Beispielsweise können die ersten und zweiten Elektroden E1 und E2 aneinander angrenzend sein, wie in [Fig. 3](#) dargestellt. In alternativen Ausführungsformen kann die zweite Elektrode E2 weggelassen werden.

**[0050]** Weiterhin muss die Elektrodenkonfiguration nicht koplanar sein, sondern kann dreidimensional sein, um eine Kugel, einem Kubus oder einer anderen geometrischen Form zu entsprechen. Diese Designflexibilität gestattet es, dass die Erfindung in einer großen Vielfalt von Anwendungen eingesetzt wird, wobei die Substrate unterschiedliche Formen und Zusammensetzungen aufweisen können. In einigen Anwendungen ist es unter Umständen nicht erforderlich, das Substrat **35** zu berühren, auf oder in dem sich das Touchpad **22** und der Kontrollschatzkreis **24** befinden. Beispielsweise zeigt [Fig. 8](#) eine Touchschaltervorrichtung **20**, in der erste und zweite Elektroden E1 und E2 auf einer Außenoberfläche **113** einer ersten Scheibe **111** eines Thermopanefensters **110** montiert sind, die durch einen Benutzer aktiviert

werden können, der einen geeigneten Stimulus **115** in die Nähe eines Außenoberflächen **114** einer gegenüberliegenden Scheibe **112** des Fensters bringt.

**[0051]** Wie oben erwähnt, müssen die ersten und zweiten Elektroden E1 und E2 nicht koplanar sein; sie können an verschiedenen Seiten oder Oberflächen eines Substrats oder sogar auf verschiedenen Substraten montiert werden. Beispielsweise zeigt [Fig. 9](#) eine Touchschaltervorrichtung **20**, bei der die erste Elektrode E1 auf einer ersten Oberfläche **36** eines Substrats **35** montiert ist und die zweite Elektrode E2 und der IC-Chip **26** auf einer zweiten, gegenüberliegenden Oberfläche **37** des Substrats **35** montiert sind. In Anwendungen, in denen die ersten und zweiten Elektroden E1 und E2 auf derselben Seite eines Substrats montiert sind, kann der IC-Chip **26** auf dieselbe Seite des Substrats wie die Elektroden oder auf einer anderen Seite des Substrats montiert werden. Wenn die ersten und zweiten Elektroden auf verschiedenen Seiten eines Substrats oder sogar auf verschiedenen Substraten montiert werden, kann der IC-Chip **26** auf dieselbe Oberfläche wie eine der Elektroden oder auf einer anderen Oberfläche oder ein anderes Substrat montiert werden. Es wird jedoch vorgezogen, dass der IC-Chip **26** in großer Nähe zu den Elektroden montiert wird.

**[0052]** Die erste Elektrode E1 ist vorzugsweise ein massiver Leiter. Die erste Elektrode E1 kann jedoch auch eine Vielzahl von Öffnungen oder ein Maschen- oder Gittermuster aufweisen. In einigen Ausführungsformen wird die zweite Elektrode E2 die Form eines schmalen Bandes annehmen, das die erste Elektrode E1 teilweise umgibt. In anderen Ausführungsformen, in denen die ersten und zweiten Elektroden E1 und E2 lediglich aneinander angrenzend sind, kann die zweite Elektrode E2 auch ein massiver Leiter sein oder ein Maschen- oder Gittermuster haben.

**[0053]** Der Kontrollschatzkreis **24** kann in vielen verschiedenen Weisen konstruiert sein und er kann mit einer Vielfalt von Energiequellen wie Wechselstrom, periodisch variierender Gleichstrom (wie eine Quadratwelle), kontinuierlicher Gleichstrom oder andere verwendet werden. [Fig. 4](#)–[Fig. 7](#) zeigen eine bevorzugte Kontrollschatzkreis-Konstruktion, die auf einfache Weise zur Verwendung mit einer Vielfalt von Energieversorgungen in einer Vielfalt von Betriebsmodi angepasst werden kann. Die Ausführungsform von [Fig. 4](#) verwendet Quadratwellen-Gleichstromenergie in einem getakteten Differenzialeingangs-Betriebsmodus; die Ausführungsform von [Fig. 5](#) verwendet kontinuierliche Gleichstromenergie in einem kontinuierlichen Differenzialeingangs-Gleichstrommodus; die Ausführungsform von [Fig. 6](#) verwendet Quadratwellen-Gleichstromenergie in einem getakteten Einakteingangsmodus und die Ausführungsform von [Fig. 7](#) verwendet kontinuierliche Gleichstromenergie

in einem kontinuierlichen Eintakteingangs-Gleichstrommodus.

**[0054]** Aus den [Fig. 4–Fig. 7](#) ist ersichtlich, dass der Kontrollschatzkreis **24** auf einfache Weise für verschiedene unterschiedliche Betriebsmodi angepasst werden kann. Die vorstehenden vier Betriebsmodi werden ausführlich beschrieben, um die von der Erfindung zugelassene Designflexibilität zu demonstrieren. Es sollte jedoch anerkannt werden, dass die Erfindung keineswegs auf diese vier Betriebsmodi beschränkt ist. Der jeweilige Betriebsmodus und die Energiequelle, die in einer bestimmten Anwendung genutzt werden, sind hauptsächlich von den Anforderungen und Spezifikationen der kontrollierten Vorrichtung abhängig.

**[0055]** Die eingerahmten Bereiche B1 und B2 in [Fig. 4–Fig. 7](#) kennzeichnen die Grenze zwischen Komponenten, von denen angenommen wird, dass sie auf dem IC-Chip **26** angeordnet sind, und Komponenten, die außerhalb des IC-Chips **26** angeordnet sind, wie die Elektroden E1 und E2, die Widerstände R1 und R2, die kontrollierte Vorrichtung (nicht dargestellt) und die Eingangs- und Ausgangsleitungen **30** bzw. **32**. Von den Abschnitten von [Fig. 4–Fig. 7](#), die außerhalb der eingerahmten Bereiche B1 und B2 sind, wird angenommen, dass sie sich auf dem IC-Chip **26** befinden, und sie sind für alle hierin dargestellten vier Figuren und Betriebsmodi identisch.

**[0056]** Die [Fig. 4–Fig. 7](#) zeigen einen Kontrollschatzkreis **24**, der einen Start- und Vorspannungsabschnitt **40**, einen Impulsgenerator **50**, einen Entscheidungsschatzkreisabschnitt **60** und einen selbst haltenden Latchabschnitt **70** umfasst, deren Funktionen nachstehend beschrieben werden. Jeder der vorstehenden Schatzkreisabschnitte **40**, **50**, **60** und **70** kann in einer Zahl von verschiedenen Weisen konstruiert werden, wie es Fachleuten auf dem Gebiet der Konstruktion von elektronischen Schaltkreisen bekannt ist.

**[0057]** Der Kontrollschatzkreis **24** umfasst außerdem erste, zweite und dritte Transistoren P1, P2 und P3. In den hierin beschriebenen Ausführungsformen sind die Transistoren P1–P3 P-MOS-Vorrichtungen, obwohl N-MOS-Vorrichtungen, bipolare Vorrichtungen und andere Transistorausführungen auch verwendet werden können. Der Kontrollschatzkreis **24** umfasst weiterhin einen Inverter I1, erste, zweite und dritte Dioden D1–D3, erste und zweite Kondensatoren C1 und C2, erste, zweite, dritte und vierte Transistorschalter SW1–SW4 und dritte und vierte Widerstände R3 und R4. Es sollte anerkannt werden, dass der dritte und vierte Widerstand R3 und R4 durch Stromquellen ersetzt werden können.

**[0058]** In jeder der in [Fig. 4–Fig. 7](#) dargestellten Ausführungsformen sind der Quellenanschluss **77**

des dritten Transistors P3 und die Energieeingangsanschlüsse **41**, **51**, **61** und **71** des Start- und Vorspannungsabschnitts **40**, des Impulsgenerator- und Logikabschnitts **50**, des Entscheidungsschaltkreises **60** bzw. des selbst haltende Latchabschnitts **70** elektrisch mit dem Anschluss PIN8 des IC-Chips **26** verbunden. Der Anschluss PIN8 ist wiederum elektrisch mit der Energieeingangsleitung **30** des Kontrollschatzkreises **24** verbunden, der wiederum elektrisch mit der Energiequelle **25** verbunden ist. Normalerweise befindet sich die Energiequelle **25** an der kontrollierten Vorrichtung (nicht dargestellt).

**[0059]** Ein Vorspannungsausgangsanschluss **43** vom Start- und Vorspannungsabschnitt **40** ist elektrisch mit den Gate-Anschlüssen G2 und G4 des zweiten und vierten Transistorschalters SW2 bzw. SW4 verbunden. In der bevorzugten Ausführungsform und wie hierin beschrieben sind die ersten bis vierten Transistorschalter SW1–SW4 N-MOS-Vorrichtungen, obwohl auch andere Transistorausführungen verwendet werden können.

**[0060]** Ein Einschalt-Rücksetzausgang **44** vom Start- und Vorspannungsabschnitt **40** ist elektrisch mit einem Einschalt-Rücksetzeingang **54** am Impulsgenerator- und Logikabschnitt **50** verbunden. Der Einschalt-Rücksetzausgang **44** des Start- und Vorspannungsabschnitts **40** ist außerdem elektrisch mit den Gate-Anschlüssen G1 und G3 der ersten und dritten Transistorschalter SW1 und SW3 verbunden.

**[0061]** Der interne Massereferenzausgang **42** vom Start- und Vorspannungsabschnitt **40** ist elektrisch mit Niedrigpotenzialplatten **102** und **103** der ersten und zweiten Widerstände C1 und C2, den Quellenanschlüssen S1, S2, S3 und S4 der ersten bis vierten Transistorschalter SW1–SW4, respektiv, dem internen Massereferenzausgang **52** des Impulsgenerator- und Logikabschnitts **50**, dem internen Massereferenzausgang **62** des Entscheidungsschaltkreises **60**, der Anode **98** der dritten Diode D3, den Niedrigpotenzialenden **96** und **97** der dritten und vierten Widerstände R3 und R4 und dem Anschluss PIN6 des IC-Chips **26** verbunden. Der damit beschriebene Knoten wird im Folgenden manchmal als die interne Massereferenz CHIP VSS bezeichnet werden.

**[0062]** Ein Impulsausgang **53** vom Impulsgenerator- und Logikabschnittsausgang **50** ist elektrisch mit den Quellenanschlüssen **80** und **81** der ersten und zweiten Transistoren P1 bzw. P2 und mit dem Anschluss PIN2 des IC **26** verbunden. Der Gate-Anschluss **82** des zweiten Transistors P1 ist elektrisch mit dem Anschluss PIN1 des IC **26** verbunden. Der Gate-Anschluss **83** des zweiten Transistors P2 ist elektrisch mit dem Anschluss PIN3 des IC **26** verbunden.

**[0063]** Der Drain-Anschluss **84** des ersten Transistors P1 ist elektrisch mit der Anode **90** der ersten Di-

ode D1 und dem Hochpotenzialende **94** des dritten Widerstands R3 verbunden. Der Drain-Anschluss **85** des zweiten Transistors P2 ist elektrisch mit der Anode **91** der zweiten Diode D2 und dem Hochpotenzialende **95** des vierten Widerstands R4 verbunden.

**[0064]** Die Katode **92** der ersten Diode D1 ist elektrisch mit dem PLUS-Eingangsanschluss **64** des Entscheidungsschaltkreises **60**, den Drain-Anschlüssen **86** und **87** der ersten und zweiten Transistorschalter SW1 und SW2 und der Hochpotenzialplatte **100** des ersten Kondensators C1 verbunden. Die Katode **93** der zweiten Diode D2 ist elektrisch mit dem MINUS-Eingangsanschluss **66** des Entscheidungsschaltkreises **60**, den Drain-Anschlüssen **88** und **89** der dritten und vierten Transistorschalter SW3 und SW4 und der Hochpotenzialplatte **101** des zweiten Kondensators C2 verbunden.

**[0065]** Der Logikausgang **63** des Entscheidungsschaltkreises **60** ist elektrisch mit dem Eingang **75** des Inverters I1 und dem Latch-Auslösereingang **73** des selbst haltenden Latchabschnitts **70** verbunden. Der Ausgang **72** des selbst haltenden Latchabschnitts **70** ist elektrisch mit dem Anschluss PIN4 des IC **26** verbunden.

**[0066]** In den dargestellten Ausführungsformen ist der Entscheidungsschaltkreis **60** so konstruiert, dass sein Ausgang **63** ein niedriges Potenzial aufweist, wenn seine PLUS- und MINUS-Eingänge **64** bzw. **66** auf im Wesentlichen gleichen Potenzialen liegen oder wenn der MINUS-Eingang **66** auf einem beträchtlich höheren Potenzial als der PLUS-Eingang **64** liegt. Der Ausgang **63** des Entscheidungsschaltkreises **60** liegt nur auf einem hohen Potenzial, wenn der PLUS-Eingang **64** auf einem beträchtlich höheren Potenzial liegt als der MINUS-Eingang **66**.

**[0067]** Der selbst haltende Latchabschnitt **70** ist so konstruiert, dass kein Strom von der Energieversorgung **25** des Kontrollschatlkreises **24** durch den Latchabschnitt **70** zur internen Massereferenz CHIP VSS und durch die dritte Diode D3 fließt, wenn der Logikausgang **63** des Entscheidungsschaltkreisabschnitts **60** auf einem niedrigen Potenzial liegt. Wenn der Logikausgang **63** des Entscheidungsschaltkreisabschnitts **60** jedoch auf einem hohen Potenzial liegt, liegt der Latchauslösereingang **73** auf einem hohen Potenzial, wodurch er den Latchschaltkreis **70** auslöst und ermöglicht, dass Strom durch den Latchabschnitt **70** von der Energieversorgung **25** des Kontrollschatlkreises **24** zur internen Massereferenz CHIP VSS und durch die dritte Diode D3 über die Energie-Eingangs- und -Ausgangsanschlüsse **71** bzw. **72** des Latches **70** fließt. Nachdem das Latch **70** ausgelöst wurde, bleibt es ausgelöst oder eingeschmolzen, bis die Energie vom Kontrollschatlkreis **24** entfernt wird. Die Konstruktion und Bauweise eines Latchabschnitts, der in dieser Weise funktioniert, ist

Fachleuten bekannt und braucht hierin nicht ausführlich beschrieben zu werden.

**[0068]** Der Ausgangsanschluss **76** des Inverters I1 ist elektrisch mit dem Gate-Anschluss **78** des dritten Transistors P3 verbunden. Der Drain-Anschluss **79** des dritten Transistors P3 ist elektrisch mit dem Anschluss PIN7 des IC **26** verbunden.

**[0069]** Die dritte Diode D3 ist vorgesehen, um Sperrvorspannung des Kontrollschatlkreises **24** zu verhindern, wenn die Touchschaltermittlung **20** in Mehrfachanwendungen verwendet wird. Sie kann in Anwendungen weggelassen werden, in denen nur ein einzelnes Touchpad **22** verwendet wird oder in denen mehrere Touchpads **22** verwendet werden, aber nicht in Mehrfachschaltung.

**[0070]** Die vorstehende Beschreibung der grundlegenden Konstruktion des Kontrollschatlkreises **24** ist für jede der in [Fig. 4–Fig. 7](#) dargestellten vier Betriebsmodi identisch. Die Unterschiede in der gesamten Vorrichtungskonfiguration zwischen den vier Betriebsmodi liegen hauptsächlich in den externen Anschlussverbindungen des IC **26**, die nachstehend ausführlich beschrieben werden.

**[0071]** [Fig. 4](#) zeigt eine Touchschaltermittlung **20**, die für Betrieb im getakteten Differenzialeingangsmodus konfiguriert ist, wie nachstehend beschrieben. Der Kontrollschatlkreis **24** ist für den Betrieb in diesem Modus konfiguriert, wie vorstehend für die [Fig. 4–Fig. 7](#) allgemein beschrieben. Der Anschluss PIN2 des IC **26** ist elektrisch mit den Hochpotenzialenden **104** und **105** der ersten und zweiten Widerstände R1 bzw. R2 verbunden. Der Anschluss PIN1 des IC **26** ist elektrisch sowohl mit dem Niedrigpotenzialende **106** des ersten Widerstands R1 als auch mit der ersten Elektrode E1 verbunden. Der Anschluss PIN3 des IC **26** ist elektrisch sowohl mit dem Niedrigpotenzialende **107** des zweiten Widerstands R2 als auch mit der zweiten Elektrode E2 verbunden.

**[0072]** Die als C3 und C4 in den [Fig. 4–Fig. 7](#) dargestellten Schaltkreiselemente sind keine diskreten elektrischen Komponenten. Die Bezugszeichen C3 und C4 repräsentieren vielmehr die Ableitkapazität der ersten und zweiten Elektroden E1 bzw. E2.

**[0073]** Der Anschluss PIN8 des IC **26** ist elektrisch mit der Eingangsleitung **30** verbunden, die wiederum elektrisch mit der Energiesignalquelle **25** an beispielsweise der kontrollierten Vorrichtung (nicht dargestellt) verbunden ist. Der Anschluss PIN4 des IC **26** ist elektrisch mit dem Anschluss PIN6 des IC **26** verbunden und verbindet dadurch den Ausgangsanschluss **72** des Latches **70** elektrisch mit der internen Massereferenz CHIP VSS und der Anode **98** der dritten Diode D3. Der Anschluss PIN7 des IC-Chips **26** ist in dieser Ausführungsform nicht extern terminiert.

Der Anschluss PIN5 des IC **26** ist elektrisch mit der Ausgangsleitung **32** verbunden, die wiederum elektrisch mit dem Hochpotenzialende **108** des fünften Widerstands R5 und der Ausgangsleitung **120** verbunden ist, die mit der kontrollierten Vorrichtung (nicht dargestellt) verbunden ist, entweder direkt oder über einen Prozessor oder eine andere zwischengeschaltete Vorrichtung (nicht dargestellt). Das Niedrigpotenzialende **109** des Widerstands R5 ist elektrisch mit der Systemmasse verbunden. In einer typischen Anwendung wird der Widerstand R5 eine beträchtliche Distanz von den anderen Komponenten, die die Touchschaltervorrichtung **20** umfasst, entfernt sein. Das heißt, dass in der bevorzugten Ausführungsform davon ausgegangen wird, dass der Widerstand R5 sich nicht nahe dem Touchpad **22** und dem Kontrollschatzkreis **24** befindet.

**[0074]** [Fig. 5](#) zeigt einen typischen Touchschalter-Kontrollschatzkreis **24**, der für Betrieb im kontinuierlichen Differenzialeingangs-Gleichstrommodus konfiguriert ist, wie nachstehend beschrieben. Der gesamte Kontrollschatzkreis und die Vorrichtung sind identisch zu denen vorstehend in [Fig. 4](#) beschriebenen, mit drei Ausnahmen. Ersten ist in der Ausführungsform von [Fig. 5](#) der Anschluss PIN7 des IC **26** elektrisch mit dem Hochpotenzialende **108** des Widerstands R5 und der Ausgangsleitung **120** verbunden, die entweder direkt oder über einen Prozessor oder eine andere zwischengeschaltete Vorrichtung (nicht dargestellt) mit der kontrollierten Vorrichtung (nicht dargestellt) verbunden ist, während der Anschluss PIN7 in der Ausführungsform von [Fig. 4](#) nicht extern terminiert ist. Zweitens sind in der Ausführungsform von [Fig. 5](#) die Anschlüsse PIN4 und PIN6 des IC **26** nicht elektrisch miteinander verbunden oder in anderer Weise extern terminiert, während sie das in der Ausführungsform von [Fig. 4](#) sind. Drittens ist in der Ausführungsform von [Fig. 5](#) der Anschluss PIN5 des IC **26** elektrisch mit dem Niedrigpotenzialende **109** des Widerstands R5 verbunden, während in der Ausführungsform von [Fig. 4](#) der Anschluss PIN5 des IC **26** elektrisch mit dem Hochpotenzialende **108** des fünften Widerstands und der kontrollierten Vorrichtung (nicht dargestellt) verbunden ist. Der fünfte Widerstand R5 wird, wie in der Ausführungsform von [Fig. 4](#), normalerweise eine beträchtliche Distanz von den anderen Komponenten, die die Touchschaltervorrichtung **20** umfasst, entfernt sein.

**[0075]** [Fig. 6](#) zeigt einen typischen Touchschalter-Kontrollschatzkreis, der für Betrieb im getakteten Eintakteingangsmodus konfiguriert ist, wie nachstehend beschrieben. Der Kontrollschatzkreis **24** ist konfiguriert, wie vorstehend im Allgemeinen für die [Fig. 4](#)–[Fig. 7](#) beschrieben. Der Anschluss PIN2 des IC **26** ist elektrisch mit den Hochpotenzialenden **104** und **105** der ersten und zweiten Widerstände R1 bzw. R2 verbunden. Der Anschluss PIN1 des IC **26** ist elektrisch mit sowohl dem Niedrigpotenzialende **106**

des ersten Widerstands R1 als auch mit der ersten Elektrode E1 verbunden. Der Anschluss PIN3 des IC **26** ist elektrisch mit sowohl dem Niedrigpotenzialende **107** des zweiten Widerstands R2 als auch mit dem Hochpotenzialende **110** der sechsten Widerstandselektrode R6 verbunden, so dass der zweite Widerstand R2 und der sechste Widerstand R6 einen Spannungsteiler bilden. Das Niedrigpotenzialende **111** des sechsten Widerstands R6 ist elektrisch mit der internen Massereferenz CHIP VSS verbunden, normalerweise an einem Punkt nahe dem Anschluss PIN5 des IC **26**. In [Fig. 6](#) ist die elektrische Verbindung des sechsten Widerstands R6 mit der internen Massereferenz CHIP VSS zur Klarheit durch die unterbrochene Linie „A-A“ dargestellt.

**[0076]** Der Anschluss PIN5 des IC **26** ist elektrisch mit der Eingangsleitung **30** verbunden, die wiederum elektrisch mit einer Energiesignalquelle **25** verbunden ist. Der Anschluss PIN5 des IC **26** ist elektrisch mit der Ausgangsleitung **32** verbunden, die wiederum elektrisch mit dem Hochpotenzialende **108** des fünften Widerstands R5 und mit der Ausgangsleitung **120** verbunden ist. Die Ausgangsleitung **120** ist elektrisch mit der kontrollierten Vorrichtung (nicht dargestellt) verbunden, entweder direkt oder über einen Prozessor oder eine andere zwischengeschaltete Vorrichtung. Der Anschluss PIN4 des IC **26** ist elektrisch mit dem Anschluss PIN6 des IC **26** verbunden. Der Anschluss PIN7 des IC **26** ist in dieser Ausführungsform nicht extern terminiert. In einer typischen Anwendung wird der fünfte Widerstand R5 eine beträchtliche Distanz von den anderen Komponenten, die die Touchschaltervorrichtung **20** umfasst, entfernt sein.

**[0077]** [Fig. 7](#) zeigt einen typischen Touchschalter-Kontrollschatzkreis, der für Betrieb im kontinuierlichen Eintakteingangs-Gleichstrommodus konfiguriert ist, wie nachstehend beschrieben. Der Kontrollschatzkreis **24** ist konfiguriert, wie vorstehend allgemein für die [Fig. 4](#)–[Fig. 7](#) beschrieben. Der gesamte Kontrollschatzkreis und die Vorrichtung sind identisch zu denen vorstehend in [Fig. 6](#) beschriebenen, mit drei Ausnahmen. Ersten ist in der Ausführungsform von [Fig. 7](#) der Anschluss PIN7 des IC **26** elektrisch mit dem Hochpotenzialende **108** des fünften Widerstands R5 und der Ausgangsleitung **120** verbunden, die wiederum mit der kontrollierten Vorrichtung (nicht dargestellt) verbunden ist, normalerweise über einen Mikroprozessor oder eine andere Steuerung (nicht dargestellt). Der Anschluss PIN7 des IC **26** ist in der Ausführungsform von [Fig. 6](#) nicht extern terminiert. Zweitens sind in der Ausführungsform von [Fig. 7](#) die Anschlüsse PIN4 und PIN6 des IC **26** nicht elektrisch miteinander verbunden oder in anderer Weise extern terminiert, während sie das in der Ausführungsform von [Fig. 6](#) sind. Drittens ist in der Ausführungsform von [Fig. 7](#) der Anschluss PIN5 des IC **26** elektrisch mit dem Niedrigpotenzialende **109** des fünften Widerstands R5 verbunden, während in der Ausführungs-

form von [Fig. 6](#) der Anschluss PIN5 des IC **26** elektrisch mit dem Hochpotenzialende **108** des fünften Widerstands und der Ausgangsleitung **120** verbunden ist. In einer typischen Anwendung wird der fünfte Widerstand R5 eine beträchtliche Distanz von den anderen Komponenten, die die Touchschaltervorrichtung **20** umfasst, entfernt sein. In [Fig. 7](#) ist die elektrische Verbindung des sechsten Widerstands R6 mit der internen Massereferenz CHIP VSS zur Klarheit durch die unterbrochene Linie „A-A“ dargestellt.

**[0078]** Eine Touchschaltervorrichtung **20**, die für den getakteten Differenzialeingangsmodus konfiguriert ist, arbeitet wie folgt. Bezug nehmend auf [Fig. 4](#), wird ein Energie-/Kontrollsignal **25** dem Anschluss PIN8 des IC **26** und danach den Energieeingangsan schlüssen **41, 51, 61** und **71** des Start- und Vorspannungsabschnitts **40**, des Impulsgenerator- und Logikabschnitts **50**, des Entscheidungsschaltkreises **60** bzw. des selbst haltenden Latchabschnitts **70** zugeführt.

**[0079]** Nach der Energieversorgung und nach einem geeigneten Verzögerungsintervall, um Stabilisierung zu gestatten (ungefähr 200 Mikrosekunden sind ausreichend), gibt der Start- und Vorspannungsabschnitt **40** ein Einschalt-Rücksetzsignal kurzer Dauer vom Ausgangsanschluss **44** an die Gate-Anschlüsse G1 und G3 des ersten Transistorschalters SW1 bzw. des dritten Transistorschalters SW3 aus, das bewirkt, dass die ersten und dritten Transistor schalter SW1 und SW3 einschalten und dadurch einen Stromweg von den Hochpotenzialplatten **100** und **101** der ersten und zweiten Kondensatoren C1 bzw. C2 zur internen Massereferenz CHIP VSS bereitstellen. Die Dauer des Einschalt-Rücksetzsignals reicht aus, um zu gestatten, dass jegliche Ladung, die an den ersten und zweiten Kondensatoren C1 und C2 vorhanden ist, im Wesentlichen vollständig zur internen Massereferenz CHIP VSS entladen wird. In dieser Weise nehmen die PLUS- und MINUS-Eingänge **64** und **66** zum Entscheidungsschaltkreisabschnitt **60** einen anfänglichen Niedrigpotenzialzustand an.

**[0080]** Im Wesentlichen zur gleichen Zeit sendet der Start- und Vorspannungsabschnitt **40** ein Einschalt-Rücksetzsignal vom Ausgang **44** zum Eingang **54** des Impulsgenerator- und Logikabschnitts **50**, wodurch dieser initialisiert wird. Nach einer geeigneten Verzögerung, damit der Impulsgenerator- und Logikabschnitt **50** stabilisieren kann, erzeugt der Impulsgenerator- und Logikabschnitt **50** einen Impuls und gibt ihn vom Impulsausgangsanschluss **53** über die ersten und zweiten Widerstände R1 und R2 an die ersten und zweiten Elektroden E1 und E2 und an die Quellenanschlüsse **80** und **81** der ersten und zweiten Transistoren P1 bzw. P2 aus. Der Impuls kann jede geeignete Wellenform wie ein Quadratwellen form-Impuls aufweisen.

**[0081]** Der Start- und Vorspannungsschaltkreis **40** gibt außerdem eine Vorspannungsspannung vom Vorspannungsausgang **43** an die Gate-Anschlüsse G2 und G4 der zweiten und vierten Transistorschalter SW2 bzw. SW4 aus. Die Vorspannungsspannung ist zum Impulsausgang zu den ersten und zweiten Elektroden E1 und E2 phasenverschoben. Das heißt, dass, wenn der Impulsausgang in einem hohen Zustand ist, der Vorspannungsspannungsausgang in einem niedrigen Zustand ist, und wenn der Impulsausgang in einem niedrigen Zustand ist, ist der Vorspannungsspannungsausgang in einem hohen Zustand.

**[0082]** Wenn ein Impuls an die ersten und zweiten Elektroden E1 und E2 durch die ersten und zweiten Widerstände R1 bzw. R2 angelegt wird, ist die Spannung an den Gate-Anschläßen **82** und **83** der ersten und zweiten Transistoren P1 und P2 anfänglich auf einem niedrigeren Potenzial als die an den Quellenanschlüssen **80** und **81** der ersten und zweiten Transistoren P1 bzw. P2, wodurch die ersten und zweiten Transistoren P1 und P2 unter Vorspannung gesetzt werden und bewirkt wird, dass sie eingeschaltet werden. Wenn die ersten und zweiten Transistoren P1 und P2 eingeschaltet sind, fließt Spannung durch die dritten und vierten Widerstände R3 und R4, wodurch ein Spitzenpotenzial an den Anodenanschlüssen **90** und **91** der ersten und zweiten Dioden D1 bzw. D2 erzeugt wird.

**[0083]** Wenn das Spitzenpotenzial an den Anoden **90** und **91** der ersten und zweiten Dioden D1 und D2 höher als das Potenzial über die ersten und zweiten Kondensatoren C1 und C2 ist, wird ein Spitzenstrom durch die ersten und zweiten Dioden D1 und D2 hergestellt, der bewirkt, dass die ersten und zweiten Kondensatoren C1 und C2 geladen werden, und ein Spitzenpotenzial an jedem der PLUS- und MINUS-Eingänge **64** und **66** zu Entscheidungsschaltkreisabschnitt **60** hergestellt wird. Diese Situation tritt beispielsweise nach dem ersten Impuls ein, nachdem der Kontrollschatlkreis **24** initialisiert wurde, weil die ersten und zweiten Kondensatoren C1 und C2 nach dem Start entladen wurden, wie oben beschrieben.

**[0084]** Wie für einen Fachmann offenkundig ist, sind die Vorspannung der ersten und zweiten Transistoren P1 und P2, der Strom durch die dritten und vierten Widerstände R3 und R4, das an den Anoden **90** und **91** der ersten und zweiten Dioden D1 und D2 erzeugte Spitzenpotenzial und das an den PLUS- und MINUS-Eingängen **64** und **66** erzeugte Spitzenpotenzial zum Entscheidungsschaltkreis **60** proportional zum Zustand des elektrischen Felds an den ersten und zweiten Elektroden E1 und E2. Der Zustand des elektrischen Felds nahe den Elektroden E1 und E2 variiert als Reaktion auf Stimuli, die nahe den Elektroden vorhanden sind.

**[0085]** Wenn der Kontrollschaltkreis **24** aktiviert wurde, wie oben beschrieben, und keine Stimuli in der Nähe von entweder der ersten oder der zweiten Elektroden E1 und E2 vorhanden sind, sind die Potenziale an jedem der PLUS- und MINUS-Eingänge **64** und **66** zum Entscheidungsschaltkreis **60** in einem Zustand, der als neutraler Zustand bezeichnet werden kann. In dem neutralen Zustand können die Potenziale an jedem der PLUS- und MINUS-Eingänge **64** und **66** im Wesentlichen gleich sein. Zur Verhinderung von unbeabsichtigten Aktivierungen kann es jedoch wünschenswert sein, den Kontrollschaltkreis **24** so einzustellen, dass der neutrale Zustand des MINUS-Eingangs **66** auf einem etwas höheren Potenzial als der neutrale Zustand des PLUS-Eingangs **64** liegt. Diese Anpassungen können bewirkt werden, indem die Konfigurationen der ersten und zweiten Elektroden E1 und E2 und die Werte der ersten und zweiten Widerstände R1 und R2 variiert werden, um die gewünschten Neutralzustand-Potenziale zu erreichen. Unabhängig von den Neutralzustand-Potenzialen wird beabsichtigt, dass der Ausgang **63** des Entscheidungsschaltkreises **60** auf einem niedrigen Potenzial sein wird, außer wenn der PLUS-Eingang **64** auf einem beträchtlich höheren Potenzial als der MINUS-Eingang **66** ist.

**[0086]** Wenn der Ausgang **63** des Entscheidungsschaltkreises **60** auf einem niedrigen Potenzial ist, bewirkt der Inverter I1, dass das Potenzial am Gate-Anschluss **78** des dritten Transistors P3 auf einem hohen Pegel ist, im Wesentlichen gleich zum Potenzial am Quellenanschluss **77**. In diesem Zustand steht der dritte Transistor P3 nicht unter Vorspannung und wird ausgeschaltet bleiben. In dieser Ausführungsform ist der Anschluss PIN7 des IC **26** jedoch nicht terminiert. Der Drain-Anschluss **79** des dritten Transistors P3 ist daher in einem Leerlaufzustand und der Zustand des dritten Transistors P3 hat keine Auswirkungen auf die Funktion der Vorrichtung. Außerdem wird, wenn der Ausgang **63** des Entscheidungsschaltkreises **60** und infolgedessen der Latchauslösereingang **73** in einem niedrigen Zustand sind, der selbst haltende Latchschaltkreis **70** nicht ausgelöst und wird kein Strom von der Energieversorgung **25** durch das Latch **70** zur internen Massereferenz CHIP VSS und durch die dritte Diode D3 fließen.

**[0087]** Über eine Zeitperiode, die durch die Impulsspannung, die Werte der ersten und zweiten Widerstände R1 und R2 und die Ableitkapazität der ersten und zweiten Elektroden E1 und E2 (in den Figuren als virtuelle Kondensatoren C3 und C4 dargestellt) bestimmt wird, steigt das Potenzial an den ersten und zweiten Elektroden E1 und E2 schließlich auf im Wesentlichen gleich der Impulsspannung und damit der Spannung an den Quellenanschlüssen **80** und **81** der ersten und zweiten Transistoren P1 und P2, wodurch die ersten und zweiten Transistoren P1 und P2 vor-

spannungslos werden. Wenn dieser Zustand erreicht ist, schalten die ersten und zweiten Transistoren P1 und P2 aus, und die Potenziale an den Anoden **90** und **91** der ersten und zweiten Dioden D1 und D2 beginnen mit einer im Wesentlichen gleichen Rate hin zum Pegel der internen Massereferenz CHIP VSS zu steigen. Schließlich ist es wahrscheinlich, dass das Anodenpotenzial an jedem der ersten und zweiten Dioden D1 und D2 unter das jeweilige Katodenpotenzial fällt. An diesem Punkt werden die Dioden D1 und D2 in Sperrrichtung vorgespannt und verhindern die Entladung der ersten und zweiten Kondensatoren C1 und C2.

**[0088]** Wenn der Impuls am Ausgang **53** in einen niedrigen Zustand geht, geht der Vorspannungsspannungsausgang relativ zur internen Massereferenz CHIP VSS in einen hohen Zustand und legt die erhöhte Vorspannungsspannung an die Gate-Anschlüsse G2 und G4 der zweiten und vierten Transistorschalter SW2 und SW4 an. In diesem Zustand werden die zweiten und vierten Transistorschalter SW2 und SW4 geringfügig vorgespannt und schalten ausreichend ein, um eine langsame, kontrollierte Entladung der ersten und zweiten Kondensatoren C1 und C2 zur internen Massereferenz CHIP VSS zu bewirken. Wenn der Impuls anschließend in einen hohen Zustand geht, kehrt die Vorspannungsspannung in einen niedrigen Zustand zurück, die zweiten und vierten Transistorschalter SW2 und SW4 schalten aus, und der Schaltkreis reagiert, wie eingangs beschrieben.

**[0089]** Wenn ein Stimulus an oder nahe der zweiten Elektrode E2 vorhanden ist, wenn der Impuls vom Impulsgenerator- und Logikabschnitt **50** auf ein hohes Potenzial geht, operiert der erste Transistor P1, wie hierin vorstehend beschrieben. Das heißt, der erste Transistor P1 ist anfangs vorgespannt und erlaubt, dass ein gewisser Strom durch den dritten Widerstand R3 fließt, der ein Spitzenpotenzial an der Anode **90** der ersten Diode D1 erzeugt und erlaubt, dass ein Spitzenpotenzial an der Anode **90** der ersten Diode D1 erzeugt wird, wodurch der ersten Kondensator C1 geladen wird und ein Spitzenpotenzial am PLUS-Eingang **64** zum Entscheidungsschaltkreis **60** hergestellt wird. Nachdem sich die Spannung an der ersten Elektrode E1 als Reaktion auf den ankommenen Impuls stabilisiert hat, wird der erste Transistor P1 vorspannungslos und schaltet aus.

**[0090]** Der zweite Transistor P2 operiert in einer sehr ähnlichen Weise mit der Ausnahme, dass das Vorhandensein des Stimulus nahe der zweiten Elektrode E2 die RC-Zeitkonstante für dieses Schaltkreissegment ändert wird, wodurch die Zeit verlängert wird, die erforderlich ist, damit sich das Potenzial an der zweiten Elektrode E2 stabilisiert. Daraus ergibt sich, dass der zweite Transistor P2 für eine längere Zeitperiode als der erste Transistor P1 vorgespannt

bleiben wird, wodurch ein größerer Spaltenstrom durch den vierten Widerstand R4 fließen kann, als durch den dritten Widerstand R3 fließt, wodurch ein Spaltenpotenzial an der Anode 91 der zweiten Diode D2 erzeugt wird, das größer ist als das an der Anode 90 der ersten Diode D1 vorhandene Spaltenpotenzial. Infolgedessen wird ein Spaltenstrom durch die zweite Diode D2 fließen und bewirken, dass der zweite Kondensator C2 geladen wird, was schließlich in einem Spaltenpotenzial am MINUS-Eingang 66 zum Entscheidungsschaltkreis 60 resultiert, der größer ist als das Spaltenpotenzial am PLUS-Eingang 64 zum Entscheidungsschaltkreis. Da der Entscheidungsschaltkreis 60 konfiguriert ist, dass sein Ausgang auf einem niedrigen Potenzial ist, wenn das Potenzial am MINUS-Eingang 66 größer als das oder im Wesentlichen gleich dem Potenzial am PLUS-Eingang 64 ist, wird der Anschluss 63 des Entscheidungsschaltkreises 60 auf einem niedrigen Potenzial sein.

**[0091]** Wenn der Ausgangsanschluss 63 des Entscheidungsschaltkreises 60 und infolgedessen der Latchauslöser-Eingangsanschluss 73 auf einem niedrigen Potenzial sind, wird das selbst haltende Latch 70 nicht ausgelöst. Der Inverter I1 und der dritte Transistor P3 werden operieren, wie vorher beschrieben, obwohl, wie schon gesagt, der Zustand des dritten Transistors P3 in dieser Konfiguration keine Auswirkungen hat.

**[0092]** In dem Fall, dass eine Verunreinigung oder ein Fremdkörper oder ein anderer Stimulus sowohl die erste als auch die zweite Elektrode E1 und E2 im Wesentlichen bedeckt oder darauf angewandt wird, wird das System ungefähr in der gleichen Weise reagieren, wie es reagieren würde, wenn kein Stimulus an entweder der ersten Elektrode oder der zweiten Elektrode vorhanden ist. Wenn jedoch Verunreinigungen oder ein Fremdkörper nahe an beiden Elektroden E1 und E2 vorhanden sind, wird die RC-Zeitkonstante für diese Segmente des Schaltkreises derart geändert, dass es für die Spannung an sowohl der ersten als auch der zweiten Elektrode E1 bzw. E2 länger dauert, im Wesentlichen gleich der Impulsspannung zu werden. Infolgedessen schalten sowohl der erste als auch der zweite Transistor P1 und P2 ein und gestatten, dass mehr Strom durch die dritten und vierten Widerstände R3 und R4 fließen kann, als sie in einem Zustand würden, in dem weder die erste noch die zweite Elektrode E1 oder E2 einem Stimulus ausgesetzt ist. Die ersten und zweiten Transistoren P1 und P2 werden jedoch anschließend gleich vorgespannt. Daher entwickelt sich ein im Wesentlichen gleiches Spaltenpotenzial an den Anoden 90 und 91 der ersten und zweiten Dioden D1 und D2, wodurch bewirkt wird, dass ein im Wesentlichen gleicher Spaltenstrom durch die ersten und zweiten Dioden D1 und D2 fließt, der die ersten und zweiten Kondensatoren C1 und C2 auflädt und ein im Wesentlichen gleiches Spaltenpotenzial an sowohl dem PLUS- als

auch dem MINUS-Eingang 64 und 66 zum Entscheidungsschaltkreis 60 hergestellt wird. In diesem Zustand wird der Ausgangsanschluss 63 des Entscheidungsschaltkreisabschnitts 60 auf einem niedrigen Potenzial sein, der Latchauslöser-Eingangsanschluss 73 des selbst haltenden Latches 70 wird auf einem niedrigen Potenzial sein und das Latch 70 bleibt unausgelöst. Wie vorher beschrieben, ist der Zustand des Inverters I1 und des dritten Transistors P3 in dieser Ausführungsform ohne Auswirkungen.

**[0093]** In der Situation, in der ein Stimulus nahe der ersten Elektrode E1, aber nicht der zweiten Elektrode, angewandt wird, wird der zweite Transistor P2 anfangs vorgespannt und wird einschalten, wodurch ein Strom durch den vierten Widerstand R4 hergestellt und ein Spaltenpotenzial am Anodenanschluss 90 der zweiten Diode D2 erzeugt wird. Ein Spaltenstrom wird durch die zweite Diode D2 fließen, den zweiten Kondensator C2 aufladen und ein Spaltenpotenzial am MINUS-Eingang 66 des Entscheidungsschaltkreisabschnitts 60 herstellen. Während die Spannung am Gate-Anschluss 81 des zweiten Transistors P2 auf den Pegel der Impulsspannung steigt, wird der zweite Transistor P2 vorspannungslos und schaltet aus. Die zweite Diode D2 wird dann in Sperrrichtung vorgespannt und verhindert das Entladen des zweiten Kondensators C2.

**[0094]** Wie für einen Fachmann offenkundig ist, wird das Vorhandensein eines Stimulus nahe der ersten Elektrode E1 die Zeit verlängern, die erforderlich ist, damit sich das Potenzial an der ersten Elektrode E1 stabilisiert. Infolgedessen wird der erste Transistor P1 für eine längere Zeitperiode vorgespannt bleiben als der zweite Transistor P2, so dass ein größerer Spaltenstrom durch den dritten Widerstand R3 als durch den vierten Widerstand R4 fließen kann, wodurch ein Spaltenpotenzial an der Anode 90 der ersten Diode D1 erzeugt wird, das größer ist als das Potenzial, das an der Anode 91 der zweiten Diode D2 anliegt. Als Konsequenz wird ein Spaltenstrom größerer Größenordnung und/oder Dauer durch die erste Diode D1 als durch die zweite Diode D2 fließen, der bewirkt, dass der erste Kondensator C1 geladen wird, was schließlich in einem Spaltenpotenzial am PLUS-Eingang 64 zum Entscheidungsschaltkreis 60 resultiert, das im Wesentlichen größer ist als das Spaltenpotenzial am MINUS-Eingang 66 zum Entscheidungsschaltkreis 60. Da der Entscheidungsschaltkreis 60 so konfiguriert ist, dass der Ausgangsanschluss 63 in einem hohen Zustand sein wird, wenn das Potenzial am PLUS-Eingang 64 größer ist als das Potenzial am MINUS-Eingang 66, wird der Ausgang 63 des Entscheidungsschaltkreises 60 auf einem hohen Potenzial sein.

**[0095]** Wenn der Ausgang 63 des Entscheidungsschaltkreises 60 auf einem hohen Potenzial ist, wird der Inverter I1 bewirken, dass das Potenzial am

Gate-Anschluss **78** des dritten Transistors P3 relativ zum Potenzial am Quellenanschluss **77** niedrig ist, wodurch der dritte Transistor P3 vorgespannt wird und bewirkt wird, dass er einschaltet. Da der Anschluss PIN7 des IC **26** in dieser Ausführungsform nicht terminiert ist, hat der Zustand des dritten Transistors P3 keine Auswirkungen.

**[0096]** Wenn der Ausgangsanschluss **63** des Entscheidungsschaltkreises **60** auf einem hohen Potenzial ist, wird auch der Auslösereingangsanschluss **73** des selbst haltenden Latchschaltkreises **70** auf einem hohen Potenzial sein, wodurch das Latch **70** ausgelöst wird. Wenn das selbst haltende Latch **70** ausgelöst wird, wird ein Stromweg von der Energieversorgung **25** zur internen Massereferenz CHIP VSS und durch die dritte Diode D3 hergestellt, wodurch der Rest des Kontrollschatlkreises **24** einschließlich des Start- und Vorspannungsabschnitts **40**, des Impulsgenerator- und Logikabschnitts **50** und des Entscheidungsschaltkreisabschnitts **60** effektiv kurzgeschlossen wird. In diesem Zustand werden diese Abschnitte des Kontrollschatlkreises **24** im Wesentlichen stromlos und funktionieren nicht mehr.

**[0097]** Sobald das selbst haltende Latch **70** ausgelöst wurde, bleibt es unabhängig vom anschließenden Zustand von Stimuli nahe einem oder beiden der Elektroden E1 und E2 ausgelöst. Das Latch **70** wird zurückgesetzt, wenn die Energie von der Energieversorgung **25** auf einen Zustand nahe Null geht, wie wenn das Rechteckwellen-Strobesignal von der Energieversorgung **25** dieses Beispiels auf Null fällt.

**[0098]** Während das selbst haltende Latch **70** im ausgelösten Zustand ist, wird ein Bereitschaftszustandssignal durch den fünften Widerstand R5 und zurück zur kontrollierten Vorrichtung (nicht dargestellt) geführt. In dieser Weise emuliert die Touchschaltervorrichtung **20** die Änderung des Zustands, die mit einem mechanischen Schalter in Dauerkontaktausführung assoziiert ist.

**[0099]** Jetzt Bezug nehmend auf [Fig. 5](#), ist der Betrieb einer Touchschaltervorrichtung **20**, die für den kontinuierlichen Differenzialeingangs-Gleichstrommodus konfiguriert ist, wie folgt. Der Kontrollschatlkreis **24** bis zum und einschließlich des Entscheidungsschaltkreises **60** funktioniert in der im Wesentlichen gleichen Weise, wie wenn er für den getakteten Differenzialeingangs-Betriebsmodus konfiguriert wäre, wie oben unter Bezugnahme auf [Fig. 4](#) beschrieben. Das heißt, wenn kein Stimulus nahe entweder der ersten oder der zweiten Elektrode E1 und E2 vorhanden ist, wenn ein Stimulus nahe sowohl der ersten als auch der zweiten Elektrode E1 und E2 vorhanden ist oder wenn ein Stimulus nahe der zweiten Elektrode E2 vorhanden ist, aber nicht nahe der ersten Elektrode E1, wird der Ausgang **63** des Entscheidungsschaltkreises **60** auf einem niedrigen Potenzial

sein. Wenn ein Stimulus nahe der ersten Elektrode E1 vorhanden ist, aber nicht nahe der zweiten Elektrode E2, wird der Ausgang **63** des Entscheidungsschaltkreises **60** auf einem hohen Pegel sein.

**[0100]** Wie leicht in [Fig. 5](#) ersichtlich ist, ist der Ausgang **72** des selbst haltenden Latchschaltkreises **70** in dieser Ausführungsform nicht terminiert, und daher ist das selbst haltende Latch **70** im Differenzialeingangs-Gleichstrommodus nicht betriebsfähig. Der Drain-Anschluss **79** des dritten Transistors P3 ist in dieser Ausführungsform jedoch elektrisch mit der internen Massereferenz CHIP VSS und der Ausgangsleitung **32** verbunden und wird dadurch zu einem funktionsfähigen Teil des Kontrollschatlkreises **24**. Wenn der Ausgang **63** des Entscheidungsschaltkreises **60** auf einem niedrigen Potenzial ist, bewirkt der Inverter I1, dass das Potenzial am Gate-Anschluss **78** des dritten Transistors P3 auf einem hohen Potenzial ist, im Wesentlichen gleich dem Potenzial-Quellenanschluss **77**. In diesem Zustand ist der dritte Transistor P3 nicht vorgespannt und schaltet nicht ein. Wenn der Ausgang **63** des Entscheidungsschaltkreises **60** auf einem hohen Potenzial ist, bewirkt der Inverter I1, dass das Potenzial am Gate-Anschluss **78** des dritten Transistors P3 auf einem niedrigen Potenzial im Vergleich mit dem Potenzial am Quellenanschluss **77** ist. In diesem Zustand wird der dritte Transistor P3 vorgespannt und schaltet ein, wodurch Strom durch den dritten Transistor P3 und den fünften Widerstand R5 hergestellt wird. Der Ausgangsleitungswiderstand R5 begrenzt den Strom durch den dritten Transistor P3 derart, dass der Rest des Kontrollschatlkreises **24** nicht kurzgeschlossen wird und funktionsfähig bleibt.

**[0101]** In dem in [Fig. 5](#) dargestellten Gleichstrommodus reagiert der Kontrollschatlkreis **24** auch auf das Entfernen des Stimulus aus der Nähe der ersten Elektrode E1. Solange der Stimulus in der Nähe der ersten Elektrode E1 bleibt, aber nicht der zweiten Elektrode E2, wird jedes Mal, wenn der Impuls in einen hohen Zustand geht, ein Spitzenpotenzial an der Anode **90** der ersten Diode D1 erzeugt, das höher ist als das Spitzenpotenzial an der Anode **91** der zweiten Diode D2. Infolgedessen wird das Spitzenpotenzial am PLUS-Eingang **64** zum Entscheidungsschaltkreis **60** auf einem höheren Pegel sein als das Spitzenpotenzial am MINUS-Eingang **66** und wird sich der Kontrollschatlkreis **24** so verhalten, wie oben beschrieben. Wenn der Stimulus jedoch entfernt wird und kein Stimulus nahe entweder der ersten Elektrode E1 oder der zweiten Elektrode E2 vorhanden ist, wird die Ladung des ersten Kondensators C1 mittels der Vorspannungsfunktion des zweiten Transistor-Schalters SW2 schließlich in einen neutralen Zustand entladen. An diesem Punkt wird das Potenzial am PLUS-Eingang **64** des Entscheidungsschaltkreises **60** nicht länger höher oder im Wesentlichen höher sein als das Potenzial am MINUS-Eingang **66**, und

der Ausgang **63** des Entscheidungsschaltkreises **60** kehrt in einen niedrigen Zustand zurück.

**[0102]** In dieser Weise emuliert die im Differenzialeingangs-Gleichstrommodus operierende Touchschaltervorrichtung **20** einen mechanischen Schalter in Wischkontakt-Ausführung, der zum Schließen gedrückt und zum Öffnen freigegeben werden muss. Es sollte anerkannt werden, dass der Kontrollschatzkreis mit minimalen Änderungen konfiguriert werden könnte, um einen mechanischen Schalter zu emulieren, der zum Öffnen gedrückt und zum Schließen freigegeben werden muss.

**[0103]** Jetzt Bezug nehmend auf [Fig. 6](#), operiert die für den getakteten Eintakteingangs-Betriebsmodus konfigurierte Touchschaltervorrichtung **20** wie folgt. Wenn ein Impuls an die erste Elektrode E1 und an die ersten und zweiten Widerstände R1 und R2 angelegt wird, fließt Strom durch den zweiten Widerstand R2 und den sechsten Widerstand R6. Die zweiten und sechsten Widerstände R2 und R6 sind als ein Spannungsteiler konfiguriert; das heißt, dass, wenn der Impulsausgang in einem hohen Zustand ist, der Gate-Anschluss **83** des zweiten Transistors P2 auf einem niedrigeren Potenzial sein wird als der Quellenanschluss **81** des zweiten Transistors P2. Daher wird, wenn der Impulsausgang **53** in einem hohen Zustand ist, der zweite Transistor P2 kontinuierlich vorgespannt sein und wird zulassen, dass ein konstanter Strom durch den vierten Widerstand R4 fließt, wodurch ein Referenzpotenzial an der Anode **91** der zweiten Diode D2 erzeugt wird. Das Referenzpotenzial an der Anode **91** der zweiten Diode D2 wird einen Strom durch die zweite Diode D2 herstellen, wodurch bewirkt wird, dass der zweite Kondensator C2 geladen wird, und dadurch wird ein Referenzpotenzial am MINUS-Eingang **66** zum Entscheidungsschaltkreis **60** erzeugt. Wenn das Referenzpotenzial am MINUS-Eingang **66** im Wesentlichen gleich dem Referenzpotenzial an der Anode **91** der zweiten Diode D2 wird, wird der Strom durch die zweite Diode D2 aufhören.

**[0104]** Gleichzeitig wird, wenn kein Stimulus an der ersten Elektrode E1 vorhanden ist, der an den Quellenanschluss **80** des ersten Transistors P1 und an die erste Elektrode E1 angelegte Impuls anfangs bewirken, dass der erste Transistor P1 vorgespannt wird und einschaltet. Dadurch wird ein Strom durch den dritten Widerstand R3 hergestellt, und ein Spitzenspotenzial wird an der Anode **90** der ersten Diode D1 erzeugt. Das Spitzenspotenzial wird einen Spitzstrom durch die erste Diode D1 herstellen, der den ersten Kondensator C1 auflädt und ein Spitzenspotenzial am PLUS-Eingang **64** des Entscheidungsschaltkreises erzeugt. Die Widerstände R1, R2, R3, R4 und R6 werden so ausgewählt, dass, wenn kein Stimulus nahe der ersten Elektrode E1 vorhanden ist, das Referenzpotenzial am MINUS-Eingang **66** des Ent-

scheidungsschaltkreises **60** größer als das oder gleich dem Spitzenspotenzial am PLUS-Anschluss **64** des Entscheidungsschaltkreises **60** sein wird.

**[0105]** In diesem Zustand wird der Ausgang **63** des Entscheidungsschaltkreises **60** auf einem niedrigen Potenzial sein und das selbst haltende Latch **70** wird nicht ausgelöst. Außerdem wird der Inverter I1 bewirken, dass das Potenzial am Gate-Anschluss **78** des dritten Transistors P3 in einem hohen Zustand sein wird, im Wesentlichen gleich dem Quellenanschluss **77**, so dass der dritte Transistor P3 vorspannungslos wird und ausgeschaltet bleibt. Dies hat jedoch keine Auswirkungen, da der Drain-Anschluss **79** des dritten Transistors P3 in dieser Ausführungsform in einem Leerlaufzustand ist.

**[0106]** Diese Ausführungsform erfordert keine zweite Elektrode, obwohl ein Touchpad mit zwei Elektroden zur Verwendung in diesem Modus angepasst werden kann. In dem Fall, dass ein Touchpad mit zwei Elektroden für Verwendung in diesem Betriebsmodus angepasst wird, hat das Vorhandensein oder Nichtvorhandensein eines Stimulus nahe der zweiten Elektrode keine Auswirkungen auf die Operation des Schaltkreises.