(19) 日本国特許庁(JP)

## (12) 特 許 公 報(B2)

(11) 特許番号

特許第4656544号

(P4656544)

(45) 発行日 平成23年3月23日(2011.3.23)

(24) 登録日 平成23年1月7日(2011.1.7)

(51) Int.Cl.

**G 1 1 B 20/18 (2006.01)**

F 1

|         |       |         |

|---------|-------|---------|

| G 1 1 B | 20/18 | 5 1 2 C |

| G 1 1 B | 20/18 | 5 7 2 B |

| G 1 1 B | 20/18 | 5 7 2 G |

| G 1 1 B | 20/18 | 5 7 4 H |

| G 1 1 B | 20/18 | 5 3 6 F |

請求項の数 9 (全 12 頁) 最終頁に続く

(21) 出願番号 特願2008-526460 (P2008-526460)

(86) (22) 出願日 平成18年6月22日 (2006.6.22)

(65) 公表番号 特表2009-505316 (P2009-505316A)

(43) 公表日 平成21年2月5日 (2009.2.5)

(86) 國際出願番号 PCT/EP2006/063457

(87) 國際公開番号 WO2007/020123

(87) 國際公開日 平成19年2月22日 (2007.2.22)

審査請求日 平成21年2月24日 (2009.2.24)

(31) 優先権主張番号 11/205,713

(32) 優先日 平成17年8月17日 (2005.8.17)

(33) 優先権主張国 米国(US)

(73) 特許権者 390009531

インターナショナル・ビジネス・マシーンズ・コーポレーション

INTERNATIONAL BUSINESS MACHINES CORPORATION

アメリカ合衆国10504 ニューヨーク

州 アーモンク ニュー オーチャード

ロード

(74) 代理人 100108501

弁理士 上野 剛史

(74) 代理人 100112690

弁理士 太佐 種一

(74) 代理人 100091568

弁理士 市位 嘉宏

最終頁に続く

(54) 【発明の名称】縦方向位置データにエラー訂正能力を与える方法及び装置

## (57) 【特許請求の範囲】

## 【請求項1】

テープ記憶システムにおいて縦方向位置(LPOS)ワードにエラー訂正能力を提供する方法であって、

複数の偶数LPOSワードと複数の奇数LPOSワードとを介してデータを符号化するステップであって、

前記偶数LPOSワードのうちの1つは

S y , L 0 , L 1 , L 2 , L 3 , X , Y , T x

を含み、

前記奇数LPOSワードのうちの1つは

S y , L 0 , L 1 , L 4 , L 5 , X , Y , T x

を含み、

ここで、S y はワード同期マークであり、

L 0 は縦方向位置における最下位シンボルであり、

L 1 は縦方向位置における、L 0 の次の上位シンボルであり、

L 2 は縦方向位置における、L 1 の次の上位シンボルであり、

L 3 は縦方向位置における、L 2 の次の上位シンボルであり、

L 4 は縦方向位置における、L 3 の次の上位シンボルであり、

L 5 は縦方向位置における、L 4 の次の上位シンボルであり、

T x はテープ製造者情報のシンボルであり、

10

20

X , Yは次の8ビット: a , b , c , 1 , d , e , f , 1として符号化されたラン

レンジス・リミテッド(RLL)制限エラー訂正コードであり、

ここで、a , b , c , d , e , 及びfは短縮拡張ハミング・コードに関連付けられた

6個のパリティ・ビットである、前記符号化するステップと、

前記符号化されたデータを、

前記LPOSワードの各々について複数のシンドローム・ビットを生成すること、

前記LPOSワードのうちの1つの中にエラーがあるか無いかをそれに対応するシンドローム・ビットに基づいて判定すること

によって復号するステップと、

を含む、前記方法。

10

#### 【請求項2】

もし前記1つのLPOSワードのシンドローム・ビット合計が0又は1に等しければ前記1つのLPOSワードにエラーは無いと結論するステップを更に含む、請求項1に記載の方法。

#### 【請求項3】

もし前記1つのLPOSワードのシンドローム・ビット合計が3に等しければ前記1つのLPOSワードに1ビットのエラーがあると結論するステップを更に含む、請求項1に記載の方法。

#### 【請求項4】

もし前記1つのLPOSワードのシンドローム・ビット合計が2, 4, 5又は6に等しければ前記1つのLPOSワードに1ビットより多いエラーがあると結論するステップを更に含む、請求項1に記載の方法。

20

#### 【請求項5】

縦方向位置(LPOS)ワードのためにエラー訂正能力を有するテープ記憶システムであって、

複数の偶数LPOSワード及び複数の奇数LPOSワードを介してデータを符号化するための手段であって、

前記偶数LPOSワードのうちの1つは

Sy , L0 , L1 , L2 , L3 , X , Y , Tx

を含み、

30

前記奇数LPOSワードのうちの1つは

Sy , L0 , L1 , L4 , L5 , X , Y , Tx

を含み、

ここで、Syはワード同期マークであり、

L0は縦方向位置における最下位シンボルであり、

L1は縦方向位置における、L0の次の上位シンボルであり、

L2は縦方向位置における、L1の次の上位シンボルであり、

L3は縦方向位置における、L2の次の上位シンボルであり、

L4は縦方向位置における、L3の次の上位シンボルであり、

L5は縦方向位置における、L4の次の上位シンボルであり、

40

Txはテープ製造者情報のシンボルであり、

X , Yは次の8ビット: a , b , c , 1 , d , e , f , 1として符号化されたラン

レンジス・リミテッド(RLL)制限エラー訂正コードであり、

ここで、a , b , c , d , e , 及びfは短縮拡張ハミング・コードに関連付けられた

6個のパリティ・ビットである、前記符号化するための手段と、

前記符号化されたデータを、

前記LPOSワードの各々について複数のシンドローム・ビットを生成すること、

前記LPOSワードのうちの1つの中にエラーがあるか無いかを、それに対応するシンドローム・ビットに基づいて判定すること

によって復号するための手段と

50

を含む、前記テープ記憶システム。

【請求項 6】

もし前記 1 つの L P O S ワードのシンドローム・ビット合計が 0 又は 1 に等しければ前記 1 つの L P O S ワードにエラーは無いと結論するための手段を更に含む、請求項 5 に記載のテープ記憶システム。

【請求項 7】

もし前記 1 つの L P O S ワードのシンドローム・ビット合計が 3 に等しければ前記 1 つの L P O S ワードに 1 ビットのエラーがあると結論するための手段を更に含む、請求項 5 に記載のテープ記憶システム。

【請求項 8】

もし前記 1 つの L P O S ワードのシンドローム・ビット合計が 2 , 4 , 5 又は 6 に等しければ前記 1 つの L P O S ワードに 1 ビットより多いエラーがあると結論するための手段を更に含む、請求項 5 に記載のテープ記憶システム。

【請求項 9】

縦方向位置 ( L P O S ) ワードにエラー訂正能力を提供するためのコンピュータ・プログラムであって、テープ記憶システムに、請求項 1 ~ 4 のいずれか一項に記載の方法の各ステップを実行させる前記コンピュータ・プログラム。

【発明の詳細な説明】

【技術分野】

【0001】

10

本発明は、一般的にテープ記憶システムに関する。特に、本発明は、テープ記憶システムにおいて縦方向位置 ( L P O S ) データを提供する方法及び装置に関する。更に特に、本発明は、テープ記憶システムにおいて L P O S ワードにエラー訂正能力を提供する方法及び装置に関する。

【背景技術】

【0002】

テープ記憶システムは、他の記憶技術と同じ低コストで大容量の組み合わせ利点を提供しないので、依然としてデータ・バックアップを提供するための最も効率的でコスト効率の良い手段である。その上、テープ記憶システムは非常に信頼できるものであることが照明されている。

30

【0003】

一般的に使われているリニア・マルチチャネル双方向テープ・フォーマットのいろいろな利点を結合させることにより、リニア・テープ・オープン ( Linear Tape - Open ( L T O ) ) 技術はテープ記憶システムの容量と性能を最大にするべく開発された。 L T O テープは、縦方向に予め書き込まれたサーボ・トラックを有するテープ・フォーマットを使用する。サーボ・トラックはタイミング・ベースのトラック追従位置エラー方式を提供する。サーボ・トラックは、5 , 5 , 4 及び 4 遷移というグループを成すバーストで発生する記録されたフラックス遷移の繰り返しパターンを含む。 5 バーストのセット間のタイミングと 4 バーストのセット間のタイミングとはトラック追従のための位置情報を提供する。更に、5 バースト内の個々の遷移は、縦方向位置情報 ( L P O S ) をサーボ・トラック内に符号化する仕方で移相される。

40

【0004】

L P O S 情報は、テープに書き込まれ或いは読み取られるデータ・レコードの縦方向位置を追跡するために使用され、また読み取り又は書き込みプロセスが一時的に停止したときのデータ・レコードの位置を突き止めるために使用される。位相符号化された L P O S 情報を検出することにより、テープ記憶システムは、テープに縦方向に沿うランドマークに関してのテープ位置を判定することができる。テープ上のデータ・ファイルの L P O S 位置も、読み出しのために又は書き込み ( テープに書き込まれた最後のファイルの終わりに新しいファイルを追加すること ) のための後のテープ・カートリッジ装填のときにデータ・ファイルの位置を突き止めるために用いられるべくボリューム制御データに格納される

50

。 L P O S データは、読み書きヘッドを所要速度でデータ・レコードの先頭に位置させ、また、新しいデータ転送動作の開始を可能にする位置を追跡するためにテープ記憶サーボ制御システムがテープの起動及び停止を決定し、またテープを後方に引くための主要な位置情報として使用される。

【発明の開示】

【発明が解決しようとする課題】

【0005】

L P O S データは、通例、如何なるエラーも許容することができない。しかし、他のサーボ・ヘッドがスマートされたり或いは短絡したりしたためにテープ駆動機構が单一チャネルに縮小したならば、そのチャネルにおける単一のビット・エラーは書き込みストップ(Stop Write)状態を引き起こし得る。従って、L P O S データは、エラー発生後に良好なサーボ・ヘッドが動作し続けることができるよう、或るレベルのエラーを許容できなければならない。

【0006】

上記の問題に対する1つの公知解決策はL P O S ワードにリード・ソロモン・パリティ・シンボルを付け加えることであるが、それはL P O S ワードの長さを増大させ、また、リード・ソロモン・ワードは同期化に配慮するためにL P O S フォーマットにより要求されるベース-14ではないので、L P O S ワードとの同期化に関して問題を引き起こす。他の解決策はベース-14チェックサムを付け加えることであるが、それもL P O S ワードの長さを増大させ、また、エラー検出を提供するだけでエラー訂正を提供しない。

【0007】

従って、L P O S ワードにエラー訂正能力を提供する改善された方法及び装置を提供することが望ましいであろう。

【課題を解決するための手段】

【0008】

本発明の好ましい実施態様によれば、データは始めに偶数L P O S ワードのセットと奇数L P O S ワードのセットとを介して符号化される。符号化されたデータは、後に、L P O S ワードの各々についてシンドローム・ビットのセットを生成することによって復号される。その後、L P O S ワードのうちの1つの中にエラーがあるか無いかが、それに対応するシンドローム・ビットに基づいて、判定される。

【0009】

本発明の全ての特徴及び利点は、以下の詳細な記述で明らかになるであろう。

【0010】

本発明自体と、好ましい使用方法、その更なる目的及び利点とは、実例となる実施態様についての以下の詳細な記述を添付図面と関連させて読み参照することにより最善に理解されるであろう。

【発明を実施するための最良の形態】

【0011】

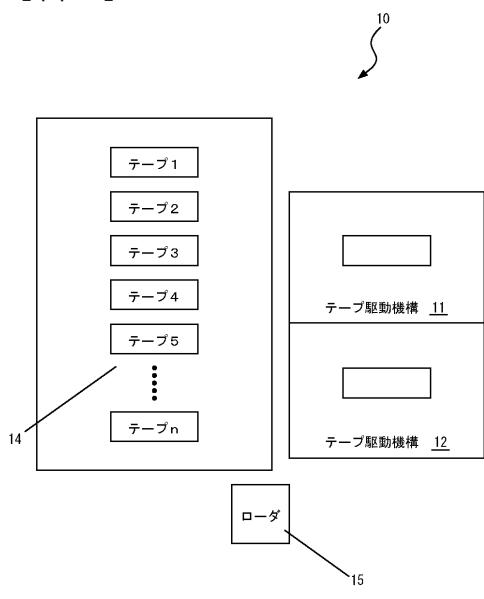

次に図面を、特に図1を参照すると、本発明の好ましい実施態様を組み込むことのできるテープ・ライブラリ・システムが描かれている。図示されているように、テープ・ライブラリ・システム10は、テープ起動機構11-12と、ローダ15と、テープ・カセット(又はカートリッジ)のライブラリ14とを含む。ローダ15は、テープ・カセット14のうちの任意の1つを取り出し、それをテープ駆動機構11-12のうちの1つに装填することができる。

【0012】

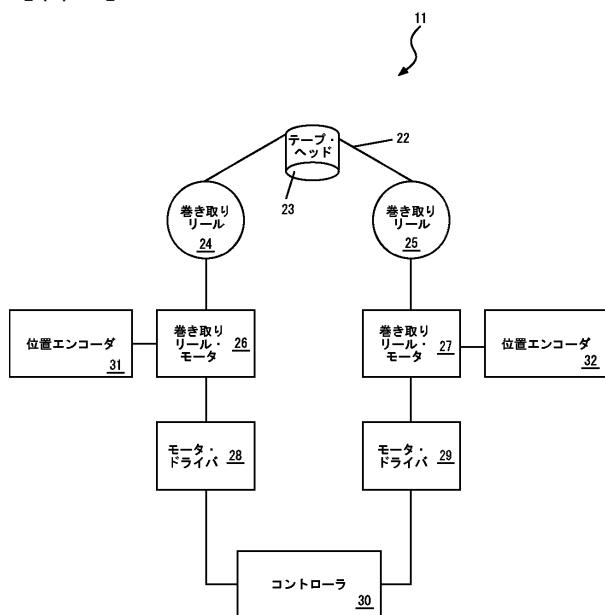

次に図2を参照すると、図1のテープ駆動機構11のようなテープ駆動機構が描かれており、それに本発明の好ましい実施態様を組み込むことができる。図示されているように、テープ駆動機構11は、テープ読み書きヘッド23と、巻き取りリール24-25と、巻き取りリール・モータ26-27とを含む。磁気テープ22は、巻き取りリール24-25に巻かれて、テープ読み書きヘッド23の上を通される。読み書きヘッド23は磁気

10

20

30

40

50

テープ 22 からデータを読み取り、またデータを書き込む。巻き取りリール・モータ 26 - 27 は、夫々巻き取りリール 24 - 25 を介してテープ読み書きヘッド 23 上の磁気テープ 22 の位置決めを制御する。

#### 【 0 0 1 3 】

更に、コントローラ 30 はモータ・ドライバ 28 - 29 に制御信号を供給する。モータ・ドライバ 28 - 29 は、夫々巻き取りリール・モータ 26 - 27 に駆動信号を供給する。位置エンコーダ 31 - 32 は、夫々、巻き取りリール・モータ 26 - 27 を整流する。縦方向位置 (LPOS) 情報は、コントローラ 30 に、磁気テープ 22 を磁気テープ 22 の全長にわたって移動させたり、磁気テープ 22 の末端から磁気テープ 22 の先頭まで巻き戻させたり、巻き取ったり、解きほぐさせたりする。

10

#### 【 0 0 1 4 】

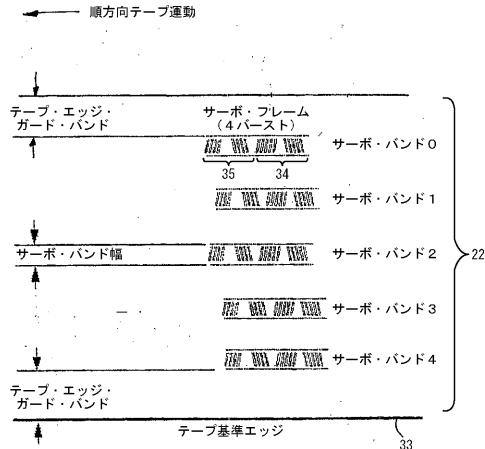

次に図 3 を参照すると、本発明の好ましい実施態様に従う、図 2 の磁気テープ 22 のような磁気テープにおける記録フォーマットが示されている。図示されているように、磁気テープ 22 は、データ・トラック上でのテープ読み書きヘッドの正確な位置決めを可能にすると共に、テープ読み書きヘッドが隣接するデータ・トラックへ逸れないことを保証するサーボ・バンド 0 - 4 を含む。サーボ・バンド 0 - 4 は磁気テープ 22 に製造時に書き込まれる。サーボ・バンド 0 - 4 の各々はテープ基準エッジ 33 から特定の距離を置いて位置する。サーボ・バンド 0 - 4 の各々の中にサーボ・ストライプがあり、そのグループはサーボ・バーストを構成する。4 つのサーボ・バーストが 1 つのサーボ・フレームを構成する。例えば、サーボ・バンド 0 では、サーボ・フレームはサーボ・バースト 34 - 35 を含む。始めの 2 つのサーボ・バースト 34 は 5 つのフラックス遷移を含み、第 2 の 2 つのサーボ・バースト 35 は 4 つのフラックス遷移を含む。

20

#### 【 0 0 1 5 】

従来技術では、LPOS ワードは、下記のように、1 つの同期マークと 7 つの 14 - ar y シンボルとを含む（順方向テープ運動方向に書かれている）。

Sy, L0, L1, L2, L3, L4, L5, Tx

ここで、Sy はワード同期マークであり、

L0 は縦方向位置における最下位シンボルであり、

L1 は縦方向位置における次の上位シンボルであり、

L2 は縦方向位置における次の上位シンボルであり、

L3 は縦方向位置における次の上位シンボルであり、

L4 は縦方向位置における次の上位シンボルであり、

L5 は縦方向位置における次の上位シンボルであり、

Tx はテープ製造者情報である。

30

LPOS ワード・シンボルは、表 I に記載されているビット・シーケンスのセットから構成される。各 LPOS ワード・シンボル内の最上位ビットは初めにサーボ・サブフレームに符号化される。LPOS ワードは、36 ビットを含み、36 サーボ・フレームの長さを有する。

#### 【 0 0 1 6 】

【表1】

表 I

| シンボル | ビット・シーケンス       |

|------|-----------------|

| S y  | 1 0 0 0 0 0 0 0 |

| D    | 0 0 0 1         |

| C    | 0 0 1 0         |

| B    | 0 0 1 1         |

| A    | 0 1 0 0         |

| 9    | 0 1 0 1         |

| 8    | 0 1 1 0         |

| 7    | 0 1 1 1         |

| 6    | 1 0 0 1         |

| 5    | 1 0 1 0         |

| 4    | 1 0 1 1         |

| 3    | 1 1 0 0         |

| 2    | 1 1 0 1         |

| 1    | 1 1 1 0         |

| 0    | 1 1 1 1         |

## 【0017】

本発明の好ましい実施態様によれば、LPOS情報は、初めに1つの偶数LPOSワードと1つの奇数LPOSワード(又はその逆)により表され、その次に偶数LPOSワード又は奇数LPOSワードの組み合わせから構成されるLPOSワードのグループが続く。偶数LPOSワード及び奇数LPOSワードの各々は、次のように、1つの同期マークと7つの14 - aryシンボルとを含む(順方向テープ運動方向に書かれている)。

偶数LPOSワード: S y , L 0 , L 1 , L 2 , L 3 , X , Y , T x

奇数LPOSワード: S y , L 0 , L 1 , L 4 , L 5 , X , Y , T x

ここで S y はワード同期マークであり、

L 0 は縦方向位置における最下位シンボルであり、

L 1 は縦方向位置における次の上位シンボルであり、

L 2 は縦方向位置における次の上位シンボルであり、

L 3 は縦方向位置における次の上位シンボルであり、

L 4 は縦方向位置における次の上位シンボルであり、

L 5 は縦方向位置における次の上位シンボルであり、

T x はテープ製造者情報のシンボルであり、

X , Y は8ビットの(d = 0, k = 3)ランレンジス・リミテッド(RLL)制限エラー訂正コード(constrained error correction code)であり、それらは次の8ビット:a , b , c , 1 , d , e , f , 1,として符号化され、ここでa , b , c , d , e , 及びfは、

- 偶数LPOSワード: L 0 , L 1 , L 2 , L 3 , 及びT x ここでL 0 は0 , 2 , . . . , 1 2

- 奇数LPOSワード: L 0 , L 1 , L 4 , L 5 , 及びT x ここでL 0 は1 , 3 , . . . , 1 3

の上の短縮拡張ハミング・コード(shortened extended Hamming code)

10

20

30

40

50

`ng code`) (4のハミング距離を生成し、これはどんな1ビット・エラーも訂正することができると共にどんな2ビット・エラーも検出することができる)に関連付けられた6個のパリティ・ビットである。

2個の1のRLLは、間違ったSyが見られないようにX, Yビット・シーケンスを制限する。

#### 【0018】

偶数LPOSワードにおける $14 - ary$ シンボル(すなわち、L0 L1 L2 L3 X Y Tx)のためのマッピングと、奇数LPOSワードにおける $14 - ary$ シンボル(すなわち、L0 L1 L4 L5 X Y Tx)のためのマッピングとは次のとおりである。 10

|            |                                                                 |

|------------|-----------------------------------------------------------------|

| L0ビット:     | u <sub>1</sub> u <sub>2</sub> u <sub>3</sub> u <sub>4</sub>     |

| L1ビット:     | u <sub>5</sub> u <sub>6</sub> u <sub>7</sub> u <sub>8</sub>     |

| L2又はL4ビット: | u <sub>9</sub> u <sub>10</sub> u <sub>11</sub> u <sub>12</sub>  |

| L3又はL5ビット: | u <sub>13</sub> u <sub>14</sub> u <sub>15</sub> u <sub>16</sub> |

| Xビット:      | a b c 1                                                         |

| Yビット:      | d e f 1                                                         |

| Txビット:     | u <sub>17</sub> u <sub>18</sub> u <sub>19</sub> u <sub>20</sub> |

LPOSワード・シンボルは表Iに示されているビット・シーケンスから構成され、L0-L5及びTxビットの各々について、u<sub>i</sub>...u<sub>j</sub>の各々は表Iのビット・シーケンス中のビットに対応する。例えば、もしL0=5ならば、L0についてのビット・シーケンスは、表Iによれば、1010であるべきであり、これはu<sub>1</sub>=1, u<sub>2</sub>=0, u<sub>3</sub>=1, u<sub>4</sub>=0を意味する。他の例として、もしL2=8ならば、L1についてのビット・シーケンスは、表Iによれば、0110であるべきであり、それはu<sub>9</sub>=0, u<sub>10</sub>=1, u<sub>11</sub>=1, u<sub>12</sub>=0を意味する。 20

#### 【0019】

パリティ・ビットa, b, c, d, e及びfをu<sub>1</sub>...u<sub>20</sub>の関数として計算するためにエンコーダが使用される。エンコーダの中では、下記の計算が行われる。

$$\begin{aligned}

a &= u_1 / u_5 / u_6 / u_9 / u_{11} / u_{14} / u_{15} / u_{16} / u_{18} / u_{20} \\

b &= u_1 / u_2 / u_7 / u_{10} / u_{11} / u_{12} / u_{15} / u_{16} / u_{17} / u_{19} \\

c &= u_2 / u_3 / u_6 / u_8 / u_{11} / u_{12} / u_{13} / u_{17} / u_{18} / u_{20} \\

d &= u_3 / u_4 / u_7 / u_9 / u_{12} / u_{13} / u_{14} / u_{16} / u_{18} / u_{19} \\

e &= u_4 / u_5 / u_8 / u_{10} / u_{13} / u_{14} / u_{15} / u_{17} / u_{19} / u_{20} \\

f &= u_1 / u_2 / u_3 / u_4 / u_5 / u_6 / u_7 / u_8 / u_9 / u_{10}

\end{aligned}$$

ここで/は排他的論理和演算(すなわち、モジュロ2の加法)を表す。好ましくは、そのエンコーダを実現するために合計54個の排他的論理和論理ゲートが必要であり、パリティ・ビットa-fの各々を計算するために合計9個の排他的論理和ゲートが使用される。 30

#### 【0020】

パリティ・ビットa-fを形成するためのu<sub>1</sub>...u<sub>20</sub>の値は $6 \times 2^6$ パリティ・チェック行列H=[h<sub>1</sub> h<sub>2</sub> h<sub>3</sub> ... h<sub>20</sub> h<sub>21</sub> h<sub>22</sub> h<sub>23</sub> h<sub>24</sub> h<sub>25</sub> h<sub>26</sub>]に基づき、ここでh<sub>i</sub>は下記により与えられる行列Hのi番目の列ベクトルである。 40

#### 【0021】

【数1】

$$H = \begin{bmatrix} 10001100101001110101100000 \\ 11000010011100111010010000 \\ 01100101001110001101001000 \\ 00110010100111010110000100 \\ 00011001010011101011000010 \\ 11111111110000000000000001 \end{bmatrix}$$

10

【0022】

6個のシンドローム・ビット  $s_1 \dots s_6$  を計算するためにデコーダが使用される。このデコーダは、計算されたシンドローム・ビットの値に基づいて L P O S ワード中にエラーがあるか無いかを判定する。デコーダ内で、次の計算が行われる。

$$\begin{aligned} s_1 &= a' / u'_1 / u'_5 / u'_6 / u'_9 / u'_{11} / u'_{14} / u'_{15} / \\ &u'_{16} / u'_{18} / u'_{20} \\ s_2 &= b' / u'_1 / u'_2 / u'_7 / u'_{10} / u'_{11} / u'_{12} / u'_{15} / \\ &u'_{16} / u'_{17} / u'_{19} \\ s_3 &= c' / u'_2 / u'_3 / u'_6 / u'_8 / u'_{11} / u'_{12} / u'_{13} / u'_{17} / u'_{18} / u'_{20} \\ s_4 &= d' / u'_3 / u'_4 / u'_7 / u'_9 / u'_{12} / u'_{13} / u'_{14} / u'_{16} / u'_{18} / u'_{19} \\ s_5 &= e' / u'_4 / u'_5 / u'_8 / u'_{10} / u'_{13} / u'_{14} / u'_{15} / u'_{17} / u'_{19} / u'_{20} \\ s_6 &= f' / u'_1 / u'_2 / u'_3 / u'_4 / u'_5 / u'_6 / u'_7 / u'_8 / u'_9 / u'_{10} \end{aligned} \quad 20$$

ここで / は排他的論理和演算を表す。好ましくは、シンドローム・ビットを計算するために合計 60 個の排他的論理和論理ゲートが必要であり、各シンドローム・ビットを計算するために合計 10 個の排他的論理和論理ゲートが使用される。プライム記号は受信されたビットを意味し（例えば、 $a'$  は受信されたビット  $a$  であり、 $b'$  は受信されたビット  $b$  であり、 $u'_1$  は受信されたビット  $u_1$  であり、 $u'_2$  は受信されたビット  $u_2$  であるなど）、それは間違っている可能性がある。デコーダは、次のように、3 つの別々のケースを考慮して、その 3 つのケースの各々に関して判定を行う。

ケース 1 :  $s_1 + s_2 + s_3 + s_4 + s_5 + s_6 = 0$  又は 1

ケース 1 では、受信された 4 ビット・データ・ニブルの全てが有効な 14 - a r y ニブルであれば、何も行われない（すなわち、ビット  $u'_1 \dots u'_{20}$  においてエラー訂正是行われない。）本例では、 $u_1 = u'_1 \dots u'_{20}$  がデコーダにより宣言され、ここで  $u_1 \dots u_{20}$  はデコーダのデータ推定値である。しかし、受信された 4 ビット・ニブルのうちの少なくとも 1 つが有効でなければ、エラー検出フラグが掲げられる。

ケース 2 :  $s_1 + s_2 + s_3 + s_4 + s_5 + s_6 = 2$  又は 4 又は 5 又は 6

ケース 2 では、エラー検出フラグが掲げられる。

ケース 3 :  $s_1 + s_2 + s_3 + s_4 + s_5 + s_6 = 3$

ケース 3 では、シンドローム・ビットの値に依存して、ビット  $u'_1 \dots u'_{20}$  の中の特定の単一のビットが“ひっくり返される”(f l i p p e d)”。特に、列形のシンドローム・ベクトルがパリティ・チェック行列 H の  $i$  番目の列ベクトルに等しければ ( $i = 1, 2, \dots, 20$ )、 $i$  番目のビット  $u'_{i}$  が“ひっくり返される”。換言すれば、もし  $[s_1 \ s_2 \ s_3 \ s_4 \ s_5 \ s_6]^t = h_i$ 、ここで  $i = 1, 2, \dots, 20$ 、であるならば、 $i$  番目のビット  $u'_{i}$  が“ひっくり返され”、ここで  $t$  は転置操作を

30

40

50

意味する。このとき、デコーダは、 $u_i = u'_{i-1}$  と結論し、また  $j$  が  $i$  に等しくなければ  $u_j = u'_{j-1}$  であると結論する。もしエラー訂正後のデータ推定値  $u_i$  (ここで  $i = 1, 2, \dots, 20$ ) を有するデータ・ニブルの全てが有効な 14 - ary ニブルであれば、復号は完了している。しかし、エラー訂正後のデータ・ニブルのうちの 1 つが有効な 14 - ary ニブルでなければ、エラー検出フラグが掲げられる。

#### 【0023】

各々の新しい LPOS ワード・シーケンスについて、L0, L1, L2, L3, L4, 及び L5 が必要とされるのでシーク位置を完全に獲得 (and) するためにテープ駆動機構は初めに 2 つの LPOS ワードを連続的に読み出さなければならない。しかし初めの 2 つの LPOS ワード (すなわち、L2 から L5 まで) が知られて更新され得るようになつた後、1 つの LPOS ワードだけが後の更新のために必要とされる。

10

#### 【0024】

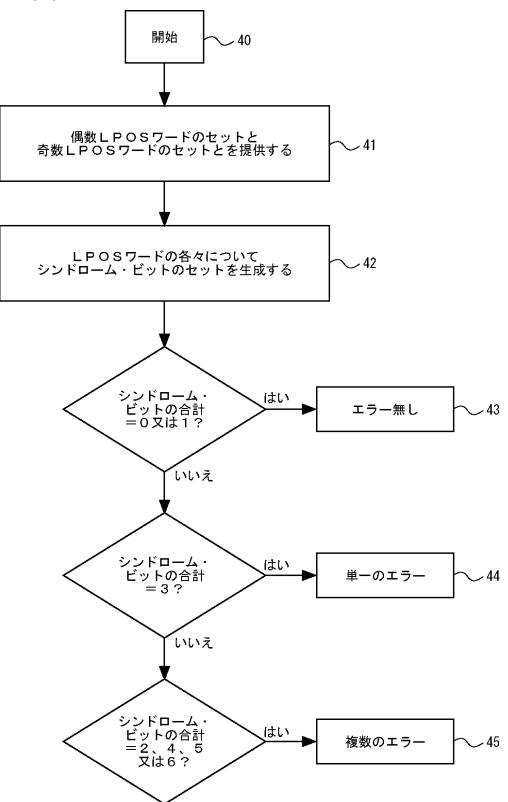

次に図 4 を参照すると、本発明の好ましい実施態様に従う、テープ記憶システム内で縦方向位置ワードにエラー訂正能力を提供する方法の高レベル論理流れ図が描かれている。ブロック 40 から出発して、ブロック 41 に示されているように、データは始めに偶数 LPOS ワードのセットと奇数 LPOS ワードのセットとを介して符号化される。ブロック 42 に描かれているように、符号化されたデータは、LPOS ワードの各々についてシンドローム・ビットのセットを生成することによって復号され得る。その後、LPOS ワード中にエラーがあるか無いかが、それに対応するシンドローム・ビットに基づいて、判定される。ブロック 43 に示されているように、もしシンドローム・ビットの合計が 0 又は 1 に等しければ、その LPOS ワードにエラーは無い。ブロック 44 に示されているように、もしシンドローム・ビットの合計が 3 に等しければ、その LPOS ワードのビットのうちの 1 つにエラーがある。ブロック 45 に示されているように、もしシンドローム・ビットの合計が 2, 4, 5 又は 6 に等しければ、その LPOS ワードのビットには 2 つ以上のエラーがある。

20

#### 【0025】

上記のように、本発明は、LPOS ワードにエラー訂正能力を提供する改善された方法及び装置を提供する。本発明の方法は、LPOS ワードの長さを増大させること無く单一ビット・エラーを訂正することを可能にすると共に二重ビット・エラーを検出することを可能にする。設計された特定の ( $n, k$ ) = (26, 20) 拡張短縮ハミング・コードは、全ての單一エラーを訂正することができると共に全ての二重エラーを検出することができる。更に、本発明の方法は、全てのあり得る三重エラー (いずれかの位置にある 3 つのエラー) の 20.77% と、全ての四重エラー (いずれかの位置にある 4 つのエラー) の 96.55% を検出することができる。

30

#### 【0026】

本発明はハードウェアに関して記述されたけれども、本発明のメカニズムがプログラム製品として種々の形で配布され得ることを当業者が認めるであろうこと、また、実際に配布を行うために利用される信号担持媒体の具体的なタイプに関わらずに本発明が等しく適用されることに注意することも重要である。信号担持媒体の例は、限定無しに、フレキシブル・ディスク又はコンパクト・ディスクのような記録可能型の媒体と、アナログ又はデジタル通信リンクのような伝送型の媒体とを含む。

40

#### 【0027】

本発明は好ましい実施態様に関して詳しく示され記述されたけれども、本発明の範囲から逸脱せずにその形及び細部に種々の変更を加え得ることが当業者により理解されるであろう。

#### 【図面の簡単な説明】

#### 【0028】

【図 1】本発明の好ましい実施態様を組み込むことのできるテープ・ライブラリ・システムのプロック図である。

【図 2】本発明の好ましい実施態様を組み込むことのできるテープ駆動機構のプロック図

50

である。

【図3】本発明の好ましい実施態様に従う磁気テープにおける記録フォーマットを示す。

【図4】本発明の好ましい実施態様に従う、テープ記憶システム内で縦方向位置ワードにエラー訂正能力を提供する方法の高レベル論理流れ図である。

【図1】

【図2】

【図3】

【図4】

---

フロントページの続き

(51)Int.Cl.

F I

G 1 1 B 20/18 5 2 0 E

(74)代理人 100086243

弁理士 坂口 博

(72)発明者 セガール、ポール

アメリカ合衆国 8 5 7 4 5 アリゾナ州 ツーソン ウエスト・パセオ・デル・バランコ 5 1 4

5

(72)発明者 エレフセリウ、エバンゲロス

スイス連邦 シーエイチ - 8 0 3 8 チューリッヒ ベラリアシュトラーセ 5 3

(72)発明者 ジャケット、グレン、アラン

アメリカ合衆国 8 5 7 5 0 アリゾナ州 ツーソン ノース・ロックキー・リッジ・プレイス 5 2

7 0

(72)発明者 シデシアン、ロイ、ダロン

スイス連邦 シーエイチ - 8 8 0 3 レースヒリコン ルーシュトラーセ 1 5

審査官 堀 洋介

(56)参考文献 特開2 0 0 5 - 1 6 6 1 4 0 (JP, A)

特表2 0 0 2 - 5 1 5 6 2 2 (JP, A)

特開2 0 0 4 - 0 8 7 0 0 0 (JP, A)

特開2 0 0 1 - 0 6 7 8 4 7 (JP, A)

"Data Interchange on 12,7mm 384-Track Magnetic Tape Cartridge Ultrium-1 Format", Standard ECMA - 319, 2001年 6月, p. 53 - 54

(58)調査した分野(Int.Cl., DB名)

G11B 20/18