(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5496541号

(P5496541)

(45) 発行日 平成26年5月21日(2014.5.21)

(24) 登録日 平成26年3月14日(2014.3.14)

|               |              |

|---------------|--------------|

| (51) Int.Cl.  | F 1          |

| HO 1 L 21/822 | (2006.01)    |

| HO 1 L 27/04  | (2006.01)    |

| HO 1 L 23/52  | (2006.01)    |

|               | HO 1 L 27/04 |

|               | HO 1 L 23/52 |

|               | HO 1 L 27/04 |

請求項の数 7 (全 15 頁)

(21) 出願番号 特願2009-102278 (P2009-102278)

(22) 出願日 平成21年4月20日 (2009.4.20)

(65) 公開番号 特開2010-251663 (P2010-251663A)

(43) 公開日 平成22年11月4日 (2010.11.4)

審査請求日 平成24年4月12日 (2012.4.12)

(73) 特許権者 302062931

ルネサスエレクトロニクス株式会社

神奈川県川崎市中原区下沼部1753番地

(74) 代理人 100110928

弁理士 速水 進治

(74) 代理人 100118544

弁理士 野本 可奈

(74) 代理人 100127236

弁理士 天城 聰

(72) 発明者 中柴 康隆

神奈川県川崎市中原区下沼部1753番地

NECエレクトロニクス株式会社内

審査官 須原 宏光

最終頁に続く

(54) 【発明の名称】半導体装置

## (57) 【特許請求の範囲】

## 【請求項 1】

配線層を有する一つまたは二つの半導体チップ、及び前記一つまたは二つの半導体チップの配線層側に取り付けられた配線基板を備え、

前記一つまたは二つの半導体チップは、

信号を生成する第1回路と、

前記配線層に形成され、前記第1回路に接続された第1インダクタと、

前記信号を処理する第2回路と、

前記配線層に形成され、前記第2回路に接続された第2インダクタと、

を有し、

前記配線基板は、

前記第1インダクタの上方に位置する第3インダクタと、

前記第2インダクタの上方に位置し、前記第3インダクタに接続している第4インダクタと、

を有し、

前記第1インダクタから前記第3インダクタまでの距離は、前記第2インダクタから前記第4インダクタまでの距離と異なり、

前記第1回路及び前記第1インダクタは第1の前記半導体チップに形成されており、

前記第2回路及び前記第2インダクタは第2の前記半導体チップに形成されており、

前記配線基板は、前記第1の半導体チップ上から前記第2の半導体チップ上に亘って取

り付けられている半導体装置。

【請求項 2】

配線層を有する一つまたは二つの半導体チップ、及び前記一つまたは二つの半導体チップの配線層側に取り付けられた配線基板を備え、

前記一つまたは二つの半導体チップは、

信号を生成する第1回路と、

前記配線層に形成され、前記第1回路に接続された第1インダクタと、

前記信号を処理する第2回路と、

前記配線層に形成され、前記第2回路に接続された第2インダクタと、

を有し、

前記配線基板は、

前記第1インダクタの上方に位置する第3インダクタと、

前記第2インダクタの上方に位置し、前記第3インダクタに接続している第4インダクタと、

を有し、

前記第1インダクタから前記第3インダクタまでの距離は、前記第2インダクタから前記第4インダクタまでの距離と異なり、

前記第1回路、前記第2回路、前記第1インダクタ、及び前記第2インダクタは一つの前記半導体チップに形成されており、

前記第1回路及び前記第1インダクタは前記半導体チップの第1領域に形成されており

、

前記第2回路及び前記第2インダクタは前記半導体チップの第2領域に形成されており

、

前記第1領域及び前記第2領域は絶縁されている半導体装置。

【請求項 3】

請求項1又は2に記載の半導体装置において、

前記第1インダクタから前記第3インダクタまでの距離は、前記第2インダクタから前記第4インダクタまでの距離より長い半導体装置。

【請求項 4】

請求項1～3のいずれか一つに記載の半導体装置において、

前記配線基板はシリコン基板を用いて形成されている半導体装置。

【請求項 5】

請求項4に記載の半導体装置において、

前記一つまたは二つの半導体チップはシリコン基板を用いて形成されており、

前記配線基板における基板不純物濃度は、前記一つまたは二つの半導体チップの基板不純物濃度より低い半導体装置。

【請求項 6】

請求項4又は5に記載の半導体装置において、

前記配線基板に形成され、回路上において前記第3インダクタと前記第4インダクタの間に設けられた送受信回路を備える半導体装置。

【請求項 7】

請求項1～6のいずれか一つに記載の半導体装置において、

前記第3インダクタ及び前記第4インダクタは、前記配線基板のうち前記一つまたは二つの半導体チップとは反対側の面に形成されている半導体装置。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、入力される電気信号の電位が互いに異なる2つの回路の間で電気信号を伝達することができる半導体装置に関する。

【背景技術】

10

20

30

40

50

## 【0002】

入力される電気信号の電位が互いに異なる2つの回路の間で電気信号を伝達する場合、フォトカプラを用いることが多い。フォトカプラは、発光ダイオードなどの発光素子とフォトトランジスタなどの受光素子を有しており、入力された電気信号を発光素子で光に変換し、この光を受光素子で電気信号に戻すことにより、電気信号を伝達している。

## 【0003】

しかし、フォトカプラは発光素子と受光素子を有しているため、小型化が難しい。また、電気信号の周波数が高い場合には電気信号に追従できなくなる。これらの問題を解決する技術として、例えば特許文献1に記載されているように、2つのインダクタを誘導結合させることにより、電気信号を伝達する技術が開発されている。

10

## 【0004】

また特許文献2には、送信側の第1半導体チップと受信側の第2半導体チップとを伝送経路を介して相互に接続する際に、インダクタ対を用いることが記載されている。詳細には、伝送線路と第1半導体チップは、送信側インダクタ対の電磁結合によって非接触に接続している。また伝送線路と第2半導体チップは、受信側インダクタ対の電磁結合によって非接触に接続している。

## 【先行技術文献】

## 【特許文献】

## 【0005】

【特許文献1】特表2001-513276号公報

20

【特許文献2】特開2008-113093号公報

## 【発明の概要】

## 【発明が解決しようとする課題】

## 【0006】

送信側の回路と受信側の回路とを配線基板を介して接続する場合において、送信側の回路と配線基板とをインダクタ対で接続し、配線基板と受信側の回路とをインダクタ対によって接続することが考えられる。この場合、インダクタ対が2つになるため、信号が伝達する間に減衰し、信号が正確に伝達できない可能性がでてくる。信号を正確に伝達するためには、インダクタ対を構成する2つのインダクタの相互間隔を狭くすれば良い。しかし、送信側の回路と受信側の回路の基準電圧が異なる場合、2つのインダクタ対それぞれにおいて、インダクタ対を構成する2つのインダクタの相互間隔を狭くすると、送信側の回路と受信側の回路の間の絶縁を確保できなくなる。このように、信号を正確に伝達しつつ、送信側の回路と受信側の回路の間の絶縁を確保することは難しかった。

30

## 【課題を解決するための手段】

## 【0007】

本発明によれば、配線層を有する一つまたは二つの半導体チップ、及び前記一つまたは二つの半導体チップの配線層側に取り付けられた配線基板を備え、

前記一つまたは二つの半導体チップは、

信号を生成する第1回路と、

前記配線層に形成され、前記第1回路に接続された第1インダクタと、

40

前記信号を処理する第2回路と、

前記配線層に形成され、前記第2回路に接続された第2インダクタと、

を有し、

前記配線基板は、

前記第1インダクタの上方に位置する第3インダクタと、

前記第2インダクタの上方に位置し、前記第3インダクタに接続している第4インダクタと、

を有し、

前記第1インダクタから前記第3インダクタまでの距離は、前記第2インダクタから前記第4インダクタまでの距離と異なる半導体装置が提供される。

50

**【0008】**

本発明によれば、第1インダクタから第3インダクタまでの距離は、第2インダクタから第4インダクタまでの距離と異なっている。第1回路と第2回路の間の耐圧は、第1インダクタから第3インダクタまでの距離と、第2インダクタから第4インダクタまでの距離の和によって定まる。このため、第1インダクタから第3インダクタまでの距離と、第2インダクタから第4インダクタまでの距離の和は、ある値以上を有する必要がある。半導体装置を設計する場合、上記した必要な値を、第1インダクタから第3インダクタまでの距離と、第2インダクタから第4インダクタまでの距離に配分することになる。第1インダクタから第3インダクタまでの距離、及び第2インダクタと第4インダクタの距離をそれぞれ互いに異ならせ、適切な値にすれば、第1回路から第2回路までの信号伝達効率を最大値にすることができる。従って、信号を正確に伝達しつつ、第1回路と第2回路の間の絶縁を確保することができる。10

**【発明の効果】****【0009】**

本発明によれば、配線基板と送信側の第1回路、及び配線基板と受信側の第2回路とをインダクタ対によって接続するときに、信号を正確に伝達しつつ、第1回路と第2回路の間の絶縁を確保することができる。

**【図面の簡単な説明】****【0010】**

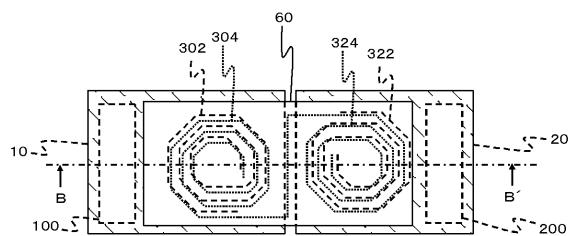

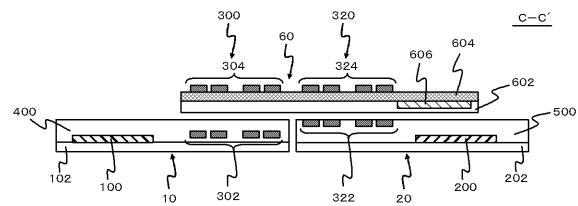

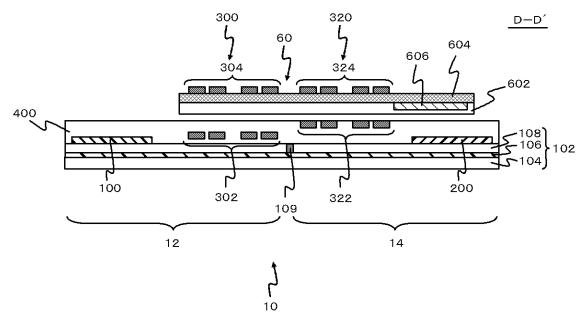

【図1】第1の実施形態に係る半導体装置の構成を示す断面図である。20

【図2】図1に示した半導体装置の平面概略図である。

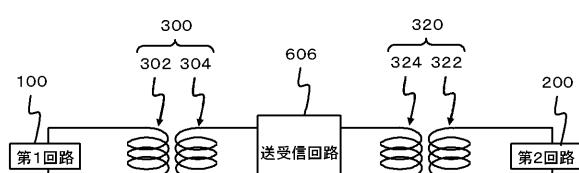

【図3】図1に示した半導体装置の等価回路図である。

【図4】第2の実施形態に係る半導体装置の構成を示す断面図である。

【図5】図4に示した半導体装置の平面概略図である。

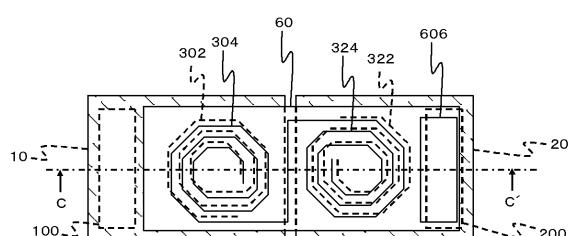

【図6】第3の実施形態に係る半導体装置の構成を示す断面概略図である。

【図7】図6に示した半導体装置の平面概略図である。

【図8】図6に示した半導体装置の等価回路図である。

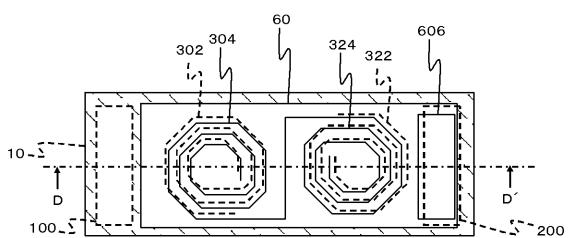

【図9】第4の実施形態に係る半導体装置の構成を示す断面概略図である。

【図10】図9に示した半導体装置の平面概略図である。

**【発明を実施するための最良の形態】****【0011】**

以下、本発明の実施の形態について、図面を用いて説明する。尚、すべての図面において、同様な構成要素には同様の符号を付し、適宜説明を省略する。

**【0012】**

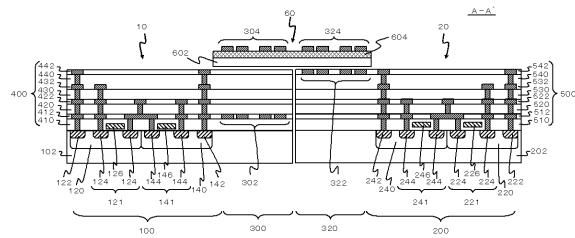

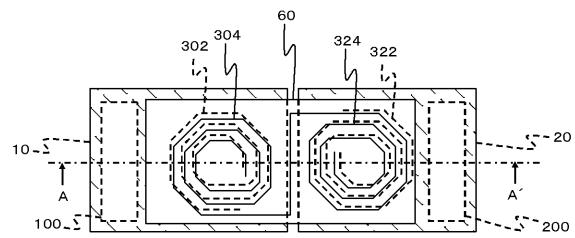

図1は、第1の実施形態に係る半導体装置の構成を示す図であり、図2は図1に示した半導体装置の平面概略図である。図1は図2のA-A'断面に相当している。なお図1において、図を簡略化するため、後述する第1インダクタ302及び第2インダクタ322の巻き数を図2と異ならせている。この半導体装置は、二つの半導体チップ10, 20及び配線基板60を備える。半導体チップ10は多層配線層400を有しており、半導体チップ20は多層配線層500を有している。40

**【0013】**

半導体チップ10は、第1基板102、第1回路100、及び第1インダクタ302を有している。第1基板102はシリコン基板などの半導体基板である。第1回路100は送信される信号を生成する。第1インダクタ302は多層配線層400に形成されている。第1インダクタ302は、第1回路100に接続しており、第1回路100で生成した信号が入力される。

**【0014】**

半導体チップ20は、第2基板202、第2回路200及び第2インダクタ322を有している。第2基板202はシリコン基板などの半導体基板である。第2回路200は、第1回路100が生成した信号を受信して処理する。第2インダクタ322は多層配線層

10

20

30

40

50

500に形成されている。第2インダクタ322は、第2回路200に接続しており、第2回路200に信号を伝達する。伝達される信号は、例えばデジタル信号であるが、アナログ信号であっても良い。

【0015】

配線基板60は、半導体チップ10の第1インダクタ302上から半導体チップ20の第2インダクタ322上に亘って取り付けられている。配線基板60は、例えば接着剤(図示せず)を介して、半導体チップ10及び半導体チップ20に取り付けられている。配線基板60は、第3インダクタ304及び第4インダクタ324を有している。第3インダクタ304は第1インダクタ302の上方に位置している。第4インダクタ324は、第2インダクタ322の上方に位置しており、第3インダクタ304に接続している。第1インダクタ302から第3インダクタ304までの距離は、第2インダクタ322から第4インダクタ324までの距離より長い。各インダクタは、渦巻き型の配線パターンである。

【0016】

図1に示す例において、配線基板60は、シリコン基板602を用いて形成されたシリコンインターポーラである。ただし、配線基板60は、樹脂製の基板を用いたインターポーラや配線基板であってもよい。また配線基板60がシリコン基板602を用いて形成されており、第1基板102及び第2基板202がシリコン基板である場合、配線基板60のシリコン基板の不純物濃度は、第1基板102の基板不純物濃度及び第2基板202の基板不純物濃度より低いのが好ましい。このようにすると、シリコン基板602に渦電流が発生することを抑制できる。

【0017】

本実施形態では、第3インダクタ304及び第4インダクタ324は、配線基板60のうち半導体チップ10及び半導体チップ20とは反対側の面に形成されている。なお第3インダクタ304及び第4インダクタ324は、シリコン基板602上に形成された配線層604に形成されている。配線層604は多層配線層であり、第3インダクタ304及び第4インダクタ324は、配線層604内の配線(図示せず)を介して互いに接続している。

【0018】

第1インダクタ302及び第3インダクタ304は、第1信号伝達素子300を構成しており、第2インダクタ322及び第4インダクタ324は第2信号伝達素子320を構成している。上記したように、第1インダクタ302から第3インダクタ304までの距離は、第2インダクタ322から第4インダクタ324までの距離と異なっている。

【0019】

詳細には、第1インダクタ302は半導体チップ10の多層配線層400に形成されており、第2インダクタ322は半導体チップ20の多層配線層500に形成されている。多層配線層400, 500は、絶縁層及び配線層をこの順にそれぞれ複数回以上交互に積層したものである。本実施形態において、多層配線層400は、絶縁層410、配線層412、絶縁層420、配線層422、絶縁層430、配線層432、絶縁層440、及び配線層442をこの順に重ねた構成を有している。また多層配線層500は、絶縁層510、配線層512、絶縁層520、配線層522、絶縁層530、配線層532、絶縁層540、及び配線層542をこの順に重ねた構成を有している。各絶縁層は、複数の絶縁膜を積層した構造であってもよいし、一つの絶縁膜であってもよい。なお、多層配線層400, 500は、保護膜(図示せず)により被覆されている。また多層配線層400, 500の層数は互いに同じであっても良いし、異なっていても良い。

【0020】

本図に示す例において、第1インダクタ302は、多層配線層400の第1配線層である配線層412に設けられており、第2インダクタ322は、多層配線層500の最上層の配線層542に設けられている。

【0021】

10

20

30

40

50

各配線層の配線は、ダマシン法により形成されたCu配線であり、それぞれ配線層に形成された溝に埋め込まれている。最上層の配線には、パッド（図示せず）が形成されている。なお、多層配線層400, 500において、配線層の少なくとも一つはAl合金配線であっても良い。なお各配線層に形成された配線は、絶縁層に埋め込まれたプラグを介して互いに接続している。

#### 【0022】

絶縁層及び配線層を構成する各絶縁膜はSiO<sub>2</sub>膜であっても良いし、低誘電率膜であってもよい。低誘電率膜は、例えば比誘電率が3.3以下、好ましくは2.9以下の絶縁膜とすることができる。低誘電率膜としては、SiOCの他に、HSQ（ハイドロジエンシルセスキオキサン）、MSQ（メチルシルセスキオキサン）、またはMHSQ（メチル化ハイドロジエンシルセスキオキサン）等のポリハイドロジエンシロキサン、ポリアリールエーテル（PAE）、ジビニルシロキサン ビス ベンゾシクロブテン（BCB）、またはSilk（登録商標）等の芳香族含有有機材料、SOG、FOX（flowable oxide）（登録商標）、サイトップ（登録商標）、またはBCB（Benzocyclobutene）等を用いることもできる。また、低誘電率膜としては、これらの多孔質膜を用いることもできる。

#### 【0023】

なお、多層配線層400と多層配線層500の厚さが異なる場合、配線基板60が傾くことが考えられる。この場合、第1基板102と第2基板202の裏面研削量を変えて半導体チップ10及び半導体チップ20の厚さを同じにすればよい。

#### 【0024】

第1回路100は送信回路であり、第2回路200は受信回路である。このため、第1インダクタ302は送信側インダクタとして機能し、第3インダクタ304は受信側インダクタとして機能する。また第4インダクタ324は送信側インダクタとして機能し、第2インダクタ322は受信側インダクタとして機能する。

#### 【0025】

第1回路100は、例えば送信側ドライバ回路（例えばゲートドライバ）であり、デジタル信号を変調した送信用の信号を増幅して第1インダクタ302に出力する。第2回路200は、例えば受信側ドライバ回路（例えばゲートドライバ）であり、第2インダクタ322が受信した信号を変調することにより生成したデジタル信号を増幅して出力する。

#### 【0026】

第1回路100及び第2回路200は、入力される電気信号の電位が互いに異なるが、第1信号伝達素子300及び第2信号伝達素子320は誘導結合を用いて電気信号を伝達するため、第1回路100及び第2回路200に問題は生じない。なお図1の構成において、「入力される電気信号の電位が互いに異なる」場合として、電気信号の振幅（0を示す電位と1を示す電位の差）が互いに異なる場合、電気信号の基準電位（0を示す電位）が異なる場合、及び電気信号の振幅が互いに異なり、かつ電気信号の基準電位が異なる場合などがある。

#### 【0027】

半導体チップ10の第1回路100は第1トランジスタを有している。第1トランジスタには、N型のトランジスタとP型のトランジスタがある。N型の第1トランジスタ121はP型のウェル120に形成されており、ソース及びドレインとなる2つのN型の不純物領域124及びゲート電極126を有している。P型の第1トランジスタ141はN型のウェル140に形成されており、ソース及びドレインとなる2つのP型の不純物領域144及びゲート電極146を有している。ゲート電極126, 146それぞれの下にはゲート絶縁膜が位置している。これら2つのゲート絶縁膜は、厚さが略等しい。そして第1トランジスタ121, 141は、上記した送信側ドライバ回路、例えばインバータを構成している。

#### 【0028】

ウェル120にはP型の不純物領域122が形成されており、ウェル140にはN型の

10

20

30

40

50

不純物領域 142 が形成されている。不純物領域 122 には N 型の第 1 トランジスタ 121 の基準電位 (グラウンド電位) を与える配線が接続されており、不純物領域 142 には P 型の第 1 トランジスタ 141 の電源電位を与える配線が接続されている。

【0029】

半導体チップ 20 の第 2 回路 200 は第 2 トランジスタを有している。第 2 トランジスタにも、N 型のトランジスタと、P 型のトランジスタがある。N 型の第 2 トランジスタ 221 は P 型のウェル 220 に形成されており、ソース及びドレインとなる 2 つの N 型の不純物領域 224 及びゲート電極 226 を有している。P 型の第 2 トランジスタ 241 は N 型のウェル 240 に形成されており、ソース及びドレインとなる 2 つの P 型の不純物領域 244 及びゲート電極 246 を有している。ゲート電極 226, 246 それぞれの下にはゲート絶縁膜が位置している。そして第 2 トランジスタ 221, 241 は、上記した受信側ドライバ回路、例えばインバータを構成している。

10

【0030】

ウェル 220 には P 型の不純物領域 222 が形成されており、ウェル 240 には N 型の不純物領域 242 が形成されている。不純物領域 222 には N 型の第 2 トランジスタ 221 の基準電位を与える配線が接続されており、不純物領域 242 には P 型の第 2 トランジスタ 241 の電源電位を与える配線が接続されている。

【0031】

本図に示す例において、第 1 トランジスタ 121, 141 と第 2 トランジスタ 221, 241 は、ゲート絶縁膜の厚さが互いに異なっているが、同じであっても良い。

20

【0032】

なお、配線基板 60 の面積は、半導体チップ 10 の面積と半導体チップ 20 の面積の和より小さい。

【0033】

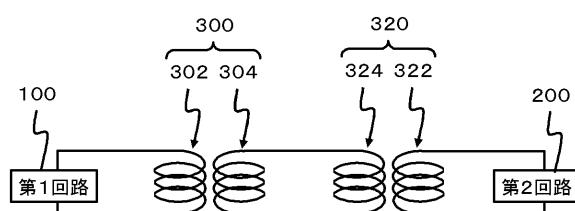

図 3 は、図 1 に示した半導体装置の等価回路図である。第 1 回路 100 で生成した信号は、第 1 信号伝達素子 300 及び第 2 信号伝達素子 320 を介して、第 2 回路 200 に受信される。第 1 信号伝達素子 300 は、第 1 インダクタ 302 と第 3 インダクタ 304 の誘導結合によって信号を伝達し、第 2 信号伝達素子 320 は、第 4 インダクタ 324 と第 2 インダクタ 322 の誘導結合によって信号を伝達する。

30

【0034】

次に、本実施形態の作用及び効果について説明する。第 1 回路 100 と第 2 回路 200 は、入力される電気信号の電位が互いに異なる。第 1 回路 100 と第 2 回路 200 の間の耐圧は、第 1 インダクタ 302 と第 3 インダクタ 304 の間隔と、第 2 インダクタ 322 と第 4 インダクタ 324 の間隔の和によって定まる。このため、第 1 インダクタ 302 と第 3 インダクタ 304 の間隔と、第 2 インダクタ 322 と第 4 インダクタ 324 の間隔の和は、ある値以上になる必要がある。そして、半導体装置を設計する場合、上記した必要な値を、第 1 インダクタ 302 と第 3 インダクタ 304 の間隔と、第 2 インダクタ 322 と第 4 インダクタ 324 の間隔に配分することになる。第 1 インダクタ 302 と第 3 インダクタ 304 の間隔、及び第 2 インダクタ 322 と第 4 インダクタ 324 までの間隔をそれぞれ互いに異ならせ、適切な値にすれば、第 1 回路 100 から第 2 回路 200 までの信号伝達効率を最大値にすることができる。本実施形態では、第 1 インダクタ 302 から第 3 インダクタ 304 までの距離は、第 2 インダクタ 322 から第 4 インダクタ 324 までの距離と異なっている。従って、信号を正確に伝達しつつ、第 1 回路 100 と第 2 回路 200 の間の絶縁を確保することができる。

40

【0035】

例えば、第 1 信号伝達素子 300 の送信側インダクタである第 1 インダクタ 302 は、送信回路である第 1 回路 100 に接続しているため、比較的大きな電流が流れる。これに対して第 2 信号伝達素子 320 の送信側インダクタである第 4 インダクタ 324 は、第 1 信号伝達素子 300 の受信側インダクタである第 3 インダクタ 304 に流れた誘導電流が流れるため、比較的小さな電流が流れる。このため、第 1 信号伝達素子 300 の受信側イ

50

ンダクタである第3インダクタ304には、相対的に大きな誘導電流が生じ、第2信号伝達素子320の受信側インダクタである第2インダクタ322には、相対的に小さな誘導電流が生じる。そこで本実施形態のように、第1インダクタ302を多層配線層400の最下層の配線層412に配置して、第2インダクタ322を多層配線層500の最上層の配線層に配置すると、第1信号伝達素子300内で耐圧を確保しつつ、第2信号伝達素子320の信号伝達効率を高くすることができる。

【0036】

また本実施形態では、第3インダクタ304は、配線基板60のうち半導体チップ10とは反対側の面に形成されている。このため、第1インダクタ302と第3インダクタ304を離して、第1信号伝達素子300の耐圧を大きくすることができる。

10

【0037】

また、配線基板60のシリコン基板602の基板不純物濃度を、第1基板102の基板不純物濃度及び第2基板202の基板不純物濃度より低くすると、第1信号伝達素子300及び第2信号伝達素子320が生じる磁場によって、シリコン基板602に渦電流が生じることが抑制される。

【0038】

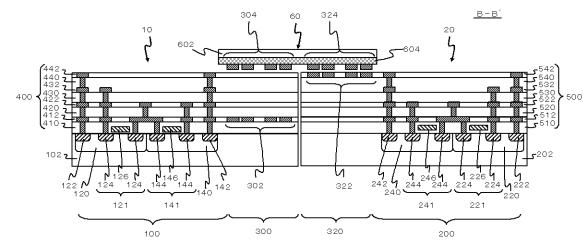

図4は、第2の実施形態に係る半導体装置の構成を示す断面図であり、図5は図4に示した半導体装置の平面概略図である。図4は図5のB-B'断面に相当している。この半導体装置は、第3インダクタ304及び第4インダクタ324が、配線基板60のうち半導体チップ10及び半導体チップ20に対向する面に形成されている点を除いて、第1の実施形態に係る半導体装置と同様の構成である。

20

【0039】

本実施形態によっても、信号を正確に伝達しつつ、第1回路100と第2回路200の間の絶縁を確保することができる。また、第4インダクタ324は、配線基板60のうち半導体チップ20に対向する面に形成されている。このため、第4インダクタ324と第2インダクタ322を近づけて、第2信号伝達素子320の信号伝達効率を大きくすることができる。

【0040】

図6は、第3の実施形態に係る半導体装置の構成を示す断面概略図であり、図7は、図6に示した半導体装置の平面概略図である。図6は図7のC-C'断面に相当している。この半導体装置は、シリコン基板602のうち配線層604が形成されている面に送受信回路606が形成されている点を除いて、第1の実施形態と同様の構成である。

30

【0041】

図8は、図6及び図7に示した半導体装置の等価回路図である。送受信回路606は、回路上において第3インダクタ304と第4インダクタ324の間に設けられている。送受信回路606は、受信回路及び送信回路を有しており、第3インダクタ304が第1インダクタ302から受信した信号を復調した後、再度変調して第4インダクタ324に出力する。図6に示すように送受信回路606は、配線基板60のうち配線層604が形成された面に形成されているが、配線層604が形成された面とは逆の面に形成されても良い。

40

【0042】

本実施形態によっても、第1又は第2の実施形態と同様の効果を得ることができる。また、送受信回路606は、第3インダクタ304が第1インダクタ302から受信した信号を復調した後、再度変調して第4インダクタ324に出力する。このため、信号伝達効率がさらに向上する。

【0043】

図9は、第4の実施形態に係る半導体装置の構成を示す断面概略図であり、図10は図9に示した半導体装置の平面概略図である。図9は図10のD-D'断面に相当している。この半導体装置は、第1回路100及び第1インダクタ302は半導体チップ10の第1領域12に形成されており、第2回路200及び第2インダクタ322は半導体チップ

50

10の第2領域14に形成されている点を除いて、第1～第3の実施形態のいずれかと同様の構成である。なお図9及び図10は、第3の実施形態と同様の場合を示している。

【0044】

第1基板102はSOI(Silicon On Insulator)基板であり、シリコン基板104上に絶縁層106及びシリコン層108をこの順に積層した構成である。シリコン層108には、第1領域12及び第2領域14を絶縁する絶縁分離層109が埋め込まれている。絶縁分離層109の下端は、絶縁層106に達している。

【0045】

本実施形態によっても、第1～第3の実施形態と同様の効果を得ることができる。また半導体チップ10に、送信回路としての第1回路100及び受信回路としての第2回路200を形成することができる。

【0046】

以上、図面を参照して本発明の実施形態について述べたが、これらは本発明の例示であり、上記以外の様々な構成を採用することもできる。なお、上記した実施形態によれば、以下の発明が開示されている。

(付記1)

配線層を有する一つまたは二つの半導体チップ、及び前記一つまたは二つの半導体チップの配線層側に取り付けられた配線基板を備え、

前記一つまたは二つの半導体チップは、

信号を生成する第1回路と、

前記配線層に形成され、前記第1回路に接続された第1インダクタと、

前記信号を処理する第2回路と、

前記配線層に形成され、前記第2回路に接続された第2インダクタと、

を有し、

前記配線基板は、

前記第1インダクタの上方に位置する第3インダクタと、

前記第2インダクタの上方に位置し、前記第3インダクタに接続している第4インダクタと、

を有し、

前記第1インダクタから前記第3インダクタまでの距離は、前記第2インダクタから前記第4インダクタまでの距離と異なる半導体装置。

(付記2)

付記1に記載の半導体装置において、

前記第1インダクタから前記第3インダクタまでの距離は、前記第2インダクタから前記第4インダクタまでの距離より長い半導体装置。

(付記3)

付記1又は2に記載の半導体装置において、

前記配線基板はシリコン基板を用いて形成されている半導体装置。

(付記4)

付記3に記載の半導体装置において、

前記一つまたは二つの半導体チップはシリコン基板を用いて形成されており、

前記配線基板における基板不純物濃度は、前記一つまたは二つの半導体チップの基板不純物濃度より低い半導体装置。

(付記5)

付記3又は4に記載の半導体装置において、

前記配線基板に形成され、回路上において前記第3インダクタと前記第4インダクタの間に設けられた送受信回路を備える半導体装置。

(付記6)

付記1～5のいずれか一つに記載の半導体装置において、

前記第3インダクタ及び前記第4インダクタは、前記配線基板のうち前記一つまたは二

10

20

30

40

50

つの半導体チップとは反対側の面に形成されている半導体装置。

(付記 7 )

付記 1 ~ 6 のいずれか一つに記載の半導体装置において、

前記第1回路及び前記第1インダクタは第1の前記半導体チップに形成されており、

前記第2回路及び前記第2インダクタは第2の前記半導体チップに形成されており、

前記配線基板は、前記第1の半導体チップ上から前記第2の半導体チップ上に亘って取り付けられている半導体装置。

(付記 8 )

付記 1 ~ 6 のいずれか一つに記載の半導体装置において、

前記第1回路、前記第2回路、前記第1インダクタ、及び前記第2インダクタは一つの前記半導体チップに形成されており、 10

前記第1回路及び前記第1インダクタは前記半導体チップの第1領域に形成されており、

前記第2回路及び前記第2インダクタは前記半導体チップの第2領域に形成されており、

前記第1領域及び前記第2領域は絶縁されている半導体装置。

【符号の説明】

【0 0 4 7】

1 0 半導体チップ

1 2 第1領域

20

1 4 第2領域

2 0 半導体チップ

6 0 配線基板

1 0 0 第1回路

1 0 2 第1基板

1 0 4 シリコン基板

1 0 6 絶縁層

1 0 8 シリコン層

1 0 9 絶縁分離層

1 2 0 ウェル

30

1 2 1 第1トランジスタ

1 2 2 不純物領域

1 2 4 不純物領域

1 2 6 ゲート電極

1 4 0 ウェル

1 4 1 第1トランジスタ

1 4 2 不純物領域

1 4 4 不純物領域

1 4 6 ゲート電極

2 0 0 第2回路

40

2 0 2 第2基板

2 2 0 ウェル

2 2 1 第2トランジスタ

2 2 2 不純物領域

2 2 4 不純物領域

2 2 6 ゲート電極

2 4 0 ウェル

2 4 1 第2トランジスタ

2 4 2 不純物領域

2 4 4 不純物領域

50

|       |          |    |

|-------|----------|----|

| 2 4 6 | ゲート電極    |    |

| 3 0 0 | 第1信号伝達素子 |    |

| 3 0 2 | 第1インダクタ  |    |

| 3 0 4 | 第3インダクタ  |    |

| 3 2 0 | 第2信号伝達素子 |    |

| 3 2 2 | 第2インダクタ  |    |

| 3 2 4 | 第4インダクタ  |    |

| 4 0 0 | 多層配線層    |    |

| 4 1 0 | 絶縁層      | 10 |

| 4 1 2 | 配線層      |    |

| 4 2 0 | 絶縁層      |    |

| 4 2 2 | 配線層      |    |

| 4 3 0 | 絶縁層      |    |

| 4 3 2 | 配線層      |    |

| 4 4 0 | 絶縁層      |    |

| 4 4 2 | 配線層      |    |

| 5 0 0 | 多層配線層    |    |

| 5 1 0 | 絶縁層      |    |

| 5 1 2 | 配線層      |    |

| 5 2 0 | 絶縁層      | 20 |

| 5 2 2 | 配線層      |    |

| 5 3 0 | 絶縁層      |    |

| 5 3 2 | 配線層      |    |

| 5 4 0 | 絶縁層      |    |

| 5 4 2 | 配線層      |    |

| 6 0 2 | シリコン基板   |    |

| 6 0 4 | 配線層      |    |

| 6 0 6 | 送受信回路    |    |

【 図 1 】

【 図 2 】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

〔 四 9 〕

【図10】

---

フロントページの続き

(56)参考文献 特開2010-103611(JP,A)

特開2007-235034(JP,A)

特表2008-502215(JP,A)

特開2006-246372(JP,A)

(58)調査した分野(Int.Cl., DB名)

H01L 27/04

H01L 25/07

H04B 5/00