등록특허 10-2315467

(19) 대한민국특허청(KR)

(12) 등록특허공보(B1)

(45) 공고일자 2021년10월22일

(11) 등록번호 10-2315467

(24) 등록일자 2021년10월15일

- (51) 국제특허분류(Int. Cl.)

*H01L 23/538* (2006.01) *H01L 23/00* (2006.01)

*H01L 23/15* (2006.01) *H01L 23/48* (2006.01)

*H01L 25/065* (2006.01)

- (52) CPC특허분류

*H01L 23/538* (2013.01)

*H01L 23/15* (2013.01)

- (21) 출원번호 10-2016-0042066

- (22) 출원일자 2016년04월06일

심사청구일자 2021년04월06일

- (65) 공개번호 10-2016-0126863

- (43) 공개일자 2016년11월02일

- (30) 우선권주장

14/694,132 2015년04월23일 미국(US)

- (56) 선행기술조사문현

US20150102852 A1

US20120106117 A1

- (73) 특허권자

팔로 알토 리서치 센터 인코포레이티드

미국 캘리포니아주 94304 팔로 알토 코요테 힐 로드 3333

- (72) 발명자

윔브 스콧 제이. 에이치.

미국 94306 캘리포니아 팔로 알토 넘버 1 그랜트 에비뉴 455

- 화이팅 그雷고리 엘.

미국 94025 캘리포니아 멘로 파크 미들 에비뉴 617

- (74) 대리인

장훈

전체 청구항 수 : 총 11 항

심사관 : 이석주

(54) 발명의 명칭 이온-교환 유리 처리된 인터포우저를 갖는 일시적인 전자장치

**(57) 요 약**

일시적인 전자장치는 그 취약성을 증가시키기 위해 이온-교환 처리를 사용하여 처리되는 유리-기반 인터포우저를 활용하며, 그 표면상에 동작 가능하게 장착된 트리거 장치를 포함한다. 집적회로(IC) 다이는 그 다음으로 상기 인터포우저에 접착되며, 상기 인터포우저는 패키지 구조에 장착되며, 상기 인터포우저는, 정상적인 동작상태를 하 (뒷면에 계속)

**대 표 도** - 도1

에서, 상기 IC 다이를 상기 패키지 I/O 핀들/볼들에 동작 가능하게 연결시키도록 기여한다. 일시적인 이벤트(예컨대, 비공인된 템퍼링이 검출될 때) 동안, 트리거 신호가 상기 트리거 장치에 전송되어, 상기 트리거 장치가 상기 유리-기반 인터포우저 기판에 인가되는 초기 균열력을 발생시키도록 야기한다. 상기 인터포우저는 상기 초기 균열력이 상기 인터포우저를 전적으로 분말화하고, 상기 IC 다이로 전달하기 위한 충분한 에너지로 상기 유리-기반 인터포우저 기판을 통해 전달됨으로써, 상기 IC 다이도 또한 분말화하도록(즉, 가시적으로 사라지도록) 구성된다.

(52) CPC특허분류

*H01L 23/481* (2013.01)

*H01L 24/97* (2013.01)

*H01L 25/0655* (2013.01)

---

## 명세서

### 청구범위

#### 청구항 1

반도체 기판 위에 형성된 전자회로를 갖는 상기 반도체 기판, 및 상기 반도체 기판의 표면상에 제1 패턴으로 배치된 IC 접촉 패드들을 포함하는 집적회로(IC) 다이로서, 상기 IC 접촉 패드들은 상기 전자회로에 동작 가능하게 결합되는, 상기 집적회로(IC) 다이;

패키지 기판, 상기 패키지 기판의 제1 표면상에 제2 패턴으로 배치된 복수의 제1 패키지 접촉구조들, 상기 패키지 기판의 제2 표면상에 배치된 복수의 제2 패키지 접촉구조들, 및 각각의 패키지 도체가, 관련된 제1 패키지 접촉구조 및 관련된 제2 패키지 접촉구조 사이의 전기적인 통로를 형성하도록, 상기 제1 표면 및 상기 제2 표면 사이의 패키지 구조를 통해 뻗어 있는 복수의 패키지 도체들을 포함하는 상기 패키지 구조;

유리 기판의 제1 표면상에 상기 제1 패턴으로 배치된 복수의 제1 접촉점들, 상기 유리 기판의 제2 표면상에 배치된 복수의 제2 접촉점들, 및 복수의 인터포우저 도체들(interposer conductors)을 포함하는 상기 유리 기판을 포함하는 인터포우저로서, 각각의 상기 인터포우저 도체는 관련된 제1 접촉점 및 관련된 제2 접촉점 사이의 전기적 통로를 형성하도록 구성되는, 상기 인터포우저; 및

상기 인터포우저에 부착되며 트리거 신호에 반응하여 상기 유리 기판상에 초기 파괴력(fracture force)을 발생시켜 가하도록 구성된 트리거 장치;

를 포함하며,

상기 인터포우저는 상기 제2 표면상에 배치된 상기 제2 접촉점들의 각각이 해당 제1 패키지 접촉구조들에 전기적으로 연결되도록 상기 패키지 기판에 고정되며,

상기 유리 기판은 2차 균열들이 상기 초기 파괴력에 반응하여 상기 유리 기판에서 발생되고 상기 유리 기판에 걸쳐 전달됨으로써, 상기 유리 기판이 분말화되도록 이온들의 양을 포함하며,

상기 IC 다이는 상기 유리 기판에 고정적으로 부착되어 상기 2차 균열들이 상기 IC 다이를 분말화하기 위한 충분한 에너지로 상기 IC 다이로 전달되는, 일시적인 전자장치.

#### 청구항 2

제 1 항에 있어서,

상기 유리 기판은  $100 \mu\text{m}$  및  $300 \mu\text{m}$ 의 범위의 두께를 포함하는 일시적인 전자장치.

#### 청구항 3

제 2 항에 있어서,

상기 유리 기판은 규산염 유리를 포함하는, 일시적인 전자장치.

#### 청구항 4

제 2 항에 있어서,

상기 유리 기판은 상기 제 1 표면 및 상기 제 2 표면 사이에 뻗어 있는 복수의 쓰루-그래스 바이어들(through-glass vias)을 규정하는, 일시적인 전자장치.

#### 청구항 5

제 4 항에 있어서,

각각의 상기 인터포우저 도체는 관련된 상기 쓰루-그래스 바이어를 통해 뻗어 있는 금속 바이어(metal via) 구조를 포함하는, 일시적인 전자 장치.

**청구항 6**

제 5 항에 있어서,

상기 금속 바이어 구조는 유리 기판의 CTE와 일치하는 열팽창 계수(CTE)를 갖는 전도성 물질을 포함하는, 일시적인 전자 장치.

**청구항 7**

제 4 항에 있어서,

상기 인터포우저 도체들 중 적어도 일부는, 상기 제 1 표면 및 상기 제 2 표면 중 하나에 배치되고, 관련된 금속 바이어 구조로부터, 관련된 상기 제 1 접촉점 및 관련된 상기 제 2 접촉점 중 하나로 뻗어 있는, 금속 트레이스 구조를 더 포함하는, 일시적인 전자 장치.

**청구항 8**

제 1 항에 있어서,

상기 트리거 장치는 외부에서 공급되는 트리거 신호에 반응하여 상기 초기 파괴력의 방출을 제어하도록 구성된 작동 구조를 포함하는, 일시적인 전자 장치.

**청구항 9**

제 8 항에 있어서,

상기 작동 구조는 상기 유리 기판에 저항 가열(resistive heating)을 가하도록 구성된 장치, 및 상기 유리 기판에 기계적인 압력을 가하도록 구성된 장치 중 하나를 포함하는, 일시적인 전자 장치.

**청구항 10**

제 1 항에 있어서,

상기 IC 다이는 상기 유리 기판에 양극 접합되는, 일시적인 전자 장치.

**청구항 11**

제 1 항에 있어서,

상기 IC 다이는 실리콘-온-절연체(SOI) 접적화로 장치를 포함하는, 일시적인 전자 장치.

**발명의 설명****기술 분야**

[0001]

본 발명은 일시적인 전자장치들에 관한 것으로, 특히 일시적인 조립체들에 활용된 인터포우저들에 관한 것이다.

**배경 기술**

[0002]

대면적 감지는 다양한 군사적, 생태학적, 상업적 관심분야들에 대해 중요하며 역사적으로 중앙 집중식 장거리 센서들의 사용을 통해 기여해 왔다. 그러나, 전자 시스템들의 소형화에서의 급속한 개선들은 소형 센서 장치들의 능력을 상당히 개선시켰다. 이러한 마이크로-센서들은 동작 적응성(operational adaptability)에서의 장점을 갖는 "대규모 N"을 생성하기 위한 잠재력을 가지며, 아주 근접해 있을 때만 가능한 비전통적인 감지양식들은 네트워크화된 지능을 통한 감도 및 지식 추출을 증가시켰다.

[0003]

유통된 네트워크 시스템들은 현저한 장래성을 가지는 한편, 그들의 실제적인 사용은 그 환경에서의 그들의 접적(accumulation), 겹출 및 실패, 및 적극적인 제어를 유지하기 위한 어려움에 기인하는 악용과 관련된 위험들에 의해 제한된다(중앙 집중식 장거리 센서들과 다르게).

[0004]

일시적인 전자장치들(transient electronics)은 시간의 일정 주기 내에 사라지며(분해 및 해체), 그것들을 이상적으로 유통된 네트워크 시스템들용으로 적합하게 만드는 비교적 새로운 군(群)의 전자장치들을 의미한다. 종래의 일시적인 전자 시스템들은 전형적으로 용해성 기판들 및 전자물질들(은(銀)과 같은)에 의존한다. 용제(溶

劑)(solvent)(전형적으로 물)내에 위치될 때, 이러한 종래의 기판들 및 전자장치들은 천천히 용액에 용해된다. 이와 같이, 종래의 일시적인 전자장치들로 구성된 유통된 네트워크 시스템은 비교적 짧은 시간 동안(예컨대, 주기적인 강우 후) "사라질" 것으로 예상될 수 있다.

[0005] 종래의 일시적인 전자장치들은 전자장치들이 사용 후에 "사라지도록" 야기하는 목적을 달성하지만, 완전한 분해 및 해체를 달성하는데 필요한 긴 용해 주기는 종래의 전자장치들이 명령에 따라 빠르면서도 완전한 용해를 필요로 하는 별개의(예컨대, 군사적인) 응용분야들에 대해 부적합하게 만든다. 게다가, 상기 종래의 전자장치들은 현존하는 접적회로 제조 및 조립 기술들과 호환성이 없는 물질들을 활용하여, 상당한 비용으로의 새로운 접적회로 제조공정들의 개발을 필요로 한다.

[0006] 인터포우저들(Interposers)은 반도체 장치 패키징의 본문에서의 잘 알려진 전기적인 인터페이스들이며, 전형적으로 IC 다이(칩) 및, 볼-그리드 배열(BGA) 패키지 또는 핀-그리드 배열(PGA) 패키지와 같은, 표준화된 반도체 패키지 구조 사이에 배치된다. 인터포우저들은 전형적으로 다수의 금속 도체들이 반대의 기판 표면들 상에 2개의 다른 패턴들로 배치되어 있는 해당 접촉구조들(점들) 사이에 뻗어 있는 평평한 절연체 기판(예컨대, FR4와 같은 딱딱한 절연체, 또는 폴리이미드와 같은 유연한 절연체)을 포함한다. 즉, 인터포우저 기판의 한쪽에 배치된 제1 세트의 접촉점들은 IC-인터포우저 연결(예컨대, 표면 장착기술에 의해)을 용이하게 하기 위해 상기 IC 다이 상의 해당 접촉 패드들과 일치하는 패턴으로 형성되며, 상기 인터포우저의 반대편의 제2 세트의 접촉점들은 호스트 패키지로의 상기 인터포우저의 표면 장착을 용이하게 하기 위해 상기 호스트 패키지의 표면의 내부에 배치된 해당 접촉구조들과 일치하는 제2(다른) 패턴으로 배열된다. 상기 금속 도체들은 상기 제1 세트 및 제2 세트의 해당 접촉구조들 사이의 신호 통로들을 제공하기 위해 상기 인터포우저 기판을 관통한다. 이러한 배열에서, 상기 호스트 패키지 구조가, 예컨대, 전기 시스템의 인쇄회로기판(PCB)에 후속적으로 연결될 때, 상기 인터포우저는 상기 호스트 패키지의 I/O 핀들/볼들에 의해 상기 IC 다이(들) 및 상기 전기 시스템 사이의 신호들의 통과를 용이하게 한다.

[0007] 인터포우저들은 원래 전형적으로 표준 패키지 구조들 상의 해당 접촉점들로의 IC 다이 연결들을 재루팅(reroute)하는데 활용되었지만, 가장 최근에는 다른 목적으로 역시 기여하고 있다. 예를 들어, 반도체 제조에서의 발달이 더욱 세밀하게 피치된 IC 다이 접촉 패드들을 갖는 더욱 소형의 IC 다이를 용이하게 하기 때문에, 인터포우저들은 역시 더욱 세밀하게 이격된 IC 다이 접촉점들을 종래의 패키지 구조들과 더욱 호환성이 있는 더욱 넓은 피치들로 확산시키는데 활용된다. 이 경우, 상기 인터포우저는 표면상에 세밀하게 피치된 (제1) 패턴으로 배열된 제1 접촉점들, 및 반대 표면상에 넓게 피치된 (제2) 패턴으로 배열된 제2 접촉점들을 포함하며, 전도성 금속 바이어들(vias) 및 트레이스들(traces)은 관련된 제1 및 제2 접촉점들 사이의 전기적인 신호 통로들을 제공하기 위해 상기 기판을 통해 그리고 상기 반대의 표면들을 따라 뻗어 있다. 세밀하게 이격된 IC 다이 접촉점들을 더욱 넓은 피치들로 확산시키는 것 이외에도, 인터포우저들은 2개 이상의 다이(die)들을 단일 패키지 구조에 고정시키는데 사용되고 있다.

## 발명의 내용

### 해결하려는 과제

[0008] 필요한 것은 현존하는 IC 제조기술과 호환성이 있으며, IC 다이 상에 구현된 온전한 접적회로에의 액세스를 방지함에 의해 고정 및 반-탬퍼링(anti-tampering) 보호를 제공하기 위해 그 위에 배치된 IC 다이의 충분하게 완전한, 온-커맨드(on-command) 분해를 성취하는 일시적인 전자 패키지 조립체이다.

### 과제의 해결 수단

[0009] 본 발명은 적어도 하나의 접적회로(IC) 다이가 유리-기반 인터포우저의 개입에 의해 패키지 구조에 장착되는 일시적인 전자장치에 관한 것으로, 상기 인터포우저는 일시적인 이벤트 트리거링 신호에 반응하여 균열(분말화)되도록 충분한 양의 이온들을 포함하고, 그렇게 함에 있어서 또한 그 위에 접착된 상기 IC 다이(들)을 균열(분말화)시키기 위해 처리되는 유리 기판을 포함한다. 종래의 배열들과 유사하게, 참신한 인터포우저는 제1 기판 표면상에 배치된 그리고 상기 IC 다이의 해당 접촉 패드들과 일치하는 (제1) 패턴으로 배열된 제1 세트의 접촉점들(즉, 금속 패드들 또는 다른 접촉구조들), 반대편의 기판 표면상에 배치된 그리고 패키지 구조의 해당 접촉구조들과 일치하는 (제2) 패턴으로 배열된 제2 세트의 접촉점들, 및 관련된 제1 및 제2 접촉점들 사이의 전기적인 신호 통로들을 형성하는 기판상에 그리고/또는 기판을 통해 뻗어 있는 도체들을 포함한다. 본 발명의 특징에 따르면, 상기 IC 다이는 상기 인터포우저에 고정적으로 부착되며, 상기 인터포우저는 트리거 신호에 반응하여 트

리거 장치에 의해 발생된 초기 파괴력이 상기 인터포우저를 통해 전달되며 상기 IC 다이를 분말화시키도록 이온-교환 처리에 의해 연약한 유리 기판을 포함한다. 특히, 2차 균열들이 상기 유리 기판에 걸쳐 전달되도록 상기 유리가 상기 초기 파괴력에 반응하여 2차 균열들을 발생시키기 위해 충분히 저장된 에너지를 갖도록 상기 이온-교환 처리된 유리 기판은 알려진 이온-교환 공정들을 사용하여 처리됨으로써, 상기 유리 기판은 프린스 루퍼트의 드롭(Prince Rupert's Drop)에 포착된 것과 유사한 구조를 사용하는 미크론-크기의 입자들(즉,  $\leq 100 \mu\text{m}$ 의 폭)로 완전히 분해된다. 적합한 종래의 접착기술(예컨대, 양극 접합 또는 밀봉 유리에 의해)을 활용하여 상기 IC 다이를 상기 유리 기판에 고정적으로 부착함으로써, 상기 2차 균열들은 또한 상기 IC 다이를 분말화시키는데 충분한 에너지로 상기 IC 다이로 전달된다(즉, 실질적으로 상기 인터포우저 기판의 분말화와 동시에). 그러므로, 본 발명은 상기 IC 다이(들) 상에 형성된 기능회로가 종래의(예컨대, 용해성 기판) 해결책들을 사용하여 가능한 것보다 상당히 짧은 양의 시간에 효율적으로 사라지는(분말화하는) 일시적인 전자장치들 및 시스템들의 제조를 용이하게 한다. 게다가, 공인되지 않은 탬퍼링(unauthorized tampering)[예컨대, 패키지 구조 또는 일시적인 장치가 장착되는 인쇄회로기판으로의 탬퍼링]의 검출시에 분말화를 초기화하기 위해 트리거 장치를 구성함으로써, 본 발명은 그것이 온전한 동안 상기 IC 다이 상에 구현된 접착회로에의 비공인된 액세스를 방지함으로써 보안(security) 및 반-탬퍼링 보호(anti-tampering protection) 둘다 모두를 제공한다. 게다가, 상기 인터포우저는 현존하는 저비용 IC 제조기술들과 호환성이 있기 때문에, 본 발명은 IC 제조공정을 코어(core)하기 위한 최소의 수정을 갖는(또는 잠재적으로 임의의 수정을 갖지 않는) 전자장치들을 포함하는 일시적인 전자시스템들의 제조를 용이하게 한다.

[0010] 본 발명의 실시예에 따르면, 상기 인터포우저의 유리 기판은 다수의 쓰루-그래스 바이어(through-glass via, TGV) 구멍들(openings)을 포함하기 위해 예칭되는(예컨대, 레이저, 기계적 또는 화학적 예칭 기술들을 사용하여) 이온-교환 전용 유리(예컨대, 적절한 알칼리 구성요소들을 갖는 모든 규산염 유리들)의 얇은 유리 웨이퍼/시트(예컨대,  $100 \mu\text{m}$  및  $300 \mu\text{m}$ 의 범위의 두께를 갖는)를 포함한다. 그 다음으로, 상기 TGV 구멍들(openings)에는 전도성 물질(예컨대, 구리와 같은 금속)이 채워지며, 상기 전도성 물질은 바람직하게는 상기 이온-교환 전용 유리의 CTE와 일치하는(즉, 의  $+/-10\%$ ) 열팽창계수(熱膨脹係數)(Coefficient of Thermal Expansion, CTE)를 가지며, 이것에 의해 상기 전도성 물질은 반대의 기판 표면들 상에 노출된 반대의 단부들을 갖는 금속 바이어 구조들(metal via structures)을 형성한다. 접촉점들(예컨대, 금속 패드들) 및 선택적인 금속 트레이스(trace) 구조들은 그 다음으로 각각 반대의 기판 표면들 중 하나 또는 양쪽에 패터닝되고, 상기 접촉점들은 위에 설명된 원하는 패턴들로 배열되며, 상기 선택적인 금속 트레이스들(trace)은 해당 쌍들의 상부/하부(제1/제2) 접촉점들 및 관련된 금속 바이어 구조들의 반대의 단부들 사이의 전기적인 연결들을 제공하기 위해 패터닝됨으로써, 상기 해당 쌍들의 상부/하부(제1/제2) 접촉점들 사이의 인터포우저 도체(전도성 통로)를 형성한다.

[0011] 바람직한 실시예에 따르면, 상기 인터포우저 접촉구조들 및 금속 트레이스 구조들이 상기 유리 기판상에 형성될 때 일시적인 이벤트 트리거 장치가 제조되거나 그렇지 않으면 각각의 인터포우저 상에 배치된다. 상기 트리거 장치는 상기 트리거 장치에 공급되는 트리거 신호(예컨대, 외부로 전달된 전류 펄스)에 반응하여 상기 초기 파괴력의 방출(즉, 발생시키고 인가하는)을 제어하는 작동구조를 포함한다. 선택적인 실시예들에서, 상기 작동구조는 상기 유리 기판에 저항 가열(resistive heating)을 가하도록 구성된 장치, 및 상기 유리 기판에 기계적인 압력을 가하기 위해 구성된 장치중 하나를 포함한다.

[0012] 상기 트리거 장치를 이러한 방식으로 구성함으로써, 트리거 신호의 수신시에, 상기 작동구조는 상기 유리 기판에의 충분히 강력한 초기 파괴력을 발생 및 인가시킬 수 있어 상기 인터포우저가 그 위에 장착된 상기 IC 다이(들)의 완전한 파괴(분말화)를 보장하기 위한 충분한 힘으로 갑자기 그리고 돌발적으로 분말화시킨다.

[0013] 본 발명의 다른 특징에 따르면, 상기 IC 다이는 상기 인터포우저를 갖는 상기 IC 다이의 동시에의 분말화를 보장하는 제조 및 접착 기술들을 사용하여 제조되어 상기 유리 기판에 고정적으로 부착된다. 바람직한 실시예에서, 상기 IC 다이는 표준 실리콘-온-절연체(SOI) 제조 기술들(즉, 상기 기능회로가 SOI 접착회로 구조로서 구현되도록)을 사용하여 제조되는 IC 장치를 포함한다. 일 실시예에서, 상기 IC 다이는 양극 접합을 사용하여 상기 유리 기판에 부착되며, 이것은 접착된 칩의 파괴를 보장하기 위해 상기 유리 기판으로부터의 균열 전달을 가능하게 하기 위한 양호한 인터페이스 접착을 제공한다. 선택적인 실시예에서, 밀봉 유리를 사용하는 것과 같은, 다른 하나의 접착방법이 활용될 수도 있다. 상기 기능회로를 SOI 접착회로들로서 형성하고 상기 IC 다이를 상기 유리 기판에 양극 접합함으로써, 일시적인 이벤트들 동안의 작은 입자들로의 상기 IC 다이의 신뢰성 있는 분말화가 달성된다. 다른 하나의 실시예에서, 상기 IC 다이는 상기 IC 다이의 두께를 감소시키기 위해 상기 접착 공정 전 또는 상기 접착 공정 후에 "박막화되며"(예컨대, 화학적이면서도 기계적인 연마(polishing)에 예속된), 이것은 추가로 일시적인 이벤트 동안의 상기 IC 다이의 분말화(powderization)를 보장한다.

[0014]

본 발명의 다른 하나의 실시예에 따르면, 일시적인 전자장치들의 제조방법은 위에 설명된 인터포우저 구조를 적어도 부분적으로 형성하고 유리 기판의 연약성(frangibility)이 증가하도록 상기 유리 기판을 이온-교환 처리하는 단계를 포함한다. 선택적이면서도 편상적인 이온-교환 공정은 바이어(via) 측벽들을 따른 연약성을 증가시키기 위해 바이어(via) 에칭 후에 수행된다. 상기 트리거 장치(위에 설명된), 상기 인터포우저 접촉구조들 및 금속 트레이스 구조들은 상기 이온-교환 처리 전 또는 상기 이온-교환 처리 후에 상기 유리 기판상에 형성/배치된다. 1개 이상의 IC 다이들은 그 다음으로 상기 처리된 유리 기판의 상부(제1) 면에 고정적으로 부착되어(예컨대, 양극 접합에 의해) IC 접촉점들이 해당(제1) 인터포우저 접촉구조들에 전기적으로 연결된 다음, 패키지 구조상에 제2 패턴으로 배치된 상기 접촉구조들이 상기 유리 기판의 하부(제2) 면상에 배치된 해당(제2) 인터포우저 접촉구조들에 전기적으로 연결되도록 상기 인터포우저는 상기 패키지 구조상에 장착된다. 상기한 바와 같이, 상기 인터포우저의 유리 기판은 상기 처리된 유리 기판이 상기 트리거 장치에 의해 공급된 초기 파괴력에 반응하여 2차 균열들을 발생시킬도록 충분히 연약해질 때까지 그 이온 함유량이 증가되도록 이온-교환 처리되며, 상기 IC 다이는 상기 처리된 유리 기판에 접착되어 상기 2차 균열들이 상기 IC 다이를 분말화시키기 위한 충분한 에너지로 상기 IC 다이로 전달된다. 트리거링 후의 최종 입자 크기는 유리 기판 두께, 이온-교환 처리, 상기 다이 접착 공정 및 상기 초기 파괴력과 같은 요인들에 근거한다. 일 실시예에서, 상기 IC 다이는 상기 최종 균열된 입자 크기를 제어하는 것을 도와주는 균열점들(특징들)을 제공하기 위해 패터닝된다(즉, 상기 유리 기판이 분말화될 때, 상기 IC 칩이 상기 패터닝된 균열 특징들을 따라 균열하도록 상기 균열 특징들이 형성된다).

[0015]

선택적인 특정 실시예들에 따르면, 일시적인 전자장치 제조방법은 시트 레벨 인터포우저 패터닝 단계 또는 다이 레벨 인터포우저 패터닝 단계를 포함한다. 각 경우에서, 다수의 인터포우저 코어들은 단일 유리 시트 상에 일체형으로 배치된다(즉, 각각의 인터포우저 코어의 상기 유리 기판은 상기 유리 시트의 해당 부분에 의해 형성된다). 상기 시트 레벨 패터닝 단계에서, 인터포우저 접촉구조들 및 트리거 장치들은 각각의 인터포우저 코어 상에 형성된 다음, 상기 유리 시트는 개별적인 인터포우저들을 분리하기 위해 다이싱(dice)된 다음, 이것들은 이온-교환 처리된 다음(예컨대, 개별적으로 또는 뮁음으로), IC 다이들은 상기 인터포우저들 중 각각에 접착된다. 상기 다이 레벨 패터닝 단계에 따르면, 상기 유리 시트는 상기 개별적인 인터포우저들을 분리시키기 위해 다이싱(dice)되며, 인터포우저 접촉구조들 및 트리거 장치들이 각각의 인터포우저 코어 상에 형성되기 전에 이온-교환 처리가 수행된 다음, IC 다이들은 상기 인터포우저들 중 각각에 접착된다. 이러한 2개의 단계들 사이의 주요 차이점들은 비용 및 기능이다. 다이싱 전의 상기 인터포우저 층의 패터닝은 처리량을 개선시키며 비용을 감소시킬 것이지만 패터닝된 금속층들을 갖는 유리를 이온-교환 처리하는 것은 또한 연약성을 감소시킬 수도 있는 비균일 표면 스트레스 프로필(surface stress profile)을 생성시킬 것이다. 한편, 패터닝 전의 개별적인 이온-교환 다이는 보다 신뢰성 있는 연약한 기판을 제공할 것이지만 개별적인 조각들의 패터닝의 부가된 비용은 적합하지 않을 수도 있다.

### 발명의 효과

[0016]

이러한 예시적인 실시예들에 대한 다른 변형들이 이 기술분야에 통상의 지식을 가진 자들에게는 자명하다.

### 도면의 간단한 설명

[0017]

본 발명의 이러한 그리고 다른 특징들 및 장점들은 다음의 설명, 첨부된 청구항들, 및 첨부도면들과 관련하여 보다 잘 이해될 것이다. 여기서:

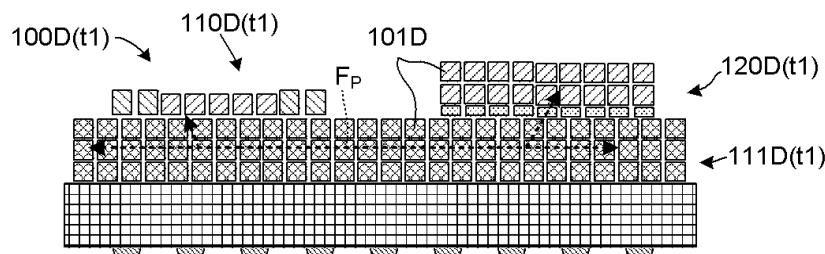

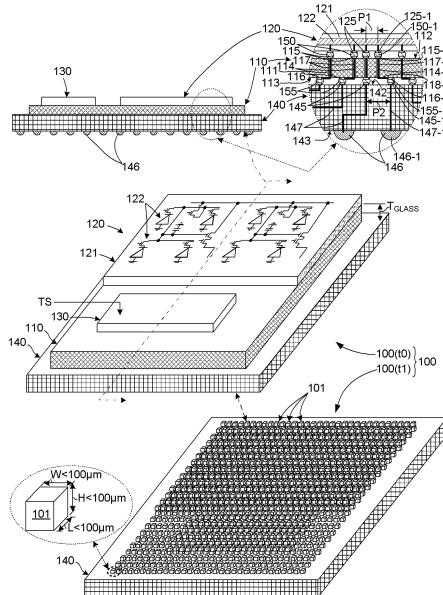

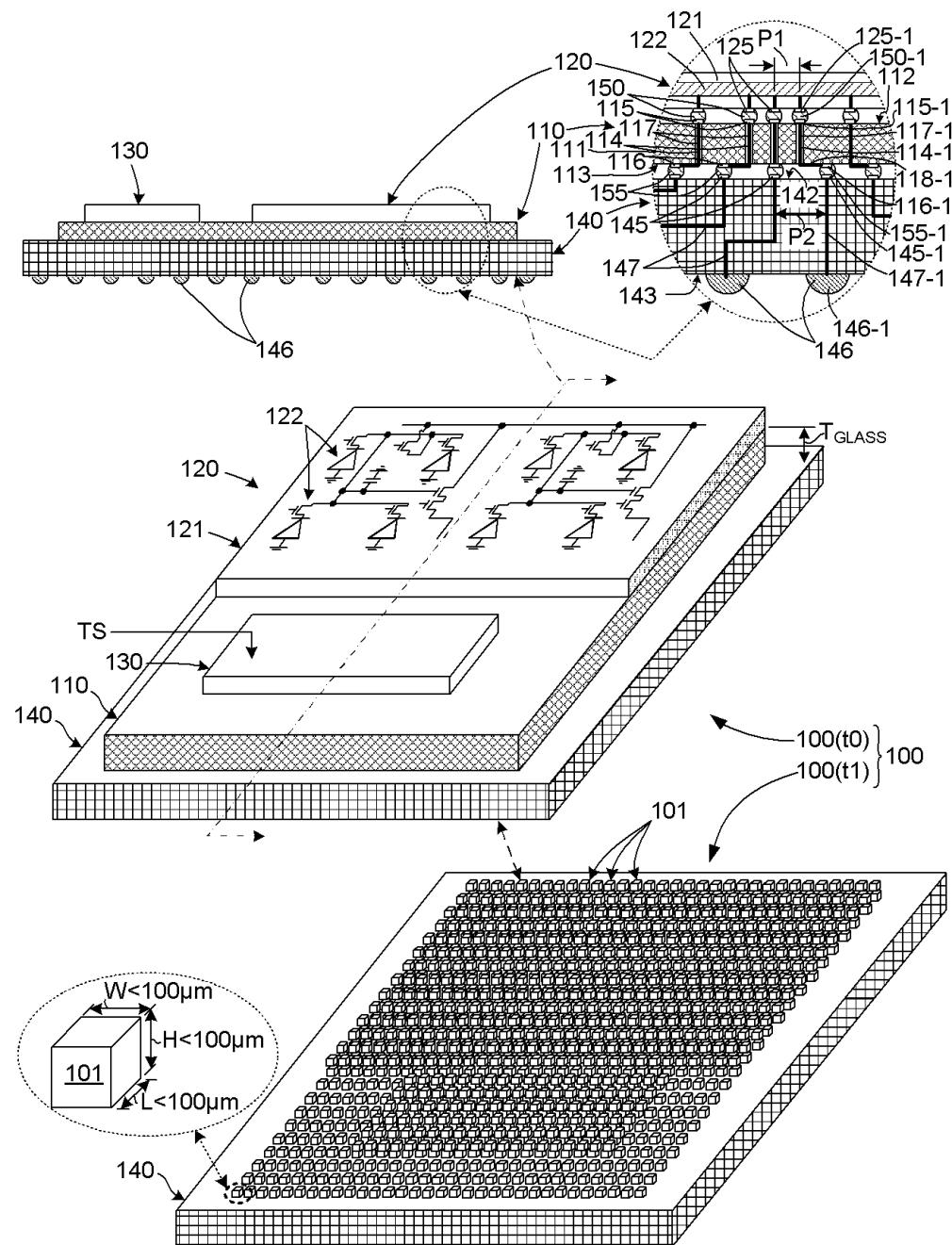

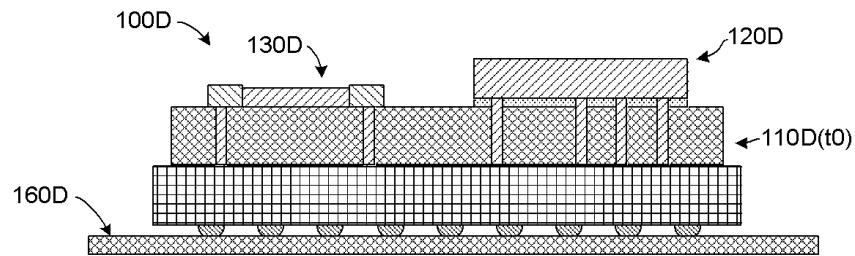

도 1은 본 발명의 예시적인 실시예에 따라 제조된 일시적인 전자장치를 도시하는 상면 사시도.

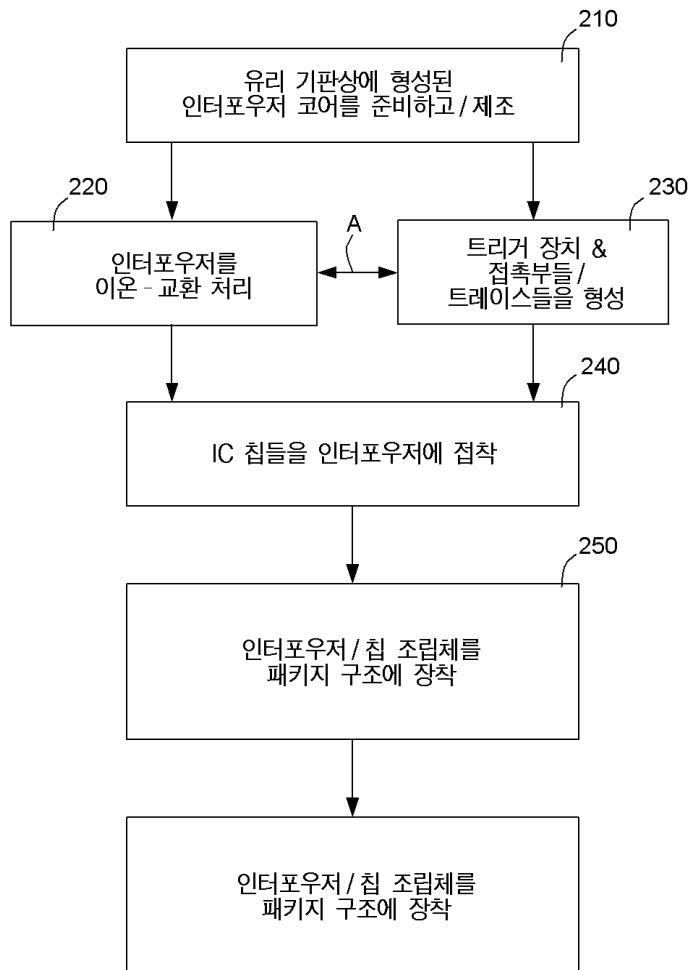

도 2는 도 1의 상기 일시적인 전자장치를 제조하기 위한 일반화된 제조 공정을 도시하는 흐름도.

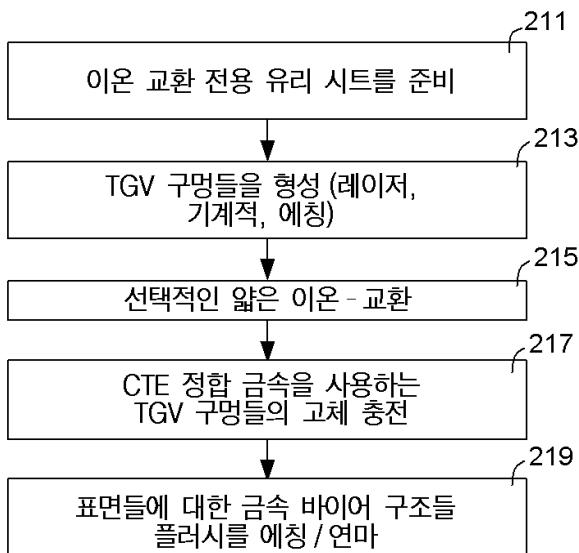

도 3은 본 발명의 실시예에 따른 쓰루-그래스 금속 바이어 구조(through-glass metal via structure)를 포함하는 인터포우저 코어를 제조하기 위한 제조 공정을 도시하는 흐름도.

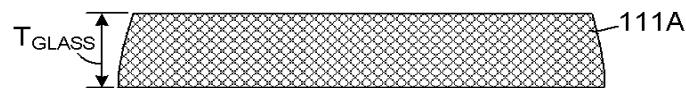

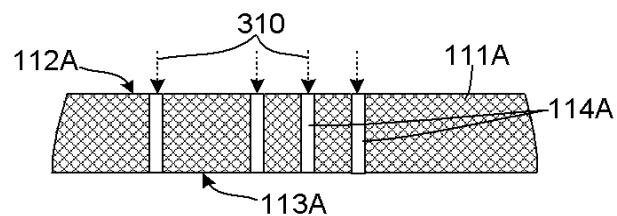

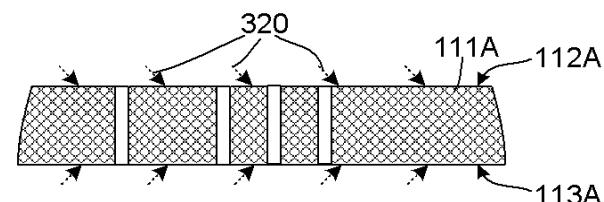

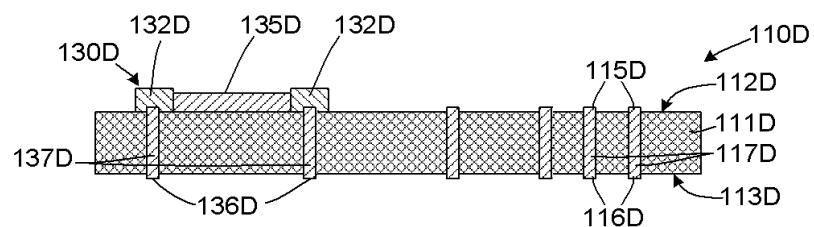

도 3(A), 3(B), 3(C), 3(D) 및 3(E)는 도 3의 공정 흐름에 따른 인터포우저 코어의 제조를 도시하는 단순화된 측면 단면도들.

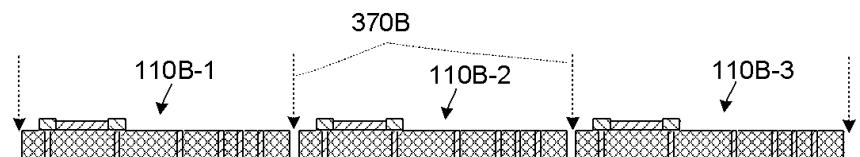

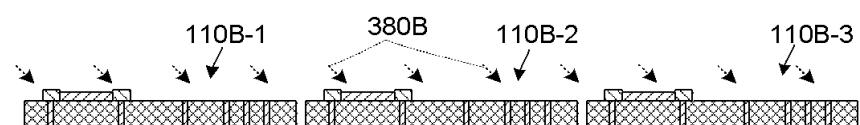

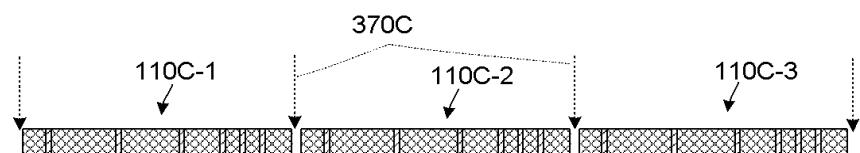

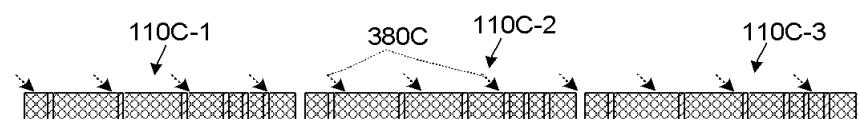

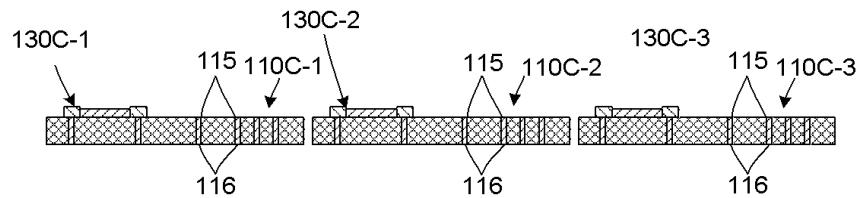

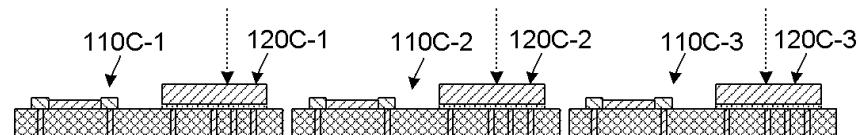

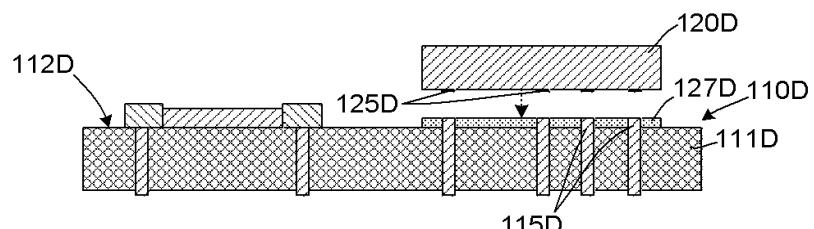

도 4(A), 4(B), 4(C), 4(D) 및 4(E)는 본 발명의 시트 레벨 패터닝 실시예에 따른 다수의 일시적인 전자장치들의 제조를 도시하는 단순화된 측면 단면도들.

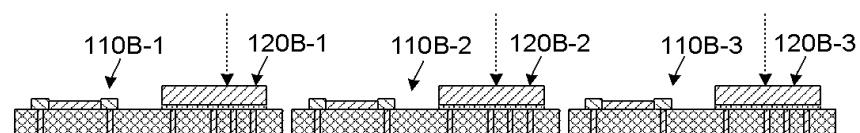

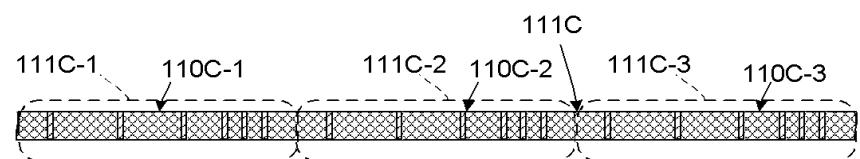

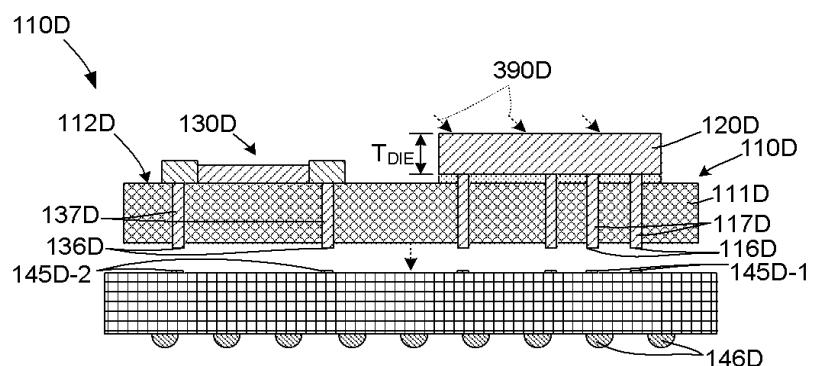

도 5(A), 5(B), 5(C), 5(D) 및 5(E)는 본 발명의 다이 레벨 패터닝 실시예에 따른 다수의 일시적인 전자장치들

의 제조를 도시하는 단순화된 측면 단면도들.

도 6(A), 6(B), 6(C), 6(D), 6(E) 및 6(F)는 본 발명의 다른 하나의 실시예에 따라 제조된 일시적인 전자장치를 도시하는 측면 단면도들.

### 발명을 실시하기 위한 구체적인 내용

[0018]

본 발명은 일시적인 전자장치들에서의 개선에 관한 것이다. 다음의 설명은 이 기술분야에 통상의 지식을 가진 자가 특별한 응용 및 그 필요조건들의 본문에 제공된 발명을 제조 및 사용 가능하게 하기 위해 제공되어 있다. 여기에 사용된 바와 같이, "상부", "상부쪽으로", "하부", "하부쪽으로"와 같은 방향적 용어들은 설명의 목적을 위한 상대적인 위치들을 제공하기 위해 의도된 것이고, 절대적인 준거 틀(absolute frame of reference)을 표기하는 것으로 의도되지는 않는다. 바람직한 실시예에 대한 다양한 수정들이 이 기술분야에 통상의 지식을 가진 자들에게 명백할 것이며, 여기에 정의된 일반적인 원리들은 다른 실시예들에도 적용될 수도 있다. 그러므로, 본 발명은 도시된 그리고 설명된 특정 실시예들에 제한되는 것으로 의도되지는 않지만, 여기에 설명된 원리들 및 참신한 특징들과 부합하는 가장 넓은 범위와 일치할 것이다.

[0019]

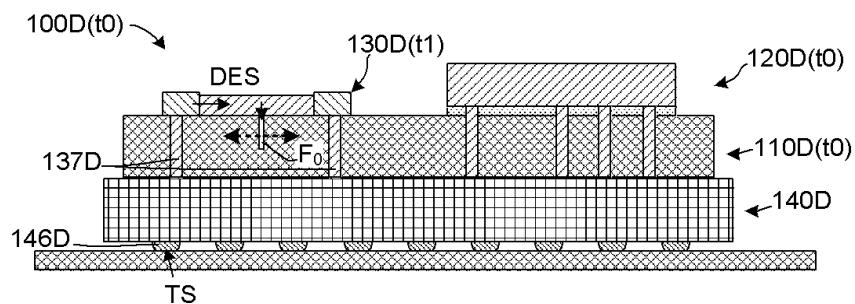

도 1은 순간-전(pre-transience) "온전한" 상태[즉, 도 1의 중앙 및 상부들에 도시된 장치(100)(t0)] 및 순간-후(post-transience) "분말화된" 상태[즉, 도 1의 하부에 도시된 장치(t1)]의 일시적인 전자장치(100)를 도시하는 사시도 및 단면도들을 포함하는 단순화된 도면이다.

[0020]

도 1의 중앙 및 상부들에 관해 설명하자면, 순간-전(pre-transience) 상태(예컨대, 제조 후 즉시)에서, 일시적인 전자장치(100)(t0)는 일반적으로 인터포우저(110) 상에 배치되는 접적회로(IC) 다이(die)(120) 및 트리거 장치(130)를 포함하며, 인터포우저(110)는 예시적인 패키지 구조(140)에 장착된다.

[0021]

도 1의 상부 우측부에 위치한 버블(bubble)에 관해 설명하자면, IC 다이 (120)는 임의의 알려진 반도체 제조기술을 사용하여 기판(121) 상에 형성된 전자회로(122)를 포함하는 접적회로로 장치이며, 바람직한 실시예에서이지만, IC 다이(120)는 실리콘-온-절연체(SOI) 접적회로로 장치이다. 전자장치(122)는, 아래에 설명된 바와 같이, 일시적인 이벤트까지 규정된 유용한 기능(예컨대, 센서 동작들)을 수행하도록 구성되는 1개 이상의 전자소자들을 포함한다. IC 접촉 패드들(125)은 상기 반도체 기판(121)의 표면상에 제1 패턴(P1)으로 배치되며 예컨대, 종래의 금속화 패턴들(미도시)에 의해, 전자장치(122)에 동작 가능하게 결합된다.

[0022]

도 1의 상부 좌측부에 도시된 바와 같이, 패키지 구조(140)는 시스템 회로기판(미도시)으로의 표면-장착 조립을 용이하게 하기 위해 구성된 다수의 볼들 또는 범프들(bumps)(146)을 포함하는 볼-그리드 배열(ball-grid array)(BGA) 패키지 구조로서 예시적인 실시예에 도시되어 있다. 특히, 도 1의 상부 우측부에 위치된 버블로서 표시된 바와 같이, 패키지(140)는 패키지 기판(141)의 상면(142) 상에 제2 패턴(P2)으로 배치된 다수의 (제1) 패키지 접촉구조들(145)을 포함하며, 볼들/범프들(제2 패키지 접촉구조들)(146)은 기판(141)의 하면(143) 상에 배치된 그리고 기판(141)의 하면(143)으로부터 뻗어 있다. 패키지 도체들(147)은 알려진 기술들을 사용하여 형성되며 관련된 접촉구조들 사이의 신호 통로들을 제공하기 위해 패키지 구조(141)를 통해 뻗어 있다(예컨대, 도체(147-1)는 패키지 접촉구조(145-1) 및 관련된 볼/범프(146-1) 사이의 전기적인 통로를 형성). 물론, 패키지 구조(140)는, 핀-그리드(pin-grid) 배열 패키지 구조들과 같은, 다른 패키지 형태들을 사용하여 실시될 수도 있다.

[0023]

도 1의 상부 좌측부에 관해 다시 설명하자면, 종래의 배열들과 유사하게, 인터포우저(110)는 IC 다이(120) 및 패키지 구조(140) 사이에 배치되며, 패키지 기판(140)에 고정되어 IC 다이(120)의 각각의 접촉 패드(125)를 패키지 구조(140) 상의 볼/범프(146)에 결합하는 어댑터로서 기여한다. 특히, 인터포우저(110)는 상면(112) 및, 바람직한 실시예에서는, 100 μm 및 300 μm의 범위의 기판 두께( $T_{GLASS}$ )만큼 분리된 반대편의 하면(113)을 갖는 얇은 유리 기판(111)을 포함한다. 제1 세트의 접촉점들(즉, 금속 패드들 또는 다른 접촉구조들)(115)은 상면(112) 상에 패턴(P1)으로 배치되어, IC 다이가 표면 장착되어 인터포우저(110)에 고정적으로 부착(예컨대, 접착)될 때, 각각의 접촉점(115)의 위치가 동작 가능한 전기적인 연결(예컨대, 납땜 구조들(150)에 의해)을 용이하게 하기 위해 상기 IC 다이(120)의 해당 접촉 패드(125)의 위치와 일치하게 된다. 예를 들면, 도 1의 버블에 표시된 바와 같이, 접촉점(115-1)은 해당 접촉 패드(125-1)와 정렬되며, 납땜 구조(150-1)에 의해 전기적으로 연결된다.

[0024]

인터포우저(110)는 하면(113) 상에 배치된 제2 접촉점들(116)에 의해 패키지 기판(140)에 고정되며, 상기 제2 접촉점들(116)은 패턴(P2)으로 배치되며, 인터포우저(110)가 패키지 구조(140)에 동작 가능하게 장착될 때, 동

작 가능한 전기적인 연결을 용이하게 하기 위해 패키지 구조(140) 상의 해당 패키지 접촉구조들(145)에 각각 전기적으로 연결(예컨대, 납땜 구조들(155)에 의해)된다. 예를 들면, 도 1의 베블에 표시된 바와 같이, 접촉점(116-1)은 해당 접촉구조(145-1)와 정렬되며, 납땜 구조(155-1)에 의해 전기적으로 연결된다. 인터포우저(110)는 추가로 관련된 접촉점들(115, 116) 사이의 전기적인 신호 통로들을 형성하는 다수의 도체들을 포함하며, 각 도체는 유리 기판(111)을 통해 뻗어 있는 관련된 쓰루-그래스 바이어 (through-glass via)(TGV) 구멍(opening)(114)에 배치된 금속 바이어 구조(117), 및 1개 이상의 상면(112) 및 하면(113) 상에 형성되는 선택적인 1개 이상의 금속 트레이스들(traces)을 포함한다. 예를 들면, 접촉점들(115-1, 116-1)은 금속 바이어 구조(117-1) 및 금속 트레이스(118-1)에 의해 형성된 도체에 의해 연결되며, 이것은 하면(113) 상에 형성된다. 따라서, 인터포우저(110)는 접촉점(116-1)에 의해 IC 다이(120)의 접촉 패드(125-1) 및 패키지 구조(140)의 볼/범프(146-1) 사이의 전기적인 신호 통로를 제공하며, 이것은 접촉구조(145-1) 및 도체(147-1)에 의해 볼/범프(146-1)에 연결되고, 상기 도체는 금속 바이어 구조(117-1) 및 금속 트레이스(118-1), 및 접촉점(115-1)에 의해 형성된다.

[0025] 아래에 부가적으로 상세하게 설명된 바와 같이, 트리거 장치(130)는 외부적으로 발생된 트리거 신호(TS)에 반응하여 초기 파괴력을 발생시켜 유리 기판(111)에 인가함에 의해 일시적인 이벤트 동안 IC 다이(120)의 분말화(분열)를 초기화하도록 기능한다. 특히, 트리거 장치(130)는 외부적으로 발생된 트리거 신호(TS)에 반응하여 초기 파괴력을 발생시키기 위해 구성되며, 유리 기판(111)의 상면에 동작 가능하게 부착되어 상기 발생된 초기 파괴력이 유리 기판(111)에 가해진다. 아래에 설명된 바와 같이, 상기 초기 파괴력은 인터포우저(110) 및 IC 다이(120)의 분말화를 야기하기 위한 충분한 에너지를 갖도록 발생된다.

[0026] 본 발명의 특징에 따르면, 유리 기판(111)은 이온-교환 전용 유리 물질(즉, 이온 교환 처리를 감내하는 유리)을 포함하며, 인터포우저(110)는 유리 기판(111)이 충분히 연약하게 되어, 트리거 장치(130)에 의해 발생된 상기 초기 파괴력에 반응하여, 2차 균열들이 발생되어 유리 기판(111)을 분말화시키기 위한 충분한 에너지로 유리 기판(111)을 통해 전달되는 공정들을 사용하여 제조된다. 특히, 인터포우저 코어가 아래에 설명된 방식으로 발생된 후, 유리 기판(111)은 알려진 이온-교환 공정들을 사용하여 처리[탬퍼링(tampering)]되어 유리 기판(111)의 이온적 함유량(즉, 유리 기판(111)에 포함된 이온들의 양)은 상기 유리를 충분히 연약하게 하는 점까지 증가되어, 후속적이면서도 일시적인 이벤트 동안, 2차 균열들이 트리거 장치(130)에 의해 가해진 초기 파괴력에 반응하여 유리 기판(111)에서 발생된다. 게다가, 도 1의 하부에서의 장치[100(t1)]에 의해 표시된 바와 같이, 유리 기판(111)은 이온-교환 처리에 의해 충분히 연약해져서 2차 균열들이 일시적인 이벤트 동안 유리 기판(111)에 걸쳐 전달됨으로써, 유리 기판(111)은 프린스 루퍼트의 드롭(Prince Rupert's Drop)에 포착된 것과 유사한 구조를 사용하여 미크론-크기의 입자들(즉,  $\leq 100 \mu\text{m}$ 의 폭)로 완전히 분해("분말화")한다. 즉, 도 1의 하부 좌측부에 위치된 베블에 표시된 바와 같이, 상기 2차 균열들은 처리된 유리 기판(111)에 걸쳐 급속하게 이동함으로써, 유리 기판(111)은 미크론-크기의 입자들(101)(즉, 거의  $100 \mu\text{m}$ 의 폭보다 작은 길이 L, 폭 W, 및 높이 H 치수들을 갖는)로 갑자기 그리고 돌발적으로 분해(분말화)된다. 상기 연약한 상태를 달성하기 위해 필요한 유리 기판(111)의 최적의 이온 함유량(즉, 인터포우저가 예속되는 이온-교환 처리의 매개변수들)은 유리 기판(111)의 형태 및 두께를 포함하는 몇개의 요소들에 의존하며, 상기 최적의 양을 결정하는 것은 이 기술분야에 통상의 지식을 가진 자들의 역량 내에 있다.

[0027] 본 발명의 다른 하나의 특징에 따르면, IC 다이(120)는 인터포우저(110)에 고정적으로 부착되어 일시적인 이벤트 동안 유리 기판(111)에 발생된 상기 2차 균열들이 IC 다이(120)를 또한 분말화시키는데 충분한 힘으로 전달된다. 종래의 적합한 접합 기술(예컨대, 양극 접합 또는 밀봉 유리에 의해)을 활용하여 IC 다이(110)를 유리 기판(111)에 고정적으로 부착함으로써, 유리 기판(111)에 발생된 상기 2차 균열들은 또한 IC 다이(120)를 분말화시키는데 충분한 에너지로 IC 다이(120)로 전달된다(즉, 도 1의 하부에 도시된 바와 같이, 실질적으로 인터포우저(110)의 분말화와 동시에). 그러므로, 본 발명은 IC 다이(120) 상에 형성된 기능회로가 종래의(예컨대, 가용성 기판) 기술들을 사용하여 가능한 것보다 상당히 짧은 시간에서 효과적으로 사라지는(분말화하는) 일시적인 전자장치(100)의 제조를 용이하게 한다. 게다가, 비공인된 테이퍼링(tapering)[예컨대, 패키지 구조(140) 또는 일시적인 장치(100)가 장착되는 시스템 회로기판(미도시)으로 탬퍼링(tampering)]의 검출시에 분말화를 시작하기 위해 트리거 장치(130)를 구성함으로써, 본 발명은 IC 다이(120)가 온전한 동안 전자회로(122)에의 비공인된 액세스를 방지함으로써 보안(security) 및 반-탬퍼링 보호(anti-tampering protection) 둘다 모두를 제공한다. 게다가, 인터포우저(110)는 현존하는 저비용의 IC 제조기술들과 호환성이 있기 때문에, 본 발명은 코어 IC 제조 공정들에 대한 최소의(또는 잠재적으로 임의의 수정이 없는) 수정을 갖는 일시적인 전자장치(100)의 제조를 용이하게 한다.

[0028]

도 2는 예시적인 실시예에 따라 일시적인 전자장치(100)(도 1 참조)를 제조하기 위한 제조공정을 도시하는 흐름도이며, 상기 방법은 일반적으로 인터포우저(110)를 이온-교환 처리한 다음, IC 다이(120)를 처리된 유리 기판(111)에 고정적으로 부착한 다음, 인터포우저(110)를 패키지(140)에 고정시키는 단계를 포함한다. 도 2의 상부에서의 블록(210)에 관해 설명하자면, 상기 방법은 인터포우저 코어(금속 바이어(via) 구조들을 포함하지만, 접촉구조들, 금속 트레이스들(traces) 또는 트리거 장치를 포함하지는 않는 적합한 유리 기판)를 준비하거나 제조함으로써 시작한다. 예시적인 인터포우저 코어의 제조는 도 3 및 도 3(A) 내지 도 3(E)를 참조하여 아래에 설명된다. 다음으로, 이온-교환 처리가 상기 유리 기판(블록 220)의 이온적 함유량을 증가시키기 위해 수행되며, 상기 인터포우저의 제조는 완료된다(즉, 접촉구조들은 도 1과 관하여 위에 설명된 패턴들(P1 및 P2)과 같은, 미리 결정된 배열들에 따라 형성되며, 금속 트레이스들은 하나나 둘다 모두의 기판 표면들 상에 형성되고, 트리거 장치는 상기 유리 기판상에 형성 또는 장착된다). 도 2에 화살표 A에 의해 표시되고 아래에 설명된 예시적인 특정 실시예들에 설명된 바와 같이, 완료되지 않은 인터포우저 코어는 블록(220)에서 이온-교환 처리되거나, 상기 인터포우저는 블록(230)에서 완료된 다음, 블록(220)에서 이온-교환 처리된다. 블록(240)에 표시된 바와 같이, 이온-교환 처리가 수행된 후, 1개 이상의 IC 다이(들)는 일시적인 이벤트들 동안 상기 IC 다이(들)을 분말화시키는데 충분한 에너지를 갖도록 상기 인터포우저로부터 상기 IC 다이(들)로의 2차 균열들의 전달을 촉진시키는 다이-접착 기술들을 사용하여 위에 설명된 방식으로 각각의 인터포우저에 접착된다. 블록(250)에 관해 설명하자면, 상기 인터포우저는 다음으로 패키지 구조에 동작 가능하게 고정됨으로써[예컨대, 도 1에 도시된, BGA 패키지 구조(140)], 상기 일시적인 전자장치는 호스트 시스템으로의 조립을 위해 준비된다.

[0029]

도 3은 본 발명의 실시예에 따른 인터포우저 코어를 제조하기 위한 제조 공정을 도시하는 흐름도이며, 도 3(A) 내지 도 3(E)는 도 3의 공정 흐름의 다양한 단계들 동안의 예시적인 인터포우저 코어를 도시하는 도면들이다.

[0030]

도 3의 블록(211) 및 도 3(A)에 관해 설명하자면, 상기 공정은 적합한 두께  $T_{GLASS}$ 를 갖는 이온-교환 전용 유리 시트(111A)를 준비함으로써 시작한다. 적합한 이온-교환 전용 유리가 강화되지 않은 코닝 고릴라 그래스(Corning Gorilla Glass), 쇼트 쟁세이션(SCHOTT Xensation) 및 AGC 드래곤트레일 유리(AGC Dragontrail glass)를 포함하며, 이것들은 캘리포니아, 산타 폴라에 있는 압리사 테크놀로지(Abrisa Technologies in Santa Paula, CA)와 같은, 다양한 유리 판매업체로부터 유용하다.

[0031]

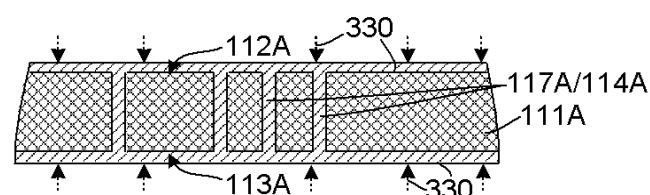

도 3의 블록(213) 및 도 3(B)에 관해 설명하자면, 쓰루-그래스 바이어(through-glass via)(TGV) 구멍들(openings)(114A)은 전적으로 유리 기판(111A)(즉, 상면(112A) 및 하면(113A) 사이의)을 통해 뻗어 있도록 형성된다. 선택적인 특정 실시예들에서, TGV 구멍들(openings)(114A)은 레이저 에칭 공정, 기계적 에칭 공정 및 화학적 에칭 공정(이것들은 종합적으로 도 3(B)에서 화살표들(310)에 의해 표시됨) 중 하나를 사용하여 유리 기판(111A)의 부분들을 에칭하거나 그렇지 않으면 제거함으로써 형성된다.

[0032]

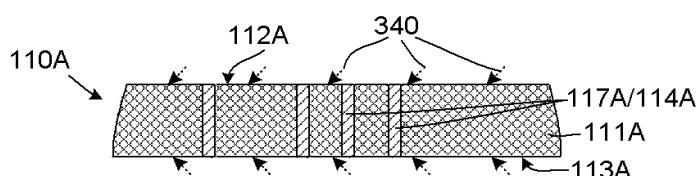

도 3의 블록(215) 및 도 3(C)에 관해 설명하자면, 선택적이면서도 괴상적인 이온-교환 공정(화살표들(320)에 의해 표시된)이 다음으로 수행된다(즉, TGV 구멍들(openings)(114)에 금속 바이어 구조들을 형성하기 전).

[0033]

금속 바이어 구조(117A)는 다음으로 적합한 방법을 사용하여 각각의 TGV 구멍들(openings)(114A)에 형성된다. 도 3의 블록(217) 및 도 3(D)에 관해 설명하자면, 1개의 특정 실시예에서, 금속 물질(330)은 상면(112A) 및 하면(113A) 위에 퇴적되어 상기 금속 물질의 부분들이 각각의 TGV 구멍(opening)(114A)에 들어가며 해당 금속 바이어 구조들(117A)을 형성한다. 도 3의 블록(219) 및 도 3(E)에 관해 설명하자면, 상기 금속 물질의 잔여 부분들은 그 다음으로, 예컨대, 적합한 부식제(腐蝕劑)를 사용하여 상면(112A) 및 하면(113A)으로부터 제거된다. 도 3(E)에 도시된 바와 같이, 상기 에칭 공정이 수행되어 그 결과의 인터포우저 코어(110A)가 유리 기판(111A)을 통해 뻗어 있으며 각각 상면(112A) 및 하면(113A) 상에 노출되는 반대의 단부들을 갖는 각각의 금속 바이어 구조(117A)를 포함하며, 이것은 후속적으로 형성된 구조들(예컨대, 인터포우저 접촉구조들 및 금속 트레이스 구조들)로의 연결을 용이하게 한다.

[0034]

위에 설명된 인터포우저 코어들은 그 다음으로 IC 다이들이 장착되는 완성된 인터포우저들을 제공하기 위해 처리된다. 선택적이면서도 예시적인 실시예들에 따르면, 인터포우저 코어들은 시트 레벨 패터닝 또는 다이 레벨 패터닝을 사용하여 처리된다. 예시적인 시트 레벨 패터닝 공정은 도 4(A) 내지 도 4(E)와 관련하여 아래에 설명되며, 예시적인 다이 레벨 패터닝 공정은 도 5(A) 내지 도 5(E)와 관련하여 아래에 설명된다.

[0035]

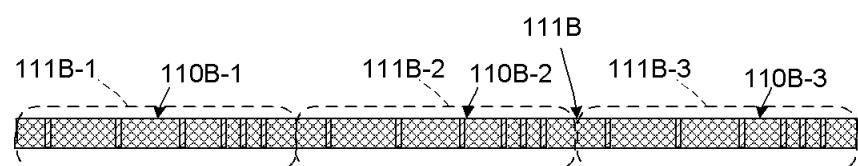

시트 레벨 및 다이 레벨 공정은 단일 유리 시트 상에 형성되어 함께 일체형으로 연결되는 다수의 인터포우저 코어들로 시작된다. 예를 들면, 도 4(A)에 도시된 바와 같이, 단일(연속적인/파괴되지 않은) 유리 시트(111B)는 3 개의 일체형으로 연결된 인터포우저 코어들(110B-1, 110B-2 및 110B-3)을 포함하며, 그 각각은 유리 시트(111

B)의 해당 부분에 의해 형성된 각각의 유리 기판(111B-1 111B-2 및 111B-3)을 갖는다. 유사하게, 도 5(A)에 도시된 바와 같이, 일체형 인터포우저 코어들 (110C-1, 110C-2 및 110C-3)은 각각 단일 유리 시트(111C)의 해당 부분들에 의해 형성된 유리 기판들(111C-1 111C-2 및 111C-3)을 갖는다.

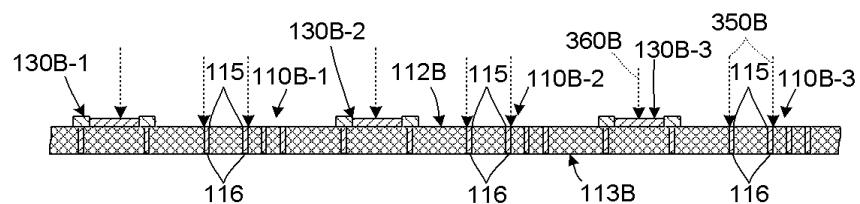

[0036] 도 4(A)에 도시된 일체형 인터포우저 코어들로 시작하여, 도 4(B)에 도시된 바와 같이, 시트 레벨 패터닝은 알려진 기술을 사용하여 접촉구조들, 선택적인 금속 트레이스 구조들, 및 트리거 장치들을 각각의 인터포우저 코어에 패터닝함으로써 시작된다. 예를 들어, 접촉구조들(115)(및 선택적인 금속 트레이스 구조들, 미도시)은 적합한 금속(350B)을 상부 시트면(112B)에 인쇄함에 의해 유리 시트(111B)에 형성된다. 접촉구조들(116) 및 선택적인 금속 트레이스 구조들(미도시)은, 예컨대, 시트(111B)를 전도(顛倒)시키고 금속 인쇄 공정을 반복함으로써 하부 시트면 (113B) 상에 형성된 후 형성된다.

[0037] 트리거 장치들(130B-1 내지 130B-3)은 그 다음으로 인쇄 공정을 사용하여 적합한 물질(360B)을 퇴적함으로써, 또는 미리-형성된 구조를 각각의 인터포우저(110B-1 내지 110B-3)에 각각 표면 장착함으로써 형성된다. 도 4(C)에 관해 설명하자면, 그 다음으로, 유리 시트(111B)가 인터포우저들(110B-1 내지 110B-3)을 서로 분리하기 위해 다이싱(dice)된 다음(예컨대, 레이저(370B)를 사용하여 절단), 개별적인 인터포우저들(110B-1 내지 110B-3)은 이온-교환 처리된다(도 4(D)에 도시된 바와 같은 화살표들(380B)에 의해 표시됨). 도 4(E)에 도시된 바와 같이, 이온-교환 처리 후에, IC 다이들(120B-1, 120B-2 및 120B-3)은 그 다음으로 각각 인터포우저들(110B-1 내지 110B-3)에 접착된다.

[0038] 도 5(A) 내지 도 5(E)에 도시된 다이 레벨 패터닝은 각각의 인터포우저 코어를 개별적으로 처리하는 것을 포함한다. 즉, 도 5(A)에 도시된 일체형 인터포우저 코어들로 시작하면, 다이 레벨 패터닝은 인터포우저 코어들 (110C-1 내지 110C-3)을 서로 분리하기 위해 다이싱(예컨대, 레이저(370C)를 사용하여 절단)으로 시작된 다음, 상기 개별적인 인터포우저 코어들(110C-1 내지 110C-3)은 도 5(C)에 도시된 바와 같이 이온-교환 처리(화살표들 (380C)에 의해 표시됨)된다. 이온-교환 처리 후에, 도 5(D)에 도시된 바와 같이, 접촉구조들(115 및 116), 선택적인 금속 트레이스 구조들, 및 트리거 장치들(130C-1 내지 130C-3)은 위에 설명된 기술들을 사용하여 각각의 인터포우저 코어들(110C-1 내지 110C-3) 상에 형성된 다음, 도 5(E)에 도시된 바와 같이, IC 다이들(120C-1, 120C-2 및 120C-3)은 각각 인터포우저들(110C-1 내지 110C-3)에 접착된다.

[0039] 도 6(A) 내지 도 6(F)는 본 발명의 다른 하나의 실시예에 따른 일시적인 전자장치(100D)의 제조 및 후속적인 작동을 도시하는 도면들이다.

[0040] 도 6(A)는 위에 설명된 방법론과 부합하는 방식으로 제조된 인터포우저(100 D)를 도시하는 도면이다. 설명용으로, 각각 상면(112D) 및 하면(113D) 상에 배치되는 관련된 접촉구조들(115D 및 116D)은 관련된 금속 바이어 구조(117D)를 포함하는 단순한 접촉구조들에 의해 연결된다. 본 실시예에서, 트리거 장치(130D)는 전기적으로 제어되며, 특히 금속 바이어 구조들(137D)을 통해 전달된 인가된 전기 펄스에 반응하여 국부 가열을 발생하기 위한 가열소자를 활용하며, 상기 금속 바이어 구조들은 하면(113D) 상에 배치된 관련된 접촉구조들(136D)에 연결된다. 한 실시예에서, 트리거 장치(130D)는 넓은/더 두꺼운 더욱 낮은 저항 전극들(132D)을 금속 바이어 구조들 (137D)의 관련된 상부 단부들에 형성한 다음, 저항성의, 얇은, 좁은 저항(액튜에이터) 구조(135D)를 전극들 (132D) 사이에 형성함으로써 구성되며, 저항 구조(135D)는 고온 유지 가능한 물질(예컨대, 텅스텐과 같은 금속)을 사용하여 형성된다. 트리거 장치(130D)는 표준 미세 가공기술(microfabrication techniques)(증착 및 광-패터닝)을 사용하거나 단순히 쉐도우-마스크 증착(shadow-masked evaporation)을 통해 유리 기판(110D)에 직접 제조된다.

[0041] 도 6(B)는 밀봉 유리(127D) 또는 양극 접합에 의해 유리 기판(111D)에의 IC 다이(120D)의 후속적인 고정된 부착을 도시하는 도면이다. 도 1과 관련하여 위에 설명된 바와 같이, IC 다이(120D)는 접촉 패드들(125D)이 유리 기판(111D)의 상면 (112D) 상에 배치된 접촉구조들(115D)과 전기적인 접촉을 하도록 장착된다.

[0042] 도 6(C)는 일시적인 전자장치(110D)의 조립을 완성하기 위해 인터포우저(110D)를 패키지 구조(140D)에 고정하는 것을 도시하는 도면이다. 상기한 바와 같이, 인터포우저(110D)는 패키지 접촉구조들(145D-1)이 해당 인터포우저 접촉구조들(116 D)에 전기적으로 연결되도록 장착되며, 이것들은 유리 기판(111D)의 하면(113D) 상에 배치된다. 이러한 실시예에서, 트리거 장치(130D)의 작동은 또한 패키지 접촉구조들(145D-2) 및 해당 접촉구조들 (136D) 사이의 전기적인 연결에 의해 가능해지며, 이것은 인터포우저(110D)에 배치된 패키지 구조(140) 및 금속 바이어 구조들(137D)에 형성된 도체들(미도시)에 의해 패키지 구조(140D)의 볼들/범프들(146D) 및 트리거 장치 (130D) 사이의 신호 통로를 형성한다.

- [0043] 도 6(C)에 도시된 바와 같이, 일 실시예에서 IC 다이(120D)는 분말화를 추가로 촉진시키기 위해 실제적인 두께  $T_{DIE}$  로의 화학적 기계적인 연마(CMP)(390D)를 통해 박막화된다. IC 다이(120D)의 분열을 달성하기 위한 주요한 열쇠는 유리 기판(111D)으로부터 IC 다이(120D)로의 균열 크랙들(fracture cracks)의 전달을 결합시키는 것이며, 이것은 추가로 IC 다이(120D)를 박막화함으로써 가능하다(즉, 도시된 바와 같이, 인터포우저(110D)에의 부착 후 또는 부착 전). 상기 균열 공정은 2개의 가능한 결과들 사이의 경쟁으로서 보여질 수 있다: 크랙은 다이 기판/실리콘 쪽으로의 위쪽으로 전달될 수 있거나, 금커브를 하여 대신에 접합 영역을 통해 전달되어, 분리(de-bonding)로 이끌어진다. 유리/실리콘 접합을 위해 필요한 비(比)를 초과하기 위해, 양극 접합 또는 저융점 밀봉 유리(127D)가 IC 다이(120D)를 유리 기판(111D)에 고정시키기 위해 활용된다.

- [0044] 선택적으로, 저온 또는 접착 결합(adhesive bonding)이 IC 다이(120D)를 유리 기판(110D)에 고정시키기 위해 사용될 수도 있다.

- [0045] 도 6(D)는 시스템 레벨 인체회로기판(160D)에의 일시적인 전자장치(100D)의 후속적인 부착을 도시하는 도면이고, 이것은 패키지 구조(140D) 및 인터포우저(110 D)에 의해 IC(120D)에 전력을 공급하며 IC(120D)와 통신한다. 예시적인 실시예에서, 회로기판(160D)은 하우징의 비공인된 조작(tampering)을 검출할 수 있는 보안 시스템(예컨대, 센서들), 및 IC 다이(120D) 및 트리거 장치(130D)와 통신하도록 구성된 제어 시스템을 포함하는 고정된 하우징(미도시) 내에 장착된다. 즉, 정상적인 동작 상태들하에, 상기 시스템 제어기는 IC 다이의 기능적인 동작을 용이하게 한다.

- [0046] 그러나, 도 6(E) 및 도 6(F)와 관련하여 아래에 설명된 바와 같이, 상기 시스템 제어기가 상기 시스템 하우징의 비공인된 조작(tampering)을 검출할 때(이것은 IC 다이(120D)의 기능회로에 액세스 또는 조작하기 위한 시도와 관련될 수도 있다), 상기 시스템 제어기는 일시적인 이벤트를 시작하기 위해 트리거 장치(130D)에 트리거 신호들을 전송한다.

- [0047] 도 6(E) 및 도 6(F)는 일시적인 이벤트 동안 일시적인 전자장치(100D)의 제어된 파괴(분해)를 예시한다(즉, 패키지 구조(140D)의 볼들/범프들(146D)에 의해 일시적인 전자장치(100D)에 인가된 트리거 신호 TS에 반응하여). 예시적인 실시예에서, 트리거 장치(130D)에 의해 발생된 균열의 구조는 저항 구조(135D)에 의해 가열된 유리 기판(110D)의 부분이 팽창하면서 발생된 후우프 변형력(變形力)(hoop stress)이다. 상기 트리거 장치들의 시뮬레이션은 전류 펄스가 인가된 0.5 ms 후, 100-150 MPa 범위의 인장 후우프 변형력(變形力)이 저항 구조의 아래에 존재함을 나타낸다 -- 이것은 거의 임의의 전통적으로 강화된 유리에서의 균열을 초기화하는데 충분할 것이다. 이러한 시뮬레이션 결과들은 큰 표면 인장 응력(surface tensile stresses)이 보통 양의 전류 및 에너지로 얻어질 수 있음을 나타낸다.

- [0048] 이 예에서, 텅스텐에 대한 특성을 사용하는 저항 추정치들에 근거하여, 전류는 거의 70 mA이며, 저항에 걸린 전압은 약 80 mV이다. 이 양들은 현재 유용한 소형 인수(小型因數)(small-form-factor) 밧데리들의 능력 내에 있다. 도 6(E)에 도시된 바와 같이, 시간  $t_0$ 에서(즉, 트리거 신호 TS의 전송 후 즉시), 결과의 초기 균열  $F_0$ 는 국부화된 가열에 의해 유리 기판(110D)에서 발생되나, IC 다이(120D)는 전적으로 온전하게 남아 있다. 도 6(F)에 도시된 바와 같이, 2차 균열들  $F_p$ 는 유리 기판[111D( $t_1$ )]에 걸쳐 전달되는 초기 균열력에 반응하여 유리 기판[111D( $t_1$ )]에서 발생됨으로써, 상기 유리 기판[111D( $t_1$ )]은 미립들(particulates)(101D)로 분말화된다. 게다가, IC 다이(120D)( $t_1$ )가 유리 기판[111D( $t_1$ )]에 충분히 접착되기 때문에, 2차 균열들  $F_p$ 는 다이 물질을 미립들(particulates)(101D)로 분말화시키는데 충분한 에너지로 IC 다이[(120D)( $t_1$ )]로 전달된다.

- [0049] 이전의 실시예에 설명된 상기 국부화된 가열 수단에 더하여, 다른 트리거 장치들이 상기 장치의 분말화를 발생시키는데 필요한 초기 균열을 발생시키기 위해 활용될 수도 있다. 예를 들면, 적합한 트리거 장치들은 상기 유리 기판의 표면상의 화학적 반응을 초기화함으로써, 또는 국부화된 기계적 압력(예컨대, 압전소자를 사용하여)을 상기 유리 기판에 가함으로써 국부화된 균열을 발생하도록 제조될 수도 있다.

- [0050] 본 발명은 일정한 특정 실시예들에 관하여 설명되어졌지만, 본 발명의 독창적인 특징들은 다른 실시예들에도 적용 가능하며, 그것의 모든 것들은 본 발명의 범위내에 속하도록 의도되었음이 이 기술분야에 통상의 지식을 가진 자들에게 분명할 것이다.

도면

도면1

## 도면2

## 도면3

도면3a

도면3b

도면3c

도면3d

도면3e

도면4a

도면4b

도면4c

도면4d

도면4e

도면5a

도면5b

도면5c

도면5d

도면5e

도면6a

도면6b

도면6c

도면6d

도면6e

도면6f