(19) **日本国特許庁(JP)**

# (12) 公 開 特 許 公 報(A)

(11)特許出願公開番号

特開2007-6433 (P2007-6433A)

(43) 公開日 平成19年1月11日(2007.1.11)

(51) Int.C1.

FΙ

テーマコード (参考)

HO3G 11/02 HO3G 11/04 (2006, 01) (2006, 01) HO3G 11/02 HO3G 11/04

Z

5 J O 3 O

審査請求 未請求 請求項の数 13 〇L (全 15 頁)

(21) 出願番号 (22) 出願日

特願2005-253804 (P2005-253804) 平成17年9月1日(2005.9.1)

(31) 優先権主張番号 特願2005-151235 (P2005-151235)

(32) 優先日

平成17年5月24日 (2005.5.24)

(33) 優先権主張国

日本国(JP)

(71) 出願人 000006013

三菱電機株式会社

東京都千代田区丸の内二丁目7番3号

(74)代理人 100066474

弁理士 田澤 博昭

(74)代理人 100088605

弁理士 加藤 公延

(74)代理人 100123434

弁理士 田澤 英昭

(74)代理人 100101133

弁理士 濱田 初音

(72) 発明者 半谷 政毅

東京都千代田区丸の内二丁目2番3号 三

菱電機株式会社内

最終頁に続く

(54) 【発明の名称】リミッタ回路

# (57)【要約】

【課題】 部品点数を削減でき、小型化、低価格化、低 リーケージ化および低損失化を実現するリミッタ回路を 得る。

【解決手段】 入力端子1 a からの高周波信号を分岐す る結合回路 2 と、入力側キャパシタ 3 a と出力側キャパ シタ3bとの間に高周波信号線路7を挟んで並列接続さ れた複数のPINダイオード回路6a,6bと、結合回 路2の分岐側から入力される高周波信号の信号レベルに 応じた直流バイアスを入力側キャパシタ3 a と出力側キ ャパシタ3 bとの間に供給する検波回路8とを備えたも のである。

一組の結合回路2および検波回路8によって複数のP INダイオード回路6a,6bに直流バイアスを供給す るので、部品点数を削減でき、小型化、低価格化、低リ ーケージ化および低損失化を実現することができる。

図 1 【選択図】

## 【特許請求の範囲】

### 【請求項1】

入力端子からの高周波信号を分岐する結合回路と、

PINダイオードの一端が上記結合回路の通過側と出力端子との間に並列接続されると共に他端がグランドに接続された複数のPINダイオード回路と、

上記入力端子と上記複数のPINダイオード回路のうちの最も上記結合回路の通過側に接続されたPINダイオード回路との間のいずれかの個所に直列接続された入力側キャパシタと、

上記複数のPINダイオード回路のうちの最も上記出力端子側に接続されたPINダイオード回路とその出力端子との間に直列接続された出力側キャパシタと、

上記結合回路の分岐側から入力される高周波信号の信号レベルに応じた直流バイアスを上記入力側キャパシタと上記出力側キャパシタとの間に供給する検波回路とを備えたリミッタ回路。

# 【請求項2】

入力端子からの高周波信号を分岐する結合回路と、

PINダイオードの一端が上記結合回路の通過側と出力端子との間に並列接続されると共に他端がグランドに接続された少なくとも1つ以上のPINダイオード回路と、

上記少なくとも 1 つ以上の P I N ダイオード回路のうちの最も上記出力端子側に接続された P I N ダイオード回路とその出力端子との間に接続された高周波信号線路と、

上記入力端子と上記少なくとも 1 つ以上の P I N ダイオード回路のうちの最も上記結合 回路の通過側に接続された P I N ダイオード回路との間のいずれかの個所に直列接続された入力側キャパシタと、

上記高周波信号線路と上記出力端子との間に直列接続された出力側キャパシタと、

上記結合回路の分岐側から入力される高周波信号の信号レベルに応じた直流バイアスを上記高周波信号線路と上記出力側キャパシタとの間に供給する検波回路とを備えたリミッタ回路。

# 【請求項3】

隣り合うPINダイオード回路間に高周波信号線路を備えたことを特徴とする請求項1 または請求項2記載のリミッタ回路。

#### 【請求項4】

高周波信号線路の線路長を、使用周波数における4分の1波長としたことを特徴とする請求項2または請求項3記載のリミッタ回路。

#### 【請求項5】

1 つの P I N ダイオード回路を、 複数 の P I N ダイオードの並列 接続 からなるようにしたことを特徴とする請求項 1 から請求項 4 のうちのいずれか 1 項記載のリミッタ回路。

## 【請求項6】

PINダイオード回路は、

PINダイオードのアノードが結合回路の通過側と出力端子との間に接続されると共にカソードがグランドに接続され、

検波回路は、

上記結合回路の分岐側から入力される高周波信号の信号レベルに応じた正の直流バイアスを供給するようにしたことを特徴とする請求項1から請求項5のうちのいずれか1項記載のリミッタ回路。

# 【請求項7】

P I N ダイオード回路は、

PINダイオードのカソードが結合回路の通過側と出力端子との間に接続されると共にアノードがグランドに接続され、

検波回路は、

上記結合回路の分岐側から入力される高周波信号の信号レベルに応じた負の直流バイアスを供給するようにしたことを特徴とする請求項1から請求項5のうちのいずれか1項記

10

20

30

40

載のリミッタ回路。

# 【請求項8】

高周波信号線路は、

複数の高周波信号線路に分割されると共に、それら複数の高周波信号線路は直列に接続され、

検波回路は、

上記結合回路の分岐側から入力される高周波信号の信号レベルに応じた直流バイアスを それら複数の高周波信号線路の接続点のうちのいずれかの接続点に接続するようにしたことを特徴とする請求項2から請求項4のうちのいずれか1項記載のリミッタ回路。

#### 【請求項9】

結合回路の分岐側と検波回路との間に接続され、その結合回路の高周波結合特性を補償する補償回路を備えたことを特徴とする請求項1から請求項8のうちのいずれか1項記載のリミッタ回路。

# 【請求項10】

結合回路は、

使用周波数における4分の1波長よりも短い結合線路を有し、

補償回路は、

使用周波数帯で高周波信号の通過レベルが周波数が高くなるにつれて減少する特性を有することを特徴とする請求項9記載のリミッタ回路。

#### 【請求項11】

補償回路は、

使用周波数帯における所望周波数よりも低い周波数で整合を取ることを特徴とする請求項 1 0 記載のリミッタ回路。

#### 【請求項12】

請求項1から請求項11に記載のリミッタ回路のうちの同一または異なる複数のリミッタ回路を直列接続したことを特徴とするリミッタ回路。

# 【請求項13】

入力端子からの高周波信号を分岐する第1のハイブリッド回路と、

上記第1のハイブリッド回路の通過側に入力側が接続された請求項1から請求項11のうちのいずれか1項記載の第1のリミッタ回路と、

上記第1のハイブリッド回路の分岐側に入力側が接続され、上記第1のリミッタ回路と 共に並列に接続された請求項1から請求項11のうちのいずれか1項記載の第2のリミッタ回路と、

上記第1のハイブリッド回路に接続された第1の終端抵抗と、

上記第1のリミッタ回路の出力側に結合側が接続されると共に上記第2のリミッタ回路の出力側に通過側が接続され、それら第1および第2のリミッタ回路の出力を結合すると共に出力端子から出力する第2のハイブリッド回路と、

上記第2のハイブリッド回路に接続された第2の終端抵抗とを備えたリミッタ回路。

# 【発明の詳細な説明】

### 【技術分野】

[0001]

この発明は、不要な高周波を低減するリミッタ回路に関するものである。

## 【背景技術】

# [0002]

従来のリミッタ回路としては、リミッタ要素回路として、2つのDCカットコンデンサと、それら2つのDCカットコンデンサ間に並列に接続された1つのPINダイオードと、入力側に接続された結合回路と、その結合回路に接続され、整流ダイオードおよび高周波阻止インダクタからなり、PINダイオードの出力側にバイアスを供給する検波回路とを備え、2つのリミッタ要素回路を直列に接続すると共に、2つのリミッタ要素回路の信号制限レベルが1段目から2段目に向けて順次低くなるように構成することにより、少な

10

20

30

50

40

20

30

40

50

い段数と調整で広いレンジの信号レベル制限特性が適正に得られるようにしたものがある (例えば、特許文献 1 参照)。

[00003]

【特許文献1】特開2004-40173号公報

【発明の開示】

【発明が解決しようとする課題】

[0004]

従来のリミッタ回路は以上のように構成されているので、1つのリミッタ要素回路を構成単位として、一組の結合回路および検波回路によって1つのPINダイオードにしかバイアスを供給していないので、低リーケージ化(高遮断性能化)するために複数のPINダイオードを設ける場合には、それらPINダイオードの数に応じた組数の結合回路および検波回路、すなわち、複数のリミッタ要素回路を設けなくてはならず、部品点数が多くなり、小型化、低価格化および低損失化の妨げになる課題があった。

また、検波回路からのバイアスを、PINダイオードの出力側に直接に供給するようにしたので、PINダイオードを通過した高い信号レベルの高周波信号が迂回して検波回路に印加され、検波回路の耐電力性を高めるために新たに保護回路等を設ける必要が生じ、その結果、部品点数が多くなり、小型化、低価格化、低リケージ化および低損失化の妨げになるなどの課題があった。

[00005]

この発明は上記のような課題を解決するためになされたもので、部品点数を削減でき、 小型化、低価格化、低リーケージ化および低損失化を実現するリミッタ回路を得ることを 目的とする。

【課題を解決するための手段】

[0006]

この発明に係るリミッタ回路は、入力端子からの高周波信号を分岐する結合回路と、PINダイオードの一端が結合回路の通過側と出力端子との間に並列接続されると共に他端がグランドに接続された複数のPINダイオード回路と、入力端子と複数のPINダイオード回路のうちの最も結合回路の通過側に接続されたPINダイオード回路との間のいずれかの個所に直列接続された入力側キャパシタと、複数のPINダイオード回路のうちの最も出力端子側に接続されたPINダイオード回路と出力端子との間に直列接続された出力側キャパシタと、結合回路の分岐側から入力される高周波信号の信号レベルに応じた直流バイアスを入力側キャパシタと出力側キャパシタとの間に供給する検波回路とを備えたものである。

【発明の効果】

[0007]

この発明によれば、一組の結合回路および検波回路によって複数のPINダイオード回路に直流バイアスを供給するように構成したので、部品点数を削減でき、小型化、低価格化、低リーケージ化および低損失化を実現するリミッタ回路が得られる効果がある。

【発明を実施するための最良の形態】

[0008]

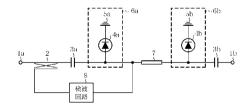

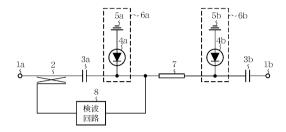

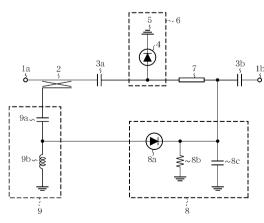

実施の形態1.

図1はこの発明の実施の形態1によるリミッタ回路を示す回路図であり、図において、結合回路2は、入力端子1 aに接続され、入力端子1 aからの高周波信号を分岐するものである。入力側キャパシタ3 aは、結合回路2の通過端子に一端が直列接続され、高周波信号における直流成分を阻止するものである。PINダイオード回路6 aは、PINダイオード4 aのアノードが入力側キャパシタ3 aの他端に並列接続されると共にカソードがグランド5 aに接続されたものである。高周波信号線路7は、線路長が使用周波数における1/4 ( : 波長)に設定され、一端が入力側キャパシタ3 aの他端に直列接続されたものである。PINダイオード回路6 bは、PINダイオード4 bのアノードが高周波信号線路7の他端に並列接続されると共にカソードがグランド5 bに接続されたものであ

20

30

40

50

る。出力側キャパシタ3 b は、一端が高周波信号線路7の他端に直列接続されると共に他端が出力端子1 b に直列接続され、高周波信号における直流成分を阻止するものである。 検波回路8 は、結合回路2の結合端子に接続されると共に入力側キャパシタ3 a と高周波信号線路7 との間に接続され、結合回路2 から入力される高周波信号の信号レベルに応じた正の直流バイアスをそれら入力側キャパシタ3 a と高周波信号線路7 との間に供給するものである。

# [0009]

次に動作について説明する。

入力端子1aから入力される高周波信号は、結合回路2によって分岐されると共に、結合回路2を通過した高周波信号は、入力側キャパシタ3aにより直流成分が阻止され、高周波信号線路7および出力側キャパシタ3bを通じて出力端子1bから出力される。この時、検波回路8は、結合回路2によって分岐された高周波信号の信号レベルに応じた正の直流バイアスを入力側キャパシタ3aと高周波信号線路7との間に供給する。

## [0010]

入力端子1aから入力される高周波信号の信号レベルが十分低い場合は、検波回路8から正の直流バイアスが供給されること無く、PINダイオード4a,4bを等価的にオープンと見なすことができるため、PINダイオード回路6a,6bを等価的にスルーと見なすことができ、入力端子1aから入力される高周波信号の大部分は出力端子1bに出力される。

### [0011]

入力端子1aから入力される高周波信号の信号レベルが十分高い場合は、入力端子1aから入力される高周波信号の一部が結合回路2を介して検波回路8に入力され、検波回路8において入力された高周波信号は正の直流バイアスに変換される。その結果、その直流バイアスによってPINダイオード4a,4bにバイアス電流が流れ、PINダイオード4a,4bを等価的にショートと見なすことができるため、PINダイオード回路6a,6bを等価的にショートと見なすことができ、入力端子1aから入力される高周波信号の大部分はPINダイオード回路6a,6bのグランド5a,5bで反射され、出力端子1bから出力されることなく入力端子1aに戻される。

このようにして、不要な高周波を低減するリミッタ回路としての機能を満たすと共に、一組の結合回路 2 および検波回路 8 によって 2 つの P I N ダイオード回路 6 a , 6 b に直流バイアスを供給することができる。

# [0012]

図 2 はこの発明の実施の形態 1 による他のリミッタ回路を示す回路図であり、図において、高周波信号線路 7 b は、線路長が使用周波数における 1 / 4 に設定され、一端が高周波信号線路 7 a の他端に直列接続されたものである。 P I N ダイオード回路 6 c は、 P I N ダイオード 4 c のアノードが高周波信号線路 7 b の他端に並列接続されると共にカソードがグランド 5 c に接続されたものである。その他の構成については図 1 と同様である

このように、図1では一組の結合回路2および検波回路8によって2つのPINダイオード回路6a,6bに直流バイアスを供給するようにしたが、一組の結合回路2および検波回路8によって3つのPINダイオード回路6a~6c、さらには4つ以上のPINダイオード回路に直流バイアスを供給するようにしても良く、さらに、部品点数を削減でき、小型化、低価格化、低リーケージ化(高遮断性能化)および低損失化を実現することができる。

なお、この実施の形態 1 では、検波回路 8 から直流バイアスを入力側キャパシタ 3 a と 高周波信号線路 7 との間に供給するようにしたが、入力側キャパシタ 3 a と出力側キャパ シタ 3 b との間であればいずれの個所であっても良い。

#### [0013]

この実施の形態 1 によれば、一組の結合回路 2 および検波回路 8 によって複数の P I N ダイオード回路 6 a , 6 b に直流バイアスを供給するようにしたので、部品点数を削減で

き、小型化、低価格化、低リーケージ化および低損失化を実現することができる。

また、隣り合うPINダイオード回路6a,6b間に高周波信号線路7を備えたので、高周波信号線路7の作用により、さらに、低リーケージ化を実現することができ、さらに、高周波信号線路7の線路長を使用周波数における1/4 に設定したことにより、1/4 の高周波信号線路7の作用により、さらに、低リーケージ化を実現することができる

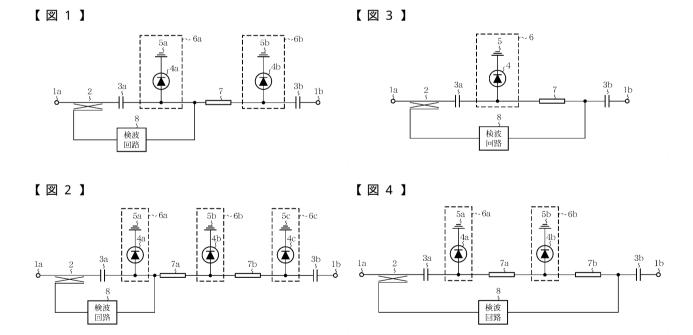

## [0014]

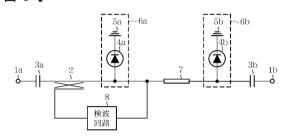

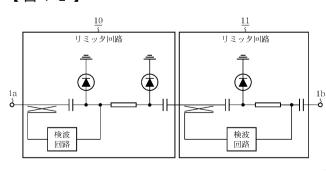

実施の形態2.

図3はこの発明の実施の形態2によるリミッタ回路を示す回路図であり、図において、検波回路8は、結合回路2の結合端子に接続されると共に高周波信号線路7と出力側キャパシタ3bとの間に接続され、結合回路2から入力される高周波信号の信号レベルに応じた正の直流バイアスをそれら高周波信号線路7と出力側キャパシタ3bとの間に供給するものである。その他の構成については図1と同様である。

# [ 0 0 1 5 ]

次に動作について説明する。

入力端子1aから入力される高周波信号の信号レベルが十分低い場合は、検波回路8から正の直流バイアスが供給されること無く、PINダイオード4を等価的にオープンと見なすことができるため、PINダイオード回路6を等価的にスルーと見なすことができ、入力端子1aから入力される高周波信号の大部分は出力端子1bに出力される。

### [0016]

入力端子1aから入力される高周波信号の信号レベルが十分高い場合は、入力端子1aから入力される高周波信号の一部が結合回路2を介して検波回路8に入力され、検波回路8において入力された高周波信号は正の直流バイアスに変換される。その結果、その直流バイアスによってPINダイオード4にバイアス電流が流れ、PINダイオード4を等価的にショートと見なすことができるため、PINダイオード回路6を等価的にショートと見なすことができ、入力端子1aから入力される高周波信号の大部分はPINダイオード回路6のグランド5で反射され、出力端子1bから出力されることなく入力端子1aに戻される。

このようにして、不要な高周波を低減するリミッタ回路としての機能を満たすことができる。

### [0017]

また、図3に示した構成では、検波回路8からの直流バイアスを高周波信号線路7と出力側キャパシタ3bとの間に供給するようにしている。入力端子1aに信号レベルの高い高周波信号が入力された時、その高周波信号は、PINダイオード回路6で減衰され、さらに、高周波信号線路7で減衰された後に迂回して検波回路8に印加される。したがって、この高周波信号線路7によって、検波回路8に迂回して印加される高周波信号の信号レベルを低く抑えることができ、検波回路8の耐電力性を高めるために新たに保護回路等を設けることなく、その結果、部品点数を削減でき、小型化、低価格化、低リーケージ化および低損失化を実現することができる。

### [0018]

図4はこの発明の実施の形態2による他のリミッタ回路を示す回路図であり、図において、検波回路8は、結合回路2の結合端子に接続されると共に高周波信号線路7bと出力側キャパシタ3bとの間に接続され、結合回路2から入力される高周波信号の信号レベルに応じた正の直流バイアスをそれら高周波信号線路7bと出力側キャパシタ3bとの間に供給するものである。その他の構成についてはPINダイオード回路6cを除いた以外は図2と同様である。

このように、図3では一組の結合回路2および検波回路8によって1つのPINダイオード回路6に直流バイアスを供給するようにしたが、一組の結合回路2および検波回路8によって2つのPINダイオード回路6a,6b、さらには3つ以上のPINダイオード回路に直流バイアスを供給するようにしても良く、この場合、検波回路8に迂回して印加

20

30

40

される高周波信号の信号レベルをさらに低く抑えることができることから、さらに、部品 点数を削減でき、小型化、低価格化、低リーケージ化および低損失化を実現することがで きる。

# [0019]

この実施の形態 2 によれば、検波回路 8 からの直流バイアスを高周波信号線路 7 と出力側キャパシタ 3 b との間に供給するようにしたので、検波回路 8 に迂回して印加される高周波信号の信号レベルを低く抑えることができ、検波回路 8 の耐電力性を高めるために新たに保護回路等を設けることなく、その結果、部品点数を削減でき、小型化、低価格化、低リーケージ化および低損失化を実現することができる。

また、隣り合うPINダイオード回路6a,6b間に高周波信号線路7aを備えたので、高周波信号線路7aの作用により、さらに、低リーケージ化を実現することができ、さらに、高周波信号線路7aの線路長を使用周波数における1/4 に設定したことにより、1/4 の高周波信号線路7aの作用により、さらに、低リーケージ化を実現することができる。

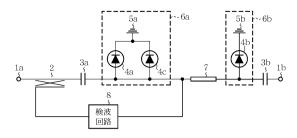

#### [0020]

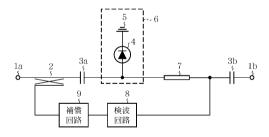

実施の形態3.

図5はこの発明の実施の形態3によるリミッタ回路を示す回路図であり、図において、PINダイオード回路6 a は、アノード同士が入力側キャパシタ3 a の他端に並列接続されると共にカソード同士がグランド5 a に接続された2 つの PINダイオード4 a , 4 c の並列接続からなるようにしたものである。その他の構成については図1と同様である。【0021】

この実施の形態 3 によれば、 1 つの P I N ダイオード回路 6 a を、 2 つの P I N ダイオード 4 a , 4 c の並列接続からなるようにしたので、 2 つの P I N ダイオード 4 a , 4 c の作用により、さらに、低リーケージ化を実現することができる。

なお、PINダイオード回路6aを構成する回路は、3つ以上のPINダイオードの並列接続からなるようにしても良く、さらに、PINダイオード回路6aを構成する回路についても、複数のPINダイオードの並列接続からなるようにしても良く、さらに、低リーケージ化を実現することができる。

また、図 5 では上記実施の形態 1 に示した構成に、複数の P I N ダイオードの並列接続からなる回路を適用したものについて示したが、上記実施の形態 2 に示した構成に適用しても良く、両実施の形態の効果を奏することができる。

# [0022]

実施の形態4.

図 6 はこの発明の実施の形態 4 によるリミッタ回路を示す回路図であり、図において、PINダイオード回路 6 a は、PINダイオード 4 a のカソードが入力側キャパシタ 3 a の他端に並列接続されると共にアノードがグランド 5 a に接続されたものである。PINダイオード回路 6 b は、PINダイオード 4 b のカソードが高周波信号線路 7 の他端に並列接続されると共にアノードがグランド 5 b に接続されたものである。検波回路 8 は、結合回路 2 の結合端子に接続されると共に入力側キャパシタ 3 a と高周波信号線路 7 との間に接続され、結合回路 2 から入力される高周波信号の信号レベルに応じた負の直流バイアスをそれら入力側キャパシタ 3 a と高周波信号線路 7 との間に供給するものである。その他の構成については図 1 と同様である。

## [0023]

次に動作について説明する。

入力端子1aから入力される高周波信号は、結合回路2によって分岐されると共に、結合回路2を通過した高周波信号は、入力側キャパシタ3aにより直流成分が阻止され、高周波信号線路7および出力側キャパシタ3bを通じて出力端子1bから出力される。この時、検波回路8は、結合回路2によって分岐された高周波信号の信号レベルに応じた負の直流バイアスを入力側キャパシタ3aと高周波信号線路7との間に供給する。

## [0024]

50

20

30

30

50

(8)

入力端子1aから入力される高周波信号の信号レベルが十分低い場合は、検波回路8から負の直流バイアスが供給されること無く、PINダイオード4a,4bを等価的にオープンと見なすことができるため、PINダイオード回路6a,6bを等価的にスルーと見なすことができ、入力端子1aから入力される高周波信号の大部分は出力端子1bに出力される。

#### [0025]

入力端子1aから入力される高周波信号の信号レベルが十分高い場合は、入力端子1aから入力される高周波信号の一部が結合回路2を介して検波回路8に入力され、検波回路8において入力された高周波信号は負の直流バイアスに変換される。その結果、その直流バイアスによってPINダイオード4a,4bにバイアス電流が流れ、PINダイオード4a,4bを等価的にショートと見なすことができるため、PINダイオード回路6a,6bを等価的にショートと見なすことができ、入力端子1aから入力される高周波信号の大部分はPINダイオード回路6a,6bのグランド5a,5bで反射され、出力端子1bから出力されることなく入力端子1aに戻される。

このようにして、不要な高周波を低減するリミッタ回路としての機能を満たすと共に、一組の結合回路 2 および検波回路 8 によって 2 つの P I N ダイオード回路 6 a , 6 b に直流バイアスを供給することができる。

#### [0026]

この実施の形態 4 によれば、 P I N ダイオード 4 a , 4 b の極性が逆になるように接続しても、検波回路 8 の直流バイアス供給の特性を負特性にすれば、上記実施の形態 1 と同様な機能を有することができる。

なお、図6では上記実施の形態1に示した構成に、PINダイオード4a,4bの極性が逆になるように接続した回路を適用したものについて示したが、上記実施の形態2に示した構成に適用しても良く、両実施の形態の効果を奏することができる。

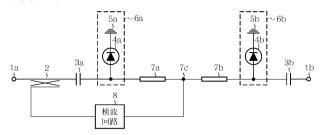

## [0027]

実施の形態5.

図7はこの発明の実施の形態5によるリミッタ回路を示す回路図であり、図において、高周波信号線路7a,7bは、線路長が使用周波数における1/4 に設定された高周波信号線路7を2つに分割したものであり、それら2つの高周波信号線路7a,7bは接続点7cにおいて直列に接続したものである。検波回路8は、結合回路2の結合端子に接続されると共に接続点7cに接続され、結合回路2から入力される高周波信号の信号レベルに応じた正の直流バイアスをその接続点7cに供給するものである。その他の構成については図1と同様である。

# [0028]

この実施の形態 5 によれば、検波回路 8 からの直流バイアスを 2 つの高周波信号線路 7 a , 7 b の接続点 7 c に供給するようにしたので、上記実施の形態 2 と同様に、分割された高周波信号線路 7 a の作用によって、検波回路 8 に迂回して印加される高周波信号の信号レベルを低く抑えることができ、検波回路 8 の耐電力性を高めるために新たに保護回路等を設けることなく、その結果、部品点数を削減でき、小型化、低価格化、低リーケージ化および低損失化を実現することができる。また、上記実施の形態 3 と同様に、高周波信号線路 7 a , 7 b の作用により、さらに、低リーケージ化を実現することができる。

なお、この実施の形態 5 では、高周波信号線路 7 を 2 つに分割したが、 3 つ以上に分割して、直流バイアスをそれらの接続点のうちのいずれかの接続点に供給するようにしても良く、同様な効果を奏することができる。

また、図7では上記実施の形態1に示した構成に、高周波信号線路7を複数に分割した回路を適用したものについて示したが、上記実施の形態2に示した構成に適用しても良く、両実施の形態の効果を奏することができる。

# [0029]

実施の形態6.

図8はこの発明の実施の形態6によるリミッタ回路を示す回路図であり、図において、

入力側キャパシタ3aは、入力端子1aに一端が直列接続され、結合回路2は、入力側キャパシタ3aの他端に接続されたものである。その他の構成については図1と同様である

## [0030]

この実施の形態6によれば、入力端子1 a に接続される結合回路2 と入力側キャパシタ3 a との順序を逆にしても良く、上記実施の形態1 と同様な機能を有することができる。なお、図8では上記実施の形態1に示した構成に、入力端子1 a に接続される結合回路2 と入力側キャパシタ3 a との順序を逆にした回路を適用したものについて示したが、上記実施の形態2に示した構成に適用しても良い。

#### [ 0 0 3 1 ]

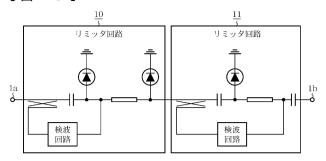

実施の形態7.

図9はこの発明の実施の形態7によるリミッタ回路を示す回路図であり、図において、補償回路9は、結合回路2の結合端子と検波回路8との間に接続され、結合回路2の高周波結合特性を補償するものである。その他の構成については図3と同様である。

図10はこの発明の実施の形態7によるリミッタ回路の詳細を示す回路図であり、図において、結合回路2は、使用周波数における1/4 よりも短い結合線路を有するものである。補償回路9は、一端が結合回路2の結合端子に直列接続された直列キャパシタ9aと、一端がその直列キャパシタ9aの他端に接続され、他端がグランドに接続された直列キャパシタ9aと直列インダクタ9bとの接続点に接続された検波ダイオード8aと、一端が検波ダイオード8aのカソードに接続され、他端がグランドに接続された並列抵抗8bと、一端が検波ダイオード8aのカソードに接続され、他端がグランドに接続された並列キャパシタ8cとからなるものである。なお、検波ダイオード8aのカソードは、高周波信号線路7と出力キャパシタ3bとの間に接続されるものである。

## [ 0 0 3 2 ]

次に動作について説明する。

小信号入力時の損失を低減するために、結合回路2を小型にすることが考えられる。この時、結合回路2の結合線路として使用周波数における1/4 よりも短い、例えば、1/20 のものを用いる場合を考える。

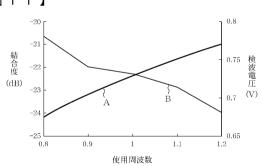

図11はこの発明の実施の形態7によるリミッタ回路における結合回路の高周波結合特性と、補償回路を備えた検波回路の高周波検波電圧特性とを示す特性図である。図において、横軸は、使用周波数における所望周波数を(1.0)とした時の相対的な周波数で示したものであり、高周波結合特性Aは、結合回路2の結合線路として使用周波数における1/20 のものを用いた場合の使用周波数(0.8~1.2)に応じたその結合回路2の結合度(dB)を示し、高周波検波電圧特性Bは、使用周波数に応じた補償回路9を備えた検波回路8の検波電圧(V)を示すものである。

#### [ 0 0 3 3 ]

図11に示したように、結合回路2の結合線路として使用周波数における1/20 の ものを用いた場合では、高周波結合特性Aは、平坦でなくなり、右肩上がりの特性となる

一方、補償回路9は、使用周波数帯における所望周波数(1.0)よりも低い周波数で整合を取ることにより、所望周波数よりも低い周波数で反射が小さく、所望周波数よりも高い周波数で反射が大きくなり、使用周波数帯で高周波信号の通過レベルが周波数が高くなるにつれて減少する特性を有するように設定されたものであり、補償回路9を備えた検波回路8の高周波検波電圧特性Bは、高周波結合特性Aとは逆の右肩下がりの特性となる

## [0034]

図11に示した高周波結合特性 A の傾きを高周波検波電圧特性 B の傾きによって相殺されるように、図10に示した補償回路 9 の直列キャパシタ 9 a および直列インダクタ 9 b として最適値を選定するようにすれば、結合回路 2 の小型化のために高周波結合特性 A に

10

20

30

傾きが生じても、次段の補償回路9および検波回路8の高周波検波電圧特性Bの傾きによってその高周波結合特性Aを補償することができる。

その結果、入力側キャパシタ3aと出力側キャパシタ3bとの間に供給される直流バイアスを、平坦な周波数特性とすることができる。なお、検波回路8において、検波ダイオード8aは、入力される高周波信号を整流し、並列抵抗8bおよび並列キャパシタ8cは、その整流された高周波信号の入力レベルに応じたバイアス電圧を充電し、高周波信号線路7と出力キャパシタ3bとの間に供給するものである。

なお、この実施の形態 7 では、図 3 に示した構成に、補償回路 9 を適用したものについて示したが、図 1 から図 8 に示したいずれの構成に補償回路 9 を適用しても良く、両実施の形態の効果を奏することができる。

[0035]

この実施の形態 7 によれば、結合回路 2 の分岐側と検波回路 8 との間に結合回路 2 の高周波結合特性 A を補償する補償回路 9 を備えたので、小信号入力時の損失を低減するために、結合回路 2 を小型にした時に、結合回路 2 の高周波結合特性 A が平坦でなくなるが、補償回路 9 によりこれを補償することによって、大信号入力時のリーケージ特性を平坦化することができ、その結果、低損失で且つ低リーケージ化を実現することができる。

[0036]

実施の形態8.

図12はこの発明の実施の形態8によるリミッタ回路を示す回路図であり、図において、リミッタ回路10は、図1に示したものであり、リミッタ回路11は、図3に示したものであり、2つのリミッタ回路10,11を直列接続したものである。

[0037]

次に動作について説明する。

図12に示したリミッタ回路は、2つのリミッタ回路10,11を直列接続したものである。すなわち、リミッタ回路10の出力端子1bとリミッタ回路11の入力端子1aとを直列接続したものである。

入力端子1aより高周波信号が入力されれば、リミッタ回路10で不要な高周波を低減すると共に、リミッタ回路11で不要な高周波を低減することができ、低リーケージ化を 実現することができる。

図13はこの発明の実施の形態8による他のリミッタ回路を示す回路図であり、図に示すように、リミッタ回路10の出力側キャパシタ3bを省略しても良く、この場合、さらに部品点数を削減することができる。

なお、図12および図13では、図1および図3に示した2つのリミッタ回路10,11を直列接続したものについて示したが、対象とするリミッタ回路は、図1~図10に示した同一または異なるいずれのものであっても良く、また、直列接続されるリミッタ回路の数も3つ以上であっても良く、さらに、低リーケージ化を実現することができる。

[ 0 0 3 8 ]

この実施の形態 8 によれば、同一または異なる複数のリミッタ回路を直列接続するようにしたので、複数の直列接続されたリミッタ回路の作用により、さらに、低リーケージ化を実現することができる。

[ 0 0 3 9 ]

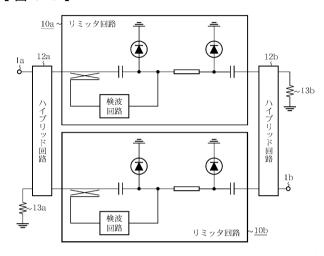

実施の形態9.

図14はこの発明の実施の形態9によるリミッタ回路を示す回路図であり、図において、ハイブリッド回路(第1のハイブリッド回路)12 a は、入力端子1 a に接続され、その入力端子1 a からの高周波信号を分岐するものである。リミッタ回路(第1のリミッタ回路)10 a は、ハイブリッド回路12 a の通過端子に入力側が接続された図1に示したものであり、リミッタ回路(第2のリミッタ回路)10 b は、ハイブリッド回路12 a の結合端子に入力側が接続され、リミッタ回路10 a と共に並列に接続された図1に示したものである。終端抵抗(第1の終端抵抗)13 a は、ハイブリッド回路12 a の遮断端子に接続され、リミッタ回路10 a 、10 b 内で反射された高周波信号を消去するものであ

10

20

30

40

20

30

40

50

る。ハイブリッド回路(第2のハイブリッド回路)12 bは、リミッタ回路10 aの出力側に結合端子が接続されると共にリミッタ回路10 bの出力側に通過端子が接続され、リミッタ回路10 a、10 bの出力を結合すると共に出力端子1 bから出力するものである。終端抵抗(第2の終端抵抗)13 bは、ハイブリッド回路12 bの遮断端子に接続され、リミッタ回路10 a、10 b内で反射された高周波信号を消去するものである。

[0040]

次に動作について説明する。

図 1 4 に示したリミッタ回路は、 2 つのリミッタ回路 1 0 a , 1 0 b を並列接続したものである。

入力端子1aより高周波信号が入力されれば、ハイブリッド回路12aにより分岐され、2つのリミッタ回路10a,10bで不要な高周波を低減することができ、低リーケージ化を実現することができる。

また、この時、ハイブリッド回路12a,12bに接続された終端抵抗13a,13bは、リミッタ回路10a,10b内で反射された高周波信号を確実に消去し、反射された高周波信号が入力端子1a側に戻ることなく、低反射のリミッタ回路が構成できる。

なお、図14では、図1に示した2つのリミッタ回路10a,10bを並列接続したものについて示したが、対象とするリミッタ回路は、図1~図10に示した同一または異なるいずれのものであっても良い。

[0041]

この実施の形態 9 によれば、同一または異なる 2 つのリミッタ回路 1 0 a , 1 0 b を並列接続するようにしたので、 2 つの並列接続されたリミッタ回路 1 0 a , 1 0 b の作用により、さらに、低リーケージ化を実現することができる。

また、終端抵抗13a,13bは、リミッタ回路10a,10b内で反射された高周波信号を確実に消去し、反射された高周波信号が入力端子1a側に戻ることなく、低反射のリミッタ回路が構成できる。

【図面の簡単な説明】

[0042]

- 【図1】この発明の実施の形態1によるリミッタ回路を示す回路図である。

- 【図2】この発明の実施の形態1による他のリミッタ回路を示す回路図である。

- 【図3】この発明の実施の形態2によるリミッタ回路を示す回路図である。

- 【図4】この発明の実施の形態2による他のリミッタ回路を示す回路図である。

- 【図5】この発明の実施の形態3によるリミッタ回路を示す回路図である。

- 【図6】この発明の実施の形態4によるリミッタ回路を示す回路図である。

- 【図7】この発明の実施の形態5によるリミッタ回路を示す回路図である。

- 【図8】この発明の実施の形態6によるリミッタ回路を示す回路図である。

- 【図9】この発明の実施の形態7によるリミッタ回路を示す回路図である。

- 【図10】この発明の実施の形態7によるリミッタ回路の詳細を示す回路図である。

- 【図11】この発明の実施の形態7によるリミッタ回路における結合回路の高周波結合特性と、補償回路を備えた検波回路の高周波検波電圧特性とを示す特性図である。

- 【図12】この発明の実施の形態8によるリミッタ回路を示す回路図である。

- 【図13】この発明の実施の形態8による他のリミッタ回路を示す回路図である。

- 【 図 1 4 】この発明の実施の形態 9 によるリミッタ回路を示す回路図である。

【符号の説明】

[ 0 0 4 3 ]

1 a , 1 b 入力端子、2 結合回路、3 a 入力側キャパシタ、3 b 出力側キャパシタ、4 , 4 a , 4 b , 4 c PINダイオード、5 , 5 a , 5 b , 5 c グランド、6 , 6 a , 6 b , 6 c PINダイオード回路、7 , 7 a , 7 b 高周波信号線路、7 c 接続点、8 検波回路、8 a 検波ダイオード、8 b 並列抵抗、8 c 並列キャパシタ、9 補償回路、9 a 直列キャパシタ、9 b 直列インダクタ、1 0 , 1 1 リミッタ回路、1 0 a リミッタ回路(第 1 のリミッタ回路)、1 0 b リミッタ回路(第 2 のリ

ミッタ回路)、12a ハイブリッド回路(第1のハイブリッド回路)、12b ハイブリッド回路(第2のハイブリッド回路)、13a 終端抵抗(第1の終端抵抗)、13b 終端抵抗(第2の終端抵抗)。

# 【図5】

# 【図7】

# 【図6】

# 【図8】

# 【図9】

【図11】

# 【図10】

【図12】

# 【図13】

# 【図14】

# フロントページの続き

(72) 発明者 西野 有

東京都千代田区丸の内二丁目2番3号 三菱電機株式会社内

(72)発明者 宮口 賢一

東京都千代田区丸の内二丁目2番3号 三菱電機株式会社内

(72)発明者 湯之上 則弘

東京都千代田区丸の内二丁目2番3号 三菱電機株式会社内

(72)発明者 山室 守広

東京都千代田区丸の内二丁目2番3号 三菱電機株式会社内

(72)発明者 宮 ざき 守 やす

東京都千代田区丸の内二丁目2番3号 三菱電機株式会社内

Fターム(参考) 5J030 CB04 CB08 CC05 CC09