# (19) 대한민국특허청(KR) (12) 공개특허공보(A)

(51) Int. CI.<sup>6</sup> G11C 16/06 (11) 공개번호 특1996-0025792

(43) 공개일자 1996년07월20일

| (21) 출원번호  | 특 1995-0072142                                           |

|------------|----------------------------------------------------------|

| (22) 출원일자  | 1995년 12월22일                                             |

| (30) 우선권주장 | 362,688 1994년12월22일 미국(US)                               |

| (71) 출원인   | 에이티 앤드 티 코포레이션 - 데이빗 엘. 스미스                              |

| (72) 발명자   | 미합중국, 뉴욕 10013-2412, 뉴욕, 애비뉴 오드 디 아메리카즈 32<br>아론 루이스 피셔  |

| (74) 대리인   | 미합중국, 펜실베니아 18104, 레하이 카운티, 알렌타운, 캐롤 레인 2764<br>이병호, 최달용 |

심사청구 : 없음

### (54) 감지 증폭기를 구비하는 집적회로

#### 요약

본원은 감지 증폭기(예를 들어, 16)를 구비하는 집적 회로에 관한 것이다. 감지 증폭기(예를 들어, 16)는  $2^{^{n}}$  레벨의 출력 특성을 n 대응 비트의 패턴으로 엔코딩할 수 있다. 감지 증폭기(예를 들어,16)는 비제로 검출 회로 (예를들어,18)를 구비하여 출력 특성이 제로일 때를 검출한다.

감지 증폭기(예를 들어, 16)는 또한  $2^{n}$  -2비교기(예를 들어, 20)를 구비하여 출력 특성이 비제로일 때 출력투성을  $2^{n}$  -2기준 레벨과 비교한다,  $012^{n}$  -2기준 레벨 (예를 들어,  $I_{REF1},I_{REF2}$ )은 출력 특성의  $2^{n}$  가능한

레벨의  $2^{n}$  -2비제로 레벨로부터 구성된다, 엔코더(예를 들어,18)는 비제로 검출 회로 및 비교기에 결합된다. 엔코더 (예를 들어,18)는 비제로 검출 회로로부터의 출력 및 비교기(예를 들어,20)로부터의 출력을 대응하는 소정의 비트 패턴으로 엔코딩 하며, 출력 특성이 비제로 검출회로에 의해 제로라고 결정될 때, 비트 패턴 출력은 디폴트 비트 패턴이 된다, 출력 특성이 비제로일 때, 비트 패턴은 출력 특성이 어트 기준 레벨쌍(예를 들어, $l_{REF1}$ )간에 놓이는지 즉 출력 특성이 최대 기준 레벨(예를 들어, $l_{REF2}$ )보다 큰지최소 기준 레벨(예를 들어, $l_{REF1}$ )보다 작은지 여부에 의해 결정되는 소정값을 취한다.

# 叫丑도

### 도1

# 명세서

[발명의 명칭]

감지 증폭기를 구비하는 집적 회로

[도면의 간단한 설명]

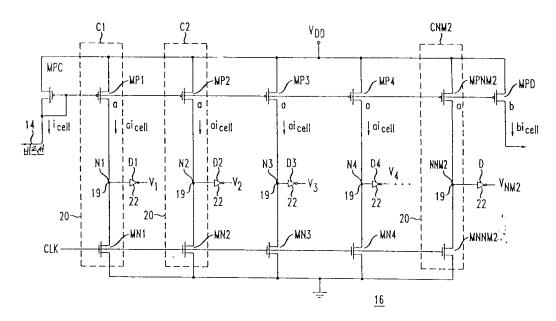

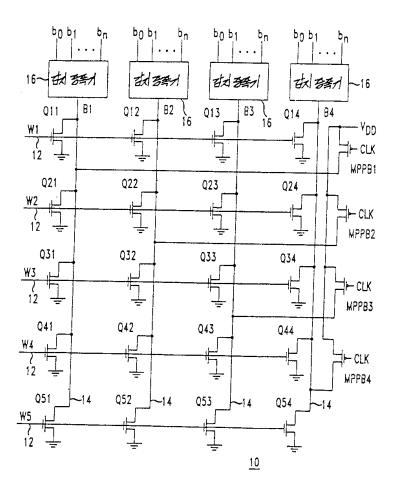

제1도는 워드선(수평으로 도시됨)상의 2진수 입력 및 비트선(수직으로 도시됨)상의 다수 레벨 출력을 도 시하는 판독-전용 메모리의 일부분을 도시하는 개요도, 제2도는 다수의 레벨 ROM에 사용하기 위한 감지 증폭기의 실시예를 도시한 개요도.

본 내용은 요부공개 건이므로 전문내용을 수록하지 않았음

### (57) 청구의 범위

# 청구항 1

2<sup>n</sup> 레벨의 출력 특성을 n대응 비트 패턴으로 엔코딩하며, 출력 특성을 소정 기준 레벨과 비교하는 비교기 및 이 출력 특성을 n 소정 비트 패턴들중 하나의 패턴으로 엔코딩하는 엔코더를 포함하는 감지 증폭기(예를 들어,16)를 구비하는 집적 회로에 있어서, 상기 감지 증폭기는 : 출력 특성이 제로일 때를 검출하고 출력을 제공하는 비제로 검출 회로와, 출력 특성이 비제로일 때 상기 출력 특성을 2<sup>n</sup>-2기준 레벨과 비교하는 출력을 제공하는 2<sup>n</sup>-2비교기(20)로서, 상기 2<sup>n</sup>-2기준레벨은 2<sup>n</sup> 레벨의 출력 특성의 2<sup>n</sup>-2비제로 레벨로부터 구성 되는 상기 2<sup>n</sup>-2 비교기와, 상기 비제로 검출 회로 및 상기 비교기에 결합되어 상기 비제로 검출 회로로부터의 출력 및 상기 비교기로부터의 출력을 n 비트 패턴들중 대응하는 1비트로 엔코딩하는 엔코더(18)로서, 상기 대응하는 비트 패턴은 상기 감지 증폭기로부터 출력을 제공하며, 상기 비트 패턴은 상기

출력 특성이 비제로 검출 회로에 제로하고 결정될 때 소정의 디폴트 비트 패턴이 되며, 상기 비트 패턴은 상기 출력 특성이 비제로일 때 상기 출력이 어느 기준 레벨의 쌍(예를 들어, $I_{REF1}$ , $I_{REF2}$ )에 놓이는지, 즉 상기 출력 특성이 최대 기준 레벨(예를 들어, $I_{REF2}$ )보다 큰지 또는 최소 기준 레벨(예를 들어, $I_{REF1}$ )보다 작은 지 여부에 의해 결정되는 소정값을 취하므로써  $2^n$ -2기준레벨(예를 들어, $I_{REF1}$ , $I_{REF2}$ )만을 출력 특성이  $2^n$  레벨을 엔코딩하는데 필요로 하는 상기 엔코더를 구비하는 것을 특징으로 하는 집적 회로.

#### 청구항 2

제1항에 있어서, 상기 출력 특성은 전류인 것을 특징으로 하는 집적 회로.

#### 청구항 3

제1항에 있어서, 상기 비교기(예를 들어,20) 각각은 제1트랜지스터(예를 들어, MP1내지 NPNM2)및 제2트랜지스터(예를 들어, MP1내지 NPNM2)로 이루어지는데, 상기 제1트랜지스터(예를 들어, MP1내지 NPNM2)각각은 상기 출력 특성을 복사하는 트랜지스터(예를 들어,MPC)로 전류 미러 동작시에 각 비교기(예를 들어,20)에서 상기 출력 특성을 복사하도록 하며,상기 제1트랜지스터(예를 들어, MP1내지 NPNM2)각각은 팩터에 의해 상기 출력 특성을 발생시키는 트랜지스터와 비례적으로 관계하는 크기가 되는 것을 특징으로하는 직접회로.

#### 청구항 4

정보를 저장하며, n비트 정보의 다수의 세트들중 한 세트를 표시하며, 상기 한 세트의 n비트에 대응하는 전기 특성을 출력으로서 제공하는 셀(예를 들어,Qij)을 갖는 판독-전용 메모리(예를 들어,10)와, 적어도 하나의 셀(예를 들어,Qij)에 결합되어 상기 적어도 하나의 셀로부터 상기 전기 특성을 수신하는 감지 증폭기(예를 들어,16) 및 상기 감지 증폭기(예를 들어,16)로부터 출력을 수신하도록 결합되는 엔코더(예를 들어,18)를 구비하는 직접회로에 있어서, 상기 감지 증폭기(예를 들어,16)는 비제로인 경우 상기 전기 특성을  $2^{n}$ -2기준 레벨과 비교하여 상기 전기 특성이 상기 2개의  $2^{n}$ -2기준 레벨들중 어느 레벨(예를 들어, $1_{REF2}$ )에 놓이는지, 즉 상기 전기 특성이 최대 기준 레벨(예를 들어, $1_{REF2}$ )보다 큰지 또는 최소 기준 레벨에 놓이는지, 즉 상기 전기 특성이 최대 기준 레벨(예를 들어, $1_{REF2}$ )보다 큰지 최소 기준 레벨예를 들어  $1_{REF1}$ )보다 작은지 여부를 결정하며, 상기 전기 특성이 상기 2개의  $2^{n}$ -2기준 레벨예를 들어  $1_{REF1}$ )보다 작은지 표시하고 상기 전기 특성이 제로인 경우 출력이 없다는 것을 표시하는 출력을 제공하고 상기 엔코더(예를 들어,18)는 상기 전기 특성이 제로인 경우 소정 세트의n비트를 발생시키는고

### 청구항 5

발생시키는 것을 특징으로 하는 집적회로.

제4항에 있어서, 상기 판독 전용 메모리(예를 들어,10)는 행 및 열의 셀을 포함하며, 상기 감지 증폭기 (예를 들어,16)에 결합되는 상기 적어도 하나의 셀(예를 들어,Qij)은 한 열의 셀인 것을 특징으로 한는 집적회로.

상기 전기 특성이 비제로일 때 상기 감지 증폭기(예를 들어,16)의 출력에 대응하는 소정 세트의 n 비트를

# 청구항 6

제4항에 있어서, 각 셀(예를 들어,Qij)에 의해 기억된 정보 비트수는n=2가 되도록 두개가 되어 상기 감지 증폭기(예를 들어,16)에서 두개의 기준 레벨을 발생시키는 것을 특징으로 하는 집적 회로.

#### 청구항 7

제 4항에 있어서, 각 셀로 부터의 전기 출력 특성은 전류인 것을 특징으로 하는 집적 회로.

#### 청구항 8

제7항에 있어서 각 셀(예를 들어,Qij)은 채널을 갖는 전계 효과 트랜지스터를 구비하며, 상기 채널의 단면적은 $2^{n}$ 기선택된 값들중 하나의 값으로부터 선택되어 상기 세트의 n비트에 대응하는 전기 출력을 제공하는 것을 특징으로 하는 직접 회로.

#### 청구항 9

제4항에 있어서, 각 셀로부터의 상기 전기 출력 특성은 전압인 것을 특징으로 하는 직접 회로.

## 청구항 10

제8항에 있어서, 각 셀(Qij)은 채널을 갖는 전계 효과 트랜시스터를 구비하며, 상기 채널은  $2^N$ 기 선택된도핑 레벨들중 하나의 레벨로 도핑되어 상기 한세트의 n 비트들에 대응하는 전기 출력을 제공하는 것을 특징으로 하는 직접 회로.

# 청구항 11

제4항에 있어서, 상기 판독-전용 메모리(예를 들어,10)는 소거 가능한 것을 특징으로 하는 집적 회로.

※ 참고사항 : 최초출원 내용에 의하여 공개하는 것임.

#### 도면

# 도면1

# 도면2