(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6134493号

(P6134493)

(45) 発行日 平成29年5月24日(2017.5.24)

(24) 登録日 平成29年4月28日(2017.4.28)

|                |           |        |       |         |

|----------------|-----------|--------|-------|---------|

| (51) Int.Cl.   | F 1       |        |       |         |

| HO 1 L 29/786  | (2006.01) | HO 1 L | 29/78 | 6 2 6 C |

| HO 1 L 21/336  | (2006.01) | HO 1 L | 29/78 | 6 1 8 B |

| HO 1 L 21/8242 | (2006.01) | HO 1 L | 29/78 | 6 2 7 F |

| HO 1 L 27/108  | (2006.01) | HO 1 L | 27/10 | 3 2 1   |

| HO 1 L 27/115  | (2017.01) | HO 1 L | 27/10 | 4 3 4   |

請求項の数 2 (全 41 頁) 最終頁に続く

|              |                               |           |                                                |

|--------------|-------------------------------|-----------|------------------------------------------------|

| (21) 出願番号    | 特願2012-231322 (P2012-231322)  | (73) 特許権者 | 000153878<br>株式会社半導体エネルギー研究所<br>神奈川県厚木市長谷398番地 |

| (22) 出願日     | 平成24年10月19日(2012.10.19)       | (72) 発明者  | 佐々木 俊成<br>神奈川県厚木市長谷398番地 株式会社<br>半導体エネルギー研究所内  |

| (65) 公開番号    | 特開2013-102158 (P2013-102158A) | (72) 発明者  | 野田 耕生<br>神奈川県厚木市長谷398番地 株式会社<br>半導体エネルギー研究所内   |

| (43) 公開日     | 平成25年5月23日(2013.5.23)         | (72) 発明者  | 佐藤 裕平<br>神奈川県厚木市長谷398番地 株式会社<br>半導体エネルギー研究所内   |

| 審査請求日        | 平成27年7月24日(2015.7.24)         | (72) 発明者  | 遠藤 佑太<br>神奈川県厚木市長谷398番地 株式会社<br>半導体エネルギー研究所内   |

| (31) 優先権主張番号 | 特願2011-231477 (P2011-231477)  |           |                                                |

| (32) 優先日     | 平成23年10月21日(2011.10.21)       |           |                                                |

| (33) 優先権主張国  | 日本国(JP)                       |           |                                                |

最終頁に続く

(54) 【発明の名称】半導体装置

## (57) 【特許請求の範囲】

## 【請求項 1】

複数のトランジスタを有し、

前記トランジスタは第1の絶縁膜と、

前記第1の絶縁膜と接する領域を有する、酸化物半導体膜と、

前記酸化物半導体膜と接する領域を有する、ゲート絶縁膜と、

前記ゲート絶縁膜を介して、前記酸化物半導体膜と重なる領域を有する、ゲート電極と、を有し、

前記第1の絶縁膜は、酸化アルミニウム又は酸化シリコンを有し、

前記第1の絶縁膜において、電子スピン共鳴にて測定される、g値の信号が、2.00 10

5以上2.015以下に表れ、

前記酸化物半導体膜は、比抵抗率が3k·cm以上の範囲内にあり、

前記酸化物半導体膜は、前記複数のトランジスタ間を電気的に分離するために島状に加工されていないことを特徴とする半導体装置。

## 【請求項 2】

複数のトランジスタを有し、

前記トランジスタは第1の絶縁膜と、

前記第1の絶縁膜と接する領域を有する、酸化物半導体膜と、

前記酸化物半導体膜と接する領域を有する、ゲート絶縁膜と、

前記ゲート絶縁膜を介して、前記酸化物半導体膜と重なる領域を有する、ゲート電極と

20

20

、を有し、

前記第1の絶縁膜は、酸化アルミニウム又は酸化シリコンを有し、

前記第1の絶縁膜において、電子スピン共鳴にて測定される、g値の信号が、2.005以上2.015以下に表れ、

前記酸化物半導体膜において、電子スピン共鳴にて測定される、g値の信号が、1.88以上1.98以下に表れず、

前記酸化物半導体膜は、比抵抗率が3k $\cdot$ cm以上の範囲内にあり、

前記酸化物半導体膜は、前記複数のトランジスタ間を電気的に分離するために島状に加工されていないことを特徴とする半導体装置。

【発明の詳細な説明】

10

【技術分野】

【0001】

半導体装置およびその作製方法に関する。

【0002】

なお、本明細書中において半導体装置とは、半導体特性を利用することで機能し得る装置全般をいい、電気光学装置、半導体回路および電子機器などは全て半導体装置である。

【背景技術】

【0003】

絶縁表面を有する基板上に形成された半導体膜を用いて、トランジスタを構成する技術が注目されている。該トランジスタは集積回路（IC）や画像表示装置（表示装置）のような半導体装置に広く応用されている。トランジスタに適用可能な半導体としてシリコン系半導体が知られているが、近年では酸化物半導体が注目されている。

20

【0004】

例えば、トランジスタのチャネル領域に、電子キャリア濃度が $10^{18}/\text{cm}^3$ 未満であるインジウム、ガリウムおよび亜鉛を含む非晶質酸化物膜を用いたトランジスタが開示されている（特許文献1参照。）。

【0005】

酸化物半導体膜を用いたトランジスタは、非晶質シリコンを用いたトランジスタよりも動作が速く、多結晶シリコンを用いたトランジスタよりも製造が容易であるものの、電気特性が変動しやすく信頼性が低いという問題点が知られている。具体的には、バイアス-熱ストレス試験（BT試験）後に、トランジスタのしきい値電圧の変動が生じてしまうことが挙げられる。

30

【先行技術文献】

【特許文献】

【0006】

【特許文献1】特開2006-165528号公報

【発明の概要】

【発明が解決しようとする課題】

【0007】

トランジスタの動作に起因する電気特性（しきい値電圧など）の変動は、トランジスタを有する半導体装置の信頼性を低下させる。

40

【0008】

酸化物半導体膜を用いたトランジスタにおいて、電気特性の変動の一因として、酸化物半導体膜中の水素に由来する不純物準位、および酸素欠損に由来する欠陥準位にキャリアが捕獲されることがある。

【0009】

なお、酸化物半導体膜に対し、450以上の中温で加熱処理を行うことにより水素濃度を大幅に低減することが可能であるが、同時に酸化物半導体膜の酸素欠損を増大させてしまう。

【0010】

50

そこで、酸化物半導体膜の水素濃度および酸素欠損を低減することを課題の一とする。

【0011】

また、酸化物半導体膜を用いたトランジスタを有する半導体装置の信頼性を向上させることを課題の一とする。

【課題を解決するための手段】

【0012】

酸化物半導体膜の酸素欠損の評価として、電子スピン共鳴 ( E S R : E l e c t r o n S p i n R e s o n a n c e ) を用いることができる。具体的には、酸化物半導体膜が酸素欠損を含む場合、 E S R にて  $g$  値が 1 . 9 3 で信号を表す。

【0013】

従って、水素濃度が低く、かつ E S R にて  $g$  値が 1 . 9 3 で信号を表さない場合、酸化物半導体膜において、水素に由来する不純物準位、および酸素欠損に由来する欠陥準位をほとんど有さないことになる。そのため、該酸化物半導体膜を用いたトランジスタは、トランジスタの動作に起因する電気特性の変動が小さくなる。

【0014】

同様に、下地絶縁膜が加熱処理により酸素を放出する膜の場合、 E S R にて  $g$  値が 2 . 0 1 で信号を表す。

【0015】

例えば、酸化物半導体膜の酸素欠損を、加熱処理することで下地絶縁膜から放出される酸素によって低減することが可能である。そのためには、下地絶縁膜として、 E S R にて  $g$  値が 2 . 0 1 で信号を表す膜を用いることが好ましい。

【0016】

なお、下地絶縁膜およびゲート絶縁膜で酸化物半導体膜を挟み、加熱処理を行うことで、下地絶縁膜から放出させた酸素を、効率よく酸化物半導体膜に供給することができる。また、該加熱処理を、 4 5 0 以上 7 0 0 以下の温度で行うと、酸化物半導体膜の水素濃度を低減することも可能となる。

【0017】

ただし、膜種や形成方法などによっては、加熱処理により、下地絶縁膜は、 E S R にて  $g$  値が 2 . 0 1 で信号を表さなくなってしまう。トランジスタの電気特性の変動を低減するという観点では、加熱処理後も下地絶縁膜は E S R にて  $g$  値が 2 . 0 1 で信号を表すことが好ましい。

【0018】

また、トランジスタの作製工程において酸化物半導体膜を加工した場合、酸化物半導体膜の形成されていない領域で、下地絶縁膜から放出する酸素が外方拡散してしまう。結果、加熱処理により、 E S R にて  $g$  値が 2 . 0 1 で信号を表さない下地絶縁膜になってしまふ。

【0019】

ここで、 E S R にて  $g$  値が 2 . 0 1 で信号を表す下地絶縁膜、および E S R にて  $g$  値が 1 . 9 3 で信号を表さず、かつ水素濃度の低い酸化物半導体膜を用いたトランジスタを複数有する半導体装置において、酸化物半導体膜はキャリア密度が極めて低く、ほとんど導電性を示さない。そのため、該半導体装置において、酸化物半導体膜を島状に加工しなくても異なるトランジスタ間に意図しない電流が流れることはない。

【0020】

即ち、半導体装置が複数のトランジスタを有する場合、従来においては、トランジスタ間を電気的に分離するために酸化物半導体膜を島状に加工することが一般的であった。ところが、本発明の一態様に係る半導体装置は、トランジスタ間を電気的に分離するために酸化物半導体膜を島状に加工しない。そのため、従来の半導体装置と比較し、下地絶縁膜から放出する酸素の外方拡散が起こりにくい。即ち、下地絶縁膜は、加熱処理後も E S R にて  $g$  値が 2 . 0 1 で信号を表しやすい。従って、本発明の一態様に係るトランジスタは、トランジスタの動作などに起因して生じる電気特性の変動を低減することができる。

10

20

30

40

50

**【0021】**

そこで、本発明の一態様は、下地絶縁膜と下地絶縁膜上に設けられた酸化物半導体膜と、酸化物半導体膜上に設けられたゲート絶縁膜と、ゲート絶縁膜を介して酸化物半導体膜に重畠して設けられたゲート電極と、を有し、下地絶縁膜は、ESRにてg値が2.01で信号を表し、酸化物半導体膜は、ESRにてg値が1.93で信号を表さない半導体装置である。

**【0022】**

また、第1の領域および第2の領域を有する下地絶縁膜を形成し、該下地絶縁膜上に酸化物半導体膜を成膜し、該酸化物半導体膜上にゲート絶縁膜を成膜した後に加熱処理を行うことで、導電性の異なる第3の領域および第4の領域を有する酸化物半導体膜を形成することができる。

10

**【0023】**

なお、酸化物半導体膜の第3の領域は下地絶縁膜の第1の領域と重なる領域に、酸化物半導体膜の第4の領域は下地絶縁膜の第2の領域と重なる領域に、それぞれ形成される。

**【0024】**

例えば、酸化物半導体膜を用いたトランジスタを複数有する半導体装置において、酸化物半導体膜の第3の領域を、ESRにてg値が1.93で信号を表さず、かつ水素濃度の低い領域とすることで、第3の領域は極めて高抵抗となり、酸化物半導体膜を島状に加工しなくても異なるトランジスタ間に意図しない電流が流れることはない。

**【0025】**

そこで、本発明の一態様に係る半導体装置は、第1の領域および第2の領域を有する下地絶縁膜と、下地絶縁膜上に設けられた第3の領域および第4の領域を有する酸化物半導体膜と、酸化物半導体膜上に設けられたゲート絶縁膜と、ゲート絶縁膜を介して酸化物半導体膜の第4の領域に重畠して設けられたゲート電極と、を有し、酸化物半導体膜の第3の領域は、下地絶縁膜の前記第1の領域と重なる領域であり、酸化物半導体膜の第4の領域は、下地絶縁膜の第2の領域と重なる領域であり、下地絶縁膜の第2の領域は、ESRにてg値が2.01で信号を表し、酸化物半導体膜の第3の領域は、ESRにてg値が1.93で信号を表さない半導体装置である。

20

**【0026】**

また、下地絶縁膜の第1の領域を、シリコンを含み、ESRにてg値が2.01で信号を表さない領域とすることで、該領域に作製したトランジスタのオン電流を向上させることができる。トランジスタのオン電流とは、トランジスタをオン状態としたときのソース領域 - ドレイン領域間を流れる電流（ドレイン電流ともいう。）をいう。また、トランジスタのオン状態とは、ゲート電極に、トランジスタのしきい値電圧以上の電位が印加された状態をいう。なお、本明細書において、しきい値電圧とは、トランジスタを「オン状態」にするために必要なゲート電圧をいう。そして、ゲート電圧とは、ソースの電位を基準としたときのゲートの電位との電位差をいう。

30

**【発明の効果】****【0027】**

高温で加熱処理を行うことで、酸化物半導体膜の水素濃度を低減することができる。また、下地絶縁膜から酸素が供給されることで、酸化物半導体膜の酸素欠損を低減することができる。

40

**【0028】**

水素による不純物準位および酸素欠損による欠陥準位が低減されることにより、酸化物半導体膜を用いたトランジスタを有する半導体装置の信頼性を向上させることができる。

**【図面の簡単な説明】****【0029】**

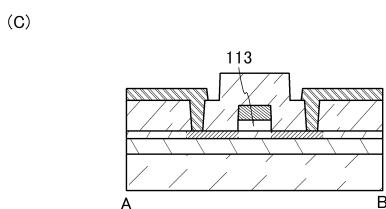

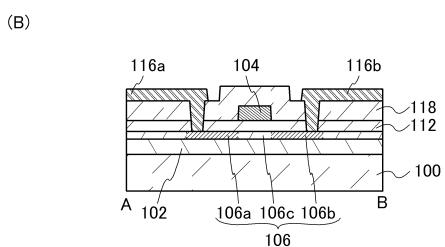

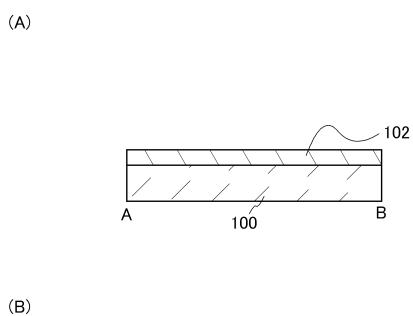

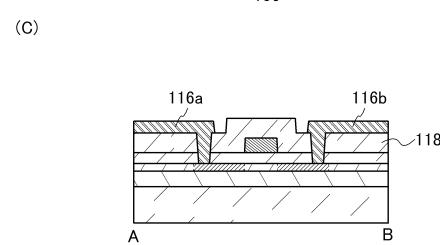

【図1】本発明の一態様に係るトランジスタの一例を示す上面図および断面図。

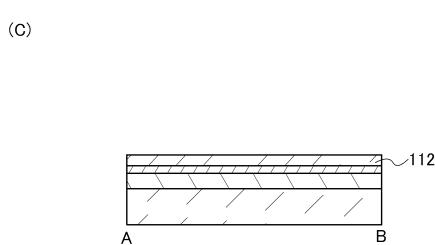

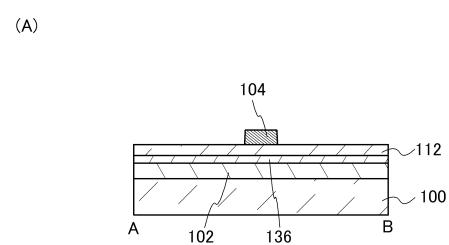

【図2】本発明の一態様に係るトランジスタの作製方法の一例を示す断面図。

【図3】本発明の一態様に係るトランジスタの作製方法の一例を示す断面図。

50

【図4】本発明の一態様に係るトランジスタの一例を示す上面図および断面図。

【図5】本発明の一態様に係るトランジスタの作製方法の一例を示す断面図。

【図6】本発明の一態様に係るトランジスタの作製方法の一例を示す断面図。

【図7】本発明の一態様に係るトランジスタの作製方法の一例を示す断面図。

【図8】本発明の一態様に係るトランジスタの作製方法の一例を示す断面図。

【図9】本発明の一態様に係るトランジスタの一例を示す上面図および断面図。

【図10】本発明の一態様に係るトランジスタの作製方法の一例を示す断面図。

【図11】本発明の一態様に係るトランジスタの一例を示す上面図および断面図。

【図12】本発明の一態様に係るトランジスタの作製方法の一例を示す断面図。

【図13】E S Rスペクトルを示した図。

10

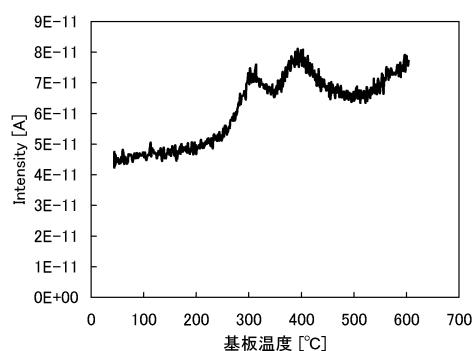

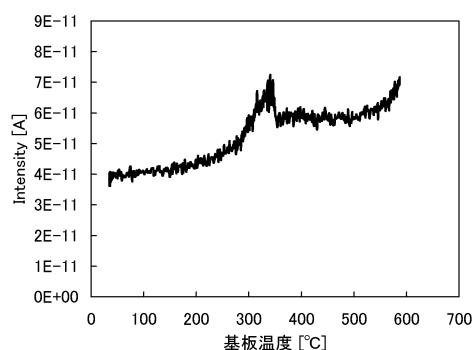

【図14】T D SによるM / zが32であるガスのイオン強度。

【図15】T D SによるM / zが2であるガスのイオン強度。

【図16】試料のホール効果測定結果を示す図。

【図17】試料のホール効果測定結果を示す図。

【図18】本発明の一態様に係る液晶表示装置の一例を示す回路図。

【図19】本発明の一態様に係る半導体記憶装置の一例を示す回路図および電気特性を示す図。

【図20】本発明の一態様に係る半導体記憶装置の一例を示す回路図および電気特性を示す図。

【図21】本発明の一態様に係るC P Uの具体例を示すブロック図およびその一部の回路図。

20

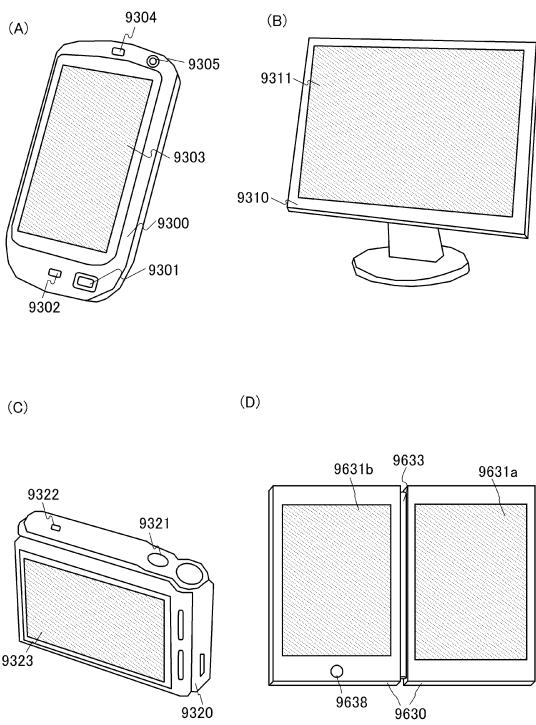

【図22】本発明の一態様に係る電子機器の一例を示す斜視図。

【発明を実施するための形態】

【0030】

本発明の実施の形態について、図面を用いて詳細に説明する。ただし、本発明は以下の説明に限定されず、その形態および詳細を様々に変更し得ることは、当業者であれば容易に理解される。また、本発明は以下に示す実施の形態の記載内容に限定して解釈されるものではない。なお、図面を用いて発明の構成を説明するにあたり、同じものを指す符号は異なる図面間でも共通して用いる。なお、同様のものを指す際にはハッチパターンを同じくし、特に符号を付さない場合がある。

30

【0031】

なお、第1、第2として付される序数詞は便宜上用いるものであり、工程順または積層順を示すものではない。また、本明細書において発明を特定するための事項として固有の名称を示すものではない。

【0032】

(実施の形態1)

本実施の形態では、本発明の一態様に係るトランジスタおよびその作製方法について図1乃至図3を用いて説明する。

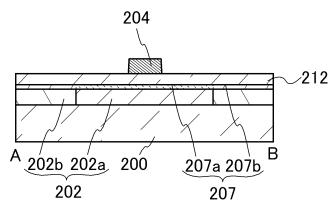

【0033】

図1(A)は本発明の一態様に係るトランジスタの上面図である。図1(A)に示す一点鎖線A - Bに対応する断面図を図1(B)に示す。なお、簡単のため、図1(A)においては、層間絶縁膜118、ゲート絶縁膜112などを省略して示す。

40

【0034】

図1(B)に示すトランジスタは、基板100上に設けられた下地絶縁膜102と、下地絶縁膜102上に設けられた第1の領域106a、第2の領域106bおよび第3の領域106cを有する酸化物半導体膜106と、酸化物半導体膜106上に設けられたゲート絶縁膜112と、ゲート絶縁膜112を介して酸化物半導体膜106の第3の領域106cの一部と重畳するゲート電極104と、を有する。

【0035】

なお、図1(A)において、酸化物半導体膜106の第1の領域106aの一側端および

50

第2の領域106bの一側端は、それぞれゲート電極104の長手方向に平行な側端部と重なる。即ち、図1(B)において、酸化物半導体膜106の第1の領域106aの一端および第2の領域106bの一端は、それぞれゲート電極104の下端部と重なる。

【0036】

なお、酸化物半導体膜106の第1の領域106aおよび第2の領域106bは、トランジスタのソース領域およびドレイン領域として機能する。また、酸化物半導体膜106の第3の領域106cのうち、ゲート電極104下にあり、かつ第1の領域106aおよび第2の領域106bに挟まれた領域はトランジスタのチャネル領域として機能する。

【0037】

また、酸化物半導体膜106の第3の領域106cのうち、チャネル領域以外の領域は、絶縁領域として機能する。そのため、酸化物半導体膜106が複数のトランジスタのチャネル領域として用いられる場合でも、トランジスタ間を電気的に分離することができる。

10

【0038】

なお、図1(B)に示すトランジスタは、ゲート電極104およびゲート絶縁膜112上に設けられた層間絶縁膜118と、層間絶縁膜118およびゲート絶縁膜112に設けられた、酸化物半導体膜106の第1の領域106aおよび第2の領域106bに達する開口部にて酸化物半導体膜106の第1の領域106aおよび第2の領域106bとそれぞれ接して設けられた配線116aおよび配線116bと、を有してもよい。

【0039】

また、配線116aおよび配線116bと同一層で設けられた配線と、ゲート電極104と、を接続してもよい。

20

【0040】

下地絶縁膜102は、ESRにてg値が2.01で信号を表す絶縁膜である。

【0041】

なお、ESRによる電子スピンの評価には、日本電子株式会社製電子スピン共鳴装置JES-F A 300や、ブルカー・バイオスピン株式会社製E 500 CW-EPRスペクトロメーターなどを用いればよい。

【0042】

なお、本明細書において、ESRにてg値が2.01で信号を表すという場合、ESRにてg値が2.01近傍(2.005以上2.015以下)に中心が位置する非対称性の信号を表すことを示す。該信号は、絶縁膜を構成する酸素原子のダングリングボンドを示す。ESRにてg値が2.01で信号を表すという場合、酸素原子のダングリングボンドが $5 \times 10^{17} \text{ spins/cm}^3$ 以上であることを示す。また、ESRにてg値が2.01で信号を表さないという場合、酸素原子のダングリングボンドが $5 \times 10^{17} \text{ spins/cm}^3$ 未満であることを示す。

30

【0043】

下地絶縁膜102としては、具体的には、マグネシウム、アルミニウム、バナジウム、クロム、ゲルマニウム、イットリウム、ランタン、ハフニウム、ジルコニウムおよびタンタルから選ばれた一種以上を含む酸化物膜を用い、単層または積層で用いればよい。

【0044】

40

下地絶縁膜102は、450以上700以下の温度における加熱処理により酸素を放出する絶縁膜を用いると好ましい。

【0045】

「加熱処理により酸素を放出する」とは、TDS分析にて、酸素原子に換算しての酸素の放出量が $1.0 \times 10^{18} \text{ atoms/cm}^3$ 以上、好ましくは $3.0 \times 10^{18} \text{ atoms/cm}^3$ 以上、さらに好ましくは $1.0 \times 10^{19} \text{ atoms/cm}^3$ 以上、さらに好ましくは $3.0 \times 10^{19} \text{ atoms/cm}^3$ 以上であることをいう。

【0046】

ここで、TDS分析を用いた酸素の放出量の測定方法について、以下に説明する。

【0047】

50

測定試料を TDS 分析したときの気体の全放出量は、放出ガスのイオン強度の積分値に比例する。そして標準試料との比較により、気体の全放出量を計算することができる。

【0048】

例えば、標準試料である所定の密度の水素を含むシリコンウェハの TDS 分析結果、および測定試料の TDS 分析結果から、測定試料の酸素分子の放出量 ( $N_{O_2}$ ) は、数式 (1) で求めることができる。ここで、TDS 分析で得られる質量電荷比 ( $M/z$ ) が 32 で検出されるガスの全てが酸素分子由来と仮定する。 $M/z$  が 32 であるガスとしてほかに  $CH_3OH$  があるが、存在する可能性が低いものとしてここでは考慮しない。また、酸素原子の同位体である質量数が 17 の酸素原子および質量数が 18 の酸素原子を含む酸素分子についても、自然界における存在比率が極微量であるため考慮しない。

10

【0049】

【数1】

$$N_{O_2} = \frac{N_{H_2}}{S_{H_2}} \times S_{O_2} \times \alpha \quad (1)$$

【0050】

$N_{H_2}$  は、標準試料から脱離した水素分子を密度で換算した値である。 $S_{H_2}$  は、標準試料を TDS 分析したときのイオン強度の積分値である。ここで、標準試料の基準値を、 $N_{H_2} / S_{H_2}$  とする。 $S_{O_2}$  は、測定試料を TDS 分析したときのイオン強度の積分値である。  $\alpha$  は、TDS 分析におけるイオン強度に影響する係数である。数式 (1) の詳細に関しては、特開平 6 - 275697 公報を参照する。なお、上記酸素の放出量は、電子科学株式会社製の昇温脱離分析装置 EMD-WA1000S/W を用い、標準試料として  $1 \times 10^{16} \text{ atoms/cm}^2$  の水素原子を含むシリコンウェハを用いて測定した。

20

【0051】

また、TDS 分析において、酸素の一部は酸素原子として検出される。酸素分子と酸素原子の比率は、酸素分子のイオン化率から算出することができる。なお、上述の  $\alpha$  は酸素分子のイオン化率を含むため、酸素分子の放出量を評価することで、酸素原子の放出量についても見積もることができる。

【0052】

30

なお、 $N_{O_2}$  は酸素分子の放出量である。酸素原子に換算したときの放出量は、酸素分子の放出量の 2 倍となる。

【0053】

下地絶縁膜 102 は十分な平坦性を有することが好ましい。具体的には、平均面粗さ ( $R_a$ ) が  $1 \text{ nm}$  以下、好ましくは  $0.3 \text{ nm}$  以下、さらに好ましくは  $0.1 \text{ nm}$  以下となるように下地となる膜を設ける。上述の数値以下の  $R_a$  とすることで、酸化物半導体膜 106 に結晶領域が形成されやすくなる。なお、 $R_a$  とは、JIS B 0601:2001 (ISO 4287:1997) で定義されている算術平均粗さを曲面に対して適用できるよう三次元に拡張したものであり、「基準面から指定面までの偏差の絶対値を平均した値」で表現でき、数式 (2) にて定義される。

40

【0054】

【数2】

$$Ra = \frac{1}{S_0} \int_{y1}^{y2} \int_{x1}^{x2} |f(x, y) - Z_0| dx dy \quad (2)$$

【0055】

ここで、指定面とは、粗さ計測の対象となる面であり、座標 ( $x_1, y_1, f(x_1, y_1)$ ), ( $x_1, y_2, f(x_1, y_2)$ ), ( $x_2, y_1, f(x_2, y_1)$ ), ( $x_2, y_2, f(x_2, y_2)$ ) の 4 点で表される四角形の領域とし、指定面を  $xy$  平面上に

50

投影した長方形の面積を  $S_0$  、基準面の高さ（指定面の平均の高さ）を  $Z_0$  とする。Raは原子間力顕微鏡（AFM: Atomic Force Microscope）にて測定可能である。

【0056】

酸化物半導体膜106は、ESRにてg値が1.93で信号を表さないと好ましい。少なくとも、酸化物半導体膜106の第3の領域106cは、ESRにてg値が1.93で信号を表さない。

【0057】

なお、本明細書において、ESRにてg値が1.93で信号を表すという場合、ESRにてg値が1.93近傍（1.88以上1.98以下、より詳細には1.91以上1.95以下）に中心が位置する対称性の信号を表すことを示す。該信号は、酸化物半導体膜を構成する金属原子のダングリングボンドを示す。ESRにてg値が1.93で信号を表すという場合、金属原子のダングリングボンドが $5 \times 10^{16}$  spins/cm<sup>3</sup>以上であることを示し、ESRにてg値が1.93で信号を表さないという場合、金属原子のダングリングボンドが $5 \times 10^{16}$  spins/cm<sup>3</sup>未満であることを示す。

【0058】

また、酸化物半導体膜106の第1の領域106aおよび第2の領域106bは、酸化物半導体膜を低抵抗化する不純物を含む。

【0059】

酸化物半導体膜106の第1の領域106aおよび第2の領域106bは、具体的には、ヘリウム、ホウ素、窒素、フッ素、ネオン、アルミニウム、リン、アルゴン、ヒ素、クリプトン、インジウム、スズ、アンチモンおよびキセノンから選ばれた一種以上の不純物を含む領域である。

【0060】

酸化物半導体膜106として、In-M-Zn酸化物膜を用いればよい。ここで、Mは酸素との結合エネルギーがInおよびZnよりも高い元素である。または、In-M-Zn酸化物膜から酸素が脱離することを抑制する機能を有する元素である。Mの作用によって、酸化物半導体膜の酸素欠損の生成が抑制される。そのため、酸素欠損に起因するトランジスタの電気特性の変動を低減することができ、信頼性の高いトランジスタを得ることができる。

【0061】

Mは、具体的にはAl、Si、Sc、Ti、V、Cr、Mn、Fe、Co、Ni、Ga、Ge、Y、Zr、Nb、Mo、Sn、La、Ce、Pr、Nd、Sm、Eu、Gd、Tb、Dy、Ho、Er、Tm、Yb、Lu、Hf、TaまたはWとすればよく、好ましくはAl、Ti、Ga、Y、Zr、CeまたはHfとする。

【0062】

なお、酸化物半導体膜106は広いバンドギャップを有し、水素濃度が低く、ESRにてg値が1.93で信号を表さない酸化物半導体膜である。従って、酸化物半導体膜106を用いたトランジスタはオフ電流の極めて小さいトランジスタとすることができます。具体的には、オフ電流を $1 \times 10^{-21}$ A以下、好ましくは $1 \times 10^{-24}$ A以下とすることができます。

【0063】

酸化物半導体膜106は、単結晶、多結晶（ポリクリスタルともいう。）または非晶質などの状態をとる。

【0064】

好ましくは、酸化物半導体膜106は、CAAC-OS(C Axis Aligned Crystalline Oxide Semiconductor)膜とする。

【0065】

CAAC-OS膜は、完全な単結晶ではなく、完全な非晶質でもない。CAAC-OS膜は、非晶質相に結晶部および非晶質部を有する結晶・非晶質混相構造の酸化物半導体膜で

10

20

30

40

50

ある。なお、該結晶部は、一辺が 100 nm 未満の立方体内に収まる大きさであることが多い。また、透過型電子顕微鏡 (TEM: Transmission Electron Microscope) による観察像では、CAAC-OS 膜に含まれる非晶質部と結晶部との境界は明確ではない。また、TEM によって CAAC-OS 膜には粒界 (グレインバウンダリーともいう。) は確認できない。そのため、CAAC-OS 膜は、粒界に起因する電子移動度の低下が抑制される。

【0066】

CAAC-OS 膜に含まれる結晶部は、c 軸が CAAC-OS 膜の被形成面の法線ベクトルまたは表面の法線ベクトルに平行な方向に揃い、かつ a b 面に垂直な方向から見て三角形状または六角形状の原子配列を有し、c 軸に垂直な方向から見て金属原子が層状または金属原子と酸素原子とが層状に配列している。なお、異なる結晶部間で、それぞれ a 軸および b 軸の向きが異なっていてもよい。本明細書において、単に垂直と記載する場合、85° 以上 95° 以下の範囲も含まれることとする。

【0067】

なお、CAAC-OS 膜において、結晶部の分布が一様でなくてもよい。例えば、CAAC-OS 膜の形成過程において、酸化物半導体膜 106 の表面側から結晶成長させる場合、被形成面の近傍に対し表面の近傍では結晶部の占める割合が高くなることがある。また、CAAC-OS 膜へ不純物を添加することにより、該不純物添加領域において結晶部が非晶質化することもある。

【0068】

CAAC-OS 膜に含まれる結晶部の c 軸は、CAAC-OS 膜の被形成面の法線ベクトルまたは表面の法線ベクトルに平行な方向に揃うため、CAAC-OS 膜の形状 (被形成面の断面形状または表面の断面形状) によっては互いに異なる方向を向くことがある。なお、結晶部の c 軸の方向は、CAAC-OS 膜が形成されたときの被形成面の法線ベクトルまたは表面の法線ベクトルに平行な方向となる。結晶部は、成膜することにより、または成膜後に加熱処理などの結晶化処理を行うことにより形成される。

【0069】

CAAC-OS 膜を用いたトランジスタは、可視光や紫外光の照射による電気特性の変動を低減することが可能である。よって、該トランジスタは、信頼性が高い。

【0070】

基板 100 に大きな制限はないが、少なくとも、後の熱処理に耐え得る程度の耐熱性を有している必要がある。例えば、ガラス基板、セラミック基板、石英基板、サファイア基板などを、基板 100 として用いてもよい。また、シリコンや炭化シリコンなどの単結晶半導体基板、多結晶半導体基板、シリコンゲルマニウムなどの化合物半導体基板、SOI (Silicon On Insulator) 基板などを適用することも可能であり、これらの基板上に半導体素子が設けられたものを、基板 100 として用いてもよい。

【0071】

また、基板 100 として、可とう性基板を用いてもよい。なお、可とう性基板上にトランジスタを設ける方法としては、非可とう性の基板上にトランジスタを作製した後、トランジスタを剥離し、可とう性基板である基板 100 に転置する方法もある。その場合には、非可とう性基板とトランジスタとの間に剥離層を設けるとよい。

【0072】

ゲート絶縁膜 112 は、酸化シリコン、酸化窒化シリコン、窒化酸化シリコン、窒化シリコン、酸化アルミニウム、窒化アルミニウム、酸化ハフニウム、酸化ジルコニウム、酸化イットリウム、酸化ランタン、酸化セシウム、酸化タンタルおよび酸化マグネシウムの一種以上を選択して、単層または積層で用いればよい。

【0073】

ゲート電極 104 は、Al、Ti、Cr、Co、Ni、Cu、Y、Zr、Mo、Ag、Ta および W、それらの窒化物、酸化物ならびに合金から一種以上選択し、単層または積層で用いればよい。または、少なくとも In および Zn を含む酸化物または酸窒化物を用

10

20

30

40

50

いても構わない。例えば、In-Ga-Zn酸窒化物などを用いればよい。

【0074】

層間絶縁膜118は、ゲート絶縁膜112として示した絶縁膜から選択して用いればよい。

【0075】

層間絶縁膜118は、比誘電率が低く、かつ十分な厚さを有すると好ましい。例えば、比誘電率が3.8程度である酸化シリコン膜を用い、300nm以上1000nm以下の厚さで設ければよい。層間絶縁膜118の表面は、大気成分などの影響で僅かに固定電荷を有し、その影響により、トランジスタのしきい値電圧が変動することがある。そのため、層間絶縁膜118は、表面に生じる電荷の影響が十分に小さくなるような範囲の比誘電率および厚さとすることが好ましい。同様の理由で、層間絶縁膜118上に樹脂膜を形成することで、表面に生じる電荷の影響を低減しても構わない。

10

【0076】

配線116aおよび配線116bは、ゲート電極104として示した導電膜から選択して用いればよい。なお、配線116aおよび配線116bは、同一層とすればよい。

【0077】

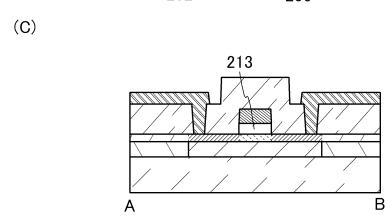

なお、図1(C)に示すトランジスタは、図1(B)に示すトランジスタとゲート絶縁膜の形状が異なる以外は同様である。具体的には、図1(B)に示すトランジスタではゲート絶縁膜112が酸化物半導体膜106を覆って設けられるのに対し、図1(C)に示すトランジスタではゲート絶縁膜113はゲート電極104と同様の上面形状となる。

20

【0078】

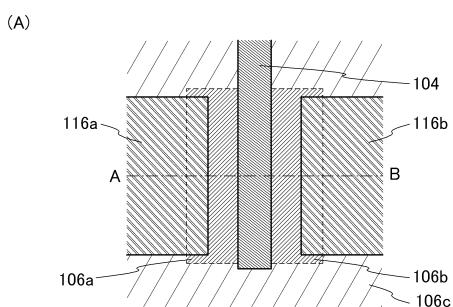

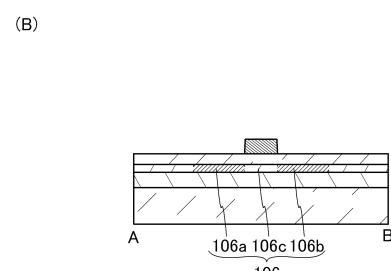

以下に図1(B)に示すトランジスタの作製方法を示す。

【0079】

まず、基板100を準備し、基板100上に下地絶縁膜102を成膜する(図2(A)参照。)。下地絶縁膜102は、スパッタリング法、化学気相成長(CVD:Chemical Vapor Deposition)法、分子線エピタキシー(MBE: Molecular Beam Epitaxy)法、原子層堆積(ALD:Atomic Layer Deposition)法またはパルスレーザ堆積(PLD: Pulse Laser Deposition)法を用いて成膜すればよい。

30

【0080】

下地絶縁膜102は、好ましくはスパッタリング法を用いる。この際、酸化性ガス(酸素、オゾンまたは亜酸化窒素)を、5%以上、好ましくは10%以上、さらに好ましくは20%以上、さらに好ましくは50%以上含む成膜ガスを用いる。該成膜ガスとして、水素などの不純物濃度が低いガスを用いる。また、成膜時の基板加熱温度は室温以上200以下、好ましくは室温以上150以下、さらに好ましくは室温以上120以下とする。以上のような方法で下地絶縁膜102を成膜すると、水素などの不純物濃度が低く、かつ酸素を余剰に含みやすいため、下地絶縁膜102に酸素原子のダングリングボンドが形成されやすい。即ち、ESRにてg値が2.01で信号を表す絶縁膜を成膜することができる。なお、室温は、代表的には20または25である。

40

【0081】

次に、下地絶縁膜102上に酸化物半導体膜137を成膜する(図2(B)参照。)。酸化物半導体膜137は、スパッタリング法、CVD法、MBE法、ALD法またはPLD法を用いて成膜すればよい。

【0082】

酸化物半導体膜137は、好ましくはスパッタリング法を用いる。この際、酸化性ガスを、5%以上、好ましくは10%以上、さらに好ましくは20%以上、さらに好ましくは50%以上含む成膜ガスを用いる。該成膜ガスとして、水素などの不純物濃度の低いガスを用いる。また、成膜時の基板加熱温度は室温以上450以下、好ましくは100以上400以下、さらに好ましくは150以上350以下とする。以上のような方法で酸化物半導体膜137を成膜すると、水素などの不純物濃度が低く、かつ酸素欠損が生じ

50

にくいため、金属原子のダングリングボンドが形成されにくい。即ち、E S R にて  $g$  値が 1.93 で信号を表さない酸化物半導体膜を成膜することができる。

【 0 0 8 3 】

次に、酸化物半導体膜 137 上にゲート絶縁膜 112 を成膜する（図 2 ( C ) 参照。）。ゲート絶縁膜 112 は、スパッタリング法、CVD 法、MBE 法、ALD 法または PLD 法を用いて成膜すればよい。

【 0 0 8 4 】

ゲート絶縁膜 112 は、下地絶縁膜 102 と同様の方法で成膜してもよい。こうすることで、ゲート絶縁膜 112 を、E S R にて  $g$  値が 2.01 で信号を表す絶縁膜とすることができる。

10

【 0 0 8 5 】

ゲート絶縁膜 112 の成膜後、第 1 の加熱処理を行い、酸化物半導体膜 137 を水素濃度が低い酸化物半導体膜 136 にする。第 1 の加熱処理は、不活性ガス（窒素、またはヘリウム、ネオン、アルゴン、クリプトン、キセノンなどの希ガス）雰囲気、酸化性ガスを、10 ppm 以上、好ましくは 1% 以上、さらに好ましくは 10% 以上含む雰囲気、または減圧状態 (10 Pa 以下) において、450 以上 700 以下、好ましくは 500 以上 700 以下、さらに好ましくは 550 以上 700 以下の温度で行う。

【 0 0 8 6 】

第 1 の加熱処理によって、酸化物半導体膜 137 の水素濃度が低減する。また、通常 450 以上 700 以下の温度で加熱処理を行うと、酸化物半導体膜の酸素欠損が増加するが、本実施の形態では、第 1 の加熱処理により下地絶縁膜 102 などから酸素が放出され、該酸素が酸化物半導体膜 137 へ供給されるため、第 1 の加熱処理に起因する酸化物半導体膜 137 の酸素欠損の増加を抑制できる。むしろ、酸化物半導体膜 136 は、酸化物半導体膜 137 を成膜した直後よりも酸素欠損が低減される場合もある。

20

【 0 0 8 7 】

即ち、第 1 の加熱処理を行うことで、酸化物半導体膜 136 を、E S R にて  $g$  値が 1.93 で信号を表さず、かつ水素濃度の低い酸化物半導体膜とすることができます。即ち、酸化物半導体膜 136 は、極めて水素濃度が低く、酸素欠損の少ない高抵抗な酸化物半導体膜である。

【 0 0 8 8 】

30

なお、第 1 の加熱処理後も、下地絶縁膜 102 に加熱処理によって放出する酸素が残存することが好ましい。具体的には、第 1 の加熱処理後も下地絶縁膜 102 は、E S R にて  $g$  値が 2.01 で信号を表すと好ましい。

【 0 0 8 9 】

また、下地絶縁膜 102 およびゲート絶縁膜 112 で酸化物半導体膜 137 を挟み、第 1 の加熱処理を行うことで、下地絶縁膜 102 から放出される酸素の外方拡散が起こりにくい。即ち、下地絶縁膜 102 は、第 1 の加熱処理後も E S R にて  $g$  値が 2.01 で信号を表しやすい。

【 0 0 9 0 】

40

次に、ゲート絶縁膜 112 を介して酸化物半導体膜 136 上にゲート電極 104 となる導電膜を成膜する。該導電膜は、スパッタリング法、CVD 法、MBE 法、ALD 法または PLD 法を用いて成膜すればよい。

【 0 0 9 1 】

次に、ゲート電極 104 となる導電膜を加工し、ゲート電極 104 を形成する（図 3 ( A ) 参照。）。なお、本明細書において、単に「加工する」と記載する場合、例えばフォトリソグラフィ工程により形成したレジストマスクを用いて、膜を所望の形状にすることを示す。

【 0 0 9 2 】

次に、フォトリソグラフィ工程により形成したレジストマスクおよびゲート電極 104 をマスクとし、酸化物半導体膜 136 に不純物を添加することで、第 1 の領域 106a、第

50

2 の領域 106b および第 3 の領域 106c を形成する。ここで、不純物は、酸化物半導体膜を低抵抗化する不純物である。具体的には、ヘリウム、ホウ素、窒素、フッ素、ネオジン、アルミニウム、リン、アルゴン、ヒ素、クリプトン、インジウム、スズ、アンチモンおよびキセノンから選ばれた一種以上を添加すればよい。なお、その方法は、イオン注入法、イオンドーピング法で行えばよい。または、酸化物半導体膜を低抵抗化する不純物を含む雰囲気でのプラズマ処理もしくは加熱処理を行えばよい。好ましくはイオン注入法を用いる。

【0093】

なお、イオン注入法にて酸化物半導体膜を低抵抗化する不純物を添加した後、第 2 の加熱処理を行ってもよい。第 2 の加熱処理は、第 1 の加熱処理と同様の加熱処理とすればよい。なお、第 2 の加熱処理を、第 1 の加熱処理に代えて行ってもよい。なお、第 3 の領域 106c は、前述の不純物の添加されない領域である。不純物添加の後、第 2 の加熱処理を行うことによって、酸化物半導体膜 136 を、第 1 の領域 106a、第 2 の領域 106b および第 3 の領域 106c を有する酸化物半導体膜 106 としてもよい(図 3 (B) 参照。)。

【0094】

第 2 の加熱処理後も、下地絶縁膜 102 に加熱処理によって放出する酸素が残存することが好ましい。具体的には、第 2 の加熱処理後も下地絶縁膜 102 は、ESR にて  $g$  値が 2.01 で信号を表すと好ましい。

【0095】

下地絶縁膜 102 およびゲート絶縁膜 112 で酸化物半導体膜 136 を挟み、第 2 の加熱処理を行うことで、下地絶縁膜 102 から放出される酸素の外方拡散が起こりにくい。即ち、下地絶縁膜 102 は、第 2 の加熱処理後も ESR にて  $g$  値が 2.01 で信号を表しやすい。

【0096】

次に、ゲート絶縁膜 112 およびゲート電極 104 上に層間絶縁膜 118 を成膜する。層間絶縁膜 118 は、スパッタリング法、CVD 法、MBE 法、ALD 法または PLD 法を用いて成膜すればよい。

【0097】

層間絶縁膜 118 は、下地絶縁膜 102 と同様の方法で成膜してもよい。こうすることでも、層間絶縁膜 118 を、ESR にて  $g$  値が 2.01 で信号を表す絶縁膜とすることができます。

【0098】

次に、層間絶縁膜 118 およびゲート絶縁膜 112 を加工して、酸化物半導体膜 106 の第 1 の領域 106a および第 2 の領域 106b を露出する開口部を形成する。該開口部の形成は、酸化物半導体膜 106 がなるべくエッチングされないような条件で行うが、これに限定されない。具体的には、該開口部を形成する際に、酸化物半導体膜 106 を貫通し、下地絶縁膜 102 を露出してしまっても構わない。

【0099】

次に、層間絶縁膜 118、ならびに露出された酸化物半導体膜 106 の第 1 の領域 106a および第 2 の領域 106b 上に、配線 116a および配線 116b となる導電膜を成膜する。該導電膜は、スパッタリング法、CVD 法、MBE 法、ALD 法または PLD 法を用いて成膜すればよい。

【0100】

次に、配線 116a および配線 116b となる導電膜を加工し、配線 116a および配線 116b を形成する(図 3 (C) 参照。)。

【0101】

以上の工程により、図 1 (B) に示すトランジスタを作製することができる。

【0102】

なお、図 1 (C) に示すトランジスタは、図 1 (B) に示すトランジスタとゲート絶縁膜

10

20

30

40

50

の形状が異なるのみである。そのため、図1(C)のトランジスタの作製方法の詳細は図1(B)のトランジスタの作製方法を参照すればよい。

【0103】

本実施の形態によって得られたトランジスタは、酸素欠損が少なく、かつ水素濃度の低い酸化物半導体膜、および加熱処理により酸素を放出する下地絶縁膜を用いている。そのため、トランジスタの動作に起因する電気特性の変動が小さく、また、該トランジスタを用いた半導体装置は高い信頼性を有する。

【0104】

本実施の形態は、適宜他の実施の形態と組み合わせて用いることができる。

【0105】

(実施の形態2)

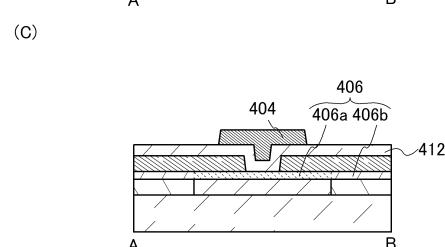

本実施の形態では、実施の形態1で示したトランジスタとは異なる構造を有するトランジスタおよびその作製方法について、図4乃至図8を用いて説明する。

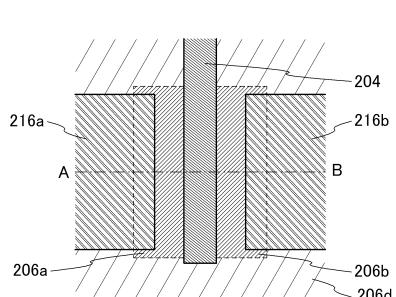

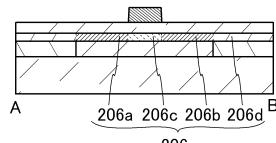

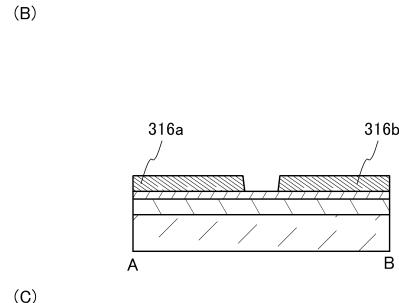

【0106】

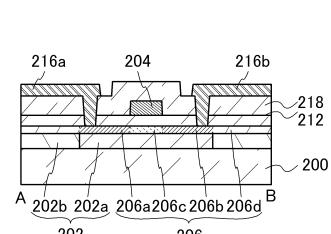

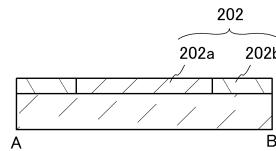

図4(A)は本発明の一態様に係るトランジスタの上面図である。図4(A)に示す一点鎖線A-Bに対応する断面図を図4(B)に示す。なお、簡単のため、図4(A)においては、層間絶縁膜218、ゲート絶縁膜212などを省略して示す。

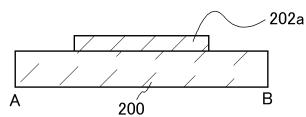

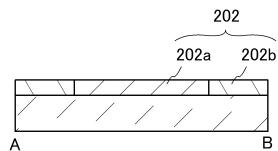

【0107】

図4(B)に示すトランジスタは、基板200上に設けられた第1の領域202aおよび第2の領域202bを有する下地絶縁膜202と、下地絶縁膜202上に設けられた第3の領域206a、第4の領域206b、第5の領域206cおよび第6の領域206dを有する酸化物半導体膜206と、酸化物半導体膜206上に設けられたゲート絶縁膜212と、ゲート絶縁膜212を介して酸化物半導体膜206の第5の領域206cと重畠するゲート電極204と、を有する。

【0108】

なお、図4(A)において、酸化物半導体膜206の第3の領域206aの一側端および第4の領域206bの一側端は、それぞれゲート電極204の長手方向に平行な側端部と重なる。即ち、図4(B)において、酸化物半導体膜206の第3の領域206aの一端および第4の領域206bの一端は、それぞれゲート電極204の下端部と重なる。

【0109】

ここで、酸化物半導体膜206の第6の領域206dは、下地絶縁膜202の第2の領域202bと重なる領域とすればよい。また、酸化物半導体膜206の第3の領域206a、第4の領域206bおよび第5の領域206cを併せた領域は、下地絶縁膜202の第1の領域202aと重なる領域とすればよい。こうすると、トランジスタの作製時に下地絶縁膜202と酸化物半導体膜206でフォトマスクを共用できるため好ましい。また、酸化物半導体膜206の第5の領域206cは、酸化物半導体膜206の第3の領域206aおよび第4の領域206bに挟まれた領域であり、図4(A)において、二端がゲート電極204の長手方向に平行な側端部と重なる。即ち、図4(B)において、酸化物半導体膜206の第5の領域206cの二端は、それぞれゲート電極204の下端部と重なる。

【0110】

なお、酸化物半導体膜206の第3の領域206aおよび第4の領域206bは、トランジスタのソース領域およびドレイン領域として機能する。また、酸化物半導体膜206の第5の領域206cはトランジスタのチャネル領域として機能する。

【0111】

また、酸化物半導体膜206の第6の領域206dは、絶縁領域として機能する。そのため、同一層に複数のトランジスタが設けられる場合でも、トランジスタ間を電気的に分離することができる。

【0112】

なお、図4(B)に示すトランジスタは、ゲート電極204およびゲート絶縁膜212上

10

20

30

40

50

に設けられた層間絶縁膜 218 と、層間絶縁膜 218 およびゲート絶縁膜 212 に設けられた、酸化物半導体膜 206 の第3の領域 206a および第4の領域 206b に達する開口部にて酸化物半導体膜 206 の第3の領域 206a および第4の領域 206b とそれ接して設けられた配線 216a および配線 216b と、を有してもよい。

## 【0113】

また、配線 216a および配線 216b と同一層で設けられた配線と、ゲート電極 204 と、を接続してもよい。

## 【0114】

ここで、下地絶縁膜 202 の第2の領域 202b は、下地絶縁膜 102 と同様の絶縁膜を用いればよい。

10

## 【0115】

また、下地絶縁膜 202 の第1の領域 202a は、ESRにてg値が2.01で信号を表さない絶縁膜である。

## 【0116】

下地絶縁膜 202 の第1の領域 202a は、シリコンを有する。具体的には、酸化シリコン膜または酸化窒化シリコン膜を単層または積層で用いればよい。

## 【0117】

下地絶縁膜 202 の第1の領域 202a は、200 以上 450 未満の温度における加熱処理により酸素を放出する絶縁膜を用いると好ましい。

## 【0118】

酸化物半導体膜 206 は、酸化物半導体膜 106 と同様の酸化物膜を用いればよい。

20

## 【0119】

また、酸化物半導体膜 206 の第3の領域 206a および第4の領域 206b は、酸化物半導体膜 106 の第1の領域 106a および第2の領域 106b と同様の領域とすればよい。

## 【0120】

基板 200 は、基板 100 と同様の基板を用いればよい。

## 【0121】

ゲート絶縁膜 212 は、ゲート絶縁膜 112 と同様の絶縁膜を用いればよい。

## 【0122】

ゲート電極 204 は、ゲート電極 104 と同様の導電膜を用いればよい。

30

## 【0123】

層間絶縁膜 218 は、層間絶縁膜 118 と同様の絶縁膜を用いればよい。

## 【0124】

配線 216a および配線 216b は、配線 116a および配線 116b と同様の導電膜を用いればよい。

## 【0125】

なお、図4(C)に示すトランジスタは、図4(B)に示すトランジスタとゲート絶縁膜の形状が異なる以外は同様である。具体的には、図4(B)に示すトランジスタではゲート絶縁膜 212 が酸化物半導体膜 206 を覆って設けられるのに対し、図4(C)に示すトランジスタではゲート絶縁膜 213 はゲート電極 204 と同様の上面形状となる。

40

## 【0126】

本実施の形態に示すトランジスタは、下地絶縁膜 202 の第1の領域 202a がESRにてg値が2.01で信号を表さない領域である。従って、下地絶縁膜 202 の第1の領域 202a 上に設けられた、酸化物半導体膜 206 の第3の領域 206a および第4の領域 206b を低抵抗化しやすく、かつ高抵抗化しにくいため、トランジスタのオン電流を高めることができる。

## 【0127】

以下に図4(B)に示すトランジスタの作製方法を示す。

## 【0128】

50

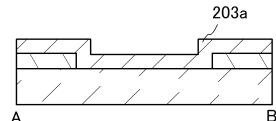

第1の領域202aおよび第2の領域202bを有する下地絶縁膜202の作製方法について、図5を用いて説明する。

【0129】

まず、基板200を準備し、基板200上に第1の領域202aとなる絶縁膜を成膜する。第1の領域202aとなる絶縁膜は、スパッタリング法、CVD法、MBE法、ALD法またはPVD法を用いて成膜すればよい。

【0130】

次に、第1の領域202aとなる絶縁膜を加工し、第1の領域202aを形成する(図5(A)参照。)。

【0131】

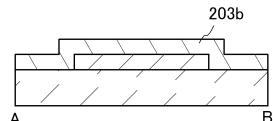

次に、第1の領域202aおよび基板200を覆って絶縁膜203bを成膜する(図5(B)参照。)。絶縁膜203bは、スパッタリング法、CVD法、MBE法、ALD法またはPVD法を用いて成膜すればよい。

【0132】

このとき、第1の領域202aの端部がテーパー角を有すると、第1の領域202a上に絶縁膜203bを良好に被覆することができ、段差部などに隙間ができにくくなる。

【0133】

なお、「テーパー角を有する」とは、テーパー角の角度が20°以上90°未満(好ましくは、40°以上85°未満)をいう。

【0134】

次に、第1の領域202aの露出処理を行い、第1の領域202aおよび第2の領域202bを有する下地絶縁膜202を形成する(図5(C)参照。)。なお、第1の領域202aの露出処理を行うことで、第1の領域202aおよび第2の領域202bは表面の高さが同程度となる。

【0135】

第1の領域202aの露出処理は、絶縁膜203bが平坦になるよう上面から除去していく、第1の領域202aを露出させる処理のことである。具体的には化学機械研磨(CMP: Chemical Mechanical Polishing)処理、エッティング処理などを、第1の領域202aが露出するまで行えばよい。

【0136】

なお、エッティング処理により第1の領域202aを露出するためには、絶縁膜203b上に平坦化膜を形成し、その後、該平坦化膜と第2の絶縁膜203bとが同程度のエッティングレートとなる条件でエッティング処理を行えばよい。

【0137】

同様に、図5で説明した方法とは異なる方法で、第1の領域202aおよび第2の領域202bを有する下地絶縁膜202を作製する方法を図6を用いて説明する。

【0138】

まず、基板200を準備し、基板200上に第2の領域202bとなる絶縁膜を成膜する。第2の領域202bとなる絶縁膜は、スパッタリング法、CVD法、MBE法、ALD法またはPVD法を用いて成膜すればよい。

【0139】

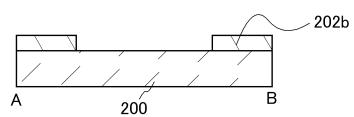

次に、第2の領域202bとなる絶縁膜を加工し、第2の領域202bを形成する(図6(A)参照。)。

【0140】

次に、第2の領域202bおよび基板200を覆って絶縁膜203aを成膜する(図6(B)参照。)。絶縁膜203aは、スパッタリング法、CVD法、MBE法、ALD法またはPVD法を用いて成膜すればよい。

【0141】

このとき、第2の領域202bの端部がテーパー角を有すると、第2の領域202b上に絶縁膜203aを良好に被覆することができ、段差部などに隙間ができにくくなる。

10

20

30

40

50

## 【0142】

次に、第2の領域202bの露出処理を行い、第1の領域202aおよび第2の領域202bを有する下地絶縁膜202を形成する(図6(C)参照。)。なお、第2の領域202bの露出処理を行うことで、第1の領域202aおよび第2の領域202bは表面の高さが同程度となる。

## 【0143】

第2の領域202bの露出処理は、図5で説明した第1の領域202aの露出処理と同様の方法で行えばよい。具体的にはCMP処理、エッチング処理などによって行えばよい。

## 【0144】

以上のように、第1の領域202aおよび第2の領域202bを有する下地絶縁膜202を形成することができる。 10

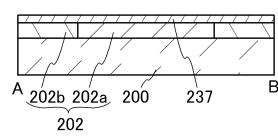

## 【0145】

次に、下地絶縁膜202上に酸化物半導体膜237を成膜する(図7(A)参照。)。酸化物半導体膜237は、酸化物半導体膜137と同様の方法を用いて成膜すればよい。

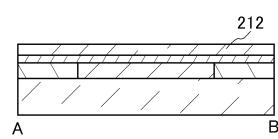

## 【0146】

次に、酸化物半導体膜237上にゲート絶縁膜212を成膜する(図7(B)参照。)。

## 【0147】

次に、第1の加熱処理を行い、第3の領域207aおよび第4の領域207bを有する酸化物半導体膜207を形成する(図7(C)参照。)。

## 【0148】

第1の加熱処理は、実施の形態1で示した第1の加熱処理と同様の加熱処理とすればよい。 20

## 【0149】

ここで、酸化物半導体膜207の第3の領域207aは、下地絶縁膜202の第1の領域202aと重なる領域である。また、酸化物半導体膜207の第4の領域207bは、下地絶縁膜202の第2の領域202bと重なる領域である。これは、第1の加熱処理によって、下地絶縁膜202から酸化物半導体膜237へ供給される酸素の量が、下地絶縁膜202の第1の領域202aおよび第2の領域202bで異なるためである。

## 【0150】

なお、下地絶縁膜202の第1の領域202aは、第1の加熱処理により、酸化物半導体膜206に供給可能な酸素のほとんどを放出してしまう。従って、下地絶縁膜202の第1の領域202aは、第1の加熱処理後にESRにてg値が2.01で信号を表さなくなる。一方、下地絶縁膜202の第2の領域202bは、第1の加熱処理後もESRにてg値が2.01で信号を表す。 30

## 【0151】

下地絶縁膜202およびゲート絶縁膜212で酸化物半導体膜237を挟み、第1の加熱処理を行うことで、下地絶縁膜202から放出される酸素の外方拡散が起こりにくい。即ち、下地絶縁膜202の第1の領域202aは、第1の加熱処理後にESRにてg値が2.01で信号を表さなくなるが、該領域に形成した酸化物半導体膜206は、その後の工程における第1の加熱処理の温度以下の処理では、酸素欠損が生じにくい。 40

## 【0152】

次に、ゲート絶縁膜212上にゲート電極204を形成する(図8(A)参照。)。なお、ゲート絶縁膜212の成膜後に代えて、ゲート電極204の形成後に第1の加熱処理を行ってもよい。

## 【0153】

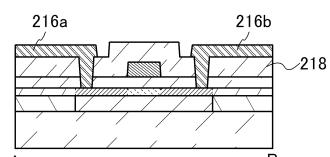

次に、フォトリソグラフィ工程により形成したレジストマスクおよびゲート電極204をマスクとし、酸化物半導体膜207に不純物を添加することで、第3の領域206a、第4の領域206b、第5の領域206cおよび第6の領域206dを形成する。ここで、不純物添加は、実施の形態1で示した方法で行えばよい。

## 【0154】

なお、不純物を添加した後に、第2の加熱処理を行ってもよい。第2の加熱処理は、第1の加熱処理と同様の加熱処理とすればよい。なお、第2の加熱処理を、第1の加熱処理に代えて行ってもよい。なお、第5の領域206cおよび第6の領域206dは、前述の不純物の添加されない領域である。不純物添加の後、第2の加熱処理を行うことによって、酸化物半導体膜207を、第3の領域206a、第4の領域206b、第5の領域206cおよび第6の領域206dを有する酸化物半導体膜206としてもよい(図8(B)参照。)。

**【0155】**

なお、下地絶縁膜202の第1の領域202aがESRにてg値が2.01で信号を表さない領域である。従って、下地絶縁膜202の第1の領域202a上に設けられた、酸化物半導体膜206の第3の領域206aおよび第4の領域206bは前述の不純物添加により低抵抗化しやすく、かつ第2の加熱処理により高抵抗化しにくいため、トランジスタのオン電流を高めることができる。

10

**【0156】**

なお、前述の不純物添加において、フォトリソグラフィ工程で用いるフォトマスクは、下地絶縁膜202の第1の領域202aおよび第2の領域202bを形成するために用いたフォトマスクを用いてもよい。

**【0157】**

次に、ゲート絶縁膜212およびゲート電極204上に層間絶縁膜218を成膜する。

20

**【0158】**

次に、層間絶縁膜218およびゲート絶縁膜212を加工して、酸化物半導体膜206の第3の領域206aおよび第4の領域206bを露出する開口部を形成する。該開口部の形成は、酸化物半導体膜206がなるべくエッチングされないような条件で行うが、これに限定されない。具体的には、該開口部を形成する際に、酸化物半導体膜206を貫通し、下地絶縁膜202を露出してしまっても構わない。

**【0159】**

次に、層間絶縁膜218、ならびに露出された酸化物半導体膜206の第3の領域206aおよび第4の領域206b上に、配線216aおよび配線216bを形成する(図8(C)参照。)。

**【0160】**

30

以上の工程により、図4(B)に示すトランジスタを作製することができる。

**【0161】**

なお、図4(C)に示すトランジスタは、図4(B)に示すトランジスタとゲート絶縁膜の形状が異なるのみである。そのため、図4(C)のトランジスタの作製方法の詳細は図4(B)のトランジスタの作製方法を参照すればよい。

**【0162】**

本実施の形態によって得られたトランジスタは、酸素欠損が少なく、かつ水素濃度の低い酸化物半導体膜、および加熱処理により酸素を放出する下地絶縁膜を用いている。そのため、トランジスタの動作に起因する電気特性の変動が小さく、また、該トランジスタを用いた半導体装置は高い信頼性を有する。

40

**【0163】**

また、トランジスタのソース領域およびドレイン領域として、低抵抗化しやすく、高抵抗化しにくい領域を有するため、オン電流の高いトランジスタを作製することができる。

**【0164】**

本実施の形態は、適宜他の実施の形態と組み合わせて用いることができる。

**【0165】**

(実施の形態3)

本実施の形態では、実施の形態1および実施の形態2で示したトランジスタとは異なる構造を有するトランジスタおよびその作製方法について、図9および図10を用いて説明する。

50

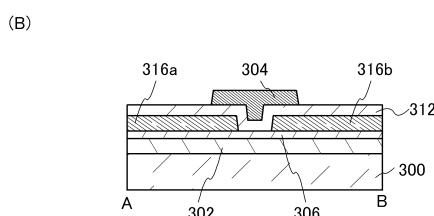

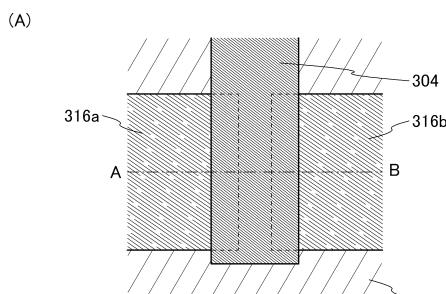

## 【0166】

図9(A)は本発明の一態様に係るトランジスタの上面図である。図9(A)に示す一点鎖線A-Bに対応する断面図を図9(B)に示す。なお、簡単のため、図9(A)においては、ゲート絶縁膜312などを省略して示す。

## 【0167】

図9(B)に示すトランジスタは、基板300上の下地絶縁膜302と、下地絶縁膜302上に設けられた酸化物半導体膜306と、酸化物半導体膜306上に電気的に分離して設けられた電極316aおよび電極316bと、酸化物半導体膜306、電極316aおよび電極316b上のゲート絶縁膜312と、ゲート絶縁膜312を介し、電極316aと電極316bとの間の領域と重畠して設けられたゲート電極304と、を有する。

10

## 【0168】

酸化物半導体膜306は、酸化物半導体膜137と同様の酸化物膜を用いればよい。

## 【0169】

下地絶縁膜302は、下地絶縁膜102と同様の絶縁膜を用いればよい。

## 【0170】

基板300は、基板100と同様の基板を用いればよい。

## 【0171】

電極316aおよび電極316bは、配線116aおよび配線116bと同様の導電膜を用いればよい。

20

## 【0172】

ゲート絶縁膜312は、ゲート絶縁膜112と同様の絶縁膜を用いればよい。

## 【0173】

ゲート電極304は、ゲート電極104と同様の導電膜を用いればよい。

## 【0174】

なお、ゲート電極304は、電極316aおよび電極316bと一部が重畠して設けられる。

## 【0175】

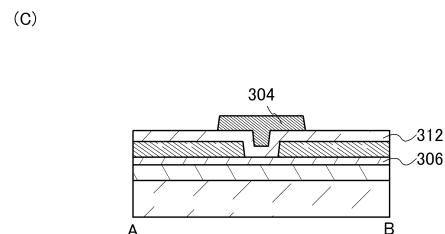

以下に図9(B)に示すトランジスタの作製方法を示す。

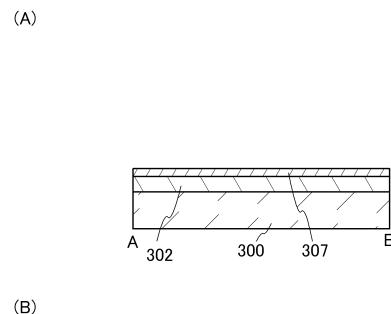

## 【0176】

まず、基板300を準備し、基板300上に下地絶縁膜302および酸化物半導体膜307を、この順番で成膜する(図10(A)参照。)。

30

## 【0177】

次に、酸化物半導体膜307上に電極316aおよび電極316bとなる導電膜を成膜し、加工して電極316aおよび電極316bを形成する(図10(B)参照。)。

## 【0178】

次に、酸化物半導体膜307、電極316aおよび電極316b上にゲート絶縁膜312を成膜する。

## 【0179】

次に、第1の加熱処理を行う。第1の加熱処理は、実施の形態1で示した第1の加熱処理と同様の加熱処理とすればよい。

40

## 【0180】

第1の加熱処理によって、酸化物半導体膜307の水素濃度が低減する。また、通常450以上700以下の温度で加熱処理を行うと、酸化物半導体膜の酸素欠損が増加するが、本実施の形態では、第1の加熱処理により下地絶縁膜302などから酸素が放出され、該酸素によって第1の加熱処理に起因する酸化物半導体膜307の酸素欠損の増加を抑制できる。むしろ、酸化物半導体膜306は、酸化物半導体膜307を成膜した直後よりも酸素欠損が低減される場合がある。

## 【0181】

即ち、第1の加熱処理を行うことで、酸化物半導体膜306を、水素濃度が低く、かつESRにてg値が1.93で信号を表さない酸化物半導体膜とすることができます。即ち、酸

50

化物半導体膜 306 は、極めて水素濃度が低く、酸素欠損の少ない高抵抗な酸化物半導体膜である。

【0182】

なお、第1の加熱処理によって下地絶縁膜302から酸素が放し切らないことが好ましい。具体的には、第1の加熱処理後も下地絶縁膜302は、ESRにてg値が2.01で信号を表すと好ましい。

【0183】

下地絶縁膜302およびゲート絶縁膜312で酸化物半導体膜307を挟み、第1の加熱処理を行うことで、下地絶縁膜302から放出される酸素の外方拡散が起こりにくい。即ち、下地絶縁膜302は、第1の加熱処理後もESRにてg値が2.01で信号を表しやすい。

【0184】

次に、ゲート絶縁膜312上にゲート電極304となる導電膜を成膜し、該導電膜を加工してゲート電極304を形成する(図10(C)参照。)。

【0185】

なお、ゲート絶縁膜312の成膜後に代えて、ゲート電極304の形成後に第1の加熱処理を行ってもよい。

【0186】

以上の工程により、図9(B)に示すトランジスタを作製することができる。

【0187】

以上に示した工程では、電極316aおよび電極316b、ならびにゲート電極304のみフォトリソグラフィ工程を行えばよい。フォトリソグラフィ工程数を低減することができるため、トランジスタの作製に係るコストを大幅に低減することができる。

【0188】

また、本実施の形態によって得られたトランジスタは、酸素欠損が少なく、かつ水素濃度の低い酸化物半導体膜、および加熱処理により酸素を放出する下地絶縁膜を用いている。そのため、トランジスタの動作に起因する電気特性の変動が小さく、また、該トランジスタを用いた半導体装置は高い信頼性を有する。

【0189】

本実施の形態は、適宜他の実施の形態と組み合わせて用いることができる。

【0190】

(実施の形態4)

本実施の形態では、実施の形態1乃至実施の形態3で示したトランジスタとは異なる構造を有するトランジスタおよびその作製方法について、図11および図12を用いて説明する。

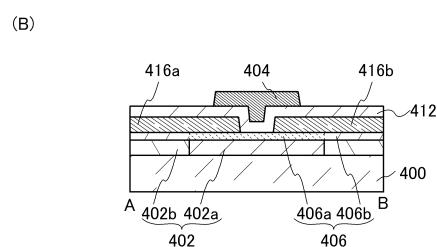

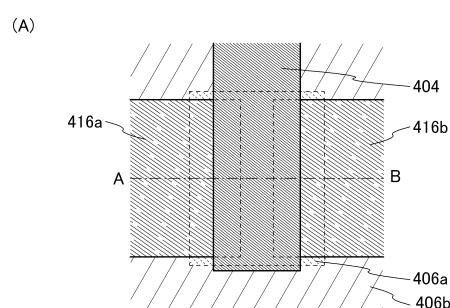

【0191】

図11(A)は本発明の一態様に係るトランジスタの上面図である。図11(A)に示す一点鎖線A-Bに対応する断面図を図11(B)に示す。なお、簡単のため、図11(A)においては、ゲート絶縁膜412などを省略して示す。

【0192】

図11(B)に示すトランジスタは、基板400上の第1の領域402aおよび第2の領域402bを有する下地絶縁膜402と、下地絶縁膜402上に設けられた第3の領域406aおよび第4の領域406bを有する酸化物半導体膜406と、酸化物半導体膜406上に電気的に分離して設けられた電極416aおよび電極416bと、酸化物半導体膜406、電極416aおよび電極416b上のゲート絶縁膜412と、ゲート絶縁膜412を介し、酸化物半導体膜406の第4の領域406bと重畠して設けられたゲート電極404と、を有する。

【0193】

酸化物半導体膜406は、酸化物半導体膜207と同様の酸化物膜を用いればよい。

【0194】

10

20

30

40

50

第1の領域402aおよび第2の領域402bを有する下地絶縁膜402は、第1の領域202aおよび第2の領域202bを有する下地絶縁膜202と同様の絶縁膜を用いればよい。

【0195】

なお、図11(B)に示すトランジスタは、図9(B)に示すトランジスタと、下地絶縁膜および酸化物半導体膜の構成が異なる以外同様である。

【0196】

基板400は、基板100と同様の基板を用いればよい。

【0197】

電極416aおよび電極416bは、電極316aおよび電極316bと同様の導電膜を用いればよい。 10

【0198】

ゲート絶縁膜412は、ゲート絶縁膜312と同様の絶縁膜を用いればよい。

【0199】

ゲート電極404は、ゲート電極304と同様の導電膜を用いればよい。

【0200】

なお、ゲート電極404は、電極416aおよび電極416bと一部が重畠して設けられる。

【0201】

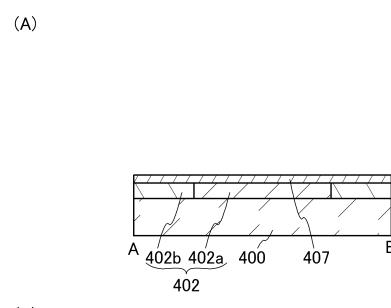

以下に図11(B)に示すトランジスタの作製方法を示す。 20

【0202】

まず、基板400を準備し、基板400上に第1の領域402aおよび第2の領域402bを有する下地絶縁膜402を形成する。第1の領域402aおよび第2の領域402bを有する下地絶縁膜402は、実施の形態2で示した下地絶縁膜202と同様の方法で形成すればよい。

【0203】

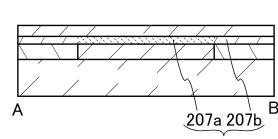

次に、下地絶縁膜402上に酸化物半導体膜407を成膜する(図12(A)参照。)。

【0204】

次に、酸化物半導体膜407上に電極416aおよび電極416bとなる導電膜を成膜し、加工して電極416aおよび電極416bを形成する(図12(B)参照。)。 30

【0205】

次に、酸化物半導体膜407、電極416aおよび電極416b上にゲート絶縁膜412を成膜する。

【0206】

次に、第1の加熱処理を行い、第3の領域406aおよび第4の領域406bを有する酸化物半導体膜406を形成する。

【0207】

第1の加熱処理は、実施の形態1で示した第1の加熱処理と同様の加熱処理とすればよい。

【0208】

ここで、酸化物半導体膜406の第3の領域406aは、下地絶縁膜402の第1の領域402aと重なる領域である。また、酸化物半導体膜406の第4の領域406bは、下地絶縁膜402の第2の領域402bと重なる領域である。これは、第1の加熱処理によつて、下地絶縁膜402から酸化物半導体膜407へ供給される酸素の量が、下地絶縁膜402の第1の領域402aおよび第2の領域402bで異なるためである。 40

【0209】

なお、下地絶縁膜402の第1の領域402aは、第1の加熱処理により、酸化物半導体膜406に供給可能な酸素をほとんど放出してしまう。そのため、下地絶縁膜402の第1の領域402aは、第1の加熱処理後にESRにてg値が2.01で信号を表さない。

一方、下地絶縁膜402の第2の領域402bは、第1の加熱処理後もESRにてg値が 50

2.01で信号を表す。

【0210】

酸化物半導体膜406の第3の領域406aは、酸化物半導体膜406の第4の領域406bよりも高抵抗化しにくい。そのため、該領域に作製したトランジスタのオン電流を高めることができる。

【0211】

次に、ゲート絶縁膜412上にゲート電極404となる導電膜を成膜し、該導電膜を加工してゲート電極404を形成する(図12(C)参照。)。

【0212】

なお、ゲート絶縁膜412の成膜後に代えて、ゲート電極404の形成後に第1の加熱処理を行ってもよい。

10

【0213】

以上の工程により、図11(B)に示すトランジスタを作製することができる。

【0214】

以上に示した工程では、下地絶縁膜402、電極416aおよび電極416b、ならびにゲート電極404のみフォトリソグラフィ工程を行えばよい。フォトリソグラフィ工程数を低減することができるため、トランジスタの作製に係るコストを大幅に低減することができる。

20

【0215】

また、本実施の形態によって得られたトランジスタは、酸素欠損が少なく、かつ水素濃度の低い酸化物半導体膜、および加熱処理により酸素を放出する下地絶縁膜を用いている。そのため、トランジスタの動作に起因する電気特性の変動が小さく、また、該トランジスタを用いた半導体装置は高い信頼性を有する。

【0216】

また、トランジスタの形成領域において、高抵抗化しにくい酸化物半導体膜の領域を形成することで、オン電流の高いトランジスタを作製することができる。

【0217】

本実施の形態は、適宜他の実施の形態と組み合わせて用いることができる。

【0218】

(実施の形態5)

30

本実施の形態では実施の形態1乃至実施の形態4のいずれかに示すトランジスタを用いて作製した液晶表示装置について説明する。なお、本実施の形態では液晶表示装置に本発明の一形態を適用した例について説明するが、これに限定されるものではない。例えば、発光装置の一つであるEL(Electro Luminescence)表示装置に本発明の一形態を適用することも、当業者であれば容易に想到しうるものである。

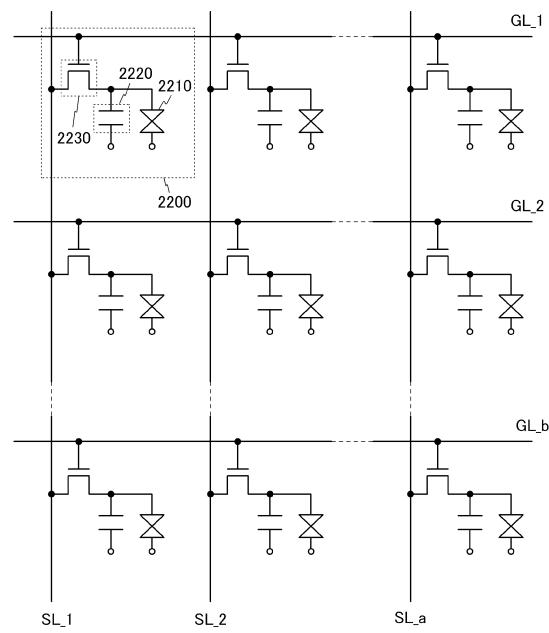

【0219】

図18にアクティブマトリクス駆動方式の液晶表示装置の回路図を示す。液晶表示装置は、ソース線SL\_1乃至SL\_a、ゲート線GL\_1乃至GL\_bおよび複数の画素2200を有する。画素2200は、トランジスタ2230と、キャパシタ2220と、液晶素子2210と、を含む。こうした画素2200が複数集まって液晶表示装置の画素部を構成する。なお、単にソース線またはゲート線を指す場合には、ソース線SLまたはゲート線GLと記載することもある。

40

【0220】

トランジスタ2230は、実施の形態1乃至実施の形態4のいずれかで示すトランジスタを用いる。実施の形態1乃至実施の形態4のいずれかで示すトランジスタは電気的特性が良好な酸化物半導体を用いたトランジスタであるため、表示品位の高い表示装置を得ることができる。

【0221】

ゲート線GLはトランジスタ2230のゲートと接続し、ソース線SLはトランジスタ2230のソースと接続し、トランジスタ2230のドレインは、キャパシタ2220の一

50

方の容量電極および液晶素子 2210 の一方の画素電極と接続する。キャパシタ 2220 の他方の容量電極および液晶素子 2210 の他方の画素電極は、共通電極と接続する。なお、共通電極はゲート線 GL と同一層で設けてもよい。

【0222】

また、ゲート線 GL は、ゲート駆動回路と接続される。ゲート駆動回路は、実施の形態 1 乃至実施の形態 4 のいずれかで示すトランジスタを含んでもよい。

【0223】

また、ソース線 SL は、ソース駆動回路と接続される。ソース駆動回路は、実施の形態 1 乃至実施の形態 4 のいずれかで示すトランジスタを含んでもよい。

【0224】

なお、ゲート駆動回路およびソース駆動回路のいずれかまたは両方を、別途用意された基板上に形成し、COG (Chip On Glass)、ワイヤボンディング、または TAB (Tape Automated Bonding)などの方法を用いてそれぞれゲート線 GL、ソース線 SL と接続してもよい。

10

【0225】

また、トランジスタは静電気などにより破壊されやすいため、保護回路を設けることが好み。保護回路は、非線形素子を用いて構成することが好み。

【0226】

ゲート線 GL にトランジスタ 2230 のしきい値電圧以上になるように電圧を印加すると、ソース線 SL から供給された電荷がトランジスタ 2230 のドレイン電流となってキャパシタ 2220 に蓄積される。1 行分の充電後、該行にあるトランジスタ 2230 はオフ状態となり、ソース線 SL から電圧が掛からなくなるが、キャパシタ 2220 に蓄積された電荷によって必要な電圧を維持することができる。その後、次の行のキャパシタ 2220 の充電に移る。このようにして、1 行から b 行の充電を行う。ドレイン電流は、トランジスタにおいてチャネルを介してドレイン - ソース間を流れる電流のことである。ドレイン電流はゲート電圧がしきい値電圧よりも大きいときに流れる。

20

【0227】

なお、トランジスタ 2230 はオフ電流が小さいため、キャパシタ 2220 に蓄積された電荷の保持時間が長くなる。そのため、動きの少ない画像（静止画を含む。）では、表示の書き換え周波数を低減でき、さらなる消費電力の低減が可能となる。また、キャパシタ 2220 の容量をさらに小さくすることが可能となるため、充電に必要な消費電力を低減することができる。

30

【0228】

また、トランジスタ 2230 はトランジスタの動作に起因する電気特性の変動が小さいため、信頼性の高い液晶表示装置を得ることができる。

【0229】

以上のように、本発明の一態様によって、表示品位が高く、消費電力の小さく、信頼性に優れる液晶表示装置を提供することができる。

【0230】

本実施の形態は、他の実施の形態と適宜組み合わせて用いることができる。

40

【0231】

（実施の形態 6）

本実施の形態では、実施の形態 1 乃至実施の形態 4 のいずれかで示すトランジスタを用いて、半導体記憶装置を作製する例について説明する。

【0232】

揮発性半導体記憶装置の代表的な例としては、記憶素子を構成するトランジスタを選択してキャパシタに電荷を蓄積することで、情報を記憶するDRAM (Dynamic Random Access Memory)、フリップフロップなどの回路を用いて記憶内容を保持するSRAM (Static Random Access Memory) がある。

50

## 【0233】

不揮発性半導体記憶装置の代表例としては、トランジスタのゲートとチャネル領域との間にフローティングゲートを有し、該フローティングゲートに電荷を保持することで記憶を行うフラッシュメモリがある。

## 【0234】

上述した半導体記憶装置に含まれるトランジスタの一部に実施の形態1乃至実施の形態4のいずれかで示すトランジスタを適用することができる。

## 【0235】

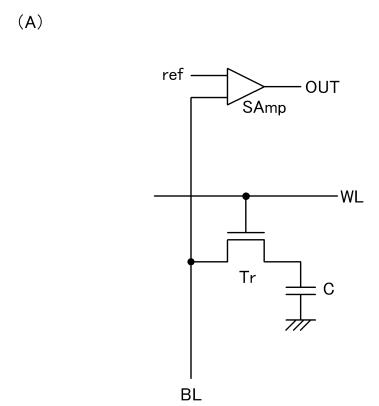

まずは、実施の形態1乃至実施の形態4のいずれかで示すトランジスタを適用した半導体記憶装置のメモリセルについて図19を用いて説明する。

10

## 【0236】

メモリセルは、トランジスタTrと、キャパシタCと、を有し、トランジスタTrのソースまたはドレインの一方はビット線BLと電気的に接続し、トランジスタTrのソースまたはドレインの他方はキャパシタCと電気的に接続し、トランジスタTrのゲートはワード線WLと電気的に接続し、ビット線BLはセンスアンプSampと電気的に接続する(図19(A)参照。)。

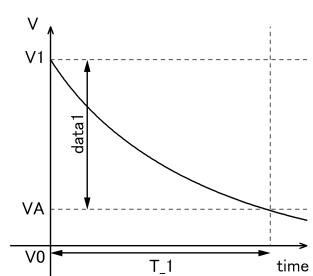

## 【0237】

キャパシタCに保持された電圧の時間変化は、トランジスタTrのオフ電流によって図19(B)に示すように徐々に低減していくことが知られている。当初V0からV1まで充電された電圧は、時間が経過するとdata1を読み出す限界点であるVAまで低減する。この期間を保持期間T\_1とする。即ち、2値メモリセルの場合、保持期間T\_1の間にリフレッシュをする必要がある。

20

## 【0238】

ここで、トランジスタTrに実施の形態1乃至実施の形態4のいずれかで示すトランジスタを適用すると、該トランジスタはオフ電流が小さいため、保持期間T\_1を長くすることができます。即ち、リフレッシュの頻度を少なくすることが可能となるため、消費電力を低減することができる。例えば、メモリセルに、オフ電流が $1 \times 10^{-21} A$ 以下、好ましくは $1 \times 10^{-24} A$ 以下となった酸化物半導体膜を用いたトランジスタを用いると、電力を供給せずに数日間から数十年間に渡ってデータを保持することが可能となる。

30

## 【0239】

また、トランジスタTrに実施の形態1乃至実施の形態4のいずれかで示すトランジスタを適用すると、該トランジスタはトランジスタの動作に起因する電気特性の変動が小さいため、信頼性の高い半導体記憶装置のメモリセルを得ることができる。

## 【0240】

以上のように、本発明の一態様によって、信頼性が高く、消費電力の小さい半導体記憶装置を得ることができる。

## 【0241】

次に、上述した半導体記憶装置とは異なる構成の、実施の形態1乃至実施の形態4のいずれかで示すトランジスタを適用した半導体記憶装置のメモリセルについて図20を用いて説明する。

40

## 【0242】

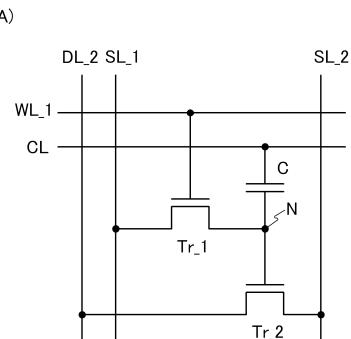

図20(A)は、メモリセルの回路図である。メモリセルは、トランジスタTr\_1と、トランジスタTr\_2と、キャパシタCと、を有し、トランジスタTr\_1のゲートはワード線WL\_1と電気的に接続し、トランジスタTr\_1のソースはソース線SL\_1と電気的に接続し、トランジスタTr\_2のソースはソース線SL\_2と電気的に接続し、トランジスタTr\_2のドレインはドレイン線DL\_2と電気的に接続し、キャパシタCの一端は容量線CLと電気的に接続し、キャパシタCの他端、トランジスタTr\_1のドレインおよびトランジスタTr\_2のゲートはノードNと電気的に接続する。

## 【0243】

なお、該メモリセルは、ノードNの電位に応じて、トランジスタTr\_2の見た目のしき

50

い値電圧が変動することを利用することでデータを記憶できる。例えば、図20(B)は容量線CLの電圧 $V_{CL}$ と、トランジスタTr\_2を流れるドレイン電流 $I_{d_2}$ との関係を説明する図である。

【0244】

ここで、ノードNは、トランジスタTr\_1を介して電圧を調整することができる。例えば、ソース線SL\_1の電位をVDDとする。このとき、ワード線WL\_1の電位をトランジスタTr\_1のしきい値電圧 $V_{th}$ にVDDを加えた電位以上とすることで、ノードNの電位をHIGHにすることができる。また、ワード線WL\_1の電位をトランジスタTr\_1のしきい値電圧 $V_{th}$ 以下とすることで、ノードNの電位をLOWにすることができる。

10

【0245】

そのため、 $N = LOW$ で示した $V_{CL} - I_{d_2}$ カーブと、 $N = HIGH$ で示した $V_{CL} - I_{d_2}$ カーブのいずれかを得ることができる。即ち、 $N = LOW$ では、 $V_{CL} = 0V$ にて $I_{d_2}$ が小さいため、データ0となる。また、 $N = HIGH$ では、 $V_{CL} = 0V$ にて $I_{d_2}$ が大きいため、データ1となる。このようにして、データを記憶することができる。

【0246】

ここで、トランジスタTr\_1に実施の形態1乃至実施の形態4のいずれかで示すトランジスタを適用すると、該トランジスタはオフ電流を小さくすることができるため、ノードNに蓄積された電荷がトランジスタTr\_1のソースおよびドレイン間を意図せずにリークすることを抑制できる。そのため、長期間に渡ってデータを保持することができる。

20

【0247】

また、トランジスタTr\_1に実施の形態1乃至実施の形態4のいずれかで示すトランジスタを適用すると、該トランジスタはトランジスタの動作に起因する電気特性の変動が小さいため、信頼性の高い半導体記憶装置を得ることができる。

【0248】

なお、トランジスタTr\_2に、実施の形態1乃至実施の形態4のいずれかで示すトランジスタを適用しても構わない。

【0249】

以上のように、本発明の一態様によって、長期間の信頼性が高く、消費電力の小さい半導体記憶装置を得ることができる。

30

【0250】

本実施の形態は、他の実施の形態と適宜組み合わせて用いることができる。

【0251】

(実施の形態7)

実施の形態1乃至実施の形態4のいずれかで示すトランジスタまたは実施の形態6に示した半導体記憶装置を少なくとも一部に用いてCPU(Central Processing Unit)を構成することができる。

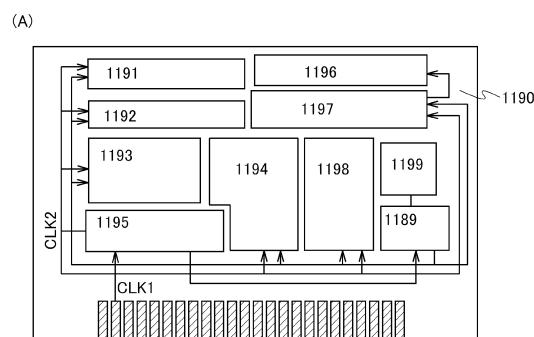

【0252】

図21(A)は、CPUの具体的な構成を示すブロック図である。図21(A)に示すCPUは、基板1190上に、演算論理装置(ALU: Arithmetic logic unit)1191、ALUコントローラ1192、インストラクションデコーダ1193、インタラプトコントローラ1194、タイミングコントローラ1195、レジスタ1196、レジスタコントローラ1197、バスインターフェース(Bus I/F)1198、書き換え可能なROM1199、およびROMインターフェース(ROM I/F)1189を有している。基板1190は、半導体基板、SOI基板、ガラス基板などを用いる。ROM1199およびROMインターフェース1189は、別チップに設けてもよい。もちろん、図21(A)に示すCPUは、その構成を簡略化して示した一例にすぎず、実際のCPUはその用途によって多種多様な構成を有している。

40

【0253】

50

バスインターフェース 1198 を介して C P U に入力された命令は、インストラクションデコーダ 1193 に入力され、デコードされた後、A L U コントローラ 1192、インタラプトコントローラ 1194、レジスタコントローラ 1197、タイミングコントローラ 1195 に入力される。

【 0254 】

A L U コントローラ 1192、インタラプトコントローラ 1194、レジスタコントローラ 1197、タイミングコントローラ 1195 は、デコードされた命令に基づき、各種制御を行う。具体的に A L U コントローラ 1192 は、A L U 1191 の動作を制御するための信号を生成する。また、インタラプトコントローラ 1194 は、C P U のプログラム実行中に、外部の入出力装置や、周辺回路からの割り込み要求を、その優先度やマスク状態から判断し、処理する。レジスタコントローラ 1197 は、レジスタ 1196 のアドレスを生成し、C P U の状態に応じてレジスタ 1196 の読み出しや書き込みを行う。

10

【 0255 】

また、タイミングコントローラ 1195 は、A L U 1191、A L U コントローラ 1192、インストラクションデコーダ 1193、インタラプトコントローラ 1194、およびレジスタコントローラ 1197 の動作のタイミングを制御する信号を生成する。例えばタイミングコントローラ 1195 は、基準クロック信号 C L K 1 を元に、内部クロック信号 C L K 2 を生成する内部クロック生成部を備えており、クロック信号 C L K 2 を上記各種回路に供給する。

20

【 0256 】

図 21 ( A ) に示す C P U では、レジスタ 1196 に、記憶素子が設けられている。レジスタ 1196 の記憶素子には、実施の形態 6 に示す半導体記憶装置を用いることができる。

【 0257 】

図 21 ( A ) に示す C P U において、レジスタコントローラ 1197 は、A L U 1191 からの指示に従い、レジスタ 1196 における保持動作を行う。即ち、レジスタ 1196 が有する記憶素子において、フリップフロップによるデータの保持を行うか、キャパシタによるデータの保持を行う。フリップフロップによってデータが保持されている場合、レジスタ 1196 内の記憶素子への、電源電圧の供給が行われる。キャパシタによってデータが保持されている場合、キャパシタへのデータの書き換えが行われ、レジスタ 1196 内の記憶素子への電源電圧の供給を停止することができる。

30

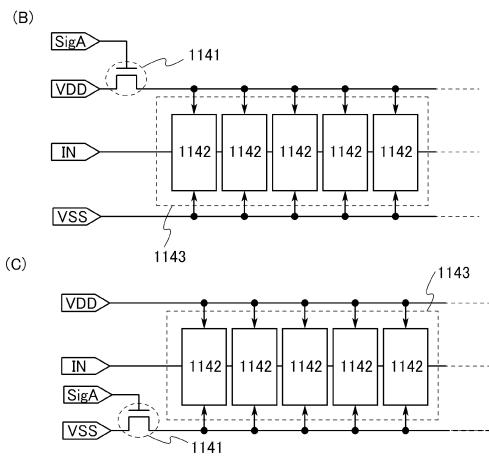

【 0258 】

電源停止に関しては、図 21 ( B ) または図 21 ( C ) に示すように、記憶素子群と、電源電位 V D D または電源電位 V S S の与えられているノード間に、スイッチング素子を設けることにより行うことができる。以下に図 21 ( B ) および図 21 ( C ) の回路の説明を行う。

【 0259 】

図 21 ( B ) および図 21 ( C ) では、記憶素子への電源電圧の供給を制御するスイッチング素子に実施の形態 1 乃至実施の形態 4 のいずれかに示すトランジスタを用いた構成の一例を示す。

40

【 0260 】

図 21 ( B ) に示す記憶装置は、スイッチング素子 1141 と、記憶素子 1142 を複数有する記憶素子群 1143 とを有している。具体的に、それぞれの記憶素子 1142 には、実施の形態 6 に示す記憶素子を用いることができる。記憶素子群 1143 が有するそれぞれの記憶素子 1142 には、スイッチング素子 1141 を介して、ハイレベルの電源電位 V D D が供給されている。さらに、記憶素子群 1143 が有するそれぞれの記憶素子 1142 には、信号 I N の電位と、ローレベルの電源電位 V S S の電位が与えられている。

【 0261 】

図 21 ( B ) では、スイッチング素子 1141 として、実施の形態 1 乃至実施の形態 4 のいずれかに示すトランジスタを用いており、該トランジスタは、そのゲートに与えられる

50

信号 Sig A によりスイッチングが制御される。

【0262】

なお、図21(B)では、スイッチング素子1141がトランジスタを一つだけ有する構成を示しているが、これに限定されず、トランジスタを複数有していてもよい。スイッチング素子1141が、スイッチング素子として機能するトランジスタを複数有している場合、上記複数のトランジスタは並列に接続されてもよいし、直列に接続されてもよいし、直列と並列が組み合わされて接続されてもよい。

【0263】

また、図21(C)には、記憶素子群1143が有するそれぞれの記憶素子1142に、スイッチング素子1141を介して、ローレベルの電源電位VSSが供給されている、記憶装置の一例を示す。スイッチング素子1141により、記憶素子群1143が有するそれぞれの記憶素子1142への、ローレベルの電源電位VSSの供給を制御することができる。

10

【0264】

記憶素子群と、電源電位VDDまたは電源電位VSSの与えられているノード間に、スイッチング素子を設け、一時的にCPUの動作を停止し、電源電圧の供給を停止した場合においてもデータを保持することが可能であり、消費電力の低減を行うことができる。例えば、パーソナルコンピュータのユーザーが、キーボードなどの入力装置への情報の入力を停止している間でも、CPUの動作を停止することができ、それにより消費電力を低減することができる。

20

【0265】

ここでは、CPUを例に挙げて説明したが、DSP(Digital Signal Processor)、カスタムLSI、FPGA(Field Programmable Gate Array)などのLSIにも応用可能である。

【0266】

本実施の形態は、上記実施の形態と適宜組み合わせて実施することができる。

【0267】

(実施の形態8)

本実施の形態では、実施の形態1乃至実施の形態7を適用した電子機器の例について説明する。

30

【0268】

図22(A)は携帯型情報端末である。図22(A)に示す携帯型情報端末は、筐体9300と、ボタン9301と、マイクロフォン9302と、表示部9303と、スピーカ9304と、カメラ9305と、を具備し、携帯型電話機としての機能を有する。表示部9303およびカメラ9305に他の実施の形態を適用することができる。また、図示しないが、本体内部にある演算装置、無線回路または記憶回路に他の実施の形態を適用することもできる。

【0269】

図22(B)は、ディスプレイである。図22(B)に示すディスプレイは、筐体9310と、表示部9311と、を具備する。表示部9311に他の実施の形態を適用することができる。その結果、表示部9311のサイズを大きくしたときにも表示品位の高く、信頼性の高いディスプレイとすることができます。

40

【0270】

図22(C)は、デジタルスチルカメラである。図22(C)に示すデジタルスチルカメラは、筐体9320と、ボタン9321と、マイクロフォン9322と、表示部9323と、を具備する。表示部9323に他の実施の形態を適用することができる。また、図示しないが、記憶回路またはイメージセンサに他の実施の形態を適用することもできる。

【0271】

図22(D)は2つ折り可能な携帯型情報端末である。図22(D)に示す2つ折り可能な携帯型情報端末は、筐体9630、表示部9631a、表示部9631b、留め具96

50

33、操作スイッチ9638、を有する。表示部9631aおよび表示部9631bに他の実施の形態を適用することができる。また、図示しないが、本体内部にある演算装置、無線回路または記憶回路に他の実施の形態を適用することもできる。

【0272】

なお、表示部9631aまたは/および表示部9631bは、一部または全部をタッチパネルとすることができます、表示された操作キーに触れることでデータ入力などを行うことができる。

【0273】

従って、本発明の一態様に係る電子機器は、性能が高く、信頼性の高い電子機器である。

【0274】

本実施の形態は、他の実施の形態と適宜組み合わせて用いることができる。

10

【実施例1】

【0275】

本実施例では、ESRを用い、酸化物半導体膜および下地絶縁膜を有する試料のスピノ評価を行った。

【0276】

なお、ESRは、日本電子株式会社製電子スピノ共鳴装置JES-F A 300を用いた。

【0277】

以下に試料の作製方法を示す。

【0278】

20

まず、石英基板を準備し、石英基板上に下地絶縁膜を成膜した。下地絶縁膜は、酸化アルミニウム膜または酸化シリコン膜とした。

【0279】

酸化アルミニウム膜は、スパッタリング法により成膜した。具体的には、酸化アルミニウムターゲットを用い、アルゴンを25sccmおよび酸素を25sccm含む雰囲気において、圧力を0.4Paに制御し、成膜時の基板加熱温度を250、成膜電力を2.5kW(13.56MHz)として300nmの厚さで成膜した。

【0280】

酸化シリコン膜は、スパッタリング法により成膜した。具体的には、酸化シリコンターゲットを用い、アルゴンを25sccmおよび酸素を25sccm含む雰囲気において、圧力を0.4Paに制御し、成膜時の基板加熱温度を100、成膜電力を5kW(13.56MHz)として300nmの厚さで成膜した。

30

【0281】

次に、下地絶縁膜上に酸化物半導体膜を成膜した。

【0282】

酸化物半導体膜は、スパッタリング法により成膜した。具体的には、In-Ga-Zn-O( In : Ga : Zn = 1 : 1 : 1 [原子数比] )ターゲットを用い、酸素を45sccm含む雰囲気において、圧力を0.4Paに制御し、成膜時の基板加熱温度を400、成膜電力を500W(DC)として100nmの厚さで成膜した。

【0283】

40

次に、窒素ガス雰囲気において、450の温度で1時間、第1の加熱処理を行った。

【0284】

次に、酸化物半導体膜上に保護絶縁膜を成膜した。

【0285】

保護絶縁膜は、プラズマCVD法により成膜した。具体的にはモノシランを1sccmおよび亜酸化窒素を800sccm含む雰囲気において、圧力を40Paに制御し、成膜時の基板加熱温度を400、電極に150W(60MHz)を印加して100nmの厚さで成膜した。

【0286】

次に、各基板を3mm×20mmのサイズに分割した。

50

## 【0287】

次に、分割した基板を窒素ガス雰囲気において、1時間の第2の加熱処理を行った。第2の加熱処理は、250、300、350、400、450、500、550または600の温度で行った。

## 【0288】

次に、各試料を2枚重ねてESRを評価した。なお、ESRは、室温にて行い、マイクロ波電力を20mW(9.2GHz)とした。また、磁場の向きが基板表面と平行となるように各試料を設置した。

## 【0289】

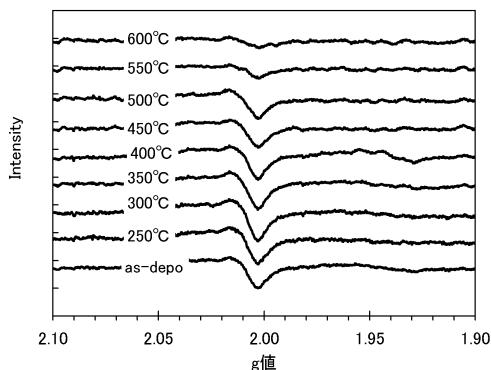

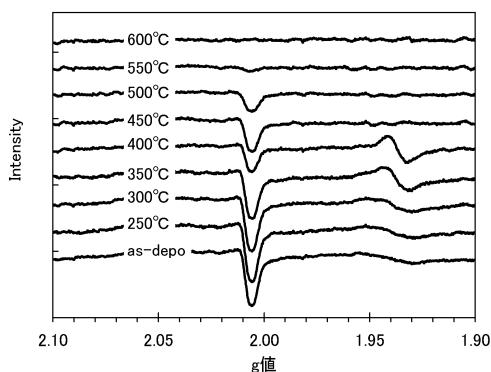

結果を図13に示す。ここで、図13(A)は、下地絶縁膜として酸化アルミニウム膜を用いた試料のESRスペクトルを示す。また、図13(B)は、下地絶縁膜として酸化シリコン膜を用いた試料のESRスペクトルを示す。なお、図13中のESRスペクトルに付した温度は、第2の加熱処理の温度を示す。また、図13中のESRスペクトルに付したas-depoの表記は、第2の加熱処理を行っていないことを示す。

10

## 【0290】

図13において、g値が2.01で表される信号に着目する。図13(A)より、下地絶縁膜に酸化アルミニウム膜を用いた試料では、第2の加熱処理の温度を高めるに従い、該信号に相当する спинのスピンドル密度が低減していった。また、第2の加熱処理を600で行った試料においても、該信号を表した。また、図13(B)より、下地絶縁膜に酸化シリコン膜を用いた試料でも、第2の加熱処理の温度を高めるに従い、該信号に相当するスピンドル密度が低減していった。ところが、第2の加熱処理を550または600で行った試料においては、該信号が消失したか、極めて小さくなつた。なお、g値が2.01で表される信号に相当するスピンドル密度を定量した値を下記表1に示す。

20

## 【0291】

## 【表1】

| 加熱処理温度 [°C] | スピンドル密度 [spins/cm <sup>3</sup> ] |         |

|-------------|----------------------------------|---------|

|             | 酸化アルミニウム膜                        | 酸化シリコン膜 |

| 処理なし        | 2.1E+18                          | 4.3E+18 |

| 250         | 1.9E+18                          | 6.6E+18 |

| 300         | 2.7E+18                          | 5.0E+18 |

| 350         | 2.0E+18                          | 4.4E+18 |

| 400         | 2.2E+18                          | 7.6E+17 |

| 450         | 2.0E+18                          | 8.0E+17 |

| 500         | 1.8E+18                          | 7.9E+17 |

| 550         | 1.1E+18                          | 測定不可    |

| 600         | 1.1E+18                          | 測定不可    |

30

## 【0292】

上記表1より、下地絶縁膜に酸化アルミニウム膜を用いた試料では、600以下の加熱処理後もg値が2.01で表される信号に相当するスピンドル密度が $1 \times 10^{18}$ spins/cm<sup>3</sup>以上であることがわかった。

40

## 【0293】

同様に、図13において、g値が1.93で表される信号に着目する。図13(A)より、下地絶縁膜に酸化アルミニウム膜を用いた試料では、as-depoおよび第2の加熱処理が400の試料において、該信号が確認された。そのほかの試料では、該信号は確認されなかった。一方、図13(B)より、下地絶縁膜に酸化シリコン膜を用いた試料でも、as-depoおよび第2の加熱処理が250乃至400の試料において、該信号が確認された。そのほかの試料では、該信号は確認されなかった。

## 【0294】

以上に示すように、下地絶縁膜に酸化アルミニウム膜を用いた試料のESRスペクトルにおいて、下地絶縁膜および保護絶縁膜で酸化物半導体膜を挟み、250乃至600の

50

範囲にあるいづれかの温度で加熱処理を行った試料で、g値が2.01で信号を表した。また、as-depoおよび該加熱処理の温度が400の試料を除き、g値が1.93で信号を表さなかった。

【0295】

一方、下地絶縁膜に酸化シリコン膜を用いた試料のESRスペクトルにおいて、下地絶縁膜および保護絶縁膜で酸化物半導体膜を挟み、250乃至500の範囲にあるいづれかの温度で加熱処理を行った試料で、g値が2.01で信号を表した。ところが、該加熱処理の温度が550または600のときは、g値が2.01で信号を表さなかった。また、as-depoおよび該加熱処理の温度が250乃至400の試料を除き、g値が1.93で信号を表さなかった。

10

【0296】

本実施例より、下地絶縁膜が酸化アルミニウム膜のとき、下地絶縁膜上に設けられた酸化物半導体膜は450乃至600のいづれかの温度で加熱処理後に、ESRにてg値が1.93で信号を表さず、かつ下地絶縁膜は該加熱処理後もg値が2.01で信号を表すことがわかる。

【0297】

一方、下地絶縁膜が酸化シリコン膜のとき、下地絶縁膜上に設けられた酸化物半導体膜は450または500の温度で加熱処理後に、ESRにてg値が1.93で信号を表さず、かつ下地絶縁膜は該加熱処理後もg値が2.01で信号を表すことがわかる。また、550または600の温度で加熱処理後に、ESRにてg値が1.93で信号を表さず、かつ下地絶縁膜は該加熱処理後もg値が2.01で信号を表さないことがわかる。

20

【実施例2】

【0298】

本実施例では、TDSを用い、絶縁膜を有する試料の放出ガスの評価を行った。

【0299】

放出ガスの評価は、電子科学株式会社製の昇温脱離分析装置EMD-WA1000S/Wを用いた。

【0300】

以下に試料の作製方法を示す。

【0301】

30

まず、シリコンウェハを準備し、シリコンウェハ上に熱酸化膜を成膜した。熱酸化膜の成膜は、3%HClを含む酸素雰囲気にて、950の温度で行い、厚さは100nmとした。

【0302】

次に、熱酸化膜上に絶縁膜として、酸化アルミニウム膜または酸化シリコン膜を成膜した。

【0303】

酸化アルミニウム膜は、スパッタリング法により成膜した。具体的には、酸化アルミニウムターゲットを用い、アルゴンを25sccmおよび酸素を25sccm含む雰囲気において、圧力を0.4Paに制御し、成膜時の基板加熱温度を250、成膜電力を2.5kW(13.56MHz)として100nmの厚さで成膜した。

40

【0304】

酸化シリコン膜は、スパッタリング法により成膜した。具体的には、酸化シリコンターゲットを用い、酸素を50sccm含む雰囲気において、圧力を0.4Paに制御し、成膜時の基板加熱温度を100、成膜電力を2kW(13.56MHz)として300nmの厚さで成膜した。

【0305】

次に、各試料の放出ガスの量を評価した。

【0306】

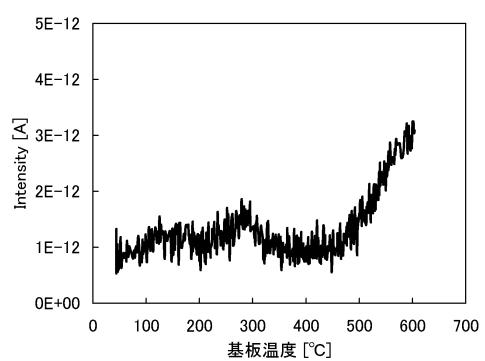

TDSによるM/zが32であるガスのイオン強度を図14に示す。ここで、図14(A

50

) は、絶縁膜として酸化アルミニウム膜を用いた試料の、TDS による放出ガスのイオン強度を示す。また、図14 (B) は、絶縁膜として酸化シリコン膜を用いた試料のTDS による放出ガスのイオン強度を示す。

【0307】

図14 (A) に示す、絶縁膜に酸化アルミニウム膜を用いた試料の、TDS による放出ガスのイオン強度より、基板温度が450 以上でM/z が32 であるガスの放出が確認された。測定の都合上、基板温度が600 以上での放出ガスの評価を行うことができないが、M/z が32 であるガスの放出量がもっとも高くなる温度は600 よりも高いことが予測される。

【0308】

一方、図14 (B) に示す、絶縁膜に酸化シリコン膜を用いた試料の、TDS による放出ガスのイオン強度より、基板温度が100 以上500 以下でM/z が32 であるガスの放出が確認された。なお、放出量を酸素原子に換算すると $5.0 \times 10^{20}$  atoms/cm<sup>3</sup> であった。測定の都合上、基板温度が600 以上での放出ガスの評価を行うことができないが、少なくともM/z が32 であるガスの放出は、基板温度が500 以上600 以下の範囲ではほとんど生じないことがわかる。

【0309】

本実施例より、酸化アルミニウム膜は、酸素の放出温度が酸化シリコン膜よりも高いことがわかった。そのため、450 以上の温度で加熱処理を行っても、放出可能な酸素が十分残存することがわかる。

【0310】

また、酸化シリコン膜は、450 以上の温度で加熱処理を行うことで、放出可能な酸素がほとんど失われてしまうことがわかる。

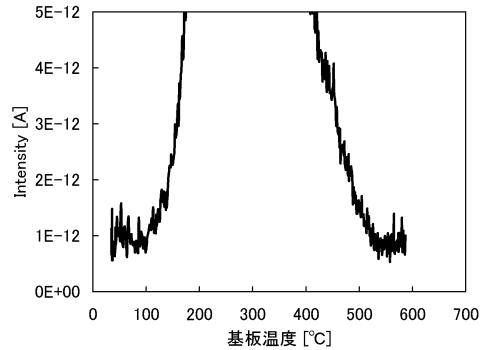

【0311】

次に、TDS によるM/z が2 であるガスのイオン強度を図15 に示す。ここで、図15 (A) は、絶縁膜として酸化アルミニウム膜を用いた試料の、TDS による放出ガスのイオン強度を示す。また、図15 (B) は、絶縁膜として酸化シリコン膜を用いた試料の、TDS による放出ガスのイオン強度を示す。

【0312】

図15 (A) に示す、絶縁膜に酸化アルミニウム膜を用いた試料の、TDS による放出ガスのイオン強度より、基板温度が320 および410 で、M/z が2 であるガスの放出量の極大値が確認された。測定の都合上、基板温度が600 以上での放出ガスの評価を行うことができないが、M/z が2 の放出量は基板温度が高いほど増大していくことが予測される。

【0313】

一方、図15 (B) に示す、絶縁膜に酸化シリコン膜を用いた試料のTDS による放出ガスのイオン強度より、基板温度が350 に、M/z が2 であるガスの放出量の極大値が確認された。また、測定の都合上、基板温度が600 以上での放出ガスの評価を行うことができないが、M/z が2 であるガスの放出量は基板温度が高いほど増大していくと予測される。

【0314】

本実施例より、酸化アルミニウム膜は、酸素の放出温度が酸化シリコン膜よりも高いことがわかった。そのため、450 以上の温度で加熱処理を行っても、放出可能な酸素が十分残存することがわかる。

【0315】

また、酸化シリコン膜は、450 以上の温度で加熱処理を行うことで、放出可能な酸素がほとんど失われてしまうことがわかる。

【0316】

また、下地絶縁膜からの水素の放出量の極大値となる温度を越える温度、例えば350 以上、好ましくは450 以上、さらに好ましくは500 以上で加熱処理を行うことで

10

20

30

40

50

、下地絶縁膜から効果的に水素を放出させられることがわかる。

【実施例 3】

【0317】

本実施例では、下地絶縁膜および保護絶縁膜に挟まれた酸化物半導体膜の比抵抗率、キャリア密度およびホール (Hall) 移動度を、ホール効果測定により評価した。

【0318】

ホール効果測定は、株式会社東陽テクニカ製 Resist 8300 シリーズを用いた。

【0319】

以下に試料の作製方法を示す。

10

【0320】

まず、ガラス基板を準備し、ガラス基板上に下地絶縁膜を成膜した。下地絶縁膜は、酸化アルミニウム膜または酸化シリコン膜とした。

【0321】

酸化アルミニウム膜は、スパッタリング法により成膜した。具体的には、酸化アルミニウムターゲットを用い、アルゴンを 25 sccm および酸素を 25 sccm 含む雰囲気において、圧力を 0.4 Pa に制御し、成膜時の基板加熱温度を 250 、成膜電力を 2.5 kW (13.56 MHz) として 100 nm の厚さで成膜した。

【0322】

酸化シリコン膜は、スパッタリング法により成膜した。具体的には、酸化シリコンターゲットを用い、アルゴンを 25 sccm および酸素を 25 sccm 含む雰囲気において、圧力を 0.4 Pa に制御し、成膜時の基板加熱温度を 100 、成膜電力を 5 kW (13.56 MHz) として 300 nm の厚さで成膜した。

20

【0323】

次に、下地絶縁膜上に酸化物半導体膜を成膜した。

【0324】

酸化物半導体膜は、スパッタリング法により成膜した。具体的には、In-Ga-Zn-O (In:Ga:Zn = 1:1:1 [原子数比]) ターゲットを用い、酸素を 45 sccm 含む雰囲気において、圧力を 0.4 Pa に制御し、成膜時の基板加熱温度を 400 、成膜電力を 500 W (DC) として 30 nm の厚さで成膜した。

30

【0325】

次に、窒素ガス雰囲気において、450 の温度で 1 時間、第 1 の加熱処理を行った。

【0326】

次に、ホール効果測定用の四端子電極として直径 1 mm の円状の電極 (Ti) を 4 つ形成した。なお、各電極は正方形状に配置し、その中心と中心との間隔を 8 mm とした。

【0327】

次に、電極および酸化物半導体膜上に保護絶縁膜を成膜した。

【0328】

保護絶縁膜は、プラズマ CVD 法により成膜した。具体的にはモノシランを 1 sccm および亜酸化窒素を 800 sccm 含む雰囲気において、圧力を 40 Pa に制御し、成膜時の基板加熱温度を 400 、電極に 150 W (60 MHz) を印加して 100 nm の厚さで成膜した。

40

【0329】

次に、保護絶縁膜を加工し、各電極のみを露出する開口部を形成した。

【0330】

次に、4 つの電極が入るよう、各基板を 10 mm × 10 mm のサイズに分割した。

【0331】

次に、分割した基板を窒素ガス雰囲気において、1 時間の第 2 の加熱処理を行った。第 2 の加熱処理は、250 、 300 、 350 、 400 、 450 、 500 、 550 または 600 の温度で行った。

50

## 【0332】

次に、各試料の比抵抗率、キャリア密度およびホール移動度を評価した。

## 【0333】

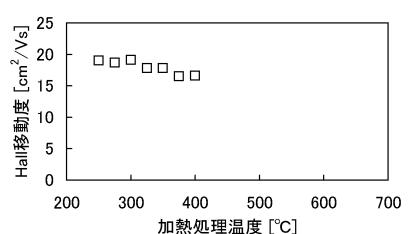

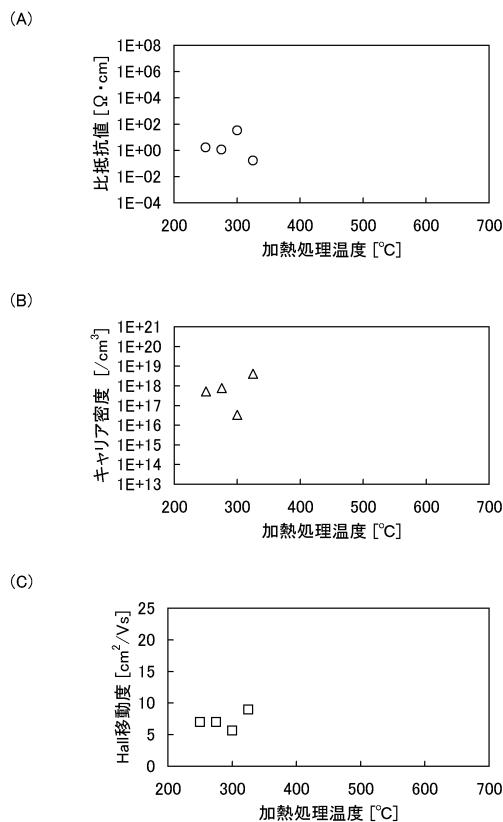

結果を図16および図17に示す。

## 【0334】

ここで、図16は、下地絶縁膜として酸化アルミニウム膜を用いた試料のホール効果測定結果を示す。なお、図16(A)は第2の加熱処理の温度と比抵抗値との関係を示し、図16(B)は第2の加熱処理の温度とキャリア密度との関係を示し、図16(C)は第2の加熱処理の温度とホール移動度との関係を示す。

## 【0335】

図16(A)より、第2の加熱処理が400を超えたところから急激に比抵抗値が増大した。また、第2の加熱処理が450以上では、ホール効果測定の測定限界である比抵抗値が3k $\cdot$ cm以上であることがわかった。

## 【0336】

なお、図16(B)および図16(C)より、第2の加熱処理の温度を高めると、ホール移動度は大きく変化せず、キャリア密度が著しく低下していることがわかった。

## 【0337】

酸化物半導体膜のキャリア発生源は水素および酸素欠損であるため、第2の加熱処理を400以上で行うことで、酸化物半導体膜の水素および/または酸素欠損を低減することができたといえる。

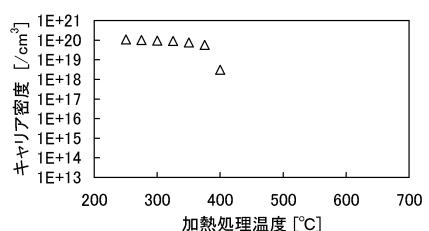

## 【0338】

次に、図17は、下地絶縁膜として酸化シリコン膜を用いた試料のホール効果測定結果を示す。なお、図17(A)は第2の加熱処理の温度と比抵抗値との関係を示し、図17(B)は第2の加熱処理の温度とキャリア密度との関係を示し、図17(C)は第2の加熱処理の温度とホール移動度との関係を示す。

## 【0339】

図17(A)より、第2の加熱処理が350以上では、ホール効果測定の測定限界である比抵抗値が3k $\cdot$ cm以上であることがわかった。

## 【0340】

酸化物半導体膜のキャリア発生源は水素および酸素欠損であるから、第2の加熱処理を350以上で行うことで、酸化物半導体膜の水素および/または酸素欠損を低減することができたといえる。

## 【0341】

実施例2によれば、酸化シリコン膜は酸化アルミニウム膜よりも低い温度で酸素を放出する。実施例3の結果を鑑みれば、下地絶縁膜からの酸素の放出と酸化物半導体膜の比抵抗値の増大(キャリア密度の低減)に関連があることは明らかである。

## 【0342】

また、実施例1および実施例2より、下地絶縁膜から酸素が放出可能な試料では、ESRにてg値が2.01で信号を表すことも明らかである。

## 【0343】

従って、酸化物半導体膜のキャリア密度を低減させるためには、下地絶縁膜としてESRにてg値が2.01で信号を表す絶縁膜を用いて、酸化物半導体膜の酸素欠損を低減させることができがほしい。ただし、酸化物半導体膜のもう一つのキャリア発生源である下地絶縁膜の水素濃度を低減させるには、450以上での加熱処理が有効であるため、450以上の加熱処理後も、加熱処理によって放出する酸素が残存する下地絶縁膜の形成が重要であることがわかる。

## 【符号の説明】

## 【0344】

100 基板

102 下地絶縁膜

10

20

30

40

50

|         |         |    |

|---------|---------|----|

| 1 0 4   | ゲート電極   |    |

| 1 0 6   | 酸化物半導体膜 |    |

| 1 0 6 a | 第1の領域   |    |

| 1 0 6 b | 第2の領域   |    |

| 1 0 6 c | 第3の領域   |    |

| 1 1 2   | ゲート絶縁膜  |    |

| 1 1 3   | ゲート絶縁膜  |    |

| 1 1 6 a | 配線      |    |

| 1 1 6 b | 配線      |    |

| 1 1 8   | 層間絶縁膜   | 10 |

| 1 3 6   | 酸化物半導体膜 |    |

| 1 3 7   | 酸化物半導体膜 |    |

| 2 0 0   | 基板      |    |

| 2 0 2   | 下地絶縁膜   |    |

| 2 0 2 a | 第1の領域   |    |

| 2 0 2 b | 第2の領域   |    |

| 2 0 3 a | 絶縁膜     |    |

| 2 0 3 b | 絶縁膜     |    |

| 2 0 4   | ゲート電極   |    |

| 2 0 6   | 酸化物半導体膜 | 20 |

| 2 0 6 a | 第3の領域   |    |

| 2 0 6 b | 第4の領域   |    |

| 2 0 6 c | 第5の領域   |    |

| 2 0 6 d | 第6の領域   |    |

| 2 0 7   | 酸化物半導体膜 |    |

| 2 0 7 a | 第3の領域   |    |

| 2 0 7 b | 第4の領域   |    |

| 2 1 2   | ゲート絶縁膜  |    |

| 2 1 3   | ゲート絶縁膜  |    |

| 2 1 6 a | 配線      | 30 |

| 2 1 6 b | 配線      |    |

| 2 1 8   | 層間絶縁膜   |    |

| 2 3 7   | 酸化物半導体膜 |    |

| 3 0 0   | 基板      |    |

| 3 0 2   | 下地絶縁膜   |    |

| 3 0 4   | ゲート電極   |    |

| 3 0 6   | 酸化物半導体膜 |    |

| 3 0 7   | 酸化物半導体膜 |    |

| 3 1 2   | ゲート絶縁膜  |    |

| 3 1 6 a | 電極      | 40 |

| 3 1 6 b | 電極      |    |

| 4 0 0   | 基板      |    |

| 4 0 2   | 下地絶縁膜   |    |

| 4 0 2 a | 第1の領域   |    |

| 4 0 2 b | 第2の領域   |    |

| 4 0 4   | ゲート電極   |    |

| 4 0 6   | 酸化物半導体膜 |    |

| 4 0 6 a | 第3の領域   |    |

| 4 0 6 b | 第4の領域   |    |

| 4 0 7   | 酸化物半導体膜 | 50 |

|           |               |    |

|-----------|---------------|----|

| 4 1 2     | ゲート絶縁膜        |    |

| 4 1 6 a   | 電極            |    |

| 4 1 6 b   | 電極            |    |

| 1 1 4 1   | スイッチング素子      |    |

| 1 1 4 2   | 記憶素子          |    |

| 1 1 4 3   | 記憶素子群         |    |

| 1 1 8 9   | ROMインターフェース   |    |

| 1 1 9 0   | 基板            |    |

| 1 1 9 1   | ALU           |    |

| 1 1 9 2   | ALUコントローラ     | 10 |

| 1 1 9 3   | インストラクションデコーダ |    |

| 1 1 9 4   | インターラプトコントローラ |    |

| 1 1 9 5   | タイミングコントローラ   |    |

| 1 1 9 6   | レジスタ          |    |

| 1 1 9 7   | レジスタコントローラ    |    |

| 1 1 9 8   | バスインターフェース    |    |

| 1 1 9 9   | ROM           |    |

| 2 2 0 0   | 画素            |    |

| 2 2 1 0   | 液晶素子          |    |

| 2 2 2 0   | キャパシタ         | 20 |

| 2 2 3 0   | トランジスタ        |    |

| 9 3 0 0   | 筐体            |    |

| 9 3 0 1   | ボタン           |    |

| 9 3 0 2   | マイクロフォン       |    |

| 9 3 0 3   | 表示部           |    |

| 9 3 0 4   | スピーカ          |    |

| 9 3 0 5   | カメラ           |    |

| 9 3 1 0   | 筐体            |    |

| 9 3 1 1   | 表示部           |    |

| 9 3 2 0   | 筐体            | 30 |

| 9 3 2 1   | ボタン           |    |

| 9 3 2 2   | マイクロフォン       |    |

| 9 3 2 3   | 表示部           |    |

| 9 6 3 0   | 筐体            |    |

| 9 6 3 1 a | 表示部           |    |

| 9 6 3 1 b | 表示部           |    |

| 9 6 3 3   | 留め具           |    |

| 9 6 3 8   | 操作スイッチ        |    |

【図1】

【図2】

【図3】

【図4】

【図5】

(A)

(B)

(C)

【図6】

(A)

(B)

(C)

【図7】

(A)

(B)

(C)

【図8】

(A)

(B)

(C)

【図9】

【図10】

【図11】

【図12】

(B)

【図13】

(A)

(B)

【図14】

(A)

(B)

【図15】

(A)

(B)

【図16】

(A)

(B)

(C)

【図17】

【図18】

【図19】

(B)

【図20】

(B)

【図21】

【図22】

---

フロントページの続き

| (51)Int.Cl.              | F I                  |

|--------------------------|----------------------|

| H 01 L 21/8244 (2006.01) | H 01 L 27/10 3 8 1   |

| H 01 L 27/11 (2006.01)   | H 01 L 27/10 4 4 1   |

| H 01 L 27/105 (2006.01)  | H 01 L 27/10 6 7 1 C |

| H 01 L 29/788 (2006.01)  | H 01 L 27/10 6 7 1 Z |

| H 01 L 29/792 (2006.01)  | H 01 L 29/78 3 7 1   |

| G 02 F 1/1368 (2006.01)  | G 02 F 1/1368        |

審査官 竹口 泰裕

(56)参考文献 特開2011-141523(JP, A)

特開2011-142311(JP, A)

特開2010-114413(JP, A)

(58)調査した分野(Int.Cl., DB名)

H 01 L 21 / 336、29 / 786