(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5232425号

(P5232425)

(45) 発行日 平成25年7月10日(2013.7.10)

(24) 登録日 平成25年3月29日(2013.3.29)

(51) Int.Cl.

F 1

HO1L 21/336 (2006.01)

HO1L 29/788 (2006.01)

HO1L 29/792 (2006.01)

HO1L 21/8247 (2006.01)

HO1L 27/115 (2006.01)

HO1L 29/78 371

HO1L 27/10 434

請求項の数 11 (全 18 頁)

(21) 出願番号

特願2007-233924 (P2007-233924)

(22) 出願日

平成19年9月10日 (2007.9.10)

(65) 公開番号

特開2009-65094 (P2009-65094A)

(43) 公開日

平成21年3月26日 (2009.3.26)

審査請求日

平成22年3月5日 (2010.3.5)

(73) 特許権者 302062931

ルネサスエレクトロニクス株式会社

神奈川県川崎市中原区下沼部1753番地

(74) 代理人 100080001

弁理士 筒井 大和

(72) 発明者 濱村 浩孝

東京都国分寺市東恋ヶ窪一丁目280番地

株式会社日立製作所 中央研究所内

(72) 発明者 柳 至

東京都国分寺市東恋ヶ窪一丁目280番地

株式会社日立製作所 中央研究所内

(72) 発明者 峰 利之

東京都国分寺市東恋ヶ窪一丁目280番地

株式会社日立製作所 中央研究所内

最終頁に続く

(54) 【発明の名称】不揮発性半導体記憶装置およびその製造方法

## (57) 【特許請求の範囲】

## 【請求項 1】

半導体基板と、前記半導体基板上に形成された第1絶縁膜と、前記第1絶縁膜上に形成された電荷蓄積膜と、前記電荷蓄積膜上に形成された第2絶縁膜と、前記第2絶縁膜上に形成されたゲート電極とを備えるメモリセルを有し、前記電荷蓄積膜が金属酸化膜により構成される不揮発性半導体記憶装置であって、

前記第1絶縁膜は一層の絶縁膜からなり、前記第1絶縁膜中の、前記半導体基板と前記第1絶縁膜との界面よりも前記第1絶縁膜と前記電荷蓄積膜との界面に近い領域に、窒素濃度が1原子%以上の窒化領域が形成されており、前記窒化領域の厚さが0.5nm以上、1.5nm以下であり、

前記電荷蓄積膜中の、前記第1絶縁膜と前記電荷蓄積膜との界面よりも前記電荷蓄積膜と前記第2絶縁膜との界面に近い領域に、窒素濃度が1原子%以上の窒化領域が形成されていることを特徴とする不揮発性半導体記憶装置。

## 【請求項 2】

- (a) 半導体基板上に第1絶縁膜を形成する工程と、

- (b) 前記第1絶縁膜に対してプラズマ窒化処理を行い、前記第1絶縁膜中の上面側に、ピーク値を有して窒素濃度が1原子%以上の窒化領域を形成する工程と、

- (c) 前記第1絶縁膜上に金属酸化膜からなる電荷蓄積膜を形成する工程と、

- (d) 前記電荷蓄積膜上に第2絶縁膜を形成する工程と、

- (e) 前記第2絶縁膜上にゲート電極を形成する工程とを含み、

前記窒化領域の厚さが 0.5 nm 以上、1.5 nm 以下であることを特徴とする不揮発性半導体記憶装置の製造方法。

【請求項 3】

請求項 2 記載の不揮発性半導体記憶装置の製造方法において、前記 (b) 工程の前記プラズマ窒化処理の処理時間は 30 秒以上であることを特徴とする不揮発性半導体記憶装置の製造方法。

【請求項 4】

請求項 2 記載の不揮発性半導体記憶装置の製造方法において、前記第 1 絶縁膜中の前記窒素濃度のピーク値は 5 原子% 以上、40 原子% 以下であることを特徴とする不揮発性半導体記憶装置の製造方法。

10

【請求項 5】

請求項 2 記載の不揮発性半導体記憶装置の製造方法において、前記窒素濃度のピーク値は前記第 1 絶縁膜と前記電荷蓄積膜との界面から 2 nm 以内の領域に位置していることを特徴とする不揮発性半導体記憶装置の製造方法。

【請求項 6】

請求項 2 記載の不揮発性半導体記憶装置の製造方法において、前記電荷蓄積膜の物理的膜厚は 20 nm 以下であることを特徴とする不揮発性半導体記憶装置の製造方法。

【請求項 7】

請求項 2 記載の不揮発性半導体記憶装置の製造方法において、前記電荷蓄積膜は、ALCVD 法により形成されることを特徴とする不揮発性半導体記憶装置の製造方法。

20

【請求項 8】

請求項 2 記載の不揮発性半導体記憶装置の製造方法において、前記第 1 絶縁膜中の前記窒化領域は、前記半導体基板と前記第 1 絶縁膜との界面よりも前記第 1 絶縁膜と前記電荷蓄積膜との界面に近い領域に形成されることを特徴とする不揮発性半導体記憶装置の製造方法。

【請求項 9】

請求項 2 記載の不揮発性半導体記憶装置の製造方法において、前記 (c) 工程と前記 (d) 工程との間に、

(f) 前記電荷蓄積膜に対してプラズマ窒化処理を行い、前記電荷蓄積膜中の上面側に、

ピーク値を有して窒素濃度が 1 原子% 以上の窒化領域を形成する工程、

をさらに含むことを特徴とする不揮発性半導体記憶装置の製造方法。

30

【請求項 10】

請求項 9 記載の不揮発性半導体記憶装置の製造方法において、前記電荷蓄積膜中の前記窒素濃度のピーク値は 5 原子% 以上、40 原子% 以下であることを特徴とする不揮発性半導体記憶装置の製造方法。

【請求項 11】

請求項 9 記載の不揮発性半導体記憶装置の製造方法において、前記電荷蓄積膜中の前記窒化領域は、前記第 1 絶縁膜と前記電荷蓄積膜との界面よりも前記電荷蓄積膜と前記第 2 絶縁膜との界面に近い領域に形成されることを特徴とする不揮発性半導体記憶装置の製造方法。

40

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、電気的な書き込み、消去動作が可能な不揮発性半導体記憶装置およびその製造技術に関し、特に、金属酸化膜を電荷蓄積膜とする MONOS (Metal Oxide Nitride Oxide Semiconductor) 型のメモリセルにより構成されるメモリ部を有する不揮発性半導体記憶装置に適用して有効な技術に関するものである。

【背景技術】

【0002】

電気的な書き込み、消去が可能な不揮発性半導体記憶装置として、EEPROM (Electr

50

ical Erasable and Programmable Read Only Memory) が広く使用されている。フラッシュメモリに代表されるこのような不揮発性半導体記憶装置のメモリ部は、複数の不揮発性メモリセルによって構成されているが、この不揮発性メモリセルには、例えばゲート電極下に、酸化膜で囲まれた導電性の浮遊ゲート電極またはトラップ性絶縁膜を有し、浮遊ゲート電極またはトラップ性絶縁膜に電荷を保持することにより情報が記憶される電界効果トランジスタが使用されている。浮遊ゲート電極またはトラップ性絶縁膜の記憶保持状態は、電界効果トランジスタのしきい値電圧の変化により読み出すことができる。

#### 【0003】

上記トラップ性絶縁膜とは、電荷を保持することが可能な絶縁膜をいい、例えば窒化シリコン膜を例示することができる。窒化シリコン膜を電荷蓄積膜とする不揮発性メモリセルは、MONOSメモリセルと呼ばれ、離散的に電荷を蓄積することから、上記浮遊ゲート電極に電荷を蓄積する不揮発性メモリセルと比べて情報保持の信頼性に優れている。また、MONOSメモリセルでは、保持電荷のリークを抑制するために窒化シリコン膜の上下に酸化膜を形成する必要があるが、情報保持の信頼性に優れていることから、その酸化膜を薄くすることができる。例えば8 nm以下の薄い酸化膜を適用することが可能であり、書き込み、消去動作の低電圧化を図ることができる。

#### 【0004】

しかしながら、窒化シリコン膜を電荷蓄積膜に用いたMONOSメモリセルでは、電荷捕獲特性および電荷保持特性ともに十分であるとは言えず、例えばアルミナをはじめとする金属酸化膜を窒化シリコン膜に代えて電荷蓄積膜に用いたMONOS型のメモリセルが提案されている。

#### 【0005】

例えば電荷保持特性を改善するためにアルミナなどの金属酸化膜を電荷蓄積膜に適用した不揮発性半導体メモリセルが特開2004-158810号公報(特許文献1参照)に開示されている。また、金属酸化膜を形成した直後に熱処理を行うことにより金属酸化膜の誘電率を向上させる技術が米国特許出願公開第2006/0022252号明細書(特許文献2参照)に記載されている。この熱処理は金属酸化膜を形成した後に一般的に行われるものである。また、消去動作を高速化するために、基板と金属酸化膜との間に酸化シリコン膜と窒化シリコン膜との積層膜(酸化シリコン膜の上に窒化シリコン膜を重ねた積層構造)を形成する技術が提案されている(非特許文献1参照)。また、電荷蓄積膜をアルミナ膜と窒化シリコン膜との積層構造(ボトム窒化シリコン膜/アルミナ膜/トップ窒化シリコン膜)とすることにより、デバイス動作ウィンドウを広げる技術が提案されている(非特許文献2参照)。

#### 【特許文献1】特開2004-158810号公報

#### 【特許文献2】米国特許出願公開第2006/0022252号明細書

【非特許文献1】テクニカル・ダイジェスト・オブ・アイ・イー・ディー・エム(Technical Digest of IEDM)、2006、p. 971

【非特許文献2】ブイ・エル・エス・アイ・テクノロジー・ダイジェスト(VLSI Technology Digest)、2007、p. 138

#### 【発明の開示】

#### 【発明が解決しようとする課題】

#### 【0006】

しかしながら、金属酸化膜を電荷蓄積膜に用いたMONOS型のメモリセルについては、以下に説明する種々の技術的課題が存在する。

#### 【0007】

本発明者らが検討したところ、電荷蓄積膜に金属酸化膜を採用し、この金属酸化膜の上下を酸化膜で挟んだ電荷保持用絶縁膜の場合、金属酸化膜を形成した後の熱処理(例えば金属酸化膜を堆積した直後の熱処理または不純物活性化のための熱処理など)により、金属酸化膜と、これの上面に接するトップ酸化膜またはこれの下面に接するボトム酸化膜とが相互反応を起こすことが明らかになった。この相互反応が起きると、金属酸化膜の金属

10

20

30

40

50

元素が拡散して、トップ酸化膜中またはボトム酸化膜中に存在することとなり、トップ酸化膜中またはボトム酸化膜中に存在する金属元素を介してゲート電極側または基板側へ電子が移動して、メモリセルの電荷保持特性が劣化するという問題が生じてしまう。

【0008】

金属酸化膜と酸化膜とが直接、接している構造は、例えば上記特許文献1、2に示されている。特許文献1に記載されている第5の実施の形態においては、トラップ膜に窒化シリコン膜とアルミナ膜との積層膜を用い、ボトム酸化膜に酸化シリコン膜とLa<sub>2</sub>O<sub>5</sub>膜との積層膜を用いている。この構造においては、酸化シリコン膜と金属酸化膜であるLa<sub>2</sub>O<sub>5</sub>膜とが直接、接するため、後の工程での熱処理により、Laが酸化シリコン膜中へ拡散してメモリセルの電荷保持特性が劣化することが問題となる。

10

【0009】

特許文献2では、電荷蓄積膜に金属酸化膜を用いており、ボトム酸化シリコン膜と金属酸化膜とが直接、接する構造となっている。金属酸化膜の誘電率を向上させるために金属酸化膜を形成した直後に熱処理を行うことが実施例に示されているが、前述したように、熱処理を行うとボトム酸化シリコン膜中へ金属酸化膜の金属元素が拡散するため、メモリセルの電荷保持特性が劣化することが問題となる。

【0010】

非特許文献1、2では、金属酸化膜とボトム酸化シリコン膜との間に窒化シリコン膜を形成している。非特許文献1では、ボトム酸化シリコン膜上に1.6nmの厚さの窒化シリコン膜をCVD法で堆積して、ボトム酸化シリコン膜と窒化シリコン膜との積層膜を形成することにより、デバイス消去動作を高速化する技術が提案されている。しかし、1.6nmの厚さの窒化シリコン膜をCVD法によりウエハ面内に均一にかつ再現性よく形成することは難しく、窒化シリコン膜の厚さの制御が課題となる。

20

【0011】

非特許文献2では、電荷蓄積膜にアルミナ膜の上下を窒化シリコン膜で挟んだ積層膜（ボトム窒化シリコン膜（3nm）/アルミナ膜（3nm）/トップ窒化シリコン膜（4nm））を用いることにより、デバイス動作ウインドウを広げることを提案している。しかし、この構造の場合、電荷蓄積膜の電気的膜厚が5nm程度となり、デバイス動作電圧を低くすることができない。窒化シリコン膜を薄膜化することで、電荷蓄積膜全体の電気的膜厚を小さくすることはできるが、その場合、3nm以下の厚さの窒化シリコン膜をCVD法により形成する必要がある。このため、前述したように、窒化シリコン膜をCVD法によりウエハ面内に均一にかつ再現性よく形成することは難しく、窒化シリコン膜の厚さの制御が課題となる。

30

【0012】

本発明の目的は、金属酸化膜とその上下を挟む絶縁膜との相互拡散を抑制することにより、電荷蓄積膜に金属酸化膜を用いた不揮発性メモリセルの電荷保持特性を向上させることのできる技術を提供することにある。

【0013】

本発明の前記ならびにその他の目的と新規な特徴は、本明細書の記述および添付図面から明らかになるであろう。

40

【課題を解決するための手段】

【0014】

本願において開示される発明のうち、代表的なものの概要を簡単に説明すれば、次のとおりである。

【0015】

本発明による不揮発性半導体記憶装置は、半導体基板のチャネル領域側から、ボトム絶縁膜、金属酸化膜からなる電荷蓄積膜、およびトップ絶縁膜が順次積層されて構成される電荷保持用絶縁膜を備えるメモリセルを有しており、ボトム絶縁膜中の電荷蓄積膜側および電荷蓄積膜中のトップ絶縁膜側に、ピーク値を有して窒素濃度が1原子%以上の窒化領域が形成されており、例えばボトム絶縁膜中の電荷蓄積膜側に形成された窒化領域では、

50

その厚さを0.5nm以上、1.5nm以下とし、窒素濃度のピーク値を5原子%以上、40原子%以下とし、窒素濃度のピーク値の位置をボトム絶縁膜と電荷蓄積膜との界面から2nm以内の領域とするものである。

【0016】

本発明による不揮発性半導体記憶装置の製造方法は、半導体基板上にボトム絶縁膜を形成する工程と、ボトム絶縁膜に対してプラズマ窒化処理を行い、ボトム絶縁膜中の上面側に、ピーク値を有して窒素濃度が1原子%以上の窒化領域を形成する工程と、ボトム絶縁膜上に金属酸化膜からなる電荷蓄積膜を形成する工程と、電荷蓄積膜に対してプラズマ窒化処理を行い、電荷蓄積膜の上面側に、ピーク値を有して窒素濃度が1原子%以上の窒化領域を形成する工程と、電荷蓄積膜上にトップ絶縁膜を形成する工程と、トップ絶縁膜上にゲート電極を形成する工程とを含み、例えばボトム絶縁膜中の電荷蓄積膜側に形成された窒化領域では、その厚さを0.5nm以上、1.5nm以下とし、窒素濃度のピーク値を5原子%以上、40原子%以下とし、窒素濃度のピーク値の位置をボトム絶縁膜と電荷蓄積膜との界面から2nm以内とするものである。

10

【発明の効果】

【0017】

本願において開示される発明のうち、代表的なものによって得られる効果を簡単に説明すれば以下のとおりである。

【0018】

ボトム絶縁膜、金属酸化膜からなる電荷蓄積膜、およびトップ絶縁膜が順次積層されて構成される電荷保持用絶縁膜において、ボトム絶縁膜中の上面側および電荷蓄積膜中の上面側にプラズマ窒化処理により窒化領域を形成することにより、ボトム絶縁膜と電荷蓄積膜、または電荷蓄積膜とトップ絶縁膜との相互拡散が抑制されて、金属元素のボトム絶縁膜またはトップ絶縁膜への拡散を防止することができる。これにより、電荷蓄積膜に金属酸化膜を用いた不揮発性メモリセルの電荷保持特性を向上させることができる。

20

【発明を実施するための最良の形態】

【0019】

本実施の形態において、便宜上その必要があるときは、複数のセクションまたは実施の形態に分割して説明するが、特に明示した場合を除き、それらはお互いに無関係なものではなく、一方は他方の一部または全部の変形例、詳細、補足説明等の関係にある。

30

【0020】

また、本実施の形態において、要素の数等（個数、数値、量、範囲等を含む）に言及する場合、特に明示した場合および原理的に明らかに特定の数に限定される場合等を除き、その特定の数に限定されるものではなく、特定の数以上でも以下でも良い。さらに、本実施の形態において、その構成要素（要素ステップ等も含む）は、特に明示した場合および原理的に明らかに必須であると考えられる場合等を除き、必ずしも必須のものではないことは言うまでもない。同様に、本実施の形態において、構成要素等の形状、位置関係等に言及するときは、特に明示した場合および原理的に明らかにそうでないと考えられる場合等を除き、実質的にその形状等に近似または類似するもの等を含むものとする。このことは、上記数値および範囲についても同様である。

40

【0021】

また、本実施の形態においては、電界効果トランジスタを代表するMIS·FET（Metal Insulator Semiconductor Field Effect Transistor）をMISと略し、nチャネル型のMIS·FETをnMISと略す。なお、MOSFET（Metal Oxide Semiconductor FET）は、そのゲート絶縁膜が酸化シリコン（SiO<sub>2</sub>等）膜からなる構造の電界効果トランジスタであり、上記MISの下位概念に含まれるものとする。また、本実施の形態で記載するMONOS型のメモリセルについても、上記MISの下位概念に含まれることは勿論である。また、本実施の形態において、ウエハと言うときは、Si（Silicon）単結晶ウエハを主とするが、それのみではなく、SOI（Silicon On Insulator）ウエハ、集積回路をその上に形成するための絶縁膜基板等を指すものとする。その形も円形また

50

はほぼ円形のみでなく、正方形、長方形等も含むものとする。

【0022】

また、本実施の形態を説明するための全図において、同一機能を有するものは原則として同一の符号を付し、その繰り返しの説明は省略する。以下、本発明の実施の形態を図面に基づいて詳細に説明する。

【0023】

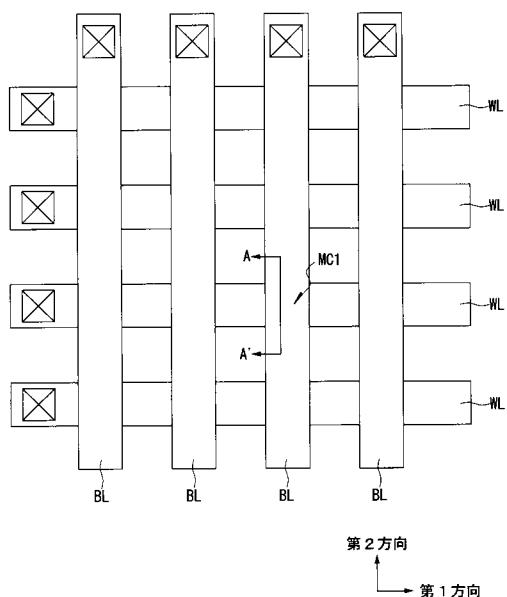

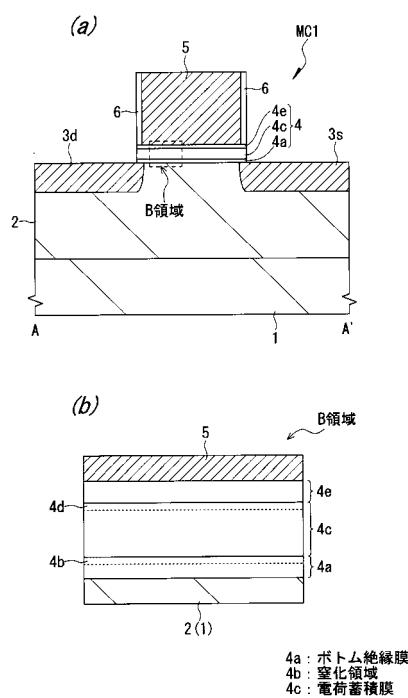

本発明の一実施の形態による不揮発性半導体記憶装置のメモリ部の一例を図1および図2を用いて説明する。図1は単体ゲート構造のMONOS型のメモリセルを用いたメモリアレイの構成を示すワード線およびビット線の平面レイアウト図、図2(a)は単体ゲート構造のMONOS型のメモリセルをゲート長方向(図1のA-A線)に沿って切断したメモリセルの要部断面図、図2(b)は図2(a)のB領域を拡大した電荷保持用絶縁膜の要部断面図である。

10

【0024】

不揮発性半導体記憶装置のメモリ部は、メモリセルMC1が二次元格子状に配列されたメモリアレイにより構成されている。図1に示すように、このメモリアレイでは、信号線である複数のワード線WLが第1方向に平行して延びてあり、もう一方の信号線である複数のビット線BLが第1方向と交差する方向である第2方向に平行して延びている。ワード線WLには各メモリセルMC1のメモリゲート電極が接続され、ビット線BLには各メモリセルMC1のドレイン領域が接続されている。

20

【0025】

図2(a)に示すように、メモリセルMC1は、半導体基板1の正面に形成されたpウェル2、ソース領域3sとなるn<sup>+</sup>型の半導体領域、ドレイン領域3dとなるn<sup>+</sup>型の半導体領域、ソース領域3sとドレイン領域3dとの間のチャネル領域上に形成された電荷保持用絶縁膜4、および電荷保持用絶縁膜4上に形成されたメモリゲート電極5を有するNIMSにより構成されている。上記電荷保持用絶縁膜4は、チャネル領域側から、ボトム絶縁膜(第1絶縁膜)4a、電荷蓄積膜4cおよびトップ絶縁膜(第2絶縁膜)4eを順次形成した積層膜により構成されており、ボトム絶縁膜4aおよびトップ絶縁膜4eは、例えば酸化シリコン膜からなり、電荷蓄積膜4cは、例えば酸化ハフニウム膜などの金属酸化膜からなる。ボトム絶縁膜4aの厚さは2.5nm以上、6nm以下、トップ絶縁膜4eの厚さは4nm以上、6nm以下、電荷蓄積膜4cの厚さ(誘電率を考慮しない物理的膜厚)は20nm以下である。また、上記メモリゲート電極5は、例えばn型不純物が導入された多結晶シリコン膜からなり、ワード線WLを構成する。

30

【0026】

さらに、図2(b)に示すように、ボトム絶縁膜4a中の電荷蓄積膜4c側には、ピーク値を有して窒素濃度が1原子%以上の窒化領域4bが形成されており、その窒化領域4bの厚さは0.5nm以上、1.5nm以下である。また、その窒化領域4bにおける窒素濃度のピーク値は5原子%以上、40原子%以下であり、ボトム絶縁膜4aと電荷蓄積膜4cとの界面から2nm以内に位置している。また、電荷蓄積膜4c中のトップ絶縁膜4e側にも、ピーク濃度を有して窒素濃度が1原子%以上の窒化領域4dが形成されている。その窒化領域4dにおける窒素濃度のピーク値は5原子%以上、40原子%以下である。

40

【0027】

メモリセルMC1では、ボトム絶縁膜4a中の電荷蓄積膜4c側に1原子%以上の窒素濃度を有する窒化領域4bを形成し、電荷蓄積膜4c中のトップ絶縁膜4e側に1原子%以上の窒素濃度を有する窒化領域4dを形成しているが、電荷蓄積膜4c中のトップ絶縁膜4e側に窒化領域4dを形成せず、ボトム絶縁膜4a中の電荷蓄積膜4c側のみに窒化領域4bを形成してもよい。後に評価結果(例えば図8に示すメモリセルの電荷保持特性)を用いて説明するが、ボトム絶縁膜4a中の電荷蓄積膜4c側のみに窒化領域4bを形成しただけでも、メモリセルのデータ保持特性の向上に効果がある。

【0028】

50

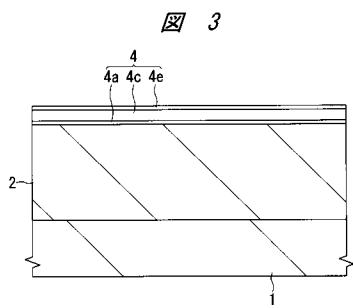

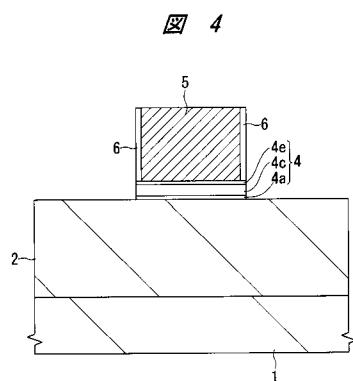

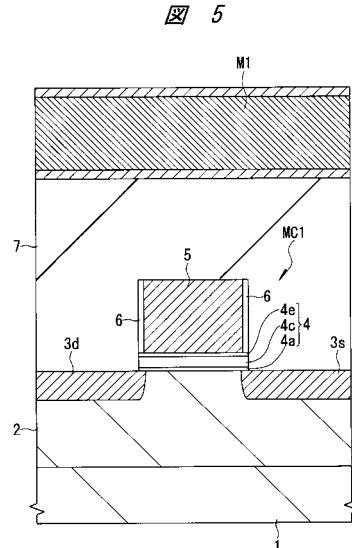

次に、本発明の一実施の形態による単体ゲート構造のMONOS型メモリセルの製造方法の一例を図3～図5を用いて説明する。図3～図5は、メモリセルの製造工程中におけるメモリセルの要部断面図である。

【0029】

まず、図3に示すように、例えば1～10 $\cdot$ cmの比抵抗を有するp型の単結晶シリコンからなる半導体基板（この段階では半導体ウエハと称する平面略円形状の半導体の薄板）1を準備する。続いて半導体基板1の主面に、例えば溝型の素子分離部およびこれに取り囲まれるように配置された活性領域等を形成する。すなわち、半導体基板1の所定箇所に分離溝を形成した後、半導体基板1の主面上に、例えば酸化シリコンからなる絶縁膜を堆積し、さらにその絶縁膜が分離溝内にのみに残されるように絶縁膜をCMP（Chemical Mechanical Polishing）法等によって研磨することで、分離部を形成する。続いて、半導体基板1の所定部分にp型の不純物を所定のエネルギーで選択的にイオン注入法等によって導入することにより、pウェル2を形成する。

【0030】

次に、半導体基板1に対して、例えば850 $^{\circ}$ Cの温度でドライ酸化を施すことにより、半導体基板1の主面に、例えば酸化シリコン膜からなる厚さ2.5nm以上、6nm以下のボトム絶縁膜4aを形成する。ボトム絶縁膜4aの形成は、これに限定されるものではなく、例えばウェット酸化、ISSG（In-Situ Steam Generation）酸化、オゾン酸化またはプラズマ酸化により形成することもできる。

【0031】

また、ボトム絶縁膜4aに酸窒化シリコン膜を用いてもよく、酸窒化シリコン膜を用いることにより、ボトム絶縁膜4aの信頼性を向上させることができる。酸窒化シリコン膜は、例えばその主面に酸化シリコン膜が形成された半導体基板1に対して一酸化炭素（NO）ガスまたは亜酸化窒素（N<sub>2</sub>O）ガス等を用いた窒素性雰囲気で熱処理を施すことにより形成することができる。例えば窒素により10%に希釈された一酸化炭素ガス雰囲気で半導体基板1に対して例えば900 $^{\circ}$ Cの温度で10分の熱処理を施すことにより、半導体基板1と酸化シリコン膜との界面に窒素が3原子%程度導入された酸窒化シリコン膜を形成することができる。

【0032】

次に、窒素ガスを用いたプラズマ窒化処理によりボトム絶縁膜4aを窒化して、ボトム絶縁膜4a中の上面側に窒化領域（前述の図2（b）に示した窒化領域4b）を形成する。前述したように、窒化領域4bは、1原子%以上の窒素濃度を有しており、その厚さは0.5nm以上、1.5nm以下である。また、その窒化領域4bにおける窒素濃度のピーク値は5原子%以上、40原子%以下であり、ボトム絶縁膜4aの上面から2nm以内に位置している。プロセスガスには窒素ガスを用いたが、これに限定されるものではなく、例えばアンモニア（NH<sub>3</sub>）ガスを用いてもよく、また、窒素と希ガスとの混合ガスまたはアンモニアガスと希ガスとの混合ガスを用いてもよい。プラズマ窒化処理におけるプロセス温度は、例えば600 $^{\circ}$ C、プロセス圧力は、例えば50Pa、RFパワーは、例えば250Wである。これらプロセス温度、プロセス圧力およびRFパワーは一例であって、これに限定されるものではない。

【0033】

次に、ボトム絶縁膜4a上に金属酸化膜、例えば酸化ハフニウム膜からなる電荷蓄積膜4cをALCVD（Atomic Layer Chemical Vapor Deposition）法により形成する。電荷蓄積膜4cの厚さは20nm以下とすることが望ましい。これは、電荷蓄積膜4cの厚さが20nmよりも厚くなると、メモリセルの書き込み、消去動作の電圧が大きくなるためであり、本発明者による酸化ハフニウム膜の膜厚を様々に変えて行った電気的特性評価によつても確かめられている。

【0034】

ハフニウムの原料にはテトラエチルメチルアミノハフニウム（Hf[N(CH<sub>3</sub>)<sub>2</sub>H<sub>5</sub>]<sub>4</sub>：TEMHf）を用い、酸化剤にはオゾンを用いて、例えば285 $^{\circ}$ Cの温度

10

20

30

40

50

で、20 nm 以下の厚さの酸化ハフニウム膜を形成する。ALCVD 法は、一般に反応サイクルを繰り返し行い、1 つの原子層を連続的に積層することによって、高品質でかつ段差被覆性の良い膜を形成させる成膜方法であり、原料が吸着する全範囲にわたって同じ成長速度を維持することができるので、ウエハ面内に均一にかつ再現性よく金属酸化膜を成膜することができる。ハフニウムの原料としては、ALCVD 法に適した他の材料を用いることもできる。また、酸化剤には水 ( $H_2O$ ) を用いることもできる。また、酸化ハフニウム膜は ALCVD 法に限らず、CVD 法またはスパッタリング法などを用いて形成することも可能である。

#### 【0035】

次に、ボトム絶縁膜 4a に対するプラズマ窒化処理と同様に、電荷蓄積膜 4c に対して 10 プラズマ窒化処理を行い、電荷蓄積膜 4c 中の上面側に窒化領域（前述した図 2 (b) に示す窒化領域 4d）を形成する。前述したように、窒化領域 4d は、1 原子%以上の窒素濃度を有しており、その窒化領域 4d における窒素濃度のピーク値は 5 原子%以上、40 原子%以下である。

#### 【0036】

次に、電荷蓄積膜 4c 上に、例えば酸化シリコン膜からなる厚さ 4 nm 以上、6 nm 以下のトップ絶縁膜 4e を形成する。酸化シリコン膜は、例えばモノシラン ( $SiH_4$ ) ガスと亜酸化窒素ガスとを原料とする低圧 CVD 法により形成することができる。また、TEOS (Tetra Ethyl Ortho Silicate;  $Si(OCH_3)_4$ ) を原料とする CVD 法またはプラズマ CVD 法により形成することもできる。 20

#### 【0037】

次に、トップ絶縁膜 4e 上に、例えば  $5 \times 10^{20} \text{ atoms/cm}^3$  の不純物濃度を有する多結晶シリコン膜からなる導体膜を堆積する。この導体膜は CVD 法により形成され、その厚さは、例えば 150 nm を例示することができる。

#### 【0038】

次に、図 4 に示すように、レジストパターンをマスクとして上記導体膜をドライエッチング法により加工し、メモリゲート電極 5 を形成する。さらに、ドライエッチング法によりメモリゲート電極 5 と半導体基板 1 との間の電荷保持用絶縁膜 4（トップ絶縁膜 4e、電荷蓄積膜 4c およびボトム絶縁膜 4a）を残して、その他の領域の電荷保持用絶縁膜 4（トップ絶縁膜 4e、電荷蓄積膜 4c およびボトム絶縁膜 4a）を選択的に除去する。この後、ドライエッチング法によるメモリゲート電極 5 の側壁形状の損傷を回復するために、半導体基板 1 に対して I<sub>SSG</sub> 酸化を施し、メモリゲート電極 5 の側壁に 4 nm の側壁膜 6 を形成する。 30

#### 【0039】

次に、図 5 に示すように、メモリゲート電極 5 をマスクとして n 型不純物、例えばヒ素 (As) を半導体基板 1 の正面にイオン注入することにより、半導体基板 1 の正面に  $n^+$  型の半導体領域をメモリゲート電極 5 に対して自己整合的に形成する。この時の不純物イオンの打ち込みエネルギーは、例えば 40 keV、ドーズ量は、例えば  $2 \times 10^{15} \text{ atoms/cm}^2$  である。その後、例えば 1000 の温度で 10 秒の熱処理を施すことにより、イオン注入した n 型不純物を活性化することにより、ソース領域 3s およびドレイン領域 3d を形成する。 40

#### 【0040】

次に、半導体基板 1 の正面に層間絶縁膜 7 を、例えば CVD 法により形成する。続いて層間絶縁膜 7 にコンタクトホールを形成した後、コンタクトホール内にプラグを形成する。その後、層間絶縁膜 7 上に、例えばタンクステン、アルミニウムまたは銅等からなる第 1 層配線 M1 を形成することによって、メモリセル MC1 が略完成する。これ以降は、通常の半導体装置の製造工程を経て、半導体装置を製造する。

#### 【0041】

次に、本発明の一実施の形態による単体ゲート構造の MONOS 型メモリセルの書き込みおよび消去方法について、前述した図 2 を用いて説明する。 50

## 【0042】

「書込み」は、メモリセルM C 1 の電荷蓄積膜 4 c 中にホットエレクトロンを注入する。例えばソース領域 3 s に印加する電圧 ( V s ) は 0 V 、ドレイン領域 3 d に印加する電圧 ( V d ) は 4 V 、メモリゲート電極 5 に印加する電圧 ( V g ) は 6 V とする。

## 【0043】

「消去」は、バンド間トンネリングにより発生したホットホールを電界加速して、メモリセルM C 1 の電荷蓄積膜 4 c 中に注入するホットホール消去 ( B T B T ( Band-To-Band Tunneling ) 消去 ) 、またはF N ( Fowler-Nordheim ) トンネリングにより半導体基板 1 からメモリセルM C 1 の電荷蓄積膜 4 c 中にホールを注入する F N 消去のいずれかで行う。 B T B T 消去を行う場合は、例えばソース領域 3 s に印加する電圧 ( V s ) は 0 V 、ドレイン領域 3 d に印加する電圧 ( V d ) は 4 V 、メモリゲート電極 5 に印加する電圧 ( V g ) は - 6 V である。 F N 消去の場合は、例えばソース領域 3 s に印加する電圧 ( V s ) は 0 V 、ドレイン領域 3 d に印加する電圧 ( V d ) は 0 V 、メモリゲート電極 5 に印加する電圧 ( V g ) は - 15 V である。なお、ここで示した書込み、消去の電圧は印加条件の一例であり、これに限定されるものではなく、必要に応じて変更可能である。

## 【0044】

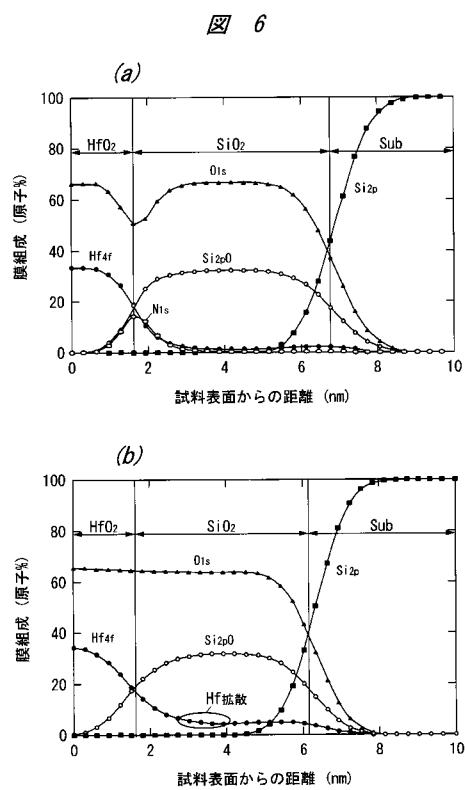

次に、本発明の一実施の形態による電荷保持用絶縁膜におけるボトム絶縁膜 ( 酸化シリコン膜 ) と電荷蓄積膜 ( 酸化ハフニウム膜 ) との相互反応について図 6 を用いて説明する。図 6 ( a ) は酸化シリコン膜中の酸化ハフニウム膜側にプラズマ室化処理により窒化領域を形成した試料の膜厚方向の組成分布を示すグラフ図、図 6 ( b ) は酸化シリコン膜中に窒化領域を形成しない試料の膜厚方向の組成分布を示すグラフ図であり、これら組成分布は X 線光電子分光法 ( X P S ( X-ray Photoelectron Spectroscopy ) 法 ) により得られた。図 6 ( a ) に組成分布を示す試料では、シリコン基板上に形成した酸化シリコン膜に対してプラズマ室化処理を行った後に酸化ハフニウム膜が堆積され、その後、 950 の温度で 1 分の熱処理を行っている。図 6 ( b ) に組成分布を示す試料では、シリコン基板上に形成した酸化シリコン膜に対してプラズマ室化処理を行わずに酸化ハフニウム膜が堆積され、その後、 950 の温度で 1 分の熱処理を行っている。ここでは、組成分布の分析感度を高めるために、酸化ハフニウム膜の厚さは 2 nm としている。

## 【0045】

図 6 ( a ) に示すように、窒化領域を形成した試料では、酸化シリコン膜中のハフニウムの拡散が抑制されている。これに対して、図 6 ( b ) に示すように、酸化シリコン膜に窒化領域を形成しない試料では、酸化シリコン膜中にハフニウムが 5 % 程度拡散している。これらの結果から、酸化シリコン膜中の酸化ハフニウム膜側に窒化領域を形成することにより、酸化シリコン膜中のハフニウムの拡散を抑制することが可能となることがわかる。

## 【0046】

図 6 ( a ) には、ボトム絶縁膜となる酸化シリコン膜中の上面側に窒化領域を形成し、このボトム絶縁膜となる酸化シリコン膜上に酸化ハフニウム膜を積層した試料の組成分析結果を示したが、酸化ハフニウム膜に対してプラズマ室化処理を行うことにより、酸化ハフニウム膜中の上面側に窒化領域を形成し、この酸化ハフニウム膜上にトップ絶縁膜となる酸化シリコン膜を積層した試料についても本発明者は組成分析をしている。その組成分析結果からもトップ絶縁膜となる酸化シリコン膜中のハフニウムの拡散を抑制できることが確かめられた。

## 【0047】

次に、本発明の一実施の形態による単体ゲート構造の M O N O S 型メモリセルの電気的特性を調べた結果について説明する。

## 【0048】

ボトム絶縁膜に対するプラズマ室化処理の処理時間とメモリセルの電荷保持特性との相関を調べたところ、プラズマ室化処理の処理時間が 30 秒以上においてメモリセルの電荷保持特性が改善される実験結果が得られた。このときのプラズマ室化処理の圧力は 50 P

10

20

30

40

50

a、パワーは250Wである。

【0049】

また、プラズマ窒化処理の窒化条件を様々に変化させて、ボトム絶縁膜の上面側に形成される窒化領域の厚さを制御し、この窒化領域の厚さとメモリセルの電荷保持特性との相関を調べたところ、窒化領域の厚さが0.5nm以上、1.5nm以下においてメモリセルの電荷保持特性が改善される実験結果が得られた。ここで窒化領域とは、シリコン、窒素および酸素から構成される絶縁領域を指し、窒化領域の厚さとは、窒素濃度の割合が1原子%以上である領域の厚さと定義する。

【0050】

また、プラズマ窒化処理の窒化条件を様々に変化させて、ボトム絶縁膜中の上面側に形成される窒化領域における窒素濃度のピーク位置を制御し、この窒素濃度のピーク位置とメモリセルの電荷保持特性との相関を調べたところ、窒素濃度のピーク位置がボトム絶縁膜と電荷蓄積膜との界面から2nm以内においてメモリセルの電荷保持特性が改善される実験結果が得られた。

10

【0051】

また、プラズマ窒化処理の窒化条件を様々に変化させて、ボトム絶縁膜中の上面側に形成される窒化領域における窒素ピーク濃度を0~40原子%の範囲で制御し、この窒素ピーク濃度とメモリセルの電荷保持特性との相関を調べた。図7に、メモリセルの電荷保持特性の窒素濃度依存性を説明するグラフ図を示す。図7の縦軸はメモリセルの初期から所定時間までの電圧シフト(メモリセルのしきい値電圧の初期からの変化量)であり、横軸はボトム絶縁膜中の窒素領域における窒素ピーク濃度である。電荷保持温度は150とした。

20

【0052】

図7に示すように、ボトム絶縁膜中の窒素領域における窒素ピーク濃度が0原子%における電圧シフトは約-0.6Vであるが、ボトム絶縁膜中の窒素濃度における窒素ピーク濃度が増加するに従い電圧シフトは減少し、5原子%における電圧シフトは約-0.22V、20原子%における電圧シフトは約-1.6Vとなる。これより、ボトム絶縁膜中の窒素濃度における窒素ピーク濃度が5原子%以上において、電圧シフトを抑制できることがわかる。

【0053】

30

図7には、ボトム絶縁膜中の上面側に形成される窒化領域における窒素ピーク濃度とメモリセルの電荷保持特性との相関を調べた結果を示しているが、プラズマ窒化処理の窒化条件を様々に変化させて、電荷蓄積膜中の上面側に形成される窒化領域における窒素ピーク濃度を0~40原子%の範囲で制御し、この窒素ピーク濃度とメモリセルの電荷保持特性との相関も調べた。その結果、ボトム絶縁膜の場合と同様に、電荷蓄積膜中の窒化領域における窒素ピーク濃度が5原子%以上において、電圧シフトを抑制できることがわかった。

【0054】

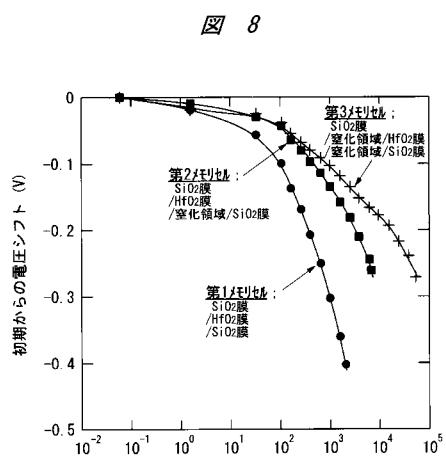

また、窒化領域の有無によるメモリセルの電荷保持特性の違いを調べた。図8に、ボトム絶縁膜中の上面側および電荷蓄積膜中の上面側に窒化領域を形成しない第1メモリセル、ボトム絶縁膜の上面側のみに窒化領域を形成した第2メモリセル、ボトム絶縁膜の上面側および電荷蓄積膜の上面側にそれぞれ窒化領域を形成した第3メモリセルの各電荷保持特性を説明するグラフ図を示す。図8の縦軸はメモリセルの初期から所定時間までの電圧シフト(メモリセルのしきい値電圧の初期からの変化量)であり、横軸はデータ保持時間である。第2メモリセルでは、ボトム絶縁膜のみに対してプラズマ窒化処理を行い、第3メモリセルでは、ボトム絶縁膜および電荷蓄積膜に対してそれぞれプラズマ窒化処理を行っており、ボトム絶縁膜中の上面側に形成された窒化領域または電荷蓄積膜中の上面側に形成された窒化領域の窒素ピーク濃度は15原子%である。ボトム絶縁膜およびトップ絶縁膜は酸化シリコン膜からなり、電荷蓄積膜は酸化ハフニウム膜からなる。

40

【0055】

50

図8に示すように、ボトム絶縁膜中の上面側のみに窒化領域を形成した第2メモリセルでも、窒化領域を形成しない第1メモリセルよりも電荷保持特性を著しく改善することができる。また、ボトム絶縁膜中の上面側および電荷蓄積膜中の上面側にそれぞれ窒化領域を形成した第3メモリセルでは、さらに第2メモリセルよりも電荷保持特性を改善することができる。しかし、プラズマ窒化処理により電荷保持特性が改善する効果は、電荷蓄積膜中の上面側に窒化領域を形成した場合よりも、ボトム絶縁膜中の上面側に窒化領域を形成した場合の方が大きいと考えられる。

#### 【0056】

以上に説明したメモリセルの電気的特性の結果から、ボトム絶縁膜に対してプラズマ窒化処理を行い、ボトム絶縁膜中の上面側に窒化領域を形成することにより、ボトム絶縁膜に窒化領域を形成しない場合よりも、メモリセルの電荷保持特性が改善できることがわかった。また、電荷蓄積膜に対してプラズマ窒化処理を行い、電荷蓄積膜中の上面側に窒化領域を形成することにより、電荷蓄積膜に窒化領域を形成しない場合よりも、メモリセルの電荷保持特性が改善できることがわかった。また、ボトム絶縁膜および電荷蓄積膜に対してそれぞれプラズマ窒化処理を行い、ボトム絶縁膜中の上面側および電荷蓄積膜中の上面側にそれぞれ窒化領域を形成することにより、ボトム絶縁膜中の上面側のみに窒化領域を形成した場合よりも、さらにメモリセルの電荷保持特性が改善できることがわかった。

10

#### 【0057】

このように、本実施の形態によれば、ボトム絶縁膜、金属酸化膜からなる電荷蓄積膜、およびトップ絶縁膜が順次積層されて構成される電荷保持用絶縁膜において、ボトム絶縁膜に対してプラズマ窒化処理を行い、ボトム絶縁膜中の上面側に窒素濃度のピーク値を有し、窒素濃度が1原子%以上の窒化領域（窒化領域の厚さは0.5nm以上、1.5nm以下、窒化領域の窒素濃度のピーク値は5原子%以上、40原子%以下、窒化領域の窒素濃度のピーク値の位置は上面から2nm以内）を形成することにより、電荷蓄積膜からボトム絶縁膜への金属元素の拡散を抑制して、メモリセルの電荷保持特性を向上させることができる。また、同様に、上記電荷保持用絶縁膜において、電荷蓄積膜に対してプラズマ窒化処理を行い、電荷蓄積膜中の上面側に窒素濃度のピーク値を有し、窒素濃度が1原子%以上の窒化領域（窒化領域の窒素濃度のピーク値は5原子%以上、40原子%以下）を形成することにより、電荷蓄積膜からトップ絶縁膜への金属元素の拡散を抑制して、メモリセルの電荷保持特性を向上させることができる。

20

#### 【0058】

また、例えば一酸化炭素、亜酸化窒素またはアンモニア雰囲気等の窒化性雰囲気中で熱処理を行った場合は、ボトム絶縁膜中の上面側に窒素が偏析せず、半導体基板とボトム絶縁膜との界面に窒素が偏析するため、ボトム絶縁膜へのハフニウムの拡散を抑制することができない。しかし、プラズマ窒化処理を採用することにより、ボトム絶縁膜中の上面側のみに窒素を偏析させることができるので、金属元素の拡散を効率よく抑制することができる。また、プラズマ窒化処理を採用することにより、CVD法と比較して、ウエハ面内において窒素濃度と窒化領域の厚さを均一に容易に制御することができる。また、窒化領域の厚さを1.5nm以下と比較的薄く形成することができる。

30

#### 【0059】

なお、本実施の形態では、本願発明を単体ゲート構造のMONOS型メモリセルに適用した場合について説明したが、これに限定されるものではなく、例えば選択用nMISとメモリ用nMISとから構成されるスプリットゲート構造のMONOS型メモリセルにも適用することができて、同様の効果を得ることができる。また、これらMONOS型メモリセルは論理用半導体装置と同一のシリコン基板上に混載することができて、高機能の半導体装置を実現することができる。

40

#### 【0060】

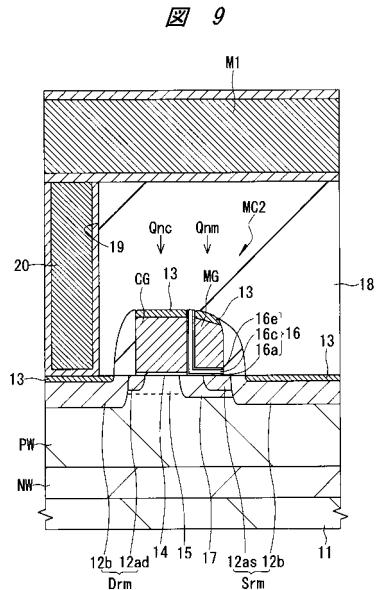

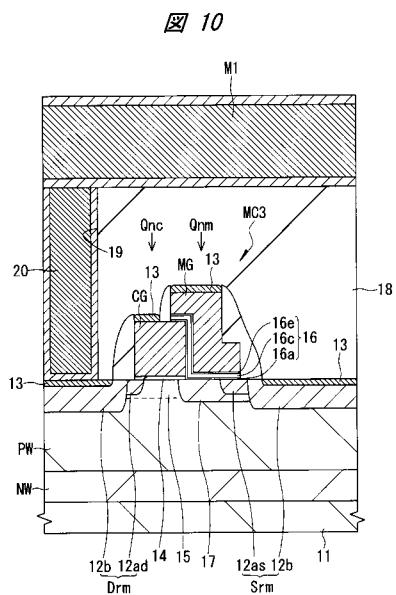

スプリットゲート構造のMONOS型メモリセルの一例を図9および図10に示す。図9および図10は、スプリットゲート構造のMONOS型メモリセルをゲート長方向に沿って切断したメモリセルの要部断面図である。

50

## 【0061】

図9に示すメモリセルMC2では、半導体基板11の正面(デバイス形成面)の活性領域に選択用nMIS(Qnc)とメモリ用nMIS(Qnm)とが配置されている。このメモリセルMC2のドレイン領域Drmおよびソース領域Srmは、例えば相対的に低濃度のn-型の半導体領域12ad, 12asと、そのn-型の半導体領域12ad, 12asよりも不純物濃度の高い相対的に高濃度のn+型の半導体領域12bとを有している(LDD(Lightly Doped Drain)構造)。n-型の半導体領域12ad, 12asは、メモリセルMC2のチャネル領域側に配置され、n+型の半導体領域12bは、メモリセルMC2のチャネル領域側からn-型の半導体領域12ad, 12as分だけ離れた位置に配置されている。図中、符号NWはnウェル、符号PWはpウェルである。

10

## 【0062】

このドレイン領域Drmとソース領域Srmとの間の半導体基板11の正面には、上記選択用nMIS(Qnc)の選択ゲート電極CGと、上記メモリ用nMIS(Qnm)のメモリゲート電極MGとが隣接して延在している。選択ゲート電極CGは半導体基板11の正面の第1領域に配置され、メモリゲート電極MGは半導体基板11の正面の第1領域とは異なる第2領域に配置されている。選択ゲート電極CGは、例えばn型の多結晶シリコン膜からなり、そのゲート長は、例えば100~200nmである。メモリゲート電極MGは、例えばn型の多結晶シリコン膜からなり、そのゲート長は、例えば50~150nmである。

## 【0063】

20

選択ゲート電極CGと、メモリゲート電極MGと、ソース領域Srmおよびドレイン領域Drmの一部を構成するn+型の半導体領域12bの上面には、例えばコバルトシリサイド、ニッケルシリサイド、チタンシリサイド等のようなシリサイド層13が形成されている。シリサイド層13の厚さは、例えば20nmである。

## 【0064】

選択ゲート電極CGと半導体基板11の正面との間には、例えば厚さ1~5nmの薄い酸化シリコン膜からなるゲート絶縁膜14が設けられている。このゲート絶縁膜14の下方の半導体基板11の正面には、例えばボロン(B)が導入されてp型の半導体領域15が形成されている。この半導体領域15は、選択用nMIS(Qnc)のチャネル形成用の半導体領域であり、この半導体領域15により選択用nMIS(Qnc)のしきい値電圧が所定の値に設定されている。

30

## 【0065】

メモリゲート電極MGは選択ゲート電極CGの側壁の片側に設けられており、ボトム絶縁膜16a、電荷蓄積膜16cおよびトップ絶縁膜16eを積層した電荷保持用絶縁膜16により選択ゲート電極CGとメモリゲート電極MGとの絶縁がなされている。また、電荷保持用絶縁膜16を介した半導体基板11の第2領域上にメモリゲート電極MGが配置されている。

## 【0066】

電荷保持用絶縁膜16は、前述の図2を用いて説明した電荷保持用絶縁膜4と同様である。すなわち、チャネル領域側から、ボトム絶縁膜16a、電荷蓄積膜16cおよびトップ絶縁膜16eが順次積層されて構成されており、ボトム絶縁膜16aおよびトップ絶縁膜16eは、例えば酸化シリコン膜からなり、電荷蓄積膜16cは、例えば酸化ハフニウム膜などの金属酸化膜からなる。ボトム絶縁膜16aおよびトップ絶縁膜16eの厚さは4nm以上、6nm以下、電荷蓄積膜16cの厚さ(物理的膜厚)は20nm以下である。さらに、ボトム絶縁膜16a中の電荷蓄積膜16c側には、ピーク値を有して窒素濃度が1原子%以上の窒化領域が形成されており、その窒化領域の厚さは0.5nm以上、1.5nm以下である。また、その窒化領域における窒素濃度のピーク値は5原子%以上、40原子%以下であり、ボトム絶縁膜16aと電荷蓄積膜16cとの界面から2nm以内に位置している。また、電荷蓄積膜16c中のトップ絶縁膜16e側にも、ピーク値を有して窒素濃度が1原子%以上の窒化領域を形成してもよい。この場合、その窒化領域にお

40

50

ける窒素濃度のピーク値は 5 原子%以上、40 原子%以下とする。

【0067】

ボトム絶縁膜 16a の下方、p 型の半導体領域 15 とソース領域 Srm との間の半導体基板 11 の正面には、例えはヒ素またはリン (P) が導入されて n 型の半導体領域 17 が形成されている。この半導体領域 17 は、メモリ用 nMIS (Qnm) のチャネル形成用の半導体領域であり、この半導体領域 17 によりメモリ用 nMIS (Qnm) のしきい値電圧が所定の値に設定されている。

【0068】

メモリセル MC2 は層間絶縁膜 18 により覆われている。ドレイン領域 Drm には、層間絶縁膜 18 に形成されたコンタクトホール 19 に埋め込まれたプラグ 20 を介して、第 1 方向に延在するメモリゲート電極 MG (または選択ゲート電極 CG) に対して交差する方向である第 2 方向に延在する第 1 層配線 M1 が接続されている。この配線 M1 が、各メモリセル MC2 のビット線を構成している。

【0069】

図 10 に示すメモリセル MC3 は、前述のメモリセル MC2 と同様の電荷保持用絶縁膜を有するものであるが、メモリ用 nMIS (Qnm) のメモリゲート電極 MG の形状およびその形成方法が、前述のメモリセル MC2 と相違する。すなわち、前述のメモリセル MC2 では、選択用 nMIS (Qnc) の選択ゲート電極 CG の側壁に、自己整合を利用してメモリ用 nMIS (Qnm) のメモリゲート電極 MG が形成されたメモリゲート電極サイドウォール方式を採用している。これに対して、メモリセル MC3 では、メモリ用 nMIS (Qnm) のメモリゲート電極 MG の一部が選択用 nMIS (Qnc) の選択ゲート電極 CG 上に乗り上げたメモリゲート電極乗り上げ方式を採用しており、選択ゲート電極 CG およびメモリゲート電極 MG をそれぞれリソグラフィ技術により形成されたレジストパターンを用いて加工している。メモリセル MC3 のメモリ用 nMIS (Qnm) のメモリゲート電極 MG 以外は、メモリセル MC2 とほぼ同様な構成であるため、その説明は省略する。

【0070】

また、前述のメモリセル MC3 では、メモリ用 nMIS (Qnm) のメモリゲート電極 MG の一部が選択用 nMIS (Qnc) の選択ゲート電極 CG 上に乗り上げたメモリゲート電極乗り上げ方式を採用したが、選択用 nMIS (Qnc) の選択ゲート電極 CG の一部がメモリゲート用 nMIS (Qnm) のメモリゲート電極 MG 上に乗り上げたメモリゲート電極乗り上げ方式を採用することもできる。

【0071】

以上、本発明者によってなされた発明を実施の形態に基づき具体的に説明したが、本発明は前記実施の形態に限定されるものではなく、その要旨を逸脱しない範囲で種々変更可能であることはいうまでもない。

【0072】

例えば前記実施の形態では、電荷保持用絶縁膜の電荷蓄積膜に金属酸化膜である酸化ハフニウム膜を用いたが、これに限定されるものではなく、例えはアルミナ膜、酸化ジルコニアウム膜、酸化タンタル膜、酸化イットリウム膜または酸化ランタン膜等の金属酸化膜を用いることができる。また、これらの金属酸化膜にシリコンを加えたいわゆるシリケート酸化膜 (例えはハフニウムシリケート、ジルコニアムシリケート、アルミニウムシリケートなど) やアルミニウムを加えたアルミネート酸化膜 (例えはハフニウムアルミネート、ジルコニアムアルミネートなど) を用いることができる。また、複数の金属酸化膜が混ざった酸化膜 (例えはハフニウムとランタンが混ざった酸化膜など) を用いることができる。

【産業上の利用可能性】

【0073】

本発明は、金属酸化膜に電荷を蓄える不揮発性メモリセルを有する半導体記憶装置に適用することができる。

## 【図面の簡単な説明】

## 【0074】

【図1】本発明の一実施の形態による単体ゲート構造のMONOS型メモリセルを用いたメモリアレイの構成を示すワード線およびビット線の平面レイアウト図である。

【図2】本発明の一実施の形態による単体ゲート構造のMONOS型メモリセルをゲート長方向に沿って切断したメモリセルの要部断面図である。

【図3】本発明の一実施の形態による単体ゲート構造のMONOS型メモリセルの製造工程中の要部断面図である。

【図4】図3に続くMONOS型メモリセルの製造工程中の図3と同じ箇所の要部断面図である。

10

【図5】図4に続くMONOS型メモリセルの製造工程中の図3と同じ箇所の要部断面図である。

【図6】(a)は、酸化シリコン膜中の上面側にプラズマ窒化処理により窒化領域を形成した試料の膜厚方向の組成分布を示すグラフ図、(b)は、酸化シリコン膜中に窒化領域を形成しない試料の膜厚方向の組成分布を示すグラフ図である。

【図7】本発明の一実施の形態によるMONOS型メモリセルの電荷保持特性の窒素濃度依存性を説明するグラフ図である。

【図8】本発明の一実施の形態によるMONOS型メモリセルの窒化領域有無による電荷保持特性の違いを説明するグラフ図である。

【図9】本発明の一実施の形態によるスプリットゲート構造のMONOS型メモリセル(メモリゲート電極サイドウォール方式)をゲート長方向に沿って切断したメモリセルの要部断面図である。

20

【図10】本発明の一実施の形態によるスプリットゲート構造のMONOS型メモリセル(メモリゲート電極乗り上げ方式)をゲート長向に沿って切断したメモリセルの要部断面図である。

## 【符号の説明】

## 【0075】

1 半導体基板

2 pウェル

3 s ソース領域

3 d ドレイン領域

4 電荷保持用絶縁膜

4 a ボトム絶縁膜(第1絶縁膜)

4 b 窒化領域

4 c 電荷蓄積膜

4 d 窒化領域

4 e トップ絶縁膜(第2絶縁膜)

5 メモリゲート電極

6 側壁膜

7 層間絶縁膜

11 半導体基板

12 a d , 12 a s , 12 b 半導体領域

13 シリサイド層

14 ゲート絶縁膜

15 半導体領域

16 電荷保持用絶縁膜

16 a ボトム絶縁膜

16 c 電荷蓄積膜

16 e トップ絶縁膜

17 半導体領域

10

20

30

40

50

1 8 層間絶縁膜

1 9 コンタクトホール

2 0 プラグ

B L ビット線

C G 選択ゲート電極

D r m ドレイン

M 1 配線

M C 1 メモリセル

M G メモリゲート電極

S r m ソース領域

W L ワード線

10

【図1】

図1

【図2】

図2

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

---

フロントページの続き

審査官 須原 宏光

(56)参考文献 特開2007-184380(JP,A)

(58)調査した分野(Int.Cl., DB名)

H01L 21/8247

H01L 27/115

H01L 29/788