Office de la Propriété

Intellectuelle

du Canada

Un organisme

d'Industrie Canada

Canadian

Intellectual Property

Office

An agency of

Industry Canada

CA 2479657 A1 2003/10/09

(21) **2 479 657**

(12) **DEMANDE DE BREVET CANADIEN**

**CANADIAN PATENT APPLICATION**

(13) **A1**

(86) Date de dépôt PCT/PCT Filing Date: 2003/03/19

(87) Date publication PCT/PCT Publication Date: 2003/10/09

(85) Entrée phase nationale/National Entry: 2004/09/16

(86) N° demande PCT/PCT Application No.: US 2003/008355

(87) N° publication PCT/PCT Publication No.: 2003/083950

(30) Priorité/Priority: 2002/03/25 (10/107,001) US

(51) Cl.Int.<sup>7</sup>/Int.Cl.<sup>7</sup> H01L 29/205, H01L 29/778, H01L 21/36,

H01L 31/0304, H01L 33/00

(71) Demandeur/Applicant:

CREE, INC., US

(72) Inventeurs/Inventors:

FLYNN, JEFFREY S., US;

BRANDES, GEORGE R., US

(74) Agent: KIRBY EADES GALE BAKER

(54) Titre : MATERIAUX DOPES AUX NITRURES DES GROUPES III-V ET DISPOSITIFS MICROELECTRONIQUES

AINSII QUE STRUCTURES DE PRECURSEURS DE DISPOSITIFS LES COMPRENNANT

(54) Title: DOPED GROUP III-V NITRIDE MATERIALS, AND MICROELECTRONIC DEVICES AND DEVICE

PRECURSOR STRUCTURES COMPRISING SAME

(57) Abrégé/Abstract:

A Group III-V nitride microelectronic device structure including a delta doped layer (24) and/or a doped superlattice. A delta doping method is described, including the steps of: depositing semiconductor material on a substrate by a first epitaxial film growth process; terminating the deposition of semiconductor material on the substrate to present an epitaxial film surface; delta doping the semiconductor material at the epitaxial film surface, to form a delta doping layer thereon; terminating the delta doping; resuming deposition of semiconductor material to deposit semiconductor material on the delta doping layer, in a second epitaxial film growth process; and continuing the semiconductor material second epitaxial film growth process to a predetermined extent, to form a doped microelectronic device structure, wherein the delta doping layer (24) is internalized in semiconductor material deposited in the first and second epitaxial film growth processes.

## (12) INTERNATIONAL APPLICATION PUBLISHED UNDER THE PATENT COOPERATION TREATY (PCT)

(19) World Intellectual Property Organization

International Bureau(43) International Publication Date

9 October 2003 (09.10.2003)

PCT

(10) International Publication Number

WO 03/083950 A1

(51) International Patent Classification<sup>7</sup>: **H01L 29/205**, 29/778, 33/00, 31/0304, 21/36

(21) International Application Number: PCT/US03/08355

(22) International Filing Date: 19 March 2003 (19.03.2003)

(25) Filing Language: English

(26) Publication Language: English

(30) Priority Data: 10/107,001 25 March 2002 (25.03.2002) US

(71) Applicant: **ADVANCED TECHNOLOGY MATERIALS, INC.** [US/US]; 7 Commerce Drive, Danbury, CT 06810 (US).

(72) Inventors: **FLYNN, Jeffrey, S.**; 392 Goshen Road, Litchfield, CT 06759 (US). **BRANDES, George, R.**; 77 Shane Drive, Southbury, CT 06488 (US).

(74) Agent: **RYANN, William, F.**; **ADVANCED TECHNOLOGY MATERIALS, INC.**, 7 Commerce Drive, Danbury, CT 06810 (US).

(81) Designated States (national): AE, AG, AL, AM, AT, AU, AZ, BA, BB, BG, BR, BY, BZ, CA, CH, CN, CO, CR, CU, CZ, DE, DK, DM, DZ, EC, EE, ES, FI, GB, GD, GE, GH, GM, HR, HU, ID, IL, IN, IS, JP, KE, KG, KP, KR, KZ, LC, LK, LR, LS, LT, LU, LV, MA, MD, MG, MK, MN, MW, MX, MZ, NI, NO, NZ, OM, PH, PL, PT, RO, RU, SC, SD, SE, SG, SK, SL, TJ, TM, TN, TR, TT, TZ, UA, UG, UZ, VC, VN, YU, ZA, ZM, ZW.

(84) Designated States (regional): ARIPO patent (GH, GM, KE, LS, MW, MZ, SD, SL, SZ, TZ, UG, ZM, ZW), Eurasian patent (AM, AZ, BY, KG, KZ, MD, RU, TJ, TM), European patent (AT, BE, BG, CH, CY, CZ, DE, DK, EE, ES, FI, FR, GB, GR, HU, IE, IT, LU, MC, NL, PT, RO, SE, SI, SK, TR), OAPI patent (BF, BJ, CF, CG, CI, CM, GA, GN, GQ, GW, ML, MR, NE, SN, TD, TG).

**Published:**

- with international search report

- before the expiration of the time limit for amending the claims and to be republished in the event of receipt of amendments

*For two-letter codes and other abbreviations, refer to the "Guidance Notes on Codes and Abbreviations" appearing at the beginning of each regular issue of the PCT Gazette.*

---

(54) Title: DOPED GROUP III-V NITRIDE MATERIALS, AND MICROELECTRONIC DEVICES AND DEVICE PRECURSOR STRUCTURES COMPRISING SAME

WO 03/083950 A1

(57) Abstract: A Group III-V nitride microelectronic device structure including a delta doped layer (24) and/or a doped superlattice. A delta doping method is described, including the steps of: depositing semiconductor material on a substrate by a first epitaxial film growth process; terminating the deposition of semiconductor material on the substrate to present an epitaxial film surface; delta doping the semiconductor material at the epitaxial film surface, to form a delta doping layer thereon; terminating the delta doping; resuming deposition of semiconductor material to deposit semiconductor material on the delta doping layer, in a second epitaxial film growth process; and continuing the semiconductor material second epitaxial film growth process to a predetermined extent, to form a doped microelectronic device structure, wherein the delta doping layer (24) is internalized in semiconductor material deposited in the first and second epitaxial film growth processes.

**DOPED GROUP III-V NITRIDE MATERIALS, AND MICROELECTRONIC

DEVICES AND DEVICE PRECURSOR STRUCTURES COMPRISING SAME**

5

**BACKGROUND OF THE INVENTION**

**Field Of The Invention**

This invention relates to doped Group III-V nitride materials, e.g., aluminum gallium

10 nitride (AlGaN), gallium nitride (GaN) and indium gallium nitride (InGaN) materials,

methods of forming such materials, and microelectronic devices and device precursor

structures comprising such materials.

**Description of the Related Art**

15 Group III/V nitride semiconductors have significant potential as useful materials in high-

temperature, high frequency and high power microelectronics and ultra-violet/blue/green

optoelectronics by virtue of their wide bandgaps, high thermal conductivities and large

electrical breakdown fields.

20 Microelectronic device applications include AlGaN-GaN multilayer-based laser diodes,

high electron mobility transistors (HEMTs), field effect transistors (FETs),

heterojunction bipolar transistors (HBTs), light emitting diodes (LEDs) and ultra-violet

photodetectors, as well as (Al,In,Ga)N-based devices generally, including devices for

high-frequency, high-power communications, for high-density optical storage, full-color

25 displays, and for other wide bandgap semiconductor applications.

Aluminum gallium nitride (AlGaN) and gallium nitride (GaN) materials are particularly promising Group III-V nitride materials for next generation electronic and optoelectronic devices for wireless and optical communications systems. Nonetheless, Group III-V nitride materials have inherent limitations that pose challenges to their development and

5 deployment.

More specifically, there is a need to improve the doping of III-V nitride semiconductor materials, to achieve the following:

- a) increased carrier mobility;

- 10 b) broader doping ranges;

- c) reduced dopant activation energy;

- d) reduced resistivity associated with concurrent improvements of increased carrier mobility and broader doping ranges;

- e) enhanced reproducibility of characteristics a) - d).

- 15 f) elimination of the need to activate the dopant impurity or alternatively of reducing the temperature/time requirement for dopant activation;

- g) removal of active areas changes to the nitride material induced through incorporation of the impurity;

- h) minimization of the changes to the nitride material resulting from incorporation

- 20 of the dopant impurity; and

i) ability to selectively vary the properties of the doped III-V nitride material, e.g., resistivity (in contrast to (d) above, it may be desirable in some applications to increase resistivity, or to otherwise vary other material properties).

5 The art has not satisfactorily resolved these issues, which are addressed by the present invention.

### **SUMMARY OF THE INVENTION**

10 The present invention relates to doped Group III-V nitrides, e.g., aluminum gallium nitride (AlGaN), indium gallium nitride (InGaN) and gallium nitride (GaN) materials, methods of forming such materials, and microelectronic devices and device precursor structures comprising such materials.

15 The present invention in one aspect contemplates delta doping of Group III-V nitrides, e.g., GaN and related nitrides, as well as superlattice doping of such materials.

As used herein, the term “Group III-V nitride” refers to semiconductor material including nitrogen and at least one of Al, In and Ga.

The present invention relates to Group III-V nitride materials, (Al,In,Ga)N and devices and device structures comprising such materials. The term (Al,In,Ga)N includes all permutations of nitrides including one or more of Al, In and Ga, and thus encompasses as alternative materials AlN, InN, GaN, AlInN, AlGaN, InGaN and AlInGaN, wherein the 5 stoichiometric coefficients of Al, In, and Ga in compounds containing two, or all three, of such metals may have any appropriate values between 0 and 1 with the proviso that the sum of all such stoichiometric coefficients is 1. In this respect, impurities such as hydrogen or carbon, dopants, or strain-altering materials such as boron can also be incorporated in the (Al,In,Ga)N material, but the sum of all stoichiometric coefficients is 10 1 within a variation of  $\pm 0.1\%$ . Examples of such compounds include  $\text{Al}_x\text{Ga}_{1-x}\text{N}$  wherein  $0 \leq x \leq 1$ , and  $\text{Al}_x\text{In}_y\text{Ga}_{1-x-y}\text{N}$  wherein  $0 \leq x \leq 1$  and  $0 \leq y \leq 1$ . Preferred materials of interest in the practice of the present invention include GaN and AlGaN.

In one aspect, the invention relates to a Group III-V nitride microelectronic device 15 structure including a delta doped layer and/or a doped superlattice.

In another aspect, the invention relates to a Group III-V nitride microelectronic device structure including a delta doped layer.

20 The delta doped layer can for example be formed intermediate undoped III-V nitride layers of said device structure.

The Group III-V nitride layers can for example comprise AlGaN or GaN, and the delta doped layer may include a dopant species selected from the group consisting of Si, Ge, 25 Mg, C, O, Ca, Zn, Li, Mn, Na, K, Cd, Rb, Sr, Sc and Be.

The microelectronic device structure can by way of example comprise a device structure selected from the group consisting of LEDs, laser diodes, AlGaN/GaN high electron mobility transistors (HEMTs), contact structures, isolation structures, AlGaN FETs, optoelectronic transistor detectors, tunnel doped structures, doped base heterojunction 5 bipolar transistors (HBTs), and optical filters.

In another aspect, the invention relates to a Group III-V nitride microelectronic device structure including a doped III-V nitride superlattice.

10 Other aspects, features and embodiments of the invention will be more fully apparent from the ensuing disclosure and appended claims.

#### **BRIEF DESCRIPTION OF THE DRAWINGS**

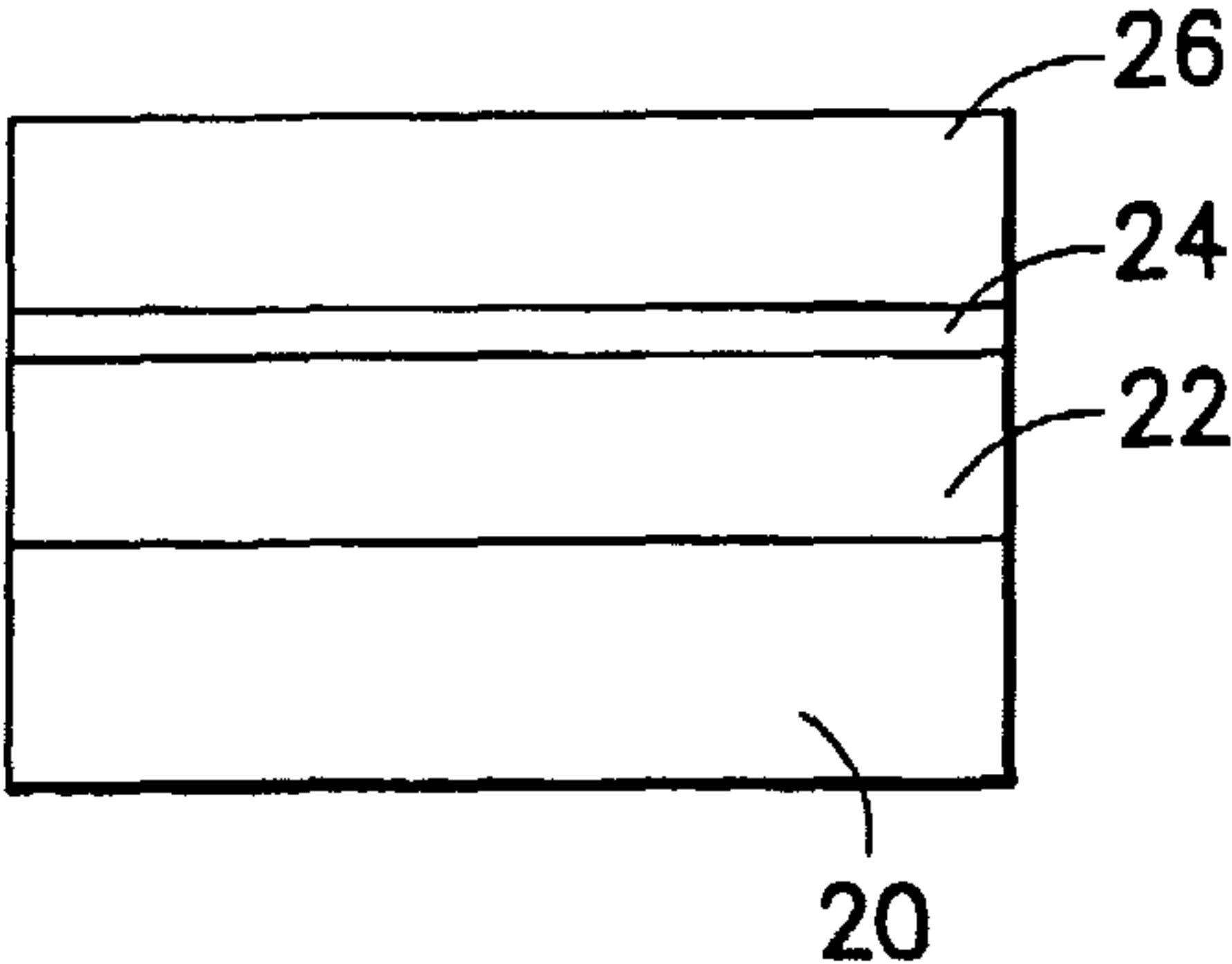

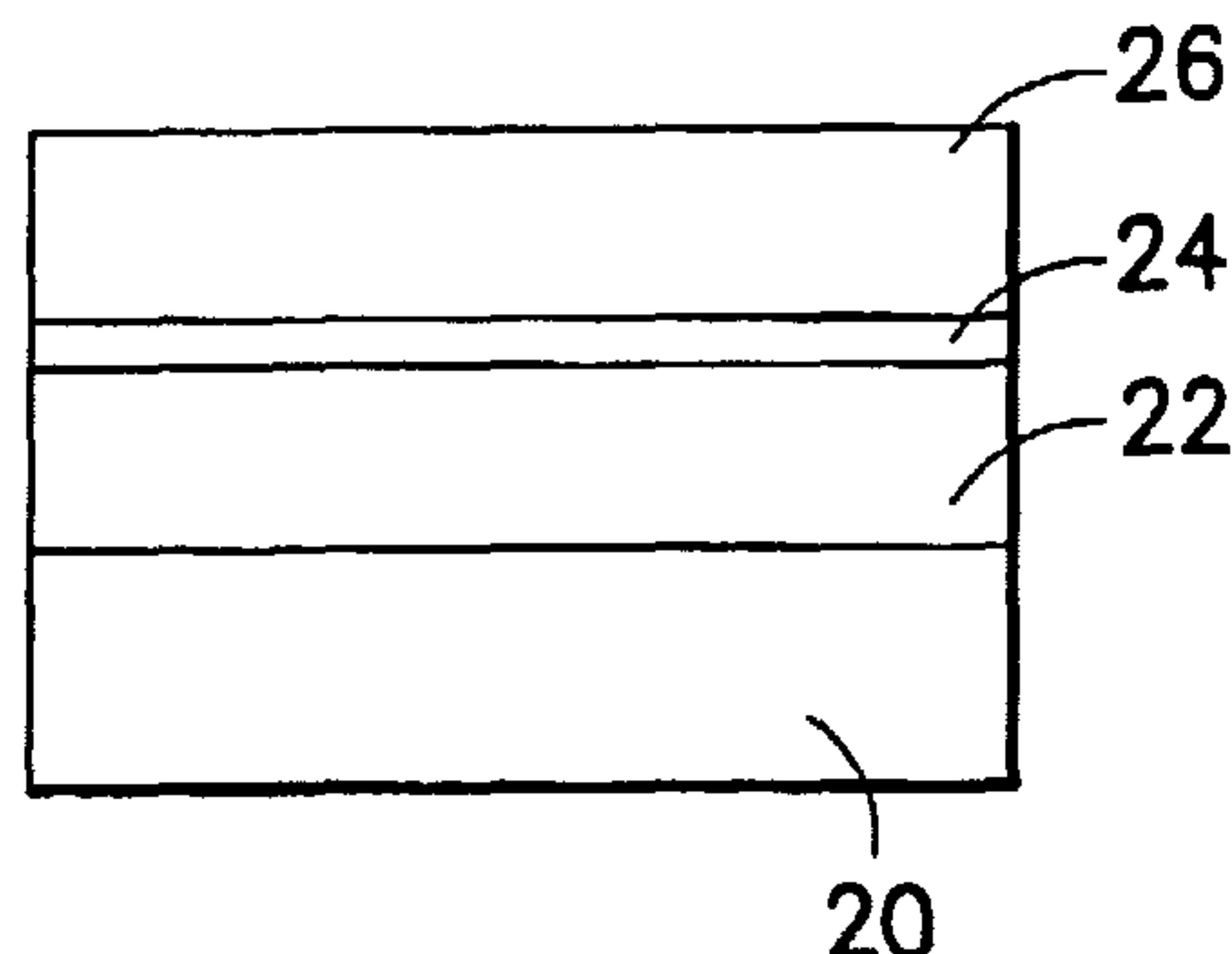

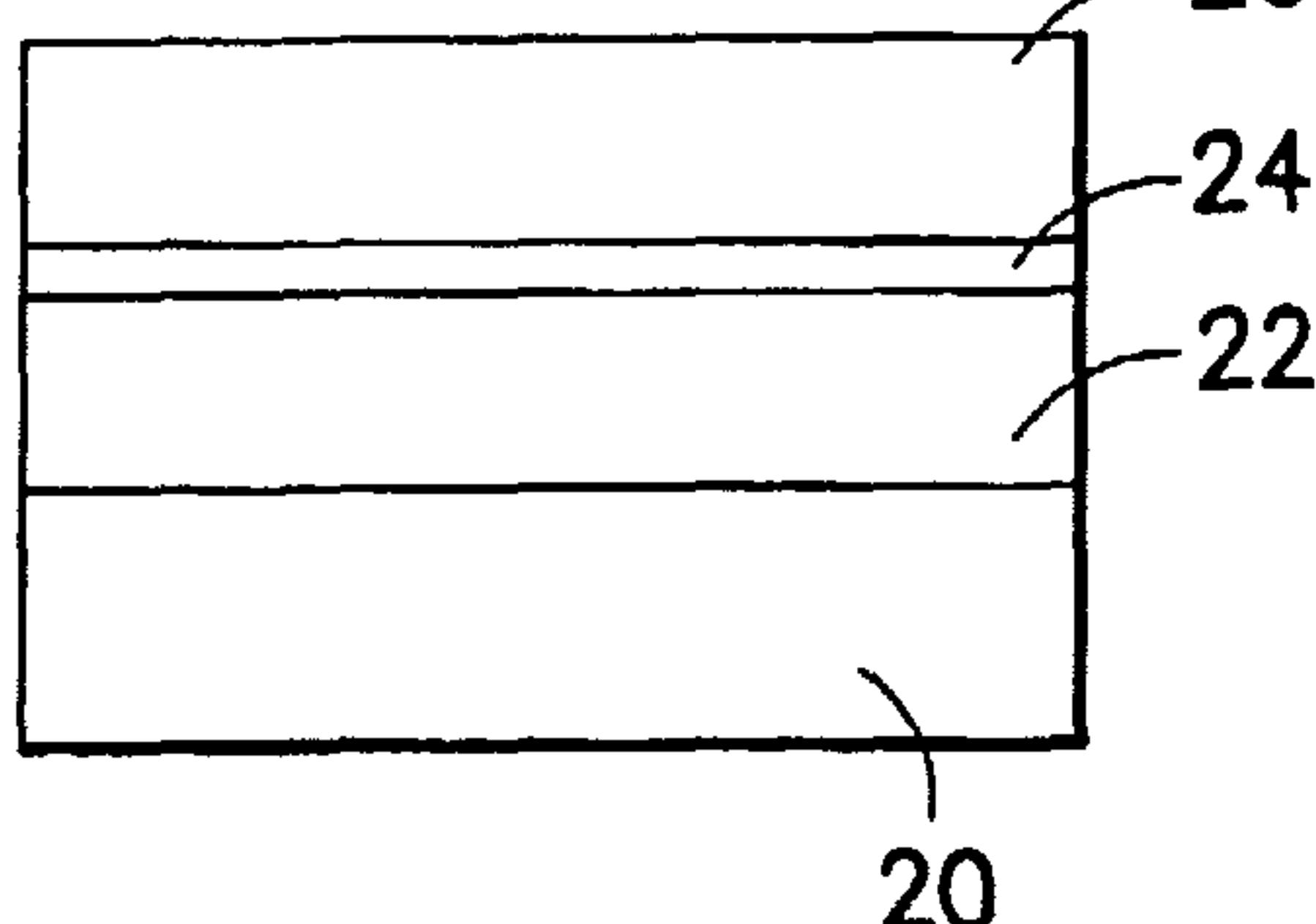

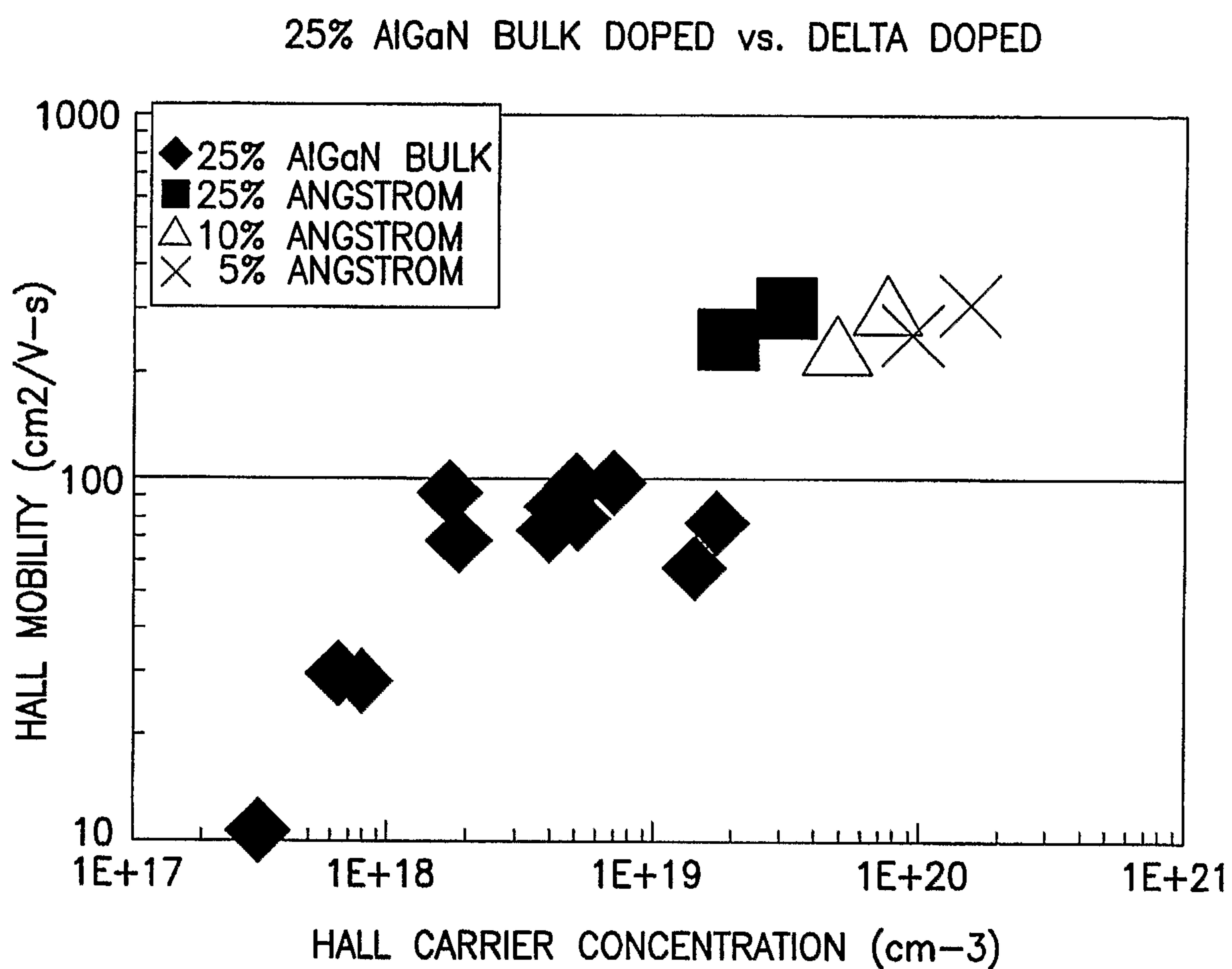

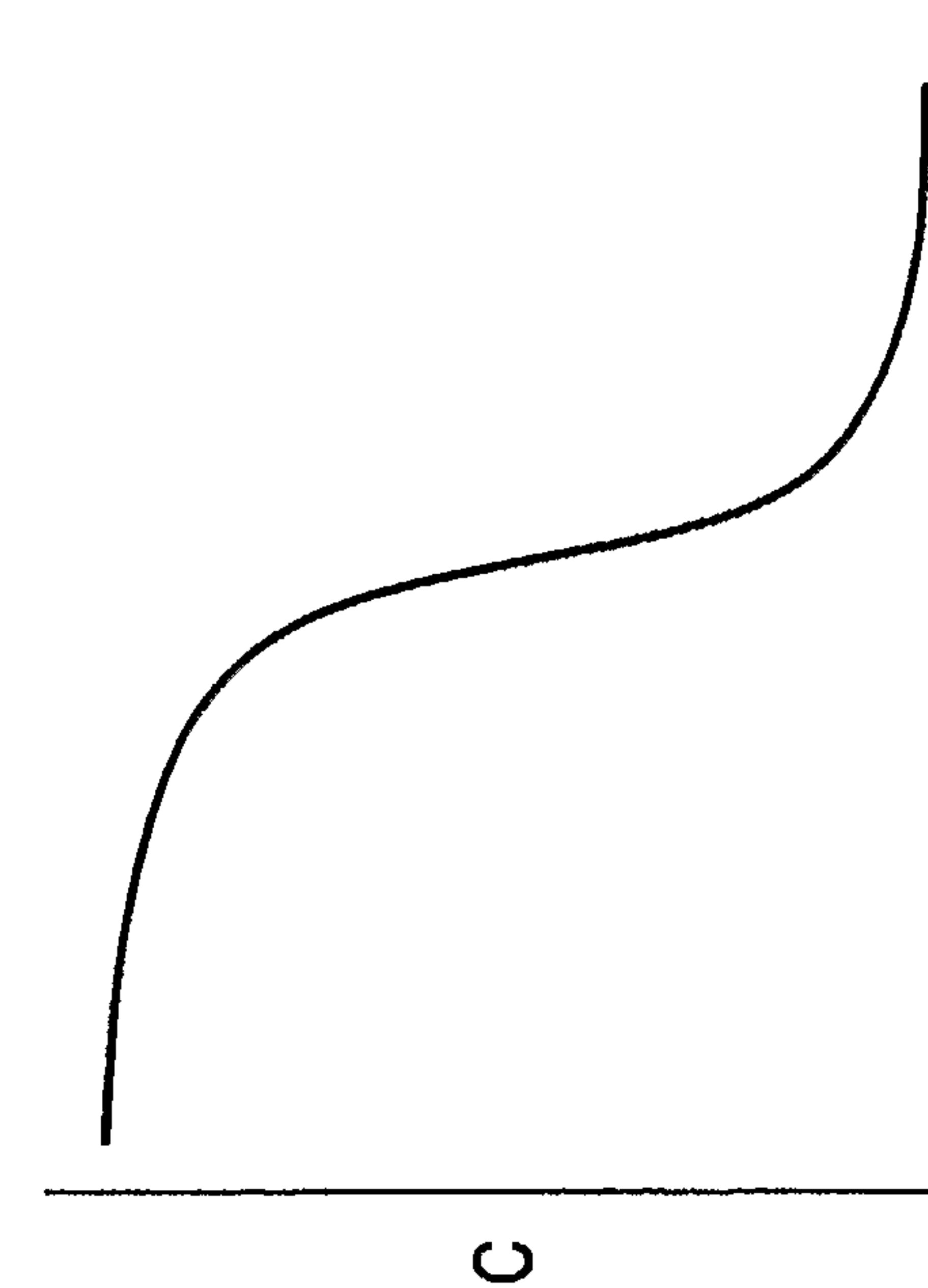

15 Figure 1 is a plot of room temperature Hall mobility as a function of Hall carrier concentration for delta doped  $\text{Al}_{0.25}\text{Ga}_{0.75}\text{N}$  layers and bulk doped structures (Hall carrier concentration in delta doped layers is defined as Hall sheet charge divided by layer thickness; C-V data shows layer thickness ranged from 5 to 25 Angstroms).

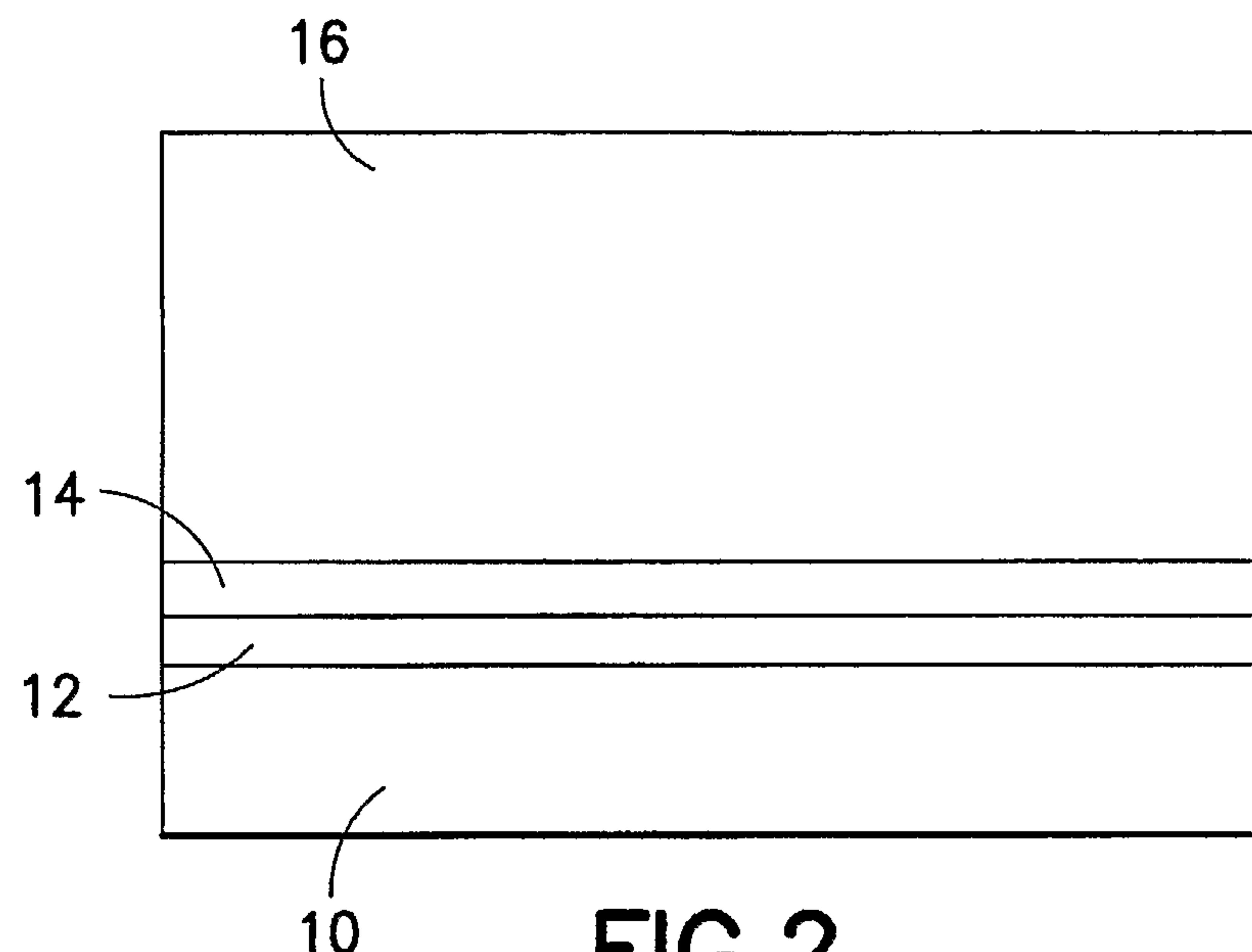

20 Figure 2 is a schematic illustration of a delta-doped HEMT structure.

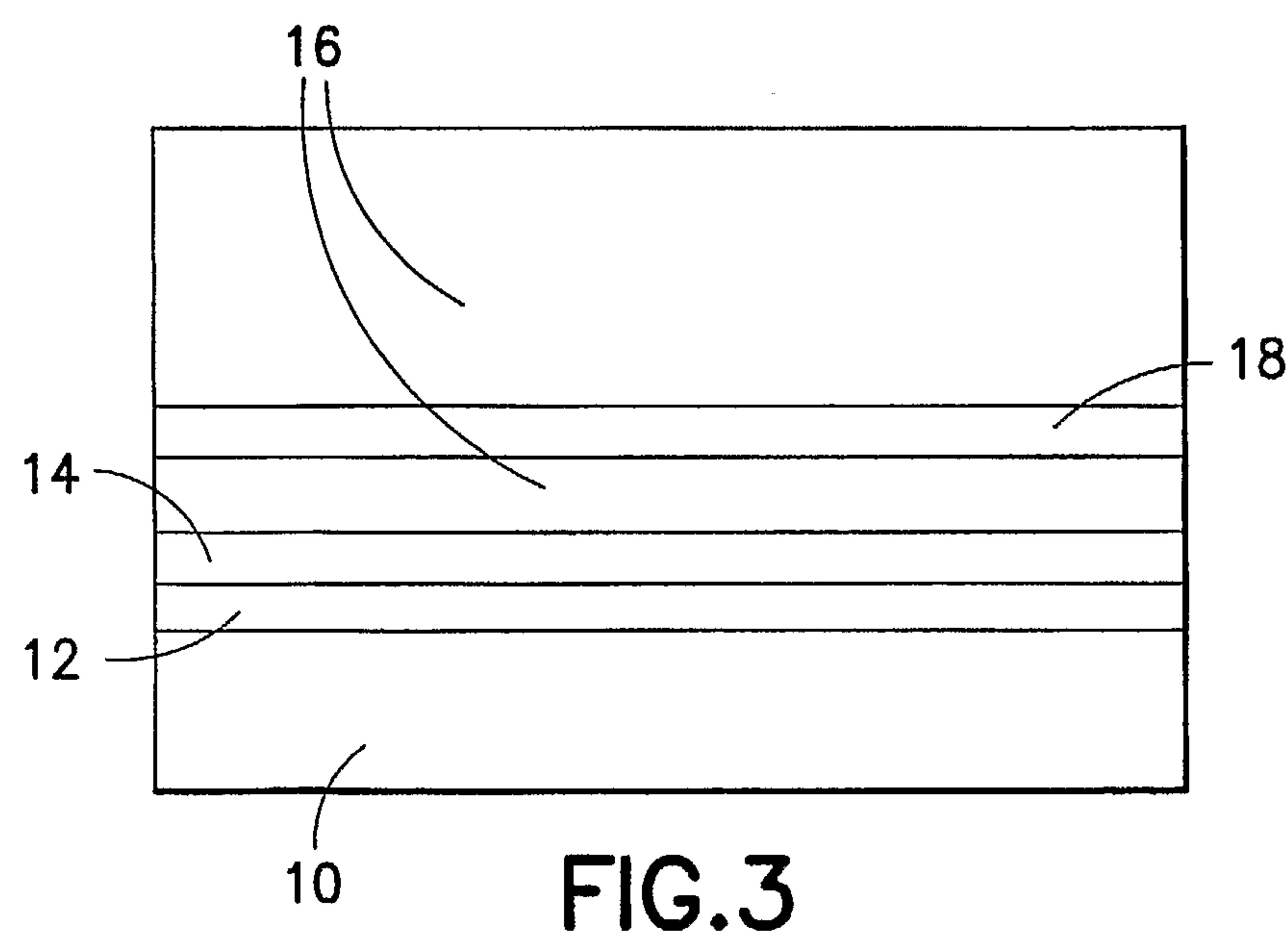

Figure 3 is a schematic illustration of an undoped HEMT structure.

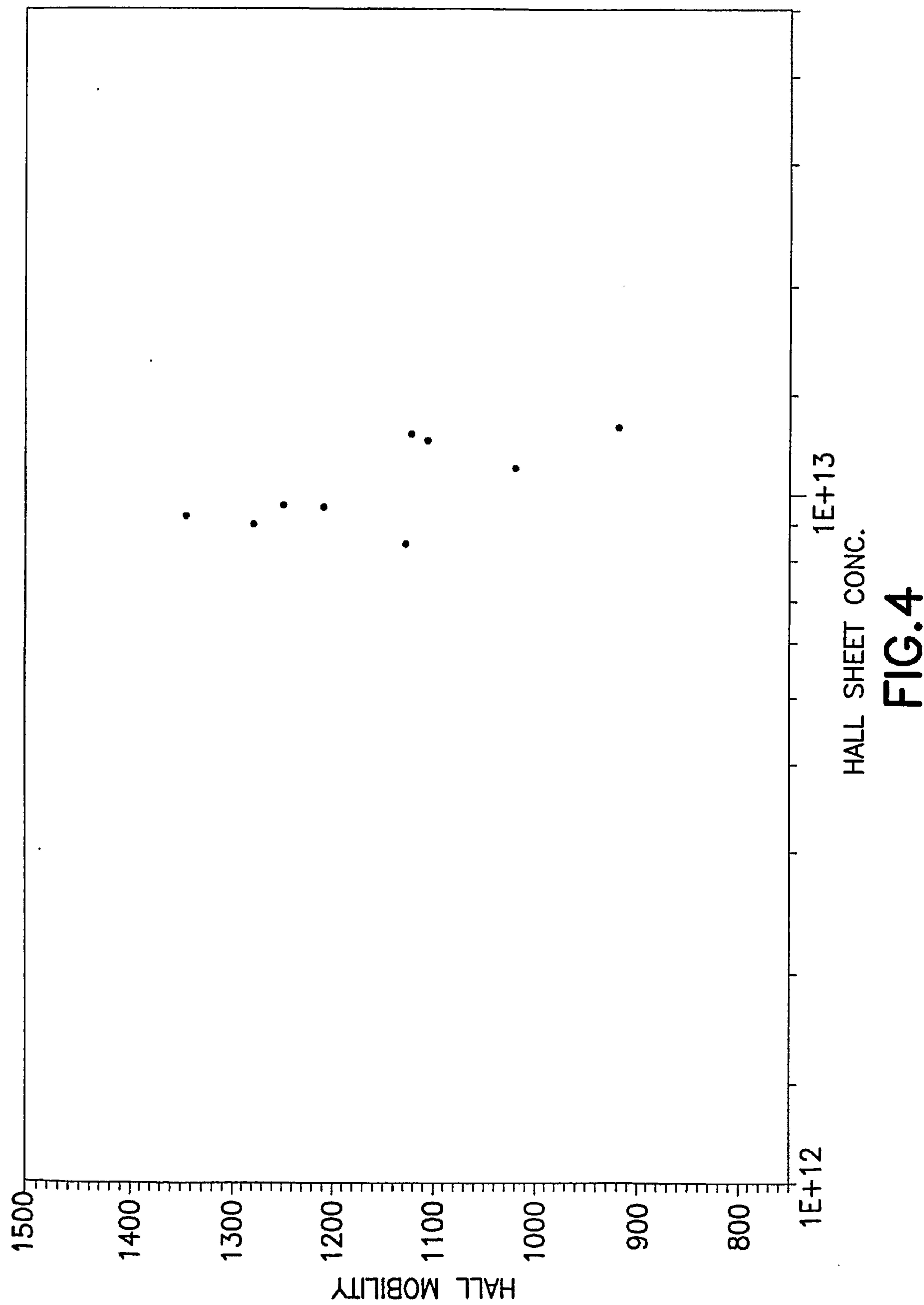

Figure 4 is a plot of Hall mobility ( $\text{cm}^2 \text{ V}^{-1} \text{ s}^{-1}$ ) vs. Hall sheet charge ( $\text{cm}^{-2}$ ) for 300 Angstrom  $\text{Al}_{0.30}\text{Ga}_{0.70}\text{N}$  HEMTs on sapphire.

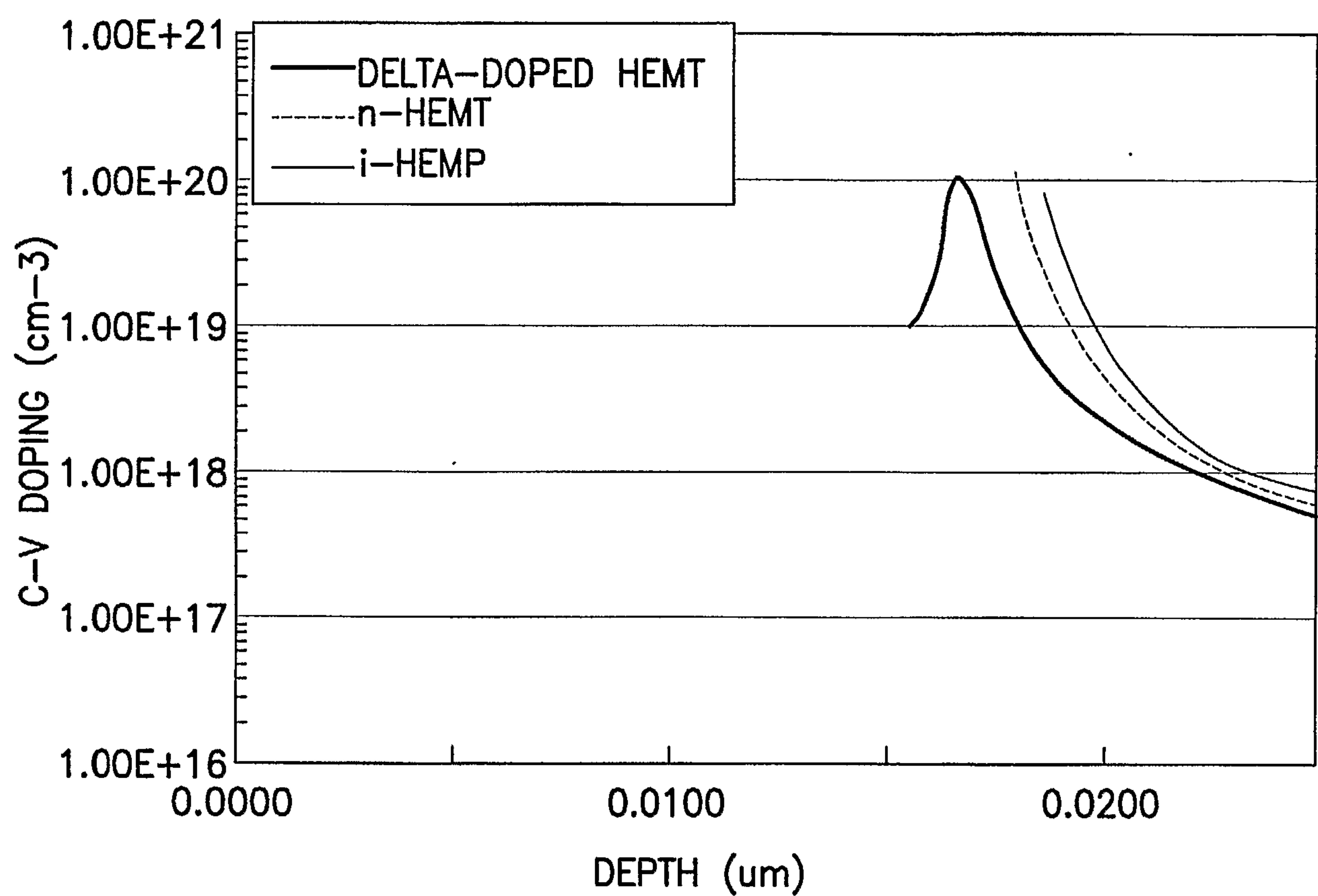

Figure 5 is a plot of C-V doping ( $\text{cm}^{-3}$ ) as a function of depth ( $\mu\text{m}$ ), for an I-HEMT 5 device of Structure A, a delta doped HEMT device of Structure B, and an n-HEMT of Structure C.

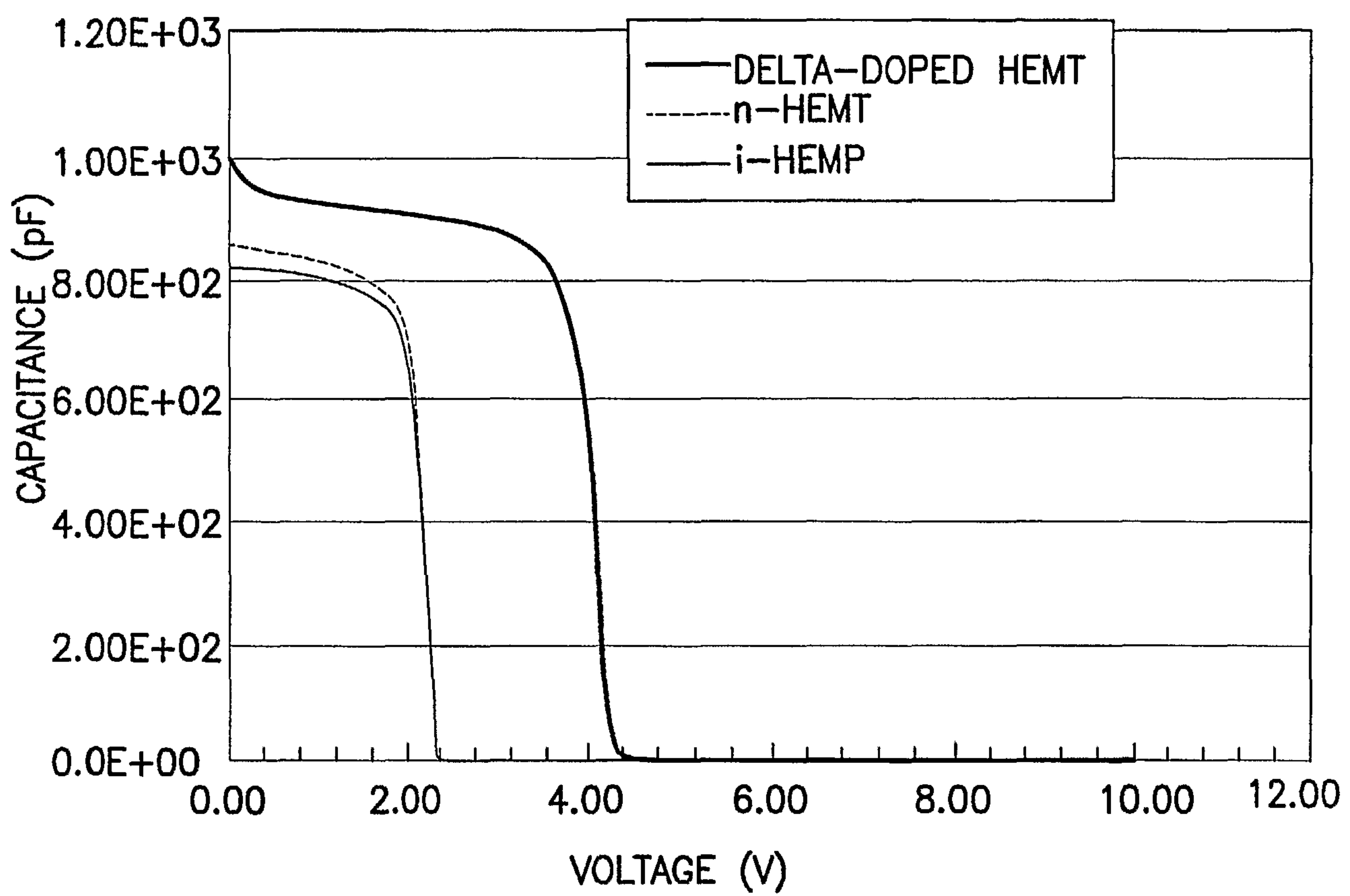

Figure 6 is a plot of Capacitance (pF) as a function of voltage (V), for an I-HEMT device of Structure A, a delta doped HEMT device of Structure B, and an n-HEMT of Structure 10 C.

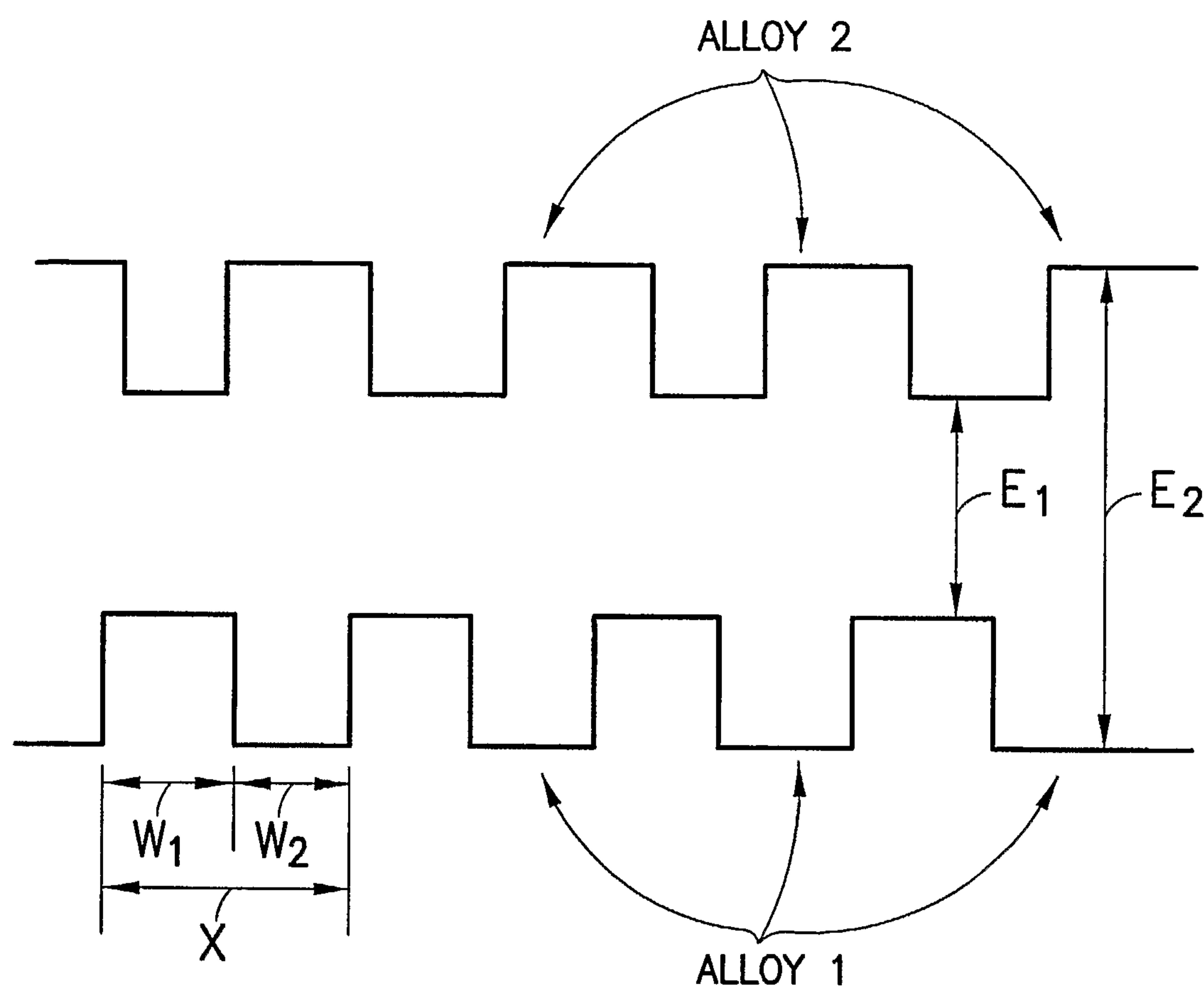

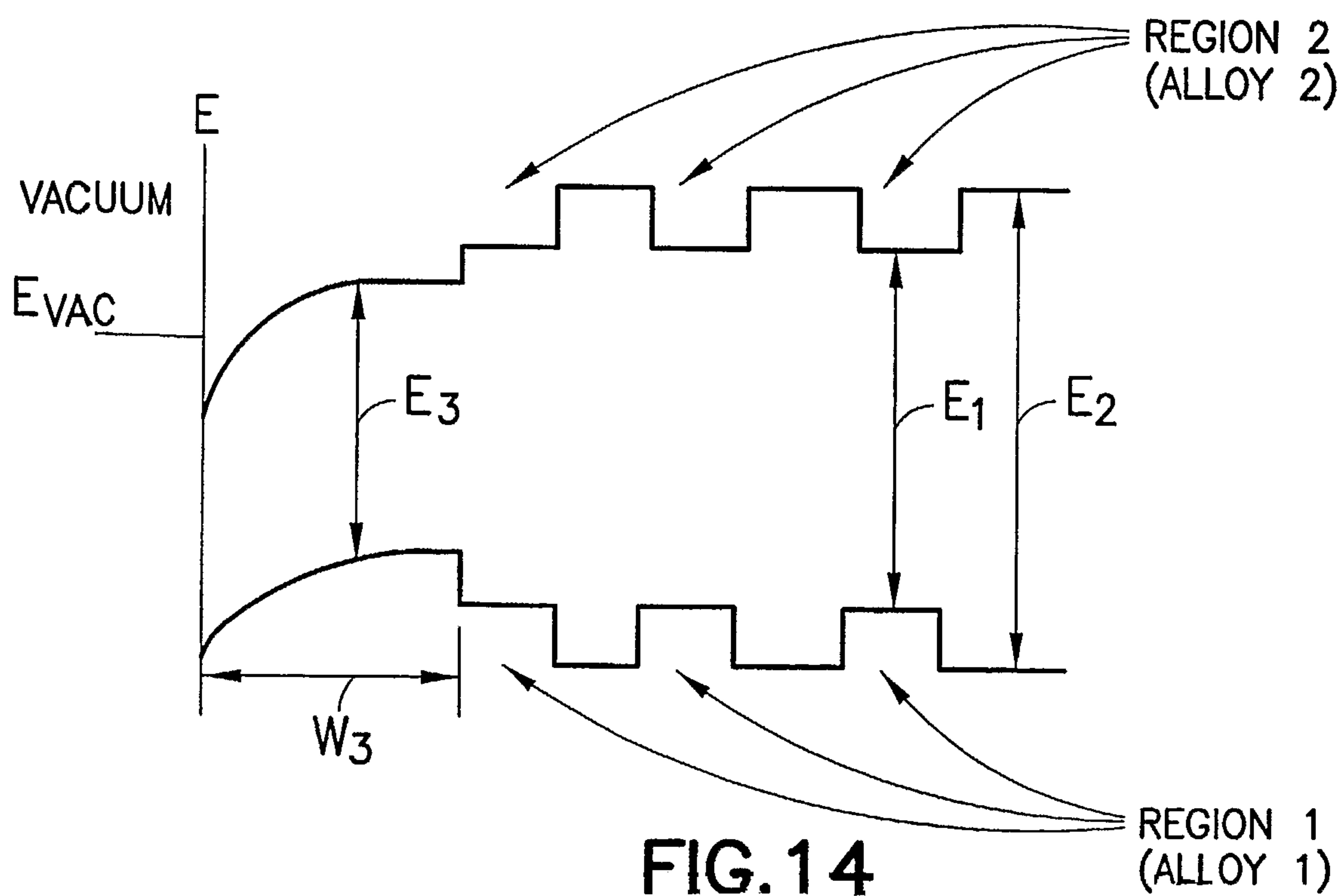

Figure 7 is an energy bandgap diagram for a two alloy superlattice structure.

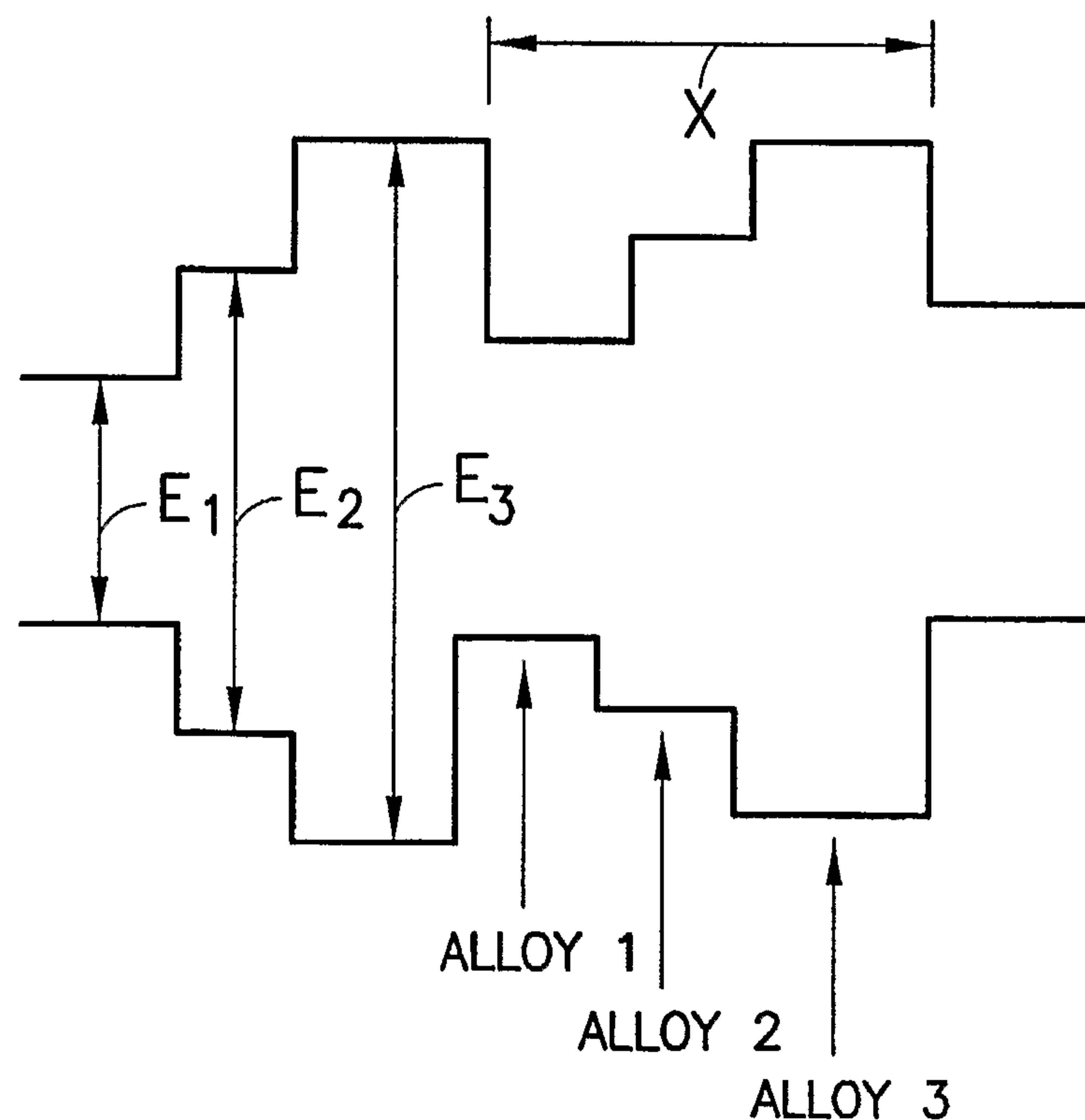

Figure 8 is an energy bandgap diagram for a three alloy superlattice structure.

15

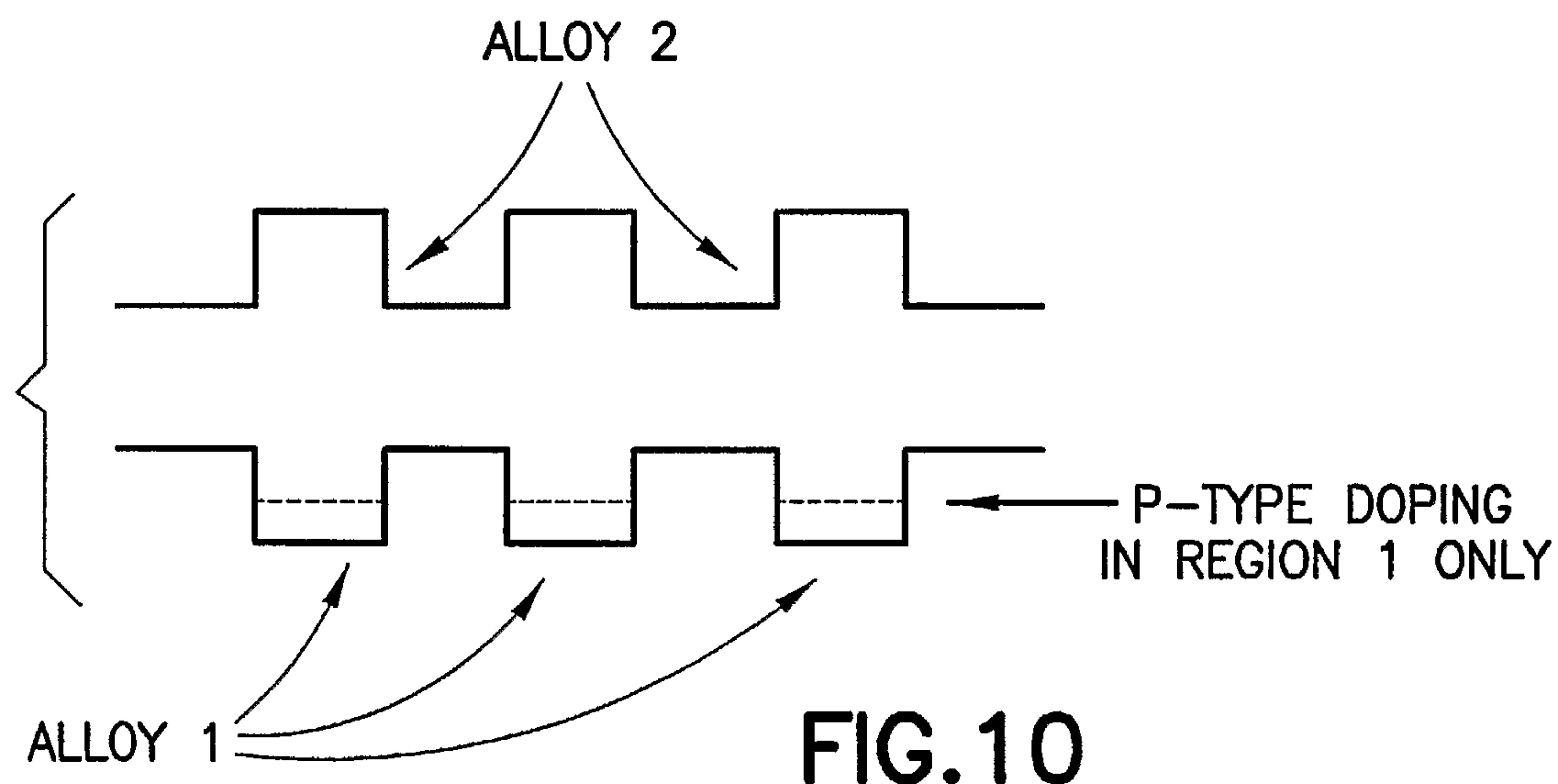

Figure 9 is an energy bandgap for a superlattice structure having n-type doping in alloy 1 and alloy 2.

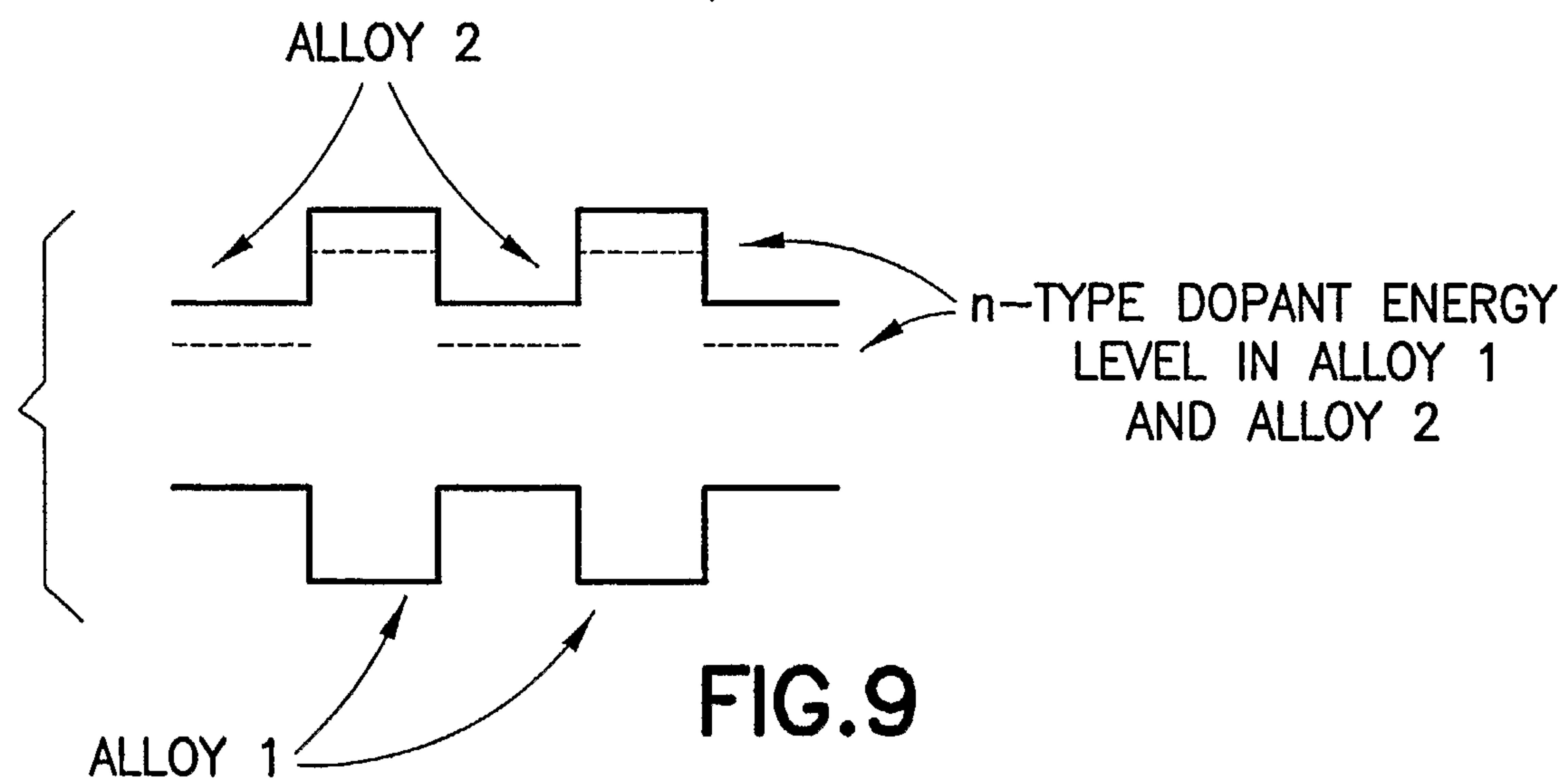

Figure 10 is an energy bandgap for a superlattice structure having p-type doping in 20 Region 1 only.

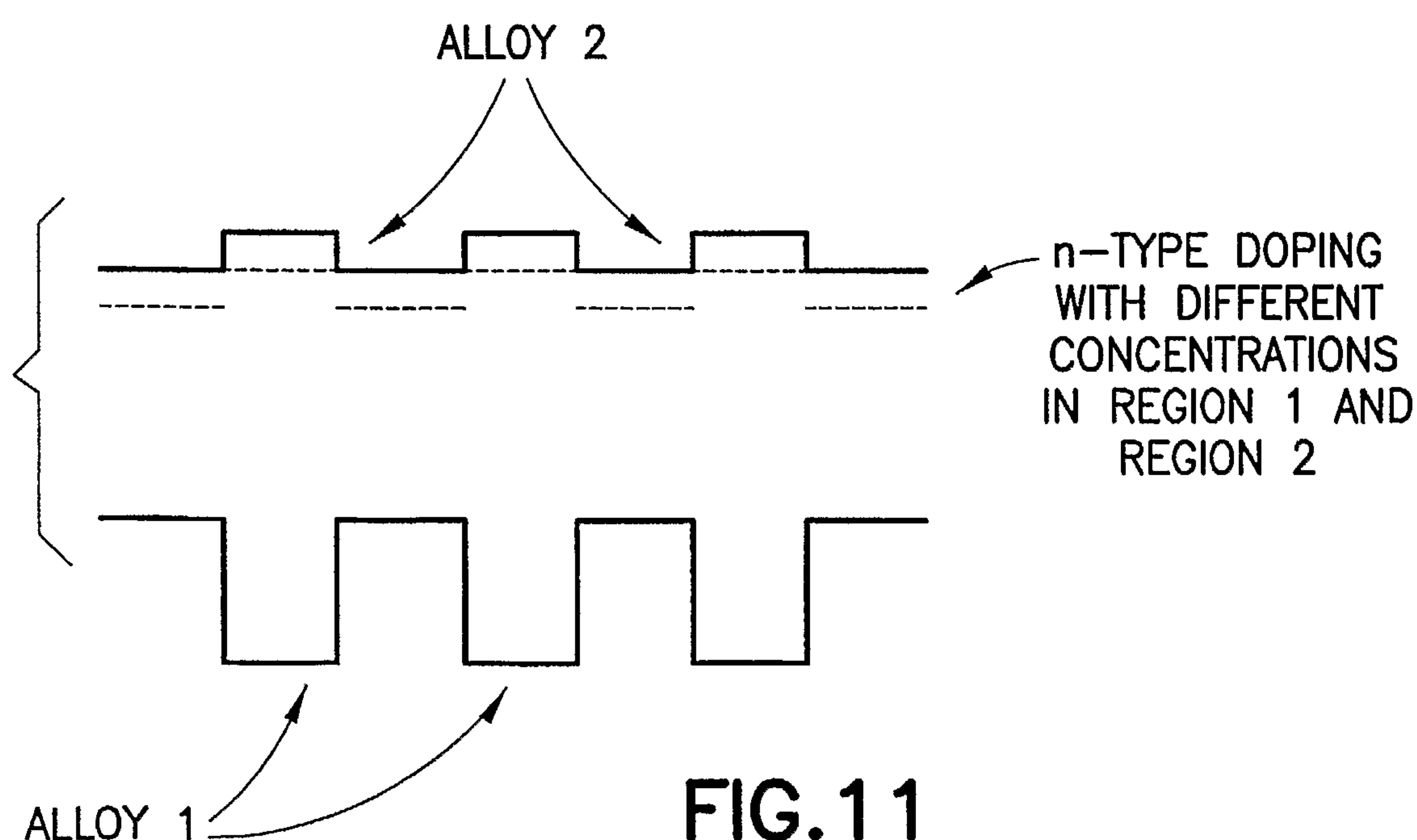

Figure 11 is an energy bandgap for a superlattice structure having n-type doping at different concentrations in Region 1 and Region 2.

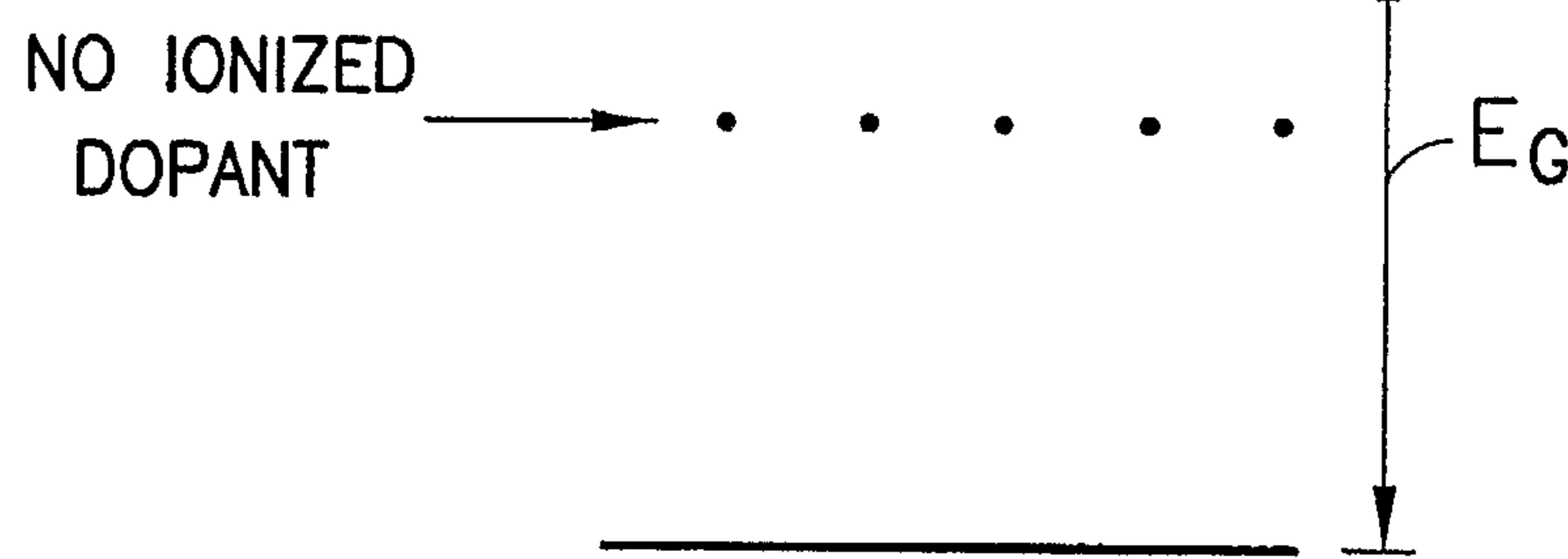

Figure 12 is an energy diagram for Alloy 1, having no associated ionized dopant 5 impurities.

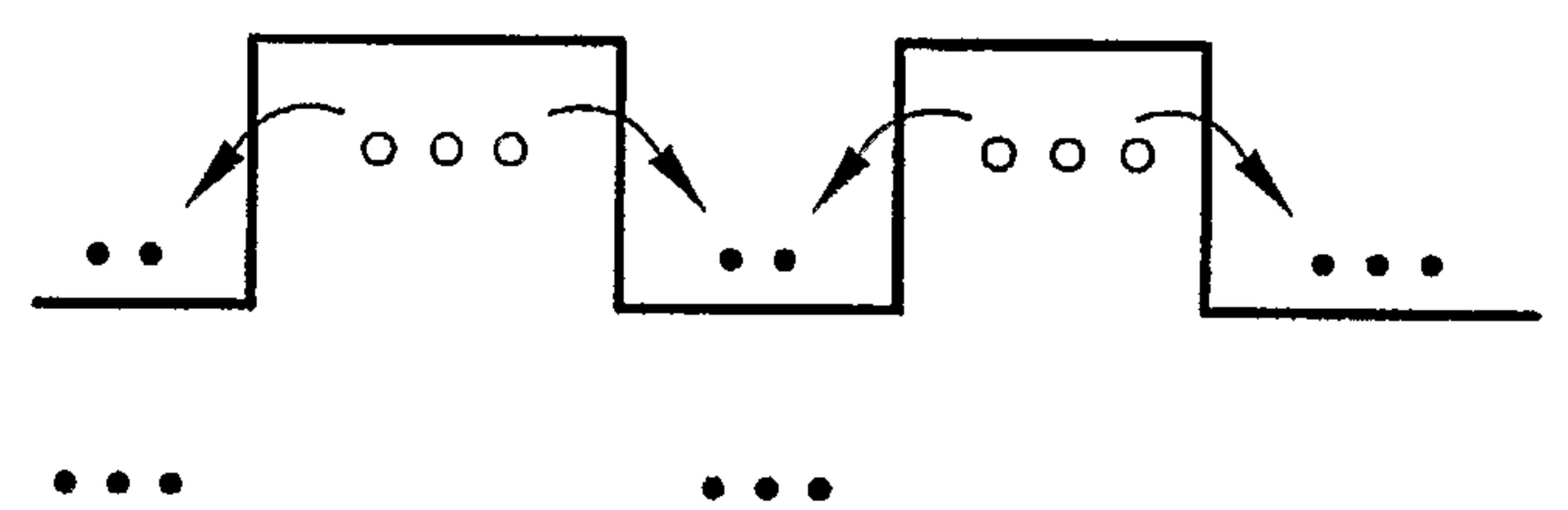

Figure 13 is an energy diagram for a superlattice structure in which higher conductivity arises from carriers in Region 1 that originate from dopants in Region 2.

10 Figure 14 is a schematic structure of a high Al content photocathode.

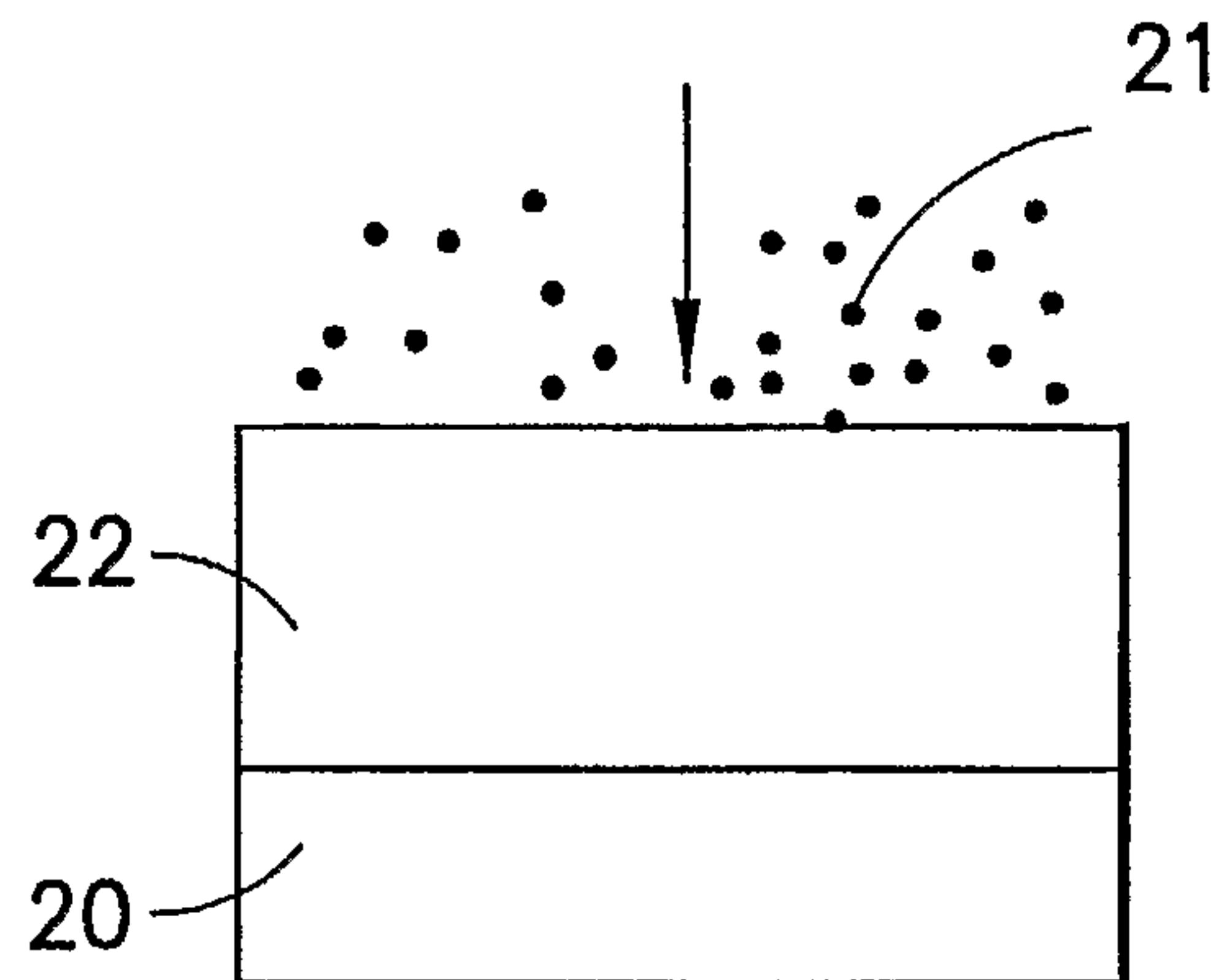

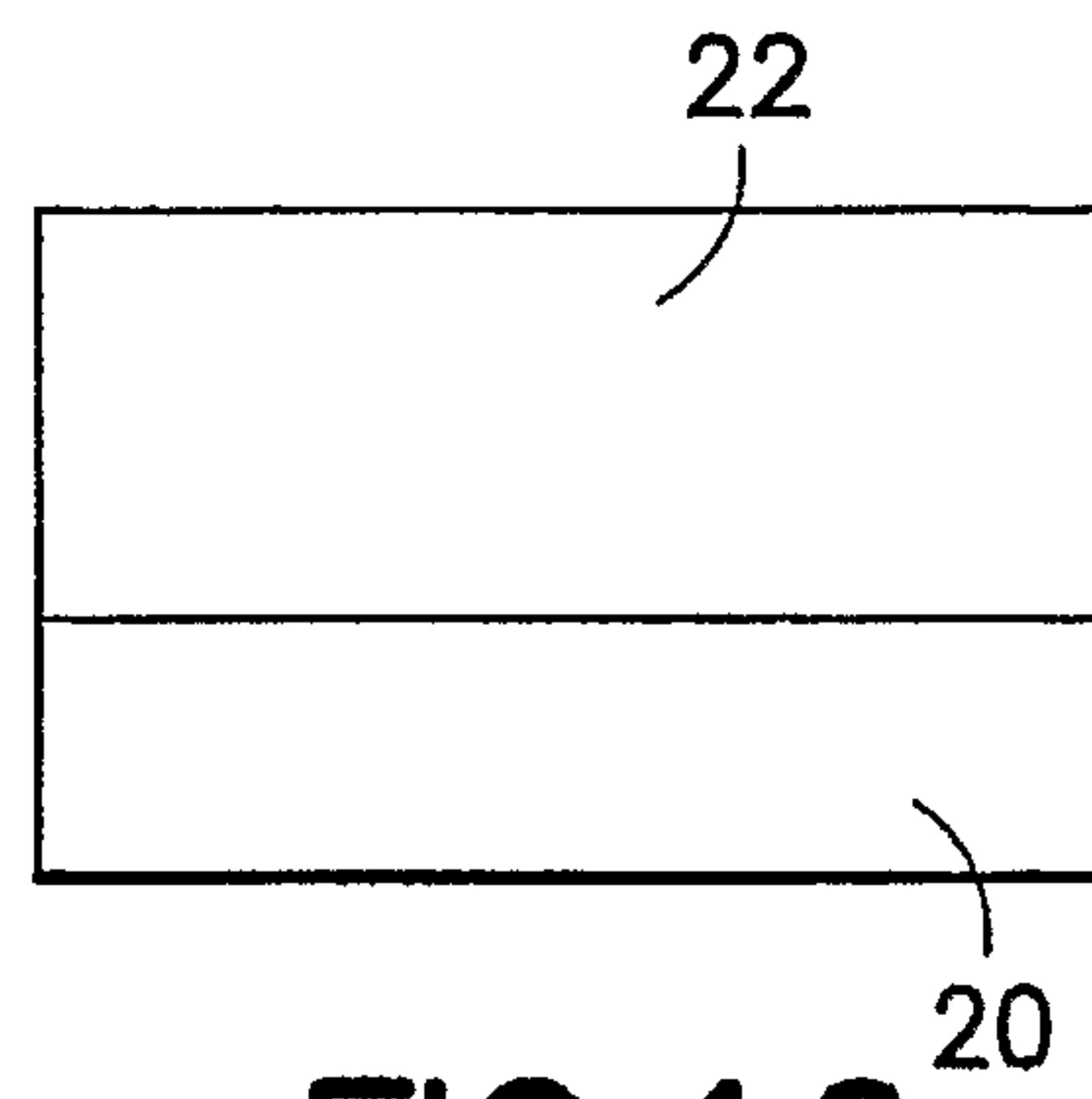

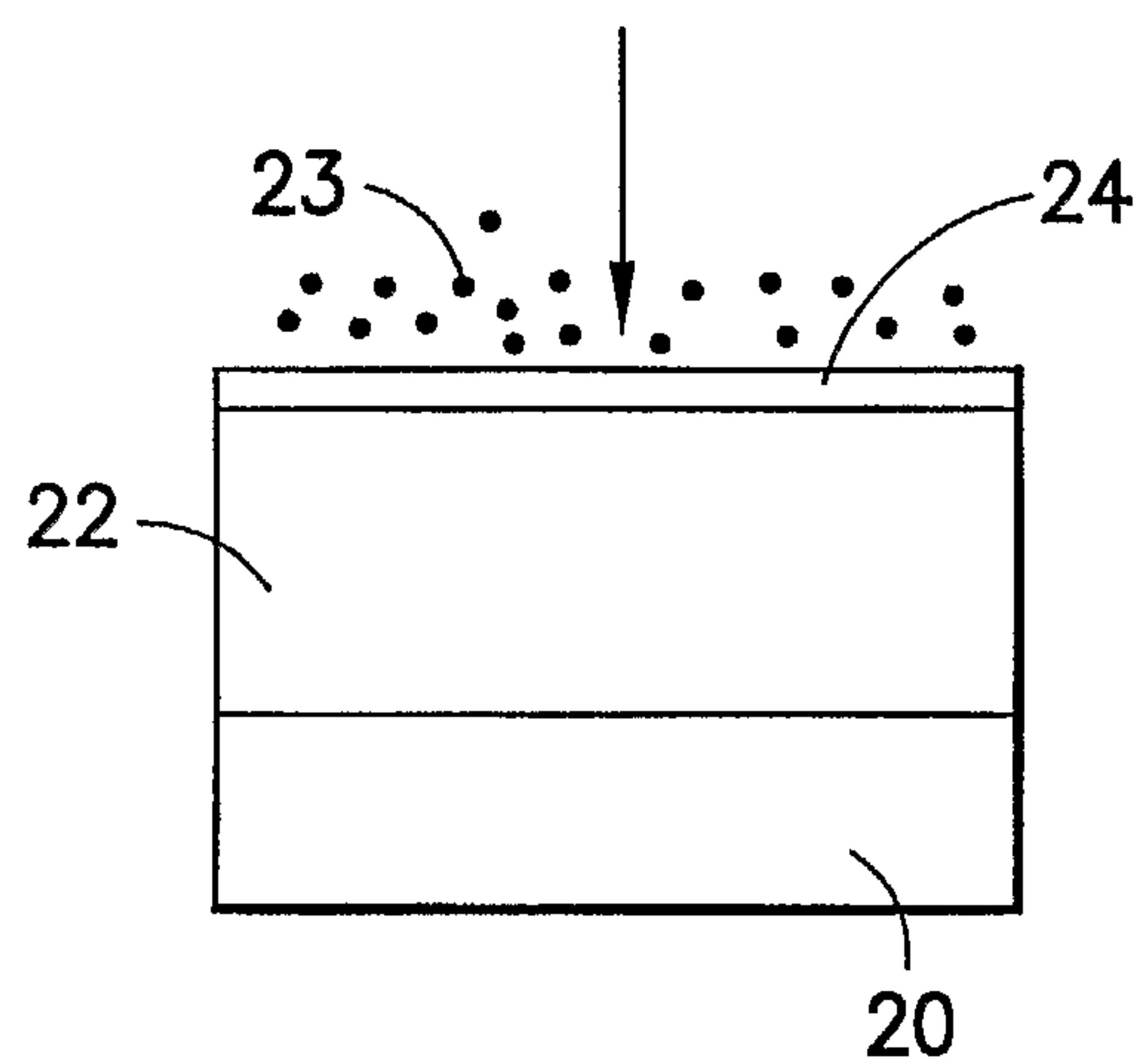

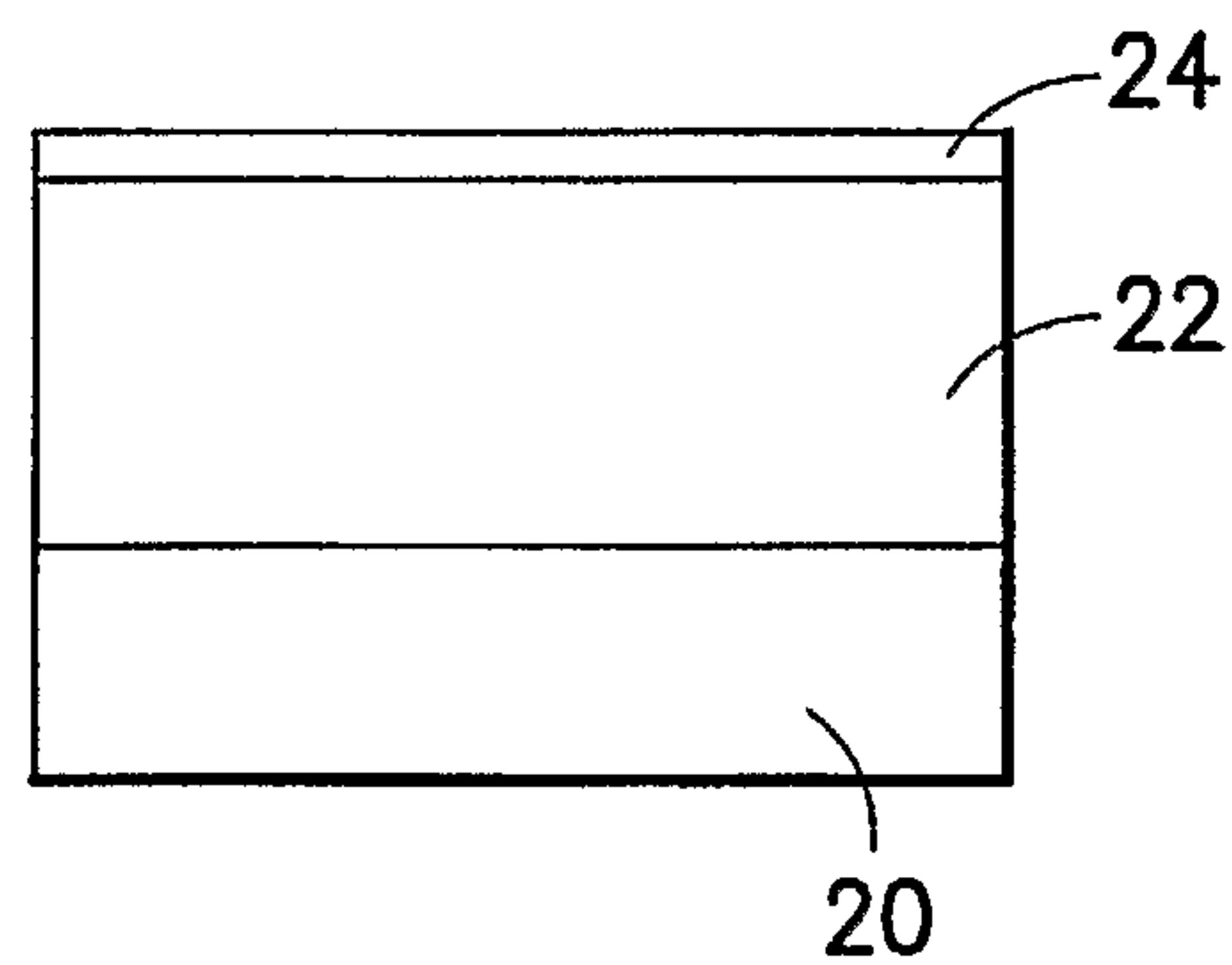

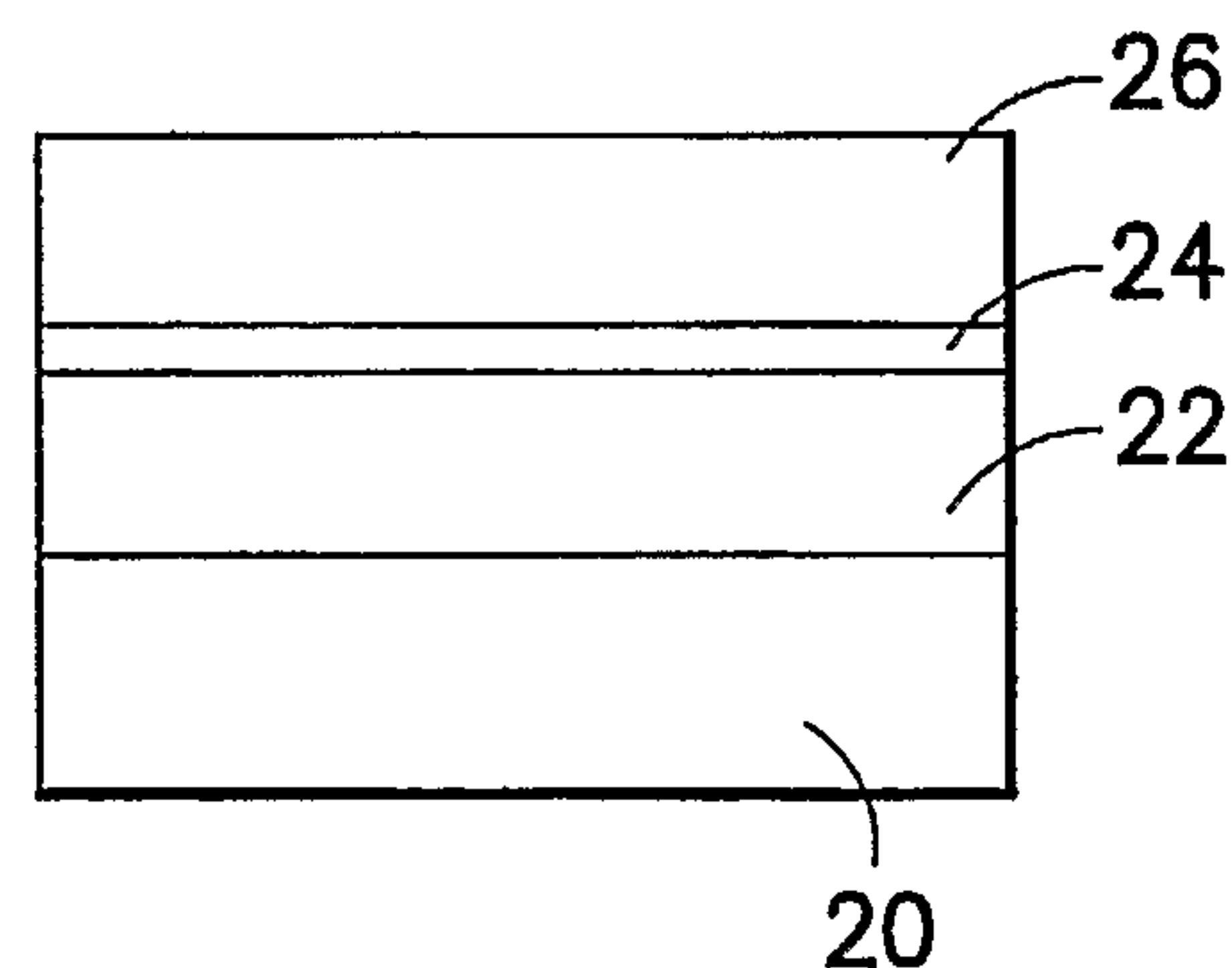

Figures 15-19 show a process flow for an epitaxial film deposition and delta doping process according to one embodiment of the invention.

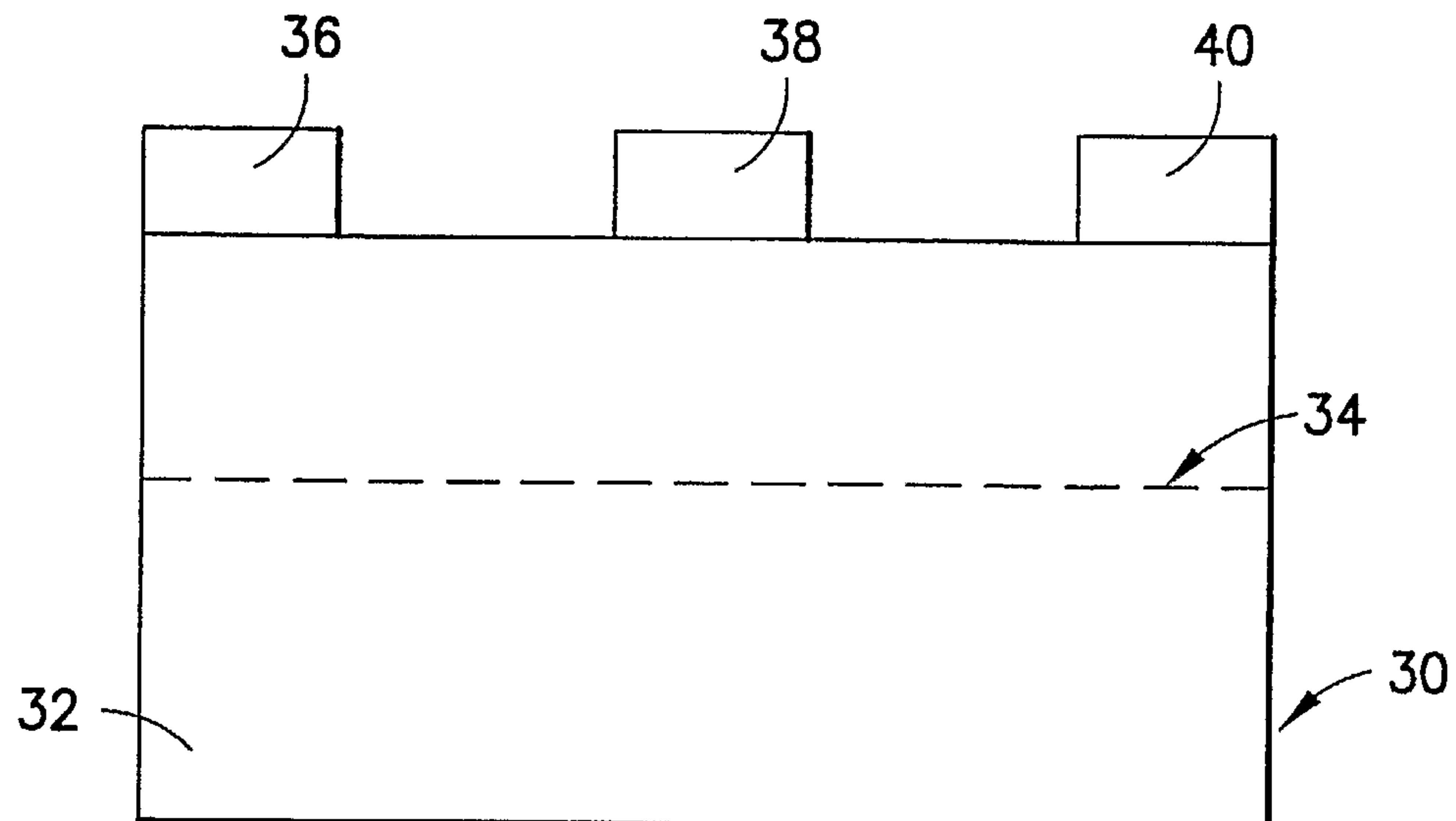

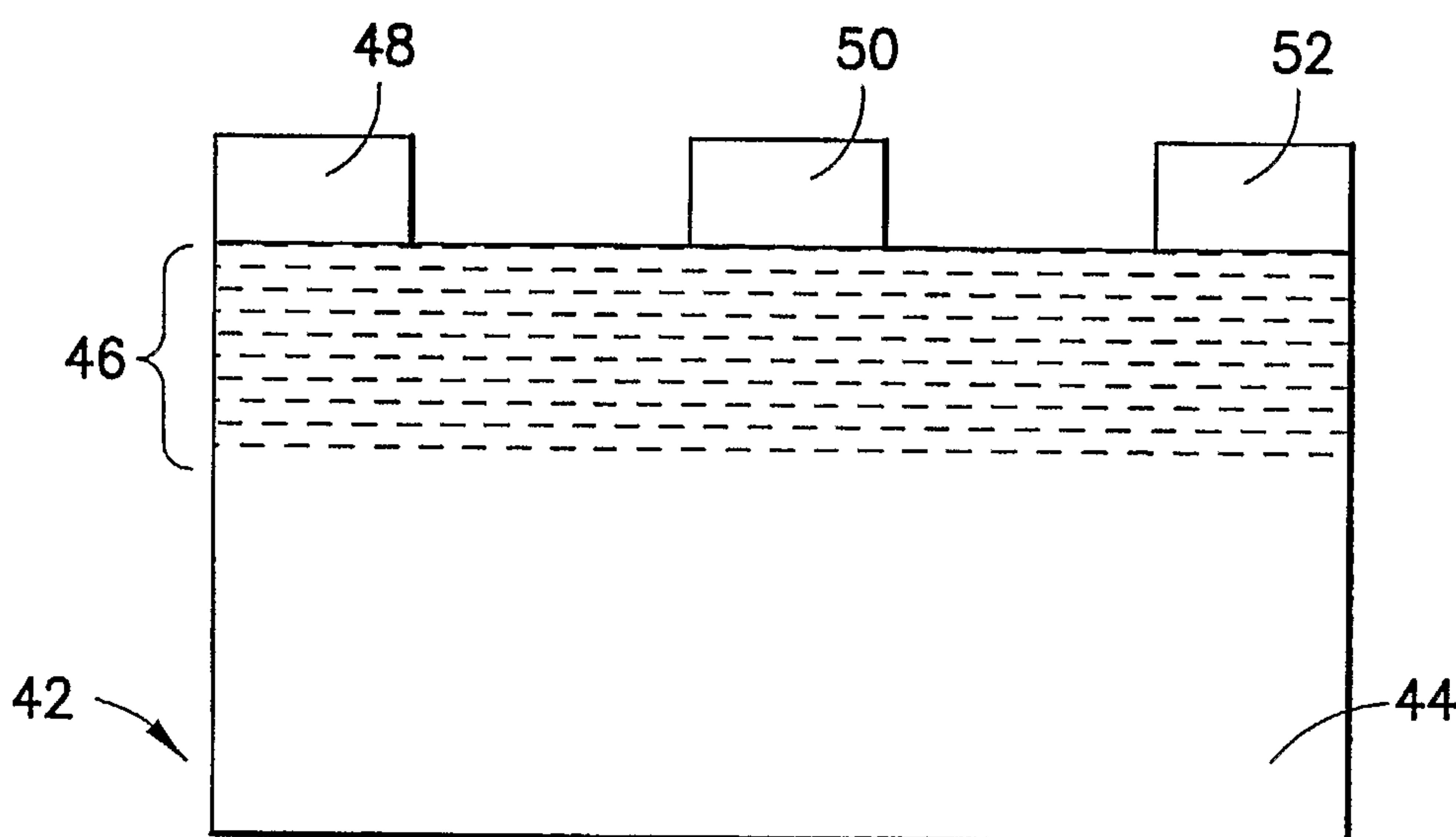

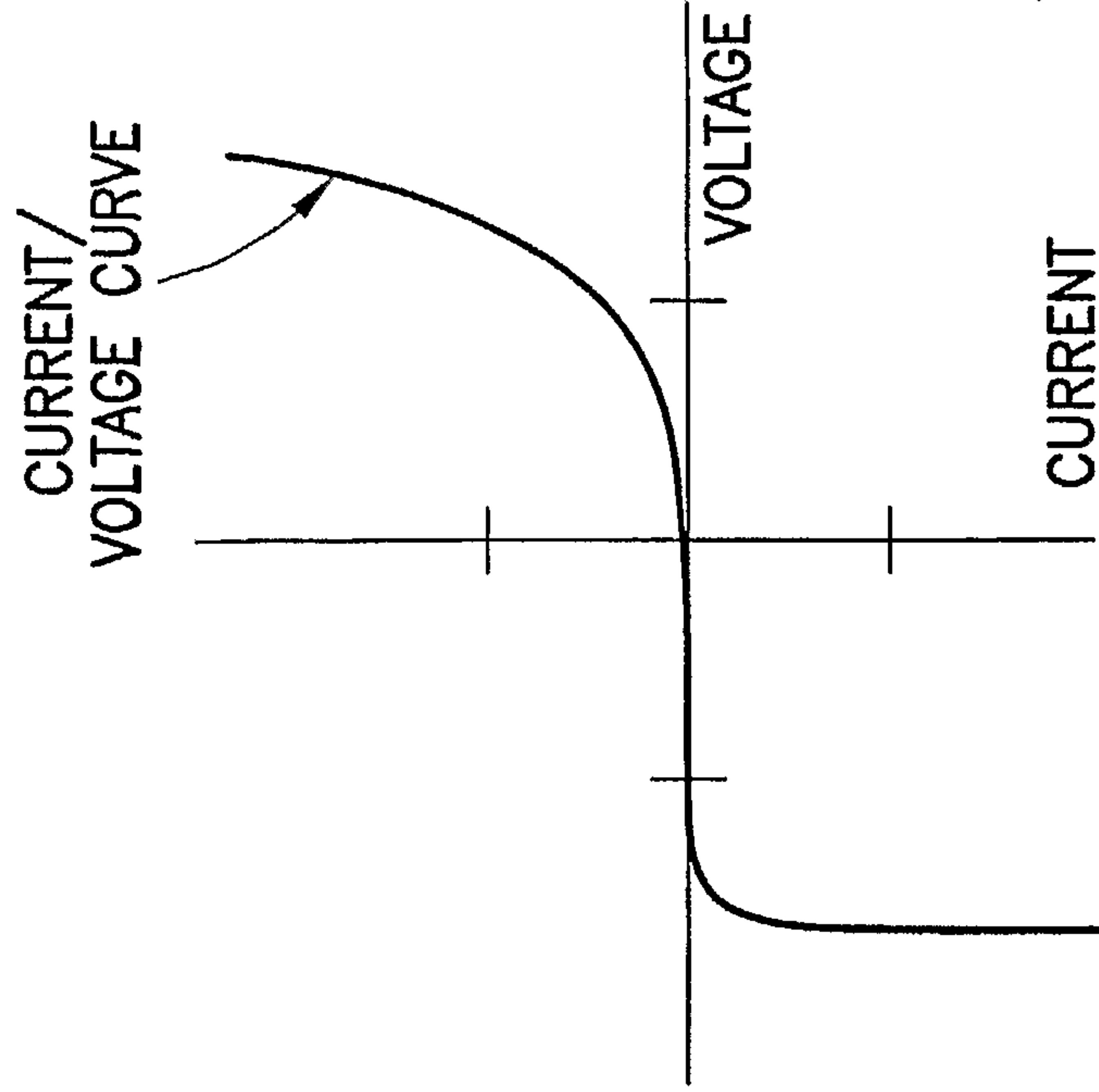

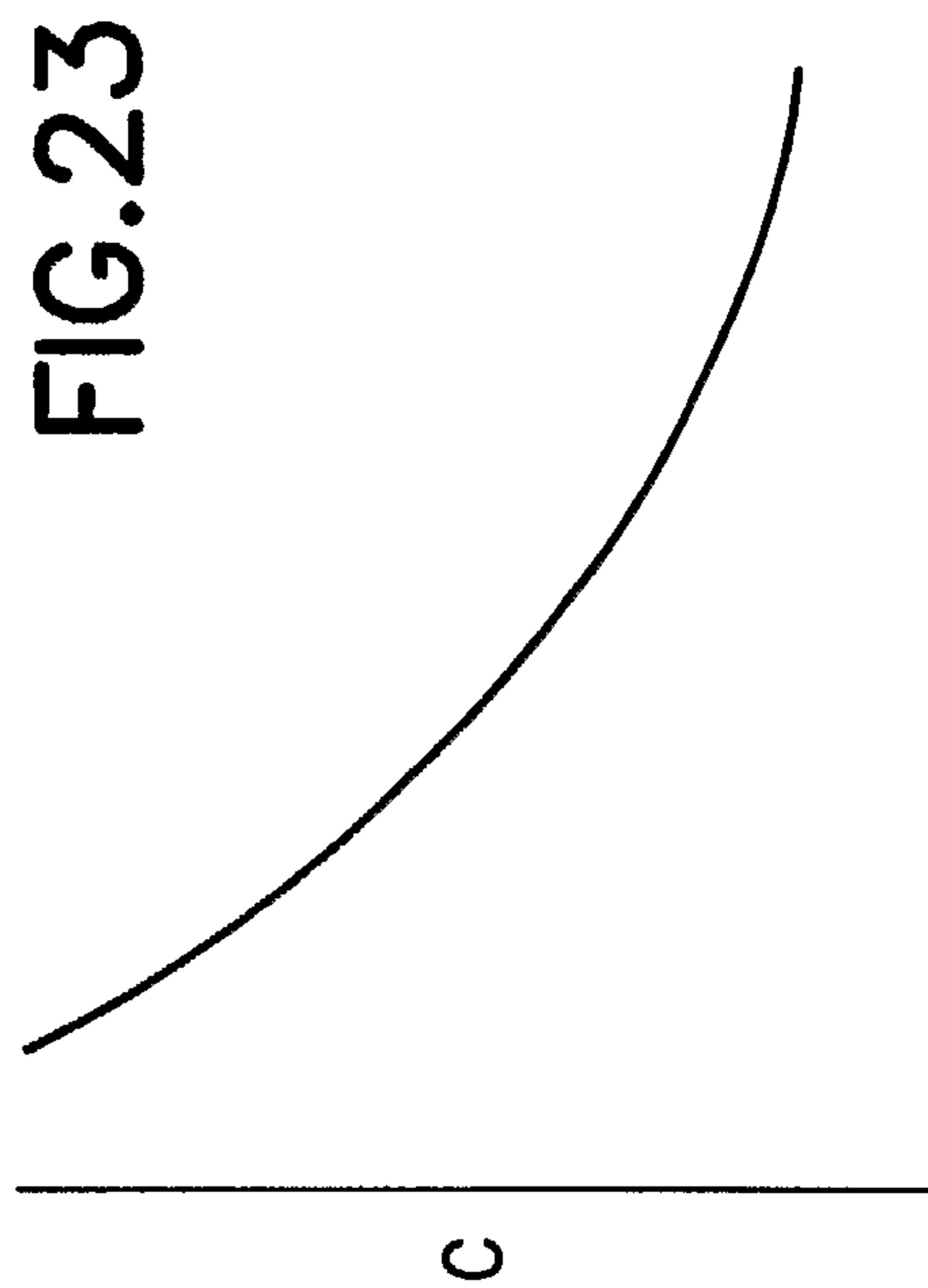

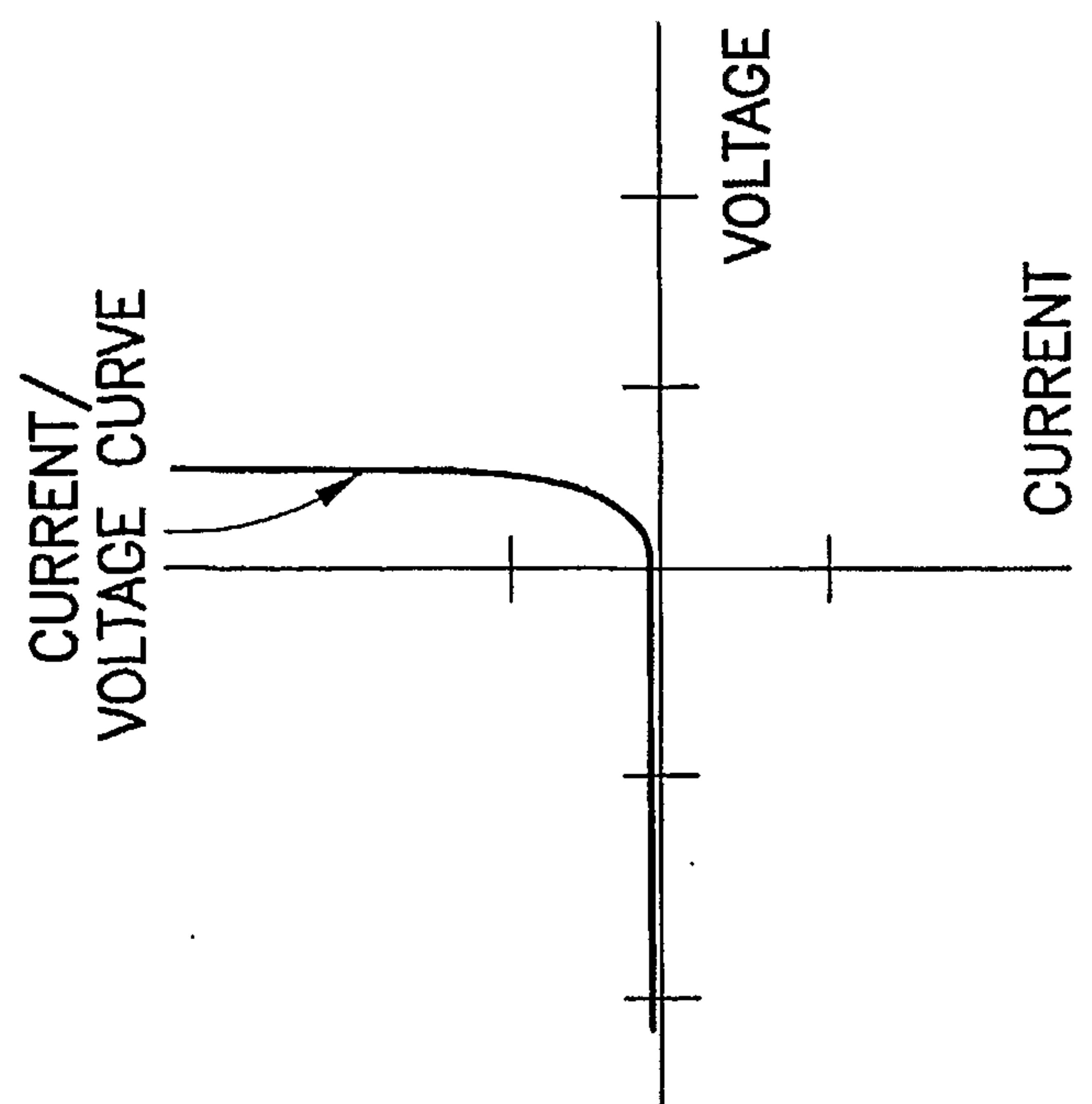

15 Figures 20, 22 and 24 show a delta doped high frequency field effect transistor (Figure 20), a corresponding current/voltage curve for the device (Figure 22) and a corresponding capacitance/voltage curve for the device (Figure 24), arranged for comparison with Figures 21, 23 and 25, respectively, showing a bulk doped high frequency field effect transistor (Figure 21), a corresponding current/voltage curve for the device (Figure 23) 20 and a corresponding capacitance/voltage curve for the device (Figure 25).

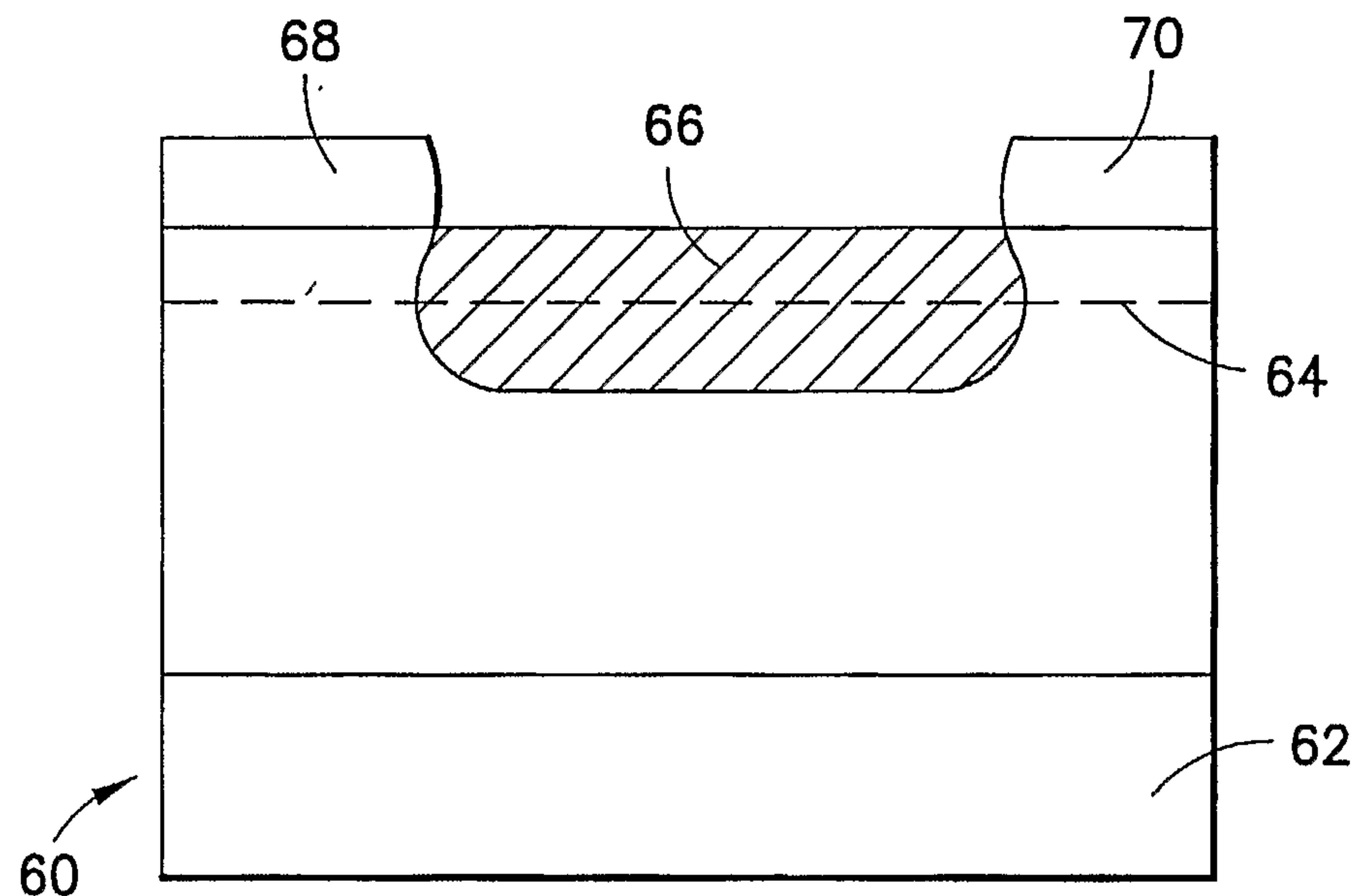

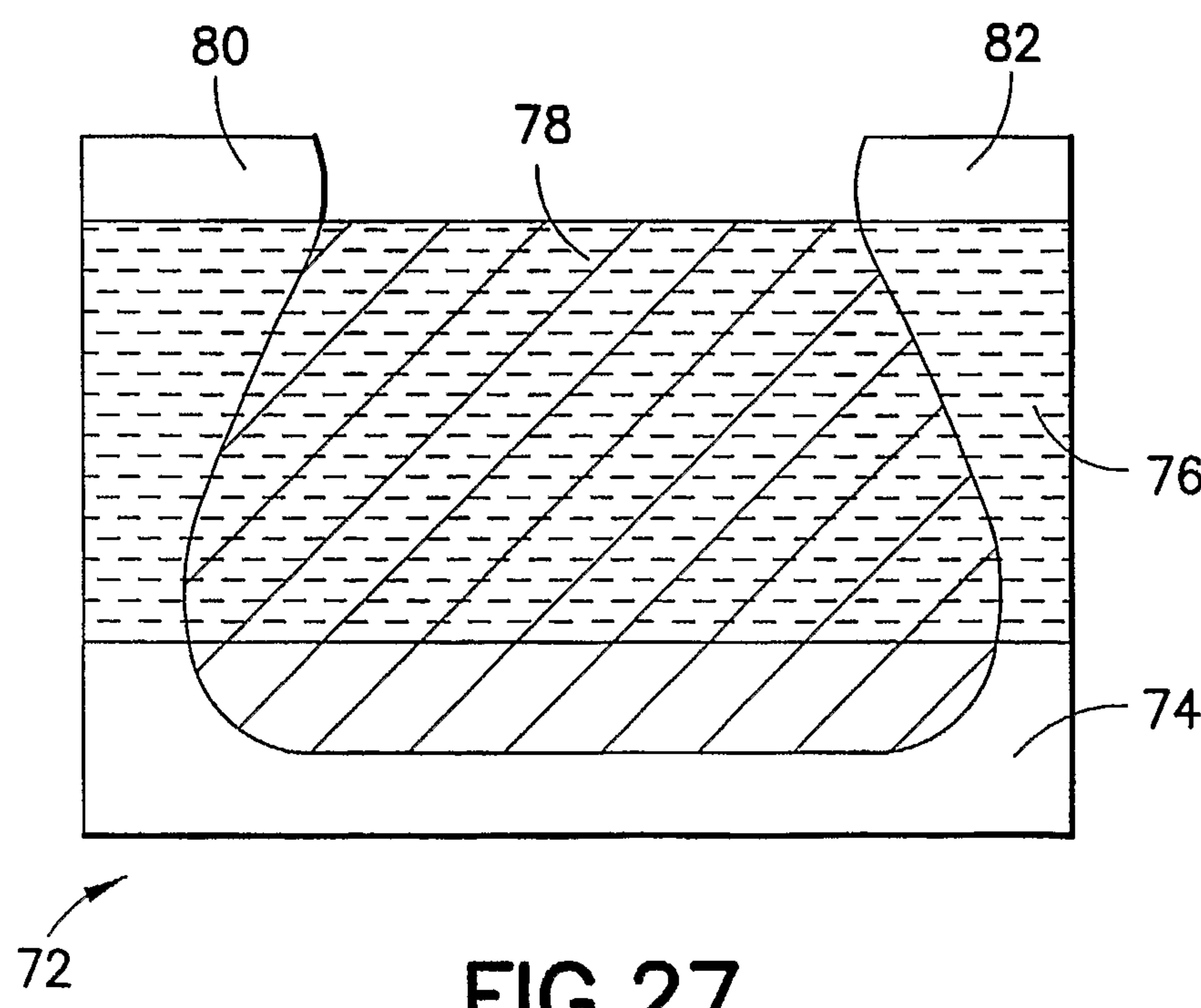

Figure 26 is a schematic view of a delta doped contact and isolation structure, arranged for comparison with Figure 27, a schematic view of a bulk doped contact and isolation structure, showing implant damage in the two device structures.

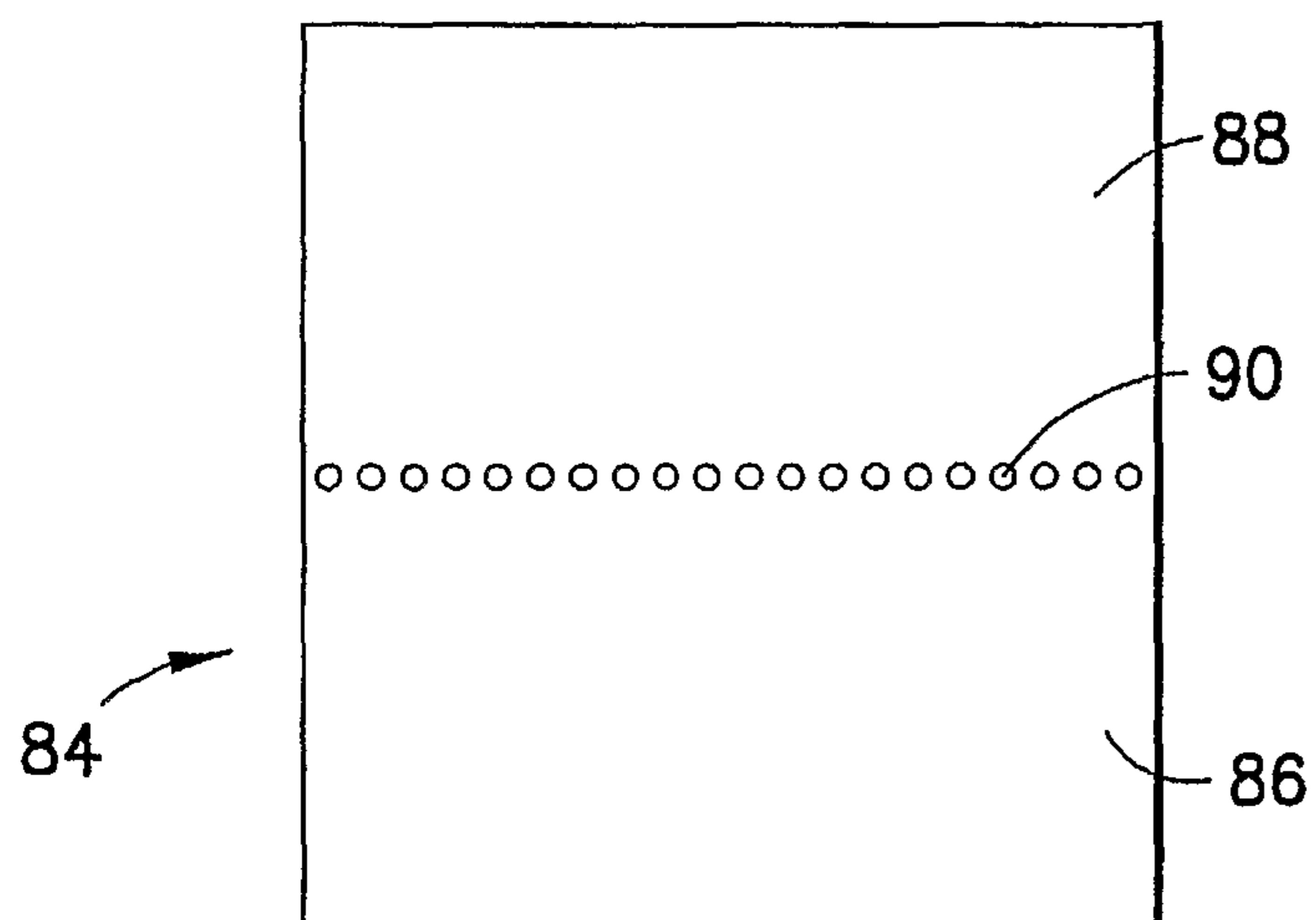

5 Figure 28 is a schematic view of a delta doped base NPN transistor according to one embodiment of the present invention.

Figure 29 is a schematic view of a delta doped base heterojunction bipolar transistor (HBT) according to another embodiment of the present invention.

10

Figure 30 is a schematic view of an emitter structure according to a further embodiment of the invention.

Figure 31 is a plot of doping versus depth, and a corresponding tunneling energy 15 diagram, for a tunnel doped HEMT device, delta doped in accordance with the invention, arranged for comparison with Figure 32, a plot of doping versus depth, and a corresponding tunneling energy diagram, for a doped HEMT device that is doped by bulk doping.

20

**DETAILED DESCRIPTION OF THE INVENTION, AND PREFERRED EMBODIMENTS THEREOF**

The disclosures of the following references are hereby incorporated herein by reference in their respective entireties: Zhao et al, Applied Physics Letters, Vol 77 (14), 2 Oct 2000, pp 2195-2197; Kim et al, MRS Internet Journal of Nitride Semiconductors, Res 4S1, G3.49 (1999); U.S. Patent Application No. 09/605,195 filed June 28, 2000 in the names of Jeffrey S. Flynn, et al. for "METHOD FOR ACHIEVING IMPROVED EPITAXY QUALITY (SURFACE TEXTURE AND DEFECT DENSITY) ON FREE-STANDING (ALUMINUM, INDIUM, GALLIUM) NITRIDE ((Al,In,Ga)N) SUBSTRATES FOR OPTO-ELECTRONIC AND ELECTRONIC DEVICES;" U.S. Patent Application No. 09/179,049 filed October 26, 1998 in the names of Robert P. Vaudo, et al. for "LOW DEFECT DENSITY (Al,In,Ga)N AND HVPE PROCESS FOR MAKING SAME;" and U.S. Patent 6,156,581 issued December 5, 2000 in the names of Robert P. Vaudo, et al. for "GaN-BASED DEVICES USING (Ga,Al,In)N BASED LAYERS."

15 Delta doping is a two-dimensional doping technique that enables a high concentration of dopant impurities to be placed in a very small volume in a semiconductor crystal. Ideally, a delta-doped layer is constituted by no more than one monolayer of a dopant impurity (n-type or p-type) placed into the host semiconductor crystal on the proper semiconductor site, III or V. Delta doping usually occurs when semiconductor crystal growth has been 20 paused with the pre-pause, pause and post-pause conditions integral in forming a high quality delta-doped layer. The delta doping contemplated by the invention involves a monolayer or near-monolayer of dopant atoms on or in a semiconductor material. In the preferred practice of "paused doping," as hereinafter more fully described, the delta doping layer is typically internalized in a semiconductor material as a layer therein, by 25 steps involving epitaxial growth of semiconductor material before and after the paused

doping, so that the dopant atoms are intercalated in the semiconductor material in a layer therein.

In the event that the delta doped layer is utilized for a contact layer, the delta doped layer

5 is exposed directly to the contact layer, and is not encapsulated or otherwise internalized

in the semiconductor material, but rather is interposed between the semiconductor

material and the metallization layer forming the contact element.

Delta doping therefore is a monolayer doping technique, in contrast to more conventional

10 bulk doping techniques, which are used to incorporate impurities in a volume of semi-

conductor crystal material that is much greater than a one monolayer thickness layer

equivalent. It will be recognized that in the general practice of the invention, during the

pause period, growth may still continue due to residual growth components in the reactor

(particularly if the pre-pause period does not allow sufficient time to completely remove

15 growth constituents) and in consequence the delta doping layer may be one or several

atomic layers in thickness, such variation being contemplated within the general purview

of delta doping in accordance with the invention, with respect to the preferred practice of

obtaining a monolayer of dopant atoms in the semiconductor material.

20 Delta doping in accordance with the present invention is carried out by in-situ doping,

utilizing a process such as metalorganic chemical vapor deposition (MOCVD), molecular

beam epitaxy (MBE), hydride vapor phase epitaxy (HVPE), plasma etch chemical vapor

deposition (PECVD), etc., wherein the dopant impurity is incorporated, implanted,

annealed and preferentially segregated. The in-situ doping technique can be carried out

in various embodiments to incorporate the dopant in Group III sites, or in Group V sites, or in interstitial sites of the Group III-V material, as may be desired in specific applications of the present invention.

5 Illustrative process conditions that are usefully employed for deposition of the Group III-V nitride semiconductor material, prior to and following delta doping in accordance with the invention, include temperature in a range of from about 400 to about 1200°C, pressure in a range of from about 1 to about 1000 torr, V/III ratio in a range of from about 1 to about 100,000, a pause period that is sufficient to enable the delta doping to be

10 carried out to produce the desired delta doped layer in the semiconductor material, and an ambient environment for the doping operation that may alternatively comprise nitrogen, hydrogen, argon, helium, or other suitable single-component or multi-component gas species. Growth conditions are readily optimized within the skill of the art to maintain a predetermined low level of native defects and to minimize incorporation of extraneous, 15 detrimental impurity in the grown material.

The doping operation is advantageously carried out at process conditions consistent with the epitaxial growth process, so that gross temperature fluctuations and variations in other process parameters are avoided, i.e., so that the doping is able to be integrated with the epitaxial growth process, in a continuous processing sequence.

20

Although such continuous processing sequence, involving epitaxial growth, cessation of film growth, doping, cessation of doping and re-initiation of epitaxial growth, is preferred, the delta doping may be carried out in a non-continuous manner. Thus, the initial epitaxial growth of (Al,In,Ga)N material may be carried out, and the resulting

article may be stored or otherwise interrupted in relation to the subsequent performance of the delta doping operation.

Thereafter, when the doping has been completed, the doped semiconductor material

5 article may be stored or otherwise delayed in respect of final epitaxial growth process, to form the semiconductor material within which the delta doped layer is contained.

The pre-pause through the post-pause steps can be repeated multiple times to yield a desired effect, e.g., the formation of multiple delta doped layers, each in spaced

10 relationship to other delta doping layers.

Optimal interface conditions in the respective pre-pause, doping, and post-pause steps include a clean surface prepared for preferential incorporation of dopant (e.g., with surface preparation being carried out as a final pre-pause operation), controlled process

15 conditions to minimize generation of defects, continuation of layer growth and incorporation of extraneous impurities, while controlling the position of incorporation (doping step), and controlled process conditions for reconstruction, segregation and redistribution of dopant impurities on the interface surface.

20 Concerning reconstruction, segregation and redistribution of dopant impurity deposits on the interface surface to form a delta doping layer, the present invention contemplates

processing involving implantation, migration and localization steps as a delta doping technique.

By way of illustrative example, during the pre-pause step, the ion implantation 5 mechanism is positioned in the reactor and growth conditions are adjusted to enable implant into the semiconductor crystal in the proper region(s) of the material. During the subsequent pause step, the implantation mechanism is activated and Si ions are introduced into the material. This is followed by a post-pause step of annealing, migrating or localizing the Si carriers to a specific dimension in the semiconductor 10 crystal to form a preferred delta doped or modified delta doped structure (e.g., wherein the dopant impurity atoms are aggregated in a generally planar region, preferably having a thickness that does not exceed about 25 times the diameter (atomic diameter) of the dopant atom species, more preferably having a thickness that does not exceed about 15 times the diameter of the dopant atom species, and most preferably having a thickness 15 that does not exceed about 10 times the diameter of the dopant atom species).

Pre-pause, pause and post-pause doping process steps may include, without limitation, additional semiconductor material preparation, restoration or modification steps for enabling high quality delta doping including temperature changes, ambient conditions 20 changes, precursor changes, pressure changes, total flow changes, impurity addition changes, surfactant addition (to improve doped surface quality and homogeneity of dopant impurity incorporation), material etch or removal, select or localized area material removal and the like.

Delta doping in accordance with the invention achieves substantial mobility enhancement and sheet resistance reduction in the product III-V nitride material, relative to doped III-V nitride materials of the prior art. By way of specific example, delta doping of AlGaN in accordance with the invention has achieved mobility enhancements greater than a factor 5 of two, as compared with corresponding bulk doped AlGaN material.

This improvement is shown by the data in Figure 1, which is a plot of room temperature Hall mobility as a function of Hall carrier concentration for delta doped AlGaN layers. The delta doping data shown in Figure 1 were generated by converting the delta doping 10 sheet charge to a carrier concentration assuming different delta-doped layer thicknesses of 5, 10 and 25 Angstroms. The delta doped layer thickness was determined from the FWHM of C-V data (approximately 10 Angstroms). The delta doping data were compared to data from conventional 1-3 $\mu$ m bulk doped AlGaN layers of equivalent aluminum composition of 25%. The data plotted in the graph of Figure 1 show that delta 15 doped structures exhibit much higher mobility at equivalent carrier concentration compared with bulk-doped structures. All data were determined at room temperature conditions.

Although we have not yet elucidated the specific mechanism for such substantial 20 improvement in electron mobility, it is apparent that the magnitude of improvement affords a resolution of doping deficiencies heretofore associated with GaN and related materials systems. While not wishing to be bound by any theory as regards the nature or extent of the demonstrated improvement, it may be that the substantially increased 25 electron mobility is attributable to strong piezoelectric effects in these III-V nitride materials from lattice strain in the region of the doped layer as well as other effects

including modifications to the carrier - impurity interaction, reduced impurity scattering, reduced defects scattering and reduced phonon-phonon interactions.

The substantial improvement of electron mobility achieved by the present invention may

5 be applied to realize contact resistivity improvements, improved p-type resistivities (e.g., in delta doped base heterojunction bipolar transistor (HBT) and laser device structures), enhanced device reliability and enhanced device performance characteristics, as well as the realization of new microelectronic device structures.

10 We have demonstrated the advantages and potential of the invention for enhanced electron mobility devices by fabricating two high electron mobility transistor (HEMT) structures and comparing their characteristics. The first structure (Structure A), shown in Figure 2, is an undoped HEMT structure. The second structure (Structure B), shown in Figure 3, is a delta doped HEMT structure. It will be recognized that gate, source, drain, 15 passivation and other layers can be deposited in a conventional manner to complete the finished HEMT structure, within the skill of the art.

As shown in Figure 2, the HEMT structure (Structure A) comprised a sapphire substrate 10 and buffer layer 12, as a base structure. The substrate 10 could alternatively have 20 comprised GaN, SiC or any other suitable substrate material. The buffer layer was formed of AlN and was on the order of about 400 Angstroms in thickness. On this base structure was grown a GaN layer 14 that was 3 micrometers in thickness, and an Al<sub>0.25</sub>Ga<sub>0.75</sub>N layer 16 that was 200 Angstroms in thickness.

The comparison Structure B is shown in Figure 3 and comprised the same layers as in Structure A (all corresponding layers being correspondingly numbered with reference to the same numbers used in Figure 2), except that the  $\text{Al}_{0.25}\text{Ga}_{0.75}\text{N}$  layer 16 comprised a 30 Angstroms thick lower portion and a 170 Angstroms thick upper portion, with a 5 silicon delta doped layer 18 therebetween. The delta doped layer 18 yields a  $5 \times 10^{12} \text{ cm}^{-2}$  Hall sheet charge in a calibration structure consisting of thick  $\text{Al}_{0.25}\text{Ga}_{0.75}\text{N}$  with a delta doped layer.

In a prior art HEMT structure of the type shown in Figure 2, increasing the sheet charge in the HEMT structure, results in a corresponding decrease in the electron mobility characteristics of the structure, as shown in Figure 4. Figure 4 is a plot of Hall mobility ( $\text{cm}^2 \text{ V}^{-1} \text{ s}^{-1}$ ) as a function of Hall sheet charge ( $\text{cm}^{-2}$ ) for the 300 Angstrom thick  $\text{Al}_{0.30}\text{Ga}_{0.70}\text{N}$  layer of an HEMT on a sapphire substrate (Structure A).

As shown in Table 1 below, the delta-doped structure (Structure B) does not demonstrate this detrimental effect of decreased electron mobility at increased sheet charge, but in fact demonstrates an equivalent mobility to the undoped HEMT structure (Structure A), at a much higher sheet charge.

TABLE 1

Hall characteristics of delta-doped (Structure B) and undoped (Structure A) HEMT structures

| Structure | RT Hall sheet charge<br>( $\text{cm}^{-2}$ ) | RT Hall mobility<br>( $\text{cm}^2/\text{V}\cdot\text{s}$ ) |

|-----------|----------------------------------------------|-------------------------------------------------------------|

|           |                                              |                                                             |

|             |         |      |

|-------------|---------|------|

| Structure A | 7.97E12 | 1145 |

| Structure B | 1.17E13 | 1152 |

A further comparison Structure C was fabricated, having the same general structure and layers as schematically shown for Structure B in Figure 3 (all corresponding layers being correspondingly numbered with reference to the same numbers used in Figure 2),

5 including a 30 Angstroms thick lower portion of the  $\text{Al}_{0.25}\text{Ga}_{0.75}\text{N}$  layer 16, except that the upper portion of the  $\text{Al}_{0.25}\text{Ga}_{0.75}\text{N}$  layer 16 was only 70 Angstroms in thickness and the intermediate layer 18 was bulk doped rather than being delta doped. The bulk doped layer 18 was 100 Angstroms in thickness, and contained a carrier concentration of  $5 \times 10^{18} \text{ cm}^{-3}$  for an equivalent sheet charge of  $5 \times 10^{12} \text{ cm}^{-2}$ .

10 As shown by the results in Table 2 below, tabulating Lehighton Sheet Resistance (ohm/sq) for the various sample structures (Structures A, B and C), the delta-doped HEMT structure (Structure B) demonstrated improved sheet resistance as compared with a corresponding bulk doped HEMT structure (Structure C).

15

TABLE 2

Lehighton characteristics of undoped HEMT structure (Structure A), delta-doped HEMT (Structure B) and bulk doped HEMT (Structure C)

| Structure   | Lehighton Sheet Resistance (ohm/sq) |

|-------------|-------------------------------------|

| Structure A | 547.6                               |

| Structure B | 459.8                               |

| Structure C | 542.8                               |

20

*Higher uniformity doping*

Conventional bulk doping uniformity is a function of growth rate and precursor uniformity, gas phase flow uniformity and dopant precursor uniformity. In delta-doping, the growth rate uniformity variable is eliminated, thereby improving the ability to achieve 5 uniform and more reproducible doping characteristics. Further, remaining factors affecting doping uniformity, including dopant concentration, delta-doping process conditions and delta-doping time, are susceptible to ready optimization within the skill of the art based on the disclosure herein, to provide a doping saturation condition that will yield a desired incorporation rate in the lattice.

10

*Engineering strain with delta doping*

When strain is present between the delta doped layer and the host semiconductor matrix as a consequence of dopant atom size relative to the host lattice, delta doping level-15 dependent piezoelectric effects in III-V nitride materials systems such as GaN materials systems can play a large role in optimizing delta doped structures and device structures comprising same. For proper engineering of the piezoelectric properties deriving from the delta doped layer, a combination of multiple types of impurities (different lattice sizes, lattice location affinities and activation energies) can be employed for the delta-20 doped layer, including Si, Ge, Mg, C, O, Ca, Zn, Li, Mn, Na, K, Cd, Rb, Sr, Sc and Be.. Further optimization of the piezoelectric properties can be effected by engineering the AlInGaN quaternary alloy mix in conjunction with the delta doping layer.

25 *Improved device structure stability*

Sheet charge of an AlGaN HEMT is typically increased through increasing strain by correspondingly increasing AlGaN aluminum content and/or increasing thickness. To achieve reasonable sheet charges on the order of  $10^{13} \text{ cm}^{-3}$ , however, the critical thickness of the AlGaN barrier layer typically needs to be exceeded. This leads to an unstable 5 device structure with a high potential for relaxation. One approach to avoiding this deficiency is growing the structure using an AlGaN layer with high Al content in the channel region (region 16 closest to layer 14) and then gradually grading it to lower Al content AlGaN away from the channel (away from the layer 14/layer 16 interface). Another approach to increasing sheet charge involves use of conventional techniques 10 such as bulk doping of the barrier layer, but the thickness of the barrier layer still needs to be quite thick or the doping level needs to be extremely high, leading to material degradation.

We have found that incorporating a delta doping layer in the barrier layer yields a 15 significantly enhanced charge contribution to the channel. We have demonstrated this for an AlGaN HEMT with a  $5 \times 10^{12} \text{ cm}^{-2}$  sheet charge, as compared with bulk doping of the barrier layer with a  $5 \times 10^{12} \text{ cm}^{-2}$  sheet charge (100 Angstroms,  $5 \times 10^{18} \text{ cm}^{-3}$ ). The delta doped structure provided an improved charge contribution to the channel, as shown in Figures 5 and 6.

20 Figure 5 is a plot of C-V doping ( $\text{cm}^{-3}$ ) as a function of depth ( $\mu\text{m}$ ), for an I-HEMT device of Structure A, a delta doped HEMT device of Structure B, and an n-HEMT of Structure C.

Figure 6 is a plot of capacitance (pF) as a function of voltage (V), for an I-HEMT device of Structure A, a delta doped HEMT device of Structure B, and an n-HEMT of Structure C.

5 These results demonstrate that lower thicknesses and lower aluminum contents can be achieved for delta doped structures with comparable characteristics to less stable thick, high aluminum content structures and bulk doped structures, thereby enabling more stable device structures to be achieved, below the critical thickness of the AlGaN layer. The ability to incorporate a delta doping layer to enhance charge contribution to the 10 channel also gives the device structure designer another degree of freedom and enables the optimization of strain and resultant piezoelectric properties so that the highest reliability and highest performance device structure can be achieved.

An additional example of improved device structure stability relates to the position of the 15 delta doped layer within the device structure. An optimal location will be present in each device depending on the application of the device and device performance needs. For instance, in a delta doped HEMT, preferred practice may include locating the delta doped layer in the barrier of the HEMT, in proximity to the channel, such that the distance between the delta doped layer and the channel is less than the tunneling distance of the 20 charge carriers (Figure 31).

#### *Improved optical characteristics*

When bulk doping GaN and AlGaN layers with dopant species such as Si or Mg, additional deep levels are generated, as evidenced by photoluminescence characteristics of the device structure. These deep levels are typically much lower energy than desired

in the energy emission and transmission applications of interest in the Group III-V nitride materials, and as a consequence these deep levels can cause very poor light extraction efficiency for an emitter, very poor response for a detector, and very poor light transmission for a filter. Delta doping can be employed in accordance with the invention 5 to mitigate the impact of these optically active defects, since delta doping provides a select, substantially mono-layer equivalent volume of doped material. Delta doping also is useful to reduce the layer or device structure sensitivity to light at energies lower than the bandgap of the semiconductor, thereby yielding improved noise characteristics for the corresponding semiconductor device.

10

*Improved device characteristics*

As discussed in the preceding section, bulk doping of III-V nitride materials such as GaN and AlGaN creates deep levels in the material. Utilizing delta doping to reduce the 15 cross-section (volume) of the device layer that contains these deep levels will effect substantial improvements in device characteristics, including temperature stability, lifetime, leakage and breakdown characteristics.

In this respect, a delta doped barrier HEMT structure (Structure B) will exhibit improved 20 breakdown and leakage characteristics when the device is pinched off, in comparison to a bulk doped HEMT structure (Structure C), since the Structure B device has fewer deep levels in it, therefore improving resistivity and reducing breakdown pathways.

*Improved device fabrication*

The delta doped layer can be engineered with respect to its location within the device, to thereby enable improved device fabrication, including for example the provision in the 5 device structure of delta doped contact layers, isolation layers and interconnect layers.

For example, a delta doped contact layer may be placed near the top of a HEMT device structure (region 16) to improve the ohmic contact behavior of the source or drain contact. The resulting device will be more readily and more reproducibly isolated via implant isolation than a bulk doped layer of equivalent resistivity, since the implant 10 energy and time will be reduced. As a result, the implant volume and implant damage will be reduced substantially, thereby yielding improved device characteristics, including isolation, breakdown and leakage characteristics (Figures 26 and 27).

As another application of the delta doping contemplated by the present invention, a delta 15 doped layer can be utilized in a further aspect of the invention as an etch stop, or alternatively a dopant signal obtained from the delta doped layer may be employed to identify etch depth that is desired in the fabrication of a particular semiconductor device or device precursor structure.

20 Devices formed with delta doped layers in accordance with the present invention may usefully be of any suitable type, including for example:

- a) contact and isolation structures

- b) high frequency AlGaN FETs or HEMTs

- c) generic delta doped structures and optical provisions

- d) opto-electronic transistor detector structures

- e) tunnel doped structures

- 5 f) delta doped base HBTs (NPN)

- g) optical filters

- h) detectors

10

*Superlattice Structures*

Superlattice structures are structures in which the alloy composition changes in a regular or periodic manner across the material thickness, or a portion of the material thickness.

15 The alloy composition usually changes between two compositions, the change is usually abrupt and the change in alloy composition usually results in a change of bandgap as shown in Figure 7. The degree of abruptness is a consequence of the device fabrication technique employed. In principle, the superlattice could comprise three or more alloys as shown in Figure 8, but for ease of ensuing description, superlattice structures will 20 hereinafter be illustratively described as comprising two regions, hereafter denoted Region 1 and Region 2.

In semiconductors the period  $x$  (see Figure 7) of the superlattice structure typically ranges from a few nanometers to a few tens of nanometers, but the range may be as small as 1 25 nanometers and as large as 500nanometers in Group III-V nitride materials system. The number of periods in the superlattice and the width of the two alloy regions  $w_1$  and  $w_2$  can be varied as required by the device and its end use.

The superlattice may be doped in either alloy or in the individual alloy regions separately as shown in Figures, 9, 10 and 11, showing n-type dopant energy levels in alloy 1 and alloy 2 (Figure 9), p-type doping in Region 1 only (Figure 10), and n-type doping with different concentrations in Region 1 and Region 2 (Figure 11). In some cases, the 5 concentration within each of the regions may be varied as well. For example, Region 1 might be n-type at a concentration of  $1 \times 10^{17} \text{ cm}^{-3}$  and Region 2 n-type at a concentration of  $5 \times 10^{17} \text{ cm}^{-3}$ . The energy level of the dopant impurity will change with the bandgap in a manner consistent with the alloy composition, dopant concentration and the dimensions of the superlattice. As shown in Figure 11, different doping 10 concentrations in Region 1 and Region 2 may lead to a band offset.

In one aspect of the invention, dopants that have a high activation energy may not contribute carriers for a particular temperature and alloy composition. See for example Alloy 1, which is shown in the energy diagram of Figure 12 having no associated ionized 15 dopant impurities. When this dopant is used in a superlattice structure comprising Alloy 1 and Alloy 2, in which the bandgap of Alloy 2 is greater than the bandgap of Alloy 1, the conductivity of the material is higher. The dopant may be incorporated in both regions or incorporated only in Region 2. The higher conductivity arises from carriers in Region 1 that originate from dopants in Region 2 as shown in the energy diagram of 20 Figure 13. Any dopants in Region 1 generally do not contribute in a meaningful manner, due to the temperature and composition of Region 1.

Mg is the commonly used dopant for p-type conduction in GaN and small Al content AlGaN, but it is difficult to achieve carrier concentrations in excess of  $1 \times 10^{18} \text{ cm}^{-3}$  in

GaN with Mg. For the reasons described above, Mg is a dopant species of preferred effectiveness. Alternative dopants for GaN and AlGaN superlattice structures include Ca, Na, K, Zn, Li, Cd, Rb, Sr, Sc and Be.

5 The width of Regions 1 and 2, the alloy composition of Region 2 (the Region 1 composition being defined by the specific end use application of the associated device structure), and the doping concentration in Regions 1 and 2 may be adjusted to attain a predetermined or otherwise desired level of conductivity.

10 When magnesium is used as a dopant impurity for GaN or AlGaN, the Mg doped GaN and Mg doped AlGaN require a high anneal temperature to activate the material, since any hydrogen that is present in the material will bond to the Mg impurity, or Mg complex, rendering it electrically inactive. Anneals are typically conducted under ammonia or nitrogen ambient in order to prevent decomposition, to free the hydrogen

15 from its bound state and to enable it to diffuse out of the material. Piezoelectric GaN/AlGaN exhibits internal electric fields that serve to reduce the energy required for removing hydrogen. This feature of piezoelectric GaN/AlGaN allows anneals to be carried out with lower power/temperature requirements, with consequent cost savings.

20 The anneal temperature may be sufficiently low to enable anneals to be conducted under non-nitrogen containing atmospheres without risk of GaN or AlGaN decomposition.

In accordance with another aspect of the invention, quaternary alloys are grown to produce superlattice structures for Group III-V nitride systems. The addition of a third

impurity may be used to modify the strain and defect density inherent in the epitaxial layers.

While the preceding discussion has been directed to the changes attributable to 5 superlattice structures on dopant activation and activation energy/carrier concentration characteristics, it is to be appreciated that improvements to other crystalline properties may occur simultaneously as a result of superlattice doping. For example, if the dopant activation energy is effectively changed in an epilayer of the superlattice, fewer dopant impurities are required and improvements in defect density and/or thermal conductivity 10 may be achieved, relative to corresponding more highly doped layers. As a consequence, improvements in crystalline quality and thermal conductivity, as well as in optical, chemical and structural properties of the superlattice material, are achievable.

Superlattice structures in accordance with the present invention may be grown or 15 produced by any suitable semiconductor manufacturing techniques appropriate therefor, including, without limitation, MOVPE, MBE, HVPE, sputter deposition (and optionally annealing), implant (and optionally annealing), and implant during growth processing by MOVPE, MBE or HVPE. MOVPE and MBE techniques are most preferred. Process conditions for such growth and production processes are readily determinable within the 20 skill of the art for a given application of such aspect of the present invention.

The improved electrical conductivity of doped superlattice structures in accordance with the present invention enables the provision of improved ohmic electrical contacts (with

lower specific contact resistivity). The higher carrier concentration attendant the presence of the doped superlattice structure will decrease the width of the metal-semiconductor barrier. Typical metals used to form contacts to GaN and AlGaN include Pd, Ni, Au, Re, Pt/Au, Pd/Au, and Ti/Pt/Au.

5

Improved p-type material formed by superlattice doping in accordance with the invention is usefully employed in one embodiment of the present invention to facilitate production of nitride photocathodes for solar blind detectors, particularly in high rate applications where substantial charge replacement capability (and therefore high material 10 conductivity) is required or when only very short wavelength photons are to be detected.

The prior art has found it very difficult to make high Al content AlGaN p-type conductive. This deficiency is overcome by the p-type doped AlGaN materials of the present invention.

15

Figure 14 shows a schematic structure of a high Al content photocathode. The Al content in Region 3 is selected so that the bandgap  $E_3$  absorbs photons of the desired wavelength and allows longer wavelength photons to pass through. The width of Region 3 is chosen so that most photons of the desired wavelength are absorbed, but it is not so 20 large that the electrons produced are likely to be reabsorbed before encountering the surface and emission into the vacuum. Based on an electron diffusion length in lightly doped p-GaN of ~0.2 micron, and a similar diffusion length obtaining in AlGaN, Region

3 will be a few tenths of a micron in thickness, depending in part on material quality, with poorer quality material preferably being thinner.

The Al content and width of Regions 1 and 2 are desirably selected to enable photons to 5 pass through it without obstruction, and to provide suitable conductivity in and near Region 3.

The structure shown in Figure 14 has a further benefit. The transition from Region 3 to Region 1 is an area in which the bandgap increases. Consequently, there is a potential 10 barrier from which carriers will reflect. This reflective barrier increases the probability that a carrier created in Region 3 will be emitted (i.e., the photocathode will have a higher efficiency).

The doped superlattice material of the present invention is advantageously useful in a 15 wide variety of electronic and optoelectronic devices, including unipolar and bipolar devices and two terminal and three or more terminal devices.

Figures 15-19 show a process flow for an epitaxial film deposition and delta doping process according to one embodiment of the invention.

20 Figure 15 shows an epitaxial film 22 being deposited on substrate 20 from a precursor vapor 21, in an epitaxial film growth process. The same features of the article being formed are correspondingly numbered for ease of reference, in Figures 16-19.

Figure 16 shows the epitaxial growth as having been pre-paused, by termination of the flow of the precursor vapor 21 (see Figure 15). As a result, the epitaxial film 22 is interrupted in the deposition process.

5

Figure 17 shows the next step of contacting the epitaxial film with dopant from dopant source material 23 to form a delta dopant layer 24 of near monoatomic thickness on the epitaxial film 22. The dopant source material may comprise a dopant vapor that is highly dilute, e.g., in an inert carrier gas, for the formation of the near-monolayer deposit of 10 dopant atoms on the surface of the epitaxial film 22. This is the pause step of the process.

After the delta doping layer 24 has been formed on the epitaxial film 22 during the pause step of the process, dopant deposition is terminated. There follows another quiescent 15 step, of post-pause, during which no deposition or film formation is being conducted.

Next, the epitaxial film formation processing is resumed, with deposition of an additional epitaxial film 26 over the delta doping layer 24. In this manner, the dopant is internalized, or intercalated, in the epitaxial film made up of lower layer 22 and upper layer 26.

20

Figures 20, 22 and 24 show a delta doped high frequency field effect transistor (Figure 20), a corresponding current/voltage curve for the device (Figure 22) and a corresponding

capacitance/voltage curve for the device (Figure 24), arranged for comparison with Figures 21, 23 and 25, respectively, showing a bulk doped high frequency field effect transistor (Figure 21), a corresponding current/voltage curve for the device (Figure 23) and a corresponding capacitance/voltage curve for the device (Figure 25).

5

Figure 20 shows the delta doped high frequency field effect transistor 30 as comprising epitaxial semiconductor material 32 that has an intercalated delta doping layer 34. The device structure features source and drain ohmic contacts 36 and 40, and gate Schottky contact 38.

10

The current/voltage curve for the Figure 20 device structure is shown in Figure 22, and the capacitance/voltage curve for the Figure 20 device structure is shown in Figure 24.

Figure 21 shows a corresponding bulk doped high frequency field effect transistor 42

15 comprising epitaxial semiconductor material 44 that is bulk doped in region 46 of the material with a same dopant species as the FET device structure of Figure 20. The FET device structure includes source and drain ohmic contacts 48 and 52 and gate Shottky contact 50.

20 The current/voltage curve for the Figure 21 device structure is shown in Figure 23, and the capacitance/voltage curve for the device structure of Figure 21 is shown in Figure 25.

Comparison of Figure 22 and Figure 23, and comparison of Figure 24 and Figure 25, show that the performance characteristics of the delta doped FET device structure of Figure 20 is markedly superior to the performance characteristics of the bulk doped FET device structure of Figure 21.

5

Figure 26 is a schematic view of a delta doped contact and isolation structure 60, arranged for comparison with Figure 27, a schematic view of a bulk doped contact and isolation structure 72, showing implant damage in the two device structures.

- 10 The delta doped contact and isolation structure 60 shown in Figure 26 features a device active layer 62 above which a delta doping layer 64 (of suitable n- or p-type dopant) is intercalated in the epitaxial semiconductor material. The structure features contacts 68 and 70. Implant damage is shown by cross-hatching.

- 15 The bulk doped contact and isolation structure 72 shown in Figure 27 includes a device active layer 74 above which is a bulk doped region 76 of the semiconductor material. The contact and isolation structure 72 features contacts 80 and 82. The cross-hatched portion 78 of the semiconductor material extending down into the active layer 74 of the device evidences a far greater extent of implant damage than the delta doped structure of

- 20 Figure 26. The dopant species in the Figure 27 device structure is the same as in the Figure 26 device structure, and both structures have comparable resistance characteristics. Again, the delta doped structure of the present invention evidences a substantially lesser extent of implant damage, consistent with the superior operational

characteristics of the contact and isolation structure shown in Figure 26 over the bulk doped structure of Figure 27.

Figure 28 is a schematic view of a delta doped NPN transistor 84 according to one 5 embodiment of the present invention. The transistor 84 includes an N collector portion 86 and an N emitter portion 88, between which is the delta doped P base layer 90 of the device.

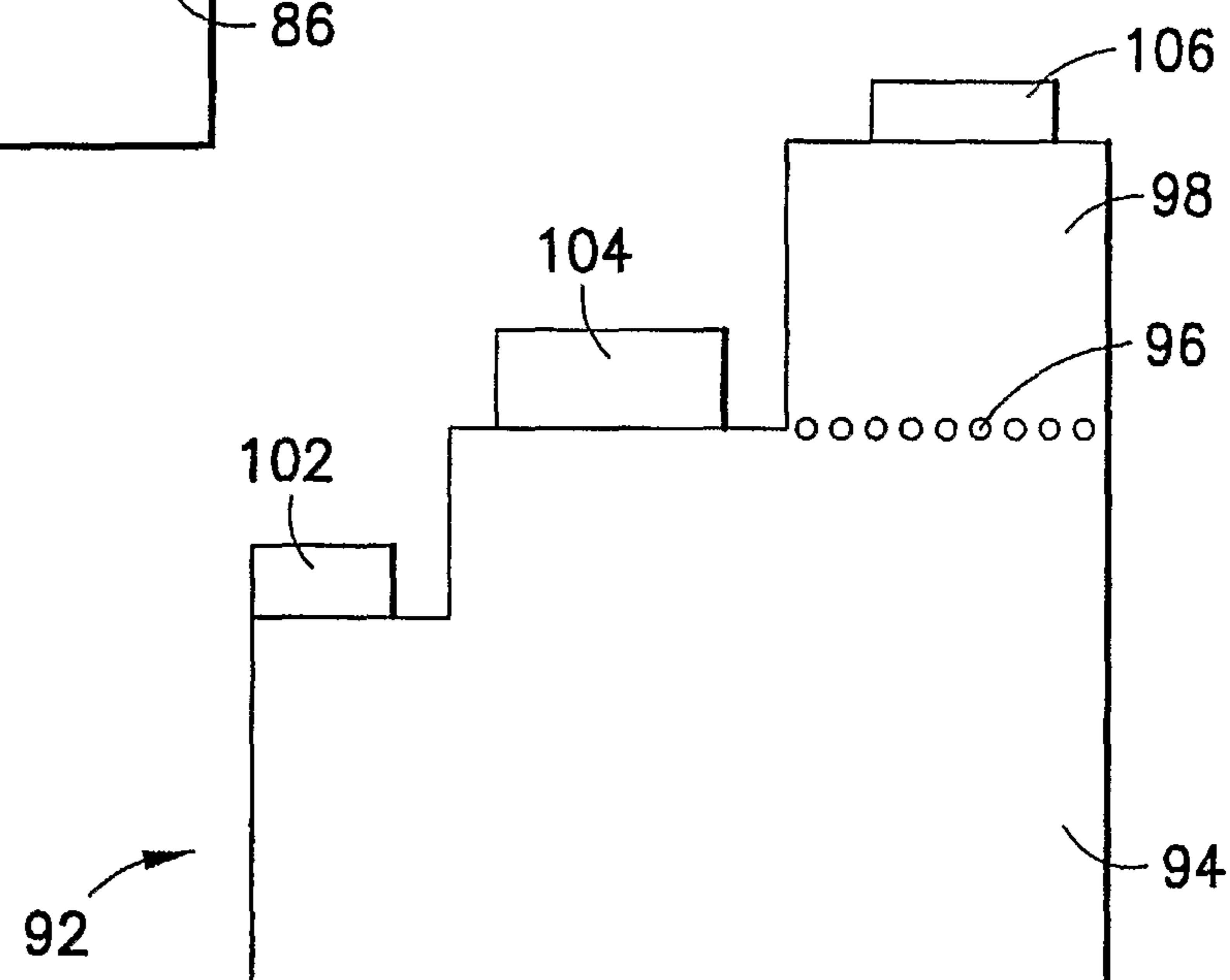

Figure 29 is a schematic view of a delta doped heterojunction bipolar transistor (HBT) 92 10 according to another embodiment of the present invention. The HBT device 92 includes an N collector portion 94, with associated contacts 102 and 104, with a delta doped P base layer 96, and with an upper N emitter (bandgap of emitter greater than bandgap of base) portion 98 having contact 106 formed thereon.

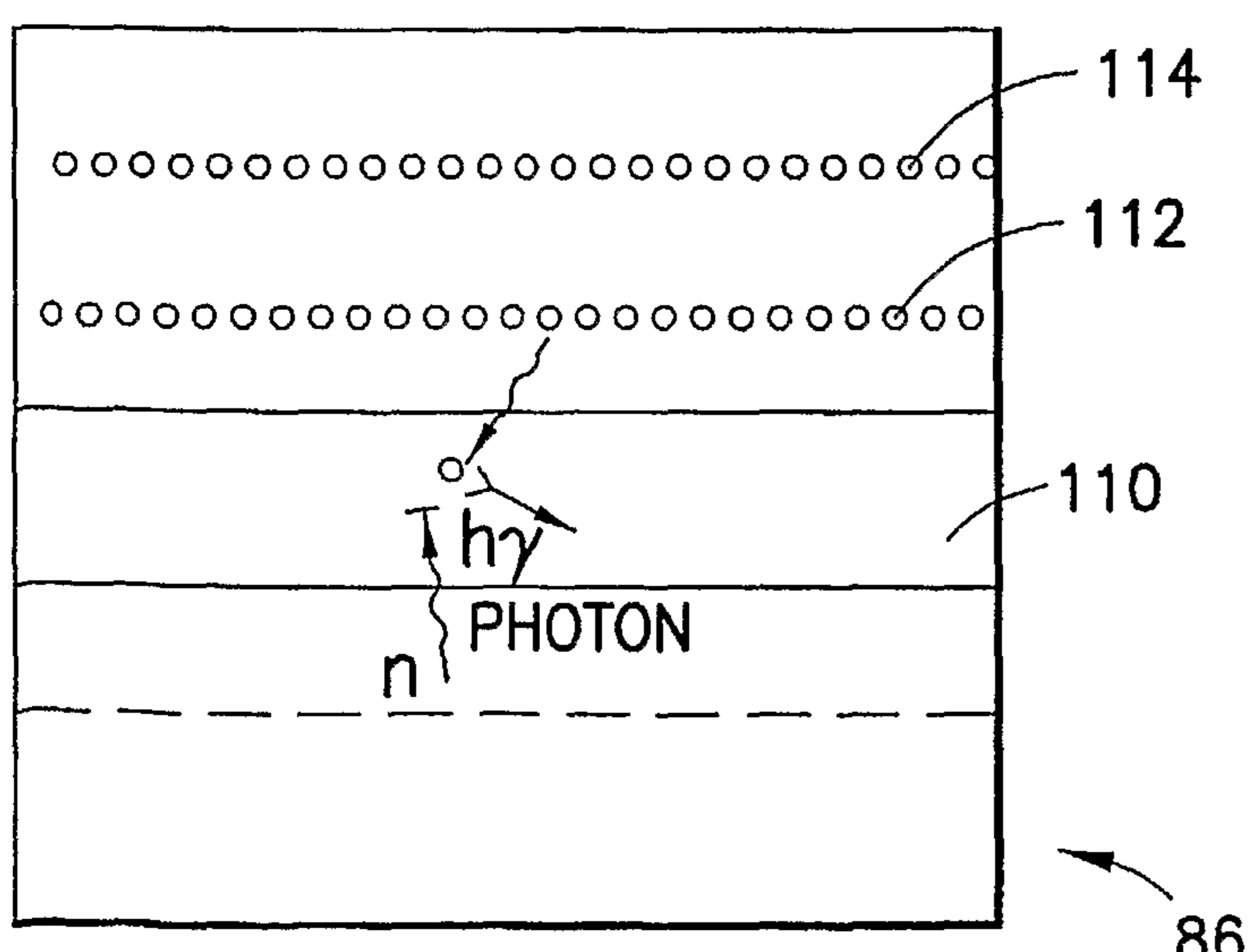

15 Figure 30 is a schematic view of an emitter structure 108 according to a further embodiment of the invention. The emitter structure 108 includes an active region 110, with a lower n region, and an upper region containing delta doped p-type dopant layers 112 and 114. Photons are generated in the active region of the device structure, as shown, in operation of the device.

20

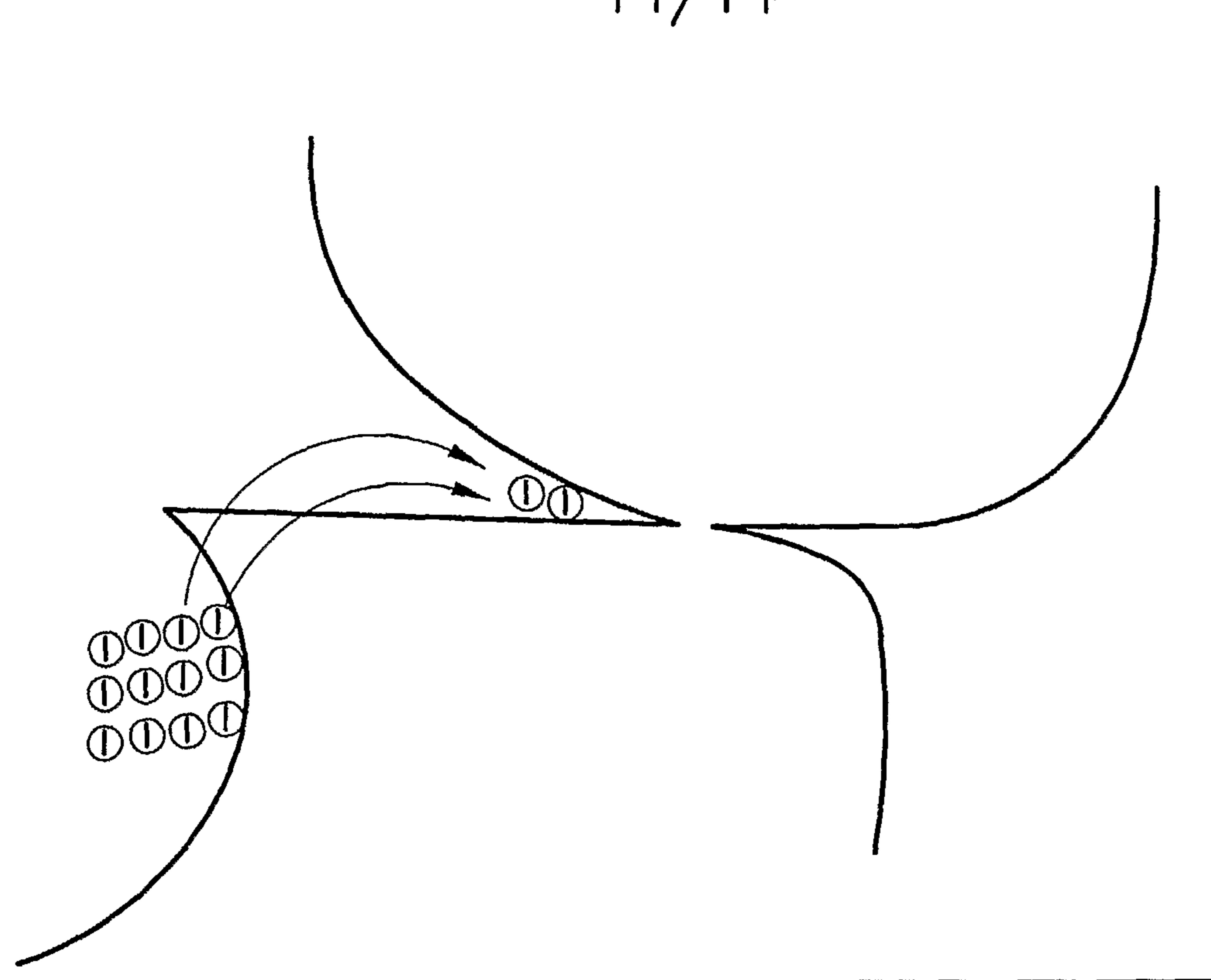

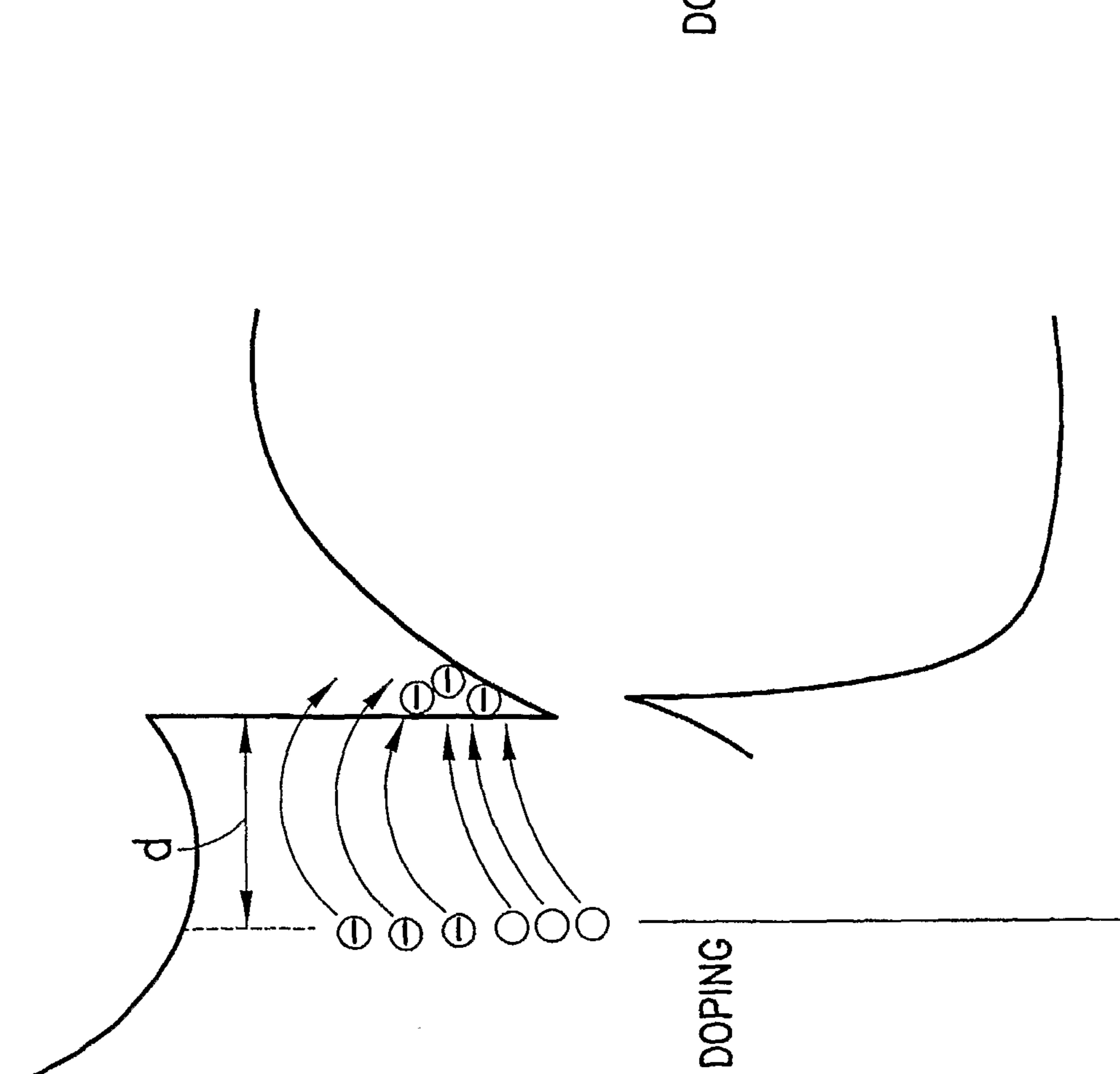

Figure 31 is a plot of doping versus depth, and a corresponding tunneling energy diagram, for a tunnel doped HEMT device, delta doped in accordance with the invention,

arranged for comparison with Figure 32, a plot of doping versus depth, and a corresponding tunneling energy diagram, for a tunnel doped HEMT device that is doped by bulk doping. The distance  $d$  shown in the tunneling energy diagram is less than the tunneling distance of carriers in the operation of the HEMT device that is delta doped.

5 By contrast, the energetics of charge carriers in the operation of the bulk doped HEMT are markedly less favorable, as is readily evident from a comparison of Figure 31 and Figure 32.

It will be apparent from the foregoing that the structural characteristics and operational function of delta doped microelectronic devices are substantially improved, and effect a major advance in the art of (Al,In,Ga)N materials and microelectronic/optoelectronic devices comprising same.

It will be appreciated, consistent with the introduction hereto, that although the invention has been described with particular reference to GaN and AlGaN herein in various 10 embodiments, all Group III-V nitride materials (Al,In,Ga)N are contemplated as being 15 within the broad scope of the invention herein described.

The features and advantages of the invention are more fully shown by the following illustrative and non-limiting examples of the invention.

### EXAMPLE 1

Delta Doped HEMT Device Structure

A sapphire substrate was heated to 1170°C in a H<sub>2</sub> environment at a pressure of 100mbar for 10 minutes. With the pressure constant for the remainder of the delta doping structure growth, the reactor was cooled to 500°C, and a low temperature AlN nucleation 5 buffer was deposited in a conventional manner. After the buffer layer was deposited on the sapphire, the reactor was heated to a susceptor temperature of 1220°C under 2.5 slm of NH<sub>3</sub> and 20 slm of H<sub>2</sub>, and the temperature was allowed to stabilize for 2 minutes.

Trimethylgallium (TMG) was introduced into the reactor at sufficient flux to provide a 10 growth rate of approximately 2.0  $\mu\text{m}/\text{hr}$  for 90minutes, to deposit a GaN layer with a thickness of 3 microns. Trimethylaluminum (TMA) was introduced for 5.5 seconds to grow a 30 Angstroms thick Al<sub>0.25</sub>Ga<sub>0.75</sub>N spacer layer.

Next, the pre-pause step was commenced by turning off the TMG and TMA to the 15 reactor and the interface was left under an NH<sub>3</sub> and H<sub>2</sub> environment at a susceptor temperature of 1220°C. The pre-pause lasted 10 seconds. After the pre-pause steps, the pause step was commenced by introducing 55 ppm disilane (Si<sub>2</sub>H<sub>6</sub> diluted in H<sub>2</sub>) into the reactor for 75 seconds at a flux effecting delta doping of silicon.

20 After the pause step, the post-pause step was commenced by simultaneously turning off the disilane to the reactor and turning on the TMA and TMG to the reactor at the previously described process conditions (for pre-pause AlGaN growth) for 31.2 seconds,

to grow an additional 170 Angstroms of  $\text{Al}_{0.25}\text{Ga}_{0.75}\text{N}$ . The V/III ratio was approximately 2500 for the GaN and AlGaN layers in this structure. Turning off the TMG and TMA to the reactor stopped the material growth. The grown material was cooled to less than 500°C under a  $\text{NH}_3$  and  $\text{H}_2$  overpressure and the reactor pressure was 5 ramped to 900 mbar, to produce a delta doped HEMT device structure.

## EXAMPLE 2

### Delta Doped Superlattice Structure

10 A sapphire substrate was heated to 1170°C in a  $\text{H}_2$  environment at 100 mbar for 10 minutes. With the pressure constant for the remainder of the delta doping structure growth, the reactor was cooled to 500°C and a low temperature AlN nucleation buffer was deposited in a conventional manner. After the AlN buffer layer was deposited on the sapphire, the substrate was heated to a susceptor temperature of 1220°C under a flow of 15 2.5 slm of  $\text{NH}_3$  and 20 slm of  $\text{H}_2$  and the temperature was allowed to stabilize for 2 minutes.

Trimethylgallium (TMG) was introduced into the reactor at an appropriate flux to provide a growth rate of approximately 2.0  $\mu\text{m}/\text{hr}$  for 90 minutes, to deposit a GaN layer 20 with a thickness of 3 microns. Trimethylaluminum (TMA) at an appropriate flux was introduced to grow an  $\text{Al}_{0.2}\text{Ga}_{0.8}\text{N}$  layer.

Next, the pre-pause step was commenced by turning off the TMG and TMA to the reactor. The interface was left under an NH<sub>3</sub> and H<sub>2</sub> environment at a susceptor temperature of 1220°C. The pre-pause lasted 10 seconds. After the pre-pause, the pause step was commenced by introducing bis-cyclopentadienyl magnesium (Cp<sub>2</sub>Mg) into the 5 reactor for 75 seconds at a flux appropriate for Mg delta doping of the previously deposited film material.

After the pause step, the post-pause step was commenced by simultaneously turning off the Cp<sub>2</sub>Mg to the reactor and turning on the TMA and TMG to the reactor, at the same 10 conditions employed in the pre-pause growth of AlGaN material. In this manner, an additional thickness of Al<sub>0.2</sub>Ga<sub>0.8</sub>N was deposited. TMA then was turned off and a GaN layer was grown again

Trimethylaluminum (TMA) was introduced to grow an Al<sub>0.2</sub>Ga<sub>0.8</sub>N layer of appropriate 15 thickness. The V/III ratio was approximately 2500 for the GaN and AlGaN layers in this structure. Turning off the TMG and TMA to the reactor stopped the material growth and the growth was cooled to less than 500°C under a NH<sub>3</sub> and H<sub>2</sub> overpressure and the reactor pressure was ramped to 900 mbar to complete the delta doped superlattice structure.

20

**EXAMPLE 3**

Photocathode Structure

A sapphire substrate was heated to 1170°C in a H<sub>2</sub> ambient environment at a pressure of 100 mbar for 10 minutes. With the pressure constant for the remainder of the delta doping structure growth, the reactor was cooled to 500°C and a low temperature AlN 5 nucleation buffer was deposited in a conventional manner. After the buffer layer of AlN was deposited on the sapphire substrate, the substrate was heated to a susceptor temperature of 1220°C under a flow rate of 2.5 slm of NH<sub>3</sub> and 20 slm of H<sub>2</sub> and the temperature was allowed to stabilize for 2 minutes. Trimethylgallium (TMG) and trimethylaluminum (TMA) were introduced into the reactor to grow an Al<sub>0.3</sub>Ga<sub>0.7</sub>N layer.

10 Then the pre-pause step was commenced by turning off the TMG and TMA to the reactor and the interface was left under an NH<sub>3</sub> and H<sub>2</sub> ambient environment at a susceptor temperature of 1220°C. The pre-pause lasted 10 seconds. After the pre-pause step, the pause step was commenced by introducing bis-cyclopentadienyl magnesium (Cp<sub>2</sub>Mg) into the reactor for 75 seconds to effect delta doping. After the pause step, the post-pause 15 step was commenced by simultaneously turning off the Cp<sub>2</sub>Mg to the reactor and turning on the TMA and TMG to the reactor as the same process conditions employed to deposit the AlGaN film prior to the delta doping step, to growth additional thickness of Al<sub>0.3</sub>Ga<sub>0.7</sub>N. TMA flux was then modified to vary the stoichiometry of the AlGaN film to produce an Al<sub>0.15</sub>Ga<sub>0.85</sub>N layer. Trimethylaluminum (TMA) flux then was increased to 20 grow an Al<sub>0.3</sub>Ga<sub>0.7</sub>N layer. Finally, the structure was capped with an Mg bulk doped GaN layer. The V/III ratio was approximately 2500 for the GaN and AlGaN layers in these structures. Turning off the TMG and TMA to the reactor stopped the material growth and the growth was cooled to less than 500°C under a NH<sub>3</sub> and H<sub>2</sub> overpressure and the reactor pressure was ramped to a pressure of 900 mbar to complete the 25 photocathode structure.

Although the invention has been variously disclosed herein with reference to illustrative embodiments and features, it will be appreciated that the embodiments and features described hereinabove are not intended to limit the invention, and that other variations, modifications and other embodiments will suggest themselves to those of ordinary skill in the art. The invention therefore is to be broadly construed, consistent with the claims hereafter set forth.

**THE CLAIMS****What is claimed is:**

1. A Group III-V nitride microelectronic device structure comprising a delta doped layer.

2. The microelectronic device structure of claim 1, wherein said delta doped layer is intermediate undoped III-V nitride layers in said device structure

- 10 3. The microelectronic device structure of claim 2, wherein said Group III-V nitride layers comprise AlGaN.

4. The microelectronic device structure of claim 2, wherein said Group III-V nitride layers comprise GaN.

- 15 5. The microelectronic device structure of claim 1, wherein said delta doped layer comprises at least one dopant species selected from the group consisting of Si, Ge, Mg, C, O, Ca, Zn, Li, Mn, Na, K, Cd, Rb, Sr, Sc and Be.

- 20 6. The microelectronic device structure of claim 1, comprising a device structure selected from the group consisting of UV LEDs, AlGaN/GaN high electron mobility transistors (HEMTs), contact structures, isolation structures, AlGaN FETs, optoelectronic transistor detectors, tunnel doped structures, doped base heterojunction bipolar transistors (HBTs), and optical filters.

7. The microelectronic device structure of claim 1, comprising an AlGaN/GaN high electron mobility transistors (HEMT).

8. The microelectronic device structure of claim 7, wherein the AlGaN/GaN high electron mobility transistors (HEMT) comprises a delta doping layer in a barrier layer of the device serving to increase sheet charge in the device structure, in comparison to a corresponding device structure lacking such delta doping layer.

9. The microelectronic device structure of claim 8, wherein the delta doped layer is located in the barrier layer at a position relative to a channel layer of the device structure such that the delta doped layer and the channel layer are spaced apart by a distance that is less than tunneling distance of charge carriers in operation of the device structure.

10. The microelectronic device structure of claim 9, wherein the dopant in the delta doping layer is silicon.

11. A Group III-V nitride microelectronic device structure including a doped III-V nitride superlattice.

12. The microelectronic device structure of claim 11, wherein said superlattice comprises a GaN or AlGaN superlattice.

13. The microelectronic device structure of claim 11, wherein said superlattice is doped with at least one dopant selected from the group consisting of Si, Ge, Mg, C, O, Ca, Zn, Li, Mn, Na, K, Cd, Rb, Sr, Sc and Be.

14. The microelectronic device structure of claim 11, wherein said superlattice comprises a first and second alloy wherein the bandgap of the second alloy is greater than the bandgap of the first alloy and conductivity is increased relative to a corresponding microelectronic device structure comprising an undoped superlattice.

5

15. A method of forming a doped Group III-V nitride semiconductor microelectronic device structure, comprising the steps of:

depositing semiconductor material on a substrate by a first epitaxial film growth process;

10 terminating the deposition of semiconductor material on the substrate to present an epitaxial film surface;

delta doping the semiconductor material at the epitaxial film surface, to form a delta doping layer thereon;

terminating the delta doping;

15 resuming deposition of semiconductor material to deposit semiconductor material on the delta doping layer, in a second epitaxial film growth process; and

20 continuing said semiconductor material second epitaxial film growth process to a predetermined extent, to form a doped microelectronic device structure, wherein the delta doping layer is internalized in semiconductor material deposited in said first and second epitaxial film growth processes.

16. The method of claim 15, wherein the delta doping comprises a process selected from the group consisting of MOCVD, MBE, HVPE, PECVD and ion implant.

25

17. The method of claim 15, wherein the semiconductor material comprises GaN or AlGaN.

18. The method of claim 15, wherein the semiconductor material comprises GaN.

19. The method of claim 15, wherein the semiconductor material comprises AlGaN.

5 20. The method of claim 15, wherein the delta doping incorporates dopant atoms in Group III sites.

21. The method of claim 15, wherein the delta doping incorporates dopant atoms in Group V sites.

10

22. The method of claim 15, wherein the delta doping incorporates dopant atoms in interstitial sites of the Group III-V nitride semiconductor.

15 23. The method of claim 15, wherein the delta doping is conducted under process conditions including the presence of a surfactant.

24. The method of claim 15, wherein the first and second epitaxial growth processes and delta doped layer formation include growth of GaN or AlGaN under process conditions including: temperature in a range of from about 400°C to about 1200°C, 20 pressure in a range of from about 1 to about 1000 torr, V/III ratio in a range of from about 1 to about 100,000.

25. The method of claim 24, wherein the first and second epitaxial growth processes and delta-doped layer formation are conducted in an ambient comprising nitrogen, 25 hydrogen or ammonia.

26. The microelectronic device structure of claim 1, further comprising a substrate formed of a material selected from the group consisting of sapphire, SiC, and GaN.

27. A HEMT device comprising a sapphire substrate, an AlN buffer layer on the 5 substrate, a GaN layer on the AlN buffer layer, and an AlGaN layer on the GaN layer, wherein the AlGaN layer has a delta doped layer therein.

28. The HEMT device of claim 27, wherein the delta doped layer comprises a dopant selected from the group consisting of Si, Ge, Mg, C, O, Ca, Zn, Li, Mn, Na, K, Cd, Rb, 10 Sr, Sc and Be..

29. The HEMT device of claim 27, wherein the delta doped layer comprises a silicon dopant.

15 30. A Group III-V nitride HEMT device including a delta doped layer in a barrier layer of the device.

20 31. The HEMT device according to claim 30, wherein the delta doped layer is in proximity to a channel layer of the device, at a position such that distance between the delta doped layer and the channel layer is less than tunneling distance of charge carriers in operation of the device.

25 32. A Group III-V nitride optoelectronic device selected from the group consisting of Group III-V nitride emitters, Group III-V nitride detectors and Group III-V nitride filters, and comprising a delta doped layer effective to improve optical characteristics of the device.

33. A Group III-V nitride optoelectronic device comprising a Group III-V nitride semiconductor, and a delta doped layer effective to reduce light sensitivity of the device at energies lower than the bandgap of the Group III-V nitride semiconductor, relative to a corresponding Group III-V nitride optoelectronic device lacking such delta doped layer.

5

34. A Group III-V nitride semiconductor device, comprising a device layer selected from the group consisting of contact layers, isolation layers and interconnect layers, wherein at least one of said layers is delta doped.

10 35. The Group III-V nitride semiconductor device of claim 34, wherein the device comprises a HEMT device, wherein the device includes a delta doped contact layer.

36. A Group III-V nitride microelectronic device structure including a doped III-V nitride superlattice, wherein the superlattice comprises three or more alloys.

15

37. A Group III-V nitride microelectronic device structure including a doped III-V nitride superlattice, wherein the superlattice comprises two alloys defining a first alloy region, and a second alloy region, and the superlattice is delta doped in at least one of said first and second regions.

20

38. The Group III-V nitride microelectronic device structure of claim 37, wherein one of the first and second regions is doped.

25 39. The Group III-V nitride microelectronic device structure of claim 37, wherein both of the first and second regions is doped.

40. A Group III-V nitride microelectronic device structure including a quaternary alloy superlattice.

41. A Group III-V nitride photocathode including a p-doped superlattice.

5

42. A doped Group III-V nitride semiconductor microelectronic device structure, formed by the method of claim 15.

43. A Group III-V nitride microelectronic device structure including a delta doped 10 layer and/or a doped superlattice.

44. The method of claim 15, wherein the delta doping comprises a process selected from the group consisting of MOCVD, MBE, HVPE, and PECVD or ion implant.45. A delta doped base for a HBT structure.

15

45. A delta doped structure with a substantially enhanced mobility compared with a bulk doped structure.

46. A Group III-V nitride microelectronic device structure comprising two or more delta 20 doped layers.

47. The Group III-V nitride microelectronic device structure of claim 46, comprising a multiplicity of delta doping layers, to control conductivity in the device structure in a predetermined manner.

25

1/14

FIG. 1

2/14

3/14

4/14

FIG.5

5/14

FIG.6

6/14

FIG.7

FIG.8

7/14

8/14

FIG.12

FIG.13

9/14

FIG. 15

FIG. 16

FIG. 17

FIG. 18

FIG. 19

10/14

FIG. 20

FIG. 21

11/14

FIG.23

FIG.25

FIG.22

FIG.24

12/14

FIG.26

FIG.27

13/14

FIG. 28

FIG. 29

FIG. 30

14/14

FIG.32

FIG.31