(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5406113号

(P5406113)

(45) 発行日 平成26年2月5日(2014.2.5)

(24) 登録日 平成25年11月8日(2013.11.8)

(51) Int.Cl.

HO3F 3/45 (2006.01)

F 1

HO3F 3/45

Z

請求項の数 3 (全 10 頁)

(21) 出願番号 特願2010-107656 (P2010-107656)

(22) 出願日 平成22年5月7日 (2010.5.7)

(65) 公開番号 特開2011-239103 (P2011-239103A)

(43) 公開日 平成23年11月24日 (2011.11.24)

審査請求日 平成25年3月12日 (2013.3.12)

(73) 特許権者 000002325

セイコーインスツル株式会社

千葉県千葉市美浜区中瀬1丁目8番地

(74) 代理人 100154863

弁理士 久原 健太郎

(74) 代理人 100142837

弁理士 内野 則彰

(74) 代理人 100123685

弁理士 木村 信行

(72) 発明者 五十嵐 敦史

千葉県千葉市美浜区中瀬1丁目8番地 セイコーインスツル株式会社内

(72) 発明者 三谷 正宏

千葉県千葉市美浜区中瀬1丁目8番地 セイコーインスツル株式会社内

最終頁に続く

(54) 【発明の名称】差動増幅回路

## (57) 【特許請求の範囲】

## 【請求項 1】

1対のPMOSトランジスタと、第一電流源を有し、2つの入力電圧に基づき出力電流を流す第一入力段と、

1対のNMOSトランジスタと、第二電流源を有し、前記2つの入力電圧に基づき出力電流を流す第二入力段と、

前記第一入力段の出力電流を流し込まれ、前記第二入力段の出力電流を引き抜かれることにより、電圧を出力する折り返しカスコード増幅段と、

前記折り返しカスコード増幅段の電圧に基づき、出力電圧を出力する出力段と、

前記第一電流源の出力電流に基づき、第一補正電流を前記出力段に流し込む第一補正電流発生回路と、

前記第二電流源の出力電流に基づき、第二補正電流を前記出力段から引き抜く第二補正電流発生回路と、

を備えることを特徴とする差動増幅回路。

## 【請求項 2】

前記第一補正電流発生回路は、

前記1対のPMOSトランジスタの1つと、同一のサイズで、且つ、ゲートを互いに接続した第三のPMOSトランジスタと、

前記第三のPMOSトランジスタのソースに設けられ、前記第一電流源の半分の電流を流す第三電流源と、を有し、

前記第二補正電流発生回路は、

前記1対のN MOSトランジスタの1つと、同一のサイズで、且つ、ゲートを互いに接続した第三のN MOSトランジスタと、

前記第三のN MOSトランジスタのソースに設けられ、前記第二電流源の半分の電流を流す第四電流源と、を有する、

ことを特徴とする請求項1記載の差動増幅回路。

### 【請求項3】

前記折り返しカスコード増幅段のカレントミラー回路の一端に設けられる第一クランプ回路と、

前記カレントミラー回路の他端に設けられる第二クランプ回路と、

前記出力段の出力端子に設けられる第三クランプ回路と、

をさらに備えることを特徴とする請求項1または2記載の差動増幅回路。

### 【発明の詳細な説明】

#### 【技術分野】

#### 【0001】

本発明は、差動増幅回路に関し、より詳しくはレール・トウ・レール型入出力の差動増幅回路に関する。

#### 【背景技術】

#### 【0002】

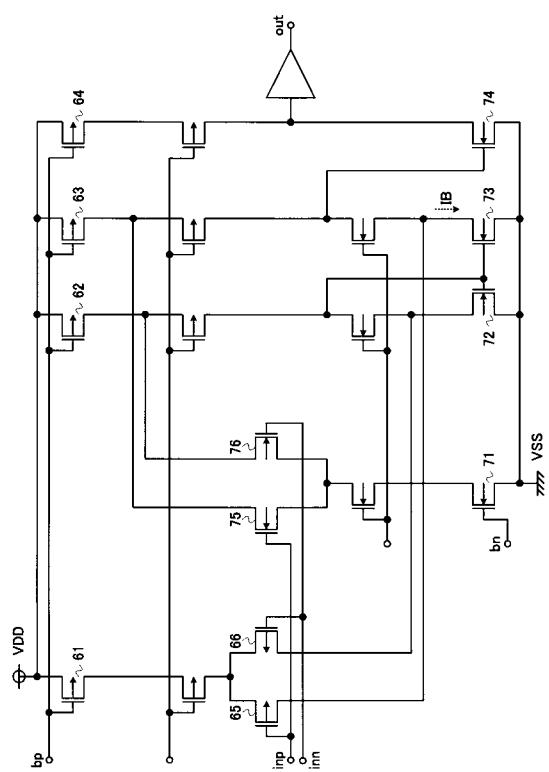

従来の差動増幅回路について説明する。図3は、従来の差動増幅回路を示す回路図である。

#### 【0003】

従来のレール・トウ・レール型入出力の差動増幅回路は、PMOSトランジスタ61とPMOSトランジスタ65及び66からなる第一入力段、NMOSトランジスタ71とNMOSトランジスタ75及び76からなる第二入力段、及び、PMOSトランジスタ62及び63とNMOSトランジスタ72及び73からなる折り返しカスコード増幅段を備える（例えば、特許文献1参照）。さらに、PMOSトランジスタ64及びNMOSトランジスタ74からなる出力段を備えることにより、出力電圧範囲を広くできる。

#### 【0004】

PMOSトランジスタ61～66のドレン電流はそれぞれドレン電流I61～I66であり、NMOSトランジスタ71～76のドレン電流はそれぞれドレン電流I71～I76である。入力端子inpの入力電圧はVinp、入力端子innの入力電圧はVinnである。ここで、ドレン電流I62及びI63は電流2Iとし、NMOSトランジスタ73のドレンに流れこむ電流は電流IBとする。

#### 【0005】

上述のような構成の差動増幅回路は、以下のように動作をする。

入力電圧Vinpが入力電圧Vinnよりも高くなると、ドレン電流I65はドレン電流I66よりも少なくなり、ドレン電流I75はドレン電流I76よりも多くなる。電流IB（IB=2I-I75+I65）は、ドレン電流I73（I73=I72=2I-I76+I66）よりも少なくなるので、NMOSトランジスタ74のゲート電圧は低くなる。従って、NMOSトランジスタ74のオン抵抗は高くなり、出力電圧outは高くなる。

#### 【0006】

ここで、入力電圧Vinp及び入力電圧VinnがVDDに近いときには、PMOSトランジスタ61が非飽和動作になり、NMOSトランジスタ75及び76を入力とする差動増幅回路として動作する。また、入力電圧Vinp及び入力電圧VinnがVSSに近いときには、NMOSトランジスタ71が非飽和動作になり、PMOSトランジスタ65及び66を入力とする差動増幅回路として動作する。また、入力電圧Vinp及び入力電圧Vinnが中間の電圧のときには、両方の差動増幅回路が動作する。

#### 【0007】

10

20

30

40

50

以上のような動作をすることによって、従来の差動増幅回路は、レール・トゥ・レール型入出力が可能となる。

**【先行技術文献】**

**【特許文献】**

**【0008】**

**【特許文献1】特開2005-223627号公報(図9)**

**【発明の概要】**

**【発明が解決しようとする課題】**

**【0009】**

しかし、上述したような従来の差動増幅回路では、入力電圧  $V_{in\ p}$  及び入力電圧  $V_{in\ n}$  が VDD や VSS に近いときには、NMOS ランジスタ 72 及び 73 のドレインに流れ込む電流は変動するが、NMOS ランジスタ 74 のドレインに流れ込む電流は一定である。従って、差動対の入力電圧レベルが異なると、NMOS ランジスタ 72 及び 73 と NMOS ランジスタ 74 ではバイアス条件が異なってしまう。すなわち、差動増幅回路は、差動対の入力電圧レベルが異なると、オフセット電圧が変化してしまう、という課題があった。10

**【0010】**

本発明は、上記課題に鑑みてなされ、オフセット電圧が差動対の入力電圧レベルに依存しない差動増幅回路を提供する。

**【課題を解決するための手段】**

**【0011】**

本発明は、上記課題を解決するため、1対のPMOS ランジスタ及び第一電流源を有し、2つの入力電圧に基づき出力電流を流す第一入力段と、1対のNMOS ランジスタ及び第二電流源を有し、2つの入力電圧に基づき出力電流を流す第二入力段と、第一入力段の出力電流を流し込まれ、第二入力段の出力電流を引き抜かれることにより、電圧を出力する折り返しカスコード増幅段と、折り返しカスコード増幅段の電圧に基づき出力電圧を出力する出力段と、第一電流源の供給電流に基づき第一補正電流を前記出力段に流し込む第一補正電流発生回路と、第二電流源の供給電流に基づき第二補正電流を前記出力段から引き抜く第二補正電流発生回路と、を備える差動増幅回路を提供する。20

**【発明の効果】**

**【0012】**

本発明では、第一補正電流発生回路及び第二補正電流発生回路が、折り返しカスコード増幅段と同じ電流を出力段に流す構成としたので、折り返しカスコード増幅段と出力段のトランジスタのバイアス条件は同じになる。従って、差動増幅回路のオフセット電圧は、入力電圧に依存しなくなる。30

**【図面の簡単な説明】**

**【0013】**

**【図1】差動増幅回路の実施形態を示す回路図である。**

**【図2】差動増幅回路の他の実施形態を示す回路図である。**

**【図3】従来の差動増幅回路を示す回路図である。**

**【発明を実施するための形態】**

**【0014】**

以下、本発明の実施形態を、図面を参照して説明する。

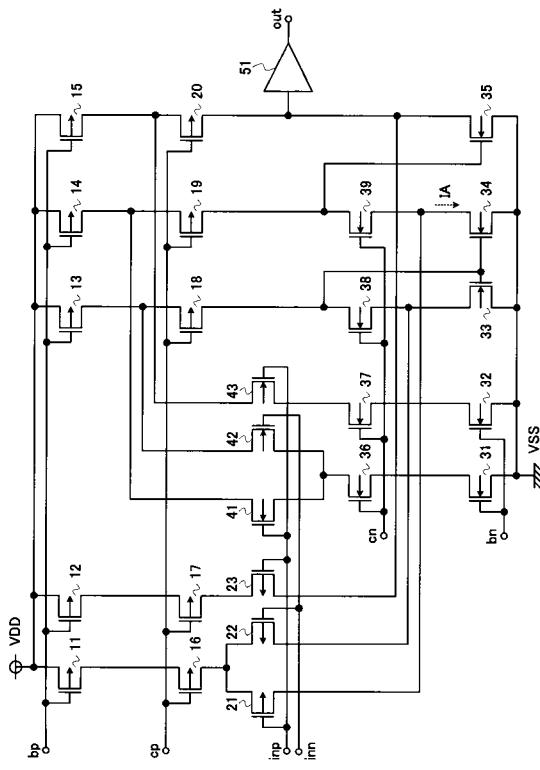

図1は、差動増幅回路の実施形態を示す回路図である。

差動増幅回路は、PMOS ランジスタ 11～23、NMOS ランジスタ 31～39、NMOS ランジスタ 41～43、及び、バッファ 51 を備える。また、差動増幅回路は、第一バイアス端子  $b\ p$  及び第二バイアス端子  $b\ n$ 、第一カスコード端子  $c\ p$  及び第二カスコード端子  $c\ n$ 、非反転入力端子  $i\ n\ p$ 、反転入力端子  $i\ n\ n$ 、及び、出力端子  $o\ u\ t$  を備える。40

**【0015】**

PMOSトランジスタ11とPMOSトランジスタ16とPMOSトランジスタ21～22とは、第一入力段を構成する。PMOSトランジスタ12とPMOSトランジスタ17とPMOSトランジスタ23とは、第一補正電流発生回路を構成する。NMOSトランジスタ31とNMOSトランジスタ36とNMOSトランジスタ41～42とは、第二入力段を構成する。NMOSトランジスタ32とNMOSトランジスタ37とNMOSトランジスタ43とは、第二補正電流発生回路を構成する。PMOSトランジスタ13～14とPMOSトランジスタ18～19とNMOSトランジスタ33～34とNMOSトランジスタ38～39とは、折り返しカスコード増幅段を構成する。PMOSトランジスタ15とPMOSトランジスタ20とNMOSトランジスタ35とは、出力段を構成する。また、PMOSトランジスタ16～20及びNMOSトランジスタ36～39はカスコード回路をそれぞれ構成する。PMOSトランジスタ11～15及びNMOSトランジスタ31～32は、電流源をそれぞれ構成する。

## 【0016】

PMOSトランジスタ11～15のゲートは、第一バイアス端子b<sub>p</sub>にそれぞれ接続され、ソースは、電源端子にそれぞれ接続され、ドレンは、PMOSトランジスタ16～20のソースにそれぞれ接続される。PMOSトランジスタ16～20のゲートは、第一カスコード端子c<sub>p</sub>にそれぞれ接続される。PMOSトランジスタ16のドレンは、PMOSトランジスタ21～22のソースに接続される。PMOSトランジスタ17～20のドレンは、PMOSトランジスタ23のソースとNMOSトランジスタ38～39のドレンとNMOSトランジスタ35のドレンとにそれぞれ接続される。

## 【0017】

NMOSトランジスタ31～32のゲートは、第二バイアス端子b<sub>n</sub>にそれぞれ接続され、ソースは、接地端子にそれぞれ接続され、ドレンは、NMOSトランジスタ36～37のソースにそれぞれ接続される。NMOSトランジスタ33～34のゲートは、PMOSトランジスタ18のドレンとNMOSトランジスタ38のドレンとの接続点にそれぞれ接続され、ソースは、接地端子にそれぞれ接続され、ドレンは、NMOSトランジスタ38～39のソースにそれぞれ接続される。NMOSトランジスタ35のゲートは、PMOSトランジスタ19のドレンとNMOSトランジスタ39のドレンとの接続点に接続され、ソースは、接地端子に接続される。NMOSトランジスタ36～39のゲートは、第二カスコード端子c<sub>n</sub>にそれぞれ接続される。NMOSトランジスタ36のドレンは、NMOSトランジスタ41～42のソースに接続される。NMOSトランジスタ37のドレンは、NMOSトランジスタ43のソースに接続される。

## 【0018】

PMOSトランジスタ21のゲートは、非反転入力端子i<sub>np</sub>に接続され、ドレンは、NMOSトランジスタ39のソースとNMOSトランジスタ34のドレンとの接続点に接続される。PMOSトランジスタ22のゲートは、反転入力端子i<sub>nn</sub>に接続され、ドレンは、NMOSトランジスタ38のソースとNMOSトランジスタ33のドレンとの接続点に接続される。PMOSトランジスタ23のゲートは、非反転入力端子i<sub>np</sub>に接続され、ドレンは、PMOSトランジスタ20のドレンとNMOSトランジスタ35のドレンとの接続点に接続される。

## 【0019】

NMOSトランジスタ41のゲートは、非反転入力端子i<sub>np</sub>に接続され、ドレンは、PMOSトランジスタ14のドレンとPMOSトランジスタ19のソースとの接続点に接続される。NMOSトランジスタ42のゲートは、反転入力端子i<sub>nn</sub>に接続され、ドレンは、PMOSトランジスタ13のドレンとPMOSトランジスタ18のソースとの接続点に接続される。NMOSトランジスタ43のゲートは、非反転入力端子i<sub>np</sub>に接続され、ドレンは、PMOSトランジスタ15のドレンとPMOSトランジスタ20のソースとの接続点に接続される。

## 【0020】

バッファ51の入力端子はPMOSトランジスタ20のドレンとNMOSトランジス

タ35のドレインとの接続点に接続され、バッファ51の出力端子は差動增幅回路の出力端子outに接続される。

#### 【0021】

ここで、電源端子の電圧は電源電圧VDDであり、接地端子の電圧は接地電圧VSSであり、第一バイアス端子bpの電圧はバイアス電圧Vbpであり、第二バイアス端子bnの電圧はバイアス電圧Vbnであり、第一カスコード端子cpの電圧はカスコード電圧Vcpであり、第二カスコード端子cnの電圧はカスコード電圧Vcnであり、非反転入力端子inpの電圧は入力電圧Vinpであり、反転入力端子innの電圧は入力電圧Vinnであり、出力端子outの電圧は出力電圧Voutである。

#### 【0022】

また、PMOSトランジスタ21～23のドレイン電流はそれぞれドレイン電流I21～I22及び第一補正電流I23であり、PMOSトランジスタ11～15のドレイン電流はそれぞれドレイン電流I11～I15であり、NMOSトランジスタ41～43のドレイン電流はそれぞれドレイン電流I41～I42及び第二補正電流I43であり、NMOSトランジスタ31～35のドレイン電流はそれぞれドレイン電流I31～I35であり、NMOSトランジスタ34のドレインに流れこむ電流は電流IAである。

#### 【0023】

第一入力段は、入力電圧Vinp及び入力電圧Vinnに基づき、ドレイン電流I21～I22を流す。第二入力段は、入力電圧Vinp及び入力電圧Vinnに基づき、ドレイン電流I41～I42を流す。折り返しカスコード増幅段は、ドレイン電流I21～I22を流し込まれ、ドレイン電流I41～I42を引き抜かれることにより、出力電圧を出力する。出力段は、折り返しカスコード増幅段の出力する電圧に基づき、出力電圧を出力する。バッファ51は、出力段の出力電圧をドライブし、出力電圧Voutを出力する。第一補正電流発生回路は、PMOSトランジスタ11からなる電流源の供給電流に基づき、PMOSトランジスタ12からなる電流源から出力段に第一補正電流I23を流し込む。第二補正電流発生回路は、NMOSトランジスタ31からなる電流源の供給電流に基づき、出力段からNMOSトランジスタ32からなる電流源に第二補正電流I43を引き抜く。

#### 【0024】

次に、差動增幅回路の動作について説明する。

ここで、入力電圧Vinp及び入力電圧VinnがVDDに近いときには、PMOSトランジスタ61が非飽和動作になり、NMOSトランジスタ75及び76を入力とする差動增幅回路として動作する。また、入力電圧Vinp及び入力電圧VinnがVSSに近いときには、NMOSトランジスタ71が非飽和動作になり、PMOSトランジスタ65及び66を入力とする差動增幅回路として動作する。また、入力電圧Vinp及び入力電圧Vinnが中間の電圧のときには、両方の差動增幅回路が動作する。

#### 【0025】

また、PMOSトランジスタ11及びPMOSトランジスタ13～15のサイズは等しく、PMOSトランジスタ16～20のサイズは等しく、PMOSトランジスタ21～23のサイズは等しく、NMOSトランジスタ31及びNMOSトランジスタ33～35のサイズは等しく、NMOSトランジスタ36～39のサイズは等しく、NMOSトランジスタ41～43のサイズは等しい。また、PMOSトランジスタ12のサイズはPMOSトランジスタ11の半分のサイズで、NMOSトランジスタ32のサイズはNMOSトランジスタ31の半分のサイズである。

#### 【0026】

まず、入力電圧Vinp及び入力電圧Vinnが中間の電圧のときの動作を説明する。この時、ドレイン電流I13～I15はそれぞれ電流2Iであるとする。また、PMOSトランジスタ11～12及びNMOSトランジスタ31～32がそれぞれ飽和動作するので、ドレイン電流I11及びドレイン電流I31はそれぞれ電流2Iになるとすると、ドレイン電流I12及びドレイン電流I32はそれぞれ電流Iになる。

10

20

30

40

50

## 【0027】

差動増幅回路の後段において、ドレイン電流  $I_{14}$  からドレイン電流  $I_{41}$  が引き抜かれ、電流 ( $I_{14} - I_{41}$ ) とドレイン電流  $I_{21}$ との合計の電流 ( $I_{14} - I_{41} + I_{21}$ ) が電流  $I_A$  になる。また、ドレイン電流  $I_{13}$  からドレイン電流  $I_{42}$  が引き抜かれ、電流 ( $I_{13} - I_{42}$ ) とドレイン電流  $I_{22}$ との合計の電流 ( $I_{13} - I_{42} + I_{22}$ ) がドレイン電流  $I_{33}$  になる。このドレイン電流 ( $I_{13} - I_{42} + I_{22}$ ) は、NMOSトランジスタ  $33 \sim 34$  によるカレントミラー回路により、ドレイン電流  $I_{34}$  になる。電流 ( $I_A = I_{14} - I_{41} + I_{21}$ ) とドレイン電流 ( $I_{33} = I_{34} = I_{13} - I_{42} + I_{22}$ ) との関係により、NMOSトランジスタ  $35$  のゲート電圧は決定される。

10

## 【0028】

また、差動増幅回路の後段において、ドレイン電流  $I_{15}$  から第二補正電流  $I_{43}$  が引き抜かれ、電流 ( $I_{15} - I_{43}$ ) と第一補正電流  $I_{23}$ との合計の電流 ( $I_{15} - I_{43} + I_{23}$ ) がドレイン電流  $I_{35}$  になる。

## 【0029】

ここで、入力電圧  $V_{inp}$  が入力電圧  $V_{inn}$ よりも高くなると、ドレイン電流  $I_{21}$  はドレイン電流  $I_{22}$ よりも少くなり、ドレイン電流  $I_{41}$  はドレイン電流  $I_{42}$  よりも多くなる。すると、ドレイン電流  $I_{13} \sim I_{14}$  は共に電流  $2I$  であるので、電流 ( $I_A = 2I - I_{41} + I_{21}$ ) はドレイン電流 ( $I_{33} = I_{34} = 2I - I_{42} + I_{22}$ ) よりも少なくなることにより、NMOSトランジスタ  $35$  のゲート電圧は低くなる。よって、NMOSトランジスタ  $35$  のオン抵抗は高くなり、バッファ  $51$  の入力電圧は高くなり、バッファ  $51$  の出力電圧  $V_{out}$  は高くなる。

20

## 【0030】

また、入力電圧  $V_{inp}$  が入力電圧  $V_{inn}$ よりも低くなると、上記のように、バッファ  $51$  の出力電圧  $V_{out}$  は低くなる。

## 【0031】

次に、入力電圧  $V_{inp}$  及び入力電圧  $V_{inn}$ が  $V_{DD}$  に近いときの動作を説明する。この時、ドレイン電流  $I_{13} \sim I_{15}$  はそれぞれ電流  $2I$  であるとする。また、PMOSトランジスタ  $11 \sim 12$  がそれぞれ非飽和動作し、NMOSトランジスタ  $31 \sim 32$  がそれぞれ飽和動作するので、ドレイン電流  $I_{11}$  はほとんど流れないとし、ドレイン電流  $I_{31}$  は電流  $2I$  になるとし、ドレイン電流  $I_{12}$  はほとんど流れないとし、ドレイン電流  $I_{32}$  は電流  $I$  になるとする。つまり、ドレイン電流  $I_{21} \sim I_{22}$  及び第一補正電流  $I_{23}$  もほとんど流れない。

30

## 【0032】

ここで、入力電圧  $V_{inp}$  が入力電圧  $V_{inn}$ よりも高くなると、ドレイン電流  $I_{21} \sim I_{22}$  がほとんど流れないものの、上記のように、バッファ  $51$  の出力電圧  $V_{out}$  は高くなる。

また、入力電圧  $V_{inp}$  が入力電圧  $V_{inn}$ よりも低くなると、上記のように、バッファ  $51$  の出力電圧  $V_{out}$  は低くなる。

## 【0033】

次に、入力電圧  $V_{inp}$  及び入力電圧  $V_{inn}$ が  $V_{SS}$  に近いときの動作を説明する。この時、ドレイン電流  $I_{13} \sim I_{15}$  はそれぞれ電流  $2I$  であるとする。また、PMOSトランジスタ  $11 \sim 12$  がそれぞれ飽和動作し、NMOSトランジスタ  $31 \sim 32$  がそれぞれ非飽和動作するので、ドレイン電流  $I_{11}$  は電流  $2I$  になるとし、ドレイン電流  $I_{31}$  はほとんど流れないとし、ドレイン電流  $I_{12}$  は電流  $I$  になるとし、ドレイン電流  $I_{32}$  はほとんど流れないとする。つまり、ドレイン電流  $I_{41} \sim I_{42}$  及び第二補正電流  $I_{43}$  もほとんど流れない。

40

## 【0034】

ここで、入力電圧  $V_{inp}$  が入力電圧  $V_{inn}$ よりも高くなると、ドレイン電流  $I_{41} \sim I_{42}$  がほとんど流れないものの、上記のように、バッファ  $51$  の出力電圧  $V_{out}$  は

50

高くなる。

また、入力電圧  $V_{inp}$  が入力電圧  $V_{inn}$  よりも低くなると、上記のように、バッファ 51 の出力電圧  $V_{out}$  は低くなる。

#### 【0035】

入力電圧  $V_{inp}$  及び入力電圧  $V_{inn}$  が中間の電圧のときには、差動増幅回路がアンプとして使用される場合、非反転入力端子  $inp$  と反転入力端子  $inn$  とはイマジナリショートし、入力電圧  $V_{inp}$  と入力電圧  $V_{inn}$  とは等しいので、ドレイン電流  $I_{42}$  と第二補正電流  $I_{43}$  とは等しく、ドレイン電流  $I_{22}$  と第一補正電流  $I_{23}$  とは等しい。よって、ドレイン電流  $I_{35}$  はドレイン電流  $I_{33}$  と等しい。また、差動増幅回路がコンパレータとして使用される場合、コンパレータの出力電圧が反転する時の入力電圧を検出する検出精度が重要であり、この時の入力電圧  $V_{inp}$  と入力電圧  $V_{inn}$  とは等しいので、ドレイン電流  $I_{42}$  と第二補正電流  $I_{43}$  とは等しく、ドレイン電流  $I_{22}$  と第一補正電流  $I_{23}$  とは等しい。よって、ドレイン電流  $I_{35}$  はドレイン電流  $I_{33}$  と等しい。つまり、ドレイン電流  $I_{33} \sim I_{35}$  は等しい。10

#### 【0036】

また、入力電圧  $V_{inp}$  及び入力電圧  $V_{inn}$  が  $V_{DD}$  に近いときはPMOSトランジスタ 11～12はそれぞれ非飽和動作し、入力電圧  $V_{inp}$  及び入力電圧  $V_{inn}$  が  $V_{SS}$  に近いときはNMOSトランジスタ 31～32はそれぞれ非飽和動作するが、上記のように、ドレイン電流  $I_{42}$  と第二補正電流  $I_{43}$  とは等しく、ドレイン電流  $I_{22}$  と第一補正電流  $I_{23}$  とは等しい。よって、ドレイン電流  $I_{35}$  はドレイン電流  $I_{33}$  と等しい。20

#### 【0037】

よって、入力電圧  $V_{inp}$  及び入力電圧  $V_{inn}$  が  $V_{DD}$  と  $V_{SS}$  間で変動しても、NMOSトランジスタ 33～34に対するNMOSトランジスタ 35のバイアス条件は常に同一である。よって、差動増幅回路のオフセット電圧は、入力電圧  $V_{inp}$  及び入力電圧  $V_{inn}$  に依存しない。20

#### 【0038】

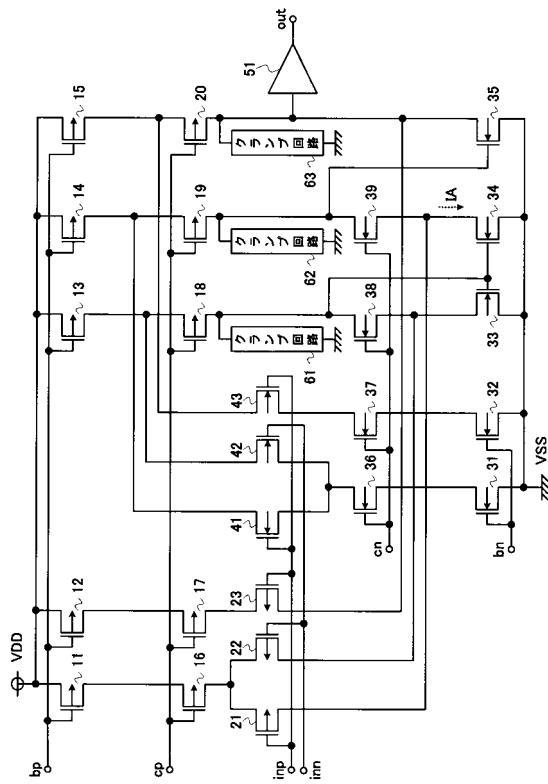

図2は、差動増幅回路の他の実施形態を示す回路図である。

図1の差動増幅回路において、応答速度を早くしたい場合に、電圧振幅を制限するためにクランプ回路 62 を設けることがある。この場合も、クランプ回路 62 のリーク電流によってバイアス条件が異なってしまい、オフセット電圧が発生してしまう、という課題がある。この課題を解決するために、図2の差動増幅回路は、クランプ回路 61 及びクランプ回路 63 を設ける。30

#### 【0039】

クランプ回路 61 は、PMOSトランジスタ 18 のドレイン及びNMOSトランジスタ 38 のドレインの接続点（カレントミラー回路の一端）と接地端子との間に設ける。クランプ回路 62 は、PMOSトランジスタ 19 のドレイン及びNMOSトランジスタ 39 のドレインの接続点（カレントミラー回路の他端）と接地端子との間に設ける。クランプ回路 63 は、PMOSトランジスタ 20 のドレイン及びNMOSトランジスタ 35 のドレインの接続点と接地端子との間に設ける。クランプ回路 61～63 は、各接続点の電圧が所定電圧よりも高くならないよう動作する。40

#### 【0040】

クランプ回路 61～63 を同じ回路構成とするので、クランプ回路 61～63 のリーク電流は等しく、NMOSトランジスタ 33～35 のドレイン電流  $I_{35} \sim I_{35}$  は等しい。

#### 【0041】

なお、図1では、PMOSトランジスタ 23 及びNMOSトランジスタ 43 のゲートは非反転入力端子  $inp$  にそれぞれ接続されているが、図示しないが、これらのゲートが反転入力端子  $inn$  にそれぞれ接続されても良い。また、図示しないが、PMOSトランジスタ 23 のゲートが非反転入力端子  $inp$  に接続され、NMOSトランジスタ 43 のゲー50

トが反転入力端子  $i_{nn}$  に接続されても良い。また、図示しないが、PMOSトランジスタ23のゲートが反転入力端子  $i_{nn}$  に接続され、NMOSトランジスタ43のゲートが非反転入力端子  $i_{np}$  に接続されても良い。

【符号の説明】

【0042】

11～23 PMOSトランジスタ

31～39、41～43 NMOSトランジスタ

51 バッファ

【図1】

【図2】

【図3】

---

フロントページの続き

審査官 高橋 義昭

(56)参考文献 特開2001-144558(JP,A)

特開2006-314040(JP,A)

特開2000-223970(JP,A)

特開平01-264406(JP,A)

実開昭60-184314(JP,U)

(58)調査した分野(Int.Cl., DB名)

H03F 3/34 3/45