Original Filed April 27, 1949

Original Filed April 27, 1949

Original Filed April 27, 1949

F/G.11

INVENTOR

RICHARD M. BLOCH

BY Elmeng Som

ATTORNEY

Original Filed April 27, 1949

Original Filed April 27, 1949

Original Filed April 27, 1949

F16.8B

Original Filed April 27, 1949

Original Filed April 27, 1949

Original Filed April 27, 1949

Original Filed April 27, 1949

Re. 24,447

# United States Patent Office

1

#### 24,447

### DIAGNOSTIC INFORMATION MONITORING SYSTEM

Richard M. Bloch, Newton, Mass., assignor to Raytheon Manufacturing Company, Newton, Mass., a corporation of Delaware

Original No. 2,634,052, dated April 7, 1953, Serial No. 89,871, April 27, 1949. Application for reissue May 3, 1957, Serial No. 659,195

### 41 Claims. (Cl. 235—61)

Matter enclosed in heavy brackets [1] appears in the original patent but forms no part of this reissue specification; matter printed in italics indicates the additions made by reissue.

This invention relates in general to the handling of information in the form of time-varied electric waves, and 20 more particularly to methods of and means for supervising the accuracy of and correct handling of such information.

It is known to supervise or monitor the identity of an electric wave which is being transferred from one place 25 to another by means of another electric wave identical with the first and transferred therewith or subsequently thereto. Such a procedure requires either complete duplicate handling equipment or a complete repetition of the operation being supervised. Likewise, it is known, in the art of electronic and electrical computing machines, to supervise the operations of such machines by sending the same problem through twice simultaneously or twice in succession. The former process again requires complete duplicate equipment, and the latter process obviously consumes double the time required merely to perform the desired operations.

The present invention provides means to monitor information in the form of time-varied electric waves which creates for each item of information a characteristic 40 time-varied electric wave of a prescribed short duration which is employed as an indicator and is thereafter carried with the main electric wave as an additional, readily Each time the main electric separable part thereof. wave is handled, the indicator is created anew, and the 45new indicator is then compared with the indicator that is carried with the main electric wave for the purpose of ascertaining whether or not the main electric wave has undergone any change. The amount of additional equipment required to provide the indicators is approximately twenty percent as extensive as the equipment that handles the main information, while the simultaneity of systems employing complete duplicate equipment is substantially preserved. Further, the present system is diagnostic for the reason that a new indicator is created from the main wave each time it is handled or transferred, so that the place in a complete system where a fault may have occurred can be readily known. The present invention is adaptable to use with limitless forms of information handling systems and various kinds of wave forms. It has utility, for example, in telemetering systems of all kinds and varieties, and in electrical computing machines of all degrees of complexity.

In its use in computing machines, the invention is particularly valuable in that it may be modified in many ways to supervise not only the identity of information which is transferred from place to place within the machine, but also the accuracy of mathematical operations performed upon such information. Thus, for example, an and second electric waves is supervised by means which creates from each wave a short indicator wave in ac2

cordance with a prescribed scheme, then creates from the sum of the two original waves a third short indicator wave, and then operates upon these indicator waves in a prescribed manner to produce an electric wave which has only one possible form if the addition was performed correctly. The means for accomplishing this supervision is again small in extent as compared with the main computing equipment, and functions practically simultaneously therewith. Other processes of subtraction, multiplication, and division are supervised by analogous means and methods.

While the invention is not limited in its employment to any particular form of electric wave, it is most easily understood in connection with systems which store and transfer information in the form of electric waves consisting of groups of discrete pulses. Digital telemetering systems and computing machines employing the binary system of notation employ such groups of discrete pulses to represent information items. In one form, a group of discrete pulses represents a binary number by providing a pulse space in a train of time-spaced spaces for each digit of the number, the presence of an electric pulse in a space representing a "1" and the absence of a pulse in a space representing a "0."

When the information which is being handled in the binary notation system originates in the decimal system, it must be converted to the binary form. Similarly, endproduct information is often converted to the decimal form. The present invention employs means which supervises the accuracy of such conversions, also, by creating indicators for the quantity being converted, the conversion product, and the unconverted remainder, the indicators being created in accordance with a scheme such that their sum results at all times in an electric wave which can have only one possible form if the conversion has been effected correctly.

The foregoing and other features of the invention will become more apparent from the detailed description of certain specific embodiments that follows. The description refers to the accompanying drawings, wherein:

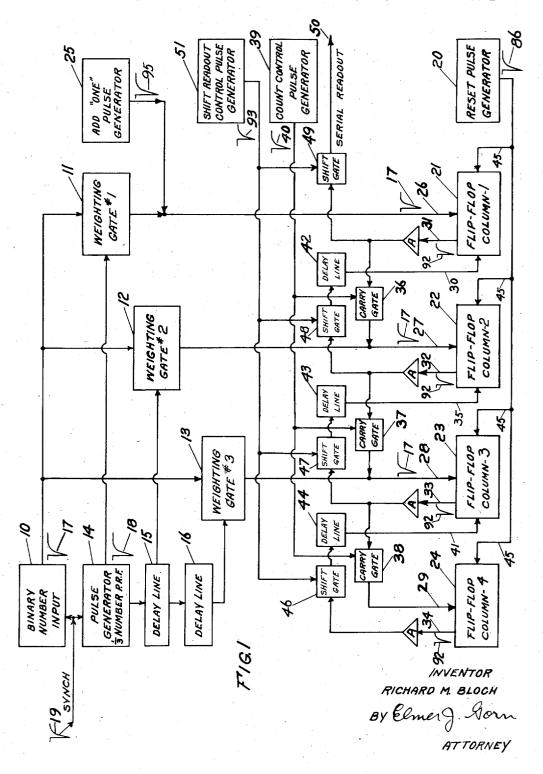

Figure 1 is a block diagram of a system which generates a four-column binary indicator from any multi-columnar series of pulses and pulse spaces representing, for example, a binary number;

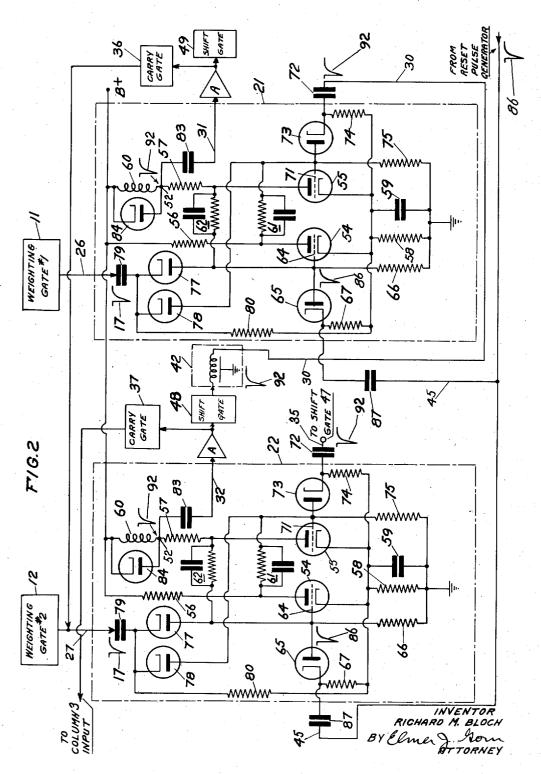

Figure 2 is a circuit diagram illustrating certain details of Figure 1;

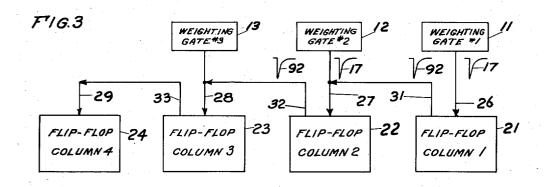

Figure 3 is a block diagram illustrating one phase of the operation of Figure 1;

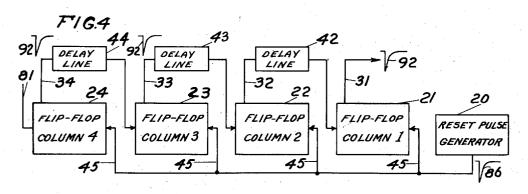

Figure 4 is a block diagram illustrating another phase of the operation of Figure 1;

Figure 5 is a diagram showing a group of time-spaced pulses representing an item of information in binary notation as handled in accordance with the invention;

Figure 6 is a block diagram of a system which supervises the identity of a group of pulses like that shown in Figure 5 which is being transferred from one location to another;

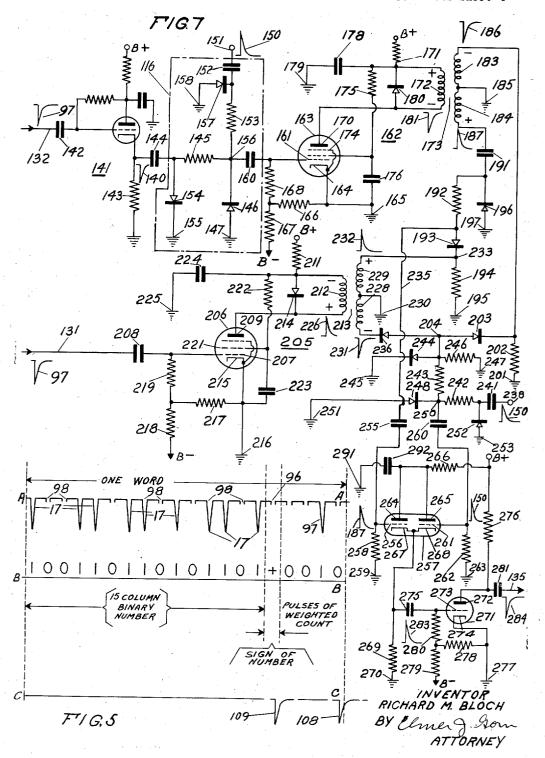

Figure 7 is a circuit diagram of an arrangement which may be employed for sensing or coincidence checking in the systems shown in Figure 6 and Figure 8;

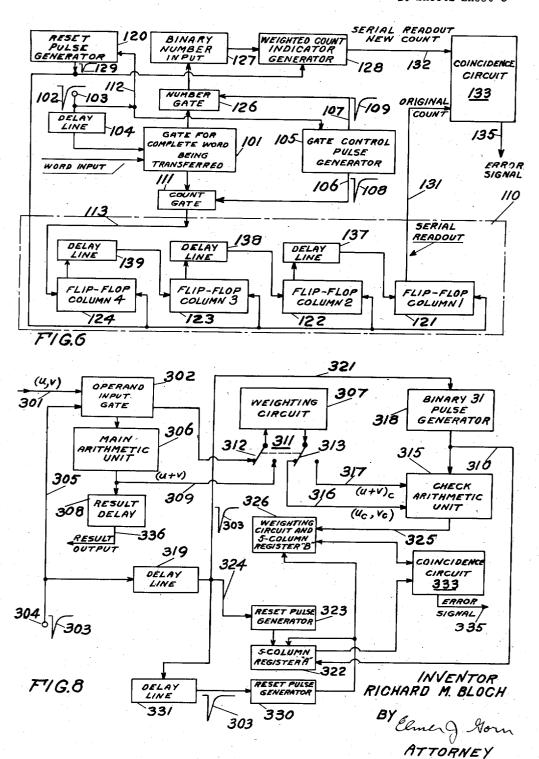

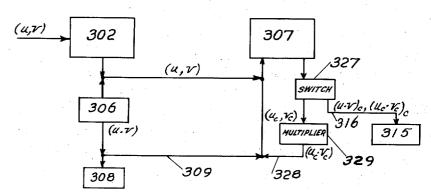

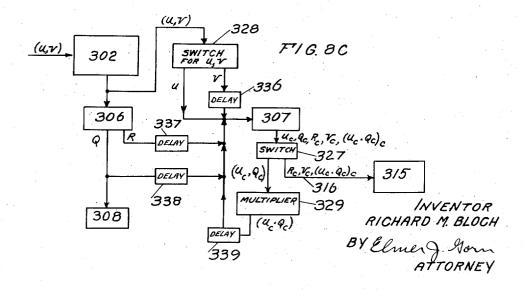

Figure 8 is a block diagram of a system which supervises the correct performance of an arithmetic operation upon two binary quantities;

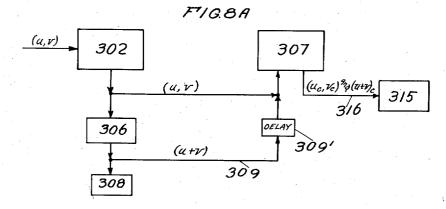

Figures 8A, 8B and 8C are modifications of the system of Figure 8;

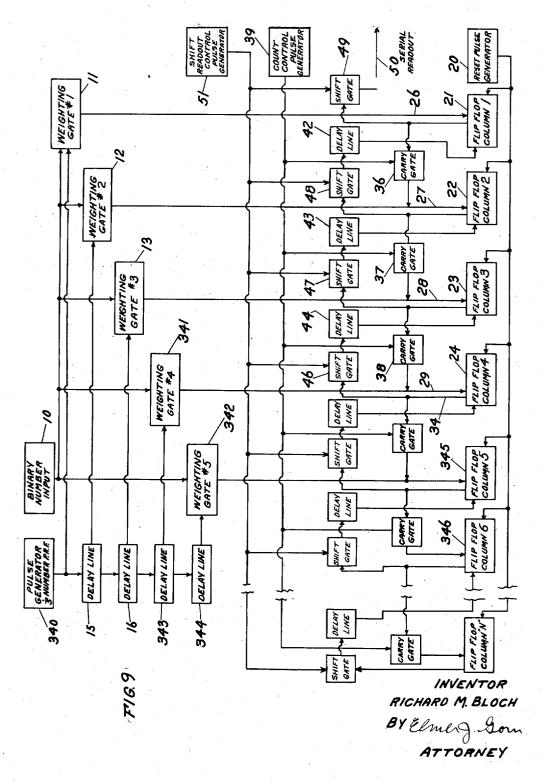

Figure 9 is a block diagram of a suitable weighting circuit for use in the system of Figure 8:

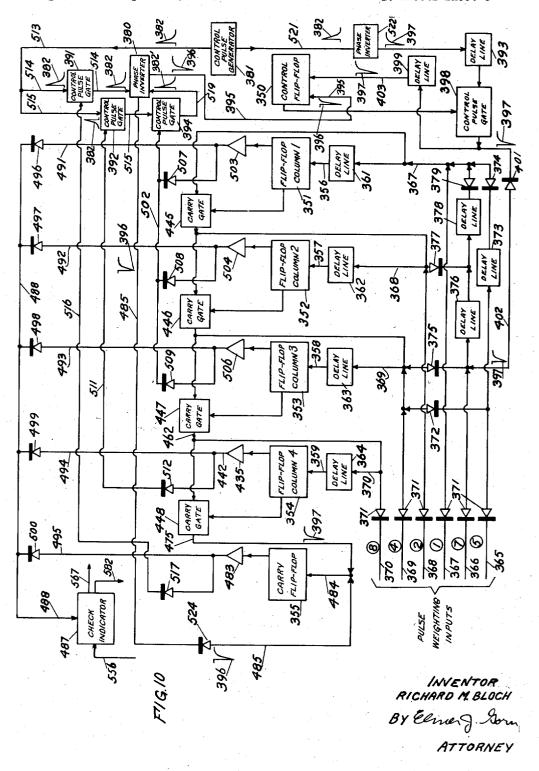

Figure 10 is a block diagram of a system which superaddition of two quantities which are represented by first 70 vises the accuracy of conversions between the binary and decimal systems of notation;

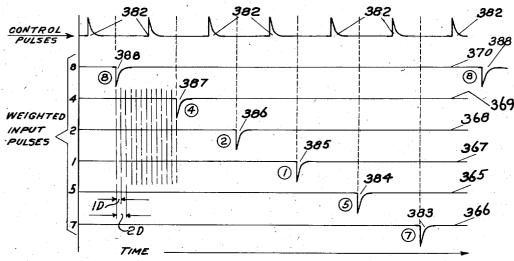

Figure 11 is a chronological diagram illustrating the

time relationship existing among certain of the pulses which are employed in the system of Figure 10;

Figure 12 is a circuit diagram illustrating details of cer-

tain parts of Figure 10;

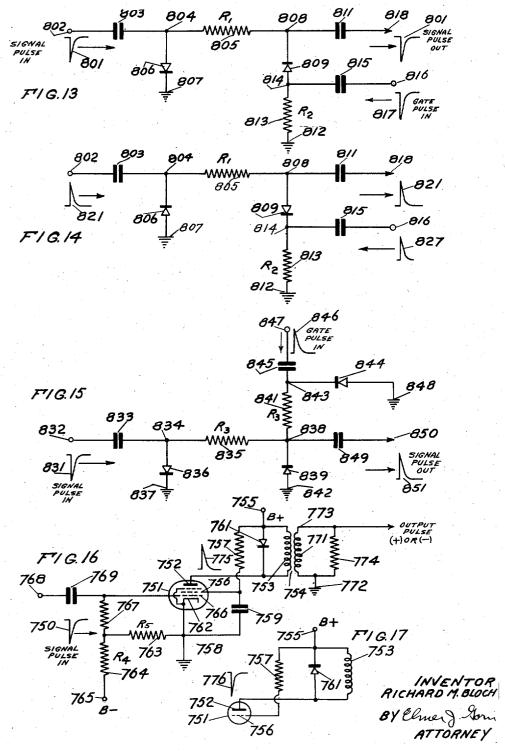

Figures 13, 14 and 15 are circuit diagrams illustrating various forms of gate circuits which may be employed in carrying out the invention; and

Figures 16 and 17 are circuit diagrams illustrating two forms of a phase inverter which may be employed in carrying out the invention.

### MONITORING THE IDENTITY OF INFORMATION

Referring now to Figure 1, a binary number consisting of a chronological series of voltage pulses 17, for which an 15indicator is to be generated, is provided from a binary number input source represented by a block 10. pulses 17 may be either positive or negative, as desired. In the present description, negative pulses are illustrated. The pulses 17 of the number from the block 10 are sequentially provided in parallel to three gates 11, 12 and 13, which may be called weighing gates #1, #2 and #3, The three weighting gates are normally closed, in the sense that they do not permit the pulse 17 to pass, and are operated to an open, or pulse-passing, condition by means of negative gate control pulses 18 furnished by a pulse generator 14 via two delay lines 15 The binary number consists of a chronological series of pulse spaces, each of which may or may not be occupied by a pulse 17, which spaces are repeated at a 30 predetermined repetition frequency. The pulse generator 14 furnishes gate control pulses 18 at a pulse repetition frequency which is one-third that of the binary number. A synchronizing pulse 19, furnished from a suitable master timing source (not shown), is furnished to both the 35 binary number input 10 and the pulse generator 14 in order that each gate control pulse 18 shall occur simultaneously with a predetermined number pulse 17 or pulse space of the binary number. The gate control pulse 18 is applied directly to weighting gate #1, and at the same time to the first delay line 15. The pulse which emerges from the first delay line 15 is applied directly to weighting gate #2 and at the same time to the second delay line 16. The pulse which emerges from the second delay line 16 is applied directly to weighting gate #3. The gate control pulse 18 is delayed in each delay line 15 and 16 by an amount equal to the spacing between two adjacent pulses 17 of the binary number which occupy adjacent pulse spaces. The effect of this arrangement is that pulses 17 which occupy successive pulse spaces of the 50binary number from the input 10 pass through successive gates from gate #1 to gate #3 and then back to gate #1.

Four "flip-flop" circuits, of a kind to be described below, are represented by blocks 21, 22, 23 and 24, respec-These blocks are in columns 1, 2, 3 and 4, respectively, of a binary system register. The binary number pulse 17 which passes through weighting gate #1 is provided to the column 1 flip-flop 21 via a signal input line 26, the number pulse 17 passing through gate #2 to the column 2 flip-flop 22 via a signal input line 27, and the number pulse passing through gate #3 to the column 3 flip-flop 23 via a signal input line 28. umn 4 flip-flop 24 is provided with a signal input line 29. As will be explained below, each of the flip-flops 21 to 24, inclusive, is arranged so that it will change state each time a number pulse 17 is applied via its signal input line 26, 27, 28 or 29, respectively. Each of the flipflops 21 to 24, inclusive, is provided also with a signal output line 31, 32, 33 and 34, respectively, in which negative output voltage pulses 92 appear. An amplifier A 70 may be included in each output line, if desired. In each flip-flop, one state of the flip-flop represents the digit "1" standing in the column of the flip-flop, while the other

4

state, a pulse appears in its output line, as will be explained more in detail below.

The output line 31 of the column 1 flip-flop 21 is connected by way of a first carry gate 36 to the signal input line 27 of the column 2 flip-flop 22. The output line 32 of the column 2 flip-flop is connected by way of a second carry gate 37 to the signal input line 28 of the column 3 flip-flop 23. The output line 33 of the column 3 flipflop is connected by way of a third carry gate 38 to the 10 signal input line 29 of the column 4 flip-flop 24. The carry gates 36, 37 and 38 are all normally closed in the sense that they do not permit the output pulse 92 to pass, and are simultaneously operated to an open or pulsepassing condition by a negative pulse 40 furnished by a count control pulse generator 39 which is connected to all three carry gates in parallel. The pulse 40 furnished by the count control pulse generator 39 occurs simultaneously with each binary number pulse or pulse space, the generator 39 being controlled, if desired, by the same central synchronising mechanism (not shown) which provides the synchronizing pulse 19.

The four flip-flops 21 to 24, inclusive, and their associated carry gates 36 to 38, inclusive, may be termed a "register," here a four-column register. The simultaneous states of the individual flip-flops at any one instant define a four-column binary quantity, which quantity is said to "stand in the register" at that instant. The quantity which stands in the register at the end of the operation upon the binary number for which an indicator is created is the indicator. The manner in which the register is operated to create an indicator will be presently explained in greater detail in connection with Figure 3.

The signal output line 34 of the column 4 flip-flop 24 is connected by way of a shift gate 46 and a delay line 44 to a first side input line 41 of the column 3 flip-flop The signal output line 33 of the column 3 flip-flop is connected by way of a shift gate 47 and a delay line 43 to a first side input line 35 of the column 2 flip-flop 22. The signal output line 32 of the column 2 flip-flop is connected by way of a shift gate 48 and a delay line 42 to a first side input line 30 of the column 1 flip-flop 21. The signal output line 31 of the column 1 flip-flop is connected by way of a shift gate 49 to a serial read-out terminal 50. The shift gates 46, 47, 48 and 49 are all normally closed in the sense that they do not permit the output pulse 92 to pass, and are simultaneously operated to an open, or pulse-passing, condition by a negative pulse 93, furnished by a shift read-out control pulse generator 51 which is connected to all the shift gates in parallel. The shift read-out control pulse generator 51 is operated only when it is desired to remove or "read out" the information standing in the register, namely, the indicator of the main binary number. A reset pulse generator 20 which produces negative reset pulses 86 is connected in parallel to a second side input line 45 of each of the flip-flops 21 to 24, inclusive. The reset pulse generator is operated in cooperation with the shift read-out control pulse generator 51 during a read-out operation, as will presently be explained in connection with Figure 4. The delay lines 42, 43 and 44 provide a time delay to the passage of the output pulses 92 furnished thereto which is substantially longer than the duration of a shift readout pulse 93.

A single-pulse generator 25 which produces a single negative pulse 95 at the end of the indicator-creating operation, is connected to the signal input line 26 of the column 1 flip-flop 21 for the purpose of adding the binary quantity "1" to whatever binary quantity stands in the register at the end of the operation wherein an indicator is created, and prior to reading out the indicator. The purpose of adding 1 will also be presently explained.

Referring now to Figure 2, the circuits therein illustrated are the column 1 and column 2 flip-flops 21 and trated are the column 1 and column 2 flip-flops 21 and 22, respectively. Considering the column 1 flop-flop 21, the circuit is basically an Eccles-Jordan circuit including

first and second triodes 54 and 55, respectively, connected at their anodes to an anode voltage terminal B+, via anode resistors 56 and 57, respectively, and at their cathodes to a common ground via a cathode resistor 58, which is bypassed for alternating current by a suitable capacitor 59. An inductor 60 is connected between the anode resistor 57 of the second triode and the B+ terminal. A diode 84 is connected in shunt with the inductor, the cathode being connected to the B+ end thereof. Each anode of each triode is connected via a suitable 10 parallel-resistance-capacitance circuit 61 or 62 to the control grid 64 or 71 of the other triode. The control grid 71 of triode 55 is connected to the output line 32 of the column 2 flip-flop 22 via the delay line 42, the shift gate 48, the first side input line 30, a capacitor 72, and a diode 73 in series, the anode of the diode 73 being connected to the grid 71. A resistor 75 is connected between the grid 71 and ground. A resistor 74 is connected between the cathode of the diode 73 and the cathode of the triode 55. By this connection to the grid of triode 55, an output pulse 92 from the column 2 flip-flop 22 is impressed upon the column 1 flip-flop 21 if the shift gate 48 is in an open condition. The reset pulse generator 20 is connected to the control grid 64 of triode 54 by way of the second side input line 45, a capacitor 87, and a diode 65 in series, the anode of diode 65 being connected to the grid 64 and the cathode of diode 65 being connected to the cathode of the triode 54 via a resistor 67. A resistor 66 is connected between the control grid 64 and ground.

Thus far, the circuit of the two triodes 54 and 55 will be recognized as the well-known Eccles-Jordan circuit which can be triggered at either of the control grids 64 or 71 by means of a negative pulse applied at the cathode of the diode 65 or 73, respectively. Each of the control grids 64 and 71 has a second diode 77 and 78, respectively, connected thereto at its anode. The cathodes of these second diodes are connected together and via a coupling capacitor 79 to the signal input line 26 which is connected to weighting gate #1. A resistor 80 is connected from the cathodes of the second diodes 77 and 78 to the cathodes of the triodes 54 and 55. A negative pulse 17 brought into the flip-flop via the input line 26 will change the state of the flip-flop regardless of its preexisting state. A negative pulse 86 or 92, which is brought into the flip-flop at one side or the other only, will change the state of the flip-flop only if the triode to which it is applied is previously in a conductive state.

The output signal line 31 of the flip-flop is connected 50 via a coupling capacitor 83 to the junction point 52 of the anode circuit resistor 57 of the second triode 55 and the inductor 60. The diode 84 is connected at its anode to said junction point. When the second triode 55 is rendered non-conductive, the potential of the anode thereof 55 assumes a "high" state, and, when this triode is rendered conductive, the anode potential thereof assumes a "low" The Eccles-Jordan circuit of the flip-flop is so dimensioned that it can occupy only one state wherein the first triode 54 is conductive and the second triode 55 is nonconductive, or the opposite state, and its state is abruptly changed by a negative pulse such as the pulse 17, 86 or 92 properly applied thereto. When the second triode 55 is abruptly rendered conductive, current begins abruptly to flow through the inductor 60. During 65 the initial surge of current, the junction point 52 of the inductor and the anode resistor 57 undergoes a correspondingly abrupt change in potential in the negative direction with respect to the B+ terminal, and thereafter positive direction, returning eventually substantially to the potential level of the B+ terminal. These changes produce the output pulse 92. Any tendency of the junction point 52 to assume a potential which is positive with relation to the B+ terminal is inhibited by the diode 84 75

which is shunted across the inductor 60, since the diode becomes conductive when that happens and short-circuits the inductor. Thus, when the second triode 55 is abruptly rendered nonconductive, no positive pulse corresponding to the negative pulse 92 is produced. The diode 84 is thus employed as a diode clamp, and it will be recognized by those skilled in the art that a crystal or other form of dry rectifier may be employed in place of an electron-tube diode, if desired.

The circuit of the column 2 flip-flop 22 is identical to that of the column 1 flip-flop 21 and will not be described in detail. Similar elements of both circuits bear the same reference characters. Likewise, the column 3 and 4 flipflops 23 and 24, which are not shown in Figure 2, have similar circuits to that of the column 1. The column 4 flip-flop 24, however, has no input line to the first side thereof, and accordingly, in column 4, the first side input diode 73, and its resistor 74 and capacitor 72, may be omitted, if desired.

Each flip-flop is operated by negative pulses. The input pulse 17 from a weighting gate is a negative pulse applied to the cathodes of input diode 77 and 78 in parallel. This pulse cuts off the triode 54 or 55 which is conductive, thereby rendering the other triode conductive. The output pulse 92 from a shift gate 46, 47 or 48 is negative, and is applied through the capacitor 72 and first side input diode 73 to the control grid 71 of the second triode 55, and is effective to cut off triode 55 should that tube be conducting when pulse 92 arrives. The reset pulse 86 30 from the reset pulse generator 20 is negative, and is applied through a capacitor 87 and second side input diode 65 to the control grid 64 of the first triode 54, and is effective to cut off triode 54 in the event that that tube is conducting when the reset pulse 86 arrives. Thus, the 35 pulse 17 from the weighting gate causes a change of state of the flip-flop regardless of the state thereof at the time pulse 17 arrives, while the reset pulse 86 or the output pulse 92 changes the state of the flip-flop only if the triode to which it is applied is conductive at the time of application.

It is important to remember that the output of each flip-flop 21 to 24, inclusive, is either a negative pulse 92 or no pulse at all. As a matter of definition, it may be stated that, when the second triode 55 is in a nonconductive condition, a "1" stands in the flip-flop, and, when triode 55 is in a conductive condition, a "0" stands in the flip-flop. The basis of this definition is that the negative pulse 92, which the flip-flop will furnish when the second triode 55 is rendered conductive, is employed to represent the digit 1 being extracted from the flip-flop. In accordance with this definition, when the negative reset pulse 86 is furnished to the flip-flops, it causes all four flip-flops to stand simultaneously at zero.

The various gates of the system of Figure 1 may be constructed in accordance with Figure 13, if desired. In Figure 13, a signal input pulse 801 is applied at a signal input terminal 802. Terminal 802 is connected to one side of an input coupling capacitor 803, which is connected at the other side to the junction 804 of a resistor 805 and a unidirectional conductor 806. The unidirectional conductor 806 and others shown and described herein may be of any desired form, for example, an electron tube diode or a crystal or other form of rectifier may be used, and will hereafter be referred to simply as a rectifier. The function of rectifier 806 is essentially that of a clamp and it is poled to conduct current to ground at 807 whenever the junction 804 becomes positive with respect to ground. In this manner, the signal pulse is maintained practically purely negative. Resistor 805 a substantially exponential change in potential in the 70 is connected at its other end to the junction 808 of a second rectifier 809 and one side of an output coupling capacitor 811. The second rectifier 809 is connected to ground at 812 via a second resistor 813, and is poled to become conductive between ground and junction 808 whenever the junction 808 is negative with respect to the

.

grounded side of the rectifier. The junction 814 of this grounded side and the second resistor 813 is connected via a gate pulse coupling capacitor 815 to a terminal 816 via which a negative gate pulse 817 is introduced. The output coupling capacitor 811 is connected at its free side to a signal pulse output terminal 818.

The values of resistors 805 and 813 are designated as  $R_1$  and  $R_2$ , respectively.  $R_1$  is much greater than  $R_2$ , for example, these may be 5,600 ohms and 300 ohms, respectively. The peak magnitude of the gate pulse 817 should 10 be at least as great as that of the signal pulse 801, and is preferably slightly greater. If these conditions are provided, the gate pulse 817 is able to so bias the grounded side of the second rectifier 809 with respect to ground that the signal pulse 801 cannot render junction 808 nega- 15 tive with respect to said grounded side. Thus, if the gate pulse 817 and the signal pulse 801 occur simultaneously, the signal pulse 801 passes through capacitor 803, resistor 805, and capacitor 811 to the output terminal 801. In this condition, the gate is said to be "open." On the other hand, if the gate pulse 817 is absent, the signal pulse 801 is able to render junction 808 negative with respect to the grounded side of the second rectifier 809, and is therefore conducted to ground at 812 via the second resistor 813. The resistance of the rectifier 809 when conductive is about 100 chms. Acordingly, the total resistance from the input terminal 802 to ground at 812 is 6,000 ohms, and junction 808 is 400 ohms from the grounded end of this resistance. Thus, there is in effect a voltage divider from the input terminal 802 to ground at 812 by which the peak voltage of the signal pulse 801 is reduced to about 1/60 of its original value. The resulting amount of signal pulse voltage that reaches the output terminal 818 is so small as to be inoperative upon the circuits that follow, and, therefore, the gate is said to be "closed" in this condition.

The gate of Figure 13 may be employed as a weighting gate 11, 12 or 13 in the system of Figure 1 by bringing the binary number pulse 17 to the signal input terminal 802 and the gating pulse 18 to the gate pulse terminal 816 thereof. It may be employed as a shift gate 46, 47, 48 or 49 by applying the flip-flop output pulse 92 to the signal input terminal 802 and the shift readout pulse 93 to the gate pulse terminal 816, or as a carry gate 36, 37 or 38 by applying the count control pulse 40 to the gate pulse terminal 816 in place of the shift read-out pulse 93.

In the gate of Figure 13, the signal and gate pulses 801 and 817, respectively, are both negative, and the output pulse is negative. In Figure 14, this gate is modified by inverting the connections to the two rectifiers 806 and 809 so that a positive input pulse 821 and a positive gate pulse 827 will produce a positive output pulse 821. Otherwise, the gates of Figures 13 and 14 are similar in construction and operation. Figure 15 illustrates a somewhat different gate wherein the polarities of the signal and gate pulses are opposite.

In Figure 15, a negative signal pulse 831 is brought to the input terminal 832 and coupled via a first coupling capacitor 833 to the junction 834 of a first resistor 835 and first rectifier 836. Rectifier 836 is connected to ground at 837, and poled to clamp the input pulse 831 to be susbtantially purely negative, in the same manner as rectifier 806 in Figure 13. Resistor 835 is connected at its other end to the junction 838 of a second rectifier 839 and a second resistor 841. The second rectifier 839 is connected to ground at 842 and poled oppositely to the first rectifier 836. Tthe other end of resistor 841 is connected to the junction 843 of a third rectifier 844 and one 70 side of a gate pulse coupling capacitor 845. A positive gate pulse 846 is brought to the other side of the capacitor 845 via a gate pulse input terminal 847. The third rectifier 844 is connected to ground at 848 and poled to

8

tive. Junction 838 is connected via signal output coupling capacitor 849 to a signal output terminal 850.

Resistors 835 and 841 are preferably of the same value, R<sub>3</sub>. In the absence of a signal pulse 831, the gate pulse 846 passes through resistors 841 and 835 and rectifier 836 to ground at 837. The potential level of the gate pulse at junction 838 is sufficiently high so that a positive signal pulse 851 appears at the output terminal 850. When the signal pulse 831 is present, it substantially cancels the positive gate pulse at junction 838. To this end, the magnitudes of the two input pulses 831, 847 are preferably adjusted so that, when both are present, rectifier 839 becomes at least slightly conductive. The gate of Figure 15 is thus one in which, when a signal pulse 831 is present, there is no output pulse, but, when the signal pulse 831 is absent, there is an output pulse 851 of the opposite polarity. This gate has use in the present invention, as will be described later. Although many other forms of gates can be devised, and some others will be described later, an understanding of the foregoing gates will aid in the explanation of the operation of many parts of the systems described herein.

Referring now to Figure 3, the diagram of this figure illustrates the operation of the four-column register of Figure 1 when binary number pulses 17 are being brought thereto to create an indicator. During each step of this operation, the carry gates 36, 37 and 38 in Figure 1 are all open, since the count control pulse 40 occurs simultaneously with each binary number pulse 17 or pulse space, while the shift gates 46 to 49, inclusive, are closed throughout the operation. A negative pulse 86 from the reset pulse generator is applied to the register, that is, to all the flip-flops in parallel, prior to commencing the operation. By so doing, triode 54 of each flip-flop is rendered nonconductive, thereby rendering triode 55 of each flip-flop conductive. Then, when the first pulse 17 from a weighting gate is introduced into the register, it renders the triode 55 of the flip-flop to which it is applied nonconductive, so that a 1 stands in the flip-flop. Thus, if there is a pulse 17 in the first binary number space, column 1 flip-flop 21 stands at 1 when the pulse is applied through weighting gate #1. In the case where the binary number has a second pulse 17 in the second binary number space, this second pulse is applied through weighting gate #2 to column 2 flip-top 22, thereby causing flip-flop 22 also to stand at 1. Consider now that the third binary number space of the input number is a zero. Then no pulse is applied to column 3 flip-flop 23 when weighting gate #3 is opened, and flip-flop 23 stands at zero. If further the fourth binary number space contains a pulse 17, this fourth space pulse is applied through weighting gate #1 to column 1 flip-flop 21, and initiates the following sequence of events. First, the fourth column number pulse 17 renders triode 54 of column 1 flip-flop 21 nonconductive and therefore renders triode 55 of the same flip-flop conductive. As a result, column 1 flip-flop 21 produces an output pulse 92 in its output line 31 and then stands at zero. The second event that takes place is that output pulse 92 from column 1 flip-flop 21 is carried via output line 31 to input line 27 of column 2 flip-flop 22 where it is effective in the same manner as a binary number pulse 17 from weighting gate #2. Therefore, column 2 flip-flop 22 is caused to stand at zero and to produce an output pulse 92 in its output line 32, which provides the pulse 92 to the input line 28 of column 3 flip-flop 23. It will be remembered that flip-flop 23 has, to this point, been standing at zero, and now is caused to stand at 1 by the output pulse 92 from the column 2 flip-flop 22. Thus, the register has performed the addition of binary number 1 to binary number 0 1 1 and now stands at the sum of those numbers, which is 100 in the binary system.

tor 845 via a gate pulse input terminal 847. The third rectifier 844 is connected to ground at 848 and poled to clamp the gate pulse 846 to be substantially purely posi- 75 to the various flip-flops in columns 1, 2 and 3. However,

the register shown in Figure 3 differs from an ordinary adding device in that it is limited to four columns. Thus, when this register arrives at binary 15, which is expressed 1 1 1 1 in the binary system, the addition of a single pulse in column 1, namely, the addition of binary 1, causes the register to stand at 0 0 0 0. As is known, the binary representation of 16 is 1 0 0 0 0, but the register shown in Figure 3 is lacking a fifth column, and therefore, represents binary 16 by 0 0 0 0. Thus, binary 17 is represented by 0 0 0 1, which is the same as the binary representation 10 of 1. It is apparent, therefore, that the register shown in Figure 3 counts up to 15 and starts over again at zero with 16, thereafter counting 17 to 31 in the same manner as 1 to 15, respectively, and starting over again with 32. This process is repeated at 48, 64 and all integral multiples of 16. The register of Figure 3 is accordingly called a "modulo 16" counter. It has the property that regardless of the magnitude of a binary number that is provided from the binary number input 10, after the entire binary number has been applied to it as shown in Figure 1, it stands at a particular four-column binary number which is arrived at by a process in which the columns of the original binary number being treated are weighted, from right to left, in the fashion 1 2 4 1 2 4 1 2 4, and then the weighted sum of those columns wherein there is a "1" is taken in the fashion modulo 16 as set forth above; that is, the first column binary digit commencing at the right-hand side of the binary number input is applied to column 1, the digit of the second column to the left to column 2, the digit of the third column to the left to column 3, the digit of the fourth column to the left to column 1, etc. As will be recognized, a digit in column 3 represents binary number 4, a digit in column 2 represents binary number 2, and a digit in column 1 represents binary number 1. Hence, the various columns of the original binary number input are considered to be weighted in the manner set forth, and, therefore, the gates 11, 12 and 13 are called "weighting gates."

Figure 4 illustrates the register of Figure 1 as arranged to read out the information stored therein. column binary number indicator which is generated by the register may be read out of the register at any desired pulse repetition frequency which is controlled by the frequency with which the reset pulse generator 20 produces reset pulses 86. The shift read-out control pulse generator 51 produces a shift read-out pulse 93 substantially simultaneously with the production of each reset pulse 86, so that the shift gates 46 to 49, inclusive, are all opened each time a reset pulse 86 is produced. Consider, for example, that the four-column binary number 1 1 0 1 stands in the register. Now apply a reset pulse 81 from the reset pulse generator 20 to the register. This pulse is applied to the first triode 54 of each flip-flop, which triode is conductive in each flip-flop which stands at 1 and nonconductive in each flip-flop which stands at zero. Being negative, the pulse 86 renders triode 54 nonconductive in each flip-flop that stands at 1, namely, the column 4, 3 and 1 flip-flops 24, 23 and 21, respectively, causing all the flip-flops to stand at zero. In the case of the column 4, 3 and 1 flip-flops 24, 23 and 21, respectively, this change causes the second triode 55 to become conductive, and, therefore, each of flip-flops 24, 23 and 21 produces an output pulse 92 in output lines 34, 33 and 31, respectively. The output pulse 92 from line 31 is available via  $_{65}$ the serial read-out terminal 50 (Figure 1) to a succeeding circuit, and may be said to have been "read out." the serial read-out terminal 50 may be connected to the memory of a complete computer system (not shown), where its output can be stored together with the original 70 binary number, in the manner illustrated in Figure 5, for example, and through the memory to the word input line of Figure 6, as will presently appear. After suitable delay furnished by the delay lines 44 and 43 which permits the output pulse 92 from the first column flip-flop 21 to 75

10

be removed, the reset and shift read-out pulses 86 and 93, respectively, to terminate, and the shift gates 46 to 49, inclusive, to become closed, the output pulses 92 in lines 34 and 33, respectively, are provided to the control grids 71 of the second triodes 55 of the column 3 and 2 flip-flops 23 and 22, respectively. As a result, the second triode 55 of each of columns 2 and 3 is again rendered nonconductive, so that a 1 stands in each of columns 2 and 3. Since the column 2 flip-flop 22 produces no output pulse 92, the column 1 flip-flop 21 stands at zero. Thus, in response to the first reset pulse 86 from the reset pulse generator 20, the binary number 1 1 0 1 is shifted one column to the right in the register which now stands at 0 1 1 0, and the extreme right-hand digit of the original number has been read out. Because of this shifting action, the register employed as in Figure 4 is termed "shift register."

Similar considerations to the foregoing make apparent the fact that each reset pulse 86 causes the number standing in the shift register to shift one column to the right and simultaneously causes the extreme right-hand digit to be read out. Thus, the repetition rate with which a number standing in the register is read out is determined by the repetition rate of the reset pulses 86. The number 1 1 0 1 can, therefore, be read out as 1 1 0 1 at any pulse repetition frequency desired.

If desired, a binary number can be serially read into the shift register of Figure 4 by applying the number at an input line 81 brought into the first side of the column 4 flip-flop 24. This input line is connected to the flip-flop as line 30 is connected to flip-flop 21 in Figure 1, for example. The process of reading in is to apply the first column binary number information via line 81 to act upon flip-flop 24, and then to shift the information to the right in the register with a reset pulse 86. This process is repeated until the binary number has been read into the register. Obviously in this arrangement, a shift register constructed as shown in Figure 4 may have as many columns as are necessary to accept the incoming binary number. A shift register employed in this manner has utility in a system to be described below. The reading out of binary-form information so stored in the shift register is exactly the same as described above.

The function of the shift gates 46, 47, 48 and 49 and the carry gates 36, 37 and 38 now becomes apparent. Referring again to Figure 1, it will be noted that the output lines 31, 32 and 33 are each connected in parallel to an input to both adjacent flip-flops. The carry gates 36, 37 and 38 are opened when it is desired to carry the output from a flip-flop of one column to the next higher column flip-flop, that is, when a binary number is being weighted and information is being put into the register to generate an indicator. The shift gates 46, 47, 48 and 49 are opened when a number is being read out of the register. Therefore, the count control pulse generator 39 provides its pulse 40 to open the carry gates 36, 37 and 38 in synchronism with the pulses 17 of the binary number which is being weighted, and the shift read-out control 60 pulse generator 51 provides its pulses 93 to open the shift gates 46, 47, 48 and 49 simultaneously with the reset pulses 86 of the reset pulse generator 20. In this manner the two functions of the register of Figure 1 are maintained separate and distinct.

When a binary number is treated in the foregoing apparatus, the four-column binary number that is generated in the register may be termed an "indicator" for the reason that it has a characteristic value which depends upon the original binary number. Since the indicator is generated by a method of weighted count, that is, a method wherein each column of the original binary number is weighted in accordance with a prescribed scheme prior to being counted, the indicator may also be termed the "weighted count of the binary number."

For the purpose of monitoring or supervising the

identity of a binary number in any system, the weighted count or indicator is preferably generated immediately upon the creation of the binary number itself, and thereafter carried with it throughout the complete computer system. For example, a binary number and its count are illustrated in Figure 5, where a fifteen-column binary number and its weighted count are shown. On line A-A of Figure 5 there is illustrated, starting at the left-hand end, a fifteen-column binary number comprising pulses 17, each of which represents the digit 1, and empty pulse 10 spaces 98, each of which represents a zero. The fifteencolumn binary number shown on line A-A thus represents the binary number 1 0 0 1 1 0 1 1 0 1 0 1 1 0 1 which is shown on line B-B. Following the number to the right, there is a single space 96 which is reserved for 15 the algebraic sign of the number, as is desirable when the number represents a mathematical quantity. In the present example, the absence of a pulse in the space 96 is representative of a (+) sign, and the presence of a plus in that space is representative of a (-) sign. In the example shown in Figure 5, the sign of the fifteen-column binary number is (+) as shown on line B-B, since there is no pulse present in space 96 in line A-A. Further to the right beyond the sign space 96 are the pulses of the weighted count, which constitute a four-column binary number. The weighted count in the present example is the binary number 0 0 1 0 where the digit 1 is represented by a single pulse 97 in the second column, the rest of the pulse columns being blank. The weighted count shown in Figure 5 was generated by weighting columns 30 of the binary number, starting at the right-hand end, in accordance with the arrangement set forth above. However, column 96, reserved for the algebraic sign, is, in this example, included with the number so that actually 16 columns were weighted. The reason for this is that 35 for mathematical purposes it is desirable to know not only when a pulse has been lost or gained in the number itself, but whether or not the algebraic sign is correct. Weighting the binary number and its sign in Figure 5 in accordance with the weights 1 2 4 1 2 4 1 2 4 etc., from 40 right to left, would yield a weight of 17, which is binary number 0 0 0 1. However, since the number zero is the same in both the binary and decimal systems, that is, the same for base 2 and base 10, binary number 1 is added to the weighted count 17 in order that the binary number 45 and its count may never both simultaneously be zero. Thus, the weighted count shown in Figure 5 is 18, or binary number 0 0 1 0, instead of 17, as would be expected. Binary number 1 is added in Figure 1 by means of the add 1 pulse generator 25 which is operated to add 1 50 pulse through the column 1 flip-flop 21 at the end of the generation of a weighted count or indicator. In this manner, if a pulse is lost or gained in any binary number or its weighted count, the fact can be detected by apparatus to be described below.

As has been set forth, it is preferable, once a binary number and its sign appear in a system, immediately to generate an indicator which is here a weighted count in the form of a four-column binary number, and to carry the indicator at all times with the original binary number and its sign. The arrangement shown in Figure 5 which includes the number, its sign, and its weighted count in one group of pulses, is termed "one word." One word for a fifteen-column binary number, its sign, and a fourcolumn indicator includes 20 columns. In a conservative system, each pulse space may be ten microseconds wide and each pulse, when it occurs, one microsecond wide within that space. This provides ample separation between pulses and ample opportunity to detect the absence of a pulse indicating a zero in a particular column. A 70 twenty-column word, as shown in Figure 5, is, with this column interval, 200 microseconds long, or one fivethousandths of a second. With such rapidity of operation, it should be obvious that a means of checking the identity of a number and its sign each time they are handled is 75 There now stands in the shift register 110 the original

12

of extreme value, if the speed with which they can be handled is to be enjoyed. It is possible to employ the present checking system with its characteristic indicators in various systems, including all forms of pulse telemetering and pulse-type calculating systems.

Referring now to Figure 6, the apparatus there shown supervises the identity of a binary number which has been converted to a word of the kind shown in Figure 5. In systems which employ binary notation, particularly, for example, calculating machines, the entire word may be stored for a period of time in a memory system (not shown). Examples of such memory systems are mercury delay lines and recirculating circuits for short-term storage, or magnetic tapes which are moved mechanically for long-term storage. Whenever it is desired to inject a particular bit of information into a calculation or a presentation of information, the binary number or binary pulse series which represents the information is extracted from the memory. The apparatus shown in Figure 6 accepts the word, which includes the binary number information, separates the number and its sign from the indicator, stores the original indicator in a register similar to that shown in Figure 1, generates from the number and its sign a new indicator in a weighted count indicator generator similar to that shown in Figure 1, and then compares the original indicator with the newly generated indicator to determine whether or not the binary number that has been extracted from the memory is the same as the binary number which was furnished to the memory.

The apparatus of Figure 6 includes a gate 101 into which is introduced the word which is being transferred from memory. A synchronizing or "clock" pulse 102, which is a pulse furnished by any suitable central control pulse generator for the purpose of initiating the operation of the apparatus, is applied at an input terminal 103, which is connected in parallel to a delay line 104 and a gate control pulse generator 105. The gate control pulse generator has two output lines 106 and 107 in the first of which it provides a control pulse 108 and in the second of which it provides a control pulse 109, when it is triggered by the clock pulse 102. The gate control pulse generator 105 will be of any suitable form, for example, a multivibrator, which produces the pulses 108 and 109 with a separation of substantially four columns of the word, as shown on line C-C in Figure 5. The clock pulse is furnished also to the word input gate 101 through the delay line 104 and opens the gate to call the word out of the memory at about the same time that the first gate control pulse 108 is generated by the gate control pulse generator 105. The control pulse 108 goes to a count gate 111, via line 106, for the purpose of opening that gate. The indicator, which is the four-column binary number having the pulses of the weighted count, appears first; that is, the word appears to be coming out of the memory with the extreme right-hand column in Figure 5 appearing first.

The first four columns of the word occur when the count gate 111 is open and are presented to a four-column register 110 like that of Figure 4, comprising flip-flops 121 to 124, inclusive, and delay lines 137 to 139, inclusive, corresponding to flip-flops 21 to 24, respectively, and delay lines 42 to 44, respectively, in Figure 4, via an input line 113 to the column 4 flip-flop 124 which corresponds to the input line 81 of Figure 4. All four flipflops in the shift register 110 are previously cleared to stand at zero by a reset pulse 129 from a reset pulse generator 120, similar to the reset pulse generator 20 of Figure 1. The reset pulse generator 120 is set into operation by the clock pulse 102 via line 112 and generates sufficient reset pulses 129 to clear the shift register and read in the weighted count of the word. Since there is no need for the separation of two functions as in Figure 1, shift register 110 is not provided with shift gates.

weighted count 0 0 1 0 of the word (Figure 5) being transferred.

Between the fourth and fifth pulse spaces of the word being transferred, the gate control pulse generator 105 provides the second control pulse 109 in line 107 which opens a number gate 126, which gate remains open for the rest of the word, namely, for 16 pulse spaces, or, in the particular example set forth above, for 160 microseconds. Accordingly, the sign and the entire fifteencolumn binary number are furnished to a binary number input 127 similar to the binary number input 10 of Figure 1. This may be any suitable arrangement for providing the binary number pulses with proper polarity or shape and, if not needed, may be omitted. In any event, the number and its sign are provided to a weighted count or indicator generator 128 which incorporates all the features of the circuit shown in Figure 1, including a similar four-column register wherein a new weighted count or indicator is generated and stored. If the binary number and its sign have not been altered in the handling or in the memory, the weighted count which is generated in the generator 128 and the original weighted count which is stored in the shift register 110 are identical.

The original count and the newly generated count are read out simultaneously through lines 131 and 132, respectively, into a coincidence circuit 133 under the control of the reset pulse generator 120. The reset pulse generator is again actuated by any suitable means (not shown), and provides the reset pulses 129, which are furnished simultaneously to the shift register 110 and the register of the new indicator generator 128, containing the original and newly generated weighted counts, respectively. In the same manner as described above, the pulses of the two weighted counts appear in the serial read-out lines 131 and 132, respectively. Corresponding pulses of each weighted count appear simultaneously at the coincidence circuit 133, which has the function of detecting when the simultaneously presented pairs of pulses or pulse spaces are alike and when they are different from each other. Should the two weighted counts be identical, that is, should their corresponding pairs of pulses or pulse spaces be the same, the system which the invention is supervising is permitted to proceed. On the other hand, should the pulses or pulse spaces of any corresponding pair in the two weighted counts differ, that is, if one pulse space has no pulse in one weighted count and the corresponding pulse space has a pulse in the other weighted count, an error signal will appear in output line 135, which signal may be employed to stop the supervised system, give an alarm, or indicate where in 50 the supervised system the fault lies, as desired.

Figure 7 illustrates a suitable coincidence circuit 133 for use in the apparatus of Figure 6. One of the input lines, for example 132, is brought to a cathode follower 141 which accepts a weighted count negative pulse 97 via a capacitor 142 at its input and provides a pulse 140 of the same polarity across the output resistor 143 thereof. The cathode follower is provided for isolating purposes only, and being a well-known device is not further The negative pulse 140 is carried via a described. coupling capacitor 144 to a gate 116 of the kind shown in Figure 15, including in series a resistor 145, and a rectifying device 146 poled to conduct negative pulses to ground at 147. The rectifying device 146 and other similar rectifying devices in this circuit may again be any suitable unidirectional conductor, for example, a diode electron tube device or a crystal, and these devices will be hereafter referred to by the term "rectifier." positive pulse 150, which will be termed a "cock pulse" is introduced at a first clock pulse input terminal 151, which is connected via a coupling capacitor 152, a resistor 153, resistor 145, and a rectifier 154 in series to ground at 155. Rectifier 154 is poled to maintain the negative pulse 140 purely negative with relation to ground. At

14

negative pulse 140 and the positive clock pulse 150 are in voltage opposition and tend to cancel each ohter when they occur simultaneously. The resistors 145 and 153 are preferably of the same value, in the neighborhood of 500 ohms. A rectifier 157 is connected from the junction of coupling capacitor 152 and resistor 153 to ground at 158, and poled to maintain the positive pulse 150 purely positive with relation to ground.

The junction point 156 is connected via a coupling capacitor 160 to the control grid 161 of an electronic relay 162 which includes an electron tube 163. The cathode 164 of this electron tube is connected to ground at 165 and through a biasing resistor 166 and a voltage dropping resistor 167 in series to a source of potential B- which is negative with respect to ground. The control grid is connected via a current limiting resistor 168 to the junction of the biasing resistor 166 and the voltage dropping resistor 167, and is normally maintained at a potential which is negative with respect to that of the cathode 164 by an amount equal to the voltage drop in the biasing resistor 166. The anode 170 of the electron tube 163 is provided with voltage which is positive with respect to ground from a source B+ thereof via a load resistor 171 and the primary 172 of a transformer 173. The screen grid 174 of the tube 163 is provided with suitable potential from B+ via resistor 171 and an additional dropping resistor 175 in series, and is coupled to ground at 165 by a capacitor 176 which acts as a bypass capacitor in the usual manner. An additional bypass capacitor 178 is connected from the junction of resistors 171 and 175 to ground at 179. A rectifier 180 is connected across the primary winding 172, poled to conduct positive pulses from the anode side to the resistor side thereof. The bias on the control grid of the electron tube 163 is such that the tube is normally cut off or substantially so, so that a positive pulse applied to the control grid 161 causes an increase in current through the tube, and, therefore, a corresponding current surge in the primary winding 172. A negative pulse 181 is produced at the anode 170, since the lower end of the primary winding becomes negative with respect to the upper end thereof. Any positive pulse, that is, a pulse of the opposite polarity, which tends to develop in the primary winding 172 when the electron tube 163 is again returned toward cutoff, is substantialy short-circuited by the shunt connected rectifier 180.

It will be recalled that the weighted count consists of a series of four pulse spaces, each of which may be blank or may contain a negative pulse 97. Clock pulses 150 are provided to the coincidence circuit by any suitable pulse generator with regularity, one for each pulse space of the weighted count and simultaneously with the pulses 97 should the latter exist. Thus, if a pulse 97 exists in the weighted count which is introduced on input line 132, it substantially cancels out the concomitant clock pulse 150, and there is no negative pulse 181 provided at the anode 170 of the relay 162. On the other hand, should a pulse space of the weighted count be vacant, the clock pulse 150 which is furnished during that pulse space is not cancelled, and is provided to the control grid 161 of the relay tube 163, thereby causing the negative pulse 181 to occur at the anode 170.

The secondary winding of the transformer 173 is made up of two parts 183 and 184 serially joined together 65 and connected at their junction point to ground at 185. Accordingly, in response to the surge of current which produced pulse 181 in the primary winding 172, there appears at the free end of secondary section 183 a pulse 186 which is negative with respect to ground, and at the free end of secondary section 184 a pulse 187 which is positive with respect to ground. A path for the positive secondary pulse 187 to ground is provided via a coupling capacitor 191, a resistor 192, a rectifier 193 and a second resistor 194 in series to ground at 195. The rectifier the junction point 156 between resistors 145 and 153, the 75 193 is suitably poled to pass the positive secondary pulse

187 to ground in this circuit. An additional rectifier 196 is connected from the junction of the coupling capacitor 191 and resistor 192 to ground at 197 and suitably poled to remove from this circuit any voltage which may appear which is negative with respect to ground. As a result, the positive pulse 187 which appears in the series circuit of resistor 192, rectifier 193 and resistor 194 is wholly positive with respect to ground. A path for the negative secondary pulse 186 is provided to ground at 201 via a resistor 202. A rectifier 203 is connected at one side to the junction of resistor 202 and secondary section 183, and to the other side to a point 204 by way of which a connection is made to further circuit elements to be described below. Rectifier 203 is poled to conduct the negative pulse 186 to point 204.

The other weighted count input line 131 is connected to a second electronic relay 205 which includes an electron tube 206. The negative pulses 97 of the weighted count which is brought in via line 131 are applied to the control grid 207 of the electron tube 206 via a coupling capacitor 208. The anode 209 of the electron tube 206 is provided with anode potential from a source B+ thereof via a resistor 211 and the primary winding 212 of a transformer 213 in series. A rectifier 214 is connected in shunt with the primary winding 212, being poled to conduct a negative pulse from the anode end to the resistor end thereof. The cathode 215 of the tube 206 is connected directly to ground at 216 and to a source, B-, of potential which is negative with respect to ground via a biasing resistor 217 and a voltage dropping resistor 218 in series. The control grid 207 is connected to the junction of these two resistors via a current-limiting resistor 219. The screen grid 221 is provided with suitable potential from the B+ source via the anode resistor 211 and an additional dropping resistor 222 in series, and is bypassed to ground at 216 via a bypass capacitor 223. An additional bypass capacitor 224 is connected from the junction of the resistors 211 and 222 to ground at 225. The circuit of relay 205 will be recognized as similar in many respects to the circuit of relay 162. However, the bias resistor 217 of relay 205 is substantially smaller than the bias resistor 166 of relay 162 with the result that the electron tube 206 is normally in a conductive state. Thus, when a negative pulse 97 is applied to the control grid 207, the tube 206 becomes less conductive and a positive pulse 226 appears at the anode 209, since the lower or anode end of the primary winding 212 becomes positive with respect to the upper or B+ end thereof.

The secondary winding of transformer 213 consists of 50 two sections 228 and 229 serially connected with their junction point grounded at 230. The secondary sections are so poled that a pulse 231 which is negative with respect to ground appears at the free end of section 228, and a pulse 232 which is positive with respect to ground 55 appears at the free end of section 229. The free end of section 229 is connected to the junction point 233 of rectifier 193 and resistor 194 of the circuit of the positive pulse 187 which is provided by relay 162. By way of this connection, the positive pulse 232 is able to bias the 60 rectifier 193 to a nonconductive state as far as positive pulse 187 is concerned. As a consequence, when the positive pulse 232 exists simultaneously with a positive pulse 187, positive pulse 187 proceeds along line 235 instead of being conducted to ground at 195.

The negative pulse 231 is connected to point 204 via a rectifier 236 which is suitably poled to conduct negative pulses to said point. It will be recalled that negative pulse 186 is also provided to point 204 via rectifying device 203.

The clock pulse 150 is provided also to a second clock pulse input terminal 238, which is connected by way of a coupling capacitor 241, resistors 242 and 243, and a rectifier 244, in series, to ground at 245. The junction 16

point 204, and this point is connected via a resistor 246 to ground at 247. The rectifier 244 is suitably poled to conduct positive pulses like the clock pulse 150 to ground at 245. Another rectifier 248 is connected from the junction 250 of resistors 242 and 243 to ground at 251, and is suitably poled to conduct negative pulses to ground. Still another rectifier 252 is connected from the junction of capacitor 241 and resistor 242 to ground at 253 and is suitably poled to conduct negative pulses to ground. This 10 arrangement will be recognized as similar in many respects to gate 116, with inputs at point 204 and terminal 238, and an output at junction 250. A negative pulse 186 or 231 flows through resistor 243 to ground at 251 via rectifier 248, while the clock pulse 150 flows through 15 resistors 242 and 243 to ground at 245 via rectifier 244. Thus, at junction point 250 either one of negative pulses 186 or 231 can be in opposition to the positive clock pulse 150. In this respect, junction point 250 and junction point 156 are similar.

Output line 235 is connected via a coupling capacitor 255 to the first control grid 256 of a double triode type electron tube 257. A resistor 258 is connected between the first control grid and ground at 259. Junction point 250 is connected via a coupling capacitor 260 to the second control grid 261 of the double triode 257, and a resistor 262 is connected from said second control grid to ground at 263. The two anodes 264 and 265 of the tube are connected together and via an anode resistor 266 to a source, B+, of anode potential and bypassed to ground at 291 via a bypass capacitor 292. cathodes 267 and 268 of the tube 257 are connected together and via a cathode resistor 269 to ground at 270. An additional electron tube 271 including an anode 272, control grid 273 and cathode 274 has its control grid 273 connected via a coupling capacitor 275 to the junction of the cathode resistor 269 and the cathodes of the double triode tube 257. Anode potential is supplied to the tube 271 from the source B+ of anode voltage via an anode circuit resistor 276. The cathode 274 of the tube 271 is grounded at 277 and connected via a biasing resistor 278 and current limiting resistor 279 to a source, B-, of potential which is negative with respect to ground. The grid 273 is connected to the junction of resistors 278 and 279 via a current-limiting resistor 280. The output signal connection 135 is made from the anode 272 of tube 271 via an output coupling capacitor 281.

The double triode tube 257 is normally conductive and self-biasing at the cathode by virtue of the cathode resistor 269 which may be approximately 3,000 ohms. When the positive pulse 187 proceeds along line 235 to the first control grid 256, it renders one triode section of the double triode tube 257 more conductive, so that a corresponding positive pulse 283 appears in the cathode resistor 269. When the clock pulse 150 which is introduced at clock pulse input terminal 238 is not opposed by a negative pulse 186 or 231, it is impressed upon the second control grid 261 and renders the other triode section conductive, causing the positive output pulse 283 to appear. The output tube 271 is normally cut off by the bias voltage in resistor 278, and is rendered conductive by the positive output pulse 283. This results in the production of a negative output pulse 284 in the output line 135, which is the error signal.

The operation of the circuit of Figure 7 should now be readily understood. There are four conditions which the circuit is called upon to determine. These are as follows:

(1) The condition in which a vacant pulse space, representative of a zero, is presented in line 131, and a similar vacant pulse space is presented in line 132. In this condition, the clock pulse 150 introduced at terminal 151 is not opposed at point 156, and the negative and positive pulses 186 and 187 are generated, while, at the of resistor 243 and rectifier 244 is directly connected to 75 same time, the negative and positive pulses 231 and 232

are not generated. Consequently, positive pulse 232 being absent, positive pulse 187 proceeds to ground at 195. Negative pulse 186, however, opposes positive clock pulse 150 at point 250. Therefore, neither of the control grids 256 or 261 is altered in potential and no error signal pulse 284 results. This is the desired operation, for the two input lines have received similar information.

(2) The condition in which a vacant pulse space is presented to input line 131 and a negative pulse 97 is presented to input line 132. In this condition, the negative and positive pulses 186 and 187, respectively, are not generated, and the negative and positive pulses 231 and 232, respectively, are not generated. As a result, clock pulse 150 is unopposed at point 250, and proceeds to the second control grid 261 of the double triode tube 15257, providing an error signal pulse 284. This is the desired operation of the circuit, for now there is lack of coincidence between the information provided in the two input lines 131 and 132.

(3) A situation in which a negative pulse 97 is provided in line 131 and a vacant pulse space is presented in line 132. In this situation, negative and positive pulses 186 and 187 are generated and negative and positive pulses 231 and 232 are generated. Positive pulse 232 biases rectifier 193 to a nonconductive state with respect to positive pulse 187, and positive pulse 187 proceeds via line 235 and capacitor 255 to the first control grid 256 of the double triode 257, causing the generation of an error signal pulse 284 to warn of the lack of coincidence.

(4) The situation in which a negative pulse 97 is provided at each of the input lines 131 and 132. In this situation, the negative and positive pulses 186 and 187 are not generated, while the negative and positive pulses 231 and 232 are generated. Negative pulse 231 opposes positive clock pulse 150 at point 250, as a result of which no alarm pulse is generated. This is the desired operation, for now there is coincidence of the information at the two input lines 131 and 132.

It is convenient now to review the invention as far as it has been described. The fundamental basis of binary notation is that the successive digits of a binary quantity may be said to be valued or weighted from right to left with the value 2n, where n is the column number, starting at the right-hand end of the quantity. The conventional or decimal system value of the binary quantity is then the sum of the weights of all of those columns in which a "1" appears. In accordance with the present invention, a different value is obtained by weighting the columns in a different, arbitrarily chosen manner. Any weighting scheme different from the scheme that yields the conventional value may be used; in the example described herein, the apparatus was designed to employ the weights 1, 2, 4, 1, 2, 4, 1, 2, 4, etc. for the successive columns from right to left. A new number is then found which is the sum of the new weights of all columns in which the digit 1 occurs. This new number, or rather the lowest order four digits of it, is called the "weighted count" of the original number and is carried with it as an indicator 60 at all times. The "modulo 16" counter described in Figures 1-4, and more particularly in Figure 3, provides the weighted count. To prevent the number and its count from ever being both zero simultaneously, the digit "1" is added to the weighted count in the first column. Thus, a complete failure in transmission of a number and its count will be detected. In the case of a computing machine, each number stored in the memory has its weighted count stored with it (Figure 5), and the complete loss of both in storage is similarly detected. A number is 70 checked at any time, particularly during a transfer from one place to another by formulating a new weighted count and checking this for identity with the weighted count carried with the number (Figures 6 and 7).

The monitoring system of the invention is not limited 75

18

to the weighting scheme 1, 2, 4, 1, 2, 4, etc., in fact, any arbitrary weights could be assigned to the columns. For example, the columns of the binary quantity may be weighted 1, 1, 1, etc. Here the summation consists merely of adding up the number of 1's which appear in the quantity. This scheme of weighting and counting does not constitute as good a check as the 1, 2, 4 scheme described above since a loss of a "1" in a given column can be compensated for by the gain of a "1" in any other column which originally held a zero, whereas, in the 1, 2, 4 scheme, a very odd combination of circumstances is needed to render the number incorrect and at the same time render a newly generated weighted count correct. For example, suppose the binary quantity were to lose four 1's in columns 3, 6, 9 and 12. Under these extraordinary circumstances the weighted count would not change and yet the number would be incorrect. The possibility of such an occurrence is very remote, however, and, therefore, the identity check afforded by the system illustrated is of a high degree of validity.

The use of modulo addition provides an indicator which has a fixed small number of columns, and can therefore be carried with the original binary quantity with small additional cost in time and equipment. However, if desired, the weighted count might be taken without modulo, or with a modulo other than 16. In a very simple system employing modulo, the sum with the columns of the original binary quantity all weighted, "1" may be added in a modulo 2 counter. Such a counter needs only one flip-flop, in which case its indication is either "1" or "0," depending upon whether the number of 1's in the original binary quantity is odd or even, or vice versa. The accuracy of such a simple system is, however, much less than that of the system described herein.

The foregoing features of the invention provide numerous advantages of economy, reliability, speed and diagnostic ability. Economy is had because it is no longer necessary or desirable to provide two identical equipments operated simultaneously with the same number information to check the identity of the information. Reliability results from the high probability that the apparatus in accordance with the invention will unfailingly detect an error. Speed is had because the checking apparatus operates practically simultaneously with the main number handling apparatus and saves great amounts of time heretofore spent in locating faults which caused errors. The diagnostic ability of the invention is a great advantage, for it contributes to speed and reliability by locating the situs of a failure as well as informing of the failure. As a word is checked as it is transferred from location to location, an error in its composition is made immediately evident, without waiting for an entire sequence of information items to be ruined, or, in the case of a computer. for an entire problem to be incorrectly solved and therefore necessary to repeat. An error is detected at the point in a problem where it occurs, and the problem can be resumed from this point when the cause of the error is removed. In prior checking systems for digital computers, for example, the existence of a time lag between an error and its detection makes it difficult to determine the exact point in the computing routine at which failure occurred, and, consequently, increases the difficulty of resuming operation. The same fault lies with prior digital telemetering system in general. It is even possible in prior systems that intermittent errors might escape detection altogether. Particularly in the case of a computer, it is difficult and sometimes impossible to construct a test problem which completely checks the machine, that is, one which tests all storage positions and/or all control circuits.

## SUPERVISING THE ACCURACY OF MATHEMATICAL OPERATIONS

Not only is the present invention valuable for identity

monitoring, but it can also be used to supervise or check the basic arithmetic processes, by means of the weighted count. Such checks are possible because the sum (or difference, product, or quotient) of the weighted counts of two numbers has a known relation to the weighted count of the sum (or difference, product, or quotient) of the numbers themselves.

An arbitrary scheme for checking binary number additions with weighted counts is set forth as follows:

Weight each column as follows:

Column: 10 9 8 7 6 5 4 3 2 1 Weighted count: 16 8 4 2 1 16 8 4 2 1

Take the total weighted summation of the columns bearing 1's without modification (that is, without modulo) to obtain the count of a number, and express the count in the binary notation. With this scheme of weighting, the formula that is used is:

$$[|(U_c+V_c)-(U+V)_c|+31]_c=1 \ 1 \ 1 \ 1$$

Relation 1

where U arnd V are the numbers to be added,  $U_c$  is the weighted count of U, and  $V_c$  is the weighted count of V.

An example of an addition checked in accordance with this system is as follows:

Let:

Then:

$$U+V=0$$

. 1 1 0 0 0 0 1 1 0 0=780

The weighted counts are as follows:

$$\begin{array}{c} U_{\bullet} = 38 = & 1 & 0 & 0 & 1 & 1 & 0 \\ \underline{V_{\bullet}} = 29 = & 0 & 1 & 1 & 1 & 0 & 1 \\ U_{\bullet} + \overline{V_{\bullet}} = 67 = 1 & 0 & 0 & 0 & 0 & 1 & 1 \end{array}$$

The weighted count of (U+V) is:

$$(U+V)_c=36=1 0 0 1 0 0$$

Then:

$$U_c+V_c-(U+V)_c=31=1\ 1\ 1\ 1\ 1$$

Relation 2 45

Now add binary 31 to the absolute value of Relation 2:

$$|U_c+V_c-(U+V)_c|+31=62=1$$

1 1 1 1 0 Relation 3

Take the weighted count of Relation 3:

$$[U_c+V_c-(U+V)_c]+31]_c=31=1$$

1 1 1 Relation 1

Relation 1 can be shown to be true for any binary addition, and, therefore, it may be used as a check that the binary addition was performed properly.

It might seem from the foregoing that the step of adding 31 (Relation 3) is superfluous, but there is the possibility that  $U_c+V_c=(U+V)_c$ , in which case the difference in Relation 2 would be 0 instead of five 1's. This happens, for example, when U or V is 32, for which the binary number is 1 0 0 0 0 and the count is 1, as shown in the following example where U=32 and V is arbitrarily chosen as 91:

Then:

$$\begin{array}{c} U_{\circ} = 1 = 0 \ 0 \ 0 \ 0 \ 1 \\ \underline{V_{\circ}} = 29 = \underbrace{1 \ 1 \ 1 \ 0 \ 1}_{1 \ 1 \ 1 \ 1 \ 0} \end{array}$$

$$(U_{\circ} + \overline{V_{\circ}}) = 30 = \underbrace{1 \ 1 \ 1 \ 1 \ 0}_{1 \ 1 \ 1 \ 1 \ 0}$$

And:

$$(U+V)_0=30=1\ 1\ 1\ 1\ 0$$

So that:

$$(U_c+V_c)-(U+V)_c=0\ 0\ 0\ 0\ 0$$

In accordance with Relation 1, add 31:

$$|(U_c+V_c)-(U+V)_c|+31=1$$

1 1 1 1

10 Whence:

$$[|(U_c+V_c)-(U+V)_c|+31]_c=1 \ 1 \ 1 \ 1$$

This scheme guarantees that the check will always be a series of five 1's in succession if the addition was performed correctly.

Multiplication is checked in accordance with formula:

$$[|(U_c \cdot V_c)_c - (U \cdot V)_c| + 311_c = 31 = 1 \ 1 \ 1 \ 1$$

Division is checked by the formula:

Relation 4

$$[|(U_c \cdot Q_c)_c + R_c - V_c| + 31]_c = 31 = 1 \ 1 \ 1 \ 1$$

Relation 5

Where:

U=divisor

25 V=dividend

Q=quotient, and

R=complete remainder

Subtraction is commonly performed as a special form of addition, employing, however, the following variation 30 of Relation 1:

$$[U_c-V_c-(U-V)_c]+31]_c=1 \ 1 \ 1 \ 1$$

Referring now to Figure 8, the system there shown checks the accuracy of an arithmetic operation in ac-35 cordance with the foregoing considerations. The operands, U and V, are introduced by way of input line 301 and an operand input gate 302. The gate is controlled by a clock pulse 303, which is introduced by way of a terminal 304 and a suitable line 305. The gate is of a 40 type which is normally closed and, when triggered open, remains open for a suitable period of time to pass both U and V to a main arithmetic unit 306 and to a weighting circuit 307. The main arithmetic unit 396 is a component of the computing system and performs the desired operation upon U and V. Assuming that the desired operation is one of addition, the sum (U+V) is furnished by the main arithmetic unit to a result delay circuit 308, the purpose of which will be explained below, and to a result line 309, which may be connected via a switch 311 to the input of the weighting circuit 307. The weighting circuit 307 is similar in many respects to that of Figure 1, and will be described more fully below. The switch 311 has an input blade 312 and an output blade 313 ganged together, of which the former, in one position, admits U and V individually to the weighting circuit from the operand input gate 302, and in the other position admits the result (U+V) to the input of the weighting circuit 307 from line 309. The output blade 313, in said one position, furnishes Uc and Vc individually to a check arithmetic unit 315 by way of a suitable line 316, and, in the other position, furnishes (U+V)<sub>c</sub> to the check arithmetic unit by way of a second suitable line 317. The switch 311 is symbolic of any suitable gate circuit arrangement. An alter-65 native arrangement is described below in connection with Figure 8A.

The check arithmetic unit 315 performs the simple mathematical operation set forth in Relation 1. The step of adding binary 31 is accomplished by furnishing 70 the proper pulse sequence to the check arithmetic unit from a binary 31 pulse generator 318. The binary 31 pulse generator is a circuit which, when set into operation, furnishes five pulses of the proper polarity, proper pulse repetition frequency, and proper interpulse spacing 75 for use in the check arithmetic unit 315. The binary 31

pulse generator 318 is triggered into operation by the clock pulse 303 which is furnished thereto through a suitable delay line 319 and thence via a suitable connection line 321 from the delay line to the pulse generator. Preferably the delay line 319 sufficiently delays the clock pulse 303 so that the operands U and V can be weighted in the weighting circuit 307, and operated upon in the main arithmetic unit 306, and the weighted counts of the operands and their sum furnished to the check arithmetic unit 315 prior to the binary number 31 pulses 10 being introduced into the check arithmetic unit.