(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5208011号

(P5208011)

(45) 発行日 平成25年6月12日(2013.6.12)

(24) 登録日 平成25年3月1日(2013.3.1)

(51) Int.Cl.

F 1

|              |           |              |      |

|--------------|-----------|--------------|------|

| G 11 C 16/02 | (2006.01) | G 11 C 17/00 | 601Q |

| G 11 C 16/06 | (2006.01) | G 11 C 17/00 | 611G |

| G 11 C 17/14 | (2006.01) | G 11 C 17/00 | 631  |

|              |           | G 11 C 17/00 | 633A |

|              |           | G 11 C 17/00 | 634A |

請求項の数 11 (全 14 頁) 最終頁に続く

|           |                               |

|-----------|-------------------------------|

| (21) 出願番号 | 特願2009-31380 (P2009-31380)    |

| (22) 出願日  | 平成21年2月13日 (2009.2.13)        |

| (65) 公開番号 | 特開2010-186525 (P2010-186525A) |

| (43) 公開日  | 平成22年8月26日 (2010.8.26)        |

| 審査請求日     | 平成23年12月5日 (2011.12.5)        |

|           |                                                 |

|-----------|-------------------------------------------------|

| (73) 特許権者 | 000002325<br>セイコーインスツル株式会社<br>千葉県千葉市美浜区中瀬1丁目8番地 |

| (74) 代理人  | 100154863<br>弁理士 久原 健太郎                         |

| (74) 代理人  | 100142837<br>弁理士 内野 則彰                          |

| (74) 代理人  | 100123685<br>弁理士 木村 信行                          |

| (72) 発明者  | 津村 和宏<br>千葉県千葉市美浜区中瀬1丁目8番地 セイコーインスツル株式会社内       |

審査官 園田 康弘

最終頁に続く

(54) 【発明の名称】メモリ回路装置

## (57) 【特許請求の範囲】

## 【請求項 1】

メモリセル A が行列状に配置され、行と列を選択することで所望のメモリセル A を選択して情報を書き込むメモリ回路装置であって、

各列を構成する前記メモリセル A の書きが完了しているか完了していないかの書き情報情報を記憶するために前記各列に備えられたメモリセル B と、

前記メモリセル B の前記書き情報を利用して列の選択を行う回路と、

を備え、

選択されている第 1 の列の前記メモリセル A への書きが完了した後に前記第 1 の列に備えられた前記メモリセル B に書き完了を示す着込情報の書きを行うと、前記回路がこの書きによって生じる前記メモリセル B の出力電圧の変化を前記第 1 の列および次列となる第 2 の列へ直接伝えることで、前記第 1 の列は選択状態から否選択状態に変わり、前記第 2 の列は否選択状態から選択状態に変わるので前記第 2 の列への書きが可能になり、本動作を繰り返すことで、書きを行う列が順次選択されていくことを特徴とするメモリ回路装置。

## 【請求項 2】

前記メモリセル B を利用した誤書き防止機能をさらに備えていることを特徴とする請求項 1 記載のメモリ回路装置。

## 【請求項 3】

前記メモリセル B が隣接する列の異なる行にわたって配置されていることを特徴とする

10

20

請求項 1 または 2 に記載のメモリ回路装置。

**【請求項 4】**

前記メモリセル B の記憶する書き込み情報の変化と、列選択信号の変化との間に遅延時間を持たせたことを特徴とする請求項 1 乃至 3 のいずれか 1 項に記載のメモリ回路装置。

**【請求項 5】**

アナログ・デジタル変換回路から構成される行デコーダをさらに有することを特徴とする請求項 1 乃至 4 のいずれか 1 項に記載のメモリ回路装置。

**【請求項 6】**

前記アナログ・デジタル変換回路から成る行デコーダからの出力であるワード線にプルアップ、もしくはプルダウン機能をさらに備えることを特徴とする請求項 5 記載のメモリ回路装置。 10

**【請求項 7】**

前記アナログ・デジタル変換回路に流れる電流を遮断する機能をさらに備えることを特徴とする請求項 5 または 6 に記載のメモリ回路装置。

**【請求項 8】**

前記メモリセル A および前記メモリセル B からの情報をラッチ回路に読み出して情報を保持する機能と、前記メモリセル A および前記メモリセル B に流れる電流を遮断する機能とをさらに備えることを特徴とする請求項 1 乃至 7 のいずれか 1 項に記載のメモリ回路装置。 20

**【請求項 9】**

行列配置された前記メモリセル A の第 1 列の前にさらにメモリセル C を備え、前記メモリセル C の記憶情報によって、前記第 1 列目の前記メモリセル A への書き込みの可否を制御することを特徴とする請求項 1 乃至 8 のいずれか 1 項に記載のメモリ回路装置。

**【請求項 10】**

情報を記憶する素子として電気的に溶断可能なヒューズを用いることを特徴とする請求項 1 乃至 9 のいずれか 1 項に記載のメモリ回路装置。

**【請求項 11】**

参照電位を有する半導体チップ上に設けられた、前記半導体チップの参照電位と前記アナログ・デジタル変換回路の参照電位とを共通化したことを特徴とする請求項 5 乃至 7 のいずれか 1 項に記載のメモリ回路装置。 30

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

本発明はメモリ回路装置へのデータの書き込み方法及び、誤書き込み防止方法に関する。

**【背景技術】**

**【0002】**

アナログ量を扱う I C では、そのアナログ量の調整のためにトリミングを行っているものが多い。このトリミングの方法にはいくつかの種類が存在する。代表的なものを以下に 40 3つあげて説明する。

(1) レーザーヒューズ法：ヒューズにレーザーを照射して溶断する方法

(2) 電気ヒューズ法：ヒューズに大電流を流して溶断する方法

(3) メモリ法：E P R O M のようなメモリ素子に情報を記憶させる方法

ヒューズは広義には 1 回プログラムできるメモリの 1 種と言える。しかし、通常はヒューズをメモリと呼ばないことから、ここではメモリとして扱わない。E P R O M には浮遊ゲートに F N トンネル電流やホットキャリアを用いてキャリアを注入することでトランジスタの V t h を変化させるものが広く使われている。

**【0003】**

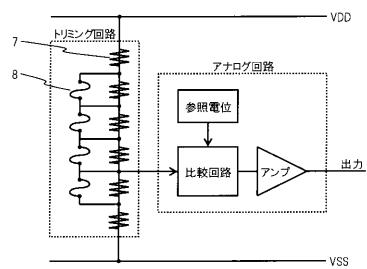

トリミングには様々なものが存在するが、分かり易くするために、図 2 を用いて説明す 50

る。図2で示す回路はボルテージディテクターと呼ばれるもので、電源電圧がある値より高いか低いかによって出力が反転するものである。用途としては電源電圧の監視に広く用いられている。

#### 【0004】

動作について概略を説明する。電源VDDとグランドVSSとの間に抵抗体7を配置して、VSSを基準にして電源VDDの電位を電位分割する。この電位分割された電位と参照電位を比較回路で比較すると、参照電位より高いか低いかによって出力レベルが反転する。これをアンプで整形して出力している。

#### 【0005】

何ボルトで反転するかは抵抗による分割比で変えることができる。また実際の製品では10

製造バラツキのために参照電位の値がばらつく。そのバラツキを抵抗の分割比を調整することで打ち消すことが出来る。よって分割比を任意の値に調整することが出来れば、所望の電圧で出力の反転するボルテージディテクターが得られる。

#### 【0006】

ヒューズ8と抵抗体7とを並列に並べ、ヒューズが溶断されている抵抗体は抵抗として働き、ヒューズが溶断されていない抵抗体はヒューズによって短絡するために抵抗として働かない、ということで分割比の調整を実現している。これを一般にトリミングと呼ぶ。トリミングの説明にボルテージディテクターを用いた理由は最も簡単にトリミングの説明が出来るからであって、この回路に限定するものではない。

#### 【0007】

レーザーヒューズ法は所望のヒューズにレーザーを照射することでヒューズを溶断することで、所望のトリミングを行うものである。この方式のメリットはどのヒューズを切るか選択するための回路、及び外部端子が必要ないことである。トリミングはパッケージ状態だとヒューズにレーザーを照射できないので、チップをパッケージに組む前に行われる。

#### 【0008】

この方式の課題はパッケージ状態でトリミングできないということである。アナログ量はパッケージ工程及びボードへ取り付ける際のリフロー工程にて変動する。よってトリミングはリフロー工程後の実施が望ましいが、パッケージ状態ではレーザーを照射出来ないため、それが出来ない。そのために最終的に必要な特性の規格範囲よりも、その変動分を見越して、より狭い規格範囲を採用する場合が多い。このために歩留まりの低下、高精度にするための回路追加によるチップ面積増大等の問題が生じている。また、製品の購入者自身がトリミングを行う必要がある製品に対しても適用できないという課題がある。

#### 【0009】

次に電気ヒューズ法について説明する。電気ヒューズ法は所望のヒューズに大電流を流すことで、発熱させ、その熱によって所望のヒューズを溶断させることで、所望のトリミングを行うというものである。これは電気的なトリミングであるため、パッケージ状態でのトリミングが可能であり、前記課題は回避できる。

#### 【0010】

この方式は、ヒューズを電気的に溶断するための大電流をヒューズに流す必要があるので、各ヒューズに外部端子を設ける場合が多い。外部端子はPadと呼ばれ、通常100um x 100um程度の大きさをもつ。そのためレーザーヒューズ法に較べて非常に大きな面積を必要とする。

#### 【0011】

また、パッケージ状態でのトリミングを行うには、Padをパッケージの足に接続する必要があるので、パッケージの足が非常に多くなる。このPadの多さを解決する手段が特許文献1に示されている。この方法の場合、必要なPad数は2つに減少するので大幅な面積削減効果が得られる。

#### 【0012】

しかしながら、シリアルデータをパラレルデータに変換する直並列変換回路が必要であ

10

20

30

40

50

ること、直並列変換回路に情報を入力するためのPadが2つ必要であること、大電流を流せるトランジスタが必要であることから、レーザーヒューズ法と比較すると、まだまだ面積が大きいという課題がある。

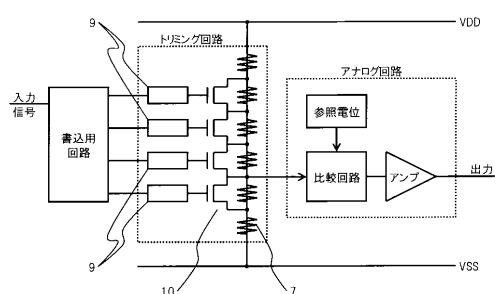

#### 【0013】

次にメモリ法について説明する。メモリ法はヒューズの替わりにメモリ素子を用いたもので、図3に示すように、抵抗体7と並列にトランジスタ10を配置し、このトランジスタのゲート電位をメモリセル9で制御することにより、トランジスタがOFFしている場合は抵抗体が抵抗として働き、トランジスタがONしている場合はONトランジスタによって短絡する、ということでトリミングを行う方法が一般的に用いられている。

#### 【0014】

E PROMのような不揮発性のメモリ素子は電源を切っても記憶情報が保持されるので、このようなトリミングに用いるのに都合がよい。

#### 【0015】

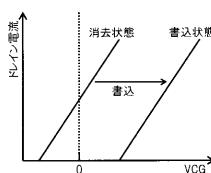

メモリセル9は図4に示す構成となっている。これはNchの浮遊ゲート構造のトランジスタからなるメモリ素子12を用いている。一般に書き込みは浮遊ゲートに電子を注入することで行われる。浮遊ゲートに電子が注入されるとNchのチャネルが形成されづらくなるのでVthが増加する。このメモリ素子12のコントロールゲート電圧VCG - ドライン電流の関係を図5に示す。このように、書き込みによってVthが増大することを利用して情報を記憶している。

#### 【0016】

トリミングはメモリ素子への書き込みで行われるので、メモリ素子を選択するための回路、及び外部端子が必要となる。

#### 【0017】

メモリ法の場合もパッケージ工程後にトリミング出来るというメリットがあるが、トリミングするメモリ素子を選択するための直並列変換回路、選択するための信号を入力するPadが必要であることは、電気ヒューズ法の特許文献1と同じである。違いは、大電流を必要としないため、大電流を流すためのトランジスタの分だけ、面積を縮小することができることである。しかしながら、これも電気ヒューズ法に較べれば小さくできるというだけで、レーザーヒューズ法と比較するとまだまだ面積が大きいこと、これらのメモリ素子は実用的には誤書き込み防止機能が必要で、そのための回路が必要になるという課題がある。

#### 【0018】

特許文献2にこれら課題の解決を試みる手法が示されているが、レーザーヒューズ法と比較すると少なくとも2個のPadが必要であること、レーザーヒューズ法では不要な回路が必要であることからチップの面積増大は避けられない。

#### 【先行技術文献】

#### 【特許文献】

#### 【0019】

【特許文献1】特開平6-37254号公報

【特許文献2】特開2003-110029号公報

#### 【発明の概要】

#### 【発明が解決しようとする課題】

#### 【0020】

前述のように従来技術では、パッケージ状態でのトリミングを可能にするためにレーザーヒューズ法と比較して余分なPad及び回路（ここではこれを付加Pad、付加回路と呼ぶ）が必要であった。そのためにチップサイズが大きくなるという課題があった。本発明はこの課題を解決するべくなされたものであり、その目的はパッケージ状態でのトリミングを可能にするために必要になった付加Padの削減、付加回路の簡略化、によってチップサイズを小型化することにある。

#### 【課題を解決するための手段】

#### 【0021】

10

20

30

40

50

上記課題を解決するために本発明のメモリ回路装置では以下に述べる手段を採用する。

【0022】

メモリセルAが行列状に配置され、行と列を選択することで所望のメモリセルを選択して情報を書き込むメモリ回路装置にあって、各列のメモリセルAの書きが完了しているか完了していないかの情報を記憶するためのメモリセルBを各列に備え、メモリセルBの記憶情報を利用して列の選択を行う回路を備え、ある列のメモリセルAへの書きが完了した後に該列の書き情報を記憶するためのメモリセルBに書き完了情報の書きを行い、この書きによって該メモリセルBの記憶情報が変化することを利用して、該列は選択状態から否選択状態に変わり、次列は否選択状態から選択状態に変わることで次列への書きが可能になり、本動作を繰り返すことで、書きを行う列が順次選択されていくことを特徴とする。 10

【0023】

前記メモリ回路装置において、メモリセルBを利用した誤書き防止機能を備えていることを特徴とする。

【0024】

前記メモリ回路装置において、隣接する列のメモリセルBが異なる行に配置されていることを特徴とする。

【0025】

前記メモリ回路装置において、メモリセルBの記憶する情報の変化と、列選択信号の変化との間に遅延時間を持たせたことを特徴とする。 20

【0026】

前記メモリ回路装置において、行デコーダがアナログ・デジタル変換回路から構成されることを特徴とする。

【0027】

前記メモリ回路装置において、アナログ・デジタル変換回路から成る行デコーダからの出力であるワード線にプルアップ、もしくはプルダウン機能を備えることを特徴とする。

【0028】

前記メモリ回路装置において、アナログ・デジタル変換回路に流れる電流を遮断する機能を備えることを特徴とする。

【0029】

前記メモリ回路装置において、メモリセルからの情報をラッチ回路に読み出して情報を保持する機能と、メモリセルに流れる電流を遮断する機能とを備えることを特徴とする。 30

【0030】

前記メモリ回路装置において、行列配置されたメモリセルAの第1列の前にメモリセルCを備え、前記メモリセルCの記憶情報によって、第1列目のメモリセルAへの書きの可否を制御することを特徴とする。

【0031】

前記メモリ回路装置において、情報を記憶する素子として電気的に溶断可能なヒューズを用いることを特徴とする。

【0032】

参照電位を必要とする半導体チップにおいて、前記メモリ回路装置を備え、前記半導体チップの参照電位と、前記メモリ回路装置のアナログ・デジタル変換回路の参照電位とを共通化したことを特徴とする。 40

【発明の効果】

【0033】

以上説明した本発明によれば、付加Padの削減、付加回路の簡略化が実現でき、チップサイズの小型化が可能になる。

【図面の簡単な説明】

【0034】

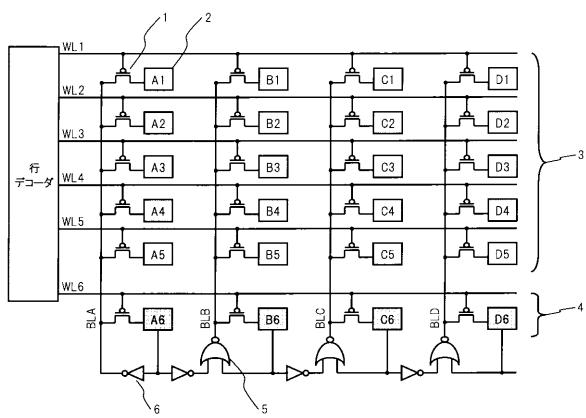

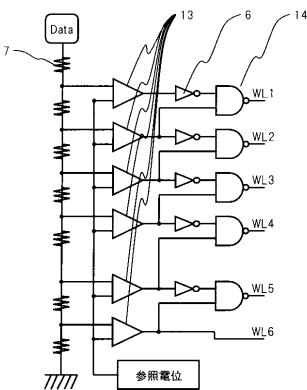

【図1】本発明実施例1のトリミングメモリ回路図

【図2】ヒューズを用いたボルテージディテクターの概略図 50

【図3】メモリ素子を用いたボルテージディテクターの概略図

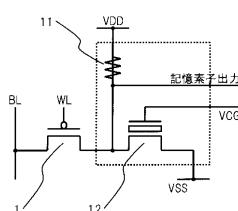

【図4】浮遊ゲート構造をもつメモリ素子から成るメモリセルの回路図

【図5】浮遊ゲート構造をもつメモリ素子のコントロールゲート電圧VCG - ドレイン電流IDの関係を示す図

【図6】従来技術にかかるメモリ回路図

【図7】D型フリップフロップ(D型ラッチと呼ぶ場合もある)の回路図

【図8】本発明実施例3のトリミングメモリ回路図

【図9】アナログ・デジタル変換を用いた行デコーダの回路図

【図10】図9のData端子入力電圧 - 出力レベルの関係を示す表

【発明を実施するための形態】

10

【0035】

【実施例1】

【0036】

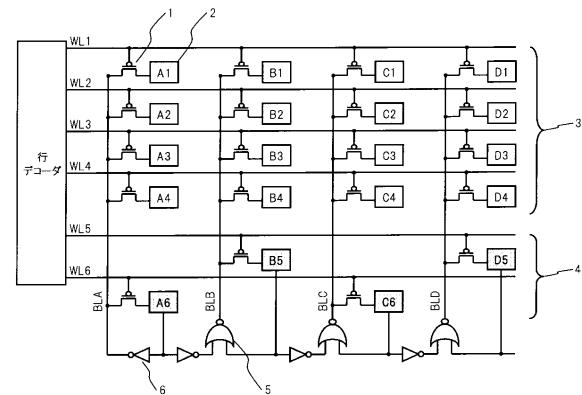

図1に従って、5行×4列 = 20ビットのトリミングメモリ回路の場合について説明する。図1は本発明の実施例1によるトリミングメモリ回路図である。

【0037】

図1の回路図にはメモリセル2が行列状に配置されている。メモリセル2は図4に示すように、メモリ素子12とPchトランジスタ1と負荷抵抗11とから成る。まず、メモリ素子12について説明する。メモリ素子12は浮遊ゲート構造を有するN型のMOSトランジスタで、浮遊ゲートに電子を蓄積することで情報を記憶するものである。浮遊ゲートへの電子の注入はFNトンネル電流やホットキャリアを利用して行うことができ、これを書きと呼ぶ。また、浮遊ゲートに蓄積した電子は紫外線を照射することで浮遊ゲートから引き抜くことができ、これを消去と呼ぶ。

20

【0038】

浮遊ゲートには容量結合によって浮遊ゲートを制御するコントロールゲートが備えられる。このコントロールゲートの電圧とドレイン電流の関係を示したグラフが図5である。書き状態においては電子が浮遊ゲートに蓄積するために、チャネルが反転しにくい。つまりVth(閾値)が消去状態に較べて大きくなる。以上は浮遊ゲート構造を有するN型のMOSトランジスタを用いたメモリ素子では一般的な動作である。

【0039】

30

図4は上記の浮遊ゲート構造をもつメモリ素子から成るメモリセルの回路図である。メモリ素子のドレインとBL(ビット線)間にPchトランジスタ1を配置し、このPchトランジスタのON/OFFで書きを制御する。メモリ素子のドレインと電源ラインVDとの間に負荷抵抗11を設ける。この抵抗はメモリ素子の書き/消去時のソース/ドレイン間抵抗の中間程度とする。すると記憶素子出力は書き状態で1(Hi)、消去状態で0(Lo)となる。

【0040】

図4記載の点線枠は、図1に示す本発明実施例1のトリミングメモリ回路図に記載のメモリセル2に相当する。図1記載のPchトランジスタ1と図4記載のPchトランジスタ1は同一のものである。

40

【0041】

以上、メモリセルの構成について述べたが、これは1例である。本発明の本筋は選択回路に関するこであって、メモリセルの構成はどのようなものであってもよい。

【0042】

図1において、横方向に伸びる配線は各行を選択するためのもので、ワード線(WL:Word Line)と呼び、各行については1行目をWL1、2行目をWL2のように呼ぶ。縦方向に伸びる配線は各列を選択するためのもので、ビット線(BL:Bit Line)と呼び、各列については1列目をBLA、2列目をBLLのように呼ぶ。各行を選択するための信号を供給する回路を行デコーダと呼ぶ。行デコーダからは行数5+1=6本のワード線が伸びている。

50

**【0043】**

WL1～5に繋がるメモリセルをトリミング用メモリセルと呼ぶことにする。WL6につながるメモリセルA6、B6、C6、D6をBL制御用メモリセルと呼ぶことにする。

**【0044】**

図1ではトリミング記憶情報の取り出しを省略しているが、図4のメモリセルの出力を図3のトランジスタ10のゲートに入力すれば抵抗分割のトリミングとして使うことが出来る。

**【0045】**

次に動作について説明する。まず、チップに紫外線を照射して、全てのメモリ素子を消去状態にする。全メモリ素子が消去状態の時、BL制御用メモリセルからの出力が0であるので、各ビット線のレベルはBLA=1、BLB=0、BLC=0、BLD=0となる。この時、ワード線で行を選択する信号を入れるとA列の該行のPMOSトランジスタだけがONして、該メモリ素子に書き込みが行われる。例えばA列では2行、3行のみに書き込みたい場合は(WL1, WL2, WL3, WL4, WL5)=(1, 0, 0, 1, 1)としてA2、A3に書きを行う。もしくは(1, 0, 1, 1, 1)と(1, 1, 0, 1, 1)の2回に分けてA2、A3に書きを行う。

10

**【0046】**

A列の書き込みが終了したら、次にWL6=0としてA6に書きを行う。するとBLA=0, BLB=1, BLC=0, BLD=0となってB列のみが書き可能な状態に切り替わる。

20

**【0047】**

ここでA列の場合と同じように(WL1, WL2, WL3, WL4, WL5)を制御してB列の書きを行う。B列の書き込みが終了したら、B6に書きを行う。すると今度はC列のみが書き可能な状態に切り替わる。このようにして限りない列数に対して順次選択することが可能になる。

**【0048】**

この説明では5行×4列=20ビットの場合について述べたが、行と列どちらもその数に制限はない。この説明で用いた、行と列は便宜的なもので、行と列が入れ替わっても本質的には同じである。この説明で述べた行列配置は回路的なものであり、チップ上のメモリ素子の配置とは無関係である。本発明の主旨は列毎に該列の書き込みが済みか未だかの情報を記憶するBL制御用メモリセルを設け、このBL制御用メモリセルの情報をを利用して列を順次選択するということにある。図1に示すNOR回路5、インバータ回路6を用いた回路はこの機能を実現する1例であり、本発明を図1に示す回路に限定するものではない。

30

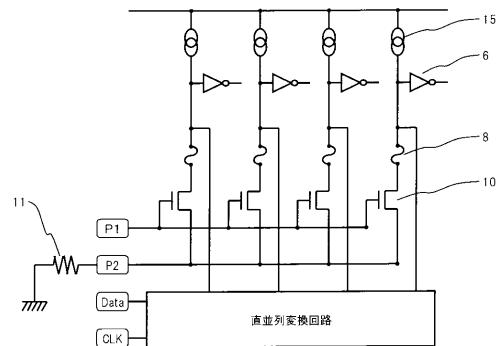

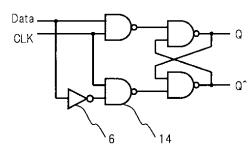

**【0049】**

図6の従来例では選択するための直並列変換回路が必要である。この従来例では電気的に溶断するヒューズが用いられているが、その選択方法はメモリ素子を用いた場合でも基本的には同じである。直並列変換回路には、図7に示すD型フリップフロップ(DFF)から成る場合が多い。これはD型ラッチとも呼ばれる。基本的にはDFFは1列に1個必要である。図7に示すようにDFFは4つのNANDと1つのインバータから成る。つまり通常トランジスタ18個から成る。1列に18個のトランジスタと比較すると本発明の列選択方式は必要なトランジスタ数が少なく、簡略化された回路になっていることが分かる。

40

**【実施例2】****【0050】**

図1のトリミングメモリ回路において、実施例1で述べたように順次列を選択しながら書きを行い、所望する全てのメモリ素子への書き込みが終了したら最終列のBL制御用メモリ素子へ書き完了情報の書きを行う。これ以降、列が一切選択できなくなるので、書き込みは不可能になる。

**【0051】**

50

メモリ素子を用いたトリミング回路においては、トリミング後に意図しない書き込みが起きることを防ぐために誤書き込み防止機能をもたせることが一般的である。特許文献2においても誤書き込み防止機能が備えられている。

#### 【0052】

本発明では、列を順次選択するために用いるBL制御用メモリ素子を用いて、各列を書き込み禁止状態にすることが可能である。最終列においては列を順次選択することが終了しているので、列選択の目的においては、BL制御用メモリ素子は不要である。しかしながら、最終列にもBL制御用メモリ素子を備え、この素子への書き込みによって、最終列を書き込み禁止状態にすれば、全メモリ素子への書き込みが禁止される。このようにして誤書き込み機能が得られる。

10

#### 【実施例3】

#### 【0053】

図8に従って、4行×4列 = 16ビットのトリミングメモリ回路の場合について説明する。行デコーダからは行数4+2=6本のワード線が伸びている。WL1~4に繋がるメモリセルがトリミング用メモリセルで、WL5、6につながるメモリセルA6、B5、C6、D5がBL制御用メモリセルとなる。実施例1を表す図1との違いはBL制御用メモリセルが同一行ではなく2行にまたがっていること、また、隣列のBL制御用メモリセルが別行にあること、つまり、交互に配置されていることである。

#### 【0054】

図8のようにBL制御用メモリセルを2行に渡って交互に配置した場合に得られる効果を説明する。図1の実施例1に示すようにBL制御用メモリセルを同一行(WL6)に配置すると、A6に書き込みが終了すると同時にB6への書き込みが開始され、B6の書き込みが終了すると同時にC6への書き込みが開始される。このためにA6への書き込みが終了するのと同時にWL6の信号を0に落とす必要がある。早くても遅くともいけない。このようなタイミングを制御することは可能であるが困難を伴う。ゆえに2行に渡っての交互配置としている。

20

#### 【0055】

2行に渡っての交互配置にした場合、A列のトリミングメモリセルへの書き込みが終了した後に、A6に書き込みを行い、A6への書き込みが終了した後もA6に書き込み電圧を印加したままにしておいても、他のセルに書き込みが行われることはない。前記のように、B列のBL制御用メモリセルに書き込みが行われることはない。よって書き込みのタイミング調整が楽になり、安定的な書き込みが出来るという効果が得られる。

30

#### 【0056】

ここで2行には意味がなく、隣列のBL制御用回路が別行にあるということに意味がある。ここでは隣列のBL制御用回路を別行にするために最も少ない2行を用いたが、2行より多くても構わない。

#### 【実施例4】

#### 【0057】

A列のトリミングメモリセルに書き込みが終了したら、次にWL6=0としてA6に書き込みを行う。するとBLA=0, BLB=1, BLC=0, BLDD=0となってA列は書き込み禁止状態に、B列は書き込み可能状態に切り替わる。C列以降は書き込み禁止状態のままで変化しない。これでも動作は問題ないのだが、この時A6の出力が切り替わると同時にA列のビット線が否選択状態になるとA6への書き込み深さが十分ではないという問題が発生する可能性がある。

40

#### 【0058】

そこでBL制御用メモリセルからの出力とビット線の信号が切り替わるタイミングの間に、いくばくかの遅延をもたせるようにする。遅延時間はBL制御用メモリセルに十分深く書き込みを行うために必要な書き込み時間程度でよい。この遅延は抵抗等を用いれば簡単に実現できる。

#### 【0059】

このようにすることで、BL制御用メモリセルに十分深く書き込みを行うことが、より安定

50

的にできるようになる。そのために書込不良やデータ化け等の不良確率も低減できる。

**【実施例 5】**

**【0060】**

行デコーダの構成について説明する。列選択回路が前述のように簡略化できたので、行デコーダは従来例でやってもチップ面積は縮小できるのだが、以下に示す手法と組み合わせることで、より大きな効果を得ることができる。

**【0061】**

図9にその行デコーダの構成を示す。行を選択する情報を入力する外部端子をData端子とする。この回路はData端子の電位によって、各WLの信号を制御するもので、一般的にアナログ／デジタル変換回路と呼ばれる回路を行デコーダに利用したものである。

10

**【0062】**

Data端子とVSS間に抵抗を配置して適切に分割された電位と参照電位とを比較して、信号を制御する。適切な分割については後で述べる。このようにアナログ量を入力信号とするメリットは、端子1個で任意の1つを選択することが可能なところにある。

**【0063】**

デジタル信号で同じことをしようとすると、少なくとも2つの外部端子が必要である。例えばクロック信号のようなシリアルデータをパラレルデータに変換する場合でも、このパラレルデータは全てを1つずつ順番に選択する信号に過ぎないので、任意の1つを選択するためには、少なくとももう1つの外部端子が必要になる。このようにアナログ量を入力信号に用いることで外部端子数を削減することが可能になる。

20

**【0064】**

しかしながら一般にはデメリットもある。上記のデジタル信号2端子の場合、選択できる数に制限がないのに対して、アナログ信号1端子の場合、アナログからデジタルへの変換する分解能によって選択できる数が制限されることである。選択できるビット数を増やすために分解能を高めると、アナログ／デジタル変換回路の規模が増大するなどして、面積縮小のメリットが得られず、メリットが無ければ、デジタルに較べてアナログは取り扱いに注意を要するので実用化されてこなかった。

**【0065】**

しかしながら、本発明の場合、WLの選択のみにアナログ信号を用いており、BL選択にはアナログ信号の制限はかかるない。のために本発明ではアナログ信号1端子のみの付加で、そのアナログ／デジタル変換回路の分解能を高くしなくても、選択できる数に制限がかからなくなる。このように前述の列選択方法を適用したトリミングメモリ回路と、図9の行デコーダ回路の組み合わせることによって初めて、ビット数の制限、或いは高分解能化を行わなくとも、選択に必要な外部端子を1つに削減できるという効果が得られるようになる。

30

**【0066】**

次に図10にData端子の電位とワード線WL1～6の信号の関係の例を示す。ここでは参照電位は1.0Vとする。参照電位は製造工程バラツキによってばらつくが、その範囲は±0.1V程度である。よって比較回路への入力が1.15V、0.85Vで切り替わるようにData端子～VSS間の抵抗比を設定する。ここで抵抗比とは、

40

抵抗比 = (各行～VSS間の抵抗) / (全抵抗)

により求められる。

**【0067】**

抵抗比を、行1:0.869、行2:0.642、行3:0.475、行4:0.351、行5:0.259、行6:0.192とすればData端子に入力する電圧が図9の左列欄の時、図9の右列欄に示すNOR回路出力、つまりWLの信号が得られる。

**【0068】**

以下、実際の動作について、例を挙げて説明する。例えば

Data = 0.98V以下の時、NOR回路の出力は(1行, 2行, ..., 6行) = (

50

1 1 1 1 1 1 )

Data = 1 . 32V の時、NOR回路の出力は(1行, 2行, …, 6行) = (100000)

Data = 1 . 79V の時、NOR回路の出力は(1行, 2行, …, 6行) = (010000)

となる。このように Data 端子の電圧によって、任意の1行を選択することが出来る。

#### 【0069】

この抵抗比の設定は参照電位、参照電位のバラツキ、分割抵抗のバラツキ、トリミングデータを書き込む装置の精度、要求スピードによって変わるので、それに合わせて設定する。また、行数もそれに合わせて変更する。

10

#### 【0070】

この方式の場合、抵抗を利用しているため出力の切り替えが遅い。そのために Data の切り替え途中で意図しない行が選択されてしまう危険性がある。そこで WL を VDD にプルアップしておくとよい。本例では選択時に WL が 0 になるので VDD にプルアップさせたが、選択時に 1 となる回路方式の場合は VSS にプルダウンさせる。

#### 【0071】

ここで挙げた回路は行デコーダをアナログ・デジタル変換回路で構成した場合の1例であって、デコーダ回路をこの方式に限定するものではない。また、アナログ・デジタル変換回路の方式をこの方式に限定するものでもない。

20

#### 【0072】

以上の構成によって、付加 Pad を1つに削減したトリミング回路、選択回路を従来技術に較べて簡略化したトリミング回路、任意のビット数のメモリ素子からなるトリミング回路が得られる。

#### 【実施例6】

#### 【0073】

実施例5で用いた、アナログ・デジタル変換回路は電流を流していないと機能しないが、この機能が必要とされるのは書込動作時のみである。よって、電流が流れる経路にスイッチを設け、必要な時だけ、電流を流すようにして、消費電流を抑制することができる。スイッチにはトランジスタを用いることができる。

#### 【0074】

30

図4に示すメモリセルは電流を流し続ける場合がある。例えばメモリ素子12がONしていると、そのON抵抗と負荷抵抗11とによって決まる電流が電源間に定常に流れる。この電流を抑えるために、メモリセルからの出力データをラッチ等の消費電流が極めて低い回路に保存し、保存した後はメモリセルに流れる電流を遮断する方法を用いることができる。ラッチ回路が情報を保存している期間の消費電流は、ラッチを構成するトランジスタのOFF時のリーク電流程度であるので極めて小さい。

#### 【0075】

図4に示すメモリセルは VDD から電流を引っ張っているが、VDD ではなく別途設けた電源ラインに接続し、その電源ラインの電位を下げることで、消費電流を抑制するという方法もある。この方法はアナログ・デジタル変換回路にも適用できる。

40

#### 【実施例7】

#### 【0076】

図1、図8に示す本発明のトリミングメモリ回路において、A列の前にBL制御用メモリセルを追加し、このメモリセルに書込が行われないと BLA 選択状態にならず、書込が行われると BLA が選択状態になるようにする。これによって A列前の BL 制御用メモリセルに書込を行う以前には、メモリ回路全体への書込が禁止される。

#### 【0077】

トリミングメモリ回路においては、トリミング情報の書込以前にも、外乱要因による誤書込が起きる可能性がある。本方式によって、この誤書込を防止する機能が得られる。

#### 【0078】

50

前実施例で述べた電流経路の遮断方法について、電流経路の途中にトランジスタを設け、A列前に配置したBL制御用メモリセルに書きが行われるとトランジスタがONして電流が流れ、メモリセルの最終列への書きが終了すると、トランジスタをOFFして電流経路を遮断するように働くよう配置する。これは、書き時以外の消費電流を抑制する1つの方法である。

#### 【0079】

図1、図8に示す本発明のトリミングメモリ回路において、A列の書き完了を記憶するBL制御用メモリセルはA列とB列を直接制御している。よって前実施例のようにA列に配置せず、B列にA列の書き完了を記憶するBL制御用メモリセルを配置しても、回路規模はほぼ同等で収まる。このようにすれば、A列に前記の書きが行われないとA列以降に書きが行えないようとするBL制御用メモリセルを配置し、B列にA列のトリミング用メモリセルの書き完了を記憶するBL制御用メモリセルを配置し、以降の列も同様にして制御することが可能である。10

#### 【実施例8】

#### 【0080】

これまでの実施例においては図4、図5に示す浮遊ゲート構造を有する不揮発性のメモリ素子を用いた場合について述べてきたが、本発明は書き法と誤書き防止法に関するこ20とであり、メモリ素子の方式に限定されるものではない。従来例の説明においてメモリ素子として呼ばないことにした電気的に溶断可能なヒューズをメモリ素子として用いる場合においても、本発明の効果が得られる。

#### 【0081】

また、不揮発性ではないメモリ素子、例えばSRAMのような電源がONしている時の情報記憶できるメモリ素子を本発明に用いることもできる。ただし、この場合は電源を入れる度に情報の書きを行う必要がある。

#### 【実施例9】

#### 【0082】

これまでの実施例ではトリミングメモリ回路に適用した場合について述べてきた。しかしながら、本発明は書き法と誤書き防止法に関するものであり、その用途がトリミング用途に限定される必要性は全くない。本発明はトリミング用途以外のメモリ回路にも適用できる。30

#### 【0083】

ただし、本発明において、書き、読みどちらにおいても完全なランダムアクセスは不可能である。そのため用途は限定される。これまで述べてきたトリミングは、その用途として最も有効な例である。

#### 【実施例10】

#### 【0084】

図2、3のボルテージディテクターと図9のアナログ・デジタル変換を用いた行デコーダはどちらも参照電位を必要とする。この参照電位を生成する回路を共通化することで面積の縮小ができる。

#### 【符号の説明】

#### 【0085】

- 1 Pchトランジスタ

- 2 メモリセル

- 3 トリミング用メモリセル

- 4 BL制御用メモリセル

- 5 NOR回路

- 6 インバータ回路

- 7 抵抗体

- 8 ヒューズ

- 9 メモリセル

40

50

- 1 0 Nchトランジスタ

1 1 負荷抵抗

1 2 メモリ素子

1 3 比較回路

1 4 NAND回路

1 5 定電流源

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図8】

【図7】

【図9】

【図10】

| Data端子<br>電圧(V) | 分割電圧(V) |      |      |      |      |      | 比較回路出力<br>(1行～6行) | NOR回路出力<br>(1行～6行) |

|-----------------|---------|------|------|------|------|------|-------------------|--------------------|

|                 | 1行      | 2行   | 3行   | 4行   | 5行   | 6行   |                   |                    |

| 0.98            | 0.85    | 0.83 | 0.46 | 0.34 | 0.25 | 0.19 | (111111)          | (000000)           |

| 1.32            | 1.15    | 0.85 | 0.63 | 0.46 | 0.34 | 0.25 | (011111)          | (100000)           |

| 1.79            | 1.56    | 1.15 | 0.85 | 0.63 | 0.46 | 0.34 | (001111)          | (010000)           |

| 2.42            | 2.11    | 1.56 | 1.15 | 0.85 | 0.63 | 0.46 | (000111)          | (001000)           |

| 3.28            | 2.85    | 2.11 | 1.56 | 1.15 | 0.85 | 0.63 | (000011)          | (000100)           |

| 4.43            | 3.85    | 2.85 | 2.11 | 1.56 | 1.15 | 0.85 | (000001)          | (000010)           |

| 6.00            | 5.21    | 3.85 | 2.85 | 2.11 | 1.56 | 1.15 | (000000)          | (000001)           |

抵抗比は、行1:0.869、行2:0.642、行3:0.475、行4:0.351、行5:0.259、行6:0.192

抵抗比=(各行～Vss間の抵抗)/(全抵抗)

---

フロントページの続き

(51)Int.Cl.

F I

G 1 1 C 17/06

B

(56)参考文献 特開平02-049297(JP, A)

国際公開第2005/109440(WO, A1)

特開平10-228792(JP, A)

特開2005-100538(JP, A)

特開平11-306782(JP, A)

特開2009-031093(JP, A)

特開平06-125275(JP, A)

特開昭63-263828(JP, A)

(58)調査した分野(Int.Cl., DB名)

G 1 1 C 16 / 0 2

G 1 1 C 16 / 0 6

G 1 1 C 17 / 1 4