(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2009-140491

(P2009-140491A)

(43) 公開日 平成21年6月25日(2009.6.25)

(51) Int.Cl.

**G06T 1/20** (2006.01)

**G06F 15/80** (2006.01)

**G06F 17/10** (2006.01)

**G06F 9/46** (2006.01)

F 1

G06T 1/20

G06T 1/20

G06F 15/80

G06F 17/10

G06F 9/46 410

テーマコード(参考)

5B056

5B057

審査請求有 請求項の数 23 O L 外国語出願 (全 44 頁)

(21) 出願番号 特願2008-302713 (P2008-302713)

(22) 出願日 平成20年11月27日 (2008.11.27)

(31) 優先権主張番号 11/952,858

(32) 優先日 平成19年12月7日 (2007.12.7)

(33) 優先権主張国 米国(US)

(71) 出願人 501261300

エヌヴィディア コーポレイション

アメリカ合衆国, カリフォルニア 950

50, サンタ クララ, サン トマス

エクスプレスウェイ 2701

(74) 代理人 100094318

弁理士 山田 行一

(74) 代理人 100123995

弁理士 野田 雅一

(74) 代理人 100107456

弁理士 池田 成人

(72) 発明者 スチュアート エフ. オベルマン

アメリカ合衆国, カリフォルニア州,

サンタ クララ, サン トマス エクス

プレスウェイ 2701

最終頁に続く

(54) 【発明の名称】融合型積和演算機能ユニット

## (57) 【要約】 (修正有)

【課題】倍精度のサポートを加えることによる、チップ面積に対する影響が低減する融合型積和演算機能ユニットを提供する。

【解決手段】グラフィックスプロセッサに、レンダリングに使用される単精度の機能ユニットに加えて、倍精度の算術演算の直接的なサポートを提供する機能ユニットが追加される。倍精度の機能ユニットは、融合型積和演算を含む複数の異なる演算を、少なくとも倍精度の幅であるデータ経路及び/又は論理回路を使用して、実行することができる。倍精度の機能ユニット及び単精度の機能ユニットは、共通の命令発行回路によって制御することができ、コアに含まれている倍精度の機能ユニットの複製の数を、単精度の機能ユニットの複製の数よりも少なくすることができます。

【選択図】図5

**【特許請求の範囲】****【請求項 1】**

画像データを生成するようになっており、複数の同時スレッドを実行するようになっている処理コアを含んでおり、単精度オペランドに対して動作するレンダリングパイプラインを備えており、

前記処理コアが、倍精度の入力オペランドのセットに対して複数の倍精度演算のうちの一つを選択的に実行するようになっている多目的の倍精度機能ユニットを更に含んでおり、該多目的の倍精度機能ユニットが、少なくとも一つの算術演算論理回路を含んでおり、

前記倍精度機能ユニットの前記算術演算論理回路の全てが、倍精度において動作するよう十分な広さになっている、

グラフィックスプロセッサ。

**【請求項 2】**

前記倍精度機能ユニットは、前記複数の倍精度演算のそれぞれが同数のクロックサイクルで完了するように、なっている、請求項 1 に記載のグラフィックスプロセッサ。

**【請求項 3】**

前記倍精度機能ユニットは、前記複数の倍精度演算のそれぞれが、オーバーフロー条件又はアンダーフロー条件が発生するかにかかわらず、同数のクロックサイクルで完了するように、なっている、請求項 2 に記載のグラフィックスプロセッサ。

**【請求項 4】**

前記倍精度機能ユニットは、オーバーフロー条件又はアンダーフロー条件が発生した場合に、浮動小数点算術演算の規格に準拠するオーバーフロー結果又はアンダーフロー結果を生成し、前記オーバーフロー条件又は前記アンダーフロー条件が発生したか否かを示すための出力ステータスフラグをセットするように、なっている、請求項 3 に記載のグラフィックスプロセッサ。

**【請求項 5】**

前記倍精度機能ユニットは、前記複数の倍精度演算のうちの任意の一つを完了するためにはする時間が、浮動小数点例外によって影響されないように、なっている、請求項 1 に記載のグラフィックスプロセッサ。

**【請求項 6】**

前記複数の倍精度演算が、

二つの倍精度オペランドを加算する加算演算と、

二つの倍精度オペランドを乗算する乗算演算と、

第 1 の倍精度オペランドと第 2 の倍精度オペランドとの積を計算し、次いで、前記積に第 3 の倍精度オペランドを加算する融合型積和演算と、

を含んでいる、請求項 1 に記載のグラフィックスプロセッサ。

**【請求項 7】**

前記複数の倍精度演算が、第 1 のオペランドと第 2 のオペランドとに対して比較テストを実行し、前記比較テストが満たされているか否かを示すブール結果を生成する倍精度比較 ( D S E T ) 演算を更に含んでいる、請求項 6 に記載のグラフィックスプロセッサ。

**【請求項 8】**

前記複数の倍精度演算が、

二つの倍精度入力オペランドのうちの大きい方のオペランドを返す倍精度最大値 ( D M A X ) 演算と、

二つの倍精度入力オペランドのうちの小さい方のオペランドを返す倍精度最小値 ( D M I N ) 演算と、

を更に含んでいる、請求項 6 に記載のグラフィックスプロセッサ。

**【請求項 9】**

前記複数の倍精度演算が、倍精度形式から倍精度以外の形式にオペランドを変換する少なくとも一つの形式変換演算を更に含んでいる、請求項 6 に記載のグラフィックスプロセッサ。

**【請求項 10】**

前記複数の倍精度演算が、

倍精度以外の形式から倍精度形式にオペランドを変換する少なくとも一つの形式変換演算、

をさらに含んでいる、請求項 6 に記載のグラフィックスプロセッサ。

**【請求項 11】**

画像データを生成するようになっており、複数の同時スレッドを実行するようになっている処理コアを含んでいるレンダリングパイプラインを備えており、

前記処理コアが、一以上の単精度オペランドに対して算術演算を実行するようになっている単精度機能ユニットを含んでおり、

前記処理コアが、倍精度入力オペランドのセットに対して融合型積和演算を実行して倍精度の結果を提供するようになっている倍精度の積和演算 (DFMA) 機能ユニット、を更に含んでおり、

前記DFMA機能ユニットがDFMAパイプラインを含んでおり、前記DFMAパイプラインは、当該DFMAパイプラインを通る单一の経路において前記融合型積和演算が実行されるよう十分に広いデータ経路を有する、

グラフィックスプロセッサ。

**【請求項 12】**

前記DFMA機能ユニットが、

二つの倍精度仮数の積を1回の反復において計算するようになっている乗算器と、

二つの倍精度仮数の和を1回の反復において計算するようになっている加算器と、

を含んでいる、請求項 11 に記載のグラフィックスプロセッサ。

**【請求項 13】**

前記DFMA機能ユニットが、一対の倍精度入力オペランドに対して乗算演算を実行して倍精度の結果を提供するように、更に構成されている、請求項 11 に記載のグラフィックスプロセッサ。

**【請求項 14】**

前記乗算演算と前記融合型積和演算のそれぞれが、同数のクロックサイクルで完了する、請求項 13 に記載のグラフィックスプロセッサ。

**【請求項 15】**

前記DFMA機能ユニットが、一対の倍精度入力オペランドに対して加算演算を実行して倍精度の結果を提供するように、更に構成されている、請求項 11 に記載のグラフィックスプロセッサ。

**【請求項 16】**

前記加算演算と前記融合型積和演算のそれぞれが、同数のクロックサイクルで完了する、請求項 15 に記載のグラフィックスプロセッサ。

**【請求項 17】**

前記DFMA機能ユニットが、一対の倍精度入力オペランドに対して乗算演算を実行して倍精度の結果を提供するように、更に構成されており、

前記融合型積和演算、前記加算演算、及び前記乗算演算のそれぞれが、オーバーフロー条件又はアンダーフロー条件が発生するか否かにかかわらず同数のクロックサイクルで完了する、

請求項 16 に記載のグラフィックスプロセッサ。

**【請求項 18】**

前記DFMA機能ユニットが、オーバーフロー条件又はアンダーフロー条件が発生した場合に、浮動小数点算術演算の規格に準拠するオーバーフロー結果又はアンダーフロー結果を生成し、前記オーバーフロー条件又は前記アンダーフロー条件が発生したか否かを示すための出力ステータスフラグをセットするように、更に構成されている、請求項 17 に記載のグラフィックスプロセッサ。

**【請求項 19】**

10

20

30

40

50

前記処理コアが、並列に動作するようになっている前記第1の機能ユニットの複数（P個）の複製と、前記D F M A機能ユニットの複数（N個）の複製と、を含んでいる、請求項11に記載のグラフィックスプロセッサ。

【請求項20】

前記数Pが前記数Nよりも大きい、請求項19に記載のグラフィックスプロセッサ。

【請求項21】

前記数Nが1である、請求項20に記載のグラフィックスプロセッサ。

【請求項22】

前記処理コアが、前記D F M A機能ユニットを対象とするP個のセットの倍精度入力オペランドを集めて、前記P個のセットの倍精度オペランドのうち異なるセットの倍精度オペランドを、異なるクロックサイクルにおいて、前記D F M A機能ユニットに提供するようになっている入力マネージャ回路を更に含んでいる、請求項21に記載のグラフィックスプロセッサ。

10

【請求項23】

前記入力マネージャ回路が、前記第1の機能ユニットを対象とするP個のセットの単精度入力オペランドを集めて、前記第1の機能ユニットの前記P個の複製のそれぞれに、前記P個のセットの単精度オペランドのうち異なるセットの単精度オペランドを、並列に提供するようになっている、請求項22に記載のグラフィックスプロセッサ。

【発明の詳細な説明】

20

【技術分野】

【0001】

[0001]本発明は、グラフィックスプロセッサに関するものであり、より詳細には、グラフィックスプロセッサにおける倍精度の融合型積和演算（Fused Multiply-add）機能ユニットに関するものである

【発明の背景】

【0002】

[0002]グラフィックスプロセッサは、コンピュータシステムにおいて、2次元のジオメトリデータ又は3次元のジオメトリデータから画像をレンダリングするステップを高速化する目的で一般に使用されている。このようなプロセッサは、一般には、高い並列性及び高いスループットを持つように設計されており、数千個のプリミティブを並列に処理して、複雑でリアルなアニメーション画像をリアルタイムでレンダリングすることができる。高性能のグラフィックスプロセッサは、一般的な中央処理装置（C P U）よりも高い計算能力を提供する。

30

【0003】

[0003]最近では、グラフィックスプロセッサの処理能力を利用して、画像のレンダリングには無関係の様々な計算を高速化することが注目されている。「汎用」グラフィックスプロセッサを使用して、科学分野、金融分野、ビジネス分野、及びその他の分野における計算を実行することができる。

【0004】

[0004]汎用計算用にグラフィックスプロセッサを適合させる上での一つの問題は、グラフィックスプロセッサは、通常、比較的低い数値精度用に設計されていることである。高品質の画像は、32ビット（「単精度」）浮動小数点値、場合によっては16ビット（「半精度」）浮動小数点値を使用してレンダリングされ得るものであり、機能ユニット及び内部パイプラインは、これらのデータ幅がサポートされるように構成されている。それに対して、多くの汎用計算では、より高い数値精度、例えば、64ビット（「倍精度」）が要求される。

40

【0005】

[0005]より高い数値精度をサポートするために、グラフィックスプロセッサによっては、一連の機械語命令と32ビット又は16ビットの機能ユニットとを用いて倍精度の計算を実行するためのソフトウェア手法を使用している。この方法ではスループットが低下し

50

、例えば、1回の64ビット乗算演算を完了するのに100個以上の機械語命令が必要となることがある。このような長い命令列により、グラフィックスプロセッサの倍精度のスループットが大幅に低下することがある。一つの代表的なケースにおいては、グラフィックスプロセッサが倍精度の計算を実行するときのスループットは、高性能のデュアルコアCPUチップによって可能であるスループットの約1/5であると推定される（これと比較して、同じグラフィックスプロセッサは、単精度の計算をデュアルコアCPUのスループットの約15~20倍で実行することができる）。ソフトウェアベースのソリューションは非常に遅いため、従来のグラフィックスプロセッサを倍精度の計算に使用することはめったにない。

#### 【0006】

[0006]別のソリューションは、単純に、グラフィックスプロセッサの算術演算回路の全てを、倍精度のオペランドを扱うよう十分な広さにすることである。これにより、倍精度演算におけるグラフィックスプロセッサのスループットが増大して、単精度におけるスループットに匹敵するものとなる。しかしながら、グラフィックスプロセッサは、一般に、並列演算をサポートするために、各算術演算回路の数十個の複製を備えており、このような各回路のサイズを増大させることによって、チップ面積、コスト、及び電力消費量が相当に増大する。

#### 【0007】

[0007]更に別のソリューションは、所有者が同一の同時係属中の米国特許出願第11/359,353号明細書（出願日：2006年2月21日）に記載されているように、単精度の算術演算回路を利用して倍精度の演算を実行することである。この方法においては、単精度の機能ユニットに含まれている特殊なハードウェアを使用して、倍精度の演算を反復的に実行する。この方法は、ソフトウェアベースのソリューションよりも相当に高速であるが（スループットは、単精度のスループットの1/100以下ではなく、例えば1/4となり得る）、チップの設計が大幅に複雑となり得る。さらに、単精度の演算と倍精度の演算との間で同じ機能ユニットを共有する結果として、同じ機能ユニットを必要とする命令が多すぎる場合に、そのユニットがパイプラインにおけるボトルネックとなることがある。

#### 【発明の概要】

#### 【0008】

[0008]本発明の実施形態は、グラフィックスプロセッサにおける倍精度の算術演算を直接的にサポートする。レンダリングに使用される単精度の機能ユニットに加えて、多目的の倍精度の機能ユニットが提供される。倍精度の機能ユニットは、倍精度の入力に対する融合型積和演算を含む複数の異なる演算を、少なくとも倍精度の幅であるデータ経路及び/又は論理回路を使用して、実行することができる。倍精度の機能ユニット及び単精度の機能ユニットは、共通の命令発行回路によって制御することができ、コアに含まれている倍精度の機能ユニットの複製の数を、単精度の機能ユニットの複製の数よりも少なくすることができ、これによって、倍精度のサポートを加えることによるチップ面積に対する影響が低減する。

#### 【0009】

[0009]本発明の一態様によると、グラフィックスプロセッサは、画像データを生成するようになっているレンダリングパイプラインを有する。このレンダリングパイプラインは、単精度オペランド用に動作するものであり、複数の同時スレッドを実行するようになっている処理コアを含んでいる。処理コアは、倍精度の入力オペランドのセットに対して複数の倍精度演算のうちの一つを選択的に実行するようになっている多目的の倍精度機能ユニットを含んでいる。この多目的の倍精度機能ユニットは、少なくとも一つの算術演算論理回路を含んでおり、倍精度機能ユニットの算術演算論理回路の全ては、倍精度において動作するための十分な広さになっている。いくつかの実施形態においては、倍精度機能ユニットは、倍精度演算のそれぞれが同数のクロックサイクルで完了するように構成されている。また、倍精度機能ユニットは、倍精度演算のうちの任意の一つを完了するために要

10

20

30

40

50

求される時間（例えば、クロックサイクルの数）がアンダーフロー条件又はオーバーフロー条件によって影響されないように、構成されていてもよい。

#### 【0010】

[0010]様々な倍精度演算及び倍精度演算の組合せをサポートすることができる。一実施形態においては、倍精度演算は、二つの倍精度オペランドを加算する加算演算と、二つの倍精度オペランドを乗算する乗算演算と、第1の倍精度オペランドと第2の倍精度オペランドとの積を計算し、次いで、この積に第3の倍精度オペランドを加算する、融合型積和演算と、を含んでいる。サポートすることのできる別の倍精度演算としては、第1のオペランドと第2のオペランドとに対して比較テストを実行し、この比較テストが満たされているかを示すプール結果を生成する倍精度比較（DSET）演算、二つの倍精度入力オペランドのうち大きい方のオペランドを返す倍精度最大値（MAX）演算、二つの倍精度入力オペランドのうち小さい方のオペランドを返す倍精度最小値（MIN）演算、が挙げられる。さらには、倍精度形式から倍精度以外の形式に（又はその逆に）オペランドを変換する形式変換演算もサポートすることができる。

10

#### 【0011】

[0011]本発明の別の態様によると、グラフィックスプロセッサは、画像データを生成するようになっているレンダリングパイプラインを含んでいる。このレンダリングパイプラインは、複数の同時スレッドを実行するようになっている処理コアを含んでいる。処理コアは、一以上の単精度オペランドに対して算術演算を実行するようになっている単精度の機能ユニットと、倍精度入力オペランドのセットに対して積和演算を実行して倍精度の結果を提供するようになっている倍精度の融合型積和演算（DFMA）機能ユニットと、を含んでいる。このDFMA機能ユニットは、DFMAパイプラインを含んでおり、DFMAパイプラインは、当該DFMAパイプラインを通る単一のパスで積和演算を実行するのに十分に広いデータ経路を有することが好適である。例えば、DFMA機能ユニットは、倍精度の二つの仮数の積を1回の反復で計算するようになっている乗算器と、倍精度の二つの仮数の和を1回の反復で計算するようになっている加算器と、を含んでいてもよい。

20

#### 【0012】

[0012]さらに、DFMA機能ユニットを、別の演算を実行するように構成することもできる。例えば、いくつかの実施形態においては、DFMAは、一組の倍精度入力オペランドに対して乗算演算を実行して倍精度の結果を提供するように構成されている。いくつかの実施形態においては、乗算演算と融合型積和演算は、それぞれ、同数のクロックサイクルで完了する。同様に、DFMA機能ユニットを、一組の倍精度入力オペランドに対して加算演算を実行して倍精度の結果を提供するように構成することができる。一実施形態においては、加算演算と融合型積和演算は、それぞれ、同数のクロックサイクルで完了する。

30

#### 【0013】

[0013]いくつかの実施形態においては、処理コアは、並列に動作するようになっている第1の機能ユニットの複数（P個）の複製と、DFMA機能ユニットの複数（N個）の複製と、を含んでいる。ここで、数Pは数Nよりも大きい。一実施形態においては、数Nは1である。

40

#### 【0014】

[0014]処理コアは、入力マネージャ回路を含んでいてもよく、当該入力マネージャ回路は、DFMA機能ユニット用のP個のセットの倍精度入力オペランドを集めて、P個のセットの倍精度オペランドのうち異なるセットの倍精度オペランドを、異なる（例えば、連続する）クロックサイクルで、DFMA機能ユニットに提供するようになっている。さらに、入力マネージャ回路は、第1の機能ユニット用のP個のセットの単精度入力オペランドを集めて、P個のセットの単精度オペランドのうちの異なるセットの単精度オペランドを、第1の機能ユニットのP個の複製の各々に並列に提供してもよい。

#### 【0015】

[0015]本発明の概念及び利点は、以下の詳細な説明と添付の図面から深く理解されるで

50

あろう。

【図面の簡単な説明】

【0016】

【図1】本発明の実施形態によるコンピュータシステムのブロック図である。

【図2】本発明の実施形態による、グラフィックス処理ユニットにおいて実施することができるレンダリングパイプラインのブロック図である。

【図3】本発明の実施形態による実行コアのブロック図である。

【図4】本発明の実施形態による倍精度機能ユニットによって実行することができる倍精度算術演算と、倍精度比較演算と、形式変換演算とを一覧表示した図である。

【図5】本発明の実施形態による倍精度機能ユニットの単純化したブロック図である。 10

【図6】図5の倍精度機能ユニットにおけるオペランド準備ブロックのブロック図である。

。

【図7】図5の倍精度機能ユニットにおける指数経路のブロック図である。

【図8】図5の倍精度機能ユニットにおける仮数経路のブロック図である。

【図9】図5の倍精度機能ユニットにおける符号経路のブロック図である。

【図10】図5の倍精度機能ユニットにおける出力セクションのブロック図である。

【図11】本発明の実施形態による実行コアのブロック図である。

【図12】本発明の実施形態による、倍精度機能ユニットのためのオペランドの順序付けを示すブロック図である。 20

【詳細な説明】

【0017】

[0028]本発明の実施形態は、専用の倍精度（例えば、64ビット）機能ユニットを含むグラフィックスプロセッサを提供する。一実施形態においては、倍精度機能ユニットは、加算演算と、乗算演算と、融合型積和演算と、更には、倍精度比較と、倍精度形式とそれ以外の形式との間の形式変換とを実行することができる。

【0018】

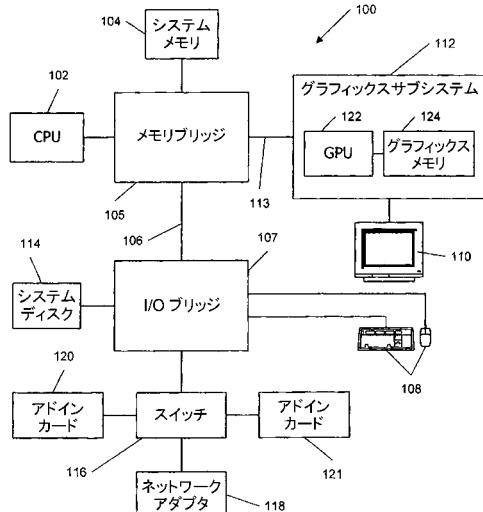

I . システムの概要

A . コンピュータシステムの概要

[0029]図1は、本発明の実施形態によるコンピュータシステム100のブロック図である。コンピュータシステム100は、メモリブリッジ105を含むバス経路を介して通信する中央処理装置（CPU）102及びシステムメモリ104を含んでいる。メモリブリッジ105は、例えば、従来のノースブリッジチップであってもよく、バス又はその他の通信経路106（例：HyperTransportリンク）を介してI/O（入力/出力）ブリッジ107に接続されている。I/Oブリッジ107は、例えば、従来のサウスブリッジチップであってもよく、一以上のユーザ入力装置108（例：キーボード、マウス）からユーザ入力を受け取り、当該入力をバス106及びメモリブリッジ105を介してCPU102に転送する。視覚的出力は、ピクセルベースの表示装置110（例：従来のCRT又はLCDベースのモニター）によって提供され、この表示装置110は、バス又はその他の通信経路113（例：PCI Express（PCI-E）、アクセラレーテッドグラフィックスポート（AGP）リンク）を介してメモリブリッジ105に接続されたグラフィックスサブシステム112の制御下で動作する。I/Oブリッジ107には、システムディスク114も接続されている。スイッチ116は、I/Oブリッジ107と、その他のコンポーネント、例えば、ネットワークアダプタ118、様々なアドインカード120, 121との間の接続を提供している。I/Oブリッジ107には、それ以外のコンポーネント（図示していない）として、USB接続装置又はその他のポート接続装置、CDドライブ、DVDドライブなどを接続することもできる。様々なコンポーネントの間のバス接続は、バスプロトコル（例えば、PCI（ペリフェラルコンポーネントインターフェクト）、PCI-E、AGP、HyperTransport）、又はその他の任意のバス通信プロトコル或いはポイントツーポイント通信プロトコルを使用して実施することができ、異なるデバイスの間の接続には、この技術分野において公知であるよ 30 40 50

うに、様々なプロトコルを使用することができる。

【0019】

[0030]グラフィックス処理サブシステム112は、グラフィックス処理ユニット(GPU)122とグラフィックスメモリ124とを含んでおり、これらは、例えば、一以上の集積回路デバイス、例えば、プログラマブルプロセッサ、特定用途向け集積回路(ASIC)、メモリデバイスを使用して実施することができる。GPU122は、様々なタスクとして、CPU102及び/又はシステムメモリ104によってメモリブリッジ105及びバス113を介して供給されるグラフィックスデータからピクセルデータを生成すること、グラフィックスメモリ124と対話してピクセルデータを格納及び更新すること等に関連するタスクを実行するように、構成することができる。例えば、GPU122は、CPU102上で実行される様々なプログラムによって提供される2次元又は3次元のシーンデータから、ピクセルデータを生成することができる。さらに、GPU122は、メモリブリッジ105を介して受け取るピクセルデータを、さらなる処理を実行して、又はそのまま、グラフィックスメモリ124に格納することができる。GPU122は、グラフィックスメモリ124からのピクセルデータを表示装置110に提供するように構成されたスキャンアウトモジュールも含んでいる。

10

【0020】

[0031]さらに、GPU122は、データ処理タスクのために、汎用計算を実行するように構成されている。当該タスクには、グラフィックスアプリケーションに関連するタスク(例えば、ビデオゲーム等における物理モデリング)と、グラフィックスアプリケーションには関連しないタスクとが含まれる。汎用計算の場合には、GPU122は、システムメモリ104又はグラフィックスメモリ124から入力データを読み取り、一以上のプログラムを実行して当該データを処理し、出力データをシステムメモリ104又はグラフィックスメモリ124に書き込むことが好適である。GPU122は、汎用計算において使用するための一以上の倍精度の融合型積和演算ユニット(図1には示していない)と、レンダリング演算時に使用する別の単精度の機能ユニットとを含むことが好適である。

20

【0021】

[0032]CPU102は、システム100のマスタークロックとして動作し、他のシステムコンポーネントの動作を制御及び調整する。具体的には、CPU102は、GPU122の動作を制御するコマンドを発行する。いくつかの実施形態においては、CPU102は、GPU122用のコマンドストリームをコマンドバッファに書き込む。このコマンドバッファは、システムメモリ104、グラフィックスメモリ124、又は、CPU102及びGPU122の双方からアクセス可能な別の記憶域中に存在し得る。GPU122は、コマンドバッファからコマンドストリームを読み取り、CPU102の動作とは非同期にコマンドを実行する。これらのコマンドは、画像を生成するための従来のレンダリングコマンドを含み得るものであり、また、CPU102上で実行されるアプリケーションが画像の生成には関連しないデータ処理をGPU122の計算能力を利用して行うことを可能にする汎用計算コマンドを含み得る。

30

【0022】

[0033]図1に示したシステムは例示を目的としており、変形及び変更が可能であることが理解されるであろう。バスのトポロジー(例えば、ブリッジの数、ブリッジの配置編成)は、必要に応じて修正することができる。例えば、いくつかの実施形態においては、システムメモリ104が、ブリッジを通じてではなく直接的にCPU102に接続されており、他のデバイスが、メモリブリッジ105及びCPU102を介してシステムメモリ104と通信する。別のトポロジーにおいては、グラフィックスサブシステム112が、メモリブリッジ105ではなくI/Oブリッジ107に接続される。さらに別の実施形態においては、I/Oブリッジ107とメモリブリッジ105とを一つのチップに統合することができる。図1に示した特定のコンポーネントはオプションであり、例えば、任意の数のアドインカード或いは周辺装置をサポートすることができる。いくつかの実施形態

40

50

においては、スイッチ 116 が省かれ、ネットワークアダプタ 118 及びアドインカード 120, 121 が I/O ブリッジ 107 に直接接続される。

#### 【0023】

[0034] さらに、GPU 122 と、システム 100 の他のコンポーネントとの間の接続を変更することも可能である。いくつかの実施形態においては、グラフィックスサブシステム 112 が、システム 100 の拡張スロットに挿入することのできるアドインカードとして実施される。別の実施形態においては、GPU が、バスブリッジ（例えば、メモリブリッジ 105、I/O ブリッジ 107）と共に一つのチップに統合される。更に別の実施形態においては、GPU 122 の要素のいくつか又は全てを CPU 102 と統合することができる。

10

#### 【0024】

[0035] GPU は、任意の量のローカルグラフィックスメモリを備えていてもよく（ローカルメモリを設けなくてもよい）、ローカルメモリ及びシステムメモリを任意の組合せで使用することができる。例えば、ユニファイドメモリアーキテクチャ（UMA）の実施形態においては、専用のグラフィックスメモリデバイスを設けず、GPU は、システムメモリを独占的又は略独占的に使用する。UMA の実施形態においては、GPU をバスブリッジチップに組み込むことができ、又は、GPU をブリッジチップ及びシステムメモリに接続する高速バス（例：PCI-E）を備えた個別のチップとして、GPU を提供することができる。

20

#### 【0025】

[0036] さらに、例えば、1枚のグラフィックスカードに複数の GPU を含めることによって、或いは、複数のグラフィックスカードをバス 113 に接続することによって、任意の数の GPU をシステムに含めることができることも理解されたい。複数の GPU を、同じ表示装置又は複数の異なる表示装置への画像を生成するように並列に動作させてもよく、或いは、一つの GPU が画像を生成するように動作する一方で、別の GPU が汎用計算（後から説明する倍精度の計算を含む）を実行してもよい。

30

#### 【0026】

[0037] さらには、本発明の態様を具現化する GPU は、様々な装置、例えば、汎用コンピュータシステム、ビデオゲームコンソール及びその他の特殊用途のコンピュータシステム、DVD プレーヤー、携帯機器（携帯電話、携帯情報端末など）に組み込むことができる。

30

#### 【0027】

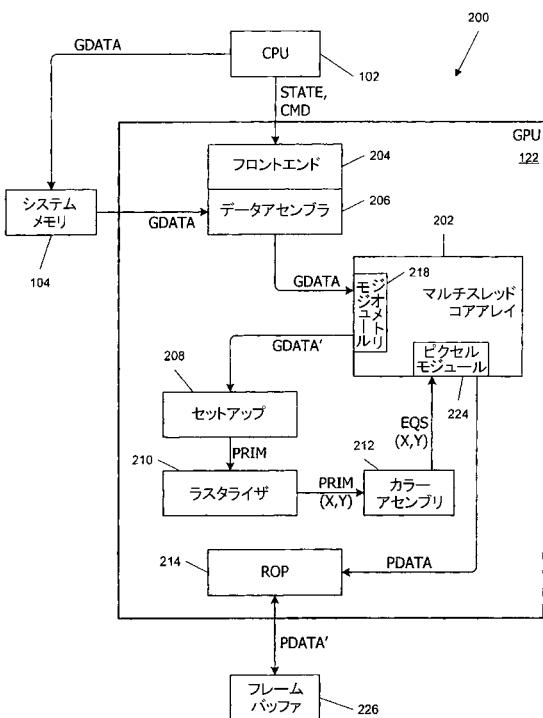

##### B. レンダリングパイプラインの概要

[0038] 図 2 は、本発明の実施形態による、図 1 の GPU 122 において実施することができるレンダリングパイプライン 200 のブロック図である。この実施形態においては、レンダリングパイプライン 200 は、適用可能なグラフィックス関連のプログラム（例えば、頂点シェーダー、ジオメトリシェーダー、ピクセルシェーダーのうちの少なくとも一つ）と汎用計算プログラムとが、同じ並列処理ハードウェア（本明細書においては「マルチスレッドコアアレイ（multithreaded core array）」202 と称する）を使用して実行されるアーキテクチャを使用して、実施されている。

40

#### 【0028】

[0039] レンダリングパイプライン 200 は、マルチスレッドコアアレイ 202 に加えて、フロントエンド 204 及びデータアセンブラー 206 と、セットアップモジュール 208 と、ラスタライザ 210 と、カラーアセンブリモジュール 212 と、ラスター操作レーションモジュール（ROP）214 と、を含んでいる。これらのコンポーネントのそれぞれは、従来の集積回路技術又はその他の技術を使用して実施することができる。

#### 【0029】

[0040] レンダリング演算においては、フロントエンド 204 が、状態情報（STATE）と、コマンド（CMD）と、ジオメトリデータ（GDATA）とを、例えば図 1 の CPU 102 から受け取る。いくつかの実施形態においては、CPU 102 は、ジオメト

50

リデータを直接提供するのではなく、ジオメトリデータが格納されているシステムメモリ 104 中の位置への参照情報を提供し、データアセンブラー 206 が、システムメモリ 104 からデータを取得する。レンダリング演算においては、状態情報、コマンド、及びジオメトリデータは、基本的に従来の性質のものとすることができます、これらを使用することにより、レンダリング後の（一以上の）必要な画像（例えば、シーンのジオメトリ、ライティング、シェーディング、テクスチャ、モーション、カメラパラメータのうちの一つ以上）を定義することができる。

#### 【0030】

[0041] 状態情報及びレンダリングコマンドは、レンダリングパイプライン 200 の様々なステージにおける処理パラメータ及びアクションを定義する。フロントエンド 204 は、状態情報及びレンダリングコマンドを、制御経路（図示していない）を介して、レンダリングパイプライン 200 の別のコンポーネントに導く。この技術分野において公知であるように、これらのコンポーネントは、処理時にアクセスされる様々な制御レジスタに値を格納し、又は制御レジスタ内の値を更新することによって、受け取った状態情報に応答することができ、パイプライン内で受け取ったデータを処理することによって、レンダリングコマンドに応答することができる。

#### 【0031】

[0042] フロントエンド 204 は、ジオメトリデータをデータアセンブラー 206 に導く。データアセンブラー 206 は、ジオメトリデータをフォーマッティングし、それをマルチスレッドコアアレイ 202 におけるジオメトリモジュール 218 への配達用に準備する。

10

20

30

#### 【0032】

[0043] ジオメトリモジュール 218 は、頂点データに対して頂点シェーダープログラム及び／又はジオメトリシェーダープログラムを実行するよう、マルチスレッドコアアレイ 202 におけるプログラマブル処理エンジン（図示していない）に命令する。これらのプログラムは、フロントエンド 204 によって提供される状態情報に応答して選択される。頂点シェーダープログラム及び／又はジオメトリシェーダープログラムは、この技術分野において公知であるようにレンダリングアプリケーションによって指定することができ、異なる頂点及び／又はプリミティブに、異なるシェーダープログラムを適用することができる。いくつかの実施形態においては、頂点シェーダープログラム及びジオメトリシェーダープログラムは、マルチスレッドコアアレイ 202 における同じプログラマブル処理コアを使用して実行される。従って、一つの処理コアは、ある時点においては頂点シェーダーとして動作し、頂点プログラムの命令を受け取って実行することができ、別の時点においては、同じ処理コアがジオメトリシェーダーとして動作し、ジオメトリプログラムの命令を受け取って実行することができる。処理コアはマルチスレッド化することができ、異なるタイプのシェーダープログラムを実行する異なるスレッドを、マルチスレッドコアアレイ 202 において同時に進行させることができる。

#### 【0033】

[0044] 頂点シェーダープログラム及び／又はジオメトリシェーダープログラムが実行された後に、ジオメトリモジュール 218 は、処理されたジオメトリデータ（GDATA'）をセットアップモジュール 208 に渡す。セットアップモジュール 208 は、一般的に従来の設計のモジュールとすることができまするものであり、各プリミティブのクリップ空間座標又はスクリーン空間座標からエッジ方程式（edge equations）を生成する。エッジ方程式は、スクリーン空間内の点がプリミティブの内側であるか外側であるかを判定する目的に好適に使用可能である。

40

#### 【0034】

[0045] セットアップモジュール 208 は、プリミティブ（PRIM）のそれぞれをラスタライザ 210 に提供する。ラスタライザ 210（一般的に従来の設計とすることができます）は、どのピクセル（存在時）がプリミティブによってカバーされているかを、例えば従来のスキャン変換アルゴリズム（scan-conversion algorithms）を使用して判定する。本明細書において使用する「ピクセル」（又は「フラグメン

50

ト」)は、一般には、一つのカラー値が決定される、2次元スクリーン空間内の領域を意味する。ピクセルの数及び配置は、レンダリングパイプライン200の設定可能なパラメータとすることができます、特定の表示装置の画面解像度に相関させてもよく、又は相関させなくてもよい。

#### 【0035】

[0046] ラスタライザ210は、どのピクセルがプリミティブによってカバーされているかを判定した後、プリミティブ(PRIM)と、そのプリミティブによってカバーされているピクセルのスクリーン座標(X, Y)のリストとを、カラーアセンブリモジュール212に提供する。カラーアセンブリモジュール212は、ラスタライザ210から受け取ったプリミティブとカバレッジ情報を、プリミティブの頂点の属性(例:色成分、テクスチャ座標、面法線)に関連付けて、属性のいくつか又は全てをスクリーン座標空間内の位置の関数として定義する平面方程式(又はその他の適切な方程式)を生成する。

10

#### 【0036】

[0047] これらの属性方程式は、ピクセルシェーダープログラムにおいて、プリミティブの中の任意の位置における属性の値を計算するために好適に使用可能である。当該方程式は、従来の手法を使用して生成することができる。例えば、一実施形態においては、カラーアセンブリモジュール212は、属性Uそれぞれについて $U = A \times + B \cdot y + C$ という形式の平面方程式の係数A、B、及びCを生成する。

20

#### 【0037】

[0048] カラーアセンブリモジュール212は、ピクセルの少なくとも一つのサンプリング位置をカバーしているプリミティブそれぞれの属性方程式(EQS、例えば、平面方程式の係数A、B、及びCを含んでいることができる)と、カバーされているピクセルのスクリーン座標(X, Y)のリストとを、マルチスレッドコアアレイ202におけるピクセルモジュール224に提供する。ピクセルモジュール224は、マルチスレッドコアアレイ202におけるプログラマブル処理エンジン(図示していない)に命令して、プリミティブによってカバーされているピクセルそれぞれに対して一以上のピクセルシェーダープログラムを実行させる。これらのプログラムは、フロントエンド204によって提供される状態情報に応答して選択される。あらゆる所与のセットのピクセルに対して使用するピクセルシェーダープログラムは、頂点シェーダープログラム及びジオメトリシェーダープログラムと同様に、レンダリングアプリケーションが指定することができる。

30

#### 【0038】

[0049] ピクセルシェーダープログラムは、頂点シェーダープログラム及び/又はジオメトリシェーダープログラムを実行する同じプログラマブル処理エンジンを使用して、マルチスレッドコアアレイ202において好適に実行される。従って、一つの処理エンジンは、ある時点においては頂点シェーダーとして動作し、頂点プログラムの命令を受け取って実行することができ、別の時点においては、同じ処理エンジンがジオメトリシェーダーとして動作し、ジオメトリプログラムの命令を受け取って実行することができ、更に別の時点においては、同じ処理エンジンがピクセルシェーダーとして動作し、ピクセルシェーダープログラムの命令を受け取って実行することができる。

40

#### 【0039】

[0050] ピクセル又はピクセルのグループの処理が完了した時点で、ピクセルモジュール224は、処理されたピクセル(PDATA)をROP214に提供する。ROP214は、一般的に従来の設計のものであってもよく、ピクセルモジュール224から受け取るピクセル値と、フレームバッファ226内の構築中の画像のピクセルとを統合する。このフレームバッファ226は、例えば、グラフィックスメモリ124内に位置し得る。いくつかの実施形態においては、ROP214は、ピクセルをマスクすることができ、又は、新しいピクセルと、レンダリングされている画像に以前に書き込まれたピクセルとをブレンドすることができる。デプスバッファ、アルファバッファ、及びステンシルバッファを使用して、レンダリングされている画像に対する、入力されるピクセルそれぞれの寄与(存在時)を決定することもできる。入力されるピクセル値それぞれと、以前に格納

50

されているピクセル値との適切な組合せに対応するピクセルデータ P D A T A' が、再びフレームバッファ 226 に書き込まれる。画像が完成した時点で、フレームバッファ 226 を表示装置にスキャンアウトし、及び / 又は、更なる処理を行うことができる。

#### 【 0 0 4 0 】

[0051] 汎用計算においては、マルチスレッドコアアレイをピクセルモジュール 224 によって（又はジオメトリモジュール 218 によって）制御することができる。フロントエンド 204 は、例えば図 1 の C P U 102 から状態情報（S T A T E）及び処理コマンド（C M D）を受け取り、これらの状態情報及びコマンドを、制御経路（図示していない）を介して作業配分ユニットに提供する。この作業配分ユニットは、例えばカラーアセンブリモジュール 212 又はピクセルモジュール 224 に組み込むことができる。作業配分ユニットは、マルチスレッドコアアレイ 202 を構成している複数の処理コアの間で処理タスクを分配する。様々な作業配分アルゴリズムを使用することができる。10

#### 【 0 0 4 1 】

[0052] 処理タスクのそれぞれは、複数の処理スレッドを実行することを含むことが好適であり、この場合、スレッドのそれぞれは同じプログラムを実行する。プログラムは、「グローバルメモリ」（例：システムメモリ 104、グラフィックスメモリ 124、又は、G P U 122 及び C P U 102 の両方からアクセス可能な任意の別のメモリ）から入力データを読み取るための命令と、少なくともいくつかの倍精度演算を含む様々な演算を入力データに対して実行して出力データを生成するための命令と、出力データをグローバルメモリに書き込むための命令と、を含むことが好適である。具体的な処理タスクについては、本発明において重要ではない。20

#### 【 0 0 4 2 】

[0053] 図 2 に記載したレンダリングパイプラインは例示を目的としており、変形及び変更が可能であることが理解されるであろう。このパイプラインは、図示したユニットとは異なるユニットを含むことができ、処理イベントの順序は、本明細書に説明した順序とは異なっていてもよい。さらに、本明細書に説明したモジュールのいくつか又は全ての複数のインスタンスを並列に動作させることができる。このような一実施形態においては、マルチスレッドコアアレイ 202 は、二つ以上のジオメトリモジュール 218 と、それと同じ数の並列に動作するピクセルモジュール 224 とを含む。ジオメトリモジュール及びピクセルモジュールのそれぞれは、マルチスレッドコアアレイ 202 における処理エンジンの異なるサブセットを協働して制御する。30

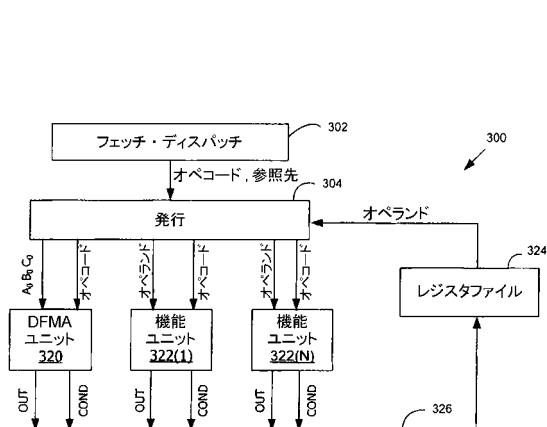

#### 【 0 0 4 3 】

##### C . コアの概要

[0054] マルチスレッドコアアレイ 202 は、多数の処理スレッドを並列に実行するようになっている一以上の処理コアを含むことが好適である。ここで、「スレッド」との用語は、特定のセットの入力データに対して実行される特定のプログラムのインスタンスを意味する。例えば、スレッドは、一つの頂点の属性に対して実行される頂点シェーダープログラムのインスタンス、或いは、与えられたプリミティブ及びピクセルに対して実行されるピクセルシェーダープログラムのインスタンス、又は、汎用計算プログラムのインスタンスとすることができる。40

#### 【 0 0 4 4 】

[0055] 図 3 は、本発明の実施形態による実行コア 300 のブロック図である。実行コア 300 は、例えば、上述したマルチスレッドコアアレイ 202 において実施することができる、様々な計算を実行するための任意の一連の命令を実行するように構成されている。いくつかの実施形態においては、同じ実行コア 300 を使用して、グラフィックスレンダリングの全ての段階におけるシェーダープログラム（例えば、頂点シェーダープログラム、ジオメトリシェーダープログラム、ピクセルシェーダープログラムのうちの一つ以上）と、汎用計算プログラムとを、実行することができる。

#### 【 0 0 4 5 】

[0056] 実行コア 300 は、フェッチ・ディスパッチユニット 302 と、発行ユニット 3

10

20

30

40

50

04と、倍精度の融合型積和演算（DFMA）ユニット320と、DFMA以外の複数（N個）の機能ユニット（FU）322と、レジスタファイル324と、を含んでいる。機能ユニット320, 322のそれぞれは、指定された演算を実行するように構成されている。一実施形態においては、DFMAユニット320は、後述するように、倍精度の融合型積和演算と、それ以外の倍精度演算とを好適に実施する。なお、コア300には任意の数のDFMAユニット320を含めることができることを理解されたい。

#### 【0046】

[0057] DFMA以外の機能ユニット322は、基本的に従来の設計のものであってもよく、様々な演算（例えば、単精度の加算演算、乗算演算、ビットごとの論理演算、比較演算、形式変換演算、テクスチャファイルタリング、メモリアクセス（例：ロード動作及び格納動作）、超越関数の近似、補間）をサポートすることができる。機能ユニット320, 322はパイプライン化されていてもよく、これにより、この技術分野において公知であるように、前の命令が終了する前に新しい命令を発行することができる。また、任意の組合せの機能ユニットが提供されていてもよい。

10

#### 【0047】

[0058] 実行コア300の動作時、フェッチ・ディスパッチユニット302は、命令の格納域（図示していない）から命令を取得し、当該命令をデコードし、そして、当該命令を、関連するオペランド参照又はオペランドデータと一緒に、オペコードとして発行ユニット304にディスパッチする。発行ユニット304は、命令のそれぞれについて、参照先のオペランドを、例えばレジスタファイル324から取得する。命令のオペランドの全てが用意されると、発行ユニット304は、オペコード及びオペランドをDFMAユニット320又はDFMA以外の機能ユニット322に送ることによって、その命令を発行する。発行ユニット304は、与えられた命令を実行するための適切な機能ユニットを、オペコードを使用して選択することが好適である。フェッチ・ディスパッチユニット302及び発行ユニット304は、従来のマイクロプロセッサのアーキテクチャ及び技術を使用して実施することができ、その詳細な説明については、本発明を理解する上で重要ではないため省略する。

20

#### 【0048】

[0059] DFMAユニット320及びDFMA以外の機能ユニット322は、オペコード及び関連するオペランドを受け取り、それらのオペランドに対して、指定された演算を実行する。結果のデータは、レジスタファイル324（又は別の転送先）にデータ転送経路326を介して転送することのできる結果値の形式で提供される。レジスタファイル324は、いくつかの実施形態においては、特定のスレッドに割り当てられる区域を有するローカルレジスタファイルと、複数のスレッド間でのデータの共有を可能にするグローバルレジスタファイル、とを含んでいる。レジスタファイル324は、プログラムの実行時に、入力データ、中間結果、及びその他のデータを格納する目的に使用することができる。レジスタファイル324の具体的な実施形態については、本発明において重要ではない。

30

#### 【0049】

[0060] 一実施形態においては、コア300はマルチスレッド化されており、例えば、スレッドのそれぞれに関連付けられる現在の状態情報を維持することによって、最大数（例えば、384個、768個）までのスレッドを同時に実行することができる。コア300は、例えば、あるクロックサイクルにおいて、頂点スレッドからのプログラム命令を発行した後、別の頂点スレッドからの、又は別のタイプのスレッド（例えば、ジオメトリスレッド、ピクセルスレッドなど）からのプログラム命令を発行することができるよう、一つのスレッドから別のスレッドに迅速に切り替えるように設計されていることが好適である。

40

#### 【0050】

[0061] 図3の実行コアは例示を目的としており、変形及び変更が可能であることが理解されるであろう。プロセッサには任意の数のコアを含めることができ、コアには任意の数の機能ユニットを含めることができる。フェッチ・ディスパッチユニット302及び発行

50

ユニット304は、任意の望ましいマイクロアーキテクチャとして、例えば、スケーラアーキテクチャ、スーパースケーラアーキテクチャ、又はベクトルアーキテクチャを実施することができ、インオーダー又はアウトオブオーダーの命令発行方式、投機的実行モード、単一命令複数データ(SIMD)命令発行方式などを必要に応じて採用する。いくつかのアーキテクチャにおいては、発行ユニットは、複数の機能ユニットを対象とする複数のオペコード及びオペランドを含むロング命令ワード、又は、一つの機能ユニットを対象とする複数のオペコード及び/又はオペランドを含むロング命令ワードを受け取る、又は発行する、又は受け取って発行することができる。いくつかのアーキテクチャにおいては、実行コアは、例えばSIMD命令を実行するための並列に動作可能な、機能ユニットそれぞれの複数のインスタンスを含むことができる。さらに、実行コアは、パイプライン化された一連の機能ユニットを含むことができ、この場合、一つのステージにおける機能ユニットからの結果は、レジスタファイルに直接転送されるのではなく、後のステージにおける機能ユニットに転送される。このような構成の機能ユニットは、一つのロング命令ワード又は複数の個別の命令によって制御することができる。

10

## 【0051】

[0062]さらに、本発明の教示内容にアクセスするこの技術分野における通常の技能を有する者には、DFMAユニット320を任意のマイクロプロセッサの中の機能ユニットとして実施することができ、グラフィックスプロセッサ又は何らかの特定のプロセッサ、或いは実行コアのアーキテクチャには限定されないことが認識されるであろう。例えば、DFMAユニット320を、汎用並列処理ユニット(general-purpose parallel processing unit)又は汎用CPUにおいて実施することができる。

20

## 【0052】

## C. DFMAユニットの概要

[0063]本発明の一実施形態によると、実行コア300は、DFMAユニット320を含んでおり、当該DFMAユニット320は、3種類の演算、すなわち、倍精度算術演算、比較演算、倍精度形式とそれ以外の形式との間の形式変換、を実行する。

20

## 【0053】

[0064]DFMAユニット320は、倍精度浮動小数点形式における入力及び出力を扱い、変換演算においては、倍精度以外の浮動小数点形式又は固定小数点形式における入力及び出力を扱うことが好適である。演算によってオペランドの形式が異なっていてもよい。DFMAユニット320の実施形態について説明する前に、代表的な形式について定義しておく。

30

## 【0054】

[0065]本明細書において使用する「fp32」は、IEEE754規格の单精度浮動小数点形式を意味し、この形式においては、正規の浮動小数点数が、符号ビットと、8個の指数ビットと、23個の仮数部ビットとによって表される。 $2^{-126} \sim 2^{127}$  の範囲内の指数が1~254の整数を使用して表されるように、指数は127だけプラス方向にバイアスされる。「正規」数の場合、23個の仮数部ビットは、24ビットの仮数のうちの小数部分として解釈され、整数部分として1が暗黙的に含まれている(本明細書においては、用語「仮数部」は、先頭の1が暗黙的に含まれているときに使用しているのに対し、「仮数」は、先頭の1が明示的に含まれている(該当時)ことを表す目的で使用している)。

40

## 【0055】

[0066]本明細書において使用する「fp64」は、IEEE754規格の倍精度浮動小数点形式を意味し、この形式においては、正規の浮動小数点数が、符号ビットと、11個の指数ビットと、52個の仮数部ビットとによって表される。 $2^{-1022} \sim 2^{1023}$  の範囲内の指数が1~2046の整数を使用して表されるように、指数は1023だけプラス方向にバイアスされる。「正規」数の場合、52個の仮数部ビットは、53ビットの仮数のうちの小数部分として解釈され、整数部分として1が暗黙的に含まれている。

50

## 【0056】

[0067]本明細書において使用する「f p 1 6」は、グラフィックスにおいて一般的に使用される「半精度」浮動小数点形式を意味し、この形式においては、正規の浮動小数点数が、符号ビットと、5個の指數ビットと、10個の仮数部ビットとによって表される。 $2^{-14} \sim 2^{15}$  の範囲内の指數が1～30の整数を使用して表されるように、指數は15だけプラス方向にバイアスされる。「正規」数の場合、10個の仮数部ビットは、11ビットの仮数のうちの小数部分として解釈され、整数部分として1が暗黙的に含まれている。

## 【0057】

[0068]f p 1 6 形式、f p 3 2 形式、及び f p 6 4 形式においては、指數ビット全てが0である数を非正規数（又は「デノーマル」）と称し、仮数における暗黙的な先頭の1を持たないものとして解釈される。このような数は、例えば、計算におけるアンダーフローを表すことができる。指數ビット全てが1であり、仮数部ビット全てが0である（正又は負の）数は、（正又は負の）無限大（INF）と称する。この数は、例えば、計算におけるオーバーフローを表すことができる。指數ビット全てが1であり、仮数部ビットが0以外である数は、非数（NaN）と称し、例えば、定義されていない値を表す目的に使用することができる。ゼロ（0）も特殊な数とみなされ、指數ビット及び仮数部ビットの全てが0にセットされていることによって表される。ゼロはどちらの符号を持つこともでき、従って、正のゼロ及び負のゼロが許可される。

## 【0058】

[0069]固定小数点形式は、本明細書においては、形式が符号付きであるか符号なしであるかを示す先頭の「s」又は「u」と、ビットの総数を表す数（例：16、32、64）とによって指定する。従って、s 3 2 は符号付き32ビット形式を意味し、u 6 4 は符号なし64ビット形式を意味し、他も同様である。符号付き形式の場合、2の補数表現を使用することができる。本明細書において使用している全ての形式において、最上位ビット（MSB）はビットフィールドの左端であり、最下位ビット（LSB）は右端である。

## 【0059】

[0070]なお、これらの形式は、本明細書においては例示を目的として定義及び使用しており、DFMAユニットは、本発明の範囲から逸脱することなく、これらの形式又はそれ以外の形式の任意の組合せをサポートすることができることを理解されたい。具体的には、「単精度」及び「倍精度」は、現在定義されている標準形式に限定されず、任意の二つの異なる小数点形式を意味することができることを理解されたい。倍精度形式（例：f p 6 4）は、より広い範囲の浮動小数点数を表し、及び／又は、より高い精度の浮動小数点数を表す関連する単精度形式（例：f p 3 2）よりも多くの数のビットを使用する任意の形式を意味する。同様に、「半精度」は、一般的には、より狭い範囲の浮動小数点数を表し、及び／又は、より低い精度の浮動小数点数を表す、関連する単精度形式よりも少ないビットを使用する形式を意味することができる。

## 【0060】

[0071]次に、本発明によるDFMAユニット320の実施形態について説明する。図4は、DFMAユニット320のこの実施形態によって実行することのできる、倍精度の算術演算、比較演算、及び形式変換演算を一覧表示する表400である。

## 【0061】

[0072]セクション402は、算術演算を一覧表示している。加算（ADD）は、f p 6 4 の二つの入力A及びCを加算し、f p 6 4 の和A + Cを返す。乗算（DMUL）は、f p 6 4 の二つの入力A及びBを乗算し、f p 6 4 の積A \* Bを返す。融合型積和演算（DFMA）は、f p 6 4 の三つの入力A, B, 及びCを受け取り、A \* B + Cを計算する。この演算は、積A \* Bが、Cに加算される前に丸められないことにおいて「融合型（fused）」である。正確な値A \* Bを使用することにより、精度が向上し、浮動小数点算術演算の近い将来の規格であるIEEE754Rに準拠する。

10

20

30

40

50

## 【0062】

[0073]セクション404は、比較演算を一覧表示している。最大値演算(DMAX)は、fp64のオペランドA及びオペランドBのうちの大きい方を返し、最小値演算(DMIN)は、二つのオペランドのうちの小さい方を返す。二項テスト演算(DSET)は、倍精度のオペランドA及びオペランドBに対して、複数の二項関係テスト(binary relationship tests)のうちの一つを実行し、そのテストが満たされているかを示すブール値を返す。この実施形態においては、テストすることのできる二項関係としては、より大きい(A > B)、より小さい(A < B)、等しい(A = B)、順序付けできない(A ? B、これは、A又はBのいずれかがNaNである場合に真である)、さらには、否定(例:A = B)、及び様々な組合せテスト(A?B、A < > B、A ? = Bなど)が挙げられる。10

## 【0063】

[0074]セクション406は、形式変換演算及び丸め演算を一覧している。この実施形態においては、DFMAユニット320は、fp64形式の数を、別の64ビット形式又は32ビット形式の数に変換する、又はその逆に変換することができる。D2F演算は、オペランドAをfp64からfp32に変換し、F2Dは、オペランドAをfp32からfp64に変換する。D2I演算は、オペランドAを、fp64から、s64、u64、s32、及びu32のうちのいずれかの形式に変換する。変換後の形式を特定するのに個別のオペコードを使用することができます理解されたい。I2D演算は、整数オペランドCを、s64、u64、s32、及びu32のうちのいずれかの形式からfp64形式に変換する。この場合も、変換前の形式を識別するのに個別のオペコードを使用することができます理解されたい。この実施形態においては、倍精度形式への変換及び倍精度形式からの変換の全てがDFMAユニット320によってサポートされる。DFMAではない機能ユニットは、他の形式変換(例えば、fp32形式とfp16形式との間、fp32形式と整数形式との間)を実行することができます。20

## 【0064】

[0075]D2D演算は、fp64のオペランドに丸め演算(例えば、IEEE丸めモード)を適用する目的に使用される。これらの演算は、fp64のオペランドを、fp64形式で表される整数値に丸める。一実施形態においては、サポートされるD2D演算として、切捨て(0の方向に丸める)、シーリング(+無限大の方向に丸める)、フロア(-無限大の方向に丸める)、最近接(最も近い整数に切り上げる又は切り捨てる)が挙げられる。30

## 【0065】

[0076]この実施形態においては、DFMAユニット320は、より高度な数学関数(例えば、除算、剰余、平方根)については、直接的なハードウェアサポートを提供しない。しかしながら、DFMAユニット320を使用して、ソフトウェアベースでのこれらの演算の実施を高速化することができる。例えば、除算するための一つの一般的な方法では、商 $q = a / b$ が推定され、次いで、 $t = q * b - a$ を使用してその推定がテストされる。 $t$ が0であれば、商 $q$ が正しく求められている。 $0$ でない場合、 $t$ の大きさを用いて推定した商 $q$ が修正され、 $t$ が0になるまでテストが繰り返される。各反復のテスト結果 $t$ は、1回のDFMA演算( $A = q$ 、 $B = b$ 、 $C = -a$ )を使用して正確に計算することができる。同様に、平方根の場合、一つの一般的な方法では、 $r = a^{1/2}$ が推定され、次いで、 $t = r * r - a$ が計算され、その推定がテストされ、 $t$ が0でなければ $r$ が修正される。この場合も、各反復のテスト結果 $t$ は、1回のDFMA演算( $A = B = r$ 、 $C = -a$ )を使用して正確に計算することができる。40

## 【0066】

[0077]第II節及び第III節では、図4に示した演算の全てを実行することのできるDFMAユニット320について説明する。第II節では、DFMAユニット320の回路構造について説明し、第III節では、その回路構造を使用して、図4に一覧した演算を実行する方法について説明する。なお、本明細書に説明するDFMAユニット320は50

例示を目的としており、異なる機能の組合せを、回路ブロックの適切な組合せを使用してサポートすることができることを理解されたい。

### 【0067】

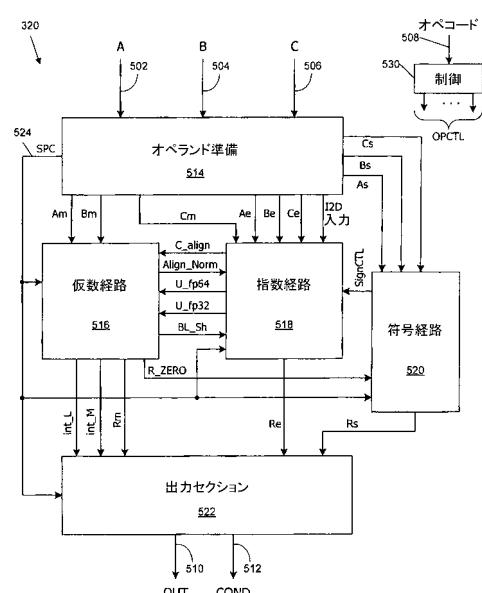

#### I I . D F M A ユニットの構造

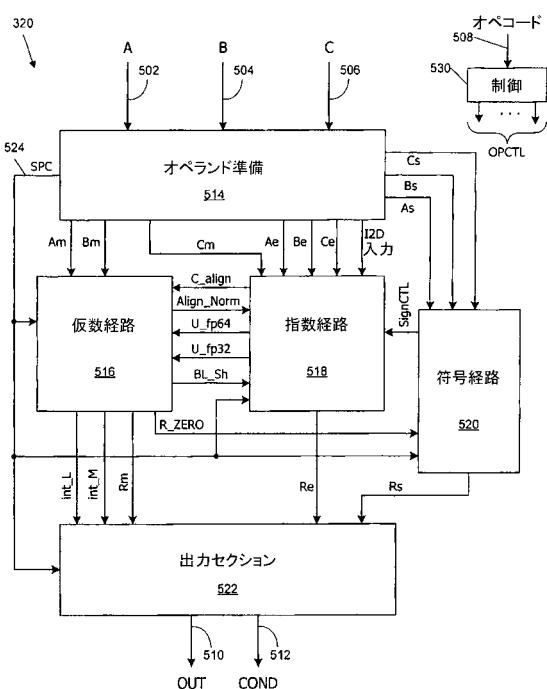

[0078] 図5は、図4に示した演算の全てをサポートする本発明の実施形態によるD F M A ユニット320の単純化したブロック図である。この実施形態においては、D F M A ユニット320は、全ての演算に使用されるマルチステージパイプラインを実施している。D F M A ユニット320は、プロセッササイクルのそれぞれにおいて、(例えば、図3の発行ユニット304から)三つの新しいオペランド( $A_0, B_0, C_0$ )を、オペランド入力経路502, 504, 506を介して受け取り、実行すべき演算を示すオペコードを、オペコード経路508を介して受け取ることができる。この実施形態においては、演算は、図4に示した任意の演算とすることができます。オペコードは、演算のみならず、オペランドの入力形式と、結果に使用する出力形式(入力形式と同じ形式又は異なる形式)とを示すことが好適である。なお、図4に示した演算は、当該演算に関連付けられた複数のオペコードを有することができることに留意されたい。例えば、出力がs64であるD2Iのための一つのオペコードと、出力がs32であるD2Iのための別のオペコードとが存在し得る。

10

### 【0068】

[0079] D F M A ユニット320は、演算のそれぞれを全てのパイプラインステージを通じて処理し、64ビット(特定の形式変換演算の場合には32ビット)の結果値(O U T)を信号経路510上に生成し、対応する条件コード(C O N D)を信号経路512上に生成する。これらの信号は、アーキテクチャに応じて、例えば、図3に示したようにレジスタファイル324、発行ユニット304、又はプロセッサコアの別の要素に転送され得る。一実施形態においては、パイプラインステージは、プロセッササイクルに対応する。別の実施形態においては、一つのステージが複数のプロセッササイクルを含み得る。さらに、パイプライン内の複数の異なる経路は、並列に動作することが有利である。

20

### 【0069】

[0080] 第I I . A節では、D F M A パイプラインの概要について説明し、第I I . B - I節では、各セクションの回路ブロックについて詳しく説明する。

30

### 【0070】

#### A . D F M A パイプライン

[0081] 最初に、パイプラインについて、D F M A 演算時に回路ブロックがどのように使用されるかに関連して説明する。オペランド準備ブロック514は、(まだf p 64形式ではないオペランドについて)オペランドのフォーマッティングと、特殊数の検出とを実行する。さらに、オペランド準備ブロック514は、入力されるf p 64のオペランドから、仮数ビット( $A_m, B_m, C_m$ )と、指數ビット( $A_e, B_e, C_e$ )と、符号ビット( $A_s, B_s, C_s$ )とを取り出す。一実施形態においては、オペランドの無効な組合せは存在しない。演算において使用されないオペランドは、単に無視することができる。

### 【0071】

[0082] 仮数経路516は、仮数 $A_m$ と仮数 $B_m$ の積を計算する。これと並列に、指數経路518は、指數 $A_e$ 及び指數 $B_e$ を使用して、積 $A * B$ とオペランド $C$ との間の相対的な位置合わせ量を求め、オペランド $C$ 用の位置合わせ後の仮数( $C_{align}$ )を仮数経路516に供給する。仮数経路516は、 $C_{align}$ を積 $A_m * B_m$ に加算し、次いで、結果を正規化する。仮数経路516は、この正規化に基づいて、位置合わせ信号(A L I G N\_N O R M)を指數経路518に戻し、指數経路518は、このA L I G N\_N O R M信号と、指數 $A_e, B_e$ 、及び $C_e$ とと一緒に使用して、最終結果の指數を求める。

40

### 【0072】

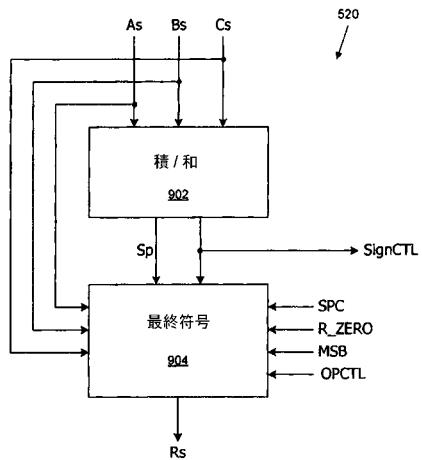

[0083] 符号経路520は、オペランド準備ブロック514から符号ビット $A_s, B_s$ 、及び $C_s$ を受け取り、結果の符号を求める。仮数経路516は、結果が0である場合を検

50

出し、結果ゼロ（R ZERO）を符号経路520に提供する。

【0073】

[0084]出力セクション522は、仮数経路516からの結果の仮数Rmと、指数経路518からの結果の指数Reと、符号経路520からの結果の符号Rsとを受け取る。さらに、出力セクション522は、オペランド準備ブロック514から特殊数信号（SPC）を受け取る。出力セクション522は、これらの情報に基づいて、出力経路510に提供することができるよう最終結果（OUT）をフォーマッティングし、条件コード（COND）を出力経路512上に生成する。条件コード（結果よりも少ない数のビットを含んでいることが好適である）は、結果の特性に関する一般情報を伝える。例えば、条件コードは、結果が正である、負である、0である、NaNである、無限大である、或いは非正規であるかを示すビットを含み得る。この技術分野において公知であるように、結果と一緒に条件コードが提供される場合、その結果を使用する下流の要素は、場合によっては、その処理において結果自体ではなく条件コードを使用することができる。いくつかの実施形態においては、演算の実行時に例外又はその他のイベントが発生したことを、条件コードを使用して示すことができる。別の実施形態においては、条件コードを完全に省くことができる。

10

【0074】

[0085]なお、「仮数経路」、「指数経路」などの名称は、特定の演算（例：DFMA）時に経路それぞれの様々な回路ブロックによって実行される機能を示唆するものであるが、任意の内部データ経路上の回路ブロックを、演算に依存する方式で様々な用途に利用することができることを理解されたい。例については後述する。

20

【0075】

[0086]データ経路に加えて、DFMAユニット320は、制御経路（図5には制御ブロック530として表してある）も提供する。制御ブロック530は、オペコードを受け取り、オペコードに依存する様々な制御信号（この図ではまとめて「OPCTL」として表してある）を生成する。この制御信号は、パイプラインを通じたデータ伝搬と同期して回路ブロックのそれぞれに伝搬され得る（様々な回路ブロックまでのOPCTL信号の接続は図5には示していない）。後述するように、OPCTL信号を使用して、DFMAユニット3220の様々な回路ブロックの動作をオペコードに応答して有効化する、無効化する、及びその他の制御を行うことにより、複数の異なる演算を同じパイプライン要素を使用して実行することを可能とする。本明細書において言及する様々なOPCTL信号は、オペコード自身を含み得るものであり、又は、例えば、制御ブロック530において実施されている組合せ論理回路によってオペコードから導かれる何らかの別の信号を含み得るものである。いくつかの実施形態においては、制御ブロック530は、いくつかのパイプラインステージにおける複数の回路ブロックを使用して実施することができる。なお、一つの演算時に複数の異なるブロックに提供されるOPCTL信号は、同じ信号、又は異なる信号とすることを理解されたい。この技術分野における通常の技能を有する者には、本開示に基づいて、適切なOPCTL信号を構築することができるであろう。

30

【0076】

[0087]一つのステージの複数の回路ブロックに要求される処理時間は、回路ブロックごとに異なることがある、一つのステージに要求される時間は、演算によって異なり得ることに留意されたい。従って、DFMAユニット320は、一つのパイプラインステージから次のステージまでの複数の異なる経路上のデータ伝搬を制御する目的で、様々なタイミング・同期回路（図5には示していない）を含むことも可能である。また、任意の適切なタイミング回路（例：ラッチ、送信ゲート）が使用されてもよい。

40

【0077】

A. オペランドの準備

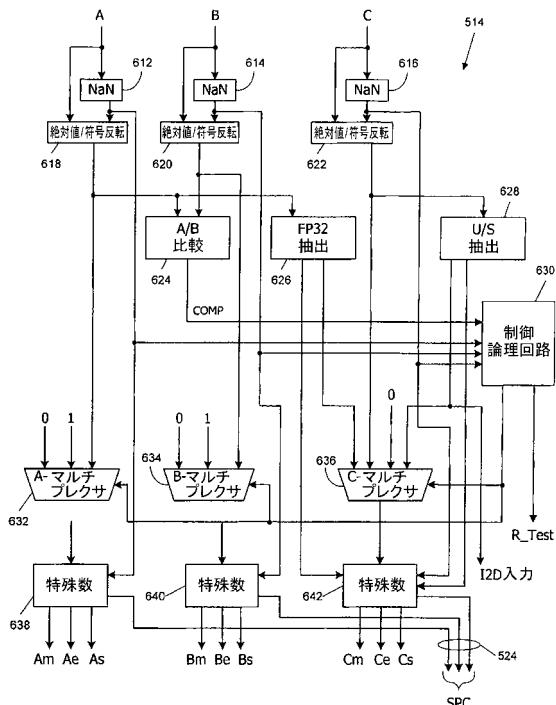

[0088]図6は、本発明の実施形態によるオペランド準備ブロック514のブロック図である。オペランド準備ブロック514は、入力オペランドA, B, 及びCを受け取り、仮数部分（Am, Bm, Cm）を仮数経路516に提供し、指数部分（Ae, Be, Ce）

50

を指数経路 518 に提供し、符号ビット (A s , B s , C s ) を符号経路 520 に提供する。

#### 【0078】

[0089] オペランド A , B , 及び C は、それぞれの NaN 検出ブロック 612 , 614 , 616 と、それぞれの絶対値 / 符号反転ブロック 618 , 620 , 622 において受け取られる。NaN 検出ブロック 612 , 614 , 616 のそれぞれは、受け取ったオペランドが NaN ( 指数ビット全てが 1 であり、仮数部ビットが 0 以外である ) であるかを判定し、対応する制御信号を生成する。

#### 【0079】

[0090] 絶対値 / 符号反転ブロック 618 , 620 , 622 は、O P C T L 信号 ( 図示していない ) に応答してオペランドの符号ビットを反転させる目的に使用することができる。例えば、図 4 に一覧表示した演算において、オペランドの負数又はオペランドの絶対値を使用することが指定されることがある。ブロック 618 , 620 , 622 は、符号ビットを反転させてオペランドの符号を反転する、又は符号ビットを負でない状態 ( I E E E 754 形式の場合には 0 ) に強制することができる。入力オペランドが NaN である場合、対応する絶対値 / 符号反転ブロック 618 , 620 , 622 は、その NaN を更に「クワイエット型にし」 ( 例えば、仮数部の先頭ビットを 1 にセットすることによる ) 、符号ビットをそのままにする。絶対値 / 符号反転ブロック 618 , 620 , 622 は、それらの出力をオペランド選択マルチプレクサ 632 , 634 , 636 に提供する。

10

#### 【0080】

[0091] 倍精度算術演算の場合、絶対値 / 符号反転ブロック 618 によって生成されるオペランド A , B , 及び C を直接的に使用することができる。比較演算の場合、A / B 比較回路 624 がオペランド A とオペランド B とを比較する。一実施形態においては、絶対値 / 符号反転ブロック 620 がオペランド B の符号を反転し、A / B 比較回路 624 が、A と -B との和を、これらがあたかも固定小数点数であるかのように計算する。結果が正であれば A が B よりも大きく、結果が負であれば A が B よりも小さく、結果が 0 であれば A は B に等しい。さらに、A / B 比較回路 624 は、NaN 検出回路 612 及び 614 からの NaN 情報を受け取ることができる ( これらの経路は図 6 には示していない ) 。 A 又は B のいずれか ( 又は双方 ) が NaN であるならば、A 及び B は「順序付けできない」。結果の情報は制御論理回路 630 に提供される。制御論理回路 630 は、結果情報を信号 R\_T\_E\_S\_T として出力セクション 522 に提供し、更に、制御信号をオペランド選択マルチプレクサ 632 , 634 , 636 に提供する。

20

30

#### 【0081】

[0092] 形式変換オペランドの場合、入力は f p 64 形式ではないことがある。f p 32 抽出回路 626 は、F2D 演算時にアクティブである。f p 32 抽出回路 626 は、オペランド A を受け取って、入力が f p 32 の非正規数であるかのテスト全てを実行する。さらに、f p 32 抽出回路 626 は、受け取ったオペランドの仮数部フィールドを 23 ビットから 52 ビットに拡張する ( 例えば、末尾の 0 を追加することによる ) 。f p 32 抽出回路 626 は、f p 32 の 8 ビットの指数を 11 ビットに拡張し、指数のバイアスを 127 から 1023 に増大させる ( 例えば、f p 32 の指数に 896 を加えることによる ) 。

40

#### 【0082】

[0093] 符号なし / 符号付き ( U / S ) 抽出回路 628 は、I2D 演算時にアクティブである。U / S 抽出回路 628 は、u32, s32, u64, s64 のいずれかの形式の固定小数点オペランド C を受け取り、f p 64 に変換することができるよう にそれを準備する。U / S 抽出回路 628 は、固定小数点オペランドを、1 の補数 ( 又は 2 の補数 ) の形式から符号・絶対値形式 ( sign-magnitude form ) に変換し、オペランドが仮数部フィールドにおいて桁が合うように先頭又は最後に 0 を付加する。U / S 抽出回路 628 は、自身の出力をオペランド選択マルチプレクサ 636 に提供し、さらに、I2D 入力信号として指数経路 518 に提供する。

#### 【0083】

50

[0094]オペランド選択マルチプレクサ 632, 634, 636 は、制御論理回路 630 からの信号に応答して、オペランド A, B, C を選択する。オペランド選択マルチプレクサ 632 は、絶対値 / 符号反転回路 618 からのオペランド A と、(fp64 形式で表現されている)一定値 0.0 及び 1.0との間での選択を行う。DMUL 演算及びDFMA 演算の場合、オペランド A が選択される。DMIN (DMAX) 演算の場合、A < B (A > B) であればオペランド A が選択され、そうでなければ 1.0 が選択される。DADD 演算及びI2D 演算の場合、0.0 が選択される。

#### 【0084】

[0095]オペランド選択マルチプレクサ 634 は、絶対値 / 符号反転回路 620 からのオペランド B と、(fp64 形式で表現されている)一定値 0.0 及び 1.0との間での選択を行う。DMUL 演算及びDFMA 演算の場合、オペランド B が選択される。DMIN (DMAX) 演算の場合、B < A (B > A) であればオペランド B が選択され、そうでなければ 1.0 が選択される。DADD 演算及びI2D 演算の場合、0.0 が選択される。

10

#### 【0085】

[0096]オペランド選択マルチプレクサ 636 は、絶対値 / 符号反転回路 622 からのオペランド C と、fp32 抽出回路 626 からの抽出された fp32 値と、U/S 抽出回路 628 からの抽出された符号なし又は符号付き整数値と、(fp64 形式で表現されている)一定値 0.0との間での選択を行う。DADD 演算及びDFMA 演算の場合、オペランド C が選択される。DMUL 演算及び比較演算の場合、一定値 0.0 が選択される。F2D 演算の場合、fp32 抽出回路 626 からの抽出された fp32 値が選択され、I2D 演算の場合、U/S 抽出回路 628 からの抽出された u/s 値が選択される。

20

#### 【0086】

[0097]選択マルチプレクサ 632, 634, 636 によって選択されたオペランド A, B, 及び C は、特殊数検出回路 638, 640, 642 に提供される。fp64 のオペランドの場合、特殊数検出回路 638, 640, 642 は、全ての特殊数条件（非正規、NaN、無限大、0を含む）を検出する。F2D 演算の場合、特殊数検出回路 642 は、fp32 抽出回路 626 から経路 644 を介して fp32 特殊数情報を受け取る。特殊数検出回路 638, 640, 642 のそれぞれは、オペランドが特殊数であるか否かと、特殊数であるならばそのタイプとを示す特殊数信号 (SPC) を生成する。特殊数信号 SPC は、図 5 に示したように信号経路 524 を通じて出力セクション 522 に提供される。特殊数検出回路には、一般的に従来の設計のものを使用することができる。代替の一実施形態においては、（回路 612, 614, 及び 616 によって実行される）NaN 検出は、回路 638, 640, 642 では繰り返されない。代わりに、特殊数検出回路 638, 640, 642 のそれぞれは、NaN 検出回路 612, 614, 及び 616 のうちの対応する回路から NaN 信号を受け取り、その信号を使用して、オペランドが NaN であるかを判定する。

30

#### 【0087】

[0098]特殊数検出回路 638, 640, 及び 642 は、いずれかの特殊数が検出されるか否かにかかわらず、オペランドを、仮数ビットと、指数ビットと、符号ビットとに分ける。特殊数検出回路 638 は、オペランド A の仮数の部分 (Am) を仮数経路 516 (図 5) に提供し、オペランド A の指数の部分 (Ae) を指数経路 518 に提供し、符号ビット (As) を符号経路 520 に提供する。特殊数検出回路 640 は、オペランド B の仮数の部分 (Bm) を仮数経路 516 に提供し、オペランド B の指数の部分 (Be) を指数経路 518 に提供し、符号ビット (Bs) を符号経路 520 に提供する。特殊数検出回路 642 は、オペランド C の仮数の部分 (Cm) 及び指数の部分 (Ce) を指数経路 518 に提供し、符号ビット (Cs) を符号経路 520 に提供する。いくつかの実施形態においては、特殊数検出回路 638, 640, 642 は、仮数 Am, Bm, Cm に先頭の 1 を付加する（数が非正規であるときを除く）。

40

#### 【0088】

B. 指数経路

50

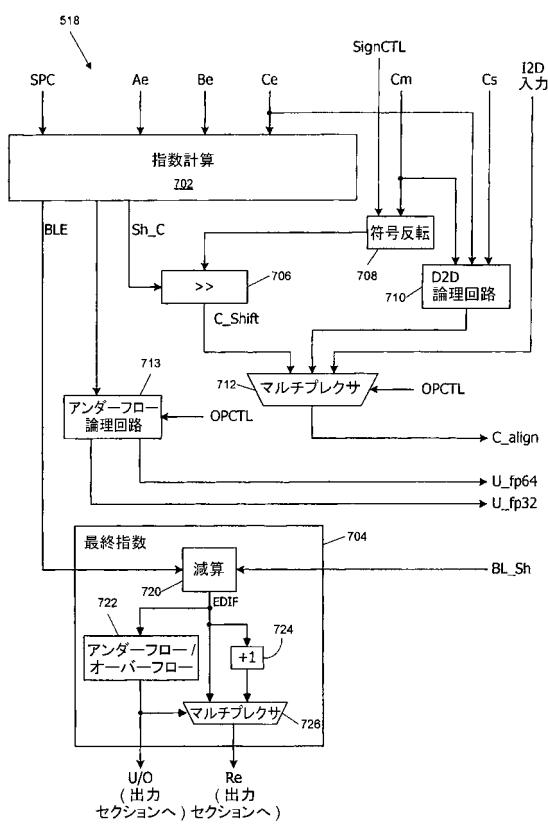

[0099] 図 7 は、本発明の実施形態による指數経路 518 のブロック図である。

#### 【0089】

[0100] 指数計算回路 702 は、オペランド準備ブロック 514 (図 5) から指數ビット Ae, Be, 及び Ce を受け取り、DFMA 結果の  $A * B + C$  のブロック指數を計算する。従来の指数計算回路が使用されてもよい。一実施形態においては、全てのオペランドが正規数である場合、指数計算回路は、Ae と Be とを加算し、fp64 の指數のバイアス (1023) を減算して積 A \* B の指數を求め、次いで、この積の指數と指數 Ce のうちの大きい方を、DFMA 結果のブロック指數 (BLE) として選択する。このブロック指數 BLE は、下流の最終指数計算回路 704 に提供される。一以上のオペランドが非正規数 (特殊数信号 SPC によって示される) である場合、適切な論理回路を使用してブロック指數 BLE を求めることができる。別の実施形態においては、特殊数が含まれる演算における指數の決定は、後述するように出力セクション 522 において扱われる。

10

#### 【0090】

[0101] さらに、指数計算ブロック 702 は、Cm と積 Am \* Bm の小数点位置が合うようにオペランド C の仮数を実質的に左又は右にシフトさせる量を求める。この量は、制御信号 Sh\_C としてシフト回路 706 に提供される。この制御信号は、Cm を右シフトすることによって、実質的な左シフト又は右シフトを必ず達成することができるよう、Cm の余分なパディングを考慮することが好適である。

20

#### 【0091】

[0102] 仮数 Cm は符号反転回路 708 に提供され、符号反転回路 708 は、条件付きで、すなわち、C と積 Am \* B との間に相対的マイナス符号 (relative minus sign) が存在している場合に、(例えば、1 の補数による符号反転を使用して) Cm の符号を反転する。相対的マイナス符号は、後述するように符号経路 520 において検出され、符号制御信号 Sign CTL は、相対的マイナス符号が存在しているかを示す。符号反転回路 708 の出力 (Cm 又は ~Cm のいずれか) は、シフト回路 706 に提供される。

20

#### 【0092】

[0103] 一実施形態においては、シフト回路 706 は 217 ビットのバレルシフターであり、54 ビットの仮数 Cm を最大 157 ビットだけ右シフトすることができる。Cm を右シフトする量は、Sh\_C 信号によって決まる。仮数 Cm は、必要な距離だけ右シフトすることができるように位置合わせされた状態でシフターに入力されることが好適である。217 ビットというサイズは、53 ビットの仮数 Cm (及びガードビットとラウンドビット) の全体を、106 ビットの積 Am \* B (及び積のガードビットとラウンドビット) の左又は右に合わせる (106 ビットの積 Am \* B は、217 ビットフィールドの MSB から右に 55 ビットの位置に合わせられる) のに十分な空間が確保されるように選択されている。右シフトによってバレルシフターからはみ出したビットは破棄することができる。別の実施形態においては、フラグビットを使用して、右シフトによってバレルシフターからはみ出したビットの全てが「1」であるかを追跡し、この情報を、後述する丸め演算において使用することができる。

30

#### 【0093】

[0104] 代替実施形態においては、従来のスワップマルチプレクサ (swap mux) を使用して、積 Am \* Bm と Cm との間で大きい方のオペランドを選択することができ、次いで、小さい方のオペランドを右シフトすることができる。

40

#### 【0094】

[0105] D2D 演算の場合、仮数 Cm は D2D 論理回路 710 にも提供される。D2D 論理回路 710 は、仮数 Cm と、指數 Ce と、符号 Cs とを受け取り、整数丸め規則を適用する。一実施形態においては、D2D 論理回路 710 は、2進小数点の位置を指數 Ce に基づいて決定し、次いで、OPCTL 信号 (図示していない) に基づいて選択される丸め規則を適用する。丸めモードは、従来の論理回路を使用して実施することができる。また、任意の組合せの丸めモード (例えば、切捨てモード、シーリングモード、フロアモード

50

、最近接モード、ただしこれらに限定されない)をサポートしてもよい。

#### 【0095】

[0106]選択マルチプレクサ712は、シフトされた仮数C\_Shiftと、D2D論理回路の出力と、U/S抽出回路628(図6)からのI2D入力とを受け取り、これらの入力のうちの一つを、OPCTL信号に基づいて、仮数経路516に供給される位置合わせ後の仮数C\_alignとして選択する。倍精度算術演算及び比較演算の場合、オペランドC\_Shiftが選択される。形式変換D2D又はI2Dの場合、C\_Shift以外の該当する入力が選択される。

#### 【0096】

[0107]アンダーフロー論理回路713は、fp64及びfp32の結果における潜在的なアンダーフローを検出するように構成されている。D2F演算以外の演算の場合、アンダーフロー論理回路713は、11ビットのfp64ブロック指数BLEが0であるか、又は、非正規結果が生じうるほど十分に0に近いかを判定する。アンダーフロー論理回路713は、指数が0に達しない範囲で仮数を左シフトすることのできる最大ビット数を、ブロック指数に基づいて求める。この数は、8ビットのアンダーフロー信号U\_fp64として仮数経路516(図8を参照)に提供される。D2F演算の場合、指数は8ビットのfp32の指数として扱われ、アンダーフロー論理回路713は、許容される最大左シフトを求める。この数は、8ビットのアンダーフロー信号U\_fp32として仮数経路516に提供される。

#### 【0097】

[0108]指数経路518は、最終指数計算論理回路704を更に含んでいる。減算回路720には、ブロック指数BLEが提供される。さらに、減算回路720には、仮数経路516からのブロックシフト(BL\_Sh)信号が提供される。このBL\_Sh信号は、後述するように、積Am\*BmをオペランドC\_alignに加算したときのMSBの相殺効果を反映している。減算回路720は、BLEからBL\_Shを減算して差EDIFを求める。アンダーフロー/オーバーフロー回路722は、減算結果EDIFにおけるアンダーフロー又はオーバーフローを検出する。プラス1回路724は、結果のEDIFに1を加算し、マルチプレクサ720は、アンダーフロー/オーバーフロー条件に基づいて、EDIF信号とEDIF+1信号のいずれかを結果の指数Reとして選択する。結果Reとアンダーフロー/オーバーフロー信号(U/O)とが、出力セクション522に提供される。

#### 【0098】

##### C. 仮数経路

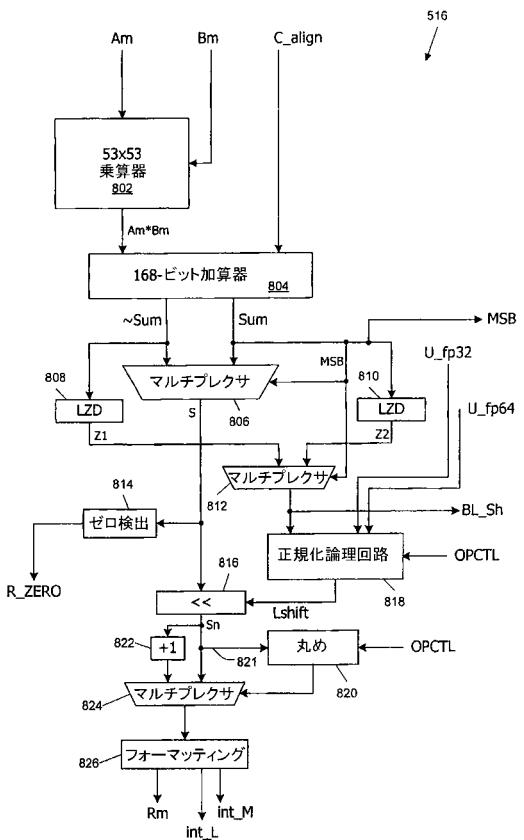

[0109]図8は、本発明の実施形態による仮数経路516のブロック図である。仮数経路516は、オペラントA,B,及びCの仮数に対して積演算及び和演算を実行する。

#### 【0099】

[0110]53×53乗算器802は、(上述した)オペラント準備ブロック514から仮数Am及びBmを受け取り、106ビットの積Am\*Bmを計算する。この積は168ビット加算器804に提供され、加算器804は、位置合わせ後の仮数C\_alignを更に受け取る。バレルシフター706によって使用される217ビットフィールドの末尾部分のビットは破棄することができ、或いは、末尾部分のビットが0でないか、又は全て1であるかを示すフラグビットを維持することができる。加算器804は、出力Sum及び~Sum(和の2の補数)を生成する。マルチプレクサ806は、Sum及び~Sumのいずれかを、和のMSB(符号ビット)に基づいて選択する。選択された和(S)は、ゼロ検出回路814と左シフト回路816とに提供される。ゼロ検出回路814は、選択された和Sが0であるか否かを判定し、対応するR\_ZERO信号を符号経路520に提供する。

#### 【0100】

[0111]さらに、仮数経路516は、和Sを正規化する。LZD回路808,810を使用して、Sum及び~Sumの双方について先頭のゼロの検出(LZD)が並列に実行さ

10

20

30

40

50

れる。L Z D 回路 808, 810 のそれぞれは、自身の入力における先頭のゼロの数を示す L Z D 信号 (Z1, Z2) を生成する。L Z D マルチプレクサ 812 は、和の M S B (符号ビット)に基づいて、該当する L Z D 信号 (Z1 又は Z2) を選択する。マルチプレクサ 806 によって Sum が選択されるならば Z2 を選択し、マルチプレクサ 806 によって ~Sum が選択されるならば Z1 を選択する。選択された L Z D 信号は、ブロックシフト信号 B L\_S h として指数経路 518 に提供され、指数経路 518 において、当該 L Z D 信号が使用されて、上述したように結果の指数が調整される。

#### 【0101】

[0112] 正規化論理回路 818 は、和 S の正規化シフトを決める左シフト量 L s h i f t を選択する。正規数の結果の場合、左シフト量は、52ビットの仮数部（及びガードビットとラウンドビット）を残して先頭の 1 が仮数フィールドの外にシフトされるだけ十分に大きいことが好適である。しかしながら、場合によっては、結果は、f p 64 非正規数又は f p 32 非正規数として表現すべきアンダーフローである。一実施形態においては、D 2 F 以外の演算の場合、正規化論理回路 818 は、B L\_S h がアンダーフロー信号 U\_f p 64 よりも大きくない限りは、L Z D マルチプレクサ 812 からの出力 B L\_S h を選択し、B L\_S h がアンダーフロー信号 U\_f p 64 よりも大きい場合、正規化論理回路 818 は、左シフト量として U\_f p 64 を選択する。D 2 F 演算の場合、正規化論理回路 818 は、f p 32 アンダーフロー信号 U\_f p 32 を使用して左シフト量 L s h i f t を制限する。

10

#### 【0102】

[0113] 左シフト回路 816 は、和 S を量 L s h i f t だけ左シフトする。結果の S n は、丸め論理回路 820 と、プラス 1 加算器 822 と、仮数選択マルチプレクサ 824 とに提供される。丸め論理回路 820 は、I E E E 規格の算術演算に対して定義されている四つの丸めモード（最近接、フロア、シーリング、切捨て）を実施することが好適であり、異なるモードにおいては異なる結果が選択され得る。O P C T L 信号又は別の制御信号（図示していない）を使用して、丸めモードの一つを指定することができる。丸め論理回路 820 は、丸めモードと、正規化された和 S n とに基づいて、結果の S n を選択するのか、又はプラス 1 加算器 822 によって計算される S n + 1 を選択するのかを決定する。選択マルチプレクサ 824 は、適切な結果 (S n 又は S n + 1) を選択することによって、丸め論理回路 820 からの制御信号に応答する。

20

#### 【0103】

[0114] マルチプレクサ 824 によって選択された結果は、フォーマッティングブロック 826 に渡される。浮動小数点出力を有する演算の場合、ブロック 826 は、仮数 R m を出力セクション 522 に提供する。和 S は、（整数演算をサポートするため）少なくとも 64 ビット幅であることが好適であり、余分なビットはフォーマッティングブロック 826 によって削除することもできる。D 2 I 演算（整数出力を有する）の場合、フォーマッティングブロック 826 は、結果を、L S B を含む 52 ビットの int\_L フィールドと、M S B を含む 11 ビットの int\_M フィールドとに分ける。R m, int\_L, 及び int\_M は、出力セクション 522 に提供される。

30

#### 【0104】

##### D . 符号経路

[0115] 図 9 は、本発明の実施形態による符号経路 520 のブロック図である。符号経路 520 は、オペランド準備ブロック 514（図 5）からオペランドの符号 A s, B s, 及び C s を受け取る。さらに、符号経路 520 は、仮数経路 516 からの結果ゼロ信号 R\_Zero と、進行中の演算のタイプを示す O P C T L 信号と、オペランド準備ブロック 514 からの特殊数信号 S P C とを受け取る。符号経路 520 は、これらの情報に基づいて、結果の符号を求めて符号ビット R s を生成する。

40

#### 【0105】

[0116] より具体的には、符号経路 520 は、積 / 和回路 902 と最終符号回路 904 とを含んでいる。積 / 和回路 902 は、オペランド準備ブロック 514 から、オペランド A

50

, B , 及び C の符号ビット A s , B s , 及び C s を受け取る。積 / 和回路 902 は、符号ビット A s 及び B s と従来の符号論理規則 ( s i g n l o g i c r u l e s ) とを使用して、積 A \* B の符号 ( S p ) を求め、次いで、この積の符号と符号ビット C s とを比較し、積とオペラント C とが同符号を有するか又は異符号を有するかを判定する。積 / 和回路 904 は、この情報に基づいて、S i g n C T L 信号をアサート又はデアサートし、S i g n C T L 信号が、最終符号回路 904 と、指数経路 518 における符号反転ブロック 708 ( 図 7 ) とに提供される。さらには、積とオペラント C とが同符号を有する場合、最終結果もその符号を有し、積とオペラント C とが異符号を有する場合、結果は、どちらが大きいかによって決まる。

## 【 0106 】

[0117] 最終符号回路 904 は、最終的な符号を決定する上で必要な情報の全てを受け取る。具体的には、最終符号回路 904 は、符号情報 ( 積の符号 S p を含む ) と、積 / 和回路 902 からの S i g n C T L 信号と、符号ビット A s , B s , 及び C s とを受け取る。さらに、最終符号回路 904 は、仮数経路 516 からのゼロ検出信号 R\_Z E R O と、オペラント準備ブロック 514 からの特殊数信号 S P C を受け取る。さらに、最終符号回路 904 は、仮数経路 516 における加算器 804 から和の M S B ( 和が正であるか負であるかを示す ) を受け取る。

## 【 0107 】

[0118] 最終符号回路 904 は、これらの情報に基づいて、従来の符号論理回路を使用して結果の符号ビット R s を決定することができる。例えば、D F M A 演算の場合、符号ビット S p と C s とが同じであるならば、結果もその符号を有する。 S p と C s とが異符号であるならば、仮数経路 516 における加算器 804 が、( A m \* B m ) - C\_a l i g n を計算する。 A m \* B m が C\_a l i g n より大きい場合、加算器 804 は正の結果 S\_u m を計算し、積の符号 S p を選択すべきである。 A m \* B m が C\_a l i g n より小さい場合、加算器 804 は負の結果 S\_u m を計算し、符号 C s を選択すべきである。加算器 804 の出力 S\_u m の M S B は、結果の符号を示しており、この選択を駆動する目的に使用することができる。結果 S\_u m が 0 である場合、R\_Z E R O 信号がアサートされ、最終符号回路 904 は、いずれか適切な符号を選択することができる ( f p 64 形式では 0 は正又は負のどちらでもよい ) 。 D F M A 以外の演算の場合、最終符号回路 904 は、最終的な符号としていずれかのオペラントの符号を通過させることができる。

## 【 0108 】

## E . 出力セクション

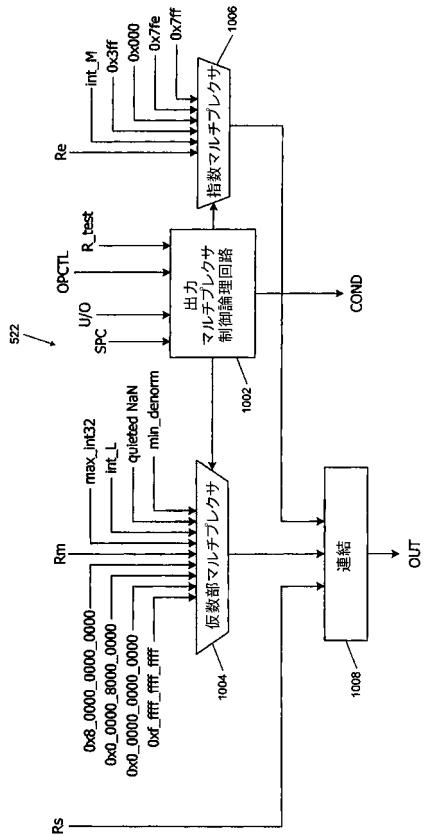

[0119] 図 10 は、本発明の実施形態による D F M A ユニット 320 の出力セクション 522 のブロック図である。

## 【 0109 】

[0120] 出力マルチプレクサ制御論理回路 1002 は、指数経路 518 ( 図 7 ) からのアンダーフロー / オーバーフロー ( U / O ) 信号と、オペラント準備ブロック 514 ( 図 6 ) からの R\_t e s t 信号及び S P C 信号と、進行中の演算のタイプを示す O P C T L 信号とを受け取る。出力マルチプレクサ制御論理回路 1002 は、これらの情報に基づいて、仮数部選択マルチプレクサ 1004 及び指数選択マルチプレクサ 1006 のための選択制御信号を生成する。さらに、出力マルチプレクサ制御論理回路 1002 は、条件コード信号 C O N D ( 例えば、オーバーフロー又はアンダーフロー条件、 N a N 条件、又はその他の条件を示すことができる ) を生成する。いくつかの実施形態においては、条件コードは、 D S E T 演算時にブール結果を伝える目的にも使用される。

## 【 0110 】

[0121] 仮数部選択マルチプレクサ 1004 は、仮数経路 516 からの結果の仮数部 R\_m と、最大 52 ビットの整数出力 ( D 2 I 演算時に使用される ) と、複数の特殊値とを受け取る。特殊値としては、一実施形態においては、1 の 52 ビットフィールド ( D 2 I 演算において 64 ビットの最大整数を表現するために使用される ) 、0 の 52 ビットフィールド ( 0 . 0 又は 1 . 0 が結果である場合に使用される ) 、52 ビットフィールド 0 × 0 \_

10

20

30

40

50

0 0 0 0 \_ 8 0 0 0 \_ 0 0 0 0 ( D 2 I 演算において 32 ビットの最小整数を表現するために使用される)、先頭が 1 である 52 ビットフィールド(内部で生成されるクワイエット型NaNを表すために使用される)、max\_int32 値(例: 0 × 7 f f f f \_ f f f f \_ f f f f ) (D 2 I 演算において 32 ビットの最大整数を表現するために使用される)、クワイエット型NaN 値(オペランド準備ブロック 514 からの、NaN である入力オペランドを通過させるために使用される)、min\_denorm 値(例: 最後のビット位置が 1 ) (アンダーフローの場合に使用される)が挙げられる。演算に応じて、及びオペランドのいずれか又は結果が特殊数であるかに応じて、入力のいずれかを選択することができる。

## 【 0 1 1 1 】

[0122] 指数選択マルチプレクサ 1006 は、指数経路 518 からの結果の指数 Re と、最大 11 個の整数ビット(整数形式の出力の場合の MSB)と、複数の特殊値とを受け取る。特殊値としては、一実施形態においては、0 × 3 ff (fp64 における 1.0 の指数)、0 × 0 0 0 (非正規及び 0.0 の場合の指数)、0 × 7 fe (正規数の fp64 最大指数)、0 × 7 ff (fp64 NaN 又は fp64 無限大の結果の場合)が挙げられる。演算に応じて、及びオペランドのいずれか又は結果が特殊数であるかに応じて、入力のいずれかを選択することができる。

## 【 0 1 1 2 】

[0123] 連結ブロック 1008 は、符号ビット Rs と、マルチプレクサ 1004 によって選択される仮数部ビットと、マルチプレクサ 1006 によって選択される指数ビットとを受け取る。連結ブロック 1008 は、結果を、(例えば、IEEE 754 規格に従って符号、指数、仮数部の順序に)フォーマッティングし、64 ビットの出力信号 OUT を提供する。

## 【 0 1 1 3 】

## F. オペランドのバイパス経路又は通過経路

[0124] D F M A ユニット 320 は、いくつかの実施形態においては、オペランドを修正せずに様々な回路ブロックを伝搬させることのできるバイパス経路又は通過経路を提供する。例えば、いくつかの演算時、乗算器 802 は、入力(例: Am)に 1.0 を乗算して、入力 Am を実質的に通過させる。Am に 1.0 を乗算するのではなく、乗算器 802 の周囲に入力 Am のバイパス経路を提供することができる。このバイパス経路は、Am が加算器 804 への入力に正しいタイミングで到着するように、乗算器 802 と同じ数のクロックサイクルを消費することが有利である。しかしながら、乗算器 802 がバイパスされるとき、乗算器 802 を電力遮断状態又は低電力状態に設定することができ、これによって、回路面積が少し増大することと引き換えに電力消費量が低減する。同様に、いくつかの演算時、加算器 804 を使用して入力(例: C\_align)に 0 を加算し、入力 C\_align を実質的に通過させる。特に、加算器 804 の出力 Sum 及び ~Sum のどちらをマルチプレクサ 806 によって選択すべきかが事前に既知である演算の場合、C\_align に 0 を加算するのではなく、加算器 804 の周囲に入力 C\_align のためのバイパス経路を提供することができる。入力 C\_align を、Sum の経路及び ~Sum の経路のうちの正しい経路にバイパスさせることができる。この場合も、バイパス経路は、タイミングが影響を受けないように、加算器 804 と同じ数のクロックサイクルを消費することが有利である。しかしながら、加算器 804 をバイパスする演算においては、加算器 804 を電力遮断状態又は低電力状態に設定することができるので、電力消費量を低減することができる。

## 【 0 1 1 4 】

[0125] 従って、(後の)第 III 節における演算の説明では、様々なオペランドを特定の回路ブロックにバイパス又は通過させることを言及している。このことは、オペランドに影響を与えない演算(例: 0 を加算する、1.0 を乗算する)を実行するよう介在する回路ブロックを制御して、当該回路ブロックへの入力がそのまま出力として通過されることによって、又は、バイパス経路を使用することによって、達成することができるこ

10

20

30

40

50

理解されたい。さらには、ある回路ブロックの周囲のバイパス経路又は通過経路をたどるとき、以降の回路ブロックにおいては、引き続きそのバイパス経路を必ずしもたどらなくてよい。さらには、一つの回路ブロックにおいて修正された値は、以降の回路ブロックの周囲のバイパス経路をたどることができる。演算時に特定の回路ブロックがバイパスされる場合、その回路ブロックを電力遮断状態に設定して電力消費量を低減する、又は、通常に動作させて、例えば選択マルチプレクサ又はその他の回路を使用することによってその出力を無視させることができる。

#### 【0115】

[0126]本明細書に説明したDFMAユニットは例示を目的としており、変形及び変更が可能であることが理解されるであろう。本明細書に説明した回路ブロックの多くは、従来の機能を提供し、この技術分野において公知である技術を使用して実施することができる。従って、これらのブロックの詳しい説明は省略した。演算回路をブロックに分割する方式は変更することができ、ブロックを組み合わせる、或いはブロックを変更することができる。さらに、パイプラインステージの数と、特定の回路ブロック又は演算を特定のパイプラインステージに割り当てる方式も、変更する、又は別の形態をとることができる。特定の実施形態における回路ブロックの選択及び編成は、サポートする一連の演算に依存し、演算の可能な組合せのそれぞれにおいて、本明細書に説明したブロックの全てが必ずしも要求されるわけではないことが、当業者には認識されるであろう。

10

#### 【0116】

##### I I I . DFMAユニットの演算

20

[0127]DFMAユニット320は、図4に一覧した演算の全てを、上述した回路ブロックを利用して、回路面積の面で効率的にサポートすることが好適である。従って、DFMAユニット320の動作は、少なくともいくつかの側面において、実行される演算に依存する。以下の節では、DFMAユニット320を使用して、図4に一覧した演算のそれぞれを実行する方法について説明する。

#### 【0117】

[0128]なお、浮動小数点例外（例えば、オーバーフロー条件、アンダーフロー条件を含む）は、余分な処理サイクルを必要とすることなくDFMAユニット320の中で扱われることに留意されたい。例えば、入力オペランドがNaN又はその他の特殊数である演算は、図5のオペランド準備ブロック514において検出され、出力セクション522において適切な特殊数出力が選択される。NaN、アンダーフロー、オーバーフロー、又はその他の特殊数が演算の過程において生じた場合、その条件が検出され、出力セクション522において適切な特殊数出力が選択される。

30

#### 【0118】

##### A . 融合型積和演算 (DFMA)

[0129]DFMA演算の場合、DFMAユニット320は、fp64形式のオペランドA0, B0, 及びC0と、DFMA演算を実行することを示すオペコードと、を受け取る。NaN回路612, 614, 616は、選択されるオペランドのいずれか一つ以上がNaNであるかを判定する。絶対値/符号反転回路618, 620, 622は、オペランドのそれぞれについて、必要な場合に符号ビットを反転する（又は反転しない）。オペランド選択マルチプレクサ632, 634, 及び636は、それぞれの絶対値/符号反転回路618, 620, 及び622の出力を選択し、これらの出力を特殊数検出回路638, 640, 642に提供する。特殊数検出回路638, 640, 及び642は、オペランドのそれぞれが特殊数であるかを判定し、該当する特殊数SPC信号を経路524上に生成する。特殊数検出回路638, 640, 及び642は、仮数Am, Bm, 及びCm（正規数の場合は先頭に1が付加されており、非正規数の場合は先頭に0が付加されている）を仮数経路516に提供し、指数Ae, Be, 及びCeを指数経路518に提供し、符号ビットAs, Bs, 及びCsを符号経路520に提供する。

40

#### 【0119】

[0130]A/B比較回路624、fp32抽出回路626、及び、U/S整数抽出回路6

50

28はDFMA演算においては使用されず、これらの回路は、必要に応じて、電力遮断状態又は低電力状態に設定され得る。

#### 【0120】

[0131]符号経路520においては、積/和回路902が、積 $A * B$ が正であるか負であるかを符号ビット $A_s$ 及び $B_s$ から判定し、積の符号 $S_p$ と符号ビット $C_s$ とを比較する。積と $C_s$ とが異符号を有する場合、異符号を示すために $Sig n C T L$ 信号がアサートされ、積と $C_s$ とが同符号を有する場合、 $Sig n C T L$ 信号がデアサートされる。

#### 【0121】

[0132]指數経路518(図7)においては、指數計算ブロック702が、指數 $A_e$ ,  $B_e$ , 及び $C_e$ を受け取る。指數計算ブロック702は、指數 $A_e$ と指數 $B_e$ とを加算し、積 $A * B$ のブロック指數を求め、次いで、この積のブロック指數と指數 $C_e$ のうちの大きい方を、結果のブロック指數 $B_{LE}$ として選択する。さらに、指數計算ブロック702は、積のブロック指數と指數 $C_e$ のうちの小さい方を、二つのうちの大きい方から減算し、対応するシフト制御信号 $S h\_C$ を生成する。アンダーフロー論理回路713は、ブロック指數 $B_{LE}$ がアンダーフロー又は潜在的なアンダーフローに対応しているかを検出し、アンダーフロー信号 $U\_f p 64$ を生成する(DFMA演算時には $U\_f p 32$ 信号は使用されない。)。

10

#### 【0122】

[0133]符号反転ブロック708は、オペランド準備ブロック514からの仮数 $C_m$ と、符号経路520からの $Sig n C T L$ 信号とを受け取る。 $Sig n C T L$ 信号がアサートされている場合、符号反転ブロック708は、相対的マイナス符号を考慮するために仮数 $C_m$ を反転し、反転された $C_m$ をシフト回路706に提供する。アサートされていない場合、符号反転ブロック708は、 $C_m$ を修正せずにシフト回路706に提供する。

20

#### 【0123】

[0134]シフト回路706は、符号反転ブロック708によって提供された仮数 $C_m$ を、シフト制御信号 $S h\_C$ に対応する量だけ右シフトし、シフトされた仮数 $C\_Shift$ を選択マルチプレクサ712に提供する。選択マルチプレクサ712は、シフトされた仮数 $C\_Shift$ を選択し、このシフトされた仮数をオペランド $C\_align$ として仮数経路516に提供する。

30

#### 【0124】

[0135]仮数経路516(図8)においては、乗算器802が、106ビットの積 $A_m * B_m$ を計算し、この積を168ビットの加算器804に提供する。乗算器802の動作は、指數計算ブロック702の動作と並列に行うことができる。

#### 【0125】

[0136]加算器804は、指數経路518の選択マルチプレクサ712からオペランド $C\_align$ を受け取り、入力 $A_m * B_m$ と $C\_align$ とを加算して $Sum$ 及び $\sim Sum$ を求める。 $Sum$ のMSBに基づいて、マルチプレクサ806は、これら出力の一方を最終的な和として選択する。 $Sum$ が正である(MSBが0)ならば $Sum$ が選択され、 $Sum$ が負である(MSBが1)ならば $\sim Sum$ が選択される。LZD回路808及び810は、それぞれ、 $\sim Sum$ 及び $Sum$ における先頭の0の数を求める。マルチプレクサ812は、LZD出力の一方を先頭の0の数として選択し、先頭ゼロ信号 $B_L\_Sh$ を指數経路518と正規化論理回路818とに提供する。

40

#### 【0126】

[0137]マルチプレクサ806によって選択される最終的な和 $S$ は、ゼロ検出回路814にも提供される。ゼロ検出回路814は、最終的な和が0である場合、符号経路520への $R\_ZERO$ 信号をアサートし、そうでない場合、 $R\_ZERO$ 信号をアサートしない。

#### 【0127】

[0138]正規化論理回路818は、 $U\_f p 64$ 信号がアンダーフローを示していない限りは、先頭ゼロ信号を正規化信号 $L\_shift$ として選択し、 $U\_f p 64$ 信号がアンダ

50

ーフローを示している場合、仮数は指数 1 に対応する位置までシフトされるのみであり、従って、結果は非正規形式において表現される。シフト回路 816 は、選択された和  $S$  を  $L_{shift}$  信号に応答して左シフトし、正規化された和  $S_n$  を生成する。プラス 1 加算器 822 は、正規化された和  $S_n$  に 1 を加算する。丸め論理回路 820 は、(OPCTL 信号によって指定される) 丸めモードと、(経路 821 上の) 正規化された和  $S_n$  の LSB とを使用して、正規化された和を切り上げるべきであるかを判定する。切り上げるべきである場合、丸め論理回路 820 は、加算器 822 からの出力  $S_n + 1$  が選択されるよう 10 に、選択マルチプレクサ 824 を制御する。そうでない場合、選択マルチプレクサ 824 は、正規化された和  $S_n$  を選択する。選択マルチプレクサ 824 は、選択された結果  $R_m$  を出力セクション 522 に提供する。いくつかの実施形態においては、選択マルチプレクサ 824 は、結果の仮数から先頭ビット(正規数の場合は 1 )をドロップする。

#### 【0128】

[0139] 丸め演算と並列に、指数経路 518 (図 7) は、結果の指数  $R_e$  を計算する。具体的には、減算ブロック 720 が、指数計算ブロック 702 からのブロック指数  $BLE$  と、仮数経路 516 からのブロックシフト信号  $BL\_Sh$  とを受け取る。減算ブロック 720 は、これら二つの入力を減算し、その結果  $EDIF$  を、アンダーフロー / オーバーフロー論理回路 722 と、プラス 1 加算器 724 と、選択マルチプレクサ 726 とに提供する。アンダーフロー / オーバーフロー論理回路 722 は、結果の  $MSB$  を使用して、アンダーフロー又はオーバーフローが発生したかを判定し、アンダーフロー又はオーバーフローの存在の有無を反映する  $U/O$  信号を生成する。選択マルチプレクサ 726 は、この  $U/O$  信号に基づいて、減算結果  $EDIF$  と、プラス 1 加算器 724 の出力との間での選択を行う。選択された値は、結果の指数  $R_e$  として、 $U/O$  信号と共に出力セクション 522 に提供される。 20

#### 【0129】

[0140] 丸め演算と並列に、符号経路 520 (図 9) における最終符号回路 904 は、積 / 和回路 902 によって判定された符号と、仮数経路 516 から受け取る  $R\_ZERO$  信号及び和の  $MSB$  と、オペランド準備ブロック 514 から受け取る特殊数  $SPC$  信号とに基づいて、最終的な符号  $R_s$  を決定する。

#### 【0130】

[0141] 出力セクション 522 (図 10) は、仮数経路 516 からの結果の仮数  $R_m$  と、指数経路 518 からの結果の指数  $R_e$  と、符号経路 520 からの結果の符号  $R_s$  と、オペランド準備ブロック 514 からの特殊数  $SPC$  信号と、指数経路 518 からの  $U/O$  信号とを受け取る。 $SPC$  信号及び  $U/O$  信号に基づいて、出力マルチプレクサ制御論理回路 1002 は、仮数部マルチプレクサ 1004 のための制御信号と、指数マルチプレクサ 1006 のための制御信号とを生成する。さらに、出力マルチプレクサ制御論理回路 1002 は、様々な条件コード  $COND$  (例えば、結果がオーバーフロー、アンダーフロー、又は  $NAN$  であるかを示す) を生成する。 30

#### 【0131】

[0142] 仮数部マルチプレクサ 1004 は、正規数及び非正規数の場合、仮数部  $R_m$  を選択する。アンダーフローの場合、丸めモードに応じて、0 又は仮数部  $m_{in\_denorm}$  が選択される。オーバーフロー(無限大)の場合、仮数部  $0 \times 0_0000_0000_0000$  が選択される。いずれかの入力オペランドが  $NAN$  である場合、クワイエット型  $NAN$  の仮数部が選択される。演算中に  $NAN$  が発生した場合、内部(クワイエット型)  $NAN$  の仮数  $0 \times 0_000_0000$  が選択される。 40

#### 【0132】

[0143] 指数マルチプレクサ 1006 は、正規数の場合、結果の指数  $R_e$  を選択する。非正規数及びアンダーフローの場合、指数  $0 \times 0_00$  が選択される。無限大又は  $NAN$  の場合、最大指数  $0 \times 7ff$  が選択される。

#### 【0133】

[0144] 連結ブロック 1008 は、選択された仮数部と、選択された指数と、符号  $R_s$  と

10

20

30

40

50

を受け取り、fp64の最終的な結果OUTを生成する。条件コードは必要に応じて設定され得る。

#### 【0134】

[0145]なお、DFMAユニット320では、全てのDFMA演算が、オーバーフロー又はアンダーフローにかかわらず同数のサイクルで完了することに留意されたい。さらに、DFMAユニット320は、IEEE754規格に従って、浮動小数点算術演算におけるオーバーフロー／アンダーフロー時の予測デフォルト動作(expected default overflow/underflow behavior)を実施する。即ち、適切な結果OUTが返され、オーバーフロー／アンダーフロー条件を示すように、(条件コードCONDにおける)ステータスフラグがセットされる。いくつかの実施形態においては、これらの条件を扱うためのユーザ定義のトラップが実施されてもよく、トラップを発生させるべきであるかを判定するよう、条件コードCONDを使用することが可能である。10

#### 【0135】

##### B. 乗算

[0146]乗算(DMUL)は、オペランドCを0にセットして、DFMAユニット320が、 $A * B + 0.0$ を計算することで、上述したDFMA演算と同じように実施することが可能である。一実施形態においては、オペコードがDMUL演算を示している場合に、選択マルチプレクサ636(図6)を使用して、入力オペランドCをfp64の値0に置き換えることができる。20

#### 【0136】

##### C. 加算

[0147]加算(DADD)は、オペランドBを1.0にセットして、DFMAユニット320が $A * 1.0 + C$ を計算することで、上述したDFMA演算と同じように実施することが可能である。一実施形態においては、オペコードがDADD演算を示している場合に、選択マルチプレクサ634(図6)を使用して、入力オペランドBをfp64の値1.0に置き換えることができる。

#### 【0137】

##### D. DMAX及びDMIN

[0148]DMAX演算又はDMIN演算の場合、オペランド準備ブロック514(図6)が、オペランドA及びオペランドBを受け取る。NaN回路612及び614が、選択されたオペランドのいずれか一方又は双方がNaNであるかを判定する。絶対値/符号反転回路618, 620が、必要に応じて符号ビットを反転する(又は反転しない)。30

#### 【0138】

[0149]A/B比較回路624は、絶対値/符号反転回路618, 620からオペランドA及びオペランドBを受け取り、例えば、これらのオペランドがあたかも整数であるかのようにAからBを減算することによって、比較を実行する。この減算に基づいて、A/B比較回路624は、AがBよりも大きい、AがBよりも小さい、又はAがBに等しいかを示すCOMP信号を生成する。COMP信号は制御論理回路630に提供される。制御論理回路630は、対応するR\_Test信号を生成し、さらに、選択マルチプレクサ632, 634, 及び636用の選択信号を生成する。40

#### 【0139】

[0150]具体的には、DMAX演算の場合、オペランドAのマルチプレクサ632は、AがBより大きければオペランドAを選択し、AがBより小さければオペランド1.0を選択し、一方で、オペランドBのマルチプレクサ634は、BがAより大きければオペランドBを選択し、BがAより小さければオペランド1.0を選択する。DMIN演算の場合、オペランドAのマルチプレクサ632は、AがBより小さければオペランドAを選択し、AがBより大きければオペランド1.0を選択し、一方で、オペランドBのマルチプレクサ634は、BがAより小さければオペランドBを選択し、BがAより大きければオペランド1.0を選択する。DMAX及びDMINのいずれの場合も、A = Bである特殊な50

場合は、マルチプレクサ 632 がオペランド A を選択する一方でマルチプレクサ 634 がオペランド 1.0 を選択するように制御することによって、或いは、マルチプレクサ 632 がオペランド 1.0 を選択する一方でマルチプレクサ 634 がオペランド B を選択するように制御することによって、扱うことができる。いずれの場合にも、オペランド C のマルチプレクサ 636 は、オペランド 0.0 を選択するように動作することが好適である。

#### 【0140】

[0151] 特殊数検出回路 638, 640, 及び 642 は、オペランドが特殊数であるかを判定し、該当する特殊数 SPC 信号を経路 524 上に生成する。特殊数検出回路 638, 640, 及び 642 は、仮数 Am, Bm, 及び Cm (正規数の場合は先頭に 1 が付加されており、非正規数の場合は先頭に 0 が付加されている) を仮数経路 516 に提供し、指数 Ae, Be, 及び Ce を指数経路 518 に提供し、符号ビット As, Bs, 及び Cs を符号経路 520 に提供する。

10

#### 【0141】

[0152] fp32 抽出回路 626 及び符号なし / 符号付き整数抽出回路 628 は、DMA X 演算又はDMIN 演算の場合には使用されず、これらの回路は、必要に応じて電力遮断状態又は低電力状態に設定され得る。

#### 【0142】

[0153] 仮数経路 516、指数経路 518、及び符号経路 520 は、DFMA 演算について上述したように動作する。DMA X 演算の場合、仮数経路 516、指数経路 518、及び符号経路 520 は、 $\max(A, B) * 1.0 + 0.0$  を計算する。DMIN 演算の場合、仮数経路 516、指数経路 518、及び符号経路 520 は、 $\min(A, B) * 1.0 + 0.0$  を計算する。従って、正規数の場合、Rm, Re, 及び Rs は、所望の結果の仮数、指数、及び符号に対応する。

20

#### 【0143】

[0154] 出力セクション 522 (図 10) は、特殊数を扱う。具体的には、DMA X 演算及び DMIN 演算の結果は、NaN オペランドに対して定義されておらず、結果は NaN 値にセットされ得る。出力マルチプレクサ制御論理回路 1002 は、結果を NaN とするべきかを、特殊数 SPC 信号を使用して判定する。NaN とするべきである場合、仮数部マルチプレクサ 1004 がクワイエット型 NaN 入力を選択し、指数マルチプレクサが  $0 \times 7ff$  を選択する。そうでない場合、結果 Rm 及び結果 Re が選択される。条件コードは必要に応じて設定され得る。

30

#### 【0144】

[0155] 代替実施形態においては、仮数経路 516、指数経路 518、及び符号経路 520 のコンポーネントのいくつか又は全てをバイパスすることができる。バイパスされるコンポーネントは低電力状態に設定され得る。バイパス経路が、仮数経路 516、指数経路 518、及び符号経路 520 のうちの最も長い経路と同数のパイプラインステージを占めるように、バイパス経路に様々な遅延回路 (ラッチなど) を含めてよい。これにより、DFMA ユニット 320 における全ての演算について、完了に要するサイクルが同数となり、これにより、命令発行論理回路が単純化される。

40

#### 【0145】

##### E. DSET

[0156] DSET 演算では、DMA X 及び DMIN と同様に、オペランド準備ブロック 514 における A / B 比較回路 624 (図 6) が使用される。DSET では、DMA X 及び DMIN とは異なり、入力オペランドの一方が返されるのではなく、テストされた条件が満たされているかを示すブール値が返される。

#### 【0146】

[0157] DSET 演算の場合、オペランド準備ブロック 514 (図 6) が、オペランド A 及びオペランド B を受け取る。NaN 回路 612 及び 614 は、選択されたオペランドのいずれか一方又は双方が NaN であるかを判定する。絶対値 / 符号反転回路 618, 620 は、必要な場合に符号ビットを反転する。

50

## 【0147】

[0158] A / B 比較回路 624 は、絶対値 / 符号反転回路 618, 620 からオペランド A 及びオペランド B を受け取り、例えば、これらのオペランドがあたかも整数であるかのように A から B を減算することによって、比較を実行し、それぞれの符号ビットを考慮する。A / B 比較回路 624 は、この減算に基づいて、A が B よりも大きい、A が B よりも小さい、又は A が B に等しいかを示す COMP 信号を生成する。COMP 信号は制御論理回路 630 に提供される。制御論理回路 630 は、対応する R\_Test 信号を生成し、さらに、A マルチプレクサ 632、B マルチプレクサ 634、及び C マルチプレクサ 636 用の選択信号を生成する。DSET 演算の結果はブール値であるため、一実施形態では、三つのマルチプレクサ 632, 634, 636 の全てがゼロオペランドを選択する。別の実施形態においては、マルチプレクサ 632 及び 634 がオペランド A 及びオペランド B を選択する。特殊数検出回路 638 及び 640 は、これらのオペランドが特殊数であるかを判定し、該当する特殊数 SPC 信号を経路 524 上に生成する。

10

## 【0148】

[0159] fp32 抽出回路 626 及び符号なし / 符号付き整数抽出回路 628 は、DSET 演算の場合には使用されず、これらの回路は、必要に応じて電力遮断状態又は低電力状態に設定され得る。

## 【0149】

[0160] 仮数経路 516、指数経路 518、及び符号経路 520 は、DFMA 演算について上述したように動作するか、又は、これらの一部又は全体をバイパスすることができる。バイパスされるコンポーネントは低電力状態に設定され得る。上述したように、バイパス経路が、仮数経路 516、指数経路 518、及び符号経路 520 のうちの最も長い経路と同じ数のパイプラインステージを占めるように、バイパス経路に様々な遅延回路（ラッチなど）を含めることができる。これにより、DFMA ユニット 320 における全ての演算について、完了に要するサイクルが同数となり、これにより、命令発行論理回路が単純化される。

20

## 【0150】

[0161] 出力セクション 522（図 10）は、特殊数を扱う。具体的には、IEEE754 規格においては、A 又は B（又は双方）が NaN であるならば、A 及び B は順序付けできない。出力マルチプレクサ制御論理回路 1002 は、A が B よりも大きい、A が B よりも小さい、又は A が B に等しいかを示す R\_Test 信号と、A 又は B が NaN であるかを示す特殊数 SPC 信号と、要求されている特定のテスト演算を示す OPCODEL 信号とを受け取る。出力マルチプレクサ制御論理回路 1002 は、R\_Test 信号及び SPC 信号を使用して、要求されたテストが満たされているかを判定する。一実施形態においては、DSET 演算の結果を条件コードとして提供し、結果 OUT を無視する。その場合、出力マルチプレクサ制御論理回路 1002 は、結果を示すように条件コードCOND を設定し、オプションとして、出力 OUT の仮数部及び指数を選択することができる。別の実施形態においては、テスト結果を反映するように出力 OUT を設定することができ、この場合、出力マルチプレクサ制御論理回路 1002 は、テストが満たされているならば論理真に対応する 64 ビット値が選択され、テストが満たされていないならば論理偽に対応する 64 ビット値が選択されるように、仮数部マルチプレクサ 1004 及び指数マルチプレクサ 1006 を動作させる。

30

## 【0151】

## F. 形式変換

[0162] いくつかの実施形態においては、DFMA ユニット 320 は、倍精度形式とそれ以外の形式との間での形式変換演算もサポートする。以下に例を説明する。

40

## 【0152】

## 1. fp32 から fp64 (F2D)

[0163] F2D 演算の場合、fp32 入力オペランド A が、対応する fp64 数に変換される。特殊数入力は適切に扱われる。例えば、fp32 無限大又は fp32 NaN は、

50

f p 6 4 無限大又は f p 6 4 NaN に変換される。全ての f p 3 2 非正規数は、 f p 6 4 の正規数に変換することができる。

#### 【 0 1 5 3 】

[0164] オペランド準備ブロック 5 1 4 ( 図 6 ) は、 f p 3 2 のオペランド A を受け取る。絶対値 / 符号反転回路 6 1 8 は、オペランド A を修正することなく f p 3 2 抽出ブロック 6 2 6 に通過させる。f p 3 2 抽出ブロック 6 2 6 は、オペランド A に対して f p 6 4 形式への最初の上位変換を実行する。具体的には、f p 3 2 抽出ブロック 6 2 6 は、8 ビットの指数を取り出し、 $1023 - 127 = 896$  を加算して、f p 6 4 形式の正しいバイアスを有する 11 ビットの指数を生成する。23 ビットの仮数には、末尾の 0 がパディングされる。さらに、f p 3 2 抽出ブロック 6 2 6 は、オペランド A が f p 3 2 の特殊数 ( 例 : 無限大、NaN、0、又は非正規 ) であるかを判定し、その情報を、経路 6 4 4 を介して特殊数検出回路 6 4 2 に提供する。さらに、f p 3 2 抽出ブロック 6 2 6 は、オペランドの符号を反転する、或いはオペランドに絶対値を適用することもできる。

#### 【 0 1 5 4 】

[0165] オペランド C のマルチプレクサ 6 3 6 は、f p 3 2 抽出ブロック 6 2 6 によって提供される上位変換されたオペランドを選択し、オペランド A のマルチプレクサ 6 3 2 及びオペランド B のマルチプレクサ 6 3 4 は、ゼロオペランドを選択する。特殊数検出回路 6 4 2 は、オペランドが f p 3 2 非正規数でない限りは、仮数に先頭の 1 を付加する。さらに、特殊数検出回路 6 4 2 は、f p 3 2 非正規数が正規数として特定されている場合を除き ( 全ての f p 3 2 非正規数は f p 6 4 において正規数として表現することができるため ) 、f p 3 2 抽出ブロック 6 2 6 によって提供される特殊数情報を、自身の特殊数 SPC 信号として使用する。

#### 【 0 1 5 5 】

[0166] 仮数経路 5 1 6 及び指数経路 5 1 8 は、DFMA 演算について上述したように動作して、f p 6 4 形式において  $0 . 0 * 0 . 0 + C$  を計算する。仮数経路 5 1 6 及び指数経路 5 1 8 における正規化要素は、上位変換された f p 6 4 オペランドを正規化する。代替実施形態においては、図 8 を参照し、指数経路 5 1 8 からの位置合わせ後の仮数 C\_a 1\_i g\_n を、仮数経路 5 1 6 における加算器 8 0 4 の周囲をマルチプレクサ 8 0 6 の sum 入力にバイパスさせることができる。ここで、乗算器 8 0 2 及び加算器 8 0 4 を低電力状態に設定することができる。符号経路 5 2 0 は符号ビット C\_s を通過させることができるのである。

#### 【 0 1 5 6 】

[0167] 出力セクション 5 2 2 ( 図 1 0 ) においては、入力オペランドが f p 3 2 無限大、f p 3 2 NaN、又は f p 3 2 0 であったことを特殊数 SPC 信号が示していない限りは、正規化された f p 6 4 の結果 ( Rm, Rs, Re ) が選択される。入力オペランドが f p 3 2 無限大であった場合、出力マルチプレクサ制御論理回路 1 0 0 2 は、f p 6 4 無限大の仮数部 ( 0 x 0\_0000\_0000\_0000 ) が選択されるように仮数部マルチプレクサ 1 0 0 4 を動作させ、f p 6 4 無限大の指数 ( 0 x 7ff ) が選択されるように指数マルチプレクサ 1 0 0 6 を動作させる。入力オペランドが f p 3 2 NaN であった場合、出力マルチプレクサ制御論理回路 1 0 0 2 は、f p 6 4 クワイエット型 NaN の仮数部が選択されるように仮数部マルチプレクサ 1 0 0 4 を動作させ、f p 6 4 NaN の指数 ( 0 x 7ff ) が選択されるように指数マルチプレクサ 1 0 0 6 を動作させる。入力オペランドが f p 3 2 0 であった場合、出力マルチプレクサ制御論理回路 1 0 0 2 は、f p 6 4 0 の仮数部 ( 0 x 0\_0000\_0000\_0000 ) が選択されるように仮数部マルチプレクサ 1 0 0 4 を動作させ、f p 6 4 0 の指数 ( 0 x 000 ) が選択されるように指数マルチプレクサ 1 0 0 6 を動作させる。条件コードは、必要に応じて設定され得る。

#### 【 0 1 5 7 】

##### 2. 整数から f p 6 4 ( I 2 D )

[0168] I 2 D 演算の場合、整数 ( u 6 4 , s 6 4 , u 3 2 , 又は s 3 2 形式 ) が f p 6

10

20

30

40

50

4形式に変換される。オペランド準備ブロック514(図6)は、64ビットの整数オペランドCを受け取る。32ビット整数形式の場合、32個の先頭の0を付加することができる。絶対値/符号反転回路622は、オペランドCを修正することなくU/S抽出ブロック628に通過させる。U/S抽出ブロック628は、オペランドCに対してfp64形式への最初の上位変換を実行する。具体的には、抽出ブロック628は、オペランドCにおける先頭の1の位置を(例えばプライオリティエンコーダを使用して)判定する。11ビットの指数は、指数フィールドを1086( $2^{6^3}$ に対応する)に初期化することによって求められる。32ビット形式の入力の場合、先頭の1がドロップされ、仮数に末尾の0がパディングされて、52ビットの仮数部が生成される。64ビット形式の入力の場合、必要に応じて仮数が53ビットに切り捨てられ、先頭の1がドロップされる。また、ガードビット及びラウンドビットが必要に応じて維持されてもよい。

10

## 【0158】

[0169]さらに、U/S抽出ブロック628は、入力オペランドが0であるかを判定し、特殊数検出回路642用の対応の制御信号を生成する。0以外の特殊数(非正規、無限大、及びNaN)は、ID演算時には発生せず、検出する必要がない。

## 【0159】

[0170]オペランドCのマルチプレクサ636は、U/S抽出ブロック628によって提供される上位変換されたオペランドを選択する。オペランドAのマルチプレクサ632とオペランドBのマルチプレクサ634のそれぞれは、ゼロオペランドを選択する。特殊数検出回路642は、U/S抽出ブロック628によって提供されるゼロ情報を使用して、入力オペランドが0であるかを示す特殊数SPC信号を生成する。

20

## 【0160】

[0171]仮数経路516及び指数経路518は、DFMA演算について上述したように動作し、 $0.0 * 0.0 + C$ を計算する。仮数経路516及び指数経路518における正規化要素は、上位変換されたfp64オペランドを正規化する。代替実施形態においては、図8を参照し、指数経路518からの位置合わせ後の仮数C\_alignを、仮数経路516における加算器804の周囲をマルチプレクサ806のSum入力にバイパスさせることができる。乗算器802及び加算器804は低電力状態に設定され得る。符号経路520は符号ビットCsを通過させることが好適である。

30

## 【0161】

[0172]出力セクション522(図10)においては、入力オペランドが整数0であったことを特殊数SPC信号が示していない限りは、正規化されたfp64の結果(Rm, Rs, Re)が選択される。入力オペランドが整数0であった場合、出力マルチプレクサ制御論理回路1002は、fp64 0の仮数部(0x0\_0000\_0000\_0000)が選択されるように仮数部マルチプレクサ1004を動作させ、fp64 0の指数(0x000)が選択されるように指数マルチプレクサ1006を動作させる。必要に応じて条件コードが設定され得る。

## 【0162】

3.f p 6 4 から f p 3 2 (D2F)

40

[0173]fp64は、fp32よりも広い範囲の浮動小数点数をカバーしているので、fp64からfp32への(D2F)変換では、fp32値におけるオーバーフロー及びアンダーフローを検出することが要求される。

## 【0163】

[0174]D2F演算の場合、オペランド準備ブロック514(図6)にオペランドCが提供される。絶対値/符号反転回路622は、必要に応じて絶対値又はオペランドの符号反転を実行し、オペランドCをオペランドCのマルチプレクサ636に渡す。オペランドCのマルチプレクサ636は、オペランドCを選択し、特殊数検出回路642に提供する。特殊数検出回路642は、fp64非正規数、fp64 0、fp64無限大、又はfp64 NaNを検出し、対応するSPC信号を出力セクション522に提供する。選択マルチプレクサ632及び634は、オペランド0.0を選択する。

50

## 【0164】

[0175] 指数経路 518(図7)においては、指数計算ブロック702は、fp64指数を897だけマイナス方向にバイアスし、対応するfp32の指数を求める。fp32の指数がアンダーフローする場合、指数計算ブロック702は、アンダーフローが排除されるようにCの仮数を右シフトするSh\_C信号を生成する(218ビット以上のシフトが必要である場合、Cの仮数は0になる)。シフト回路706は、Sh\_C信号に従ってCの仮数を右シフトする。結果はマルチプレクサ712によって選択され、位置合わせ後の仮数C\_alingnとして仮数経路516に提供される。アンダーフロー論理回路713は、fp32アンダーフローを検出し、U\_fp32信号を生成する。

## 【0165】

[0176] 仮数経路516(図8)においては、乗算器802が、積0.0\*0.0を計算する(又はバイパスされる)。この積(0)は、加算器804によって仮数C\_alingnに加算される。マルチプレクサ806は、結果Sumを選択する(入力が符号・絶対値形式であるため)。0の結果は、回路814によって検出される。0以外の結果は、DMA演算に関して上述したように正規化される。丸め論理回路820を使用して、切り上げるかを判定することができる。なお、結果は23ビットのfp32仮数であるため、プラス1加算器822は、(53番目ではなく)24番目のビット位置に1を加算する必要があることに留意されたい。

## 【0166】

[0177] 出力セクション522(図10)は、結果を組み立てる。fp32の23ビットの仮数部は、52ビットフィールドのRmにおいて提供される。出力マルチプレクサ制御論理回路1002は、結果がfp32の正規数ではない場合を除き、Rmが選択されるように仮数部マルチプレクサ1004を制御する。fp32\_0又はfp32無限大である場合、0の仮数0x00000\_0000\_0000が選択され、fp32\_NaNである場合、クワイエット型fp32\_NaNの仮数が選択される。fp32非正規数の場合、Rmを使用することができる。

## 【0167】

[0178] 8ビットのfp32の指数は、11ビットの指数フィールドにおいて提供される。出力マルチプレクサ制御論理回路1002は、結果がfp32の正規数ではない場合を除き、Reが選択されるように指数マルチプレクサ1004を制御する。fp32非正規数又はfp32\_0である場合、0の指数0x000が選択される。fp32無限大又はfp32\_NaNである場合、fp32の最大指数0x7fffが選択される。

## 【0168】

[0179] 連結ブロック1008は、Rm及びReを、64ビットの出力フィールドのうちの31ビットにパックし、符号ビットRsを先頭に付加する。11ビットの指数における3個のMSBがドロップされ、52ビットの仮数部における29個のLSBがドロップされる。fp32の結果は、例えば、必要に応じて64ビットフィールドのMSB又はLSBにおいて位置合わせすることができる。必要に応じて条件コードを設定することができる。

## 【0169】

4.fp64から整数(D2D)

[0180] D2I演算の場合、オーバーフロー及びアンダーフローが検出される。オーバーフローは最大整数値にセットされ、アンダーフローは0にセットされる。

## 【0170】

[0181] 変換するオペランドは、fp64形式におけるオペランドCとして提供される。絶対値/符号反転回路622は、必要に応じて絶対値又はオペランドの符号反転を実行し、オペランドCをオペランドCのマルチプレクサ636に渡す。オペランドCのマルチプレクサ636は、オペランドCを選択し、特殊数検出回路642に提供する。特殊数検出回路642は、fp64非正規数、fp64\_0、fp64無限大、又はfp64\_NaNを検出し、対応するSPC信号を出力セクション522に提供する。選択マルチプレク

10

20

30

40

50

サ 6 3 2 及び 6 3 4 は、オペランド 0 . 0 を選択する。

【 0 1 7 1 】

[0182]指數経路 5 1 8 (図 7)においては、指數計算ブロック 7 0 2 は、2進小数点を整数位置に合わせるために C\_m をシフトすべき量を、指數 C\_e を使用して求め、対応する S\_h\_C 信号を生成する。一実施形態においては、指數計算ブロック 7 0 2 は、指數のバイアスを取り除き、仮数部の幅と、使用される整数形式と、32ビット形式の結果を 64 ビットフィールドにおいて表現する方式(例：32 個の M S B 又は 32 個の L S B を使用する)とを考慮する。さらに、変換後の整数形式において結果がオーバーフローするか、又はアンダーフローするかを、指數 C\_e を使用して判定する。オーバーフロー又はアンダーフローする場合、対応するオーバーフロー信号又はアンダーフロー信号(図示していない)が、出力セクション 5 2 2 における出力マルチプレクサ制御論理回路 1 0 0 2 (図 10) に送られることが好適である。

10

【 0 1 7 2 】

[0183]シフト回路 7 0 6 は、C\_m を量 C\_Shift だけシフトさせ、この C\_Shift 信号がマルチプレクサ 7 1 2 によって C\_align 信号として選択される。

【 0 1 7 3 】

[0184]仮数経路 5 1 6 (図 8)においては、乗算器 8 0 2 が、結果 0 . 0 を加算器 8 0 4 に提供する。加算器 8 0 4 は、0 . 0 を C\_align に加算し、C が正であるか負であるかに応じて、Sum 又は ~Sum が選択される。シフター 8 1 6 は、この結果をシフトしないことが好適である。整数フォーマッティングブロック 8 2 6 は、結果を、11 ビットの M S B フィールド int\_M と、53 ビットの L S B フィールド int\_L とに分ける。

20

【 0 1 7 4 】

[0185]出力セクション 5 2 2 (図 10)においては、出力マルチプレクサ制御論理回路 1 0 0 2 が、オーバーフロー、アンダーフロー、又は特殊数オペランドである場合を除いて、結果の int\_L 及び結果の int\_M がそれぞれ選択されるように仮数部マルチプレクサ 1 0 0 4 及び指數マルチプレクサ 1 0 0 6 を制御する。オーバーフローの場合、出力形式 (u 32, s 32, u 64, 又は s 64) における最大整数が選択され、アンダーフローの場合、0 が選択される。条件コードは、必要に応じて設定され得る。

30

【 0 1 7 5 】

#### I V . 更なる実施形態

[0186]本発明について、特定の実施形態に関連して説明してきたが、膨大な修正・変更が可能であることが当業者には認識されるであろう。例えば、DFMA ユニットは、より多くの機能、より少ない機能、又は異なる機能が、組合せとしてサポートされるように実施されてもよく、或いは、任意の形式又は任意の形式の組合せにおけるオペランド及び結果がサポートされるように実施されてもよい。

【 0 1 7 6 】

[0187]本明細書において説明した様々なバイパス経路及び通過経路は、異なる形態をとることもできる。一般的に、回路ブロックの周囲のバイパス経路が説明してある箇所では、その経路を、そのブロックにおける恒等演算(すなわち、オペランドに影響を与えない演算(例：0 を加算する))に置き換えることができる。ある演算時にバイパスされる回路ブロックは、アイドル状態(例えば、低電力状態)に設定することができ、或いは、通常に動作させ、(例えば、選択マルチプレクサ又はその他の回路の動作によって)下流のブロックが結果を無視するようにすることができる。

40

【 0 1 7 7 】

[0188]DFMA パイプラインは、任意の数のステージに分割することができ、ステージそれぞれにおけるコンポーネントの組合せは、必要に応じて異なる組合せとすることができます。さらに、本明細書において特定の回路ブロックによって提供される機能を、複数のパイプラインステージにまたがるように分割することができる。例えば、乗算器のツリーが複数のステージを占めることができる。さらに、様々なブロックの機能を修正・変更す

50

ことができる。いくつかの実施形態においては、例えば、異なる加算器回路又は異なる乗算器回路を使用することができる。

#### 【0178】

[0189]さらに、DFMAユニットについて、理解を促進する目的で、回路ブロックに基づいて説明してきた。これらの回路ブロックは、様々な回路コンポーネント及び様々なレイアウトを使用して実施することができ、本明細書に説明してあるブロックが、特定の一連のコンポーネント又は特定の物理的レイアウトに限定されないことが、当業者には認識されるであろう。ブロックは、必要に応じて、物理的に結合する、又は分けることができる。

#### 【0179】

[0190]プロセッサは、実行コアの中に一以上のDFMAユニットを含んでいてもよい。例えば、スーパースケーラ命令発行方式（すなわち、1サイクルあたり二つ以上の命令を発行する）又はSIMD命令発行方式が望ましい場合、複数のDFMAユニットを実施することができ、異なるDFMAユニットが、異なる機能の組合せをサポートすることができる。さらに、プロセッサは、複数の実行コアを含んでいてもよく、コアのそれぞれが自身の（一つ以上の）DFMAユニットを有することができる。

#### 【0180】

[0191]いくつかの実施形態においては、実行コアが SIMD 命令発行をサポートし、一つの DFMA パイプラインにおいて複数のデータセットを連続的に処理することができるよう、一つの DFMA ユニットを、入力の順序付け及び出力収集のための適切な論理回路と組み合わせて使用することができる。

10

20

30

40

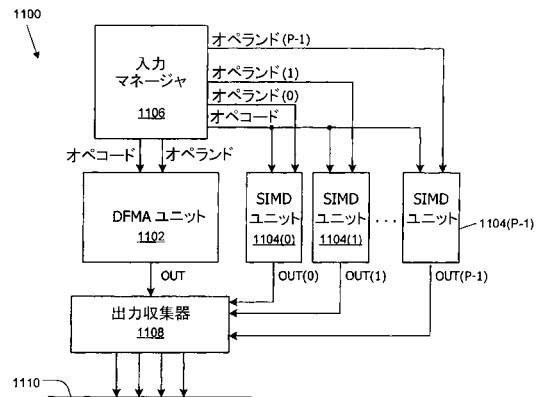

#### 【0181】

[0192]図11は、本発明の実施形態による、DFMA機能ユニット1102を含む実行コア1100のブロック図である。DFMAユニット1102は、上述したDFMAユニット320に類似するユニット、又は同じユニットとすることができる。コア1100は SIMD 命令を発行する、すなわち、P組の異なるセットの単精度オペランドを有する同じ命令を、P個のセットの単精度 SIMD ユニット1104に並列に発行することができる。 SIMD ユニット1104のそれぞれは、同じオペコードと、異なるセットのオペランドとを受け取る。P個の SIMD ユニット1104は、並列に動作してP個の結果を生成する。DFMAユニット1102には、P-way SIMD命令が、P個の一連の SIMD（单一命令單一データ）命令として発行される。

30

#### 【0182】

[0193]入力マネージャ1106（命令発行ユニットの一部とすることができる）は、 SIMD 命令のオペランドを集め、 SIMD 命令の P 個のセットのオペランド全てが集まつたとき、それらオペランド及び適用可能なオペコードを、 P 個の SIMD ユニット1104又はDFMAユニット1102のいずれかに提供する。出力収集器1008は、 SIMD ユニット1104又はDFMAユニット1102からの結果を集め、それらの結果を、結果バス1110を介してレジスタファイル（図11には示していない）に提供する。いくつかの実施形態においては、結果バス1110は、入力マネージャ1106へのバイパス経路も提供し、従って、結果を次の命令において使用することができるよう、結果をレジスタファイルに提供するのと並列に入力マネージャ1106に提供することができる。一つのDFMAユニット1102を使用して、見かけ上の SIMD 動作を提供する目的で、入力マネージャ1106は、例えば、P個の連続するクロックサイクルのそれぞれにおいて、異なるセットのオペランドを有する同じオペコードを発行することによって、DFMAユニット1102への命令の発行をシリアル化することが有利である。

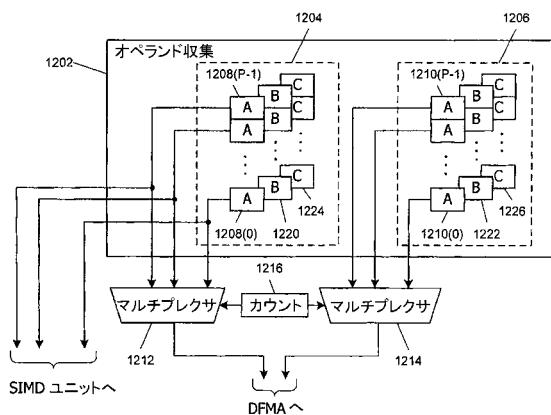

#### 【0183】

[0194]図12は、本発明の実施形態による、DFMAユニット1102のためのシリアル化された命令発行方式を示しているブロック図である。入力オペランド収集ユニット1202（図11の入力マネージャ1106に含めることができる）は、二つの収集器1204, 1206を含んでいる。収集器1204, 1206のそれぞれは、32ビットレジ

50

スタの配列であり、P組の単精度オペランドトリプレットA，B，及びCのための十分な空間を提供する。言い換れば、収集器1204，1206のそれぞれは、一つのSIMD命令の全てのオペランドを格納することができる。入力オペランド収集ユニット1202は、例えば図3のレジスタファイル324及び/又は図11の結果バス1110から、オペランドを取得する。与えられた命令に対して、どのオペランドを集めかを判定するために、タグ、又はその他の従来の手法を使用することができる。一つの命令のオペランドを、その命令が発行されるよりも数クロックサイクル前に集めることができるための十分な収集器1206が提供される。

#### 【0184】

[0195] 単精度命令の場合、P個のSIMDユニット1104が一つの命令を実行するために必要なオペランドの全てが、一方の収集器（例：収集器1204）にロードされる。P個のSIMDユニット1104に命令が発行されるとき、収集器1204全体が並列に読み取られて、SIMDユニット1104のそれぞれに異なるオペランドトリプレットA，B，Cが提供されることが好適である。10

#### 【0185】

[0196] D F M A ユニット1102への命令の場合、オペランドは倍精度（例：64ビット）である。オペランドのそれぞれは、双方の収集器1204，1206の中の対応するレジスタを使用して格納することができる。例えば、収集器1204の中のレジスタ1208は、オペランドAの一つのインスタンスの32個のM S B（例：符号ビット、11個の指数ビット、及び仮数部の20個のM S B）を格納することができ、その一方で、収集器1206の中のレジスタ1210は、同じオペランドの32個のL S B（例：仮数部の残りの32ビット）を格納する。このように、倍精度のP-way SIMD命令に必要なオペランドトリプレットA，B，Cの全てを、二つの単精度収集器1204，1206を使用して集めることができる。20

#### 【0186】

[0197] コア1100は、一つのDFMAユニット1102のみを備えており、P個のセットのオペランドは、出力マルチプレクサ（MUX）1212，1214（いずれもカウンタ1216によって制御される）を使用して連続的に提供されることが好適である。マルチプレクサ1212及び1214は、カウンタ1216に応答して、それぞれの収集器1204及び1206からのオペランドトリプレットのM S B及びL S Bを選択する。例えば、図示したデータ経路においては、マルチプレクサ1212は、収集器1204の中のレジスタ1208からのオペランドAの32個のM S Bを選択することができ、その一方で、マルチプレクサ1214は、収集器1206の中のレジスタ1210からの同じオペランドAの32個のL S Bを選択することができる。これら64ビットが、倍精度幅の経路を通じてDFMAユニット1102に提供される。同様に、（レジスタ1220及びレジスタ1222からの）オペランドBと（レジスタ1224及びレジスタ1226からの）オペランドCとを、同じカウンタ1216によって制御される対応するマルチプレクサ（図示していない）を使用して、DFMAユニット1102に提供することができる。次のクロックサイクルにおいては、収集器1204及び1206の中の次のセットのレジスタからのオペランドA，B，及びCをDFMAユニット1102に提供することができ、P個のセットのオペランドの全てが提供されるまで、以下同様に繰り返す。30

#### 【0187】

[0198] マルチプレクサ1212及び1214は、収集器1204及び1206とともに、DFMAユニット1102における見かけ上のSIMD実行を提供する（ただしスループットは低下する）。従って、コア1100のプログラミングモデルでは、全ての命令（倍精度命令を含む）についてP-way SIMDの実行が利用可能であることを想定することができる。40

#### 【0188】

[0199] 本明細書に説明したオペランドの収集及び順序付けの論理回路は、例示を目的としており、変形及び変更が可能であることが理解されるであろう。SIMD対応型のコア50

には、任意の数の D F M A ユニットを提供することができ、任意の数の D F M A ユニットに並列に命令を発行することができる。いくつかの実施形態においては、単精度演算に対する倍精度演算におけるスループットは、D F M A ユニットの数に対応して増減する。例えば、P 個の S I M D ユニットとN 個の D F M A ユニットとが存在している場合、倍精度におけるスループットは、単精度におけるスループットの N / P である。いくつかの実施形態においては、N は P に等しいことが最適である。別の実施形態においては、別の要因（例：レジスタファイルと機能ユニットとの間の内部データ経路の幅）によって、倍精度におけるスループットが、存在する D F M A ユニットの数には関係なく、単精度におけるスループットより低い値に制限されることがある。その場合、N は、その別の制限要因下において可能な値よりも大きくなることが最適である。

10

## 【 0 1 8 9 】

[0200]さらに、D F M A ユニットが单精度の機能ユニットとは個別であるため、D F M A ユニットが使用されないとき、例えば、グラフィックスプロセッサ又はコアが、レンダリングプロセス、或いは倍精度を必要としない他の計算のみに使用されているとき、D F M A ユニットの電力を落とすことができることに留意されたい。さらには、D F M A ユニットを、それ以外の回路コンポーネントの動作に影響を与えることなく、集積回路の設計から省くことができる。これにより、異なるチップによって倍精度演算の異なるサポートレベルが提供される製品ファミリーの設計が容易になる。例えば、G P U ファミリーは、それぞれが少なくとも一つの D F M A ユニットを含む多数のコアを有する高性能の G P U と、倍精度がハードウェアベースでサポートされず、D F M A ユニットが存在しない低性能の G P U とを含んでいてもよい。

20

## 【 0 1 9 0 】

[0201]さらに、本発明をグラフィックスプロセッサに関連して説明してきたが、別のプロセッサ（例えば、数学コプロセッサ、ベクトルプロセッサ、又は汎用プロセッサ）においても本発明の態様を採用することができるが、当業者には理解されるであろう。

## 【 0 1 9 1 】

[0202]このように、本発明を特定の実施形態に関連して説明してきたが、本発明は、請求項の範囲内のあらゆる変形形態及び均等の形態を包含することを理解されたい。

## 【 符号の説明 】

## 【 0 1 9 2 】

30

1 0 0 ... コンピュータシステム、1 0 2 ... C P U 、1 0 4 ... システムメモリ、1 0 5 ... メモリブリッジ、1 0 6 ... 通信経路、1 0 7 ... I / O ブリッジ、1 0 8 ... ユーザ入力装置、1 1 0 ... 表示装置、1 1 2 ... グラフィックスサブシステム、1 1 3 ... 通信経路、1 1 4 ... システムディスク、1 1 6 ... スイッチ、1 1 8 ... ネットワークアダプタ、1 2 0 , 1 2 1 ... アドインカード、1 2 2 ... G P U 、1 2 4 ... グラフィックスメモリ、2 0 0 ... レンダリングパイプライン、2 0 2 ... マルチスレッドコアアレイ、2 0 4 ... フロントエンド、2 0 6 ... データアセンブラー、2 0 8 ... セットアップモジュール、2 1 0 ... ラスタライザ、2 1 2 ... カラーアセンブリモジュール、2 1 4 ... ラスター化オペレーションモジュール ( R O P ) 、2 1 8 ... ジオメトリモジュール、2 2 4 ... ピクセルモジュール、2 2 6 ... フレームバッファ、3 0 0 ... 実行コア、3 0 2 ... フェッチ・ディスパッチユニット、3 0 4 ... 発行ユニット、3 2 0 ... D F M A ユニット、3 2 2 ... 機能ユニット、3 2 4 ... レジスタファイル、3 2 6 ... データ転送経路、5 0 2 , 5 0 4 , 5 0 6 ... オペランド入力経路、5 0 8 ... オペコード経路、5 1 0 , 5 1 2 , 5 2 4 ... 信号経路、5 1 4 ... オペランド準備、5 1 6 ... 仮数経路、5 1 8 ... 指数経路、5 2 0 ... 符号経路、5 2 2 ... 出力セクション、5 3 0 ... 制御ブロック、6 1 2 , 6 1 4 , 6 1 6 ... N a N 検出ブロック、6 1 8 , 6 2 0 , 6 2 2 ... 絶対値 / 符号反転ブロック、6 2 4 ... A / B 比較回路、6 2 6 ... F P 3 2 抽出回路、6 2 8 ... U / S 抽出回路、6 3 0 ... 制御論理回路、6 3 2 ... A マルチブレクサ、6 3 4 ... B マルチブレクサ、6 3 6 ... C マルチブレクサ、6 3 8 , 6 4 0 , 6 4 2 ... 特殊数検出回路、7 0 2 ... 指数計算回路、7 0 4 ... 最終指数計算回路、7 0 6 ... シフト回路、7 0 8 ... 符号反転回路、7 1 0 ... D 2 D 論理回路、7 1 2 ... マルチブレクサ、7 1 3 ... アンダーフロ

40

50

—論理回路、720...減算回路、722...アンダーフロー／オーバーフロー回路、724...プラス1回路、726...マルチプレクサ、802...53×53乗算器、804...168ビット加算器、806...マルチプレクサ、808, 810...LZD、812...マルチプレクサ、814...ゼロ検出回路、816...シフト回路、818...正規化論理回路、820...丸め論理回路、822...プラス1加算器、824...マルチプレクサ、826...フォーマッティング、902...積／和回路、904...最終符号回路、1002...出力マルチプレクサ制御論理回路、1004...仮数部マルチプレクサ、1006...指数マルチプレクサ、1008...連結ブロック、1102...DFMAユニット、1104...SIMDユニット、1106...入力マネージャ、1108...出力収集器、1110...結果バス、1202...オペランド収集、1208(0)~1208(P-1), 1210(0)~1210(P-1), 1220, 1224, 1226...レジスタ、1212, 1214...マルチプレクサ、1216...カウント。

10

【図1】

【図2】

【図3】

【図4】

| 倍精度算術演算 402 |             |             |

|-------------|-------------|-------------|

| 名称          | 入力          | 結果          |

| DADD        | A,C: fp64   | A+C         |

| DMUL        | A,B: fp64   | A*B         |

| DFMA        | A,B,C: fp64 | A*B+C: fp64 |

| 倍精度比較演算 404 |           |          |

|-------------|-----------|----------|

| 名称          | 入力        | 結果       |

| DMAX        | A,B: fp64 | max(A,B) |

| DMIN        | A,B: fp64 | min(A,B) |

| DSET        | A,B: fp64 | R: ブール値  |

| 形式変換及び丸め 406 |                   |                    |

|--------------|-------------------|--------------------|

| 名称           | 入力                | 結果                 |

| D2F          | A: fp64           | A': fp32           |

| F2D          | A: fp32           | A': fp64           |

| D2I          | A: fp64           | A': u/s64 or u/s32 |

| I2D          | C: u/s64 or u/s32 | C': fp64           |

| D2D          | A: fp64           | A': fp64           |

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図 1 1】

【図 1 2】

---

フロントページの続き

(72)発明者 ミン ウイ . シウ

アメリカ合衆国 , カリフォルニア州 , サンタ クララ , サン トマス エクスプレスウェイ

2701

(72)発明者 デイヴィッド シー . タネンバウム

アメリカ合衆国 , カリフォルニア州 , サンタ クララ , サン トマス エクスプレスウェイ

2701

F ターム(参考) 5B056 AA05 BB71 CC01 FF01 FF02

5B057 AA20 CH04 CH05 CH09

【外國語明細書】

2009140491000001.pdf