(19) 日本国特許庁(JP)

## (12) 公表特許公報(A)

(11) 特許出願公表番号

特表2008-500668

(P2008-500668A)

(43) 公表日 平成20年1月10日(2008.1.10)

| (51) Int.C1.      | F 1                  | テーマコード (参考) |

|-------------------|----------------------|-------------|

| <b>GO6F 12/06</b> | (2006.01) GO6F 12/06 | 522D 5B005  |

| <b>GO6F 12/10</b> | (2006.01) GO6F 12/10 | 559 5B060   |

| <b>GO6F 12/00</b> | (2006.01) GO6F 12/00 | 564D        |

| <b>GO6F 12/08</b> | (2006.01) GO6F 12/00 | 597R        |

|                   | GO6F 12/08           | 523B        |

審査請求 未請求 予備審査請求 未請求 (全 21 頁)

|               |                              |          |                                                                             |

|---------------|------------------------------|----------|-----------------------------------------------------------------------------|

| (21) 出願番号     | 特願2007-527567 (P2007-527567) | (71) 出願人 | 501055961<br>ラムバス・インコーポレーテッド<br>アメリカ合衆国・94022・カリフォルニア州・ロスアルトス・エルカミノリール・4440 |

| (86) (22) 出願日 | 平成17年5月20日 (2005.5.20)       | (74) 代理人 | 100079108<br>弁理士 稲葉 良幸                                                      |

| (85) 翻訳文提出日   | 平成18年11月10日 (2006.11.10)     | (74) 代理人 | 100093861<br>弁理士 大賀 真司                                                      |

| (86) 國際出願番号   | PCT/US2005/018246            | (74) 代理人 | 100109346<br>弁理士 大貫 敏史                                                      |

| (87) 國際公開番号   | W02005/114669                | (72) 発明者 | ウー, スティーブン, シー.<br>アメリカ合衆国, カリフォルニア州 95070, サラトガ, カントリー スクワイア レーン 12180     |

| (87) 國際公開日    | 平成17年12月1日 (2005.12.1)       |          |                                                                             |

| (31) 優先権主張番号  | 10/850,803                   |          |                                                                             |

| (32) 優先日      | 平成16年5月21日 (2004.5.21)       |          |                                                                             |

| (33) 優先権主張国   | 米国(US)                       |          |                                                                             |

最終頁に続く

(54) 【発明の名称】多重メモリアクセスレイテンシ時間の改善するためのシステムおよび方法

## (57) 【要約】

多数のメモリ装置を有するメモリシステムが、物理メモリの異なる領域に対して異なるレイテンシ時間を可能にすることと、頻繁にアクセスされるメモリアドレスを物理メモリの最短レイテンシ時間領域に位置づけるのに役立つアドレスマップを提供することと、頻繁にアクセスされるメモリアドレスを物理メモリの最短レイテンシ時間領域に割り当てるによって、平均アクセスレイテンシ時間を短縮する。

**【特許請求の範囲】****【請求項 1】**

メモリシステムにおけるメモリ装置へのアクセスを制御する方法であって、

前記メモリシステムにおけるメモリ装置を、第1のレイテンシ時間グループおよび第2のレイテンシ時間グループを含むレイテンシ時間グループに割り当てるステップであって、前記第1のレイテンシ時間グループが、前記第2のレイテンシ時間グループより短いレイテンシ時間を有するステップと、

メモリアドレス空間の少なくとも第1および第2の部分を識別するステップと、

前記アドレス空間の前記第1の部分を、前記第1のレイテンシ時間グループに割り当てられた少なくとも1つのメモリ装置にマップするステップと、

前記アドレス空間の前記第2の部分を、前記第2のレイテンシ時間グループに割り当てられた少なくとも1つのメモリ装置にマップするステップと、

を含む方法。

**【請求項 2】**

前記マッピングが、前記アドレス空間の前記第1の部分に、前記アドレス空間の前記第2の部分より短いレイテンシ時間を提供し、それにより、結果としてシステム性能の改善をもたらす、請求項1に記載の方法。

**【請求項 3】**

前記識別が、前記メモリアドレス空間の様々な部分へのアクセスの頻度に基づいており、前記アドレス空間の前記第1の部分が、前記アドレス空間の前記第2の部分より頻繁にアクセスされる、請求項1に記載の方法。

**【請求項 4】**

メモリ装置識別子を含むメモリアクセス要求を受信するステップと、

前記識別子に基づいて、前記メモリ装置のレイテンシ時間グループを決定するステップと、

前記メモリ装置の前記レイテンシ時間グループに基づいて、タイミング制御信号を生成するステップと、

をさらに含む、請求項1に記載の方法。

**【請求項 5】**

前記メモリ装置の前記レイテンシ時間グループを決定するステップが、

前記レイテンシ時間グループを、前のメモリ要求に関連するレイテンシ時間グループと比較するステップと、

前記比較に基づいて、タイミング制御信号を生成するステップと、

をさらに含む、請求項4に記載の方法。

**【請求項 6】**

前記第1および第2のレイテンシ時間グループの前記レイテンシ時間が、前記第1および第2のレイテンシ時間グループに割り当てられたメモリ装置ならびにメモリコントローラを相互接続するチャネルにおける信号の電気的なフライト時間に少なくとも部分的に起因する、請求項1に記載の方法。

**【請求項 7】**

多重メモリアクセスレイテンシ時間をサポートするメモリシステムにおいて用いるように構成されたメモリ装置であって、

メモリアレイと、

前記メモリアレイに結合され、かつ遅延値を受信するためメモリシステムに結合されるように構成されたコマンドインターフェースであって、前記遅延値が、複数のレイテンシ時間グループにおけるそれぞれのレイテンシ時間グループに関連するコマンドインターフェースと、

前記コマンドインターフェースおよび出力データパスに結合された遅延装置であって、前記メモリアレイから検索されかつ前記出力データパスで伝送されるデータを、前記遅延値によって決定された遅延期間、遅延させるように構成された遅延装置と、

10

20

30

40

50

を含むメモリ装置。

【請求項 8】

各レイテンシ時間グループが、異なる遅延値に関連している、請求項 7 に記載のメモリ装置。

【請求項 9】

少なくとも 1 つのレイテンシ時間グループに関連する少なくとも 1 つの遅延値が、このレイテンシ時間グループに割り当てられたメモリ装置およびメモリコントローラを相互接続するチャネルにおける信号の電気的なフライト時間に少なくとも部分的に起因する、請求項 8 に記載のメモリ装置。

【請求項 10】

前記それぞれのレイテンシ時間グループに関連する前記遅延値が、前記グループにおける最大アクセスレイテンシ時間に基づく、請求項 7 に記載のメモリ装置。

【請求項 11】

前記メモリ装置がメモリモジュールに含まれ、前記メモリモジュールが、前記それぞれのレイテンシ時間グループに割り当てられる、請求項 7 に記載のメモリ装置。

【請求項 12】

前記メモリモジュールが、バッファを介して前記メモリコントローラに結合される、請求項 11 に記載のメモリ装置。

【請求項 13】

前記遅延装置がシフトレジスタを含む、請求項 7 に記載のメモリ装置。

【請求項 14】

多重メモリアクセスレイテンシ時間をサポートするメモリシステムにおけるメモリ装置へのアクセスを制御する方法であって、

メモリアクセス要求を復号してメモリ装置識別子を提供するステップと、

前記メモリ装置識別子に関連するレイテンシ時間グループを識別するステップであって、前記レイテンシ時間グループが、前記メモリシステムにおける複数のレイテンシ時間グループの 1 つであるステップと、

前記識別されたレイテンシ時間グループを、前のメモリアクセス要求に関連するレイテンシ時間グループと比較するステップと、

前記比較の結果に応じてタイミング制御信号を生成するステップと、

を含む方法。

【請求項 15】

タイミング制御信号を生成するステップが、

前記識別されたレイテンシ時間グループおよび前記前のメモリアクセス要求に関連する前記レイテンシ時間グループに対応する最小時間差が、前記メモリアクセス要求と前記前のメモリアクセス要求との間の時間差より大きいかどうかを決定するステップと、

前記決定が正である場合には、バス衝突を回避するのに十分な時間、前記メモリアクセス要求のためのメモリアクセスコマンドの発行を遅延させるステップと、

をさらに含む、請求項 14 に記載の方法。

【請求項 16】

メモリアクセスコマンドの発行を遅延させるステップが、

前記メモリアクセスコマンドを発行する前に、少なくとも 1 つのノーオペレーションコマンドを発行するステップをさらに含む、請求項 15 に記載の方法。

【請求項 17】

前記タイミング制御信号が、前記メモリアクセス要求に関連するメモリアクセスコマンドの伝送を遅延させるために用いられる、請求項 14 に記載の方法。

【請求項 18】

多重アクセスレイテンシ時間をサポートするコンピュータシステムで用いるためのコンピュータプログラムプロダクトであって、前記コンピュータプログラムプロダクトが、コンピュータ可読記憶媒体およびそこに埋め込まれたコンピュータプログラム機構を含み、

10

20

30

40

50

前記コンピュータプログラム機構が、

メモリアクセス要求を復号してメモリ装置識別子を提供するステップと、

前記メモリ装置識別子に関連するレイテンシ時間グループを識別するステップであって、前記識別されたレイテンシ時間グループが、前記コンピュータシステムのメモリシステムにおける複数のレイテンシ時間グループの1つであるステップと、

前記識別されたレイテンシ時間グループを、前のメモリアクセス要求に関連するレイテンシ時間グループと比較するステップと、

前記比較の結果に応じてタイミング制御信号を生成するステップと、

を含むコンピュータプログラムプロダクト。

【請求項 19】

前記レイテンシ時間グループが、前記メモリ装置識別子を用いてルックアップ表にアクセスすることによって識別される、請求項18に記載のコンピュータプログラムプロダクト。

【請求項 20】

各レイテンシ時間グループが、異なるメモリアクセスレイテンシ時間に関連する、請求項18に記載のコンピュータプログラムプロダクト。

【請求項 21】

少なくとも1つのレイテンシ時間グループに関連する少なくとも1つのメモリアクセスレイテンシ時間が、このレイテンシ時間グループに割り当てられたメモリ装置およびメモリコントローラを相互接続するチャネルにおける信号の電気的なフライト時間に少なくとも部分的に起因する、請求項20に記載のコンピュータプログラムプロダクト。

【請求項 22】

前記識別されたレイテンシ時間グループに関連する前記メモリアクセスレイテンシ時間が、前記識別されたレイテンシ時間グループにおける最大アクセスレイテンシ時間に基づく、請求項20に記載のコンピュータプログラムプロダクト。

【請求項 23】

多重メモリアクセスレイテンシ時間をサポートするメモリシステムにおけるメモリ装置へのアクセスを制御するためのシステムであって、

プロセッサに結合されるように構成され、かつ命令を含むコンピュータプログラムプロダクトを含むメモリであって、前記命令が、前記プロセッサによって実行されたときに、

メモリアクセス要求を復号してメモリ装置識別子を提供するステップと、

前記メモリ装置識別子に関連するレイテンシ時間グループを識別するステップであって、前記識別されたレイテンシ時間グループが、前記システムのメモリシステムにおける複数のレイテンシ時間グループの1つであるステップと、

前記識別されたレイテンシ時間グループを、前のメモリアクセス要求に関連するレイテンシ時間グループと比較するステップと、

前記比較の結果に応じてタイミング制御信号を生成するステップと、

の動作を前記プロセッサに実行させるメモリを含むシステム。

【請求項 24】

前記レイテンシ時間グループが、前記メモリ装置識別子を用いてルックアップ表にアクセスすることによって識別される、請求項23に記載のシステム。

【請求項 25】

前記レイテンシ時間グループが、多くのレイテンシ時間グループから選択され、各レイテンシ時間グループが、異なるメモリアクセスレイテンシ時間に関連している、請求項23に記載のシステム。

【請求項 26】

少なくとも1つのレイテンシ時間グループに関連する少なくとも1つのメモリアクセスレイテンシ時間が、このレイテンシ時間グループに割り当てられたメモリ装置およびメモリコントローラを相互接続するチャネルにおける信号の電気的なフライト時間に少なくとも部分的に起因する、請求項25に記載のシステム。

10

20

30

40

50

**【請求項 27】**

前記識別されたレイテンシ時間グループに関連する前記メモリアクセスレイテンシ時間が、前記識別されたレイテンシ時間グループにおける最大アクセスレイテンシ時間に基づく、請求項25に記載のシステム。

**【請求項 28】**

多重メモリアクセスレイテンシ時間をサポートするメモリシステムにおけるメモリ装置へのアクセスを制御するためのシステムであって、

メモリアクセス要求を復号してメモリ装置識別子を提供するための手段と、

前記メモリ装置識別子に関連するレイテンシ時間グループを識別するための手段であって、前記識別されたレイテンシ時間グループが、前記システムのメモリシステムにおける複数のレイテンシ時間グループの1つである手段と、

前記識別されたレイテンシ時間グループを、前のメモリアクセス要求に関連するレイテンシ時間グループと比較するための手段と、

前記比較の結果に応じてタイミング制御信号を生成するための手段と、

を含むシステム。

**【請求項 29】**

各レイテンシ時間グループが、異なるメモリアクセスレイテンシ時間に関連している、

請求項28に記載のシステム。

**【請求項 30】**

少なくとも1つのレイテンシ時間グループに関連する少なくとも1つのメモリアクセス

レイテンシ時間が、このレイテンシ時間グループに割り当てられたメモリ装置およびメモ

リコントローラを相互接続するチャネルにおける信号の電気的なライト時間に少なくとも

部分的に起因する、請求項29に記載のシステム。

**【請求項 31】**

メモリコントローラと、

前記メモリコントローラに結合された第1のメモリモジュールであって、前記第1のメ

モリモジュールが、第1のバッファおよび前記第1のバッファに結合された第1のメモリ

装置を含み、前記第1のバッファが、第1の割り当てられたアクセスレイテンシ時間有する

第1のメモリモジュールと、

前記メモリコントローラに結合された第2のメモリモジュールであって、前記第2のメ

モリモジュールが、第2のバッファおよび前記第2のバッファに結合された第2のメモリ

装置を含み、前記第2のバッファが、第2の割り当てられたアクセスレイテンシ時間有する

第2のメモリモジュールと、

を含むシステム。

**【請求項 32】**

前記第1のメモリモジュールが、前記第2のメモリモジュールと直列に配置されている

、請求項31に記載のシステム。

**【請求項 33】**

前記第1の割り当てられたアクセスレイテンシ時間が、読み出し要求が前記コントローラ

から前記第1のバッファに送出される時間から、読み出し完了データが前記第1のバッ

ファから前記コントローラへ送られ、前記コントローラによってサンプリングされる時間

までを含む、請求項31に記載のシステム。

**【請求項 34】**

前記第2の割り当てられたアクセスレイテンシ時間が、読み出し要求が前記コントローラ

から前記第2のバッファに送出される時間から、読み出し完了データが前記第2のバッ

ファから前記コントローラへ送られ、前記コントローラによってサンプリングされる時間

までを含む、請求項31に記載のシステム。

**【請求項 35】**

第1の関連するレイテンシ時間を有する第1のメモリ装置と、

第2の関連するレイテンシ時間を有する第2のメモリ装置と、

10

20

30

40

50

前記第1および第2のメモリ装置に結合されたバッファであって、前記メモリ装置とメモリコントローラとの間に置かれるバッファと、

を含むメモリモジュール。

【請求項36】

メモリコントローラと、

第1のメモリモジュールであって、

前記メモリコントローラに結合されたバッファと、

前記バッファに結合された第1のメモリ装置と、

前記バッファに結合された第2のメモリ装置と、

を含む第1のメモリモジュールと、

を含むシステムであって、

前記第1のメモリ装置が、第1の関連するレイテンシ時間有し、前記第2のメモリ装置が、第2の関連するレイテンシ時間有するシステム。

【請求項37】

第1および第2のメモリモジュールに配置されたメモリ装置にアクセスする方法であって、

第1のアクセスレイテンシ時間を前記第1のメモリモジュールに割り当てるステップであって、前記第1のメモリモジュールが、第1のバッファおよび前記第1のバッファに結合された第1のメモリ装置を含むステップと、

第2のアクセスレイテンシ時間を前記第2のメモリモジュールに割り当てるステップであって、前記第2のメモリモジュールが、第2のバッファおよび前記第2のバッファに結合された第2のメモリ装置を含むステップと、

を含む方法。

【発明の詳細な説明】

【技術分野】

【0001】

技術分野

開示される実施形態は、一般的にはコンピュータメモリシステムおよび方法に関し、特に多重メモリアクセスレイテンシ時間をサポートするメモリシステムにおける性能の改善に関する。

【背景技術】

【0002】

背景

コンピュータシステムが発展し続けるにつれて、メモリシステムが、全体的なシステム性能の制限要因になっている。メモリ帯域幅の重要性が増加し続ける一方で、メモリレイテンシ時間が、システム性能においてやはり重要な役割を果たしている。たとえば、より高い信号速度では、メモリ装置の多数のランク間の伝搬遅延は、一クロックサイクルを超えて、潜在的に、メモリ装置の異なるランク間の様々なアクセスレイテンシ時間に帰着する可能性がある。ダイレクト・ランバス・ダイナミックランダムアクセスメモリ (DRAM) を用いるメモリシステムは、かかるシステムの一例である。ダブルデータレート (DDR) および DDR-II などの他のメモリタイプは、DRAM の異なるランク (たとえば異なるメモリモジュール) が、異なるアクセスレイテンシ時間有することを潜在的に可能にする信号トポロジおよび相互接続トポロジを用いる。

【0003】

ダイレクトDRAMを用いるシステムは、他よりも早く応答できる装置のランクに遅延を加えることによって、DRAMの全てのランクにわたって1つの均一なレイテンシ時間を実行するチャネルレベルライゼーション (channel levelization) (以下では「グローバルレベルライゼーション」とも呼ぶ) を利用した。これにより、結果として有効帯域幅の増加がもたらされる。なぜなら、DRAMの異なるランク間に存在するデータバブルが除去されるからである。また、これによって、メモリコントローラの

10

20

30

40

50

設計が単純化される。チャネルレベルライゼーションは、いくつかの重要な利点を提供する一方でまた、別の状況ではより少ないレイテンシ時間で応答可能な装置のランクのD R A Mレイテンシ時間を増加させる悪影響がある。その結果、アプリケーションによっては、グローバルレベルライゼーションによる性能の低下があり得る。

【発明の開示】

【課題を解決するための手段】

【0004】

実施形態の説明

概要

以下でより詳細に説明するように、メモリシステムにおけるメモリ装置へのアクセスを制御する方法において、メモリシステムのメモリ装置は、第1のレイテンシ時間グループおよび第2のレイテンシ時間グループを含むレイテンシ時間グループに割り当てられる。第1のレイテンシ時間グループは、第2のレイテンシ時間グループより短いレイテンシ時間を有する。さらに、メモリアドレス空間の第1および第2の部分は識別され、アドレス空間の第1の部分は、第1のレイテンシ時間グループに割り当てられた少なくとも1つのメモリ装置にマップされ、一方で、アドレス空間の第2の部分は、第2のレイテンシ時間グループに割り当てられた少なくとも1つのメモリ装置にマップされる。アドレス空間の第1の部分に、アドレス空間の第2の部分より短いアクセスレイテンシ時間を提供することにより、結果として、メモリシステムの性能の改善をもたらすことができる。いくつかの実施形態において、3以上のレイテンシ時間グループ、およびメモリアドレス空間の3以上の部分が用いられる。

【0005】

いくつかの実施形態において、メモリ装置には、コマンドインターフェースに結合されたメモリアレイが含まれるが、このコマンドインターフェースは、遅延値の受信のためにメモリシステムに結合されるように構成されている。メモリ装置にはまた、コマンドインターフェースおよび出力データバスに結合された遅延装置が含まれる。遅延装置は、メモリアレイから検索されかつ出力データバスで伝送されるデータを、遅延値によって決定される遅延期間、遅延させるように構成されている。他の実施形態において、レイテンシ時間制御信号を用いて、メモリアクセスレイテンシ時間を制御してもよい。

【0006】

いくつかの実施形態において、多重メモリアクセスレイテンシ時間をサポートするメモリシステムにおけるメモリ装置へのアクセスを制御する方法には、メモリアクセス要求を復号してメモリ装置識別子を提供するステップと、メモリ装置識別子に関連するレイテンシ時間グループを識別するステップであって、このレイテンシ時間グループが、メモリシステムにおける複数のレイテンシ時間グループの1つであるステップと、識別されたレイテンシ時間グループを、前のメモリアクセス要求に関連するレイテンシ時間グループと比較するステップと、比較の結果に応じてタイミング制御信号を生成するステップと、が含まれる。いくつかの実施形態において、メモリコントローラは、メモリシステムにおけるメモリ装置へのアクセスを制御するこの方法を実行するように構成されているが、この方法の実行は、前および現在のメモリアクセス要求の時間を比較し、かつ次に、比較の結果を、前および現在のメモリアクセス要求のためのレイテンシ時間グループ情報と組み合わせて用いて、バス衝突を回避するために現在のメモリアクセスコマンドの発行を遅延させるべきかどうかを決定することによる。

【0007】

いくつかの実施形態において、システムには、メモリコントローラと、メモリコントローラに結合された第1のメモリモジュールと、メモリコントローラに結合された第2のメモリモジュールと、が含まれる。第1のメモリモジュールには、第1のバッファおよび第1のバッファに結合された第1のメモリ装置が含まれる。第1のバッファは、第1の割り当てられたアクセスレイテンシ時間を有する。第2のメモリモジュールには、第2のバッファおよび第2のバッファに結合された第2のメモリ装置が含まれる。第2のバッファは

、第2の割り当てられたアクセスレイテンシ時間有する。

【0008】

第1のメモリモジュールは、第2のメモリモジュールと直列に配置してもよい。第1の割り当てられたアクセスレイテンシ時間には、読み出し要求がコントローラから第1のバッファに送出される時間から、読み出し完了データが第1のバッファからコントローラへ送られ、コントローラによってサンプリングされる時間までを含んでもよい。第2の割り当てられたアクセスレイテンシ時間には、読み出し要求がコントローラから第2のバッファに送出される時間から、読み出し完了データが第2のバッファからコントローラへ送られ、コントローラによってサンプリングされる時間までを含んでもよい。

【0009】

いくつかの実施形態において、第1および第2のメモリモジュールに配置されたメモリ装置が、アクセスされ得る。第1のメモリモジュールへの第1のアクセスレイテンシ時間を、割り当ててもよい。第1のメモリモジュールには、第1のバッファおよび第1のバッファに結合された第1のメモリ装置が含まれる。第2のメモリモジュールへの第2のアクセスレイテンシ時間が、割り当てられる。第2のメモリモジュールには、第2のバッファおよび第2のバッファに結合された第2のメモリ装置が含まれる。

【0010】

グループレベルライゼーションの利点は、実行負荷のほとんどが、ソフトウェア(たとえばBIOS)にあるということである。たとえば、この技術は、マザーボードメーカー、システムインテグレータ、エンドユーザ等がインテグレートできるBIOSオプションとして、既製のメモリコントローラ(たとえばSiS R658)で実行することができる。実行負荷のほとんどがソフトウェアにあるので、エンドユーザは、多数の装置ID/ランクマッピングから選択するか、または自身のカスタムマッピングを生成することができる。

【発明を実施するための最良の形態】

【0011】

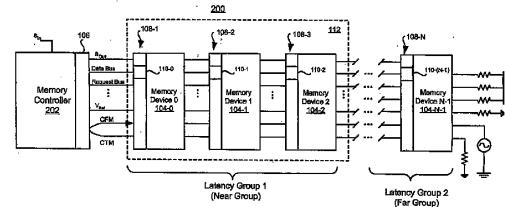

グローバルレベルライゼーション

図1は、グローバルレベルライゼーションを用いるメモリシステム100のブロック図である。メモリシステム100には、多数のパラレル伝送線路(以下では「チャネル」とも呼ぶ)を介して直列に接続された1つまたは複数のメモリ装置104-1、...、104-Nに結合されたメモリコントローラ102が含まれる。いくつかの実施形態において、パラレル伝送線路には、データバス、要求バス、基準電圧( $V_{Ref}$ )線路、マスタへのクロック(clock to master)(CTM)線路、マスターからのクロック(clock from master)(CFM)線路およびシリアル(serial)バスが含まれる。他の実施形態において、バスまたは伝送線路の追加または他の構成を用いてもよい。メモリ装置104(たとえばDRAM、RDRAM)は、別個のメモリチップまたはメモリモジュール112(たとえばSIMM、DIMM、RIMM、C-RIMM)の一部とすることができます。図1Aは、RDRAMと共に典型的に用いられるメモリシステムアーキテクチャを示すが、開示される技術が、多重アクセスレイテンシ時間と伴う任意のメモリシステムアーキテクチャ(たとえばDDR、DDR-II等)に適用可能であることに留意されたい。

【0012】

いくつかの実施形態において、メモリコントローラ102には、メモリ装置104と通信するための高速メモリインターフェース106が含まれる。メモリ装置104のそれには、コマンドインターフェース108が含まれ、このインターフェース108にはプログラマブル遅延装置110が含まれるが、この遅延装置110は、アクセスレイテンシ時間を調節するために必要な遅延を提供するように構成することができる。メモリ装置104は、メモリコントローラ102から異なる電気的距離に存在し、結果として、メモリ装置104とメモリコントローラ102との間で、信号の異なるライト時間をもたらしてもよい。メモリ装置104はまた、異なるCASレイテンシレイテンシ時間をサポートし、メモリコントローラ102によるアクセスレイテンシレイテンシ時間の差を導いても

よい。いくつかの実施形態において、各メモリ装置 104 のそれぞれのプログラマブル遅延装置 110 は、それぞれの指定された期間の間、出力データを格納するように構成され、アクセスされたメモリ装置に依存しない時間に、データが、メモリアクセス動作に応じてメモリコントローラ 102 に到達するようにする。したがって、メモリシステム 100 における各メモリ装置 104 は、メモリシステム 100 における最大レイテンシ時間のメモリ装置 104 ( すなわちメモリ装置 104 - N ) と同じレイテンシ時間  $L_G$  で応答する。

#### 【 0013 】

いくつかの実施形態において、遅延装置 110 は、周知のプログラマブル遅延装置および設計技術を用いて実現される。しかしながら、クロック速度が増加するにつれて、メモリ装置 104 および / またはメモリコントローラ 102 の設計に著しい影響 ( たとえばサイズの増加 ) を与えることも、システムを限られた数のメモリ装置 104 に制限することもなく、グローバルレベルライゼーションに必要とされる遅延を提供できる遅延装置 110 を設計することは、ますます困難になる。いくつかの実施形態において、遅延装置 100 は、指定されたクロックサイクル数だけ出力データ信号を遅延させるために、シフトレジスタおよび出力マルチプレクサを用いて実現される。指定されたクロックサイクル数は、遅延装置が埋め込まれているメモリ装置のレジスタに格納される。いくつかの実施形態において、レジスタは、初期化中に、メモリコントローラ 102 によって実行されるレジスタ書き込み動作を介してロードされ得る。他の実施形態において、レジスタは、メモリコントローラ 102 によってメモリ装置へ送られるコマンドに符号化される可変遅延をロードされ得る。クロックサイクル数は、初期化中に、メモリコントローラ 102 から最も遠いメモリ装置のメモリアクセスレイテンシ時間を計算することによって、決定することができる。

#### 【 0014 】

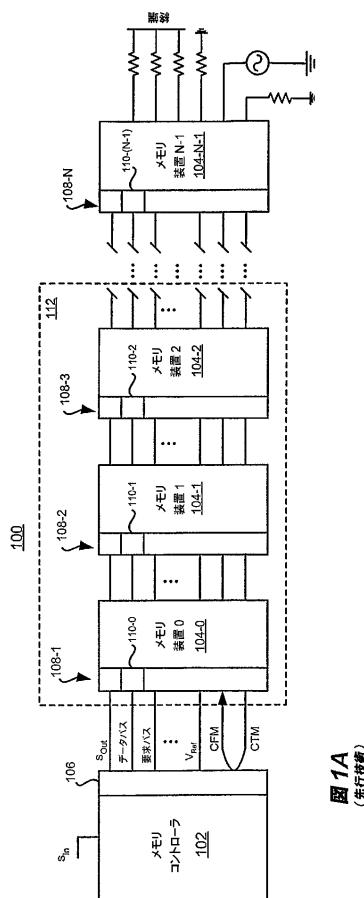

グローバルレベルライゼーションを用いるメモリシステムを含む従来のメモリシステムでは、メモリアドレスは、従来のやり方でメモリ装置 104 に割り当てられる。図 1B に示すように、従来のメモリ割り当て方式は、オペレーティングシステム ( OS ) 手順を低アドレス ( より多くのメモリが必要とされるにつれて上に行く ) に割り当て、アプリケーションプログラムを高アドレス ( より多くのメモリが必要とされるにつれて下に行く ) に割り当ててもよい。さらに、メモリアドレスは、 ( マップ 114 に示すように ) 、線形的なやり方でメモリ装置 104 にマップされ、最低アドレスが、チャネルの一端部におけるメモリ装置 ( たとえば、メモリコントローラ 102 に最も近いメモリ装置 ) にマップされ、最高アドレスが、チャネルのもう一方の端部におけるメモリ装置にマップされる。図 1B に示す例では、メモリ空間の一部分がオペレーティングシステムおよびアプリケーションによって用いられているだけであり、それは、多くのコンピュータシステムの通常動作中には、典型的である。上記のアドレスマッピング方式は、OS 手順が、メモリコントローラ 102 に最も近いメモリ装置 104 に格納され、最も頻繁に用いられるアプリケーションプログラムが、メモリコントローラ 102 から最も遠く離れたメモリ装置 104 に格納されるという結果になる。このメモリ割り当て手法は、アクセスレイテンシ時間  $L_G$  がアクセスされるメモリ装置に依存しないので、グローバルレベルライゼーションを備えたメモリシステムを用いるコンピュータでは問題ではない。しかしながら、このメモリ割り当て手法は、異なるメモリ装置が異なるアクセスレイテンシ時間を持つシステムでは、次善的に作動することになり得る。

#### 【 0015 】

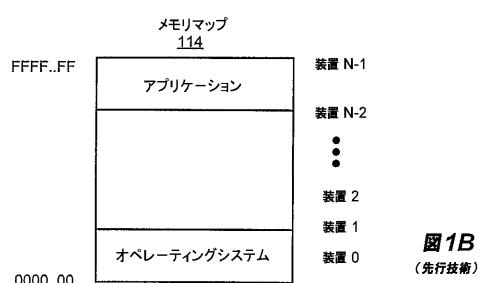

##### グループレベルライゼーション

図 2A は、領域ベースのグループレベルライゼーションを用いるメモリシステム 200 のブロック図である。メモリシステム 200 は、メモリアドレスがメモリ装置 104 にマップされる方法を除いて、メモリシステム 100 と同様である。さらに、システム 200 では、プログラマブル遅延装置 110 は、各レイテンシ時間グループにおけるメモリ装置が共通のアクセスレイテンシ時間を持つように、構成されているが、しかし、各レイテン

10

20

30

40

50

シ時間グループは、別個のアクセスレイテンシ時間有し、メモリコントローラ202に最も近いレイテンシ時間グループにおける装置が、メモリコントローラ202から最も遠いレイテンシ時間グループにおける装置より短いアクセスレイテンシ時間有する。

【0016】

メモリシステム200において、メモリコントローラ102に最も近いメモリ装置104（たとえば、装置104-0、104-1および104-2）は、頻繁にアクセスされるメモリ位置（たとえば、アプリケーションプログラムおよびオペレーティングシステムによって用いられるアドレス位置）にマップされるか又は割り当てられ、メモリコントローラから最も遠いメモリ装置104（たとえば104-5から104-N）は、アクセス頻度のより少ないメモリアドレスにマップされるか又は割り当てられる。最初に最短レイテンシ時間グループから優先的にメモリを割り当てるこによって、オペレーティングシステムが、このマッピングを利用し、性能を改善できることに留意されたい。また、メモリが満杯である場合には、オペレーティングシステムは、メモリのどのエリアが最も頻繁にアクセスされるかを監視し、次に、より短いレイテンシ時間グループとより長いレイテンシ時間グループとの間であちこちにデータを移動させて、性能を改善することができる。また、メモリシステムの動作を監視し、メモリ帯域幅ニーズおよびアプリケーションのメモリ占有量などの要素の関数として最適な平均システムレイテンシ時間を決定することによって、各レイテンシ時間グループにおける装置の数を動的に変更してシステム性能を最適化し、次に、装置の再割り当てが予測されるシステム性能を改善するであろう場合には、レイテンシ時間グループ間で装置を再割り当てすることが可能である。

10

20

30

40

【0017】

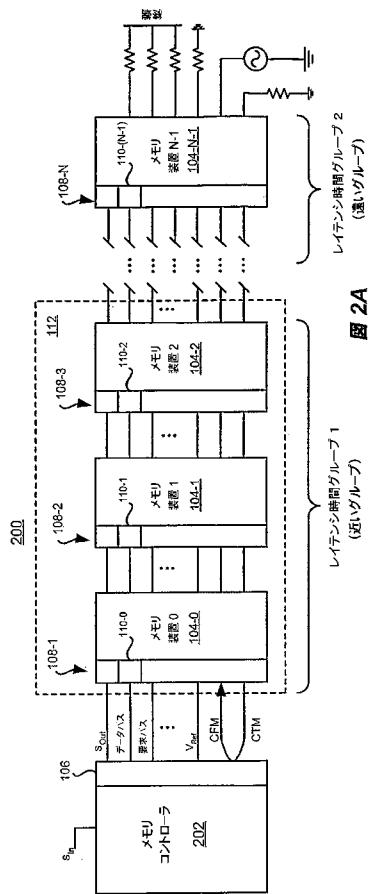

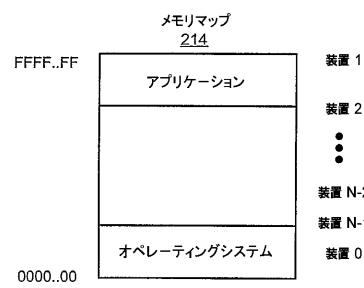

図2Bは、グループレベルライゼーションと共に用いるためのメモリマップ214を示す。装置1および2（104-1および104-2）は、アプリケーションプログラム用のアドレスにマップされ、一方で、装置5からN（104-5から104-N）は、アクセス頻度のより少ないメモリアドレスにマップされる。OS手順が、アプリケーションプログラムよりさらに一層頻繁にアクセスされるので、チャネルの第1の装置（装置0）にやはりマップされることに留意されたい。より一般的には、OS手順および最も頻繁に用いられるアプリケーションプログラム用のアドレスは、最短レイテンシ時間グループG<sub>1</sub>におけるメモリ装置にマップされる。レイテンシ時間グループは、次に論じる。

【0018】

メモリ装置104をメモリアドレス空間における部分に割り当てるに加えて、各メモリ装置104は、異なるレイテンシ時間をそれぞれ有するレイテンシ時間グループG<sub>1</sub>...G<sub>N</sub>のセットのうちの1つに割り当てられる。たとえば、図2Aでは、チャネルは、以下ではレイテンシ時間グループG<sub>1</sub>（近いグループ）およびG<sub>2</sub>（遠いグループ）と呼ばれる、メモリ装置104の2つのレイテンシ時間グループに分割される。レイテンシ時間グループG<sub>1</sub>に割り当てられたメモリ装置104は、グループにおける最大レイテンシ時間装置のレイテンシ時間L<sub>1</sub>（クロックサイクルで測定される）に均一化され、一方で、レイテンシ時間グループG<sub>2</sub>に割り当てられたメモリ装置104は、グループG<sub>2</sub>における最大レイテンシ時間装置のレイテンシ時間L<sub>2</sub>に均一化される。いくつかの実施形態において、レイテンシ時間L<sub>2</sub>は、グループG<sub>1</sub>のL<sub>1</sub>レイテンシ時間よりNクロックサイクル長い、すなわちL<sub>2</sub>=L<sub>1</sub>+Nであるが、ここで、Nは、限定するわけではないが、コントローラクロックサイクルに対するメモリバスクロックサイクルの比率、クロックサイクルでのデータパケット長さ、およびレイテンシ時間差を始めとする様々な基準に基づいて選択され、一方で、遅延装置は、グループG<sub>2</sub>における最大レイテンシ時間装置とグループG<sub>1</sub>における最大レイテンシ時間装置との間で、ゼロ遅延に設定される。いくつかの実施形態において、Nは4に等しいが、それは、RDRAM装置を用いる少なくともいくつかのメモリシステムのメモリバスクロックサイクルにおけるデータパケット長さである。

【0019】

レイテンシ時間L<sub>1</sub>およびNは、限定するわけではないが、システム構成、メモリ装置

50

のランク数、装置密度、マザーボードレイアウト、フロントサイドバス（FSB）速度、メモリバス速度、メモリコントローラクロック速度、フロントサイドバスのタイミングに合致するために必要なレイテンシ時間、およびメモリ装置104の転送速度を始めとする多くの要素に基づいて決定することができる。特定のレイテンシ時間グループに割り当てるメモリ装置104の数は、アプリケーションに基づき、必要に応じて設定することができる。かくして、次の式、

$$L_1 < L_G \leq L_2 \quad (1)$$

が満たされる場合には、グループプレベライゼーションを用いることにより、レイテンシ時間 $L_G$ を有するグローバルプレベライゼーションと比較して、潜在的な性能の改善が得られる。

10

#### 【0020】

上記の実施形態が2つのレイテンシ時間グループを有するのに対して、他の実施形態では、3以上のレイテンシ時間グループが用いられる。

#### 【0021】

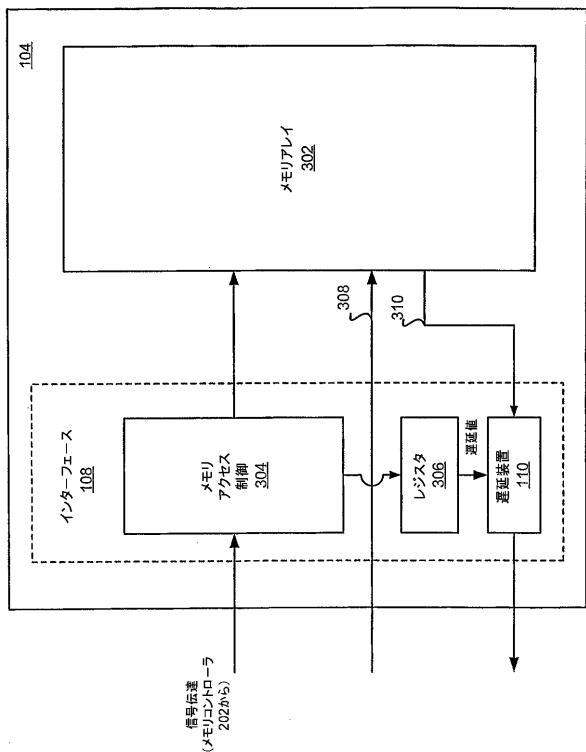

図3は、グループプレベライゼーションで用いるメモリ装置104のブロック図である。メモリ装置104には、一般に、メモリアレイ302に結合されたコマンドインターフェース108が含まれる。コマンドインターフェース108には、メモリコントローラ202から受信された信号を処理するための、およびメモリアレイ302にメモリアクセスコマンド（たとえば、読み出し、書き込み）を供給するためのメモリアクセス制御部304が含まれる。メモリ装置104には、入力および出力データバス308および310が含まれる。出力データバス310は、プログラマブル遅延装置110に結合され、遅延装置110は、メモリアレイ302から検索したデータを、レジスタ306に格納された遅延値に従って遅延させる。遅延値（クロックサイクルで測定できる）は、図4に関連して説明するように、メモリコントローラ202が送るレイテンシ時間制御信号によって決定される。

20

#### 【0022】

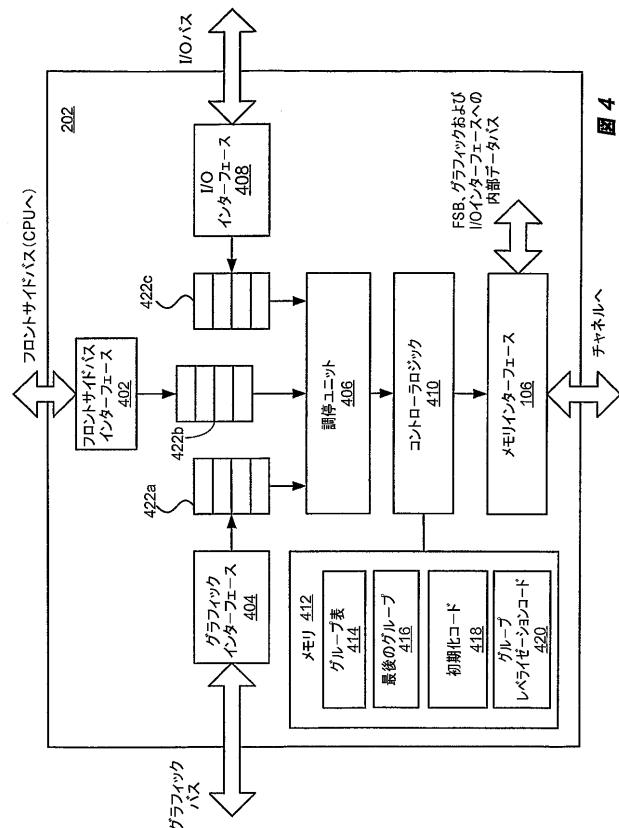

図4は、グループプレベライゼーションで用いるメモリコントローラ202の一実施形態のブロック図である。いくつかの実施形態において、メモリコントローラ202には、フロントサイドバスインターフェース402（たとえば、データプロセッサまたはCPUとの通信を取り扱うための）、グラフィックインターフェース404（たとえばAGPインターフェース）、I/Oインターフェース408、調停ユニット406、コントローラロジック410、メモリ412、および高速メモリインターフェース106が含まれる。いくつかの実施形態では、これらの構成要素の1つまたは複数が、コントローラには含まれない（たとえば、フロントサイドバスインターフェースは、コントローラ202がCPUと一体化されているインプリメンテーションでは省略してもよい）。コントローラロジック410は、メモリ412に結合されるが、メモリ412には、グループ表414、最後のグループ416、初期化コード418、およびグループプレベライゼーションコード420が含まれる。図4が、メモリコントローラの一特定実施形態を表わすことに留意されたい。開示されるグループプレベライゼーション技術は、多くのタイプのメモリコントローラ（たとえば、インテル（Intel）プロセッサ、AMDプロセッサ、GPU、ネットワークプロセッサ等と共に用いられるメモリコントローラ）を用いて利用することができる。いくつかの実施形態において、初期化コード418およびグループプレベライゼーションコード420は、BIOS EEPROMに格納されるが、このBIOS EEPROMは、バスまたは他の相互接続構造を介してメモリコントローラ202に結合される別個のチップとすることができます。

30

#### 【0023】

メモリコントローラ202の初期化中に、初期化コード418は、コントローラロジック410によって実行される。初期化コードは、メモリ装置をレイテンシ時間グループに割り当てる役割、したがって、グループ表414のエントリ部に記入する役割を担う。グループ表414のフォーマットおよび内容は、以下でより詳細に論じる。いくつかの実施

40

50

形態において、グループ表 414 は、静的表ではなく、システムが起動されるたびに動的に作成され、システムにおける変更（たとえば、メモリが追加されたかまたは除去されたかも知れない）を明らかにする。他の実施形態において、グループ表 414 は、メモリアクセス頻度が変化するとともに、変更することができる。

【0024】

また、初期化中に、グループレベルライゼーションコード 420 は、各レイテンシ時間グループにおける全てのメモリ装置が確かに同じレイテンシ時間有するように、実行される。システムが最初に起動されたとき、特定のレイテンシ時間グループにおける第 1 の装置へのアクセスレイテンシ時間は、グループにおける最後の装置へのアクセスレイテンシ時間より短くてもよい。グループレベルライゼーションコード 420 は、同じグループにおける全てのメモリ装置にわたってレイテンシ時間を均一化する役割を担う。そうするためには、グループレベルライゼーションコード 420 は、グループにおけるメモリ装置のそれぞれにどれだけの遅延（必要ならば）を加えるかを決定して、メモリ装置が、グループにおける最大レイテンシ時間メモリ装置のレイテンシ時間と一致するようにする。最短レイテンシ時間を有する、各グループのメモリ装置は、グループレベルライゼーションコードの制御下で、たとえば、レジスタ 306（図 3）にしかるべき値を格納することによって、自身の遅延装置 110（図 3）を構成してもよい。その後、このプロセスは、各レイテンシ時間グループに対して繰り返される。いくつかの実施形態において、グループレベルライゼーションコードは、初期化コード 418 の一部として実行される。

【0025】

動作中に、メモリ要求は、インターフェース 402、404 および 408 を介して受信され、キュー 422 に格納される。キュー 422 に格納されたメモリ要求は、従来の調停技術（たとえば、ラウンドロビン、優先権等）を用い、調停ユニット 406 によってメモリアクセス競合に対して検査される。調停ユニット 406 は、キュー 422 に格納された要求からメモリ要求を選択し、選択されたメモリ要求をコントローラロジック 410 へ転送する。その後、選択されたメモリ要求の N-ビットアドレス（たとえば 28 ビット、32 ビットまたは 64 ビットアドレス）が、特定のメモリ装置 104 の特定のバンク、行および列にアクセスするために復号される。サンプルアドレスマッピング（すなわち N アドレスビットのマップ）を、以下の表 I に示す。

【0026】

【表 1】

表 I

サンプルアドレスマッピング

| ビット N-1 | ビット 0 |     |   |

|---------|-------|-----|---|

| 装置 ID   | 行     | バンク | 列 |

|         |       |     |   |

10

20

30

40

【0027】

アドレスの装置 ID フィールドには、メモリシステム 200 における特定のメモリ装置を示す値が含まれ、バンクフィールドには、装置 ID によって識別されたメモリ装置内のサブアレイを示す値が含まれ、行および列フィールドには、装置 ID およびバンク値に関連するメモリバンクにおける特定の位置を識別する値が含まれる。しかしながら、次に説明するように、装置 ID の値は、メモリシステムにおける関連メモリ装置の物理的位置は特定しない。

【0028】

コントローラロジック 410 は、（たとえばビットマスキング技術を用いて）メモリアクセス頻度が変化するとともに、変更することができる。

50

ドレスから装置IDを抽出し、それをグループ表414への索引として用いる。グループ表は、それぞれのメモリ装置が割り当てられているレイテンシ時間グループを示す、各メモリ装置それぞれのためのエントリ部を有する。いくつかの実施形態において、グループ表414は、(図2に関した)以下の表IIに示すフォーマットを有する。

【0029】

【表2】

表II

グループデータ構造

| 装置ID | レイテンシ時間<br>グループ |

|------|-----------------|

| 0    | 近いグループ( $G_1$ ) |

| 1    | 遠いグループ( $G_2$ ) |

| 2    | 遠いグループ( $G_2$ ) |

| •    | •               |

| N-2  | 近いグループ( $G_1$ ) |

| N-1  | 近いグループ( $G_1$ ) |

10

物理装置

0

N-2

N-1

20

1

30

2

【0030】

グループ表414は、図6に関連して説明するプロセスを用いて、メモリアドレス(それらの装置IDによって表わされる)と、メモリ装置104を割り当てられているレイテンシ時間グループ $G_1, \dots, G_N$ との間のマッピングを提供する。表IIはまた、物理メモリ装置、すなわちそれらの装置IDおよびグループ値がグループ表に格納されている物理メモリ装置の位置を示すのに対して、いくつかの実施形態(たとえば、ここでは、メモリ装置が、それらの装置IDを用いてアドレス指定される)では、物理メモリ位置は、グループ表414に格納されない。他の実施形態において、グループ表414は、各メモリ装置の物理位置を格納する。

【0031】

メモリアクセス要求のための物理メモリ装置およびレイテンシ時間グループが、グループ表414から一旦決定されると、連続するメモリアクセス要求が異なるグループに向かっている場合には、データバス衝突を回避するために、それらの要求を遅延させが必要であり得る。連続する要求のレイテンシ時間グループが異なる場合、および特に、現在のメモリ要求が、前のメモリアクセス要求(最後のグループのデータ構造416に格

40

50

納されたデータによって識別される)のレイテンシ時間グループより短いレイテンシ時間グループのメモリ装置におけるデータを読み出す要求である場合には、コントローラロジック410は、直前および現在のメモリアクセスコマンドによって返されるデータ間の衝突を回避するのに十分な時間量だけ、現在のメモリアクセスコマンドの传送を遅延させる。より一般的には、現在および前のメモリアクセス要求のグループレイテンシ時間用いて、前のメモリアクセス要求の传送と現在のメモリアクセス要求の传送との間の最小時間遅延を決定することができる。現在および前のメモリアクセス要求間の時間が、決定された最短時間遅延より短い場合には、現在のメモリアクセストランザクションの传送は、少なくとも最短時間遅延が、前のメモリアクセス要求の传送から経過するまで、遅延されなければならない。メモリアクセスが、要求が連続ではなく、十分な時間量だけ分離されている場合には、データバス衝突がないはずなので、後のメモリアクセス要求を遅延させる必要はない。

10

#### 【0032】

連続するメモリアクセス要求間の遅延は、多くの方法で実行可能であり、これらの方法には、メモリアクセスコマンドを送る前の、コントローラロジック410による、または指定された時間量(たとえば、指定されたコントローラクロックサイクル数、または指定されたメモリバスサイクル数)だけメモリアクセスコマンドの传送を遅延させるために、メモリインターフェース106にタイミング回路をプログラムすることによる、定義済みの数の「ノーオペレーション」コマンドの実行などがある。

20

#### 【0033】

上記の技術を用いることにより、メモリ装置104-0、104-1および104-2にマップされたメモリアドレスへのメモリ要求は、グローバルレベライゼーションによって提供されるレイテンシ時間 $L_G$ より短いグループレイテンシ時間 $L_1$ を有する。同様に、メモリ装置104-5から104-Nにマップされたメモリアドレスへのメモリ要求は、グローバルレベライゼーションによって提供されるレイテンシ時間 $L_G$ 以上のグループレイテンシ時間 $L_2$ を有する。

#### 【0034】

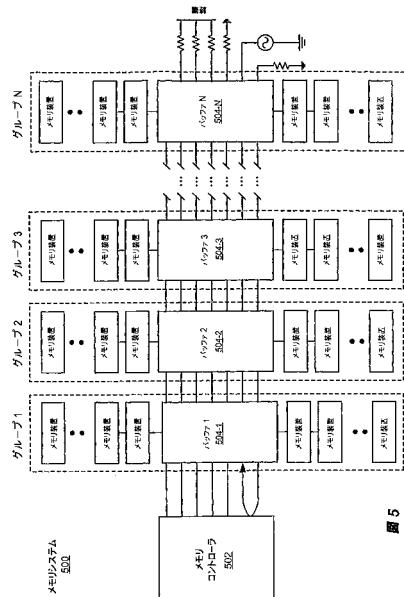

図5は、グループレベライゼーションを用い、かつ容量の増加および/またはよりよいシグナルインテグリティのためのバッファを含むメモリシステム500のブロック図である。メモリシステム500には、一般に、直列接続バッファ504に結合されたメモリコントローラ502が含まれる。各バッファは、1つまたは複数のメモリ装置に結合され、これらのメモリ装置は、共同でメモリモジュールを形成する。いくつかの実施形態において、グループレベライゼーションは、各個別のメモリモジュールを、それ自身のレイテンシ時間グループに指定することによって実現することができる。他の実施形態において、バッファに最も近い、モジュール内のメモリ装置は、あるレイテンシ時間グループにあってもよく、一方で、バッファからさらに遠い、同じモジュールのメモリ装置は、別のレイテンシ時間グループにあってもよい。この構成では、異なるモジュールにおけるメモリ装置のサブセットが、同じレイテンシ時間グループにあることができる。あるいは、多数のメモリモジュールを、同じレイテンシ時間グループに割り当てることができる。

30

#### 【0035】

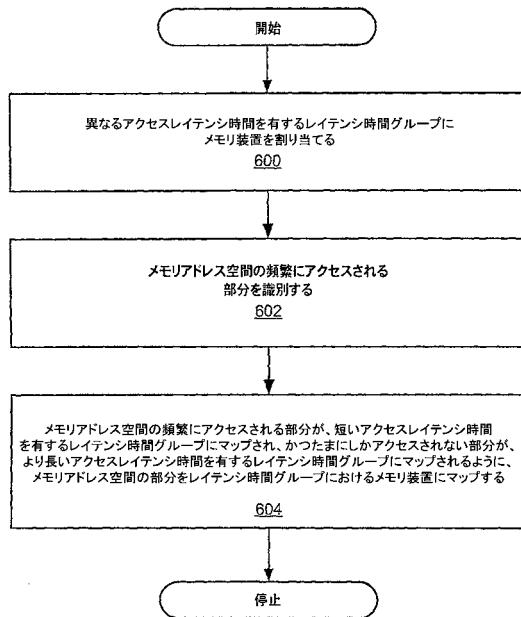

図6は、グループレベライゼーションを用いるメモリシステム200で使用するメモリ装置にメモリアドレスを割り当てるプロセスの流れ図である。いくつかの実施形態において、メモリ装置にメモリアドレスを割り当てるプロセスは、メモリシステム200の初期化中に生じる。このプロセスは、メモリ装置104をレイテンシ時間グループ $G_1, \dots, G_N$ に割り当てる(ステップ600)によって始まる。任意の数のレイテンシ時間グループ $G_1, \dots, G_N$ が存在でき、各グループは、異なるレイテンシ時間有する。次に、メモリシステム200のメモリアドレス空間における最も頻繁にアクセスされる部分が、識別される(ステップ602)。これは、監視装置(たとえばメモリアクセス監視回路)、監視ソフトウェア、またはメモリアクセス要求を監視しかつメモリアドレス空間の様々な部分に対するメモリアクセス頻度を決定する、メモリコントローラにおける監視ロジ

40

50

ックを用いて、システム開発中または実行中に行なわれる実験を介して達成できる。最終ステップには、メモリアドレス空間の識別された部分を、割り当てられたレイテンシ時間グループにおけるメモリ装置 104 へマップするステップ 604 が含まれる。これによって、最も頻繁にアクセスされるアドレス（または、より正確には、最も頻繁にアクセスされるアドレス領域）が、メモリコントローラ 202 に最も近いメモリ装置にマップされ、平均アクセスレイテンシ時間が短縮されるという結果になる。アクセス頻度は経時に変化する可能性があることに留意されたい。したがって、従来のグローバルレベルライゼーション技術より優れたグループレベルライゼーション技術の利点は、メモリアクセス頻度の監視に基づいて、メモリアドレスマッピングを動的に変更する能力である。換言すれば、いくつかの実施形態において、ステップ 602 および 604 を適切な時に再実行して、最も頻繁にアクセスされるアドレス領域を、最小レイテンシ時間有するレイテンシ時間グループへ、またはより一般的には、少なくとも 1 つの他のレイテンシ時間グループのレイテンシ時間より小さな関連レイテンシ時間有するレイテンシ時間グループへ再マップするようとする。

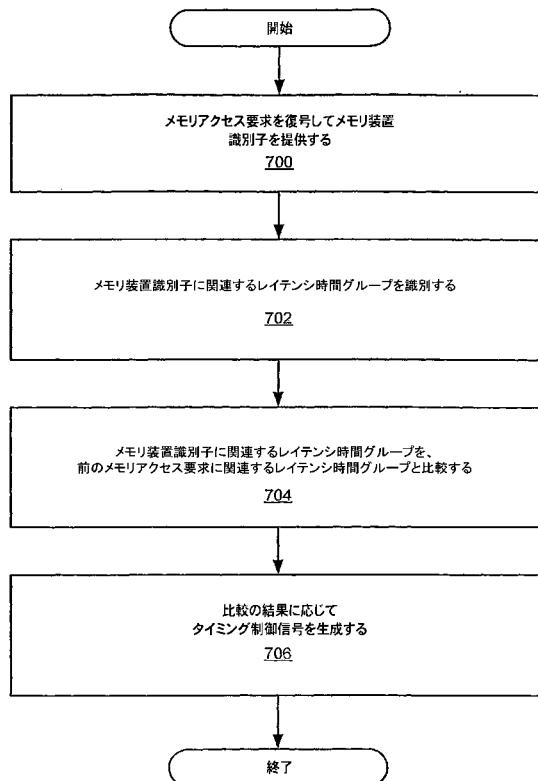

#### 【0036】

図 7 は、グループレベルライゼーションを用いるメモリシステム 200 においてレイテンシ時間を制御するプロセスの流れ図である。いくつかの実施形態では、グループレベルライゼーションを用いるメモリシステム 200 においてレイテンシ時間を制御するプロセスは、メモリシステム 200 の動作中に生じる。このプロセスは、メモリアクセス要求を復号してメモリ装置 ID を提供すること（ステップ 700）によって始まる。メモリシステム 200 は、メモリ装置識別子に関連するレイテンシ時間グループを識別する（ステップ 702）。いくつかの実施形態において、このステップは、表 I I に示す構造を有するグループ表 414 への索引としてメモリ装置 ID を用いることによって、達成される。一旦レイテンシ時間グループが識別される（ステップ 702）と、それは、前のメモリアクセス要求に関連するレイテンシ時間グループおよび前のメモリアクセス要求の時間と比較される（ステップ 704）。比較（ステップ 704）に応じて、タイミング制御信号が生成される（ステップ 706）。より具体的には、現在のメモリ要求が、現在の要求の直前のメモリ読み出し要求より短いレイテンシ時間グループのメモリ装置におけるデータを読み出す要求である場合には、タイミング制御信号は、コントローラロジックに、直前および現在のメモリアクセスコマンドによって返されるデータ間の衝突を回避するのに必要な時間量だけ、現在のメモリアクセスコマンドの伝送を遅延させる。

#### 【0037】

いくつかのシステムにとっては、データバス衝突を回避するために、多数の前のトランザクションとの比較が必要であり得る。メモリシステムの最大グループレイテンシ時間と最小グループレイテンシ時間との差が大きい（多数のメモリバスサイクル）場合には、ステップ 704 は、現在のメモリ要求のレイテンシ時間グループを、K の前のメモリアクセスコマンドのそれぞれのレイテンシ時間グループと比較することが必要になり得るが、ここで、K は、潜在的に現在のメモリアクセス要求と干渉する可能性がある前のメモリアクセス要求の最大数を表わす。さらに、現在のメモリ要求が遅延される量は、あるとすると、潜在的に衝突するメモリ要求が生じた時間と同様に、潜在的に衝突するメモリ要求間のレイテンシ時間における差の関数である。たとえば、メモリシステムの最大グループレイテンシ時間と最小グループレイテンシ時間との差が、8 メモリバスサイクルである場合、および各読み出し要求が、メモリバスで 4 メモリバスサイクルを占める場合には、コントローラロジックは、データバス衝突が生じないことを保証するために、現在のレイテンシ時間グループを、多数の前のメモリアクセス要求と比較する必要があるであろう。現在のメモリアクセス要求が、前のメモリアクセスのいずれかと干渉すると分かった場合には、現在のメモリアクセス要求のためのメモリアクセスコマンドの伝送は、前および現在のメモリアクセス要求に応じて返されるデータの衝突を回避するのに必要な時間量（たとえば、ある数のコントローラクロックサイクルまたはある数のメモリバスサイクル）だけ、遅延される。

10

20

30

40

50

## 【0038】

前述の記載は、説明のために、特定の実施形態に関連して記載した。しかしながら、上記の例証的な説明は、包括的であるようにも、本発明を開示された形態に正確に限定するよりも意図されていない。上記の教示に鑑みて、多くの変更および変形が可能である。これらの実施形態は、本発明の原理およびその実際的な適用例を最も良く説明し、それによって、他の当業者が、本発明、および意図された特定の用途に適した様々な変更を伴う様々な実施形態を最も良く利用できるようにするよう選択され記載されたものである。

## 【図面の簡単な説明】

## 【0039】

【図1A】グローバルレベライゼーションを用いるメモリシステムのブロック図である。 10

【図1B】グローバルレベライゼーションを用いるメモリシステムのメモリマップである。

【図2A】グループプレベライゼーションを用いるメモリシステムのブロック図である。

【図2B】グループプレベライゼーションを用いるメモリシステムのメモリマップである。

【図3】グループプレベライゼーションで用いるメモリ装置のブロック図である。

【図4】グループプレベライゼーションで用いるメモリコントローラのブロック図である。

【図5】グループプレベライゼーションを用い、かつ容量増加用のバッファを含むメモリシステムのブロック図である。

【図6】グループプレベライゼーションを用いるメモリシステムで用いられるメモリ装置に、メモリアドレスを割り当てるプロセスの流れ図である。 20

【図7】グループプレベライゼーションを用いるメモリシステムにおいてレイテンシ時間制御するプロセスの流れ図である。

【図1A】

【図1B】

図1B

(先行技術)図1A

(先行技術)

【 図 2 A 】

【 図 3 】

【 図 2 B 】

圖 2B

【 図 4 】

【図5】

図5

【図6】

図6

【図7】

図7

## 【国際調査報告】

## INTERNATIONAL SEARCH REPORT

PCT/US2005/018246

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                               |                                                                                |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|

| A. CLASSIFICATION OF SUBJECT MATTER<br>G11C7/00                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                               |                                                                                |

| According to International Patent Classification (IPC) or to both national classification and IPC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                               |                                                                                |

| B. FIELDS SEARCHED<br>Minimum documentation searched (classification system followed by classification symbols)<br>G11C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                               |                                                                                |

| Documentation searched other than minimum documentation to the extent that such documents are included in the fields searched                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                               |                                                                                |

| Electronic data base consulted during the International search (name of data base and, where practical, search terms used)<br>EPO-Internal, WPI Data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                               |                                                                                |

| C. DOCUMENTS CONSIDERED TO BE RELEVANT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                               |                                                                                |

| Category *                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Citation of document, with indication, where appropriate, of the relevant passages            | Relevant to claim No.                                                          |

| A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | US 2003/085744 A1 (HEO NAK WON ET AL)<br>8 May 2003 (2003-05-08)<br>the whole document        | 1-37                                                                           |

| A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | US 2003/061459 A1 (ABOULENEIN NAGI ET AL)<br>27 March 2003 (2003-03-27)<br>the whole document | 1-37                                                                           |

| <input type="checkbox"/> Further documents are listed in the continuation of box C.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                               | <input checked="" type="checkbox"/> Patent family members are listed in annex. |

| <p>* Special categories of cited documents :</p> <p>"A" document defining the general state of the art which is not considered to be of particular relevance</p> <p>"E" earlier document but published on or after the international filing date</p> <p>"L" document which may throw doubts on priority claim(s) or which is cited to establish the publication date of another citation or other special reason (as specified)</p> <p>"O" document referring to an oral disclosure, use, exhibition or other means</p> <p>"P" document published prior to the international filing date but later than the priority date claimed</p> <p>"T" later document published after the International filing date or priority date and not in conflict with the application but cited to understand the principle or theory underlying the invention</p> <p>"X" document of particular relevance; the claimed invention cannot be considered novel or cannot be considered to involve an inventive step when the document is taken alone</p> <p>"Y" document of particular relevance; the claimed invention cannot be considered to involve an inventive step when the document is combined with one or more other such documents, such combination being obvious to a person skilled in the art.</p> <p>"&amp;" document member of the same patent family</p> |                                                                                               |                                                                                |

| Date of the actual completion of the international search                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Date of mailing of the International search report                                            |                                                                                |

| 16 November 2005                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 11/01/2006                                                                                    |                                                                                |

| Name and mailing address of the ISA<br>European Patent Office, P.B. 5818 Patentlaan 2<br>NL - 2280 HV Rijswijk<br>Tel. (+31-70) 340-2040, Tx. 31 651 epo nl,<br>Fax: (+31-70) 340-3016                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Authorized officer<br>Arnault, S                                                              |                                                                                |

## INTERNATIONAL SEARCH REPORT

Information on patent family members

International Application No

PCT/US2005/018246

| Patent document cited in search report | Publication date |            | Patent family member(s)                                             | Publication date                                     |

|----------------------------------------|------------------|------------|---------------------------------------------------------------------|------------------------------------------------------|

| US 2003085744                          | A1               | 08-05-2003 | DE 10252491 A1<br>JP 2003203481 A<br>KR 2003037675 A<br>TW 578381 B | 28-05-2003<br>18-07-2003<br>14-05-2003<br>01-03-2004 |

| US 2003061459                          | A1               | 27-03-2003 | EP 1481326 A2<br>WO 03027867 A2                                     | 01-12-2004<br>03-04-2003                             |

---

フロントページの続き

(81)指定国 AP(BW,GH,GM,KE,LS,MW,MZ,NA,SD,SL,SZ,TZ,UG,ZM,ZW),EA(AM,AZ,BY,KG,KZ,MD,RU,TJ,TM),EP(AT,BE,BG,CH,CY,CZ,DE,DK,EE,ES,FI,FR,GB,GR,HU,IE,IS,IT,LT,LU,MC,NL,PL,PT,RO,SE,SI,SK,TR),OA(BF,BJ,CF,CG,CI,CM,GA,GN,GQ,GW,ML,MR,NE,SN,TD,TG),AE,AG,AL,AM,AT,AU,AZ,BA,BB,BG,BR,BW,BY,BZ,CA,CH,CN,CO,CR,CU,CZ,DE,DK,DM,DZ,EC,EE,EG,ES,FI,GB,GD,GE,GH,GM,HR,HU,ID,IL,IN,IS,JP,KE,KG,KM,KP,KR,KZ,LK,LR,LS,L,T,LU,LV,MA,MD,MG,MK,MN,MW,MX,MZ,NA,NG,NI,NO,NZ,OM,PG,PH,PL,PT,RO,RU,SC,SD,SE,SG,SK,SL,SM,SY,TJ,TM,TN,TR,TT,TZ,UA,UG,US,UZ,VC,VN,YU,ZA,ZM,ZW

(72)発明者 ツアン, ブライアン エイチ.

アメリカ合衆国, カリフォルニア州 94303, イースト パロ アルト, ベインズ ストリー

ト 945

F ターム(参考) 5B005 JJ12 MM31 UU41

5B060 AA08 MM03