(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第3797397号

(P3797397)

(45) 発行日 平成18年7月19日(2006.7.19)

(24) 登録日 平成18年4月28日(2006.4.28)

(51) Int.C1.

F 1

HO4J 11/00 (2006.01)

HO4L 7/00 (2006.01)HO4J 11/00

HO4L 7/00

Z

F

請求項の数 4 (全 17 頁)

(21) 出願番号

特願平9-114710

(22) 出願日

平成9年5月2日(1997.5.2)

(65) 公開番号

特開平10-308715

(43) 公開日

平成10年11月17日(1998.11.17)

審査請求日

平成15年10月23日(2003.10.23)

(73) 特許権者 000002185

ソニー株式会社

東京都品川区北品川6丁目7番35号

(74) 代理人 100082131

弁理士 稲本 義雄

(72) 発明者 百代 俊久

東京都品川区北品川6丁目7番35号 ソ

ニー株式会社内

(72) 発明者 岡田 隆宏

東京都品川区北品川6丁目7番35号 ソ

ニー株式会社内

(72) 発明者 池田 康成

東京都品川区北品川6丁目7番35号 ソ

ニー株式会社内

最終頁に続く

(54) 【発明の名称】受信装置および受信方法

## (57) 【特許請求の範囲】

## 【請求項 1】

振幅および位相が規定されたパイロット信号が各シンボル毎に含まれたO F D M信号を受信する受信装置であって、

前記O F D M信号を離散的フーリエ変換する変換手段と、

前記変換手段により得られた副搬送波の周波数成分を記憶する記憶手段と、

前記記憶手段に記憶されている少なくとも1シンボル前の前記周波数成分と、前記変換手段により新たに得られた周波数成分との間の位相変動量を算出する算出手段と、

前記算出手段により算出された位相変動量より、前記パイロット信号に対応する成分を抽出する抽出手段と、

前記受信装置において使用されるクロック信号を発生するクロック信号発生手段であって、クロック信号の周波数が制御可能なクロック信号発生手段と、

前記抽出手段により抽出された前記パイロット信号に対応する位相変動量を複数のパイロット信号にわたって累積加算し、この累積加算された信号に応じて前記クロック信号発生手段を制御して前記クロック信号の周波数を制御する制御手段と

を備えることを特徴とする受信装置。

## 【請求項 2】

前記抽出手段により抽出されたパイロット信号系列に対応する位相変動量が所定の値以下になったことを検出する検出手段と、

前記検出手段により前記位相変動量が所定の値以下になったことが検出された場合には

、前記記憶手段に記憶されている副搬送波の周波数成分の変更を禁止する禁止手段とを更に備える

ことを特徴とする請求項1に記載の受信装置。

**【請求項3】**

基底帯域に変換されたO F D M時間信号を有効シンボル期間だけ遅延する遅延手段と、前記遅延手段により遅延されたO F D M時間信号と、遅延されていないもとのO F D M時間信号との間の相関値を演算する演算手段と、

前記演算手段の出力の最大値を検知する検知手段と、

前記検知手段により検知されたある時点における最大値の位相を保持する保持手段と、

前記保持手段に保持されている位相と、前記検知手段により新たに検知された最大値の位相のずれを算定する算定手段とを更に備え。

10

前記制御手段は、前記算定手段により算定された位相のずれと、前記抽出手段により抽出された前記パイロット信号系列に対応する位相変動量とに応じて前記クロック信号の周波数を制御する

ことを特徴とする請求項1に記載の受信装置。

**【請求項4】**

振幅および位相が規定されたパイロット信号が各シンボル毎に含まれたO F D M信号を受信する受信装置における受信方法であって、

前記受信装置は、前記受信装置において使用されるクロック信号を発生するクロック信号発生手段であって、クロック信号の周波数が制御可能なクロック信号発生手段を備えており、

20

前記O F D M信号を離散的フーリエ変換する変換ステップと、

前記変換ステップにより得られた副搬送波の周波数成分を記憶する記憶ステップと、

前記記憶ステップに記憶されている少なくとも1シンボル前の前記周波数成分と、前記変換ステップにより新たに得られた周波数成分との間の位相変動量を算出する算出ステップと、

前記算出ステップにより算出された位相変動量より、前記パイロット信号に対応する成分を抽出する抽出ステップと、

前記抽出ステップにより抽出された前記パイロット信号に対応する位相変動量を複数のパイロット信号にわたって累積加算し、この累積加算された信号に応じて前記クロック信号発生手段を制御して前記クロック信号の周波数を制御する制御ステップと

30

を備えることを特徴とする受信方法。

**【発明の詳細な説明】**

**【0001】**

**【発明の属する技術分野】**

本発明は、受信装置および受信方法に関し、特に、O F D M方式に基づく受信装置および受信方法に関する。

**【0002】**

**【従来の技術】**

近年デジタル信号を伝送する方法として、直交周波数分割多重方式(O F D M: Orthogonal Frequency Division Multiplexing)と呼ばれる変調方式が提案されている。このO F D M方式は伝送帯域内に多数の直交する副搬送波を設け、それぞれの副搬送波の振幅及び位相にデータを割り当て、P S K(Phase Shift Keying)やQ A M(Quadrature Amplitude Modulation)によりデジタル変調する方式である。この方法では、多数の副搬送波で伝送帯域を分割するため、副搬送波1波あたりの帯域は狭くなり、変調速度は遅くなるが、搬送波の数が多数あるので総合の伝送速度は従来の変調方式と変わらない。

40

**【0003】**

このO F D M方式では多数の副搬送波が並列に伝送されるためにシンボル速度が遅くなるので、いわゆるマルチパス妨害の存在する伝送路ではシンボルの時間長に対する相対的なマルチパスの時間長を短くすることができ、マルチパス妨害に対して強い方式であること

50

が期待できる。

#### 【0004】

以上の様な特徴からO F D M方式は、マルチパス妨害の影響を強く受ける地上波によるデイジタル信号の伝送に対して特に注目されている。このような地上波によるデイジタル信号の伝送としては、例えば、D V B - T (Digital Video Broadcasting-Terrestrial)などがある。

#### 【0005】

また最近の半導体技術の進歩により離散的フ - リエ変換（以下F F T (Fast Fourier Transform)と記述する）や離散的フ - リエ逆変換（以下I F F T (Invert Fast Fourier Transform)と記述する）をハ - ドウェアで実現することが可能となり、これらを用いて簡単にO F D M方式に基づく変調を行ったり、また逆に復調する事ができる様になった事もO F D M方式が注目されてきた理由の一つである。

10

#### 【0006】

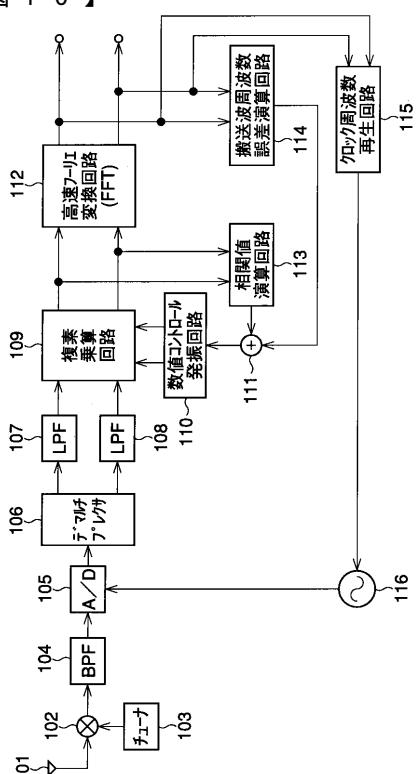

図10はO F D M受信機の構成例を示すブロック図である。受信アンテナ101は、R F信号を捕捉する。乗算回路102は、チューナ103から出力される所定の周波数を有する信号とR F信号とを乗算する。バンドパスフィルタ104は、乗算回路102の出力から所望のI F信号を抽出する。A / D (Analog to Digital)変換回路105は、バンドパスフィルタ104により抽出されたI F信号をデジタル信号に変換する。

#### 【0007】

デマルチプレクサ106は、デジタル化されたI F信号からIチャンネル信号とQチャンネル信号とを分離抽出する。ローパスフィルタ107, 108は、それぞれ、Iチャンネル信号とQチャンネル信号に含まれている不要な高域成分を除去して基底帯域（ベースバンド）の信号に変換する。

20

#### 【0008】

複素乗算回路109は、数値コントロール発振回路110より供給される所定の周波数の信号により、基底帯域信号の持つ搬送波周波数誤差を除外した後、高速フーリエ変換回路112に供給する。高速フーリエ変換回路112はO F D M時間信号を周波数分解し、IおよびQチャンネル受信データを生成する。

#### 【0009】

相関値演算回路113は、基底帯域に変換されたO F D M時間信号と有効シンボル時間だけ遅延させたO F D M信号とを乗算してガード期間幅の移動平均を計算することにより、2つの信号の相関値を求め、相関値が最大になるタイミングにおいて高速フーリエ変換回路112に演算を開始させる。

30

#### 【0010】

搬送波周波数誤差演算回路114は、周波数パワーの偏りを検出することにより搬送波周波数の誤差を算出し、加算回路111に出力する。加算回路111は、搬送波周波数誤差演算回路114と相関値演算回路113の出力を加算して数値コントロール発振回路110に供給する。

#### 【0011】

クロック周波数再生回路115は、IチャンネルデータとQチャンネルデータを参照して制御信号を生成し、クロック発振回路116の発振周波数を制御する。クロック発振回路116は、クロック周波数再生回路115から供給される制御信号に応じてクロック信号を生成し、出力する。

40

#### 【0012】

次に、以上の従来例の動作について説明する。

#### 【0013】

受信アンテナ101により捕捉されたR F信号は、チューナ103より供給された所定の周波数の信号と乗算回路102により乗算される。乗算回路102より出力された信号は、バンドパスフィルタ104により、I F信号が抽出されることになる。

#### 【0014】

50

A / D 変換回路 105 は、クロック発振回路 116 が出力するクロック信号に同期して、バンドパスフィルタ 104 から出力される I F 信号をデジタル信号に変換し、デマルチプレクサ 106 に供給する。デマルチプレクサ 106 は、デジタル化された信号から I チャンネル信号と Q チャンネル信号とを分離抽出してローパスフィルタ 107, 108 にそれぞれ供給する。ローパスフィルタ 107, 108 は、それぞれ、I チャンネル信号と Q チャンネル信号に含まれている不要な高域成分である折り返し成分を除去して基底帯域の信号に変換する。

#### 【 0015 】

複素乗算回路 109 は、数値コントロール発振回路 110 より供給される所定の周波数の信号により、基底帯域信号の持つ搬送波の周波数誤差を除去して高速フーリエ変換回路 112 に供給する。高速フーリエ変換回路 112 は O F D M 時間信号を周波数分解し、I および Q チャンネル受信データを生成する。

#### 【 0016 】

相関演算回路 113 は、基底帯域に変換された O F D M 時間信号と有効シンボル時間だけ遅延させた O F D M 信号との間の相関値を計算し、相関値が最大になるタイミングにおいて高速フーリエ変換回路 112 に演算を開始させる。その結果、高速フーリエ変換回路 112 は、送信側から送られてきた I チャンネル信号と Q チャンネル信号に含まれているデータを正確に抽出することができる。

#### 【 0017 】

ところで受信側において、O F D M 信号を正しく復調する為には、各種の同期を取ることが必要となる。例えば、先ず、I F 帯の O F D M 信号を基底帯域の O F D M 信号に変換するためには、数値コントロール発振回路 110 が発振する周波数を送信側のそれと同期させなければならない。また、全ての処理の基準となるクロック信号も送信側のそれと同期させなければならない。

#### 【 0018 】

ここで、後者のクロック信号を送信側と同期させるための方法として、従来から提案されているクロックの再生方法について説明する。

#### 【 0019 】

以下に述べる方法では、送信側においては伝送しようとする情報以外に、振幅および位相が規定された特定の信号（以下、パイロット信号という）が各シンボル毎に所定の数だけ内挿されて送信されており。また、受信側においては、F F T 演算が施された O F D M 信号から送信側で内挿されたパイロット信号が抽出され、このパイロット信号に以下に述べるコスタス演算等を施すことによりクロック信号を再生する。

#### 【 0020 】

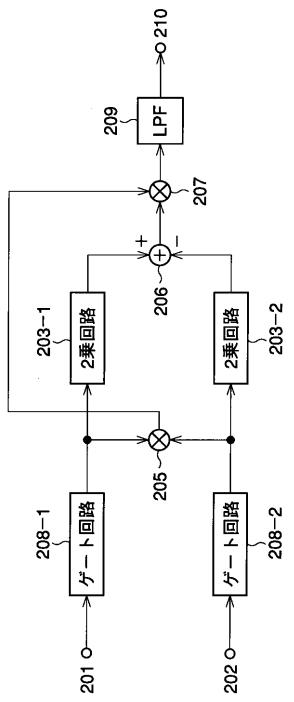

図 11 は、パイロット信号が Q P S K ( Quadrature Phase Shift Keying ) で変調されている場合に、コスタス演算を用いてクロック信号を再生する従来のクロック再生回路の構成例である。この図において、ゲート回路 208 - 1, 208 - 2 は、F F T 演算が施された I チャンネルデータと、Q チャンネルデータをそれぞれ入力し、パイロット信号だけを抽出して出力する。2 乗回路 203 - 1, 203 - 2 は、ゲート回路 208 - 1, 208 - 2 により抽出されたパイロット信号をそれぞれ 2 乗して出力する。乗算回路 205 は、ゲート回路 208 - 1, 208 - 2 により抽出されたパイロット信号を乗算して出力する。

#### 【 0021 】

減算回路 206 は、2 乗回路 203 - 1 の出力から 2 乗回路 203 - 2 の出力を減算して出力する。乗算回路 207 は、乗算回路 205 の出力と減算回路 206 の出力を乗算して出力する。L P F 209 は、乗算回路 207 の出力から不要な高周波成分を除去して出力する。

#### 【 0022 】

次に、以上の従来例の動作について説明する。

#### 【 0023 】

10

20

30

40

50

図10に示す高速フーリエ変換回路112により周波数分解されて復調されたIチャンネルデータおよびQチャンネルデータは、その周波数が小さい順にゲート回路208-1, 208-2にそれぞれ入力される。ゲート回路208-1, 208-2は、IチャンネルデータおよびQチャンネルデータよりパイロット信号のみをそれぞれ抽出し、2乗回路203-1, 203-2、および、乗算回路205に供給する。

#### 【0024】

乗算回路205は、ゲート回路208-1, 208-2により抽出されたパイロット信号を乗算して、乗算回路207に出力する。また、2乗回路203-1, 203-2は、それぞれ、ゲート回路208-1, 208-2により抽出されたパイロット信号を2乗して減算回路206に出力する。

10

#### 【0025】

減算回路206は、2乗回路203-1の出力から2乗回路203-2の出力を減算して乗算回路207に出力する。乗算回路207は、乗算回路205の出力と減算回路207の出力を乗算してLPF209に出力する。LPF209は、乗算回路207の出力に含まれている高周波成分を除去して出力する。

20

#### 【0026】

以上のような一連の操作がいわゆるコスタス演算であり、このようなコスタス演算により、クロック信号の位相誤差を検出することができる。このようにして検出されたクロック信号の位相誤差に基づいてクロック発振回路116を制御して正確なクロック信号を生成する。

#### 【0027】

##### 【発明が解決しようとする課題】

ところで、以上のようなコスタス演算等を用いて位相誤差を検出し、その結果に応じてクロック信号を再生する場合、検出された位相誤差には、クロック周波数誤差に伴う位相誤差だけではなく、再生搬送波位相誤差、FFT窓位相誤差、ガウス雑音による位相誤差、および、地上波を伝送する場合には避けて通れないマルチパスによる伝送路ひずみに起因する位相誤差が含まれているため、再生クロック誤差のみに伴う位相誤差だけを抽出してクロック発信回路を制御することが困難であるという課題があった。

#### 【0028】

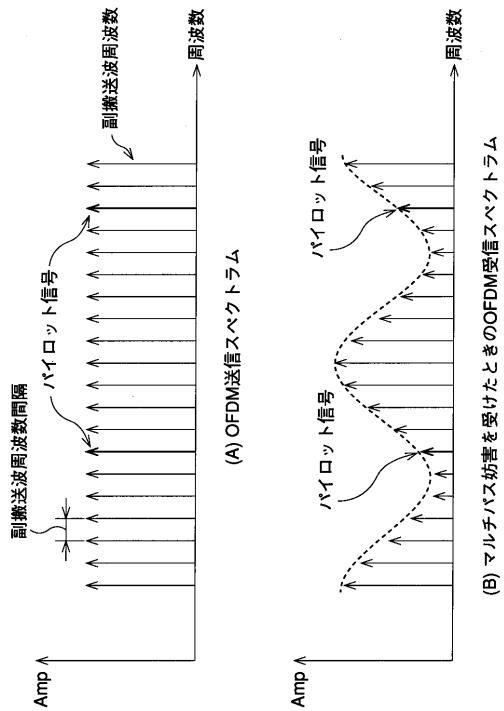

また、図12(A)にOFDM信号のスペクトラムの一例を、図12(B)にはマルチパス妨害を受けたときのOFDM信号のスペクトラムを示す。ここで太線は送信側で内挿されたパイロット信号を表している。図12(B)に示すように、マルチパスにより送信信号が周波数選択的な妨害を受けた場合、他の副搬送波に対するパイロット信号の信号対雑音比が低下する。そのような場合、前述のような方法によりパイロット信号から生成されたクロック信号の位相誤差信号も信号対雑音比が低下することになる。その結果、送信信号がマルチパス妨害を受けた場合には、正確にクロック信号を再生することが困難となるという問題があった。

30

#### 【0029】

本発明は以上のような状況に鑑みてなされたものであり、受信したOFDM信号がクロック周波数誤差に伴う位相誤差のみならず、再生搬送波位相誤差、FFT窓位相誤差、ガウス雑音による位相誤差、および、マルチパスによる伝送路ひずみに起因する位相誤差を含む場合においても、クロック信号を正確に生成することができるOFDM受信装置のクロック再生回路を提供することを目的としている。

40

#### 【0030】

##### 【課題を解決するための手段】

請求項1に記載の受信装置は、OFDM信号を離散的フーリエ変換する変換手段と、変換手段により得られた副搬送波の周波数成分を記憶する記憶手段と、記憶手段に記憶されている少なくとも1シンボル前の周波数成分と、変換手段により新たに得られた周波数成分との間の位相変動量を算出する算出手段と、算出手段により算出された位相変動量より、パイロット信号に対応する成分を抽出する抽出手段と、受信装置において使用されるク

50

クロック信号を発生するクロック信号発生手段であって、クロック信号の周波数が制御可能なクロック信号発生手段と、抽出手段により抽出されたパイロット信号に対応する位相変動量を複数のパイロット信号にわたって累積加算し、この累積加算された信号に応じてクロック信号発生手段を制御してクロック信号の周波数を制御する制御手段とを備えることを特徴とする。

【 0 0 3 1 】

請求項4に記載の受信方法は、受信装置が、受信装置において使用されるクロック信号を発生するクロック信号発生手段であって、クロック信号の周波数が制御可能なクロック信号発生手段を備えており、OFDM信号を離散的フーリエ変換する変換ステップと、変換ステップにより得られた副搬送波の周波数成分を記憶する記憶ステップと、記憶ステップに記憶されている少なくとも1シンボル前の周波数成分と、変換ステップにより新たに得られた周波数成分との間の位相変動量を算出する算出ステップと、算出ステップにより算出された位相変動量より、パイロット信号に対応する成分を抽出する抽出ステップと、抽出ステップにより抽出されたパイロット信号に対応する位相変動量を複数のパイロット信号にわたって累積加算し、この累積加算された信号に応じてクロック信号発生手段を制御してクロック信号の周波数を制御する制御ステップとを備えることを特徴とする。

10

【 0 0 3 4 】

請求項 1 に記載の受信装置においては、O F D M 信号を変換手段が離散的フーリエ変換し、変換手段により得られた副搬送波の周波数成分を記憶手段が記憶し、記憶手段に記憶されている少なくとも 1 シンボル前の周波数成分と、変換手段により新たに得られた周波数成分との間の位相変動量を算出手段が算出し、算出手段により算出された位相変動量より、パイロット信号に対応する成分を抽出手段が抽出し、クロック信号の周波数が制御可能なクロック信号発生手段が受信装置において使用されるクロック信号を発生し、抽出手段により抽出されたパイロット信号に対応する位相変動量を複数のパイロット信号にわたくて累積加算し、この累積加算された信号に応じてクロック信号発生手段を制御してクロック信号の周波数を制御手段が制御する。例えば、変換手段である F F T 変換回路が O F D M 信号を離散的フーリエ変換し、得られた副搬送波の周波数成分を記憶手段であるメモリが記憶し、メモリに記憶されている 1 シンボル前の周波数成分と、F F T 変換回路より新たに出力された周波数成分とを算出手段が差動復調することにより位相変動量を算出し、算出手段により算出された位相変動量からパイロット信号に対応する成分を抽出手段が抽出し、クロック信号の周波数が制御可能なクロック信号発生手段が受信装置において使用されるクロック信号を発生し、抽出手段により抽出されたパイロット信号の位相変動量を複数のパイロット信号にわたくて累積加算し、この累積加算された信号に応じてクロック信号発生手段を制御してクロック信号の周波数を制御手段が制御する。

20

【 0 0 3 5 】

請求項4に記載の受信方法においては、受信装置が、受信装置において使用されるクロック信号を発生するクロック信号発生手段であって、クロック信号の周波数が制御可能なクロック信号発生手段を備えており、O F D M信号を変換ステップが離散的フーリエ変換し、変換ステップにより得られた副搬送波の周波数成分を記憶ステップが記憶し、記憶ステップに記憶されている少なくとも1シンボル前の周波数成分と、変換ステップにより新たに得られた周波数成分との間の位相変動量を算出ステップが算出し、算出ステップにより算出された位相変動量より、パイラット信号に対応する成分を抽出ステップが抽出し、抽出ステップにより抽出されたパイラット信号に対応する位相変動量を複数のパイラット信号にわたって累積加算し、この累積加算された信号に応じてクロック信号発生手段を制御してクロック信号の周波数を制御ステップが制御する。例えば、変換ステップであるF F T変換回路がO F D M信号を離散的フーリエ変換し、得られた副搬送波の周波数成分を記憶ステップであるメモリが記憶し、メモリに記憶されている1シンボル前の周波数成分と、F F T変換回路より新たに出力された周波数成分とを算出ステップが差動復調することにより位相変動量を算出し、算出ステップにより算出された位相変動量からパイラット信号に対応する成分を抽出ステップが抽出し、抽出ステップにより抽出されたパイラット

30

40

信号の位相変動量を複数のパイロット信号にわたって累積加算し、この累積加算された信号に応じてクロック信号発生手段を制御してクロック信号の周波数を制御ステップが制御する。

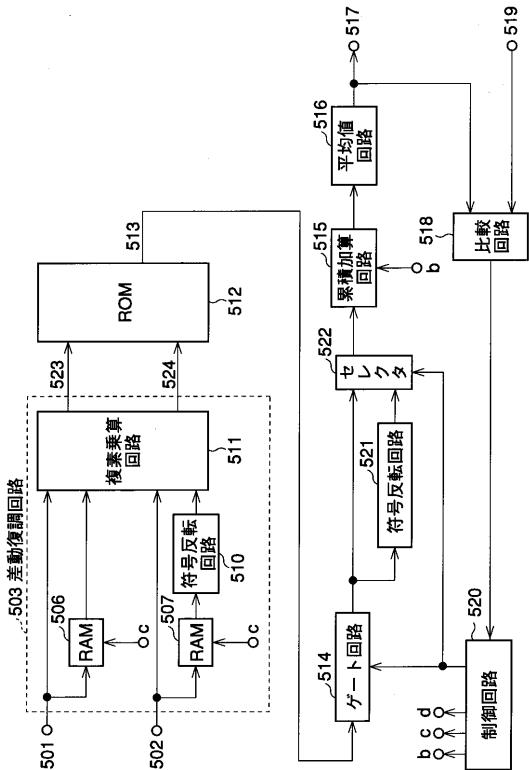

【0038】

図1に本発明の実施の形態の一例を示す。なお、本実施の形態は図10に示すクロック周波数再生回路115に関するものである。

【0039】

この図において、差動復調回路503は、RAM(Random Access Memory)506, 507、符号反転回路510、および、複素乗算回路511により構成されており、入力されたIチャンネルデータおよびQチャンネルデータを差動復調するようになされている。

RAM506, 507は、入力されたIチャンネルデータまたはQチャンネルデータを、制御回路520からの制御信号cに応じて、シンボル単位で記憶し、1シンボル時間だけ遅らせて出力するようになされている。符号反転回路510は、RAM507の出力データの符号を反転して出力するようになされている。

【0040】

複素乗算回路511は、遅延されていないIチャンネルデータとQチャンネルデータをI, Qと表し、遅延されたIチャンネルデータとQチャンネルデータをそれぞれ $I^{-1}$ ,  $Q^{-1}$ と表すと、以下に示す複素演算を行い、演算結果を実数成分523と虚数成分524とに分けて出力するようになされている。なお、ここで、jは虚数を表す。

【0041】

$$(I + j Q) (I^{-1} - j Q^{-1}) \dots \quad (1)$$

【0042】

ROM(Read Only Memory)512は、アークタンジェント(逆正接関数)データを格納しており、入力されたIチャンネルデータおよびQチャンネルデータに対応する位相変動量データ513を出力するようになされている。

【0043】

ゲート回路514は、制御回路520の制御信号に従ってROM512から出力される位相変動量データ513から、送信側で規定されたパイロット信号に対応する成分だけを選択し、符号反転回路521およびセレクタ522に供給するようになされている。符号反転回路521は入力された位相変動量データの符号を反転し、セレクタ522に供給するようになされている。

【0044】

セレクタ522は制御回路520によって制御され、入力されたパイロット信号が正の周波数であればゲート回路514から直接入力された位相変動量を選択し、また、負の周波数であれば、符号反転回路521から入力された位相変動量を選択して累積加算回路515に供給するようになされている。

【0045】

累積加算回路515は、各シンボルが入力される直前に制御回路520から供給される制御信号bにより初期化された後、セレクタ522から出力されるパイロット信号の位相誤差量を累積加算するようになされている。

【0046】

平均値回路516は、累積加算回路515からシンボル毎に出力される、累積された位相誤差量を数シンボルに渡って平均化し、位相誤差量に含まれるガウス雑音を取り除いた後、クロック発振回路116を制御するための位相誤差量517を算出するようになされている。

【0047】

比較回路518は、クロック信号の周波数が確定(ロックイン)されたことを検出して制御回路520に伝達するようになされている。即ち、比較回路518は、シンボル間差動復調データが0である場合に対応する値519と、位相誤差量517の現在値とを比較し、その結果、これらが等しいと判定した場合には、制御回路520に所定の制御信号を

10

20

30

40

50

送る。

#### 【0048】

次に、以上の実施の形態の動作について説明するが、その前に、本実施の形態の動作原理について簡単に説明しておく。

#### 【0049】

例えば、受信機側において、送信側と同期していないクロック信号によりO F D M信号を再生処理した場合、F F T処理により復調されたパイロット信号には、通常含まれているF F T窓位相誤差、再生搬送波位相誤差、ガウス雑音による位相誤差およびマルチパス妨害等の伝送路歪みによる位相誤差に加えて、クロック信号の不同期に起因する位相誤差が含まれることになる。

10

#### 【0050】

ところで、ガウス雑音による位相誤差およびクロック信号の不同期による位相誤差以外はシンボルによらず一定の位相誤差になる。従って、ある基準時間における信号と現在観測された信号のシンボル間で差動復調すれば、これらの位相誤差（シンボルによらず一定の位相誤差）は取り除くことが出来る。これを式で表すと以下のようになる。

#### 【0051】

$$n_k = k + + n_k + k (1 + ) + k + n \dots \quad (2)$$

$$(n+1)k = k + + (n+1)k + k (1 + ) + k + n+1 \dots \quad (3)$$

$$(n+1)k - n_k = k + n+1 - n \dots \quad (4)$$

#### 【0052】

20

ここで、式(2)は第n番目のシンボルの第k番目の副搬送波周波数の持つ位相データを示している。また、 $k$ は送信側で規定された位相、 $$ はクロック誤差、 $n$ は再生搬送波の位相誤差、 $$ はF F T窓位相誤差、 $k$ は第k番目の副搬送波周波数に対するマルチパス妨害等の伝送路歪みによる位相誤差、 $n$ は第n番目シンボルのガウス雑音による位相誤差をそれぞれ示している。更に、式(3)は第(n+1)番目のシンボルの第k番目の副搬送波周波数の持つ位相データであり、式(4)は式(3)から式(2)を減算した結果であり、差動復調後の第k番目の副搬送波周波数の持つ第(n+1)番目のシンボルと第n番目のシンボルの間の位相変動量を表している。

#### 【0053】

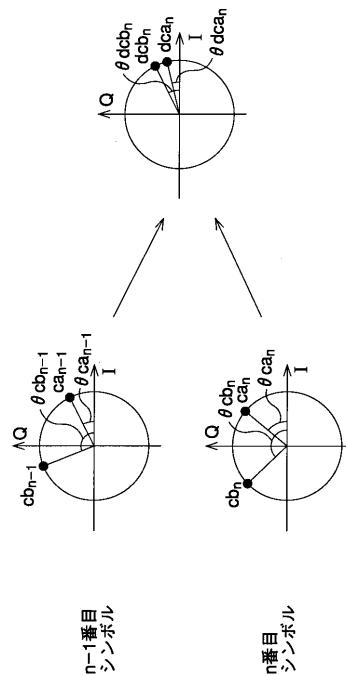

以上の関係を図2に示す。図2(A)において、 $c a_{n-1}$ ,  $c b_{n-1}$ ,  $c a_n$ ,  $c b_n$ は、それぞれ周波数a, bのパイロット信号の第(n-1)番目または第n番目のシンボルを位相平面上に示したものであり、 $c a_{n-1}$ ,  $c b_{n-1}$ ,  $c a_n$ ,  $c b_n$ はそれぞれの位相量である。ところで、これら第(n-1)番目と第n番目のシンボルに含まれているパイロット信号の周波数は元々等しいはずであるが、前述のような種々の誤差により、図2(A)に示すように位相平面上における位置にずれを生じてくる。そこで、これら第(n-1)番目と第n番目のシンボルの間で差動復調を行うことにより、シンボルによらず一定である誤差(F F T窓位相誤差、再生搬送波位相誤差、および、マルチパス妨害等の伝送路歪みによる位相誤差など)を除去することができる。

30

#### 【0054】

即ち、図2(B)に示すように、第(n-1)番目と第n番目のシンボルの差動復調を求めるに、2つのパイロット信号はI軸の近傍に移動されることになる。なお、この図において、 $d c a_n$ ,  $d c b_n$ は、それぞれ周波数a, bのパイロット信号のシンボル間差動復調後の位相平面上のデータであり、 $d c a_n$ ,  $d c b_n$ はそれぞれの位相量であり、クロック周波数誤差およびガウス雑音による位相量に対応している。

40

#### 【0055】

このようにしてシンボル間で差動復調を行うことにより、クロック周波数誤差およびガウス雑音以外の要素に起因する誤差を除去することができる。次に、ガウス雑音に起因する誤差を除去することを考える。

#### 【0056】

ところで、ガウス雑音による誤差はアトランダムに生じるので、複数のパイロット信号か

50

ら得られる位相誤差を累積加算することにより、フィルタ（平滑化）効果を用いてこれを除去することができる。その結果、クロック周波数誤差に比例した位相誤差量を得ることが出来るので、これを用いることによりクロック発振回路 116 を正確に制御してクロック信号を生成することができる。

#### 【0057】

ところで、以上のような制御はディジタル的に行われる（離散的な数値を用いて行われる）ので、隣接する 2 つのシンボル間の位相変動量が分解能以下になった場合には、それ以上の制御は不可能になる。そこで、本実施の形態においては、位相変動量が隣接する 2 つのシンボルにより検出される誤差が分解能以下になった場合には、その時点における FFT 处理後の信号をメモリに記憶させておき、記憶されたデータと新たなデータとの間で差動復調を行うことにより、シンボル間隔以上の時間間隔でクロック位相誤差を検出するようしている。即ち、このような誤差（量子化誤差）は、時間の経過に応じて累積されるので、比較の対象とする時間を長くすることにより検出可能となる。

#### 【0058】

続いて、図 1 の実施の形態の動作について説明する。

#### 【0059】

高速フーリエ変換回路 112（変換手段）により副搬送波周波数に応じて分解された I チャンネルデータ 501 と Q チャンネルデータ 502 は、差動復調回路 503 に入力される。

#### 【0060】

クロック再生動作の初期においては、差動復調回路 503 では、I チャンネルデータと Q チャンネルデータがその周波数が小さい順に RAM506, 507 および複素演算回路 511 にそれぞれ供給される。

#### 【0061】

RAM506, 507 は制御回路 520 からの制御信号 c により、各シンボル毎に I チャンネルデータと Q チャンネルデータをそれぞれ記憶し、1 シンボル時間だけ遅延して出力する。RAM507 から出力された Q チャンネルデータは、符号反転回路 510 により符号が反転されて出力される。I チャンネルデータ、1 シンボル遅延された I チャンネルデータ、Q チャンネルデータ、および、符号反転されて 1 シンボル遅延された Q チャンネルデータは、その周波数が小さい順に複素演算回路 511 により式（1）に示すような複素乗算が施され、I チャンネルデータ 523 および Q チャンネルデータ 524 として出力される。このような一連の操作がシンボル間の差動復調処理となる。

#### 【0062】

前述のように、以上の操作（差動復調）により、信号に含まれている FFT 窓位相誤差、再生搬送波位相誤差等が除去されることになる。

#### 【0063】

差動復調データ 523, 524 は ROM512 に順次供給され、それらの値に対応するシンボル間位相変動量 513 が読み出されて、ゲート回路 514 に供給される。

#### 【0064】

ゲート回路 514 は、制御回路 520 の制御に応じて、ROM512 から出力されるシンボル間位相変動量 513 のうち、パイロット信号に対応する成分だけを抽出して出力する。

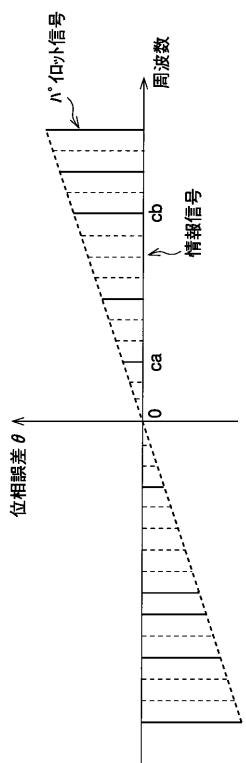

#### 【0065】

符号反転回路 521 は、ゲート回路 514 により抽出されたパイロット信号の符号を反転してセレクタ 522 に供給する。セレクタ 522 は、制御回路 520 によって制御され、入力されたパイロット信号が正の周波数であればゲート回路 514 から直接入力された位相変動量を選択し、負の周波数であれば符号反転回路 521 から入力された位相変動量を選択して累積加算回路 515 に供給する。なお、このような操作によって、図 3 に示すような、周波数の正負に依存するクロック周波数誤差の位相変動の回転方向を一元化することができる。

10

20

30

40

50

**【0066】**

累積加算回路 515 は新たなシンボルが入力される直前に制御回路 520 から供給される制御信号 b により初期化された後、セレクタ 522 から出力されるパイロット信号の位相誤差量を累積加算する。平均値回路 516 はシンボル毎に入力される累積された位相誤差量を数シンボルに亘って平均化することにより、前述のように位相誤差量に含まれるガウス雑音成分を除去し、クロック発振回路 116 を制御する位相誤差量 517 を生成する。平均値回路 516 から出力された位相誤差量 517 は、クロック発振回路 116 に供給され、その発振周波数を制御する。このような一連の処理により正確なクロック周波数が再生されることになる。

**【0067】**

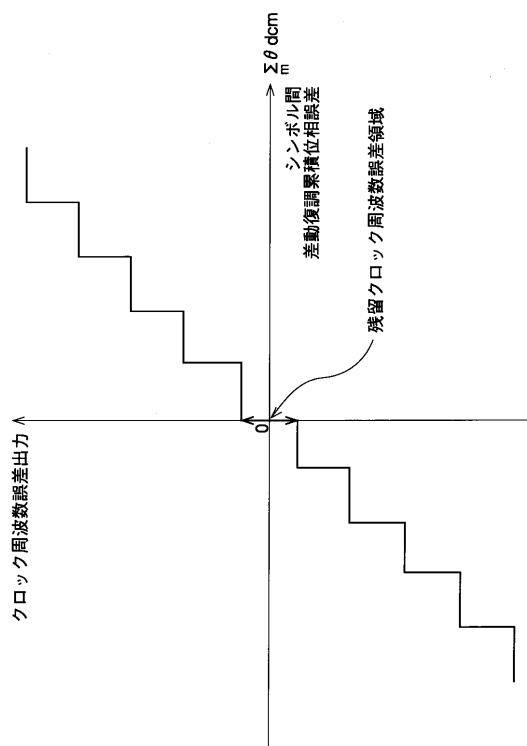

10

ところで、前述のような処理により、クロック周波数の確定処理が完了すると、シンボル間差動復調によって得られる位相誤差量 517 が分解能以下になり、図 4 に示す残留クロック周波数誤差領域に入る。即ち、クロック周波数の誤差は、離散的な値として出力されるため、シンボル間差動復調累積位相誤差が 0 の場合においても、クロック周波数誤差出力は 0 とはならない場合がある。その場合には、クロック信号をそれ以上精密に制御することはできなくなる。

**【0068】**

20

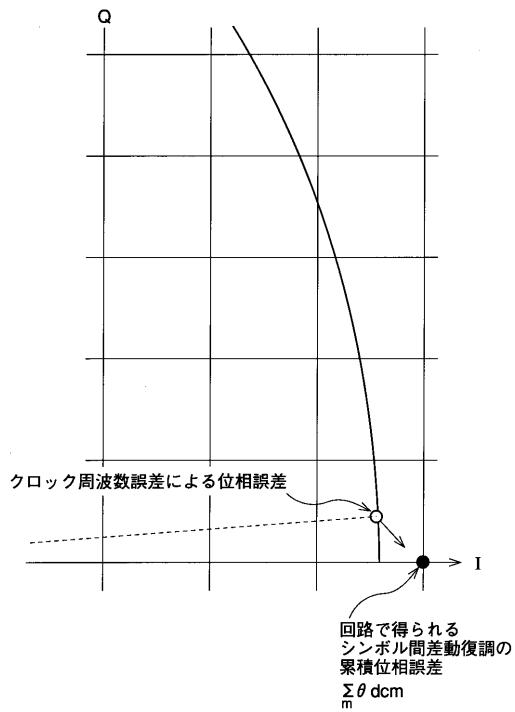

図 5 は、図 4 に示す残留クロック周波数誤差領域を位相平面上に表したものである。図の縦軸は Q 信号、横軸は I 信号をそれぞれ示しており、また、格子は量子化ステップに対応している。いま、図に白丸で示すようなパイロット信号が入力された場合、この信号は、図に示す格子を基準として判定すると、図の黒丸で示す位置のデータと同等に判定される。従って、その場合には、クロック周波数誤差による位相誤差が無視されることになるので、その誤差に対する制御は実行できないことになる。

**【0069】**

しかしながら、本実施の形態においては、比較回路 518 が平均値回路 516 の出力が収束したことを検出した場合は、制御回路 520 に制御信号を供給することにより、RAM 506, 507 の値を固定化するようになされている。

**【0070】**

30

即ち、比較回路 518 はシンボル間差動復調データが 0 である場合に対応するデータ 519 と位相誤差量 517 とを比較し、これらが等しい場合は制御回路 520 に制御信号を送る。制御回路 520 はこの制御信号を受けて、RAM 506, 507 に制御信号 c を供給し、その時点において高速フーリエ変換回路 112 から出力されている復調信号を RAM 506, 507 にそれぞれ記憶させる。以降、差動復調回路 503 は、RAM 506, 507 に記憶された信号を基準にして差動復調を行うので、位相誤差信号の検出時間がシンボル間時間に比べて長くなり、その結果、シンボル間差動復調で得られる残留クロック周波数誤差以下のクロック周波数誤差を検出して制御することが可能となる。

**【0071】**

40

以上の実施の形態によれば、OFDM 信号がクロック周波数誤差に伴う位相誤差のみならず、再生搬送波位相誤差、FFT 窓位相誤差、ガウス雑音による位相誤差、および、マルチパスによる伝送路ひずみに起因する位相誤差を含む場合においても、クロック信号を正確に再生することが可能となる。

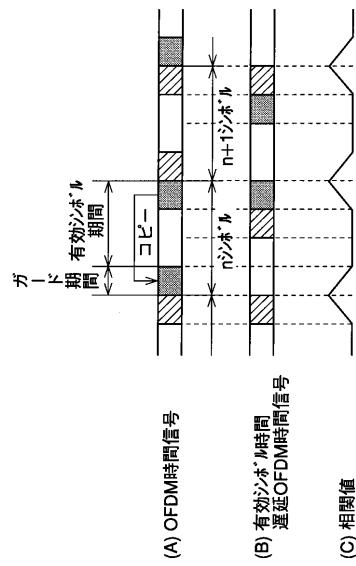

**【0072】**

ところで、一般的に、OFDM 時間信号の各シンボルは、図 6 (A) に示すように、有効シンボル期間と有効シンボル期間の一部をコピーしたガード期間とにより構成されている。従って、有効シンボル期間だけ遅延させた OFDM 時間信号 (図 6 (B) 参照) と元の OFDM 時間信号との相関値を、ガード期間幅に亘って算出すると、その値はシンボルの境界で最大値を取る (図 6 (C) 参照) ことになる。

**【0073】**

50

なお、受信側のクロック信号が送信側のクロック信号と同期していない場合には、図 7 に示すように相関値が最大となる位相が時間とともに変化することとなる。即ち、図 7 (A)

)に示すように、送信側の送信クロック信号と受信側の再生クロック信号とが正確に同期している場合には、相関値が最大となるタイミングは、常に一定であるが、例えば、送信クロック信号よりも再生クロック信号の周波数の方が高い場合には、相関値が最大となるタイミングは、次第に遅れていくことになる。また、送信クロック信号よりも再生クロック信号の周波数の方が低い場合には、相関値が最大となるタイミングは、次第に進んでいくことになる。従って、このような位相変化量を観測してクロック発振回路 116 を制御すれば、クロック位相の同期再生を行うことができる。

#### 【0074】

以上のような原理に基づく、本発明の第2の実施の形態を図8に示す。

#### 【0075】

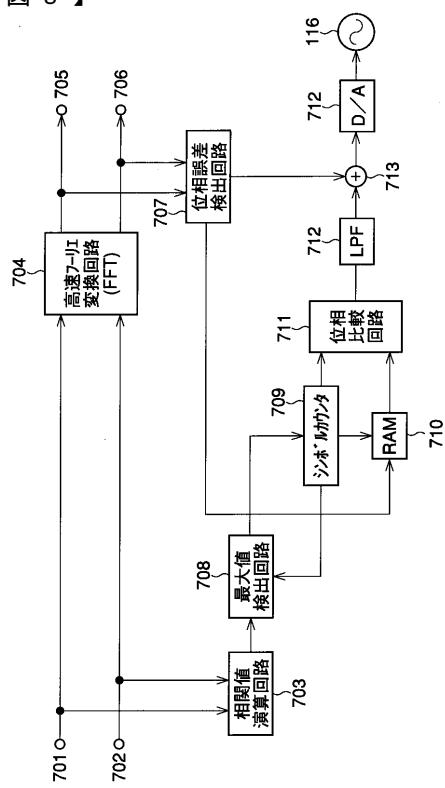

図8にO F D M時間信号の相関値を用いたクロック再生方法の実施の形態の構成例を示すブロック図である。なお、この図においては、説明を簡略化するために、クロック再生部のみに注目し、図10に示す搬送波を再生する部分は省略してある。

#### 【0076】

基底帯域に変換されたO F D M時間信号のIチャンネル成分およびQチャンネル成分は、高速フーリエ変換回路704と相関値演算回路703(遅延手段、演算手段)にそれぞれ入力される。相関値演算回路703はO F D M時間信号の周期性を利用して相関値を算出するようになされている。高速フーリエ変換回路704は、入力されたIチャンネル成分とQチャンネル成分に対してフーリエ変換を施し、Iチャンネルデータ705およびQチャンネルデータ706として出力するとともに、位相誤差検出回路707に供給するようになされている。位相誤差検出回路707は、パイロット信号を用いて位相誤差を検出するようになされており、その詳細については後述する。

#### 【0077】

最大値検出回路708(検知手段)は相関値演算回路703から出力される相関値の最大値をシンボルカウンタ709に同期して検出するようになされている。シンボルカウンタ709はシンボル時間をカウントし、そのカウント値を最大値検出回路708に供給するようになされている。R A M 710(保持手段)は、位相誤差検出回路707から制御信号が出力された場合、即ち、位相変動量が分解能以下になった場合に、最大値検出回路708が最大値を検出したシンボルのカウント値を基準位相として記憶するようになされている。

#### 【0078】

位相比較回路711(算定手段)は、R A M 710に記憶された基準位相と、シンボル毎にシンボルカウンタ709から供給される最大値が検出された場合のカウント値とを比較し、位相誤差量を検出するようになされている。L P F 712は、位相比較回路711から出力される位相誤差量から、雑音成分を取り除いて加算回路713に供給する。加算回路713は、L P F 712から出力された位相誤差量と位相誤差検出回路707から出力された位相誤差量とを加算して、D / A変換回路714に出力する。D / A変換回路714は、加算回路713から出力された位相誤差量を、対応するアナログ信号に変換してクロック発振回路116に供給するようになされている。クロック発振回路116は、D / A変換回路714から出力される信号に応じて、所定の周波数のクロック信号を発振するようになされている。

#### 【0079】

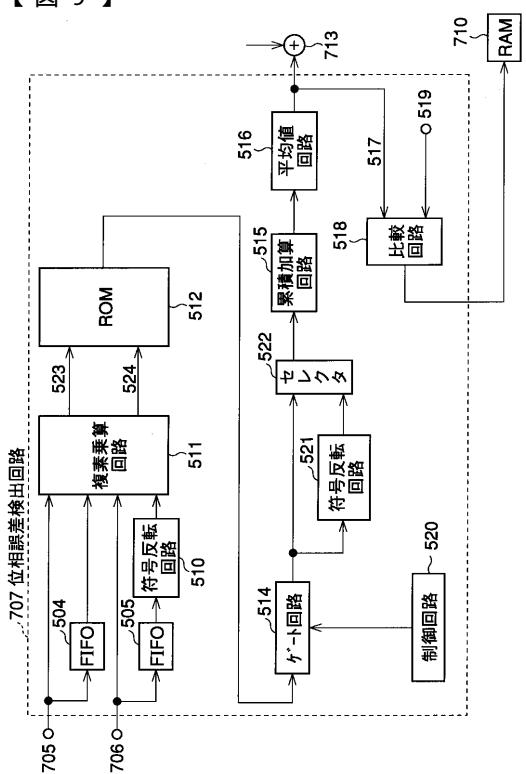

次に、図9を参照して、図8に示す位相誤差検出回路707の詳細な構成例について説明する。なお、位相誤差検出回路707は図1の実施の形態で示した構成から、位相記憶部分を除外したものであり、また、図9において、図1と対応する部分には対応する符号を付してあるのでその説明は省略する。

#### 【0080】

この実施の形態では、比較回路518の出力は、R A M 710に入力されるようになされている。その他の構成は、図1における場合と同様である。

#### 【0081】

10

20

30

40

50

次に、図8および図9を参照して、以上の実施の形態の動作について説明する。

**【0082】**

クロック再生動作の初期状態においては、第1の実施の形態において説明したように、FFT処理が施された信号に対してシンボル間の差動復調を行うことにより、各副搬送波の位相誤差を求め、更に、この位相誤差信号からパイロット信号を抜き出して累積加算する事により、クロック周波数誤差を検出し、検出された周波数誤差を基準としてクロック信号を再生する。

**【0083】**

位相誤差検出回路707によるクロック信号の再生が完了すると、誤差値が分解能以下になり、図4に示す残留クロック周波数誤差領域に陷入する。その場合、比較回路518はシンボル間差動復調データが0である場合に対応するデータ519と、位相誤差量517とを比較し、これらが等しい場合はRAM710に制御信号を送る。制御信号を受け取ったRAM710は、その時点で最大値検出回路708が検出した最大値に対応するシンボル位相をシンボルカウンタ709から受け取り、基準位相として記憶する。

**【0084】**

その後、位相比較回路711はRAM710に記憶された基準位相と、各シンボル毎にシンボルカウンタ709から供給される最大値検出位相とを比較し、位相誤差量を検出する。LPF712は、位相比較回路711から出力された位相誤差量から雑音成分を除去して加算回路713に出力する。加算回路713は、位相誤差検出回路707からの出力と、LPF712の出力を加算してD/A変換回路714に供給する。

**【0085】**

D/A変換回路714は、加算回路713の出力信号（デジタル信号）を対応するアナログ信号に変換してクロック発振回路116に出力する。クロック発振回路116は、D/A変換回路714の出力に応じた周波数で発振し、クロック信号を出力する。

**【0086】**

以上の実施の形態によれば、クロック再生動作の初期においては、位相誤差検出回路707の迅速な制御によりクロック信号の周波数が確定され、クロック信号の周波数誤差が位相誤差検出回路707の検出分解能以下になった場合には、OFDM時間信号の相関値を用いて正確な周波数制御を行うことが可能となる。

**【0087】**

**【発明の効果】**

請求項1に記載の受信装置および請求項5に記載の受信方法によれば、OFDM信号を離散的フーリエ変換し、得られた副搬送波の周波数成分を記憶し、記憶されている少なくとも1シンボル前の周波数成分と、新たに得られた周波数成分との間の位相変動量を算出し、算出された位相変動量より、パイロット信号に対応する成分を抽出し、抽出されたパイロット信号に対応する位相変動量を複数のパイロット信号にわたって累積加算し、この累積加算された信号に応じてクロック信号発生手段を制御してクロック信号の周波数を制御するようにしたので、受信したOFDM信号がクロック周波数誤差に伴う位相誤差のみならず、再生搬送波位相誤差、FFT窓位相誤差、ガウス雑音による位相誤差、および、マルチパスによる伝送路ひずみに起因する位相誤差を含む場合においても、正確にクロック信号を生成することが可能となる。

**【図面の簡単な説明】**

**【図1】**本発明の実施の形態の構成例を示すブロック図である。

**【図2】**差動復調前後のパイロット信号を位相平面上に示した図である。

**【図3】**クロック周波数誤差による位相誤差と副搬送波周波数の関係を示す図である。

**【図4】**残留クロック周波数誤差領域を示す図である。

**【図5】**残留クロック周波数誤差領域を位相平面上に示した図である。

**【図6】**OFDM時間信号と相関値の関係を示す図である。

**【図7】**相関値の最大値位相とクロック周波数誤差の関係を示す図である。

**【図8】**本発明の第2の実施の形態の構成例を示すブロック図である。

10

20

30

40

50

【図9】図8に示す位相誤差検出回路の構成例を示すブロック図である。

【図10】O F D M受信機の構成例を示すブロック図である。

【図11】従来のコスタス演算を用いたクロック再生装置の構成例を示すブロック図である。

【図12】マルチパス妨害を受けたときのO F D M受信スペクトラムを示す図である。

【符号の説明】

112 高速フーリエ変換回路(変換手段), 506, 507 RAM(記憶手段),

511 複素乗算回路(算出手段), 512 ROM(算出手段), 514 ゲート回路(抽出手段),

515 累積加算回路(累積加算手段), 516 制御回路(制御手段), 518 比較回路(検出手段),

520 制御回路(禁止手段), 703 相関値演算回路(遅延回路, 演算回路), 708 最大値検出回路(検知手段)

, 710 RAM(保持手段), 711 位相比較回路(算定手段)

【図1】

【図2】

(A) FFT後の位相平面上のデータ

(B) 差動復調後の位相平面上のデータ

【図3】

【図4】

【図5】

【図6】

【図 7】

【図 8】

【図 9】

【図 10】

【図 1 1】

【図 1 2】

---

フロントページの続き

審査官 高野 洋

- (56)参考文献 特開平08-265312(JP,A)

特開平07-143096(JP,A)

特開平06-252967(JP,A)

特開平07-273741(JP,A)

特開平07-099486(JP,A)

特開平08-274746(JP,A)

特開平08-274745(JP,A)

特開平08-265288(JP,A)

特開平07-143097(JP,A)

特開平08-139777(JP,A)

特開平08-265293(JP,A)

特開平07-321762(JP,A)

国際公開第96/019056(WO,A1)

特開平09-130362(JP,A)

特開平08-331191(JP,A)

(58)調査した分野(Int.Cl., DB名)

H04J 11/00