US 20120231623A1

### (19) United States

# (12) Patent Application Publication OSHIDA et al.

(10) Pub. No.: US 2012/0231623 A1

(43) **Pub. Date:** Sep. 13, 2012

#### (54) METHOD OF MANUFACTURING A HIGH-RELIABILITY SEMICONDUCTOR DEVICE

(75) Inventors: **Daisuke OSHIDA**, Kanagawa (JP); **Toshiyuki TAKEWAKI**, Kanagawa

(JP); Shinji YOKOGAWA,

Kanagawa (JP)

(73) Assignee: **RENESAS ELECTRONICS**

CORPORATION, Kanagawa (JP)

(21) Appl. No.: 13/479,651

(22) Filed: May 24, 2012

#### Related U.S. Application Data

(62) Division of application No. 12/350,448, filed on Jan. 8, 2009

#### (30) Foreign Application Priority Data

#### **Publication Classification**

(51) **Int. Cl.** *H01L 21/768* (2006.01)

(52) **U.S. Cl.** ....... 438/626; 257/E21.575

(57) ABSTRACT

A semiconductor device is provided, which includes a substrate, an insulator film formed over the substrate, and plural metal wirings with different widths containing copper as a main component and an impurity which is different from copper. The plural metal wirings includes a first metal wiring having a concentration profile where the concentration of the impurity metal increases from the center part of the stacking direction to the surface and the second metal wiring having a concentration profile where the concentration of the impurity metal decreases from the bottom surface of the stacking direction to the surface. Moreover, the width of the second metal wiring may be larger than the width of the first metal wiring.

FIG. 1

FIG. 2

FIG. 3A

FIG. 3B

FIG. 4A

FIG. 4B

FIG. 5A

FIG. 5B

FIG. 6A

FIG. 6B

FIG. 7A

FIG. 7B

FIG. 8

FIG. 9

FIG. 10

#### METHOD OF MANUFACTURING A HIGH-RELIABILITY SEMICONDUCTOR DEVICE

## CROSS REFERENCE TO RELATED APPLICATIONS

[0001] This application is a division of co-pending application Ser. No. 12/350,448 filed on Jan. 8, 2009, which claims foreign priority to Japanese Application No. 2008-010465 filed on Jan. 21, 2008. The entire content of each of these applications is hereby expressly incorporated by reference.

#### BACKGROUND OF THE INVENTION

[0002] 1. Field of the Invention

[0003] The present invention relates to a semiconductor device and a manufacturing method thereof. Specifically, it relates to a semiconductor device including a wiring layer which contains copper as a main component and a manufacturing method thereof.

[0004] 2. Description of the Related Art

[0005] From the demands of high integration of semiconductor devices in recent years, copper with a low resistance has come to be used as a material for wirings, plugs, and pads, etc.

[0006] It is described in JP-A-2005-158930 that a copper alloy film where an impurity is added to a copper film is adopted as a material for wiring as measures against the deterioration of reliability in the case of using copper. The aforementioned patent document describes a semiconductor device having a configuration in which the concentration of the impurity contained in at least one wiring layer of plural wiring layers increases with the width of the wiring.

[0007] JP-A-Hei6-177128 describes a semiconductor device which has a copper alloy thin film wiring containing aluminum or silicon. Moreover, JP-A-2004-039916 describes a semiconductor device in which a region containing unevenly distributed metal elements which are different from copper is provided at the vicinity of the upper surface of the metallic region containing copper as a main component. [0008] JP-A-2006-253729 describes a technology for depositing a conduction film where a conduction material containing copper to which platinum etc. is added is deposited by a sputtering method and a buried wiring is formed by plating.

#### SUMMARY OF THE INVENTION

[0009] However, in a narrow wiring with fine pitch, copper ions migrate at the interface between the copper wiring and the cap film, etc. formed thereon, so that a problem arises that the breakdown voltage between the wirings decreases and the Time Dependent Dielectric Breakdown (TDDB) lifetime remarkably decreases On the other hand, in a wide wiring with a wide wiring width, a phenomenon of SIV (Stress Induced Void), where a void caused by stress is created, becomes a problem.

[0010] Conventionally, since measures with respect to such wiring size have not been taken, it has been impossible to prevent the decrease of TDDB lifetime in the narrow wiring and SIV in the wide wiring simultaneously.

[0011] According to the present invention, a semiconductor device is provided, including a substrate, an insulator film formed over the substrate, and plural metal wirings with different widths which is formed in the insulator film, con-

tains copper as a main component, and contains an impurity metal which is different from copper, in which the plural metal wirings includes a first metal wiring with a concentration profile where the concentration of the impurity metal increases from the center part of the stacking direction to the surface and a second metal wiring with a concentration profile where the concentration of the impurity metal decreases from the bottom surface of the stacking direction to the surface.

[0012] Moreover, according to the present invention, a semiconductor device is provided, including a substrate, a first metal wiring which is formed over the substrate, contains copper as a main component, and contains an impurity metal which is different from copper, and a second metal wiring which is formed over the substrate, contains copperas a main component, contains an impurity metal which is different from copper, and is wider than the first metal wiring, in which the first metal wiring has a concentration profile where the concentration of the impurity metal increases from the center part of the stacking direction to the surface and the concentration of the impurity metal of the surface of the first metal wiring is higher than the concentration of the impurity metal of the surface of the second metal wiring.

[0013] According to such a configuration, the impurity metal is formed with high concentration at the surface of the narrow wiring, so that migration of copper ions is suppressed at the interface of the cap film formed thereon, the breakdown voltage between the wirings is improved, and the decrease in the TDDB lifetime can be suppressed. On the other hand, in a wiring with a wide width, the decrease in the TDDB lifetime does not become so big problem. Therefore, there is a possibility that the only disadvantage which arises is the occurrence of an increase in the resistance of the wiring even if the concentration of an impurity is made high at the surface of the wide wiring. However, as described above, a problem, socalled SIV, arises even in a wiring with a wide width. In the aspect of the present invention, although the wide wiring also contains an impurity metal, by taking a configuration where the impurity concentration at the surface thereof is not made as high as that of the narrow wiring, the SIV tolerance can be improved without causing unnecessary increase in the resistance of the wiring.

[0014] According to the present invention, a manufacturing method of a semiconductor device is provided, including forming a wiring metal in a plurality of grooves with different widths formed in an insulator film which is formed over a substrate, wherein forming the wiring metal includes forming a first seed alloy film containing copper and an impurity metal which is different from copper by using a sputtering method to embed a part of the grooves, planarizing the film thickness of the first seed alloy film at the side wall of the grooves by etching the first seed alloy film, forming a second seed alloy film containing copper and the impurity metal by using a sputtering method over the first seed alloy film to embed a part of the grooves, forming a plated metal layer containing copper as a main component over the second seed alloy film to embed the other part of the grooves, annealing the first seed alloy film, the second seed alloy film, and the plated metal

[0015] By taking such a configuration, wiring metal with a profile having high concentration of the impurity metal at the surface is formed in the wiring grooves for the narrow wiring with a narrow wiring width, and the wiring metal is formed in which the concentration of impurity at the surface does not become as high as that of narrow wiring in the wiring grooves

for the wide wiring with a wide wiring width. As a result, the advantages of the aforementioned semiconductor device can be obtained.

[0016] An arbitrary combination of the above-mentioned components and even one in which the present invention is expressed by exchanging methods, devices, etc. are also effective as a mode of the present invention.

[0017] According to the present invention, the decrease of TDDB lifetime in the narrow wiring and SIV in the wide wiring can be effectively prevented simultaneously.

#### BRIEF DESCRIPTION OF THE DRAWINGS

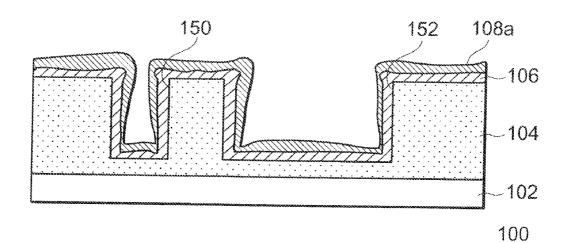

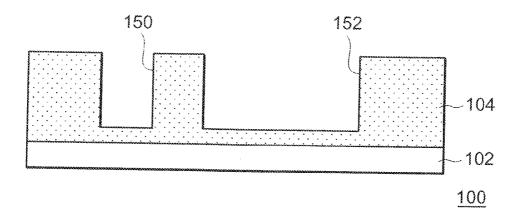

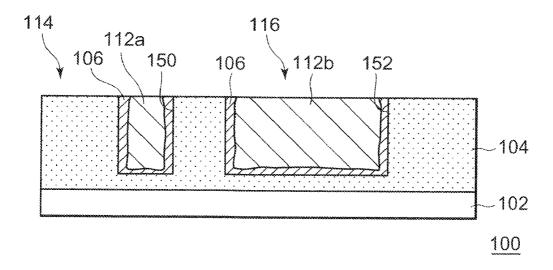

[0018] FIG. 1 is a cross-sectional drawing illustrating a configuration of the semiconductor device in the embodiment of the present invention;

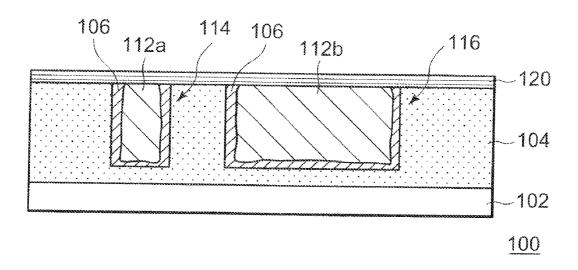

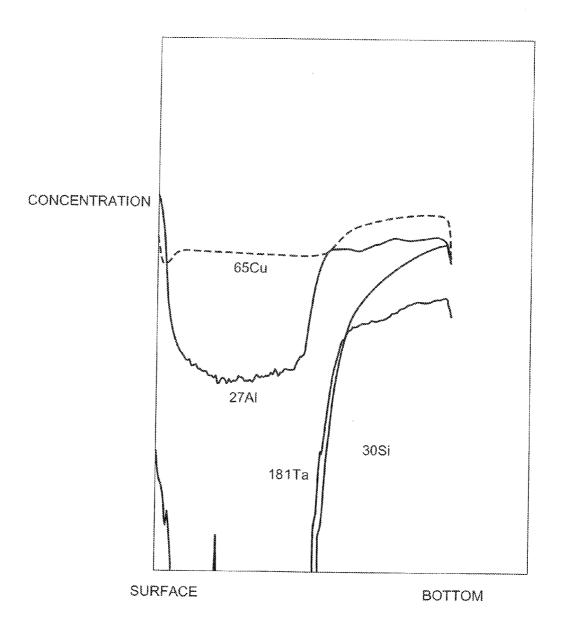

[0019] FIG. 2 is a diagram schematically illustrating concentration profiles of the impurity metals in the first wiring metal of the narrow wiring and the second wiring metal of the wide wiring:

[0020] FIG. 3A and FIG. 3B are process cross-sectional drawings illustrating a manufacturing procedure of the semiconductor device in the embodiment of the present invention; [0021] FIG. 4A and FIG. 4B are process cross-sectional drawings illustrating a manufacturing procedure of the semiconductor device in the embodiment of the present invention; [0022] FIG. 5A and FIG. 5B are process cross-sectional drawings illustrating a manufacturing procedure of the semiconductor device in the embodiment of the present invention; [0023] FIG. 6A and FIG. 6B are process cross-sectional drawings illustrating a manufacturing procedure of the semiconductor device in the embodiment of the present invention; [0024] FIG. 7A and FIG. 7B are process cross-sectional drawings illustrating a manufacturing procedure of the semiconductor device in the embodiment of the present invention; [0025] FIG. 8 is a flow chart illustrating a manufacturing procedure of the semiconductor device in the embodiment of the present invention;

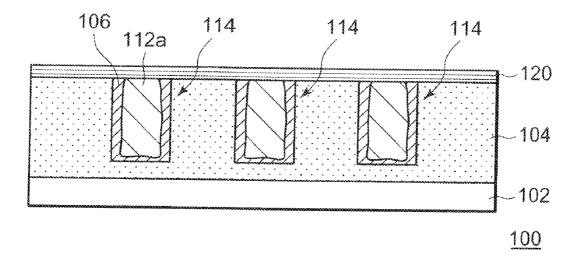

[0026] FIG. 9 is a diagram illustrating concentration profiles of the first wiring metals in the narrow wiring; and [0027] FIG. 10 is a cross-sectional drawing illustrating a configuration of the narrow wiring in the embodiment of the present invention.

## DETAILED DESCRIPTION OF THE PREFERRED EMBODIMENTS

[0028] Hereafter, the embodiment of the present invention will be described by using the drawings. In all drawings, a similar code is affixed to a similar component and the explanation is omitted arbitrarily.

[0029] FIG. 1 is a cross-sectional drawing illustrating a semiconductor device 100 in this embodiment. The semiconductor device 100 includes a semiconductor substrate (substrate) 102, an interlayer dielectric film 104 formed over the semiconductor substrate 102, a narrow wiring (first metal wiring) 111 and a wide wiring (second metal wiring) 116 formed in the interlayer dielectric film 104, and a cap film 120 formed over the interlayer dielectric film 104, the narrow wiring 114, and the wide wiring 116. Herein, a silicon substrate can be used for the semiconductor substrate 102. Although it is not shown in the figure, a transistor, etc. is formed over the semiconductor substrate 102. Another insulator film may be formed between the semiconductor substrate 102 and the interlayer dielectric film 104.

[0030] The narrow wiring 114 may be, for instance, a wiring with a minimum pitch in the semiconductor device 100. Moreover, the wide wiring 116 may be, for instance, a wiring with the maximum width in the semiconductor device 100.

[0031] In this embodiment, the narrow wiring 114 consists of a barrier metal film 106 and the first wiring metal 112a. The

[0031] In this embodiment, the narrow wiring 114 consists of a barrier metal film 106 and the first wiring metal 112a. The wide wiring 116 consists of a barrier metal film 106 and the second wiring metal 112b.

[0032] The first wiring metal 112a contains not only copper as a main component but also an impurity metal which is different from copper. The second wiring metal 112b also contains not only copper as a main component but also an impurity metal which is different from copper.

[0033] Herein, the concentration profile of the impurity metal in the stacking direction is different between the first wiring metal 112a and the second wiring metal 112b. The first wiring metal 112a has a concentration profile in which the concentration of the impurity metal increases from the center part of the stacking direction to the surface thereof. On the other hand, the second wiring metal 112b has a concentration profile in which the concentration of the impurity metal decreases from the bottom surface to the surface thereof. Moreover, the concentration of the impurity metal at the surface of the first wiring metal 112a is higher than the concentration of the impurity metal at the second wiring metal 112b.

[0034] As the impurity metal, for instance, Be, Mg, Zn, Pd, Ag, Cd, Au, Hg, Pt, Si, Zr, Al and Ti, etc. are illustrated as examples, and one or two or more kinds of those may be contained. When Be, Mg, Zn, Pd, Ag, Cd, Au, Pt or Hg is used as an impurity metal, the rate of increase in the resistances of the narrow wiring 114 and the wide wiring 116 can be suppressed. When Zr or Ti is used for the impurity metal, for instance, the adhesion between the insulator film and the barrier metal film, etc. and the metal film can be improved. When a metal, Mg, Sn, Zn, Cd, etc., which has a lower redox potential than copper is used as an impurity metal, corrosion at the surface of the metal film can be prevented.

[0035] As the interlayer dielectric film 104, for instance, a polyorganosiloxane such as HSQ (hydrogensilsesquioxane), MSQ (methylsilsesquioxane), and MHSQ (methylate hydrogensilsesquioxane), etc., an organic material containing an aromatic such as polyarylether (PAE), divinylsiloxane bisbenzocyclobutene (BCB), and Silk (trademark), etc., a low-permittivity material such as SOG (spin on glass), FOX (flowable oxide), Parylene, Cytop, and bensocyclobutene: BCB), etc. can be used.

[0036] FIG. 2 is a schematic drawing illustrating concentration profiles of the impurity metal in the first wiring metal 112a and the second wiring metal 112b. The wiring metal 112a of the narrow wiring 114 has a concentration profile in which the concentration of the impurity metal increases from the center part of the stacking direction to the surface. Moreover, in the first wiring metal 112a, the concentration of the impurity metal at the surface becomes higher than that of the center part. Moreover, the concentration of the impurity metal at the surface of the first wiring metal 112a becomes higher than that at the surface of the second wiring metal 112b of the wide wiring 116. On the other hand, the concentration of the impurity metal at the bottom surface is highest and the concentration of the impurity metal gradually decreases toward the surface.

[0037] Next, the manufacturing procedure of the semiconductor device 100 of this embodiment will be described. FIG.

3 to FIG. 7 are process cross-sectional drawings illustrating a manufacturing procedure of the semiconductor device 100.

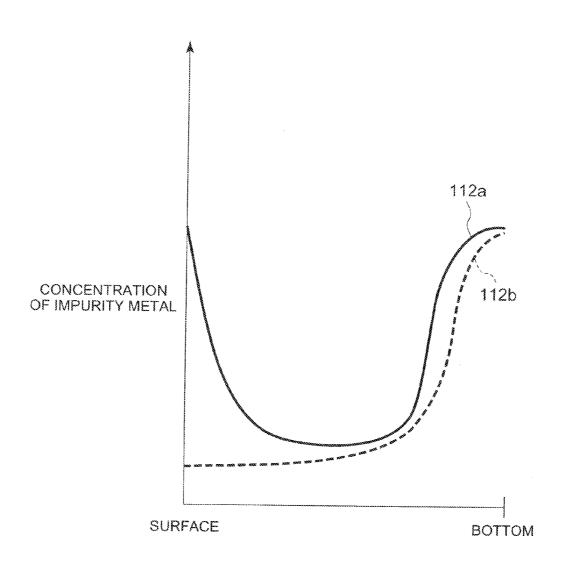

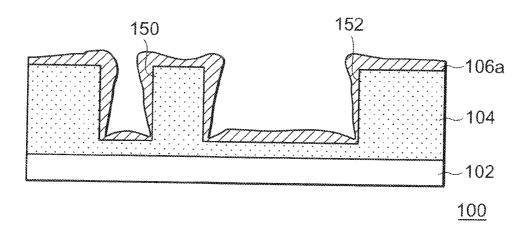

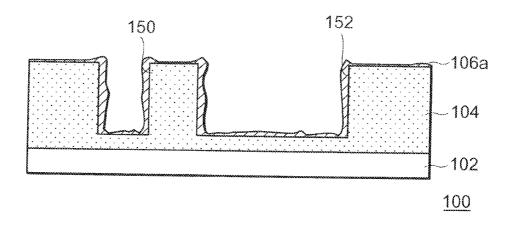

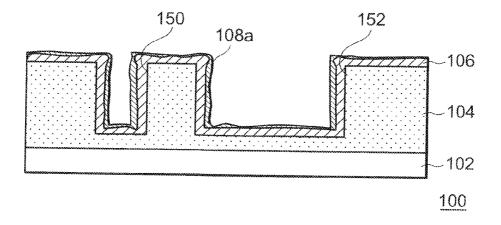

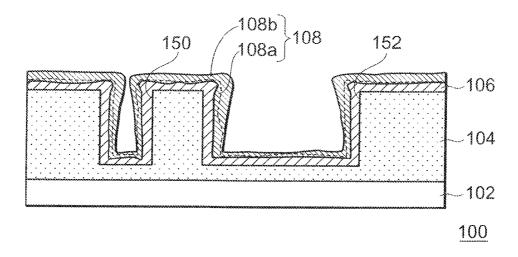

[0038] First, a narrow wiring groove 150 and a wide wiring groove 152 are formed in the interlayer dielectric film 104 (FIG. 3A). Then, a first barrier metal film 106a is formed over the entire surface of the interlayer dielectric film 104 by using a sputtering method (FIG. 3B). At this time, the film thickness of the first barrier metal film 106a becomes uneven at the side walls of the narrow wiring groove 150 and the wide wiring groove 152. The first barrier metal film 106a is deposited thickly on the upper part of the side walls of the narrow wiring groove 150 and the wide wiring groove 152. On the other hand, a part with a thin film thickness is formed in the first barrier metal film 106a at the lower part of the narrow wiring groove 150 and the wide wiring groove 152, and a region may be created where the first barrier metal film 106a is not formed over the side wall of the interlayer dielectric film 104. When the interlayer dielectric film 104 is not covered with the first barrier metal film 106a and the interlayer dielectric film 104 is exposed, it is impossible for it to function as the barrier metal. Therefore, a process for etching the barrier metal film and planarizing the film thickness of the barrier metal over the sidewall of the wiring groove is conventionally carried out. [0039] In this embodiment, by etching the first barrier metal film 106a, a process for planarizing the film thickness of the first barrier metal film 106a over the sidewalls of the narrow wiring groove 150 and the wide wiring groove 152. By etching the first barrier metal film 106a, the upper surface of the interlayer dielectric film 104, except for the region where the narrow wiring groove 150 and the wide wiring groove 152 are formed, and the first barrier metal film 106a over the bottom surfaces of the narrow wiring groove 150 and the wide wiring groove 152 are removed, thereby, the removed first barrier metal film 106a is adhered over the sidewalls of the narrow wiring groove 150 and the wide wiring groove 152 (FIG. 4A). As a result, the film thickness of the first barrier metal film 106a over the sidewalls of the narrow wiring groove 150 and the wide wiring groove 152 can be planarized, and a configuration can be produced where the first barrier metal film 106a is formed over the entire surface of the interlayer dielectric film 104.

[0040] In this embodiment, in addition to the aforementioned etching, the second barrier metal film 106b is formed again over the entire surface of the interlayer film 104 by using a sputtering method (FIG. 4B). As a result, the unevenness of the film thickness of the barrier metal film 106 over the sidewalls of the narrow wiring groove 150 and the wide wiring groove 152 is decreased further (hereinafter, the first barrier metal film 106a and the second barrier metal film 106b are combined to show the barrier metal film 106).

[0041] Herein, the first barrier metal film 106a and the second barrier metal film 106b may be composed of the same material. The first barrier metal film 106a and the second barrier metal film 106b contain, for instance, a high melting point metal such as Ti, W, and Ta, etc. For instance, Ti, TiN, W, WN, Ta, and TaN, etc. are illustrated as a preferable barrier metal film. For instance, a stacking structure, etc. of TaN and Ta may be used as a barrier metal film. In this case, sputtering, etching, and re-sputtering may be performed on each layer.

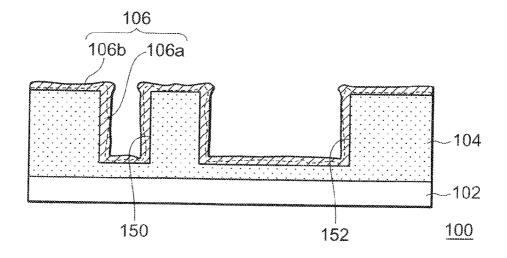

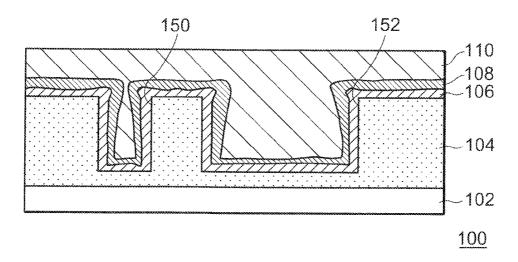

[0042] Then, a first seed alloy film 108a is formed over the

[0042] Then, a first seed alloy film 108a is formed over the entire surface of barrier metal film 106 by using a sputtering method (FIG. 5A). Here, the first seed alloy film 108a may include an alloy containing the aforementioned impurity metal. The concentration of the impurity metal may be con-

trolled to be about 0.1 to 1.0 W %. By making it to be within such a range, the plated film containing copper as a main component can be excellently formed afterwards using the seed alloy film as the seed.

[0043] "Alloy" in this specification means one in which two or more metal elements are melted and solidified, and one containing a nonmetal and a metalloid element in addition to a metal element is also called an alloy. Moreover, as the structure of the alloy, according to the method for mixing the component elements, there is a case where a solid solution and an intermetallic compound are formed and a case where they exist as a mixture. Specifically, within this specification, one in which an element is added in excess of the solid solubility limit is called an "alloy" (Encyclopedia Dictionary of Chemistry published by TOKYO KAGAKU DOJIN Co., LTD)

[0044] At this time, the film thickness of the first seed alloy film 108a becomes uneven over the side walls of the narrow wiring groove 150 and the wide wiring groove 152, just as it is in the case of forming the first barrier metal film 106a. The first seed alloy film 108a is deposited thickly at the upper part of the side walls of the narrow wiring groove 150 and the wide wiring groove 152. On the other hand, a part with a thin film thickness of the first seed alloy film 108a is formed at the lower part of the sidewalls of the narrow wiring groove 150 and the wide wiring groove 152, and a region is created where the first seed alloy film 108a may be not formed over the side wall of the barrier metal film 106. If there is a region where the first seed alloy film 108a is not formed, the plated film is not formed excellently when the plated film is formed afterwards. Therefore, conventionally, a process is performed for planarizing the film thickness of the seed film over the sidewall of the wiring groove by etching the seed film.

[0045] In this embodiment, a process is performed for planarizing the film thickness of the seed alloy film 108a over the sidewalls of the narrow wiring groove 150 and the wide wiring groove 152 by etching the first seed alloy film 108a. By etching the first seed alloy film 108a, the upper surface of the interlayer dielectric film 104, except for the region where the narrow wiring groove 150 and the wide wiring groove 152 is formed, and the first seed alloy film 108a over the bottom surfaces of the narrow wiring groove 150 and the wide wiring groove 152 are removed, thereby, the removed first seed alloy film 108a is adhered over the sidewalls of narrow wiring groove 150 and the wide wiring groove 150 is a different film 108a.

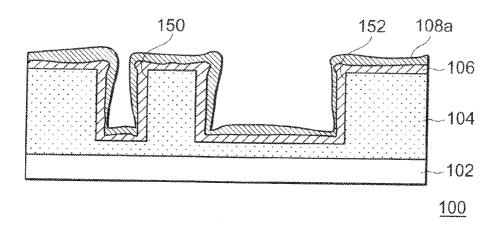

[0046] In this embodiment, in addition to the aforementioned etching, the second seed alloy film 108b is formed again over the entire surface of the interlayer film 104 by using a sputtering method (FIG. 6A). Herein, a configuration may be taken in which the second seed alloy film 108b contains the same material as the first seed alloy film 108a. As a result, the unevenness of the film thickness of the seed alloy film 108 over the side walls of the narrow wiring groove 150 and the wide wiring groove 152 is reduced. Moreover, the overhang portion where seed alloy film 108 adheres thickly is formed at the upper part in the narrow wiring groove 150 with a narrow wiring width.

[0047] Next, a plated metal film 110 is formed by a plating method to embed the narrow wiring groove 150 and the wide wiring groove 152 (FIG. 6B). The plated metal film 110 may have a configuration containing copper as a main component. The plated metal film 110 may have a configuration containing an impurity metal, but the impurity concentration thereof

should be made lower than that of the first seed alloy film 108a and the second seed alloy film 108b.

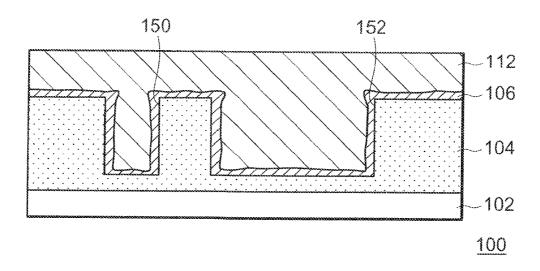

[0048] Next, annealing is performed. Thereby, the impurity metal in the seed alloy film 108 is diffused. Hereinafter, the seed alloy film 108 is combined with the plated metal film 110 and is shown as a wiring metal 112 (FIG. 7A). Here, in the narrow wiring groove 150, the concentration of the impurity metal becomes higher at the upper part of the narrow wiring groove 150 because the overhung portion is formed. On the other hand, in the wide wiring groove 152, the concentration of the impurity metal at the surface is little affected by the impurity metal in the seed alloy film 108 formed over the sidewall because the width of the wiring is wide. Therefore, as shown in FIG. 2, the concentration of the impurity metal is highest at the bottom surface of the wide wiring groove 152 and the concentration of the impurity metal becomes lower in other areas.

[0049] Grains of copper in the plated metal film 110 in the narrow wiring groove 15 and the wide wiring groove 152 are grown by annealing. Here, because of the bottom-up characteristics, the smaller the wiring width the thicker the plated film thickness of the plated metal film 110. Generally, the grain size after annealing becomes greater when the thickness of plated film is thicker. Therefore, the grain size of the plated metal film becomes greater in the narrow wiring groove 150 than in the wide wiring groove 152. Moreover, the impurity metal diffuses along the grain boundaries of copper. As a result, the diffusion rate thereof becomes smaller in the case of a large grain size than in the case of a small grain size. Specifically, the diffusion rate of the impurity metal in the narrow wiring groove 150 with narrow wiring width is smaller than that of the wide wiring groove 152. Therefore, in the narrow wiring groove 150 with narrow wiring width, the wiring metal 112 comes to have a concentration profile where the concentration profile of the seed alloy film 108 and the plated metal film 110 before annealing is maintained as is, to some extent. On the other hand, because the diffusion rate of the impurity metal is large in the wide wiring groove 152, the impurity metal is diffused more uniformly in the plated metal film 110 in the wide wiring groove 152.

[0050] After that, the plated metal film 110, the seed alloy film 108, and the barrier metal film 106 exposed to the outside of the narrow wiring groove 150 and the wide wiring groove 152 are removed by using Chemical Mechanical Polishing (CMP). As a result, the narrow wiring 114 is formed in the narrow wiring groove 150 and the wide wiring 116 is formed in the wide wiring groove 152 (FIG. 7B).

[0051] Afterwards, the cap film 120 is formed over the interlayer dielectric film 104. The cap film 120 may be, for instance, a SiCN film. As a result, the semiconductor device 100 may have the configuration shown in FIG. 1.

[0052] FIG. 8 is a flow chart illustrating a manufacturing procedure of the semiconductor device in this embodiment. First of all, the wiring grooves, such as the narrow wiring groove 150 and the wide wiring groove 152, etc. are formed in the interlayer dielectric film 104 (S102). Then, the first barrier metal film 106a is formed over the entire surface of the interlayer dielectric film by using a sputtering method (S104). Next, the first barrier metal film 106a is etched (S106). After that, by using re-sputtering method, the second barrier metal film 106b is formed over the first barrier metal film 106a (re-sputtering, S108). As a result, the barrier metal film 106 is formed.

[0053] In continuation, the first seed alloy film 108a is formed over the entire surface of the barrier metal film 106 (S110), and the first seed alloy film 108a is etched (S112). Afterwards, by using a re-sputtering method, the second seed alloy film 108b is formed over the first seed alloy film 108a (re-sputtering, S114). As a result, the seed alloy film 108 is formed. In continuation, the plated metal film 110 is formed over the seed alloy film 108 by using the plating method to embed the narrow wiring groove 150 and the wide wiring groove 152 (S116). Then, annealing is performed (S118). As a result, the impurity metal in the seed alloy film 108 is diffused in the plated metal film 110 to form the wiring metal 112. At this time, the concentration profile of the impurity metal in each wiring groove becomes the state shown in FIG.

[0054] Afterwards, using CMP, the narrow wiring 114 and the wide wiring 116 are formed by removing the wiring metal 112 and the barrier metal film 106 which are exposed to the outside of the narrow wiring groove 150 and the wide wiring groove 152 (S120). Afterwards, the cap film 120 is formed over the interlayer dielectric film 104 (S122).

#### **EMBODIMENTS**

#### First Example

[0055] A semiconductor device was manufactured by using the manufacturing procedure of the semiconductor device described and referred to from FIG. 1 and FIG. 3 to FIG. 7 and FIG. 8. FIG. 9 is a drawing illustrating concentration profiles of the impurity metals in the narrow wiring 114. Herein, an example using Al as an impurity metal is shown. The wiring width was assumed to be 90 nm. As shown in the figure, the concentration of Al becomes higher at the surface of the wiring. Moreover, when the cross-sectional photograph of the manufactured wiring was confirmed, an excellent wiring was formed without the creation of voids, etc.

#### Second Example

[0056] Similarly to the first example, neither etching of the step S112 nor the re-sputtering process of S114 in FIG. 8 have been carried out. In this case, when the cross-sectional photograph of the manufactured wiring was confirmed, voids were created over the side wall in the wiring groove. It is considered that the seed alloy film did not work as a seed and the plated film was not formed well.

[0057] Next, the effect of a semiconductor device 100 in this embodiment is described.

[0058] According to the aspect of the semiconductor device 100 in this embodiment, the highly concentrated impurity metal is formed at the surface of the narrow wiring 114, so that migration of copper ions are suppressed at the interface of the cap layer 120, etc. formed thereon. As a result, the breakdown voltage between the wirings is improved, and a decrease in the TDDB lifetime can be suppressed. Especially, when a low-permittivity film is used, the decrease in TDDB lifetime occurs easily. However, according to the semiconductor device 100 of this embodiment, the decrease in the TDDB lifetime can be suppressed even if a low-permittivity film is used for the interlayer dielectric film 104.

[0059] On the other hand, although the wide wiring 116 with a wide width also contains the impurity metal, there is an attempt to make a configuration where the concentration of impurity at the surface is not made as high as the narrow wiring 114 and to make the concentration of impurity in the

wiring more uniform. Therefore, the SIV tolerance can be effectively improved without causing an unnecessary increase in the resistance of the wiring in the wide wiring 116. [0060] According to the aspect of the configuration of the semiconductor device 100 in this embodiment, in the semiconductor device which includes a wide wiring and a narrow wiring, since configurations are taken to have appropriate concentration profiles of the impurity, respectively, the decrease of TDDB lifetime in the narrow wiring and SIV in the wide wiring are effectively prevented simultaneously.

[0061] The embodiments of the present invention have been described referring to the drawings, and these are examples of the present invention and various compositions other than the above can be adopted.

[0062] In the aforementioned embodiments, an example in which the narrow wiring 114 and the wide wiring 116 were formed in the same layer was explained, and the narrow wiring 114 and the wide wiring 116 may be made in different layers. In this case, by forming the narrow wiring and wide wiring, respectively, using the same procedure as the one described above, a wiring metal having the same concentration profile as the narrow wiring 114 is formed in the narrow wiring with a narrow width and the wiring metal having the same concentration profile as the wide wiring 116 is formed in the wide wiring with a wide width.

[0063] Moreover, the manufacturing procedure of the semiconductor device 100 in the aforementioned embodiment can be applied to a configuration where plural narrow wirings 114 have a fine pitch as shown in FIG. 10. In the region where plural narrow wirings 114 are formed with a fine pitch, a decrease in TDDB lifetime easily occurs. The decrease in TDDB lifetime can be effectively suppressed by applying the manufacturing procedure of the semiconductor device 100 in the aforementioned embodiment to such a configuration.

[0064] In the aforementioned embodiment, a procedure of sputtering, etching, and re-sputtering was shown for manufacturing the barrier metal film 106. However, the barrier metal film 106 is not limited to this method and other various procedures may be applied. For instance, the step for resputtering may be omitted. In addition, for instance, a CVD method may be applied to form it.

[0065] Moreover, the narrow wiring 114 and the wide wiring 116 may be applied to either a single-damascene method or a dual-damascene method.

What is claimed is:

1. A manufacturing method of a semiconductor device comprising:

forming a wiring metal in a plurality of grooves with different widths formed in an insulator film which is formed over a substrate,

wherein forming the wiring metal includes:

forming a first seed alloy film containing copper and an impurity metal which is different from copper by using a sputtering method to embed a part of the grooves;

planarizing the film thickness of the first seed alloy film at the side wall of the grooves by etching the first seed alloy film:

forming a second seed alloy film containing copper and the impurity metal by using a sputtering method over the first seed alloy film to embed a part of the grooves;

forming a plated metal layer containing copper as a main component over the second seed alloy film to embed the other part of the grooves; and

annealing the first seed alloy film, the second seed alloy film, and the plated metal film.

2. The manufacturing method of a semiconductor device according to claim 1,

wherein an overhung portion is formed on the second seed alloy film in forming the second seed alloy film.

3. The manufacturing method of a semiconductor device according to claim 1,

wherein the grooves include a first groove and a second groove which is wider than the first groove, and

wherein forming the wiring metal is performed on in the first groove and the second groove, respectively.

**4**. The manufacturing method of a semiconductor device according to claim **3**,

wherein the first groove is a groove for forming the minimum wiring pitch in the semiconductor device, and

wherein the second groove is a groove for forming the maximum wiring in the semiconductor device.

\* \* \* \* \*