(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5376818号

(P5376818)

(45) 発行日 平成25年12月25日(2013.12.25)

(24) 登録日 平成25年10月4日(2013.10.4)

(51) Int.Cl.

F 1

|              |           |            |      |

|--------------|-----------|------------|------|

| HO1L 21/02   | (2006.01) | HO1L 27/12 | B    |

| HO1L 27/12   | (2006.01) | HO1L 27/08 | 331E |

| HO1L 27/08   | (2006.01) | HO1L 27/08 | 321D |

| HO1L 21/8238 | (2006.01) | HO1L 27/06 | 102A |

| HO1L 27/092  | (2006.01) | HO1L 21/02 | B    |

請求項の数 1 (全 29 頁) 最終頁に続く

|              |                               |

|--------------|-------------------------------|

| (21) 出願番号    | 特願2008-72634 (P2008-72634)    |

| (22) 出願日     | 平成20年3月20日 (2008.3.20)        |

| (65) 公開番号    | 特開2008-270772 (P2008-270772A) |

| (43) 公開日     | 平成20年11月6日 (2008.11.6)        |

| 審査請求日        | 平成23年3月3日 (2011.3.3)          |

| (31) 優先権主張番号 | 特願2007-79762 (P2007-79762)    |

| (32) 優先日     | 平成19年3月26日 (2007.3.26)        |

| (33) 優先権主張国  | 日本国 (JP)                      |

|           |                                                |

|-----------|------------------------------------------------|

| (73) 特許権者 | 000153878<br>株式会社半導体エネルギー研究所<br>神奈川県厚木市長谷398番地 |

| (72) 発明者  | 山崎 舜平<br>神奈川県厚木市長谷398番地 株式会社<br>半導体エネルギー研究所内   |

| (72) 発明者  | 大沼 英人<br>神奈川県厚木市長谷398番地 株式会社<br>半導体エネルギー研究所内   |

審査官 岩本 勉

最終頁に続く

(54) 【発明の名称】 SOI 基板の作製方法

## (57) 【特許請求の範囲】

## 【請求項 1】

単結晶シリコン基板上の絶縁膜に、第1の原子ビームの照射、第1のイオンビームの照射、第1のプラズマ処理または第1のラジカル処理を行う工程と、

基板に第2の原子ビームの照射、第2のイオンビームの照射、第2のプラズマ処理または第2のラジカル処理を行う工程と、

前記単結晶シリコン基板と前記基板を、前記絶縁膜を介して貼り合わせる工程と、

前記単結晶シリコン基板から単結晶シリコン薄膜を分離して、前記基板上に前記単結晶シリコン薄膜を形成する工程と、を有し、

前記単結晶シリコン基板の大きさは、露光装置の1ショットサイズのn倍 (nは任意の正の整数で、n>1) であることを特徴とするSOI基板の作製方法。 10

## 【発明の詳細な説明】

## 【技術分野】

## 【0001】

本発明は、絶縁表面を有する基板上に形成された単結晶シリコン薄膜を有するSOI (silicon on insulator) 基板及びその作製方法に関する。また、当該SOI基板を用いて作製される半導体装置に関する。なお、本明細書中において半導体装置とは半導体特性を利用することで機能しうる装置全般を示す。

## 【背景技術】

## 【0002】

近年、VLSI技術が飛躍的な進歩を遂げる中で、高速化、低消費電力化を実現できるSOI構造が注目されている。この技術は、従来バルク単結晶シリコンで形成されていた電界効果トランジスタ(FET; Field Effect Transistor)の活性領域(チャネル形成領域)を、単結晶シリコン薄膜とする技術である。SOI構造を用いてMOS型電界効果トランジスタを作製すると、従来のバルク単結晶シリコン基板を用いる場合よりも寄生容量を小さくでき、高速化に有利になることが知られている。

#### 【0003】

従来のSOI基板としては、SIMOX基板、貼り合わせ基板が挙げられる。例えばSIMOX基板は、単結晶シリコン基板に酸素イオンを注入し、1300以上で熱処理して埋め込み酸化膜(BOX; Buried Oxide)層を形成することにより、表面に単結晶シリコン薄膜を形成してSOI構造を得ている。SIMOX基板は、酸素イオンの注入を精密に制御できるため単結晶シリコン薄膜を均一な膜厚で高制御に形成できるが、酸素イオンの注入に長時間を有するため時間及びコストに問題がある。また、酸素イオン注入の際に単結晶シリコン薄膜にダメージが入りやすいという問題もある。

10

#### 【0004】

貼り合わせ基板は、酸化膜を介して2枚の単結晶シリコン基板(ベース基板及びボンド基板)を貼り合わせ、一方の単結晶シリコン基板(ボンド基板)を裏面(貼り合わせた面ではない面)から薄膜化することにより、単結晶シリコン薄膜を形成してSOI構造を得ている。薄膜化する手段は、研削・研磨では均一で薄い単結晶シリコン薄膜を形成することが難しいため、スマートカット(登録商標)と呼ばれる水素イオン注入を利用する技術が提案されている(例えば、特許文献1参照)。

20

#### 【特許文献1】特開平5-211128号公報

#### 【発明の開示】

#### 【発明が解決しようとする課題】

#### 【0005】

しかしながら、従来のSOI基板は1枚の単結晶シリコン内に埋め込み層を形成することでSOI構造を得る、或いは1枚の単結晶シリコン基板に1枚の単結晶シリコン基板を貼りあわせてその内の1枚の単結晶シリコン基板を薄膜化することによりSOI構造を得ている。そのため、単結晶シリコン基板の大きさに依存しており、大面積化を図ることは難しかった。したがって、本発明は、大面積化を可能とするSOI基板の製造技術を提供し、生産性を向上させることを課題とする。

30

#### 【課題を解決するための手段】

#### 【0006】

本発明は、絶縁表面を有する基板上に設けられた単結晶シリコン薄膜を有するSOI基板である。単結晶シリコン薄膜は貼り合わせ法により得ることができる。本発明は、所望の大きさに加工した単結晶シリコン基板を用いて、絶縁表面を有する基板上に単結晶シリコン薄膜を形成することを特徴の1つとする。

#### 【0007】

本発明の具体的な構成は、第1単結晶シリコン基板を分断して、露光装置の1ショットサイズのn倍(nは任意の正の整数で、n>1)の第2単結晶シリコン基板を形成する工程Aと、第2単結晶シリコン基板の一表面上に絶縁層を形成し、第2単結晶シリコン基板にイオン注入層を形成する工程Bと、絶縁表面を有する基板と第2単結晶シリコン基板とを、絶縁層を間に介して貼り合わせ、熱処理することにより、イオン注入層に沿って第2単結晶シリコン基板を分断し、絶縁表面を有する基板上に単結晶シリコン薄膜を形成する工程Cと、を行うSOI基板の作製方法である。

40

#### 【0008】

上記構成において、イオン注入層は、第2単結晶シリコン基板に絶縁層が形成された面から水素イオンを注入して形成する。本明細書において、水素イオンを注入するとは、加速された水素イオンを照射して単結晶シリコン基板中に水素を含ませることを指す。また、本明細書において、イオン注入層とは、単結晶シリコン基板へイオンを照射し、イオン

50

の照射により微小な空洞を有するように脆弱化された領域であり、以下、「イオン注入層」を「脆化層」という。そして、後の熱処理によって脆化層で分断することで、絶縁表面を有する基板上に単結晶シリコン薄膜を形成することができる。

#### 【0009】

本発明の他の構成は、露光装置の1ショットサイズをX、第1単結晶シリコン基板を分断した第2の単結晶シリコン基板のサイズをYとして、XとYとの関係が $0.8X < Y < 1.2X$ 、 $0.9X < Y < 1.1X$ 、 $0.99X < Y < 1.01X$ 、又は $0.999X < Y < 1.001X$ のいずれかの条件式を満たすように第2単結晶シリコン基板を形成する工程Aと、第2単結晶シリコン基板の一表面上に絶縁層を形成し、第2単結晶シリコン基板に脆化層を形成する工程Bと、絶縁表面を有する基板と第2単結晶シリコン基板とを、絶縁層を間に介して貼り合わせ、熱処理することにより、脆化層に沿って第2単結晶シリコン基板を分断し、絶縁表面を有する基板上に単結晶シリコン薄膜を形成する工程Cと、を行うSOI基板の作製方法である。10

#### 【0010】

上記構成において、工程Aを繰り返すことにより、第2単結晶シリコン基板を複数形成し、1枚の絶縁表面を有する基板に対して工程B及び工程Cを繰り返すことにより、絶縁表面を有する基板上に単結晶シリコン薄膜を複数形成することもできる。

#### 【0011】

本発明の他の構成は、第1単結晶シリコン基板の一表面上に絶縁層を形成し、第1単結晶シリコン基板に脆化層を形成する工程Aと、第1単結晶シリコン基板を分断して、露光装置の1ショットサイズのn倍(nは任意の正の整数で、n=1)の第2単結晶シリコン基板を形成する工程Bと、絶縁表面を有する基板と第2単結晶シリコン基板とを、絶縁層を間に介して貼り合わせ、熱処理することにより、脆化層に沿って第2単結晶シリコン基板を分断し、絶縁表面を有する基板上に単結晶シリコン薄膜を形成する工程Cと、を行うSOI基板の作製方法である。20

#### 【0012】

本発明の他の構成は、第1単結晶シリコン基板の一表面上に絶縁層を形成し、第1単結晶シリコン基板に脆化層を形成する工程Aと、露光装置の1ショットサイズをX、第1単結晶シリコン基板を分断した第2の単結晶シリコン基板のサイズをYとして、XとYとの関係が $0.8X < Y < 1.2X$ 、 $0.9X < Y < 1.1X$ 、 $0.99X < Y < 1.01X$ 、又は $0.999X < Y < 1.001X$ のいずれかの条件式を満たすように第2単結晶シリコン基板を形成する工程Bと、絶縁表面を有する基板と第2単結晶シリコン基板とを、絶縁層を間に介して貼り合わせ、熱処理することにより、脆化層に沿って第2単結晶シリコン基板を分断し、絶縁表面を有する基板上に単結晶シリコン薄膜を形成する工程Cと、を行うSOI基板の作製方法である。30

#### 【0013】

上記構成において、工程Bを繰り返すことにより、第2単結晶シリコン基板を複数形成し、1枚の絶縁表面を有する基板に対して工程Cを繰り返すことにより、絶縁表面を有する基板上に単結晶シリコン薄膜を複数形成することもできる。

#### 【0014】

また、絶縁表面を有する基板にはガラス基板を用いると、より大面積化を図ることができるため好ましい。

#### 【0015】

また、本発明の構成は、ベース基板である絶縁表面を有する基板上に絶縁層を介して設けられた複数の単結晶シリコン薄膜を有するSOI基板である。

#### 【0016】

また、本発明の構成は、絶縁表面を有する基板上に絶縁層を介して設けられた複数の単結晶シリコン薄膜を有し、単結晶シリコン薄膜の一の大きさが、露光装置の1ショットサイズのn倍(nは任意の正の整数で、n=1)であるSOI基板である。

#### 【0017】

50

また、本発明の他の構成は、絶縁表面を有する基板上に絶縁層を介して設けられた複数の単結晶シリコン薄膜を有し、単結晶シリコン薄膜の1つの大きさは、露光装置の1ショットサイズをX、単結晶シリコン基板のサイズをYとして、XとYとの関係が $0.8X < Y < 1.2X$ 、 $0.9X < Y < 1.1X$ 、 $0.99X < Y < 1.01X$ 、又は $0.999X < Y < 1.001Y$ のいずれかの条件式を満たすSOI基板である。

#### 【0018】

上記構成において、複数の単結晶シリコン薄膜は矩形状であることが好ましい。

#### 【0019】

また、上記構成において、絶縁表面を有する基板はガラス基板とすることが好ましい。

#### 【発明の効果】

10

#### 【0020】

本発明を適用することで、SOI基板の大面積化が可能となる。よって、当該SOI基板を用いた製造分野、例えば半導体集積回路等の半導体装置の生産性を向上させることができる。

#### 【発明を実施するための最良の形態】

#### 【0021】

本発明の実施の形態について、図面を用いて以下に説明する。但し、本発明は以下の説明に限定されず、本発明の趣旨及びその範囲から逸脱することなく、その形態及び詳細を様々に変更しうることは、当業者であれば容易に理解される。したがって、本発明は以下に示す実施の形態の記載内容に限定して解釈されるものではない。なお、以下に説明する本発明の構成において、同じものを指す符号は異なる図面間で共通して用いる場合がある。

20

#### 【0022】

##### (実施の形態1)

本発明に係るSOI基板は、単結晶シリコン基板（以下、「ボンド基板」ともいう）から、異種基板（以下、「ベース基板」ともいう）に転写して形成する。以下、本発明を適用したSOI基板の作製方法の一形態について説明する。

#### 【0023】

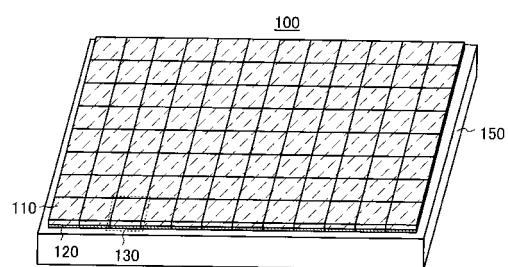

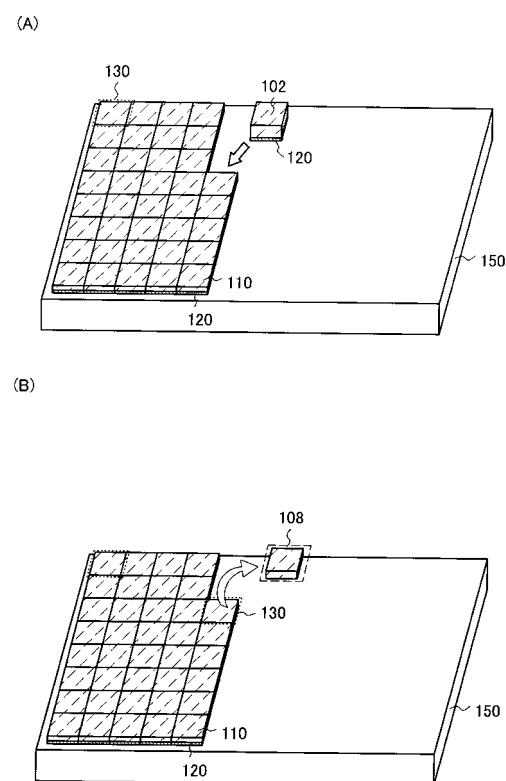

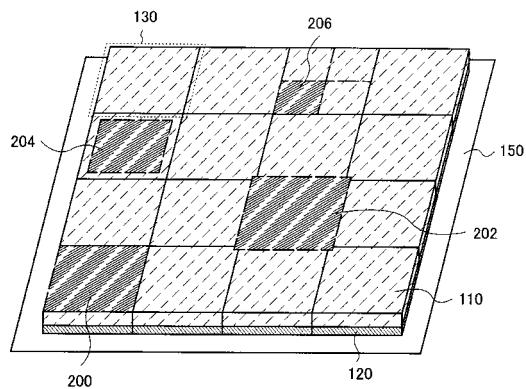

図1は、本発明に係るSOI基板100の構成を示す斜視図の一例である。SOI基板100は、1枚の基板150表面に、絶縁層120及び単結晶シリコン薄膜110が順次積層された積層体130が複数設けられた構造を有する。単結晶シリコン薄膜110は、絶縁層120を介して基板150上に設けられており、いわゆるSOI構造を形成している。つまり、1枚の基板150上に複数の単結晶シリコン薄膜110が設けられて、1枚のSOI基板100を形成している。なお、絶縁層120及び単結晶シリコン薄膜110が順に積層された積層体130は、隣接する積層体130同士の間に隙間があかないよう敷き詰めて設けられていることが好ましい。

20

#### 【0024】

単結晶シリコン薄膜110のサイズは、ステッパ露光装置に代表される露光装置の1ショットのサイズのn倍（nは任意の正の整数で、n=1）とすることが好ましい。露光装置の1ショットのサイズは装置に依存するが、例えば既存のステッパ露光装置を利用する場合、1ショットサイズは25mm角、100mm角、113mm角、132mm角、又は144mm角等が知られている。単結晶シリコン薄膜110の大きさを露光装置の1ショットサイズのn倍とすることで、完成するSOI基板を用いて各種半導体装置を作製する際に、1つの単結晶シリコン薄膜110内に所望の回路パターンを効率良く形成することができる。また、隣接する単結晶シリコン薄膜との境界にかかることなく、1つの単結晶シリコン薄膜110内で所望の回路パターンを効率的に形成することができる。よって、完成するSOI基板を用いて、歩留まり良く半導体装置を作製することが可能となる。なお、本明細書における「サイズ」とは面積を示すものとする。

30

#### 【0025】

なお、通常の製造プロセスにおいて、歩留まりや信頼性を考えた場合、1ショットの露

40

50

光範囲限界まで回路パターンを形成することは望ましくない。大抵の場合は、1ショットの露光範囲よりも狭い範囲で回路パターンを形成するよう設計している。よって、単結晶シリコン薄膜110の大きさは必ずしも1ショットサイズのn倍(nは任意の正の整数で、n=1)に限定されるものではない。例えば、露光装置の1ショットサイズをXとし、単結晶シリコン薄膜110のサイズをYとする場合、下記数式(1)の条件を満たすことが好ましい。更に好ましくは数式(2)の条件を満たすのが望ましい。より好ましくは数式(3)の条件を満たすのが望ましい。最も好ましくは数式(4)の条件を満たすのが望ましい。

【0026】

【数1】

$$0.8X < Y < 1.2X \quad \dots \quad (1)$$

10

【0027】

【数2】

$$0.9X < Y < 1.1X \quad \dots \quad (2)$$

【0028】

【数3】

$$0.99X < Y < 1.01X \quad \dots \quad (3)$$

20

【0029】

【数4】

$$0.999X < Y < 1.001X \quad \dots \quad (4)$$

【0030】

図11に、単結晶シリコン薄膜110の大きさと露光装置の1ショットサイズとの関係の例を示す。図11において、第1露光範囲200、第2露光範囲202、第3露光範囲204、第4露光範囲206は、それぞれ露光装置の1ショットサイズの露光範囲とする。

【0031】

30

ここで、第1露光範囲200及び第4露光範囲206は、単結晶シリコン薄膜110の大きさが露光装置の1ショットサイズのn倍の例を示している。具体的には、第1露光範囲200は単結晶シリコン薄膜110が1ショットサイズの等倍の例を示し、第4露光範囲206は単結晶シリコン薄膜110が1ショットサイズの4倍の例を示している。また、第2露光範囲202、第3露光範囲204は、単結晶シリコン薄膜110の大きさが上記数式(1)乃至(4)の条件を満たす例を示している。具体的には、第2露光範囲202は単結晶シリコン薄膜110が1ショットサイズよりも上記数式(1)乃至(4)満たす範囲で小さい例を示し、第3露光範囲204は、単結晶シリコン薄膜110の大きさが上記数式(1)乃至(4)を満たす範囲で大きい例を示している。このようにすることで、1つの単結晶シリコン薄膜内に所望の回路パターンを形成することができ、歩留まり向上を図ることができる。

40

【0032】

基板150は、ガラス基板、石英基板等の絶縁表面を有する基板を用いる。好ましくは基板150としてガラス基板を用いるのがよく、ガラス基板を用いる場合、例えば第6世代(1500mm×1850mm)、第7世代(1870mm×2200mm)、第8世代(2200mm×2400mm)といわれる大面積のマザーガラス基板を用いることができる。大面積のマザーガラス基板をベース基板(ここでは基板150)として用い、本発明を適用してSOI基板を作製することで、SOI基板の大面積化が実現できる。例えばSOI基板を用いて半導体集積回路を形成する場合、SOI基板の大面積化が実現すれば、一度に多数のIC、LSI等のチップを製造することができ、取り数が増大して生産

50

性を飛躍的に向上させることができる。

**【0033】**

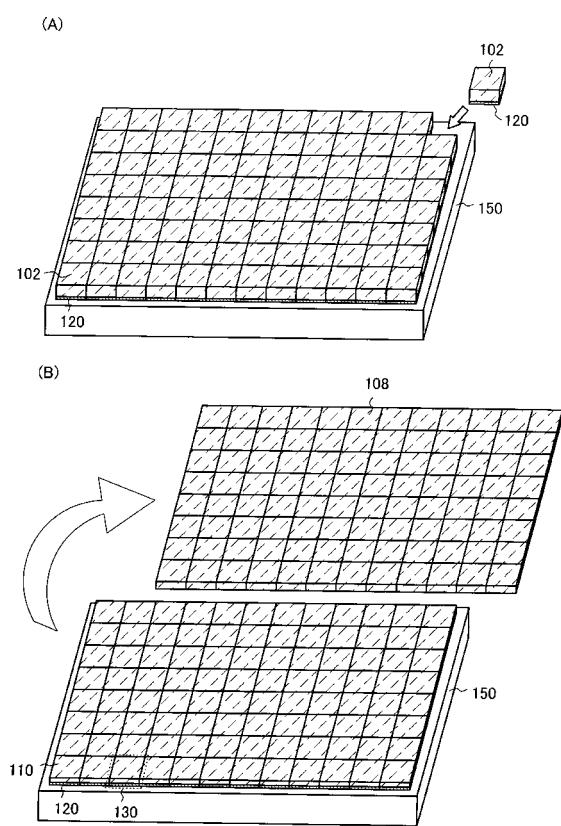

次に、図1に示すSOI基板100の作製方法について、図2、図3を用いて具体的に説明する。

**【0034】**

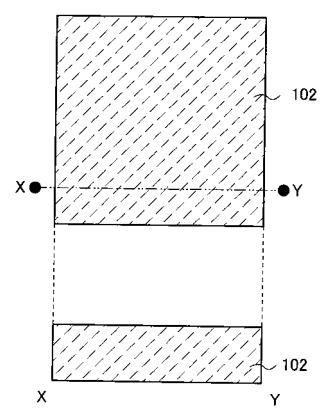

まず、ボンド基板となる単結晶シリコン基板102を準備する(図3(A)参照)。単結晶シリコン基板102は、所望の大きさ、形状に加工したものを準備する。

**【0035】**

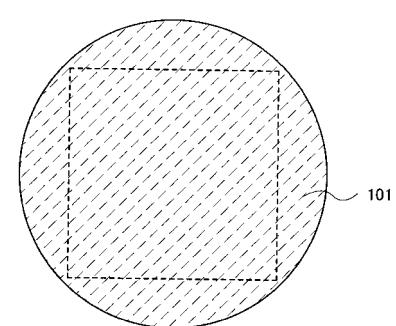

図2(A)、(B)に示すように、単結晶シリコン基板101(以下、「第1単結晶シリコン基板」ともいう)を分断して、所望の大きさ、形状を有する単結晶シリコン基板102(以下、「第2単結晶シリコン基板」ともいう)を得ることができる。ここで用いる第1単結晶シリコン基板101は市販のものを用いればよい。市販の単結晶シリコン基板としては、直径5インチ(125mm)、直径6インチ(150mm)、直径8インチ(200mm)、直径12インチ(300mm)サイズのものが代表的であり、その形状は円形のものがほとんどである。また、第1単結晶シリコン基板101の膜厚は1.5mm程度まで適宜選択できる。本実施の形態では、第1単結晶シリコン基板101の膜厚は0.7mm乃至0.75mmの範囲程度とする。

**【0036】**

第2単結晶シリコン基板102は、ステッパ露光装置の1ショットサイズのn倍(nは任意の正の整数で、n=1)、又は上記式(1)乃至(4)の条件を満たすように加工することが好ましい。例えば、25mm角、100mm角、113mm角、132mm角、144mm角、又はこれらのn倍(nは任意の正の整数で、n=1)程度に加工することが好ましい。

**【0037】**

また、第2単結晶シリコン基板102の形状は特に限定されないが、後にベース基板である基板150に貼り合わせること及びステッパ露光装置により露光されるパターン形状を考慮すると、矩形状(正方形を含む)とすることが好ましい。なお、第1単結晶シリコン基板101からの第2単結晶シリコン基板102の分断は、ダイサー或いはワイヤソー等の切断装置、レーザ切断、プラズマ切断、電子ビーム切断、その他任意の切断手段を用いることができる。

**【0038】**

本実施の形態では、第1単結晶シリコン基板101を円形の8インチサイズの基板とし、該基板から100mm角の第2単結晶シリコン基板102を加工するものとする(図2(A)、(B)参照)。第2単結晶シリコン基板102は、ボンド基板となる。なお、ここでは1枚の第1単結晶シリコン基板101から、所望の大きさの1枚の第2単結晶シリコン基板102を加工する例を示すが、本発明は特に限定されない。可能であれば、1枚の単結晶シリコン基板から所望の大きさの単結晶シリコン基板を複数枚加工しても構わない。

**【0039】**

次に、第2単結晶シリコン基板102表面に絶縁層120を形成する(図3(A)参照)。

**【0040】**

絶縁層120は、CVD法やスパッタリング法で形成することもできるが、好ましくは熱酸化法を用いて形成すると緻密で特性の良好な膜を得ることができる。なお、熱酸化法を用いる場合、絶縁層120としては酸化シリコン(SiO<sub>x</sub>)膜が形成される。その他CVD法等用いて形成する場合は、絶縁層120として酸化シリコン(SiO<sub>x</sub>)層、窒化シリコン層(SiN<sub>x</sub>)、酸化窒化シリコン層、窒化酸化シリコン層等を形成すればよい。絶縁層120は、単層構造で形成してもよいし、積層構造で形成してもよい。例えば、熱酸化法を用いて緻密な酸化シリコン層を形成した後、CVD法を用いて窒化シリコン層又は窒化酸化シリコン層を形成してもよい。なお、絶縁層120は、少なくとも単結晶

10

20

30

40

50

シリコン基板 102 の一表面上に形成すればよく、側面及び裏面を含む全面に形成しても構わない。また、絶縁層 120 は、膜厚 50 nm 乃至 3000 nm、好ましくは 50 nm 乃至 200 nm の範囲で形成する。本実施の形態では、熱酸化法により、絶縁層 120 として膜厚 100 nm の酸化シリコン層を形成する。

#### 【0041】

次に、第 2 単結晶シリコン基板 102 に水素イオン 104 を照射して脆化層 106 を形成する（図 3（B）参照）。水素イオン 104 は、絶縁層 120 が形成された面側から照射する。電界で加速された水素イオン 104 の照射によって、第 2 単結晶シリコン基板 102 の所定の深さ（膜厚方向の深さ）に脆化層 106 が形成される。なお、脆化層 106 は水素ではなく希ガスを用いて形成してもよいし、両者を混合させたものを用いて形成することもできる。

10

#### 【0042】

脆化層 106 は、イオンをイオンドーピング法やイオン注入法によって照射して形成すればよい。イオンドーピング法は、質量分離せずにイオン化したガスを電界で加速して単結晶シリコン基板に照射する方式をいう。イオンドーピング法はイオンドーピング装置を用いて行えばよい。なお、イオン注入法とは、イオン注入装置によってイオン化したガスを質量分離して単結晶シリコン基板に照射する方式をいう。イオン注入法を用いて、イオン化した水素ガスを質量分離して、電界で加速して照射することができる。

#### 【0043】

水素イオン 104 は、 $1 \times 10^{16}$  atoms/cm<sup>2</sup> 乃至  $1 \times 10^{17}$  atoms/cm<sup>2</sup> の範囲のドーザ量、20 kV 乃至 200 kV の範囲の加速電圧でイオンを照射するのが好ましい。なお、照射する水素イオン 104 のドーザ量、加速電圧等を適宜選択することで、第 2 単結晶シリコン基板 102 に形成される脆化層 106 の深さ方向の膜厚を制御することができる。第 2 単結晶シリコン基板 102 において、脆化層 106 が形成される深さ方向の膜厚は、完成する SOI 基板の単結晶シリコン薄膜の膜厚を決定する。したがって、水素イオン 104 の照射条件を適宜選択することで、SOI 基板の単結晶シリコン薄膜の膜厚を制御することが可能である。また、絶縁層 120 を介して水素イオン 104 を照射することで、脆化層 106 の深さ制御がしやすくなり、さらにイオンの照射によるシリコン基板表面の荒れを防ぐこともできる。本実施の形態では、水素イオン 104 を  $5 \times 10^{16}$  atoms/cm<sup>2</sup> のドーザ量、100 kV の加速電圧で照射する。

20

30

#### 【0044】

次に、ボンド基板である第 2 単結晶シリコン基板 102 とベース基板である基板 150 とを貼り合わせる（図 3（C）参照）。第 2 単結晶シリコン基板 102 及び基板 150 は、該第 2 単結晶シリコン基板 102 に形成された絶縁層 120 を間に介して貼り合わせる。

#### 【0045】

ベース基板となる基板 150 としては、上述したようにガラス基板、石英基板等の絶縁表面を有する基板を用いる。好ましくは、ガラス基板を用いると安価で大面積化を実現できるため望ましい。

#### 【0046】

なお、基板 150 表面に下地絶縁層として機能する絶縁層を形成してもよい。具体的には、第 2 単結晶シリコン基板 102 と貼り合わされる側の基板 150 表面に絶縁層を形成する。例えば、基板 150 表面に、CVD 法やスパッタリング法により、窒化酸化シリコン、酸化シリコン、窒化シリコン、酸化窒化シリコン等を用いて、単層構造又は積層構造の絶縁層を形成すればよい。基板 150 表面に下地絶縁層として機能する絶縁層を形成することで、該基板 150 からのアルカリ金属等の不純物拡散を防ぐことができる。例えば、下地絶縁層として、下層を窒化シリコン層や窒化酸化シリコン層、上層を酸化シリコン層や酸化窒化シリコン層とした積層構造を形成すると、よりブロッキング効果が高まり好ましい。

40

#### 【0047】

第2単結晶シリコン基板102及び基板150の貼り合わせ（接合ともいう）は、両者の基板の耐熱性を考慮した処理温度で行う。ベース基板となる基板150としてガラス基板を用いる場合は、およそ600℃以下の処理温度で行う必要がある。

#### 【0048】

例えば、原子ビームの照射或いはイオンビームの照射、又はプラズマ処理或いはラジカル処理を利用することで、200℃乃至400℃のいわゆる低温プロセスで基板を貼り合わせることが可能である。

#### 【0049】

原子ビーム或いはイオンビームを利用する場合、具体的にはアルゴン等の不活性ガス中性原子ビーム或いは不活性ガスイオンビームを用いることができる。なお、原子ビームの照射或いはイオンビームの照射は、真空中又は減圧下で行うことが好ましい。10

#### 【0050】

例えば、第2単結晶シリコン基板102の貼り合わせ面（以下、貼り合わせ面を接合面ともいう）にアルゴンイオンビームを照射して、接合面を活性化させる。なお、第2単結晶シリコン基板102及び基板150の貼り合わせは絶縁層120を間に介して行うので、絶縁層120の表面が接合面となる。よって、アルゴンイオンビームを照射することで接合面となる絶縁層120表面を活性化させる。同様に、基板150の接合面にアルゴンイオンビームを照射して、接合面を活性化させる。なお、基板150表面に下地絶縁層として機能する絶縁層を形成し、該絶縁層を介して第2単結晶シリコン基板と貼り合わせる場合は、下地絶縁層として機能する絶縁層表面にアルゴンイオンビームを照射して表面を活性化させる。なお、接合表面を活性化させるには、20eV乃至200eVの範囲のエネルギーを持つアルゴンイオンビームを照射することが好ましい。また、アルゴンイオンビームの照射は、10<sup>-6</sup>Pa台の圧力下で行うことが好ましい。20

#### 【0051】

次に、活性化させた第2単結晶シリコン基板102の接合面及び基板150の接合面同士を接触させて、重ね合わせる。第2単結晶シリコン基板102及び基板150の接合面は活性化されているため、少なくとも表面活性化接合が生じ両者が貼り合わされる。

#### 【0052】

また、プラズマ処理或いはラジカル処理を利用する場合、具体的には酸素プラズマ或いは酸素ラジカル、又は窒素プラズマ或いは窒素ラジカルを用いることができる。30

#### 【0053】

例えば、第2単結晶シリコン基板102の接合面に酸素プラズマを照射して、接合面を活性化（親水化）させる。なお、第2単結晶シリコン基板102及び基板150の貼り合わせは絶縁層120を間に介して行うので、絶縁層120の表面が接合面となる。よって、酸素プラズマ処理により接合面となる絶縁層120表面を親水化させる。同様に、基板150の接合面に酸素プラズマを照射して、接合面を親水化させる。なお、基板150表面に下地絶縁層として機能する絶縁層を形成し、該絶縁層を介して第2単結晶シリコン基板と貼り合わせる場合は、下地絶縁層として機能する絶縁層表面を酸素プラズマ処理して親水化させる。なお、接合面を親水化させる際又は親水化させた後に、水素イオン、水酸基、水分子等を含むガスを混入させてもよい。親水化の際にこのようなガスを混入させることで、接合面のOH基を増大させ、接合面を均一に親水化させる、又は親水化処理速度を促進させることができになる。また、アルゴンプラズマを照射して接合面の不純物除去を行った後、酸素プラズマ処理して、接合面を均一に親水化させることもできる。また、親水化させた後に、純水、水素添加水、酸素添加水、又はオゾン添加水等で洗浄し、乾燥させてもよい。40

#### 【0054】

なお、接合面は、超音波洗浄又はメガソニック洗浄により、接合面に付着するミクロなゴミなどのパーティクル除去を行った後、原子ビームやイオンビームを利用した表面活性化処理又はプラズマ処理やラジカル処理を利用した親水化処理を行うことが好ましい。また、接合前には、オゾン添加水での洗浄によって親水性を向上させることができることも好ましい。50

**【 0 0 5 5 】**

次に、親水化させた第2単結晶シリコン基板102の接合面及び基板150の接合面同士を接触させて、重ね合わせる。第2単結晶シリコン基板102及び基板150の接合面は親水化されており、少なくとも分子間力(水素結合)により両者が貼り合わされる。

**【 0 0 5 6 】**

なお、酸素プラズマ処理を行って接合面を親水化させた後、該接合面に窒素ラジカルを照射してもよい。窒素ラジカルを照射することで、親水化された接合面に生成されたOH基を窒素置換してON基とすることができます。この後、接合面を接触させて重ね合わせることで、接合界面に窒素化合物を形成させることができる。その結果、より強固に接合させることができる。

10

**【 0 0 5 7 】**

なお、原子ビームやプラズマを利用してボンド基板及びベース基板を接触させて貼り合わせた後は、加熱処理、加圧処理、又は加熱処理及び加圧処理を行うことが好ましい。加熱処理や加圧処理を行うことで、基板間の接合強度を向上させ、より強固に接合することが可能となる。加熱処理の温度範囲は貼り合わせる両者の基板の耐熱温度以下とし、加圧処理の圧力範囲は基板の耐圧性を考慮して行う。また、加圧処理は、接合面に対して垂直な方向に行なうことが好ましい。例えば、上述したように原子ビーム或いはイオンビーム、又はプラズマ処理或いはラジカル処理を利用して第2単結晶シリコン基板102及び基板150を貼り合わせた後、400未満、好ましくは200乃至400の温度範囲での熱処理を行う。

20

**【 0 0 5 8 】**

次に、第2単結晶シリコン基板102の一部の単結晶シリコン層108を剥離する。基板150上には、絶縁層120を介して単結晶シリコン薄膜110が残り、SOI構造が形成される(図3(D)参照)。

**【 0 0 5 9 】**

第2単結晶シリコン基板102は、熱処理を行うことにより脆化層106で剥離を行う。具体的には、400以上、好ましくは500乃至600の温度範囲で熱処理を行うことにより、脆化層106に形成された微小な空洞の体積変化が起こり、脆化層106に沿って破断面を発生させることにより剥離を行う。第2単結晶シリコン基板102は脆化層106に沿って分断され、単結晶シリコン層108が剥離される。その結果、基板150上に絶縁層120を介して単結晶シリコン薄膜110が形成される。ここでは、基板150上に絶縁層120及び単結晶シリコン薄膜110が順に積層されたものを積層体130とする。

30

**【 0 0 6 0 】**

以上で、基板150上に絶縁層120を介して単結晶シリコン薄膜110が設けられたSOI構造が形成される。なお、本発明は、1枚のベース基板上に、絶縁層を介した単結晶シリコン薄膜で形成される複数の積層体を設けてSOI基板を形成することを特徴の1つとしている。例えば、図3(A)乃至図3(D)の工程を繰り返して、図4(A)、(B)に示すように基板150上に複数の積層体130を敷き詰めるように設けていくことで、SOI基板100を作製することができる。

40

**【 0 0 6 1 】**

また、図3(A)乃至図3(C)に示す貼り合わせまで行った後、熱処理による剥離をせずに、図5(A)、(B)に示すように次の単結晶シリコン基板の貼り合わせを行い、全ての単結晶シリコン基板の貼り合わせを行った後、熱処理により一括で剥離を行ってよい。このようにすることで、工程の簡略化を図ることができる。

**【 0 0 6 2 】**

積層体130(単結晶シリコン薄膜110)は、基板150上に敷き詰めて設けることが好ましい。より好ましくは、隣接する積層体同士の隙間があかないようにするとよい。例えばCCDカメラやコンピュータ等の制御装置を用いることで、精度良く複数の積層体を設けていくことが可能になる。また、基板150や積層体130(単結晶シリコン薄膜

50

110)にマーカ等を形成して、位置合わせを行ってもよい。

【0063】

以上で、SOI基板100を得ることができる。本発明に係るSOI基板は大面積化を実現でき、また半導体装置等の製造における歩留まりの向上も可能としている。

【0064】

なお、剥離により得られる単結晶シリコン薄膜は、その表面を平坦化するため、化学的機械的研磨(Chemical Mechanical Polishing: CMP)を行うことが好ましい。また、CMP等の物理的研磨手段を用いず、単結晶シリコン薄膜の表面にレーザビームを照射して平坦化を行ってもよい。なお、レーザビームを照射する際は、酸素濃度が10 ppm以下の窒素雰囲気下で行うことが好ましい。これは、酸素雰囲気下でレーザビームの照射を行うと単結晶シリコン薄膜表面が荒れる恐れがあるからである。また、得られた単結晶シリコン薄膜の薄膜化を目的として、CMP等を行ってもよい。

10

【0065】

以上のように作製したSOI基板を用いて、半導体集積回路等を製造することができる。なお、SOI基板に所望の回路パターンを形成した後は、適宜個々のチップに分断加工すればよい。

【0066】

なお、図2、図3では単結晶シリコン基板を所望のサイズに分断した後、該所望のサイズの単結晶シリコン基板に水素イオンを照射して脆化層を形成する例を示したが、水素イオンを照射して脆化層を形成した後、単結晶シリコン基板を所望のサイズに分断することもできる。

20

【0067】

具体的には、まず、図2(A)に示すような母体となる単結晶シリコン基板に水素イオンを照射し、脆化層を形成する。そして、脆化層を形成した単結晶シリコン基板を分断して、ステッパ露光装置の1ショットサイズのn倍、又は上記数式(1)乃至(4)の条件を満たすように加工する。以降の工程は、図3(C)以降に示した工程と同様にすればよい。

【0068】

本発明を適用することで、大面積のSOI基板を製造・提供することができる。よって、半導体集積回路等の回路パターンを作製する際に、大面積基板を用いて一度に製造プロセスを流すことができ、生産性を向上させることができる。

30

【0069】

また、複数の単結晶シリコン薄膜によりSOI基板を製造するが、個々の単結晶シリコン薄膜の大きさを露光装置の1ショットサイズの整数倍程度とすることで、半導体集積回路等の半導体装置の製造において歩留まりの向上を図ることができる。

【0070】

なお、本実施の形態は、本明細書で示す他の実施の形態と適宜組み合わせができる。

【0071】

40

(実施の形態2)

本実施の形態では、上記実施の形態1で作製されるSOI基板を用いて半導体集積回路を作製する一形態について説明する。ここでは、CMOS回路を形成する一例を示す。なお、本発明に係る半導体集積回路は単純な回路に限定されず、CPU(中央演算処理回路; Central Processing Unit)をはじめとする様々な集積回路を実現することができる。

【0072】

本実施の形態に係る半導体装置の作製方法の一例に関して、図6乃至図10を用いて説明する。

【0073】

50

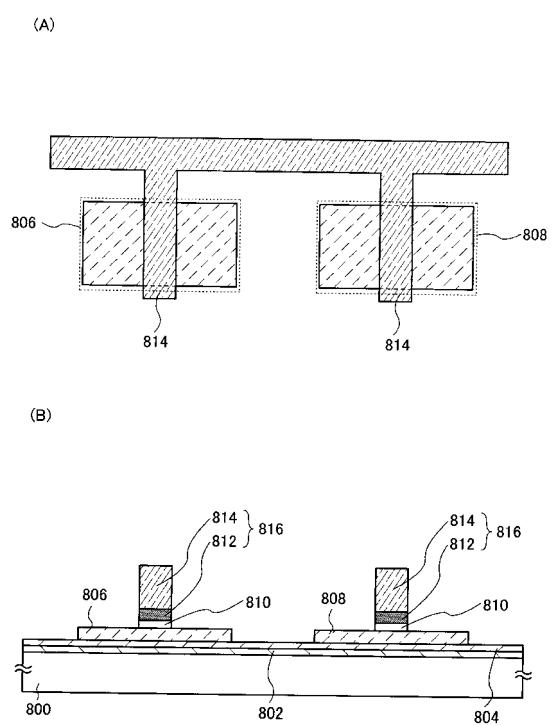

まず、S O I 基板を準備する。ここでは上記実施の形態1で作製されるS O I 基板を用いる。具体的には、絶縁表面を有する基板8 0 0 上に絶縁層8 0 2、絶縁層8 0 4を介して単結晶シリコン薄膜が設けられた基板を用いる。なお、ここでは基板8 0 0 と単結晶シリコン薄膜の間に絶縁層が2層（絶縁層8 0 2、絶縁層8 0 4）の積層構造で設けられている例を示す。絶縁層8 0 2、絶縁層8 0 4は、ボンド基板の単結晶シリコン基板表面に形成した積層構造の絶縁層としてもよいし、ボンド基板表面に形成した絶縁層とベース基板の表面に形成した下地絶縁層として機能する絶縁層との積層構造としてもよい。

#### 【 0 0 7 4 】

また、S O I 基板を構成する単結晶シリコン薄膜は、ステッパ露光装置の1ショットサイズのn倍（nは任意の正の整数で、n=1）の単結晶シリコン薄膜が複数設けられて形成されている。本実施の形態では、そのうちの1つの単結晶シリコン薄膜（すなわち、ステッパ露光装置の1ショットサイズのn倍の大きさを有する1つの単結晶シリコン薄膜）にCMOS回路を形成する例を説明する。10

#### 【 0 0 7 5 】

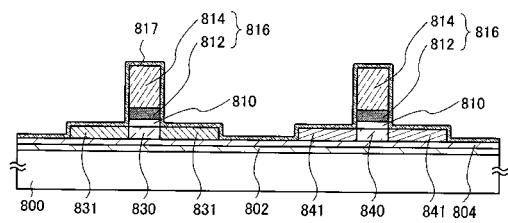

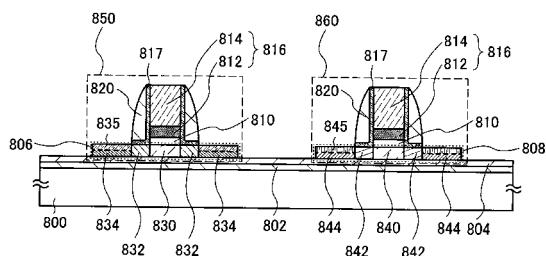

単結晶シリコン薄膜を選択的にエッチングして、第1単結晶シリコン層8 0 6、第2単結晶シリコン層8 0 8を形成する。そして、第1単結晶シリコン層8 0 6及び第2単結晶シリコン層8 0 8上に、ゲート絶縁層8 1 0を介してゲート電極8 1 6を形成する（図6（A）、（B）参照）。

#### 【 0 0 7 6 】

第1単結晶シリコン層8 0 6及び第2単結晶シリコン層8 0 8は、選択的にエッチングして所望の形状に加工する。ここでは島状に加工し、分離させる。準備したS O I 基板の単結晶シリコン薄膜よりも、第1単結晶シリコン層8 0 6及び第2単結晶シリコン層8 0 8の膜厚を薄くしたい場合には、該単結晶シリコン薄膜をエッチングして薄膜化してもよい。また、単結晶シリコン薄膜の一部を変質させて、該変質した部分を選択的にエッチングして薄膜化してもよい。ここで単結晶シリコン薄膜の変質とは、例えば酸化処理、窒化処理等を示す。また、第1単結晶シリコン層8 0 6及び第2単結晶シリコン層8 0 8は、適宜エッチング条件等を制御して、端部が垂直に近いテーパ形状となるように形成してもよいし、緩やかなテーパ形状となるように形成してもよい。例えば、テーパ角が45°以上95°未満、好ましくは60°以上95°未満となるような形状としてもよいし、テーパ角が45°未満の緩やかな形状としてもよい。20

#### 【 0 0 7 7 】

本実施の形態では、第1単結晶シリコン層8 0 6及び第2単結晶シリコン層8 0 8を膜厚30nmとする。

#### 【 0 0 7 8 】

なお、完成するトランジスタの閾値電圧を制御するため、第1単結晶シリコン層8 0 6及び第2単結晶シリコン層8 0 8に低濃度の一導電型を付与する不純物元素を添加してもよい。この場合、トランジスタのチャネル形成領域にも不純物元素が添加されることになる。なお、ここで添加する不純物元素は、ソース領域又はドレイン領域として機能する高濃度不純物領域及びLDD領域として機能する低濃度不純物領域よりも低い濃度で添加する。30

#### 【 0 0 7 9 】

ゲート電極8 1 6は、基板上全面に導電層を形成した後、選択的にエッチングして所望の形状に加工する。ここでは、ゲート電極8 1 6として導電層8 1 2、8 1 4の積層構造を形成した後、選択的にエッチングして、分離した導電層が第1単結晶シリコン層8 0 6及び第2単結晶シリコン層8 0 8をそれぞれ横断するように加工している。このとき、第1単結晶シリコン層8 0 6及び第2単結晶シリコン層8 0 8と重畠しない領域で一体となるように導電層を加工する。つまり、ゲート電極8 1 6を形成する導電層は枝分かれする構成をとり、枝分かれしたそれぞれの導電層が第1単結晶シリコン層8 0 6及び第2単結晶シリコン層8 0 8を横断するように設けられている。

#### 【 0 0 8 0 】

10

20

30

40

50

ゲート電極 816 を形成する導電層は、CVD法やスパッタリング法により、タンタル(Ta)、タンゲステン(W)、チタン(Ti)、モリブデン(Mo)、クロム(Cr)、アルミニウム(Al)、銅(Cu)、又はニオブ(Nb)等の金属元素、又は当該金属元素を含む合金材料若しくは化合物材料を用いて基板全面に導電層を形成した後、当該導電層を選択的にエッチングして形成することができる。また、リン等の一導電型を付与する不純物元素が添加された多結晶シリコンに代表される半導体材料を用いて形成することもできる。

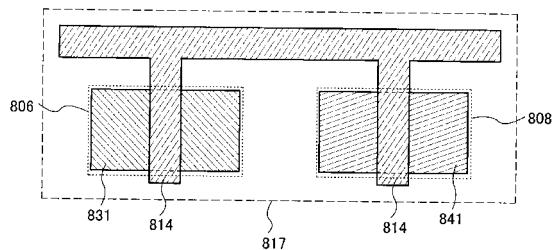

#### 【0081】

なお、ここではゲート電極 816 を導電層 812、導電層 814 の 2 層の積層構造で形成する例を示すが、ゲート電極は単層構造でも 3 層以上の積層構造でもよい。また、導電層の側面をテープ形状としてもよい。ゲート電極を導電層の積層構造とする場合、下層の導電層の幅を大きくしてもよいし、各層の側面を異なる角度のテープ形状としてもよい。

10

#### 【0082】

第1単結晶シリコン層 806 及び第2単結晶シリコン層 808 と、ゲート電極 816 との間には、ゲート絶縁層 810 を形成する。ゲート絶縁層 810 は、CVD法、スパッタリング法、ALD法(Atomic Layer Deposition)等を用いて、酸化シリコン(SiO<sub>x</sub>)、酸化窒化シリコン(SiO<sub>x</sub>Ny)(x > y > 0)、酸化ハフニウム(HfO<sub>x</sub>)、酸化アルミニウム(Al<sub>x</sub>O<sub>y</sub>)、酸化タンタル(TaxO<sub>y</sub>、x > y > 0)などの材料を用いて形成することができる。また、第1単結晶シリコン層 806 及び第2単結晶シリコン層 808 をプラズマ処理により固相酸化又は固相窒化して形成することもできる。その他、CVD法等により絶縁層を形成した後、当該絶縁層をプラズマ処理により固相酸化又は固相窒化して形成してもよい。

20

#### 【0083】

固相酸化処理若しくは固相窒化処理は、マイクロ波(代表的には 2.45GHz)等の高周波により励起されたプラズマを用いて行なうことが好ましい。具体的には、高周波を用いて励起された、電子密度が  $1 \times 10^{11} \text{ cm}^{-3}$  以上  $1 \times 10^{13} \text{ cm}^{-3}$  以下、且つ電子温度が 0.5 eV 以上 1.5 eV 以下のプラズマを利用してプラズマ処理を行うことが好ましい。これは、固相酸化処理若しくは固相窒化処理において、500 以下の温度において、緻密な絶縁層を形成すると共に実用的な反応速度を得るためである。

30

#### 【0084】

プラズマ処理により第1単結晶シリコン層 806 及び第2単結晶シリコン層 808 の表面を酸化する場合には、酸素を含む雰囲気下(例えば、酸素(O<sub>2</sub>)、オゾン(O<sub>3</sub>)、亜酸化窒素(N<sub>2</sub>O)、一酸化窒素(NO)若しくは二酸化窒素(NO<sub>2</sub>)、及び希ガス(ヘリウム(He)、ネオン(Ne)、アルゴン(Ar)、クリプトン(Kr)、キセノン(Xe)の少なくとも 1 つを含む)を含む雰囲気下、又は酸素(O<sub>2</sub>)、オゾン(O<sub>3</sub>)、亜酸化窒素(N<sub>2</sub>O)、一酸化窒素(NO)若しくは二酸化窒素(NO<sub>2</sub>)と、水素(H<sub>2</sub>)と、希ガスと、を含む雰囲気下)で行う。また、プラズマ処理により第1単結晶シリコン層 806 及び第2単結晶シリコン層 808 上に形成された絶縁層の表面を窒化する場合には、窒素を含む雰囲気下(例えば、窒素(N<sub>2</sub>)と希ガス(He、Ne、Ar、Kr、Xe の少なくとも一つを含む)を含む雰囲気下、窒素と水素と希ガスを含む雰囲気下、又は NH<sub>3</sub> と希ガスを含む雰囲気下)でプラズマ処理を行う。希ガスとしては、例えば Ar を用いることが好ましい。また、Ar と Kr を混合したガスを用いてもよい。

40

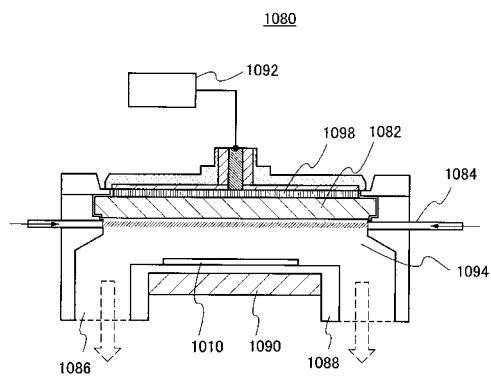

#### 【0085】

ここで、プラズマ処理を行うためのプラズマ処理装置 1080 の構成例を図 12 に示す。当該プラズマ処理装置 1080 は、支持台 1088 と、ガスを供給するためのガス供給部 1084、ガスを排気するために真空ポンプに接続する排気口 1086、アンテナ 1098、誘電体板 1082、プラズマ発生用の高周波を入力する高周波供給部 1092 を有している。被処理体 1010 は、支持台 1088 によって保持される。また、支持台 1088 に温度制御部 1090 を設けることによって、被処理体 1010 の温度を制御することも可能である。被処理体 1010 は、プラズマ処理をする基体であり、本実施の形態で

50

はベース基板である基板 800 上に絶縁層 802、804、第1単結晶シリコン層 806 及び第2単結晶シリコン層 808 が積層形成されたものに相当する。或いは、第1単結晶シリコン層 806 及び第2単結晶シリコン層 808 上に絶縁層が形成されたものに相当する。

#### 【0086】

以下、図12に示すプラズマ処理装置1080を用いて単結晶シリコン層表面に絶縁層を形成する具体例を述べる。なお、プラズマ処理とは、基板、半導体層（単結晶シリコン層）、絶縁層、導電層に対する酸化処理、窒化処理、酸化窒化処理、水素化処理などの表面改質処理を範疇に含んでいる。これらの処理は、その目的に応じて、ガス供給部1084から供給するガスを選択すれば良い。

10

#### 【0087】

まず、図12に示すプラズマ処理装置1080の処理室内を真空にする。そして、ガス供給部1084から希ガス、酸素又は窒素を含むガスを供給する。被処理体1010は室温、若しくは温度制御部1090により100以上550以下の範囲で加熱する。被処理体1010と誘電体板1082との間隔（以下、電極間隔ともいう）は、20mm以上200mm以下（好ましくは20mm以上60mm以下）程度である。

#### 【0088】

次に、高周波供給部1092からアンテナ1098に高周波を入力する。ここでは、高周波としてマイクロ波（周波数2.45GHz）を入力する。そしてマイクロ波をアンテナ1098から誘電体板1082を通して処理室内に入力することによって、プラズマ1094を生成し、当該プラズマ1094によって酸素ラジカル（OHラジカルを含む場合もある）又は窒素ラジカル（NHラジカルを含む場合もある）を生成する。このとき、プラズマ1094は、供給されたガスによって生成される。

20

#### 【0089】

マイクロ波等の高周波の入力によりプラズマ1094を生成すると、低電子温度（3eV以下、好ましくは1.5eV以下）で高電子密度（ $1 \times 10^{11} \text{ cm}^{-3}$ 以上）のプラズマを生成することができる。具体的には、電子温度が0.5eV以上1.5eV以下、且つ電子密度が $1 \times 10^{11} \text{ cm}^{-3}$ 以上 $1 \times 10^{13} \text{ cm}^{-3}$ 以下のプラズマ生成することができる。なお、本明細書では、マイクロ波の入力により生成された低電子温度で高電子密度のプラズマを高密度プラズマともいう。また、高密度プラズマを利用してプラズマ処理を行うことを高密度プラズマ処理ともいう。

30

#### 【0090】

プラズマ1094により生成された酸素ラジカル（OHラジカルを含む場合もある）又は窒素ラジカル（NHラジカルを含む場合もある）によって、被処理体1010に形成された単結晶シリコン層の表面が酸化または窒化されて絶縁層が形成される。或いは、単結晶シリコン層上に形成された絶縁層の表面又は表面近傍が酸化又は窒化される。このとき、供給するガスにアルゴンなどの希ガスを混合させると、希ガスの励起種により酸素ラジカルや窒素ラジカルを効率良く生成することができる。なお、供給ガスに希ガスを用いる場合、形成された絶縁層に希ガスが含まれる場合がある。この方法は、プラズマで励起した活性なラジカルを有効に使うことにより、500以下の低温で固相反応による酸化、窒化を行うことができる。

40

#### 【0091】

本実施の形態において、ゲート絶縁層810をプラズマ処理により形成する好適な作製方法の一例は、酸素を含む雰囲気下で第1単結晶シリコン層806及び第2単結晶シリコン層808をプラズマ処理して酸化シリコン層を形成した後、窒素を含む雰囲気下で酸化シリコン層の表面を窒化プラズマ処理して窒素プラズマ処理層を形成する。具体的には、まず酸素を含む雰囲気下でプラズマ処理を行い、第1単結晶シリコン層806及び第2単結晶シリコン層808上に3nm乃至6nmの厚さで酸化シリコン層を形成する。続けて、窒素を含む雰囲気下でプラズマ処理を行い、酸化シリコン層の表面又は表面近傍に窒素濃度の高い窒素プラズマ処理層を形成する。なお、表面近傍とは、酸化シリコン層の表面

50

から概略 0.25 nm 乃至 1.5 nm の深さをいう。例えば、酸化シリコン層を形成した後、窒素を含む雰囲気下でプラズマ処理を行うことによって、酸化シリコン層の表面から概略 1 nm の深さに窒素を 20 原子 % 乃至 50 原子 % の割合で含有した窒素プラズマ処理層を形成することができる。窒素プラズマ処理層は、プラズマ処理の条件によって、窒化シリコン又は窒化酸化シリコンで形成される。

#### 【0092】

いずれにしても、上記のようなプラズマ処理による固相酸化処理若しくは固相窒化処理を用いることで、ベース基板（ここでは基板 800）として耐熱温度が 700 以下のガラス基板を用いても、950 乃至 1050 の範囲で形成される熱酸化膜と同等な絶縁層を得ることができる。すなわち、半導体素子、特にトランジスタや不揮発性記憶素子のゲート絶縁層として機能する絶縁層として信頼性の高い絶縁層を形成することができる。10

#### 【0093】

なお、図 6 (B) では、ゲート絶縁層 810 とゲート電極 816 の側端部が揃うように加工される例を示すが、特に限定されず、ゲート電極 816 のエッチングにおいてゲート絶縁層 810 を残すように加工してもよい。

#### 【0094】

また、ゲート絶縁層 810 に高誘電率物質 (high-k 材料といわれる) を用いる場合には、ゲート電極 816 を多結晶シリコン、シリサイド、金属若しくは金属窒化物で形成する。好ましくは金属若しくは金属窒化物で形成することが望ましい。例えば、ゲート絶縁層 810 と接する導電層 812 を金属窒化物材料で形成し、その上の導電層 814 を金属材料で形成する。この組み合わせを用いることによって、ゲート絶縁層を薄膜化した場合でも空乏層が広がってしまうことを防止でき、微細化した場合にもトランジスタの駆動能力などの動作特性を損なうことを防止できる。20

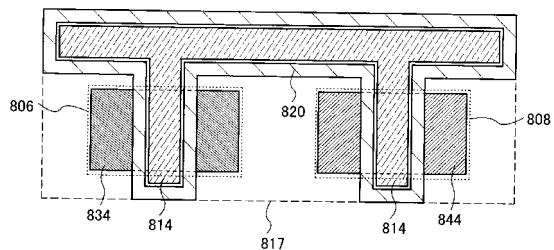

#### 【0095】

次に、ゲート電極 816 上に絶縁層 817 を形成する。そして、ゲート電極 816 をマスクとして一導電型を付与する不純物元素を添加する。なお、本実施の形態では CMOS 回路を作製するため、第 1 単結晶シリコン層 806 及び第 2 単結晶シリコン層 808 には相異なる導電型を付与する不純物元素を添加する。第 1 単結晶シリコン層 806 には、ゲート電極 816 をマスクとして自己整合的に一対の不純物領域 831 と、当該一対の不純物領域 831 の間に位置するチャネル形成領域 830 が形成される。同様に、第 2 単結晶シリコン層 808 には、ゲート電極 816 をマスクとして自己整合的に一対の不純物領域 841 と、当該一対の不純物領域 841 の間に位置するチャネル形成領域 840 が形成される。不純物領域 831 及び不純物領域 841 は、相異なる導電型の不純物元素が添加されている（図 7 (A)、(B) 参照）。30

#### 【0096】

一導電型を付与する不純物元素としては、ボロン (B)、アルミニウム (Al)、ガリウム (Ga) 等の p 型を付与する元素、リン (P)、ヒ素 (As) 等の n 型を付与する元素を用いることができる。本実施の形態では、第 1 単結晶シリコン層 806 に n 型を付与する元素、例えばリンを添加する。また、第 2 単結晶シリコン層 808 に p 型を付与する元素、例えばボロンを添加する。なお、第 1 単結晶シリコン層 806 に不純物元素を添加する際は、レジストマスク等を用いて第 2 単結晶シリコン層 808 を選択的に覆えばよい。同様に、第 2 単結晶シリコン層 808 に不純物元素を添加する際は、レジストマスク等を用いて第 1 単結晶シリコン層 806 を選択的に覆えばよい。40

#### 【0097】

絶縁層 817 は、CVD 法、スペッタリング法、ALD 法等を用いて、酸化シリコン或いは酸化窒化シリコン、又は窒化シリコン或いは窒化酸化シリコンなどの材料を用いて形成することができる。一導電型を付与する不純物元素を添加する際に、絶縁層 817 を通過させて添加する構成とすることで、単結晶シリコン層に与えるダメージを低減することができる。

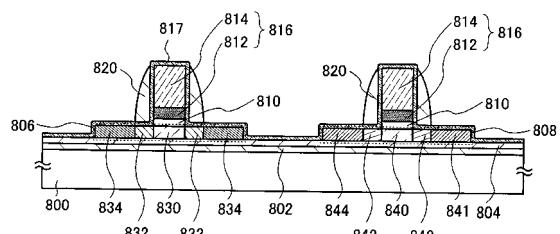

#### 【0098】

次に、ゲート電極 816 の側面にサイドウォール絶縁層 820 を形成する。そして、ゲート電極 816 及びサイドウォール絶縁層 820 をマスクとして一導電型を付与する不純物元素を添加する。なお、第1単結晶シリコン層 806 及び第2単結晶シリコン層 808 には、それぞれ先の工程（不純物領域 831 及び不純物領域 841 を形成する工程）で添加した不純物元素と同じ導電型の不純物元素を添加する。また、先の工程で添加した不純物元素よりも高い濃度で添加する（図 8（A）、（B）参照）

#### 【0099】

第1単結晶シリコン層 806 には、ゲート電極 816 及びサイドウォール絶縁層 820 をマスクとして自己整合的に一对の高濃度不純物領域 834 と、一对の低濃度不純物領域 832 が形成される。ここで形成される高濃度不純物領域 834 はソース領域又はドレイン領域として機能し、低濃度不純物領域 832 は LDD (Lightly Doped Drain) 領域として機能する。同様に、第2単結晶シリコン層 808 には、ゲート電極 816 及びサイドウォール絶縁層 820 をマスクとして自己整合的に一对の高濃度不純物領域 844 と、一对の低濃度不純物領域 842 が形成される。なお、第1単結晶シリコン層 806 に不純物元素を添加する際は、レジストマスク等を用いて第2単結晶シリコン層 808 を選択的に覆えばよい。同様に、第2単結晶シリコン層 808 に不純物元素を添加する際は、レジストマスク等を用いて第1単結晶シリコン層 806 を選択的に覆えばよい。

#### 【0100】

サイドウォール絶縁層 820 は、絶縁層 817 を介してゲート電極 816 の側面に設けられる。例えば、ゲート電極 816 を埋め込むように形成した絶縁層を、垂直方向を主体とした異方性エッチングを行うことによって、ゲート電極 816 の側面に自己整合的に形成することができる。サイドウォール絶縁層 820 は、窒化シリコン或いは窒化酸化シリコン、又は酸化シリコン或いは酸化窒化シリコンなどの材料を用いて形成することができる。なお、絶縁層 817 を酸化シリコン又は酸化窒化シリコンを用いて形成する場合、サイドウォール絶縁層 820 を窒化シリコン又は窒化酸化シリコンを用いて形成することで、絶縁層 817 をエッチングストッパーとして機能させることができる。また、絶縁層 817 を窒化シリコン又は窒化酸化シリコンを用いて形成する場合は、サイドウォール絶縁層 820 を酸化シリコン又は酸化窒化シリコンを用いて形成すればよい。このように、エッチングストッパーとして機能しうる絶縁層を設けることで、サイドウォール絶縁層を形成する際のオーバーエッチングにより単結晶シリコン層がエッチングされてしまうのを防ぐことができる。

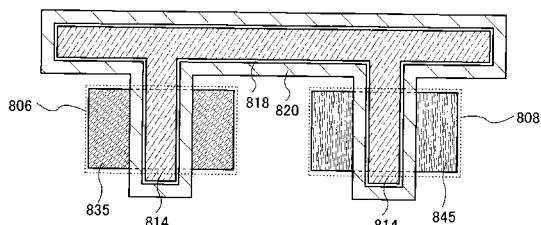

#### 【0101】

次に、絶縁層 817 の露出部をエッチングする。そして、第1単結晶シリコン層 806 及び第2単結晶シリコン層 808 の一部をシリサイド化する（図 9（A）、（B）参照）。

#### 【0102】

絶縁層 817 は、サイドウォール絶縁層 820 及びゲート電極 816 の間、サイドウォール絶縁層 820 及び第1単結晶シリコン層 806 の間、並びにサイドウォール絶縁層 820 及び第2単結晶シリコン層 808 の間に残る。よって、サイドウォール絶縁層 820 及びゲート電極 816 と重畠しない領域の第1単結晶シリコン層 806 及び第2単結晶シリコン層 808 は露出する。ここでは、第1単結晶シリコン層 806 に形成された高濃度不純物領域 834 及び第2単結晶シリコン層 808 に形成された高濃度不純物領域 844 が露出する。

#### 【0103】

シリサイド化は、単結晶シリコン層に金属を接触させて行うことができる。例えば、露出させた第1単結晶シリコン層 806 及び第2単結晶シリコン層 808 上に金属層を形成し、熱処理を行うことによってシリサイド化することができる。金属層は、スパッタリング法、蒸着法、めっき法等により、シリコンと反応してシリサイド化する材料、例えばニッケル、チタン、コバルト、白金等の金属元素や該金属元素を含む合金材料を用いて形成

10

20

30

40

50

することができる。これらの金属元素を用いた場合は、それぞれニッケルシリサイド、チタンシリサイド、コバルトシリサイド、白金シリサイドが形成される。なお、シリサイド化する領域の形状、膜厚等は、反応させる金属層の膜厚、熱処理の温度や時間等を適宜制御することで、調整することができる。図9(B)では、第1単結晶シリコン層806に形成された高濃度不純物領域834の上層及び第2単結晶シリコン層808に形成された高濃度不純物領域844の上層に、それぞれシリサイド化された領域835、領域845を有する例を示す。なお、本発明は特に限定されず、シリサイド化を行わない構成としてもよいし、単結晶シリコン層に形成された高濃度不純物領域全体をシリサイド化する構成としてもよい。また、低濃度不純物領域までシリサイド化される構成としてもよい。なお、シリサイド化後に未反応の金属が残存する場合は、ウェットエッチング法やドライエッティング法を用いて適宜除去する。

#### 【0104】

以上で、トランジスタ850及びトランジスタ860が形成される。図9(B)では、トランジスタ850としてnチャネルトランジスタが形成され、トランジスタ860としてpチャネルトランジスタが形成される。

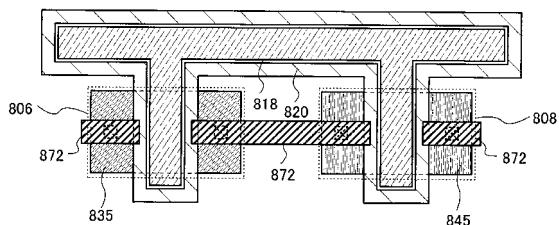

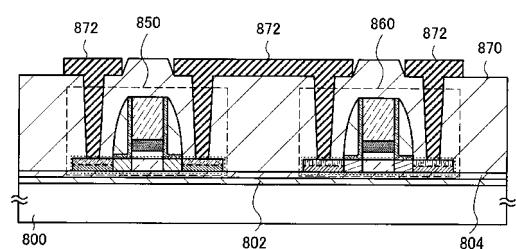

#### 【0105】

次に、トランジスタ850及びトランジスタ860上に絶縁層870を形成する。次に、絶縁層870を選択的にエッチングして、第1単結晶シリコン層806に形成された高濃度不純物領域834及び第2単結晶シリコン層808に形成された高濃度不純物領域844にそれぞれ達する開口を形成する。そして、該開口を埋め込むようにソース電極又はドレイン電極として機能する導電層872を形成する(図10(A)、(B)参照)。

#### 【0106】

絶縁層870は、CVD法やスパッタリング法、ALD法、塗布法等により、酸化シリコン、窒化シリコン、酸化窒化シリコン、窒化酸化シリコン等の酸素若しくは窒素を含む無機絶縁材料や、DLC(ダイヤモンドライクカーボン)等の炭素を含む絶縁材料、エポキシ、ポリイミド、ポリアミド、ポリビニルフェノール、ベンゾシクロブテン、アクリル等の有機絶縁材料またはシロキサン樹脂等のシロキサン材料を用いて形成する。なお、シロキサン材料とは、Si-O-Si結合を含む材料に相当する。シロキサンは、シリコン(Si)と酸素(O)との結合で骨格構造が構成される。置換基として、少なくとも水素を含む有機基(例えばアルキル基、芳香族炭化水素)が用いられる。置換基として、フルオロ基を用いることもできる。または置換基として、少なくとも水素を含む有機基と、フルオロ基とを用いてもよい。また、絶縁層870は、CVD法やスパッタリング法、ALD法を用いて絶縁層を形成した後、当該絶縁層に酸素雰囲気下又は窒素雰囲気下で高密度プラズマ処理を行うことにより形成してもよい。ここでは絶縁層870は単層構造の例を示すが、2層以上の積層構造としてもよい。また、無機絶縁層や、有機絶縁層を組み合わせて形成してもよい。例えば、トランジスタ850及びトランジスタ860上にパッシベーション層として機能できる窒化シリコン層や窒化酸化シリコン層を形成し、その上層に平坦化層として機能できるリンシリケートガラス(PSG)やボロンリンシリケートガラス(BPSG)を材料に用いた絶縁層を形成することができる。

#### 【0107】

ソース電極又はドレイン電極として機能する導電層872は、絶縁層870に形成された開口を介して、第1単結晶シリコン層806及び第2単結晶シリコン層808と電気的に接続される。また、第1単結晶シリコン層806及び第2単結晶シリコン層808は、導電層872を間に介して電気的に接続され、CMOS回路を形成する。なお、図9(B)では高濃度不純物領域の上層がシリサイド化されている例を示しており、導電層872はシリサイド化された領域835、845と電気的に接続される。よって、ソース電極又はドレイン電極として機能する導電層872と、ソース領域又はドレイン領域として機能する高濃度不純物領域834又は高濃度不純物領域844とのコンタクト抵抗を低減することができる。

#### 【0108】

10

20

30

40

50

導電層 872 は、CVD法やスパッタリング法を用いて、アルミニウム(A1)、タンゲステン(W)、チタン(Ti)、タンタル(Ta)、モリブデン(Mo)、ニッケル(Ni)、白金(Pt)、銅(Cu)、金(Au)、銀(Ag)、マンガン(Mn)、ネオジム(Nd)、炭素(C)、シリコン(Si)等の金属元素、又は当該金属元素を含む合金材料若しくは化合物材料を用いて基板全面に導電層を単層構造又は積層構造で形成した後、当該導電層を選択的にエッチングして形成することができる。アルミニウムを含む合金材料としては、例えば、アルミニウムを主成分としニッケルを含む合金材料、又は、アルミニウムを主成分とし、ニッケルと、炭素とシリコンの一方又は両方とを含む合金材料があげられる。また、タンゲステンを含む化合物材料としては、例えばタンゲステンシリサイドが挙げられる。導電層 872 は、例えば、バリア層とアルミニウムシリコン層とバリア層の積層構造、バリア層とアルミニウムシリコン層と窒化チタン層とバリア層の積層構造を採用することができる。なお、バリア層とは、チタン、チタンの窒化物、モリブデン、又はモリブデンの窒化物からなる薄膜に相当する。アルミニウムやアルミニウムシリコンは抵抗値が低く、安価であるため、ソース電極又はドレイン電極として機能する導電層を形成する材料として最適である。また、ソース電極又はドレイン電極として機能する導電層を、上層と下層にバリア層を設けた積層構造とすると、アルミニウムやアルミニウムシリコンのヒロックの発生を防止することができるため好ましい。

#### 【0109】

以上で、相異なる導電型のトランジスタが電気的に接続されたCMOS回路を形成することができる。

10

#### 【0110】

本実施の形態は、本発明に係るSOI基板を用いて大面积基板で製造プロセスを流すことができる。よって、半導体集積回路等の半導体装置を生産性良く製造することが可能となる。

#### 【0111】

なお、本実施の形態は、本明細書で示す他の実施の形態と適宜組み合わせができる。

20

#### 【0112】

##### (実施の形態3)

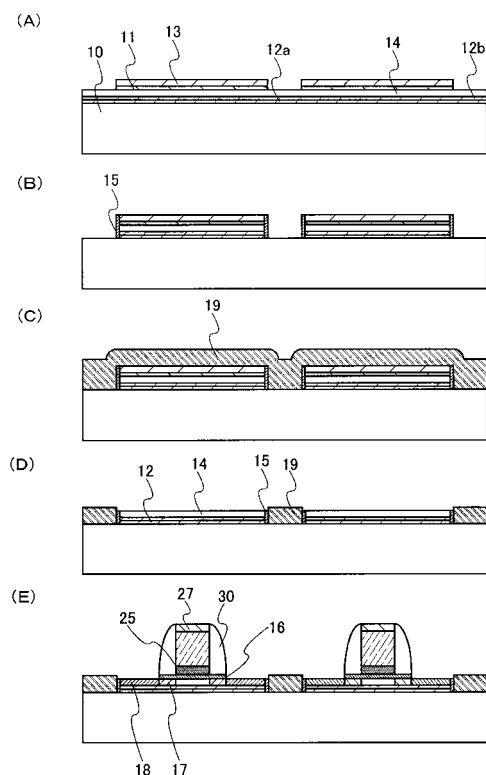

本実施の形態では、上記実施の形態1で作製されるSOI基板を用いて、上記実施の形態2と異なる構成の半導体装置を作製する一形態について説明する。具体的には、本実施の形態は、素子分離構造として半導体層(単結晶シリコン層)間に絶縁層を埋め込んだ構成の半導体装置について図18と図19を参照して説明する。

30

#### 【0113】

図18(A)において、基板10上に下地絶縁層として機能する絶縁層12a、絶縁層12b(以下、絶縁層12a、絶縁層12bを合わせて下地絶縁層12ともいう)が形成されている。絶縁層12aは基板10側に設けられたものであり、絶縁層12bは単結晶シリコン層14側に設けられたものであり、絶縁層12aと絶縁層12bが接合することにより、単結晶シリコン層14が基板10と固定されている。基板10への単結晶シリコン層14の接合は実施形態1と同様である。

40

#### 【0114】

単結晶シリコン層14上には、素子形成領域に合わせて窒化シリコン層11、酸化シリコン層13を形成する。酸化シリコン層13は、素子分離のために単結晶シリコン層14をエッチングするときのハードマスクとして用いる。窒化シリコン層11はエッチングストップである。

#### 【0115】

単結晶シリコン層14の膜厚は5nm乃至30nm、好ましくは10nm乃至25nmとすることが好ましい。単結晶シリコン層14には閾値電圧を制御するために、ボロン、アルミニウム、ガリウムなどのp型不純物を添加する。例えば、p型不純物としてボロンを $5 \times 10^{17} \text{ cm}^{-3}$ 以上 $1 \times 10^{18} \text{ cm}^{-3}$ 以下の濃度で添加されていても良い。

50

## 【0116】

図18(B)は、酸化シリコン層13をマスクとして単結晶シリコン層14、下地絶縁層12をエッティングする工程である。酸化シリコン層13、窒化シリコン層11、単結晶シリコン層14及び下地絶縁層12の露出した端面に対してプラズマ処理により窒化する。この窒化処理により、酸化シリコン層13、窒化シリコン層11、単結晶シリコン層14及び下地絶縁層12の周辺端部には窒化処理層15が形成される。また、窒化処理層15として、少なくとも単結晶シリコン層14の周辺端部には窒化シリコン層が形成される。単結晶シリコン層14の周辺端部に形成される窒化シリコン層は絶縁性であり、単結晶シリコン層14の端面でのリーク電流が流れるのを防止する効果がある。また、耐酸化作用があるので、単結晶シリコン層14と下地絶縁層12との間に、端面から酸化膜が成長してバーズピークが形成されるのを防ぐことができる。10

## 【0117】

図18(C)は、素子分離絶縁層19を堆積する工程である。素子分離絶縁層19はTEOSを原料ガスに用いて酸化シリコン層をCVD法で堆積する。素子分離絶縁層19は単結晶シリコン層14が埋め込まれるように厚く堆積する。

## 【0118】

図18(D)は窒化シリコン層11が露出するまで素子分離絶縁層19を除去する工程を示している。この除去工程は、ドライエッティングによって行うこともできるし、化学的機械研磨によって行っても良い。窒化シリコン層11はエッティングストップとなる。素子分離絶縁層19は単結晶シリコン層14の間に埋め込まれるように残存する。窒化シリコン層11はその後除去する。20

## 【0119】

図18(E)において、単結晶シリコン層14が露出した後、ゲート絶縁層16、ゲート電極25、サイドウォール絶縁層28を形成し、第1不純物領域18、第2不純物領域17を形成する。絶縁層27は窒化シリコンで形成し、ゲート電極25をエッティングするときのハードマスクとして用いる。

## 【0120】

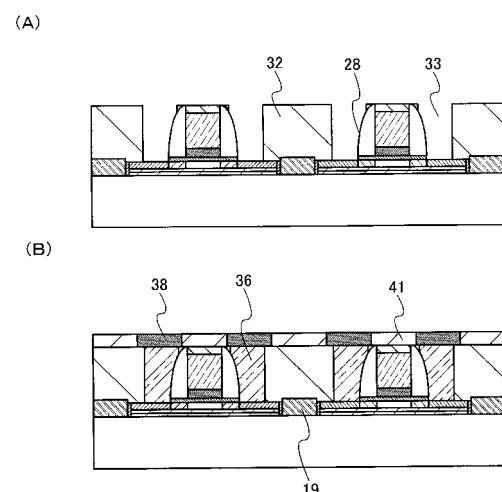

図19(A)において、層間絶縁層32を形成する。層間絶縁層32はボロンリンシリケートガラス(BPSG、Boron Phosphorus Silicon Glass)膜を形成してリフローにより平坦化させる。また、TEOS(テトラエトキシシラン)を原料ガスに用いて酸化シリコン層を形成し化学的機械研磨処理によって平坦化しても良い。平坦化処理においてゲート電極25上の絶縁層27はエッティングストップとして機能する。層間絶縁層32にはコンタクトホール33を形成する。コンタクトホール33は、サイドウォール絶縁層28を利用してセルフアラインコンタクトの構成となっている。30

## 【0121】

その後、図19(B)で示すように、六フッ化タンゲステンを用いCVD法でコンタクトプラグ36を形成する。絶縁層41を形成し、コンタクトプラグ36に合わせて開口を形成して配線38を設ける。配線38はアルミニウム若しくはアルミニウム合金で形成し、上層と下層にはバリアメタルとしてモリブデン、クロム、チタンなどの金属膜で形成する。40

## 【0122】

このようにして、単結晶シリコン層でなる電界効果型トランジスタを絶縁表面を有する基板上に作製することができる。本実施の形態によれば、実施の形態1で作製された大面積のSOI基板を用いることによって、半導体集積回路等の回路パターンを作製する際に、大面積基板を用いて一度に製造プロセスを流すことができ、生産性を向上させることができる。また、複数の単結晶シリコン薄膜によりSOI基板を製造するが、個々の単結晶シリコン薄膜の大きさを露光装置の1ショットサイズの整数倍程度とすることで、半導体集積回路等の半導体装置の製造において歩留まりの向上を図ることができる。

## 【0123】

なお、本実施の形態は、本明細書で示す他の実施の形態と適宜組み合わせができる。

#### 【0124】

##### (実施の形態4)

本実施の形態では、本発明に係るS O I 基板を用いて作製した半導体装置の一例として、C P U に適用する例に関して、図面を用いて以下に説明する。

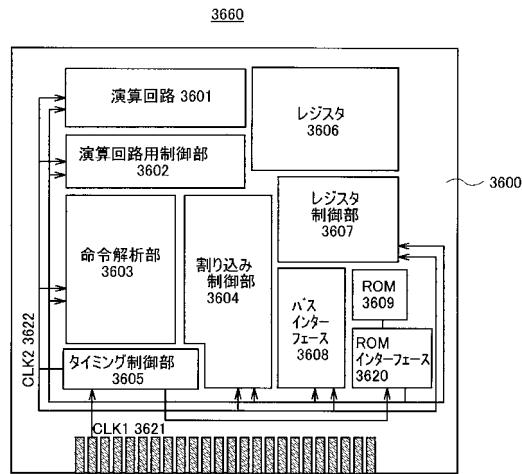

#### 【0125】

図13に示すC P U 3 6 6 0 は、基板3 6 0 0 上に演算回路 (A L U : A r i t h m e t i c l o g i c u n i t ) 3 6 0 1 、演算回路用制御回路部 (A L U C o n t r o l l e r ) 3 6 0 2 、命令解析部 (I n s t r u c t i o n D e c o d e r ) 3 6 0 3 、割り込み制御部 (I n t e r r u p t C o n t r o l l e r ) 3 6 0 4 、タイミング制御部 (T i m i n g C o n t r o l l e r ) 3 6 0 5 、レジスタ (R e g i s t e r ) 3 6 0 6 、レジスタ制御部 (R e g i s t e r C o n t r o l l e r ) 3 6 0 7 、バスインターフェース (B u s I / F ) 3 6 0 8 、書き換え可能なR O M 3 6 0 9 、R O Mインターフェース (R O M I / F ) 3 6 2 0 を主に有している。また、R O M 3 6 0 9 及びR O Mインターフェース 3 6 2 0 は、別チップに設けても良い。これらC P U 3 6 6 0 を構成する様々な回路は、上記実施の形態2、3に示されるトランジスタ、当該トランジスタを組み合わせたC M O S回路、n M O S回路、p M O S回路等を用いて構成することが可能である。

10

#### 【0126】

図13に示すC P U 3 6 6 0 は、その構成を簡略化して示した一例にすぎず、実際のC P U はその用途によって多種多様な構成を有している。したがって、本発明を適用するC P U の構成は、図13に示すものに限定されるものではない。

20

#### 【0127】

バスインターフェース 3 6 0 8 を介してC P U 3 6 6 0 に入力された命令は、命令解析部 3 6 0 3 に入力され、デコードされた後、演算回路用制御回路部 3 6 0 2 、割り込み制御部 3 6 0 4 、レジスタ制御部 3 6 0 7 、タイミング制御部 3 6 0 5 に入力される。

#### 【0128】

演算回路用制御回路部 3 6 0 2 、割り込み制御部 3 6 0 4 、レジスタ制御部 3 6 0 7 、タイミング制御部 3 6 0 5 は、デコードされた命令に基づき、各種制御を行う。具体的に演算回路用制御回路部 3 6 0 2 は、演算回路 3 6 0 1 の駆動を制御するための信号を生成する。また、割り込み制御部 3 6 0 4 は、C P U 3 6 6 0 のプログラム実行中に、外部の入出力装置や、周辺回路からの割り込み要求を、その優先度やマスク状態から判断し、処理する。レジスタ制御部 3 6 0 7 は、レジスタ 3 6 0 6 のアドレスを生成し、C P U の状態に応じてレジスタ 3 6 0 6 の読み出しや書き込みを行う。

30

#### 【0129】

またタイミング制御部 3 6 0 5 は、演算回路 3 6 0 1 、演算回路用制御回路部 3 6 0 2 、命令解析部 3 6 0 3 、割り込み制御部 3 6 0 4 、レジスタ制御部 3 6 0 7 の駆動のタイミングを制御する信号を生成する。例えばタイミング制御部 3 6 0 5 は、基準クロック信号 C L K 1 ( 3 6 2 1 ) を元に、内部クロック信号 C L K 2 ( 3 6 2 2 ) を生成する内部クロック生成部を備えており、クロック信号 C L K 2 を上記各種回路に供給する。

40

#### 【0130】

なお、本実施の形態では、半導体装置をC P U に適用する例を説明したが、特に限定されない。例えば、上記実施の形態で作製される半導体装置は、有機発光素子、無機発光素子、又は液晶表示素子等を備えた表示装置の画素部及び駆動回路部等に適用することができる。また、その他、本発明を適用して、デジタルカメラなどのカメラ、カーオーディオなどの音響再生装置、ノート型パーソナルコンピュータ、ゲーム機器、携帯情報端末（携帯電話機、携帯型ゲーム機等）、家庭用ゲーム機などの記録媒体を備えた画像再生装置などを作製することも可能である。

#### 【0131】

本実施の形態に係る半導体装置は、本発明に係るS O I 基板を用いて作製する。よって、生産性良く半導体装置を製造することができるため、コスト削減を図ることができる。

#### 【 0 1 3 2 】

なお、本実施の形態は、本明細書で示す他の実施の形態と適宜組み合わせができる。

#### 【 0 1 3 3 】

##### ( 実施の形態 5 )

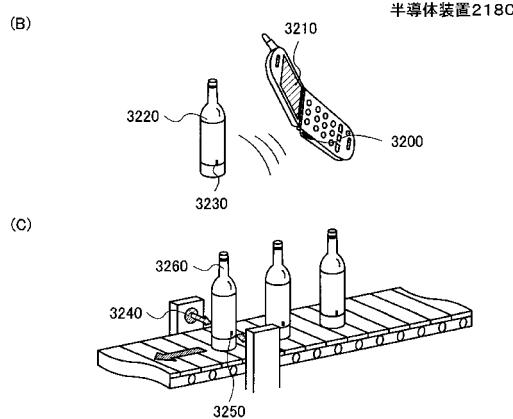

本実施の形態では、本発明に係るS O I 基板を用いて作製した半導体装置の使用形態の一例について説明する。具体的には、非接触でデータの入出力が可能である半導体装置の適用例に関して、図面を用いて以下に説明する。非接触でデータの入出力が可能である半導体装置は利用の形態によって、R F I D タグ、I D タグ、I C タグ、I C チップ、R F タグ、無線タグ、電子タグまたは無線チップとも呼ばれる。10

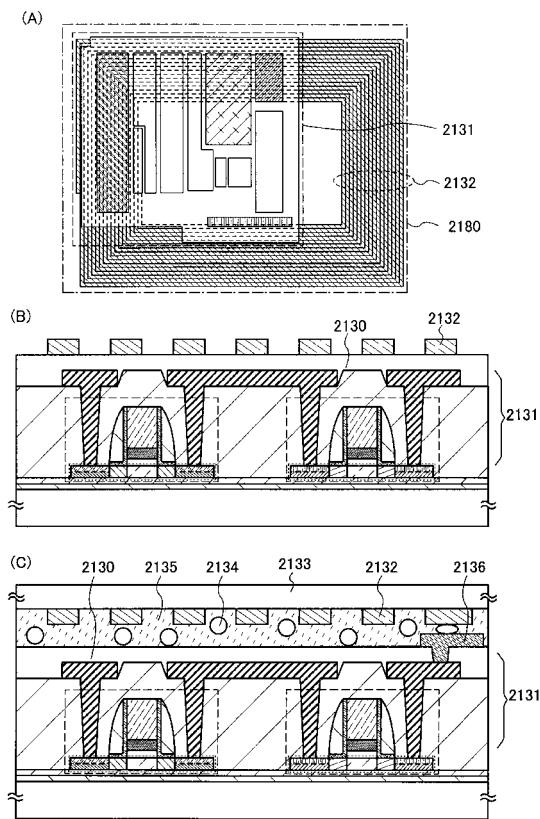

#### 【 0 1 3 4 】

本実施の形態で示す半導体装置の上面構造の一例について、図14(A)を参照して説明する。図14に示す半導体装置2180は、メモリ部やロジック部を構成する複数のトランジスタ等の素子が設けられた集積回路2131と、アンテナとして機能する導電層2132を含んでいる。アンテナとして機能する導電層2132は、集積回路2131に電気的に接続されている。集積回路2131には、上記実施の形態2、3で示したトランジスタを適用することができる。

#### 【 0 1 3 5 】

また、図14(B)、(C)に図14(A)の断面の模式図を示す。アンテナとして機能する導電層2132は、メモリ部及びロジック部を構成する素子の上方に設ければよく、例えば、上記実施の形態で示したトランジスタで構成された集積回路2131上方に、絶縁層2130を介してアンテナとして機能する導電層2132を設けることができる(図14(B)参照)。他にも、アンテナとして機能する導電層2132を基板2133に別に設けた後、当該基板2133及び集積回路2131を、導電層2132が間に位置するように貼り合わせて設けることができる(図14(C)参照)。図14(C)では、絶縁層2130上に設けられた導電層2136とアンテナとして機能する導電層2132とが、接着性を有する樹脂2135中に含まれる導電性粒子2134を介して電気的に接続されている例を示す。20

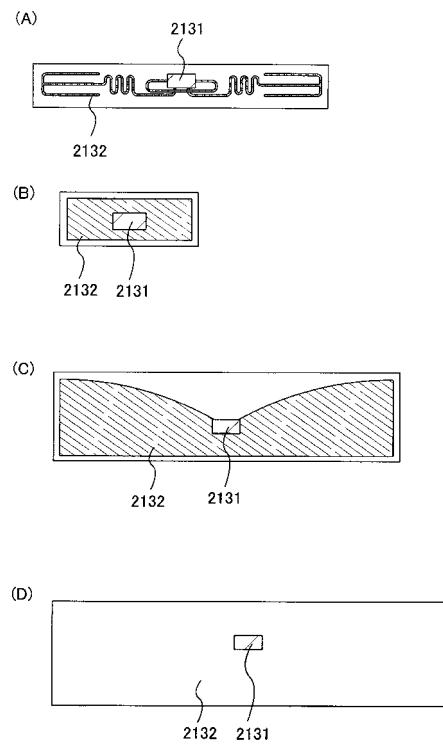

#### 【 0 1 3 6 】

なお、本実施の形態では、アンテナとして機能する導電層2132をコイル状に設け、電磁誘導方式または電磁結合方式を適用する例を示すが、本発明の半導体装置はこれに限られずマイクロ波方式を適用することも可能である。マイクロ波方式の場合は、用いる電磁波の波長によりアンテナとして機能する導電層2132の形状を適宜決めればよい。

#### 【 0 1 3 7 】

例えば、半導体装置2180における信号の伝送方式として、マイクロ波方式(例えば、U H F 帯(860 M H z 帯乃至960 M H z 帯)、2.45 G H z 帯等)を適用する場合には、信号の伝送に用いる電磁波の波長を考慮してアンテナとして機能する導電層の長さ等の形状を適宜設定すればよい。例えば、アンテナとして機能する導電層を線状(例えば、ダイポールアンテナ(図15(A)参照))、平坦な形状(例えば、パッチアンテナ(図15(B)参照)またはリボン型の形状(図15(C)、(D)参照))等に形成することができる。また、アンテナとして機能する導電層2132の形状は直線状に限られず、電磁波の波長を考慮して曲線状や蛇行形状またはこれらを組み合わせた形状で設けてもよい。40

#### 【 0 1 3 8 】

アンテナとして機能する導電層2132は、C V D 法、スパッタ法、スクリーン印刷やグラビア印刷等の印刷法、液滴吐出法、ディスペンサ法、メッキ法等を用いて、導電性材料により形成する。導電性材料は、アルミニウム(A l)、チタン(T i)、銀(A g)、銅(C u)、金(A u)、白金(P t)ニッケル(N i)、パラジウム(P d)、タン

50

30

30

50

タル( Ta )、モリブデン( Mo )等の金属元素、又は当該金属元素を含む合金材料若しくは化合物材料で、単層構造又は積層構造で形成する。

#### 【 0 1 3 9 】

例えば、スクリーン印刷法を用いてアンテナとして機能する導電層 2132 を形成する場合には、粒径が数 nm から数十  $\mu\text{m}$  の導電体粒子を有機樹脂に分散させた導電性のペーストを選択的に印刷することによって設けることができる。導電体粒子としては、銀( Ag )、金( Au )、銅( Cu )、ニッケル( Ni )、白金( Pt )、パラジウム( Pd )、タンタル( Ta )、モリブデン( Mo )およびチタン( Ti )等のいずれか一つ以上の金属粒子やハロゲン化銀の微粒子、または分散性ナノ粒子を用いることができる。また、導電性ペーストに含まれる有機樹脂は、金属粒子のバインダー、溶媒、分散剤および被覆材として機能する有機樹脂から選ばれた一つまたは複数を用いることができる。代表的には、エポキシ樹脂、シリコン樹脂等の有機樹脂が挙げられる。また、導電層の形成の際は、導電性のペーストを押し出した後に焼成することが好ましい。例えば、導電性のペーストの材料として、銀を主成分とする微粒子( 例えは粒径 1 nm 以上 100 nm 以下の微粒子 )を用いる場合、150 乃至 300 の温度範囲で焼成することにより硬化させて導電層を形成することができる。また、はんだや鉛フリーのはんだを主成分とする微粒子を用いてもよく、この場合は粒径 20  $\mu\text{m}$  以下の微粒子を用いることが好ましい。はんだや鉛フリーはんだは、低コストであるといった利点を有している。10

#### 【 0 1 4 0 】

本実施の形態に係る半導体装置を、本発明を適用して SOI 基板を用いて作製することで、生産性が向上するため、製造コストを抑えることができる。また、非接触でデータの入出力が可能で、且つ小型な半導体装置の製造に適用することもできる。20

#### 【 0 1 4 1 】

次に、本実施の形態に係る半導体装置の動作例について説明する。

#### 【 0 1 4 2 】

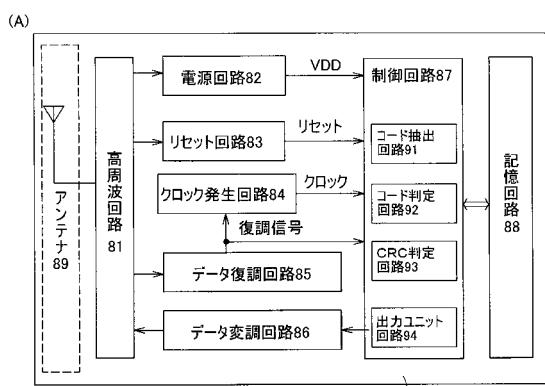

半導体装置 2180 は、非接触でデータを交信する機能を有し、高周波回路 81 、電源回路 82 、リセット回路 83 、クロック発生回路 84 、データ復調回路 85 、データ変調回路 86 、他の回路の制御を行う制御回路 87 、記憶回路 88 およびアンテナ 89 を有している( 図 16 ( A ) 参照 )。高周波回路 81 はアンテナ 89 より信号を受信して、データ変調回路 86 より受信した信号をアンテナ 89 から出力する回路である。電源回路 82 は受信信号から電源電位を生成する回路である。リセット回路 83 はリセット信号を生成する回路である。クロック発生回路 84 はアンテナ 89 から入力された受信信号を基に各種クロック信号を生成する回路である。データ復調回路 85 は受信信号を復調して制御回路 87 に出力する回路である。データ変調回路 86 は制御回路 87 から受信した信号を変調する回路である。また、制御回路 87 としては、例えはコード抽出回路 91 、コード判定回路 92 、CRC 判定回路 93 および出力ユニット回路 94 が設けられている。なお、コード抽出回路 91 は制御回路 87 に送られてきた命令に含まれる複数のコードをそれぞれ抽出する回路であり、コード判定回路 92 は抽出されたコードとリファレンスに相当するコードとを比較して命令の内容を判定する回路であり、CRC 判定回路 93 は判定されたコードに基づいて送信エラー等の有無を検出する回路である。図 16 ( A ) では、制御回路 87 の他に、アナログ回路である高周波回路 81 、電源回路 82 を含んでいる。3040

#### 【 0 1 4 3 】

次に、上述した半導体装置の動作の一例について説明する。まず、アンテナ 89 により無線信号が受信される。無線信号は高周波回路 81 を介して電源回路 82 に送られ、高電源電位( 以下、VDD と記す )が生成される。VDD は半導体装置 2180 が有する各回路に供給される。また、高周波回路 81 を介してデータ復調回路 85 に送られた信号は復調される( 以下、復調信号という )。さらに、高周波回路 81 を介してリセット回路 83 およびクロック発生回路 84 を通った信号及び復調信号は制御回路 87 に送られる。制御回路 87 に送られた信号は、コード抽出回路 91 、コード判定回路 92 および CRC 判定回路 93 等によって解析される。そして、解析された信号にしたがって、記憶回路 88 内50

に記憶されている半導体装置の情報が出力される。出力された半導体装置の情報は出力ユニット回路 94 を通って符号化される。さらに、符号化された半導体装置 2180 の情報はデータ変調回路 86 を通って、アンテナ 89 により無線信号に載せて送信される。なお、半導体装置 2180 を構成する複数の回路においては、低電源電位（以下、VSS という）は共通であり、VSS は GND とすることができます。

#### 【0144】

このように、通信手段（例えばリーダ／ライタ、又はリーダ或いはライタいずれかの機能を有する手段）から半導体装置 2180 に信号を送り、当該半導体装置 2180 から送られてきた信号をリーダ／ライタで受信することによって、半導体装置のデータを読み取ることが可能となる。

10

#### 【0145】

また、半導体装置 2180 は、各回路への電源電圧の供給を電源（バッテリー）を搭載せず電磁波により行うタイプとしてもよいし、電源（バッテリー）を搭載して電磁波と電源（バッテリー）により各回路に電源電圧を供給するタイプとしてもよい。

#### 【0146】

次に、非接触でデータの入出力が可能な半導体装置の使用形態の一例について説明する。表示部 3210 を含む携帯端末の側面には、通信手段 3200 が設けられ、品物 3220 の側面には半導体装置 3230 が設けられる（図 16（B）参照）。なお、通信手段 3200 は、例えばリーダ／ライタのように信号を読み取る機能及び信号を送信する機能を備えるもの、又は信号を読み取る機能或いは信号を送信するいずれかの機能のみを備えるものである。品物 3220 が含む半導体装置 3230 に通信手段 3200 をかざすと、表示部 3210 に品物の原材料や原産地、生産工程ごとの検査結果や流通過程の履歴等、更に商品の説明等の商品に関する情報が表示される。また、商品 3260 をベルトコンベアにより搬送する際に通信手段 3240 と、商品 3260 に設けられた半導体装置 3250 を用いて、該商品 3260 の検品を行うことができる（図 16（C）参照）。半導体装置 3230、半導体装置 3250 としては、上述した半導体装置 2180 を適用することができる。このように、システムに本発明に係る半導体装置を活用することで、情報の取得を簡単に行うことができ、高機能化と高付加価値化を実現する。また、半導体装置の製造における製造コストの削減を図ることができるため、商品の検品等のシステムも低コストで行うことも可能となる。

20

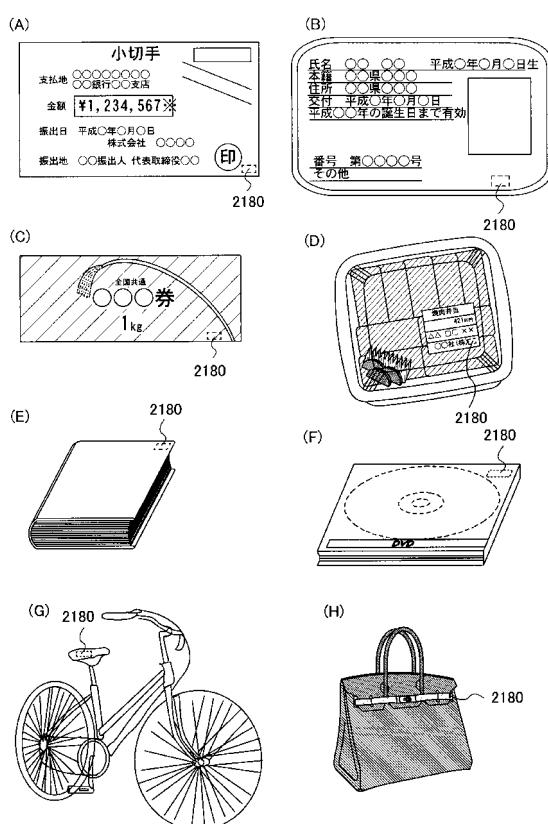

#### 【0147】

なお、上述した以外にも本発明の半導体装置の用途は広範にわたり、非接触で対象物の履歴等の情報を明確にし、生産・管理等に役立てる商品であればどのようなものにも適用することができる。例えば、紙幣、硬貨、有価証券類、証書類、無記名債券類、包装用容器類、書籍類、記録媒体、身の回り品、乗物類、食品類、衣類、保健用品類、生活用品類、薬品類及び電子機器等に設けて使用することができる。これらの例に関して図 17 を用いて説明する。

30

#### 【0148】

紙幣、硬貨とは、市場に流通する金銭であり、特定の地域で貨幣と同じように通用するものの（金券）、記念コイン等を含む。有価証券類とは、小切手、証券、約束手形等を指す（図 17（A）参照）。証書類とは、運転免許証、住民票等を指す（図 17（B）参照）。無記名債券類とは、切手、おこめ券、各種ギフト券等を指す（図 17（C）参照）。包装用容器類とは、お弁当等の包装紙、ペットボトル等を指す（図 17（D）参照）。書籍類とは、書物、本等を指す（図 17（E）参照）。記録媒体とは、DVD ソフト、ビデオテープ等を指す（図 17（F）参照）。乗物類とは、自転車等の車両、船舶等を指す（図 17（G）参照）。身の回り品とは、鞄、眼鏡等を指す（図 17（H））。食品類とは、食料品、飲料等を指す。衣類とは、衣服、履物等を指す。保健用品類とは、医療器具、健康器具等を指す。生活用品類とは、家具、照明器具等を指す。薬品類とは、医薬品、農薬等を指す。電子機器とは、液晶表示装置、EL 表示装置、テレビジョン装置（テレビ受像機、薄型テレビ受像機）、携帯電話機等を指す。

40

50

## 【0149】

紙幣、硬貨、有価証券類、証書類、無記名債券類等に半導体装置2180を設けることにより、偽造を防止することができる。また、包装用容器類、書籍類、記録媒体等、身の回り品、食品類、生活用品類、電子機器等に半導体装置2180を設けることにより、検品システムやレンタル店のシステムなどの効率化を図ることができる。乗物類、保健用品類、薬品類等に半導体装置2180を設けることにより、偽造や盗難を防止することができる。また、薬品類ならば、薬の服用の間違いを防止することができる。半導体装置2180の設け方としては、物品の表面に貼る、或いは物品に埋め込んで設ける。例えば、本の場合は紙に埋め込めばよく、有機樹脂からなるパッケージであれば有機樹脂に埋め込めばよい。

10

## 【0150】

このように、包装用容器類、記録媒体、身の回り品、食品類、衣類、生活用品類、電子機器等に半導体装置を設けることにより、検品システムやレンタル店のシステムなどの効率化を図ることができる。また乗物類に半導体装置を設けることにより、偽造や盗難を防止することができる。また、動物等の生き物に埋め込むことによって、個々の生き物の識別を容易に行うことができる。例えば、家畜等の生き物にセンサーを備えた半導体装置を埋め込む又は取り付けることによって、生まれた年や性別または種類等はもちろん現在の体温等の健康状態を容易に管理することが可能となる。

## 【0151】

なお、本実施の形態は、上記実施の形態と自由に組み合わせて行うことができる。

20

## 【図面の簡単な説明】

## 【0152】

- 【図1】本発明に係るSOI基板の構成の例を示す斜視図。

- 【図2】本発明に係るSOI基板の作製方法の一例を示す図。

- 【図3】本発明に係るSOI基板の作製方法の一例を示す図。

- 【図4】本発明に係るSOI基板の作製方法の一例を示す斜視図。

- 【図5】本発明に係るSOI基板の作製方法の一例を示す斜視図。

- 【図6】本発明に係る半導体装置の作製方法の一例を示す図。

- 【図7】本発明に係る半導体装置の作製方法の一例を示す図。

- 【図8】本発明に係る半導体装置の作製方法の一例を示す図。

- 【図9】本発明に係る半導体装置の作製方法の一例を示す図。

- 【図10】本発明に係る半導体装置の作製方法の一例を示す図。

- 【図11】本発明に係るSOI基板の構成の例を示す斜視図。

- 【図12】プラズマ処理装置の構成の例を示す図。

- 【図13】本発明に係る半導体装置の一例を示すブロック図。

- 【図14】本発明に係る半導体装置の一例を示す上面図及び断面図。

- 【図15】本発明に係る半導体装置に適用できるアンテナを説明する図。

- 【図16】本発明に係る半導体装置の一例を示すブロック図及び使用形態の例を示す図。

- 【図17】本発明に係る半導体装置の適用例を示す図。

- 【図18】本発明に係る半導体装置の作製方法の一例を示す図。

- 【図19】本発明に係る半導体装置の作製方法の一例を示す図。

30

## 【符号の説明】

## 【0153】

- 100 SOI基板

- 101 単結晶シリコン基板

- 102 単結晶シリコン基板

- 104 水素イオン

- 106 脆化層

- 108 単結晶シリコン層

- 110 単結晶シリコン薄膜

40

50

1 2 0 絶縁層

1 3 0 積層体

1 5 0 基板

【図1】

【図2】

(B)

【図3】

【図4】

【図5】

【図6】

【図7】

(A)

(B)

【図8】

(A)

(B)

【図9】

(A)

(B)

【図10】

(A)

(B)

【図11】

【図13】

【図12】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

---

フロントページの続き

(51)Int.Cl. F I

H 01 L 21/8234 (2006.01) H 01 L 29/78 6 2 7 D

H 01 L 27/06 (2006.01) H 01 L 29/78 6 2 6 C

H 01 L 21/336 (2006.01)

H 01 L 29/786 (2006.01)

(56)参考文献 特開2006-032435 (JP, A)

特開2003-324188 (JP, A)

特開昭64-061943 (JP, A)

特開平11-045862 (JP, A)

特開平11-163363 (JP, A)

特開2005-228762 (JP, A)

特表2006-518116 (JP, A)

特開2002-198328 (JP, A)

(58)調査した分野(Int.Cl., DB名)

H 01 L 27 / 12

H 01 L 21 / 02