(19)

Bundesrepublik Deutschland

Deutsches Patent- und Markenamt

(10) DE 697 31 066 T2 2005.10.06

(12)

## Übersetzung der europäischen Patentschrift

(97) EP 0 855 653 B1

(21) Deutsches Aktenzeichen: 697 31 066.3

(96) Europäisches Aktenzeichen: 97 410 009.1

(96) Europäischer Anmeldetag: 23.01.1997

(97) Erstveröffentlichung durch das EPA: 29.07.1998

(97) Veröffentlichungstag

der Patenterteilung beim EPA: 06.10.2004

(47) Veröffentlichungstag im Patentblatt: 06.10.2005

(51) Int Cl.<sup>7</sup>: G06F 13/42

G06F 13/16

(73) Patentinhaber:

Hewlett-Packard Development Co., L.P., Houston,

Tex., US

(84) Benannte Vertragsstaaten:

DE, FR, GB

(74) Vertreter:

Schoppe, Zimmermann, Stöckeler & Zinkler, 82049

Pullach

(72) Erfinder:

Thoulon, Pierre-Yves, 38000 Grenoble, FR

(54) Bezeichnung: Speichersteuerungsvorrichtung mit programmierbarer Impulsverzögerung

Anmerkung: Innerhalb von neun Monaten nach der Bekanntmachung des Hinweises auf die Erteilung des europäischen Patents kann jedermann beim Europäischen Patentamt gegen das erteilte europäische Patent Einspruch einlegen. Der Einspruch ist schriftlich einzureichen und zu begründen. Er gilt erst als eingelebt, wenn die Einspruchsgebühr entrichtet worden ist (Art. 99 (1) Europäisches Patentübereinkommen).

Die Übersetzung ist gemäß Artikel II § 3 Abs. 1 IntPatÜG 1991 vom Patentinhaber eingereicht worden. Sie wurde vom Deutschen Patent- und Markenamt inhaltlich nicht geprüft.

**Beschreibung****Gebiet der Erfindung**

**[0001]** Die vorliegende Erfindung bezieht sich auf eine Speichersteuerung mit einer programmierbaren Strobe-Verzögerung. Sie bezieht sich ferner auf ein Verfahren zum Programmieren einer solchen Speichersteuerung und auf ein Verfahren zum Verbessern der Zuverlässigkeit des Datenlesens in einer Speichersteuerung.

**Hintergrund der Erfindung**

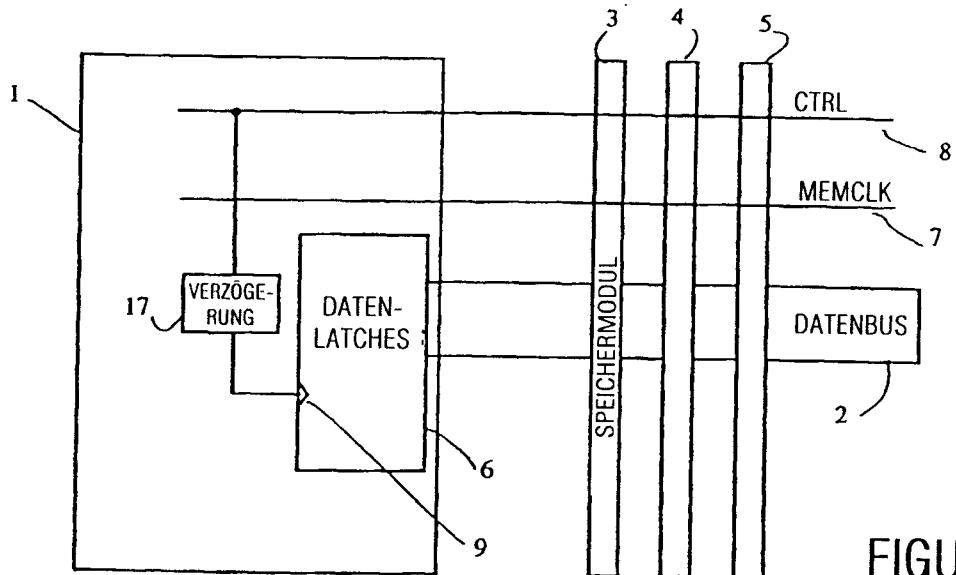

**[0002]** Die Erfindung adressiert das Problem des Lesens von Daten aus Speichern. [Fig. 1](#) der beiliegenden Zeichnungen zeigt eine diagrammatische Ansicht einer herkömmlichen Speichersteuerung **1** zusammen mit ihrem zugeordneten Datenbus **2** und verschiedenen Speichermodulen **3**, **4** und **5**. Die Speichersteuerung weist unter anderem eine Reihe **6** aus Datenlatches auf, die mit dem Datenbus **2** verbunden sind. Ein Speichertakt signal MEMCLK liegt auf der Leitung **7** in der Speichersteuerung **1** und in den unterschiedlichen Speichermodulen vor. Die Speichersteuerung **1** kann auf der Leitung **8** ein Steuerungssignal CTRL zum Lesen von Daten aus den unterschiedlichen Speichermodulen übertragen, wobei sich die Zeitgebung dieses Signals auf das Takt signal MEMCLK bezieht. Daten, die auf dem Speicherbus vorliegen, können in die Datenlatches **6** zwischengespeichert werden, wenn ein Eingang **9** der Latches durch ein Strobe-Signal freigegeben wird. Die Speicheradress-Steuerungsleitungen und die Speicherschreib-Steuerungsleitungen sind in [Fig. 1](#) nicht dargestellt.

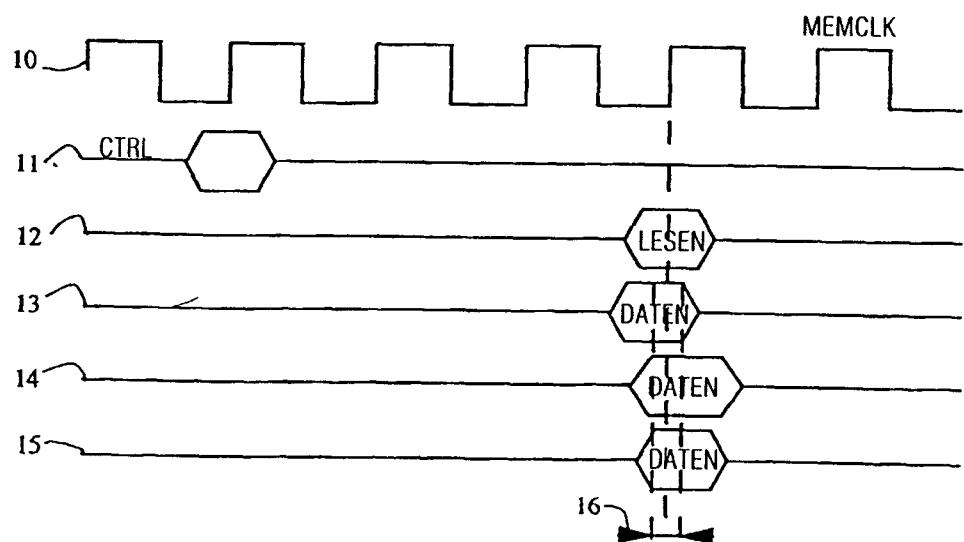

**[0003]** [Fig. 2](#) ist ein Zeitgebungsdiagramm von unterschiedlichen Signalen in der Vorrichtung aus [Fig. 1](#). In [Fig. 2](#), **10** ist das Speichertakt-MEM CLK-Signal auf Leitung **7**. Wenn Daten aus den Speichermodulen **3**, **4**, **5** gelesen werden sollen, wird ein Lesesignal CTRL **11** auf der Leitung **8** übertragen. Eine bestimmte Anzahl von Speichertaktzyklen später – z. B. drei in dem Fall von [Fig. 2](#) – wird der Eingang **9** der Datenlatches **6** in der Speichersteuerung zum Zwischenspeichern der Daten freigegeben, die von den Speichermodulen **3**, **4**, **5** kommen, die auf dem Datenbus **2** vorliegen. Die Referenz **12** identifiziert das Strobe-Signal zum Freigeben der Datenlatches **6**, wohingegen **13**, **14** und **15** die jeweiligen Daten identifizieren, die auf dem Datenbus **2** durch die unterschiedlichen Speichermodule **3**, **4**, **5** gesendet werden. Die Referenz **16** identifiziert das Datenfenster, d. h. die Zeitperiode, während der die Daten aus den Speichermodulen **3**, **4** und **5** gültig gelesen werden können.

**[0004]** Bei dem System aus [Fig. 1](#) wird die Verzögerung zwischen dem Lesesteuerungssignal **11** und

dem Strobe-Signal, das die Datenlatches an ihrem Eingang **9** freigibt, durch Hardware eingestellt, wie in [Fig. 1](#) durch den Block **17** zwischen der CTRL-Leitung **8** und dem Eingang **9** gezeigt ist.

**[0005]** Es wurde ferner vorgeschlagen, Daten in die Latches **6** zu jedem Taktzyklus zu lesen, wobei das Strobe-Signal zu einer geeigneten Zeit in jedem Taktzyklus erzeugt wird, um ein ordnungsgemäßes Lesen des Datenbusses sicherzustellen. Die Inhalte der Datenlatches werden jedoch nur eine vorbestimmte Anzahl von MEMCLK-Taktsignalflanken nach der Aktivierung des CTRL-Signals als gültig erachtet, wie durch eine geeignete Schaltungsanordnung gezählt wird. Bei diesem Lösungsansatz ist das Strobe-Signal ein Takt signal, das durch eine verzögerte Version des Takt signals MEMCLK gebildet wird, wobei die Verzögerung zwischen diesen zwei Takten z. B. durch einen leitfähigen Weg einer gegebenen Länge an der Speichersteuerungsschaltungsplatine eingestellt wird, zwischen zwei Stiften der Speichersteuerung.

**[0006]** Die oben beschriebenen Anordnungen leiden unter verschiedenen Nachteilen. Erstens adressieren sie nicht das Problem der Wirkungen von Konfigurationsänderungen in den Speichermodulen und funktionieren daher nicht für hochbelastete und/oder Speicher mit sehr hoher Geschwindigkeit. Zweitens ist die Berechnung der Strobe-Signalverzögerung eine schwierige Aufgabe und umfasst zahlreiche Untersuchungen zum Bestimmen eines korrekten statistischen Werts der Verzögerung.

**Zusammenfassung der Erfindung**

**[0007]** Die vorliegende Erfindung adressiert das Problem des Datenlesens, das bei hochbelasteten oder Hochgeschwindigkeits-Speicherkonfigurationen angetroffen wird. Dieses Problem entsteht, wenn der Speicherbus hochbelastet ist, z. B. wenn vier Speichermodule oder mehr auf demselben Speicherbus vorliegen; es entsteht ferner bei hoher Geschwindigkeit, z. B. 100 MHz oder mehr für den Speichertakt, für synchrone Speichersysteme. In diesem Fall kann die Übertragungszeitdifferenz zwischen den Speichermodulen nicht vernachlässigt werden: Das Datenfenster **16** (siehe [Fig. 1](#)) zum Lesen der Daten kann relativ klein werden, und sogar zu klein zum Sicherstellen eines korrekten Lesens der Daten bei allen möglichen Konfigurationen.

**[0008]** Tatsächlich können die Daten aus jedem Speichermodul für eine Dauer gelesen werden, die üblicherweise um 4 oder 5 ns für eine Taktfrequenz von 125 MHz liegt, und das Datenfenster **16** kann durch verschiedene Versetzungen in dem System reduziert werden.

**[0009]** Ferner adressiert die Erfindung das Problem,

das aus der Tatsache entsteht, dass die Position und die Dauer des Datenfensters **6** von der tatsächlichen Last auf dem Speicherbus **2** abhängen kann, der selbst von der tatsächlichen Konfiguration der Speichermodule abhängt. Diese Konfiguration ist nicht fest und kann zu jeder Zeit gemäß den Wünschen des Benutzers variieren. Diese Probleme machen es sehr schwierig, eine Speichersteuerung zu entwerfen, die bei voller Geschwindigkeit laufen kann und zuverlässig Daten zwischenspeichern kann, unabhängig von der Speicherkonfiguration.

**[0010]** Die vorliegende Erfindung schafft eine Lösung für das Problem des Bereitstellens einer Speichersteuerung, die bei voller Geschwindigkeit zuverlässig bei jeder Speicherkonfiguration laufen kann, unabhängig von der Last auf dem Speicherbus und der tatsächlichen Konfiguration der Speicherung, und sogar für sehr hohe Geschwindigkeiten.

**[0011]** Die EP-A-379772 beschreibt ein System zum Bereitstellen einer asynchronen Kommunikation zwischen zumindest einer zentralen Verarbeitungseinheit und zumindest einer zugeordneten Speicherseinheit mit speziell programmierten Zeitgebungssignalen, um Daten zwischen denselben zwischenspeichern, auszuwählen und zu übermitteln.

**[0012]** Die Offenbarung WO-A-98/15893 ist ein bekanntes Dokument gemäß Art. 54 (3) EPC.

**[0013]** Gemäß einem Aspekt der Erfindung wird ein System geschaffen, das zumindest ein Speichermodul und eine Speichersteuerung aufweist, wobei die Speichersteuerung folgende Merkmale aufweist:

- eine Taktleitung für ein Taktsignal;

- eine Datenempfangseinrichtung zum Verbinden mit dem zumindest einen Speichermodul;

- eine Datenzwischenspeicherungseinrichtung, die mit der Datenempfangseinrichtung verbunden ist, zum Zwischenspeichern von Daten unter der Steuerung eines Strobe-Signals; und

- eine programmierbare Einrichtung zum Liefert des Strobe-Signals in programmierte Zeitgebungsbeziehung zu dem Taktsignal, dadurch gekennzeichnet, dass das System folgende Merkmale aufweist:

- eine erste Einrichtung zum wiederholten Messen des Werts eines Parameters, der die Signalverzögerungscharakteristika in dem System anzeigt, um Abweichungen in demselben zu erfassen, und

- eine zweite Einrichtung, die auf Abweichungen in den Signalverzögerungscharakteristika anspricht, die durch die erste Einrichtung erfasst werden, um die Programmierung der programmierbaren Einrichtung zu ändern, um die programmierte Zeitgebungsbeziehung für die Abweichungen zu kompensieren.

**[0014]** Bei einem Ausführungsbeispiel weist die programmierbare Einrichtung eine programmierbare Verzögerung auf, die wirksam zwischen die Taktleitung und die Datenzwischenspeicherungseinrichtung geschaltet ist. Bei einem anderen Ausführungsbeispiel weist die programmierbare Einrichtung eine programmierbare Verzögerung auf, die wirksam zwischen einer Speichersteuerungsleitung und die Datenzwischenspeicherungseinrichtung geschaltet ist, wobei die Speichersteuerungsleitung dazu dient, ein Speicherlesesignal zu tragen, das in zeitlich abgestimmter Beziehung zu dem Taktsignal erzeugt wird.

**[0015]** Vorzugsweise wird die Verzögerungseinrichtung zum automatischen Programmieren der programmierbaren Einrichtung zum Liefern des Strobe-Signals bereitgestellt, wobei die Programmierungseinrichtung wirksam ist, um diese Programmierung zu bewirken, z. B. nach dem Einschalten des Systems, das die Speichersteuerung umfasst.

**[0016]** Die programmierbare Einrichtung bei einer solchen Speichersteuerung kann programmiert werden durch:

- (a) – Programmieren der programmierbaren Einrichtung auf einen gegebenen Wert;

- (b) – Verwenden der Speichersteuerung zum Schreiben von Daten in die Speichereinrichtung;

- (c) – Verwenden der Speichersteuerung zum Lesen der Daten, die in die Speichereinrichtung geschrieben sind;

- (d) – Bestimmen, ob die Daten, die bei Schritt (b) gelesen werden, identisch zu den Daten sind, die bei Schritt (c) geschrieben werden;

- (e) – Wiederholen der Schritte (a) bis (d), bis Schritt (d) ein positives Ergebnis für zumindest einen gegebenen Wert ergibt;

- (f) – Programmieren der programmierbaren Einrichtung auf einen des zumindest einen gegebenen Werts.

**[0017]** Schritt (e) kann das Inkrementieren des gegebenen Werts aufweisen, und in diesem Fall, sobald Schritt (d) ein positives Ergebnis ergeben hat, werden Schritte (a) bis (d) wiederholt, bis Schritt (d) ein negatives Ergebnis ergibt.

**[0018]** Alternativ kann Schritt (e) das Dekrementieren des gegebenen Werts aufweisen, und in diesem Fall, sobald Schritt (d) ein positives Ergebnis ergeben hat, werden Schritte (a) bis (d) wiederholt, bis Schritt (d) ein negatives Ergebnis ergibt.

**[0019]** In beiden Fällen weist Schritt (f) vorzugsweise das Auswählen eines Werts aus einem Bereich von Werten auf, für die Schritt (d) ein positives Ergebnis erzielt.

**[0020]** Es ist ferner möglich, dass Schritt (e) für alle

möglichen programmierbaren Werte wiederholt wird. In diesem Fall kann Schritt (f) folgendes aufweisen:

- (g) Bestimmen von Bereichen von Werten, für die Schritt (d) ein positives Ergebnis ergibt;

- (h) Bestimmen des Größten dieser Bereiche von Werten;

und bei dem die programmierbare Einrichtung auf einen Wert programmiert ist, der in dem Größten der Bereiche enthalten ist.

**[0021]** Gemäß einem weiteren Aspekt der vorliegenden Erfindung wird ein Verfahren gemäß dem unabhängigen Anspruch 12 bereitgestellt.

**[0022]** Weitere Ausführungsbeispiele der Erfindung werden in den beiliegenden abhängigen Ansprüchen spezifiziert.

#### Kurze Beschreibung der Zeichnungen

**[0023]** Eine Speichersteuerung, die die Erfindung verkörpert, wird nun mit Hilfe eines nichteinschränkenden Beispiels Bezug nehmend auf die beiliegenden Zeichnungen beschrieben, in denen:

**[0024]** [Fig. 1](#) eine diagrammatische Ansicht einer herkömmlichen Speichersteuerung zusammen mit verschiedenen Speichermodulen ist;

**[0025]** [Fig. 2](#) ein Zeitgebungsdiagramm von unterschiedlichen Signalen in der Vorrichtung von [Fig. 1](#) ist;

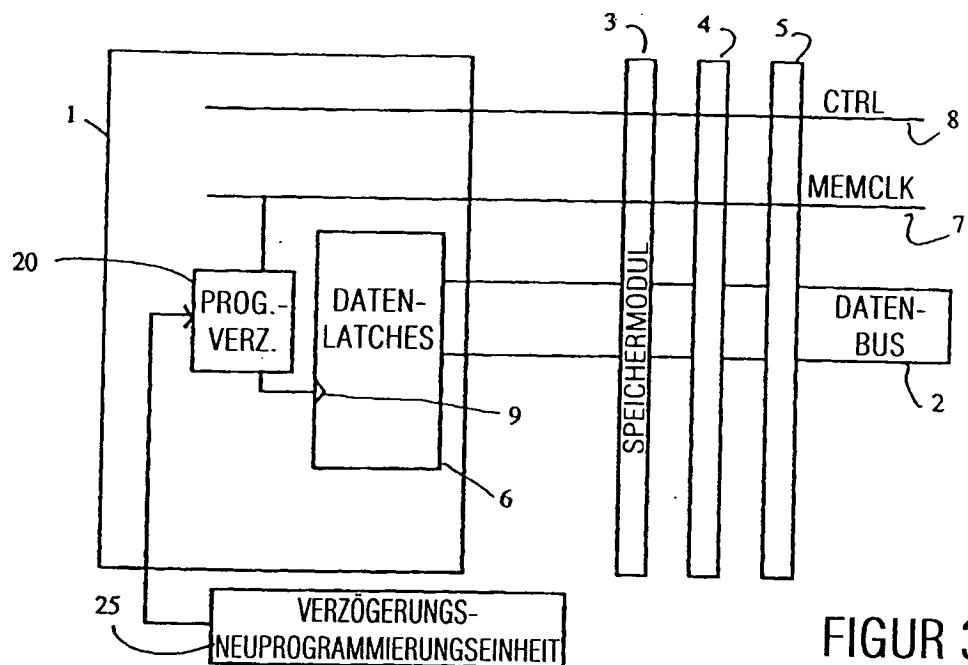

**[0026]** [Fig. 3](#) eine diagrammatische Ansicht einer Speichersteuerung ist, die die Erfindung zusammen mit verschiedenen Speichermodulen verkörpert;

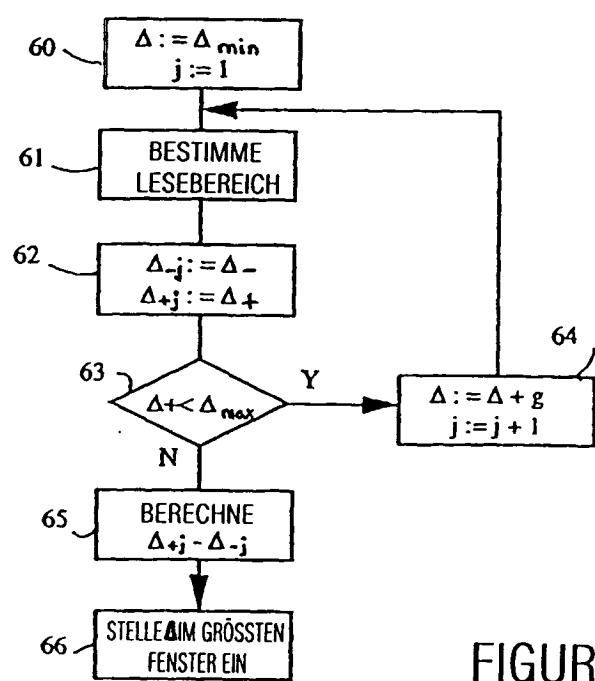

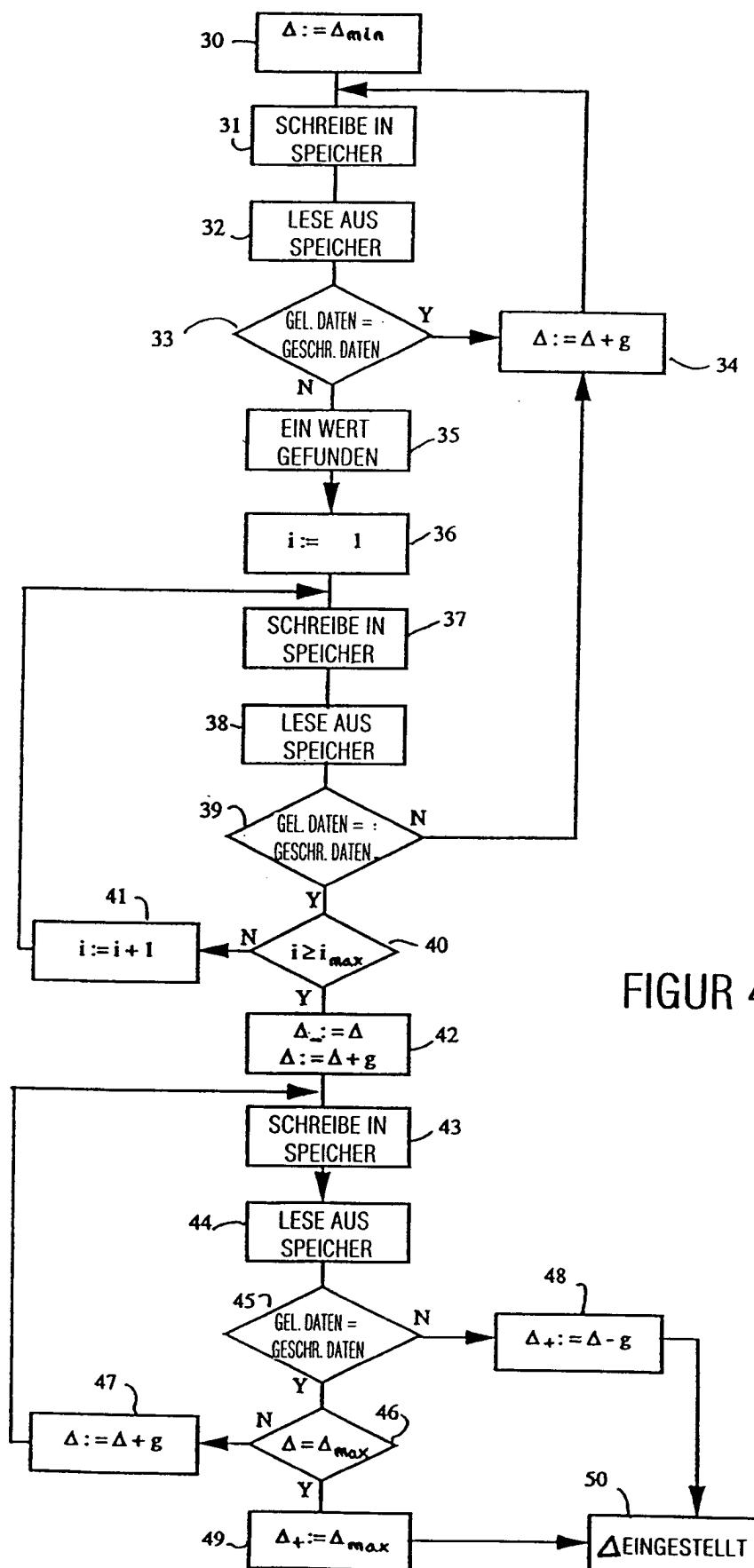

**[0027]** [Fig. 4](#) ein Flussdiagramm eines Verfahrens zum Programmieren der Strobe-Signalverzögerung gemäß der Erfindung ist;

**[0028]** [Fig. 5](#) ein Flussdiagramm eines anderen Verfahrens zum Programmieren der Strobe-Signalverzögerung gemäß der Erfindung zeigt.

#### Bester Modus zum Ausführen der Erfindung

**[0029]** [Fig. 3](#) zeigt eine diagrammatische Ansicht einer Speichersteuerung **19**, die die Erfindung verkörpert, zusammen mit verschiedenen Speichermodulen. Die Speichersteuerung **19** aus [Fig. 3](#) weist Datenlatches **6** zum Zwischenspeichern der Daten auf, die aus den Speichermodulen **3, 4** und **5** auf dem Datenbus **2** kommen; diese Speichermodule können z. B. aus SDRAM-Modulen aufgebaut sein. Die Datenlatches **6** werden durch ein Strobe-Signal an einem Eingang **9** freigegeben. Ein Speichertaktsignal MEM-CLK ist auf einer Takteleitung **7** vorhanden. Auf dieselbe allgemeine Weise, die oben Bezug nehmend auf

den Stand der Technik beschrieben ist, verursacht das Strobe-Signal, dass Daten bei jedem Taktzyklus in die Datenlatches **6** gelesen werden, wobei diese Daten nur eine vorbestimmte Anzahl von MEM-CLK-Zyklen nach der Aktivierung des CTRL-Signals als gültig behandelt werden.

**[0030]** Gemäß der vorliegenden Erfindung weist die Speichersteuerung **19** eine programmierbare Einrichtung **20** auf, zum Erzeugen des Strobe-Signals in einer programmierten Zeitgebungsbeziehung zu dem Takteingang MEMCLK. Diese programmierbare Einrichtung kann zum Programmieren der Strobe-Verzögerung gemäß der Speicherkonfiguration verwendet werden, um ein korrektes Datenlesen relativ zu dem CTRL-Signal sicherzustellen (wobei es möglich ist, das Strobe-Signal von dem MEMCLK-Signal zeitmäßig zu regeln, da das Speicherdatenlesesignal CTRL ebenfalls von dem MEMCLK-Signal zeitmäßig gesteuert wird). Wie in [Fig. 3](#) gezeigt ist, kann die Einrichtung **20** z. B. eine programmierbare Verzögerungsleitung aufweisen, die zwischen die Speichertakteleitung **7** und den Freigabeeingang **9** der Datenlatches **6** geschaltet ist. Diese programmierbare Verzögerungsleitung kann ein programmierbares Register aufweisen, das die Verzögerungsdauer auf bekannte Weise bestimmt. Dies macht die Programmierung der Strobe-Verzögerung leicht zu implementieren, durch eine einfache Softwareprogrammierung von einem Register der Speichersteuerung.

**[0031]** Der Bereich und die Granularität der Strobe-Verzögerung können von der Implementierung abhängen. Als ein Beispiel haben sich ein Bereich von 2 bis 10 Nanosekunden und eine Granularität von 150 Pikosekunden als ausreichend für eine Speichersteuerung herausgestellt, die auf bis zu vier Speicher-SDRAM-Module bei einer Taktfrequenz von 125 MHz zugreift. Wenn die programmierbare Einrichtung **20** ein Register der Speichersteuerung aufweist, wird die Größe dieses Registers durch den Bereich und die Granularität der Strobe-Verzögerung bestimmt.

**[0032]** [Fig. 3](#) zeigt nur die Komponenten der Speichersteuerung, die für das Verständnis der vorliegenden Erfindung notwendig sind. Die anderen Komponenten der Speichersteuerung **19** sind nicht dargestellt. Zum Beispiel umfasst die Speichersteuerung bei dem vorliegenden Ausführungsbeispiel eine Schaltungsanordnung zum Freigeben des Lesens der Datenlatches **6** nur eine vorbestimmte Anzahl von MEMCLK-Zyklen nach der Aktivierung des CTRL, und diese Schaltungsanordnung ist in [Fig. 3](#) nicht dargestellt.

**[0033]** Natürlich wäre es ebenfalls möglich, die vorliegende Erfindung in einer Speichersteuerung der Form von [Fig. 1](#) zu implementieren, durch Herleiten des Strobe-Signals aus dem Steuerungssignal CTRL

unter Verwendung einer programmierbaren Verzögerungsleitung. Da das CTRL-Signal von dem MEM-CLK-Signal zeitmäßig gesteuert wird, steuert dieses Ausführungsbeispiel sowie das aus [Fig. 3](#) das Strobe-Signal relativ zu dem MEMCLK-Signal zeitmäßig, aber in diesem Fall indirekt.

**[0034]** Egal welche Implementierung verwendet wird, die Speichersteuerungen, die diese Erfindung verkörpern, ermöglichen ein Programmieren der Strobe-Signalverzögerung gemäß den Umständen, z. B. gemäß der Speichermodulkonfiguration, gemäß der Speicherlast, usw. Sie ermöglicht der Speichersteuerung, bei Vollgeschwindigkeit zuverlässig in einer Speicherkonfiguration zu laufen, ungeachtet von Abweichungen bei der Last auf dem Speicherbus und der tatsächlichen Konfiguration der Speichersteuerung.

**[0035]** Im Hinblick auf das Programmieren der Strobe-Signalverzögerung in die programmierbare Einrichtung, kann dies wann immer nötig durchgeführt werden. Bei einem bevorzugten Ausführungsbeispiel der Erfindung wird die Einrichtung **20** zum Herleiten des Strobe-Signals durch einen Verzögerungsprogrammierungs-Funktions-Block oder eine -Einheit **25** beim Einschalter der Speichersteuerung programmiert, um sicherzustellen, dass eine Änderung bei der Speicherkonfiguration ordnungsgemäß berücksichtigt wird. Es ist ebenfalls möglich, die Programmierung fortzusetzen, immer wenn eine Änderung der Speicherkonfiguration erfasst wird. Die Einheit **25** zum Programmieren der programmierbaren Einrichtung **20** kann die Form einer zweckgebundenen Hardwarschaltungsanordnung annehmen, die intern oder extern von der Speichersteuerung oder durch einen Systemmikroprozessor bereitgestellt wird, der unter einer Firmwaresteuerung arbeitet.

**[0036]** [Fig. 4](#) ist ein Flussdiagramm eines Verfahrens zum Programmieren der Strobe-Signalverzögerung gemäß der Erfindung. Das Verfahren aus [Fig. 4](#) ist ein einfaches und schnelles Verfahren zum Programmieren der Einrichtung **20** zum Herleiten des Strobe-Signals. Bei dem Verfahren aus [Fig. 4](#) sei angenommen, dass die Einrichtung **20** zum Herleiten des Strobe-Signals programmiert werden kann, um eine Verzögerung  $\Delta$  zwischen dem Speichertaktsignal und dem Strobe-Signal einzustellen. Die Verzögerung  $\Delta$  kann in einem Bereich  $\Delta_{\min}$ – $\Delta_{\max}$  programmiert werden, mit einer Granularität von  $g$ .

**[0037]** Bei den Schritten **30**–**42** bestimmt das Programm einen niedrigsten Wert  $\Delta$ , der ein korrektes Lesen der Daten aus dem Speicher sicherstellt.

**[0038]** Bei Schritt **30** wird die Verzögerung  $\Delta$  auf den Minimalwert  $\Delta_{\min}$  eingestellt. Das Programm fährt mit Schritt **31** fort.

**[0039]** Bei Schritt **31** werden Daten in den Speicher geschrieben. Das Programm fährt mit Schritt **32** fort.

**[0040]** Bei Schritt **32** werden Daten aus dem Speicher gelesen. Das Programm fährt mit Schritt **33** fort.

**[0041]** Bei Schritt **33** werden die Daten, die aus dem Speicher gelesen wurden, mit den Daten verglichen, die in den Speicher geschrieben werden. Wenn die Daten, die gelesen und geschrieben werden, unterschiedlich sind, fährt das Programm mit Schritt **34** fort. Wenn die Daten, die gelesen und geschrieben werden, nicht unterschiedlich sind, fährt das Programm mit Schritt **35** fort.

**[0042]** Bei Schritt **34** wird die Verzögerung um  $g$  inkrementiert. Das Programm fährt dann mit Schritt **31** fort.

**[0043]** Bei Schritt **35** weist  $\Delta$  einen Wert auf, der bereits ein korrektes Lesen der Daten in dem Speicher verursacht hat. Vorzugsweise wird dieser Wert bei den Schritten **36**–**41** geprüft, um sicherzustellen, dass dieser Wert von  $\Delta$  ein korrektes Lesen der Daten für mehr als eine Operation ergibt. Dieser Zuverlässigkeitstest ist nicht zwingend und kann übersprungen werden. In diesem Fall fährt das Programm direkt mit Schritt **42** fort.

**[0044]** Bei den Schritten **36**–**41** wird die Zuverlässigkeit der Schreib/Lese-Operation mit dem aktuellen Wert von  $\Delta$  geprüft, durch Durchführen von  $i_{\max}$  Lese- und Schreib-Operationen. Bei Schritt **36** wird der Parameter  $i$  auf 1 eingestellt. Das Programm fährt mit Schritt **37** fort.

**[0045]** Bei Schritt **37** werden Daten in den Speicher geschrieben. Das Programm fährt mit Schritt **38** fort.

**[0046]** Bei Schritt **38** werden Daten aus dem Speicher gelesen. Das Programm fährt mit Schritt **39** fort.

**[0047]** Bei Schritt **39** werden die Daten, die aus dem Speicher gelesen werden, mit den Daten verglichen, die in den Speicher geschrieben werden. Wenn die gelesenen und geschriebenen Daten unterschiedlich sind, wird bestimmt, dass der aktuelle Wert von  $\Delta$  nicht zuverlässig ist; das Programm fährt mit Schritt **34** fort. Wenn die gelesenen und geschriebenen Daten gleich sind, fährt das Programm mit Schritt **40** fort.

**[0048]** Bei Schritt **40** wird geprüft, ob  $i_{\max}$  Schreib- und Lese-Operationen durchgeführt wurden, d. h. ob  $i \geq i_{\max}$ . Wenn dies nicht der Fall ist, fährt das Programm mit Schritt **41** fort. Wenn dies der Fall ist, hat sich der aktuelle Wert von  $\Delta$  als zuverlässig für die  $i_{\max} + 1$  Schreib- und Lese-Operationen herausgestellt. Das Programm fährt dann mit Schritt **42** fort.

**[0049]** Bei Schritt **41** wird  $i$  um 1 inkrementiert. Das Programm fährt dann mit Schritt **37** fort.

**[0050]** Bei Schritt **42** wird der aktuelle Wert von  $\Delta$  als  $\Delta_-$  gespeichert; dieser Wert von  $\Delta$  ist der niedrigste Wert, für den ein Lesen der Daten erfolgreich ist. Der Wert von  $\Delta$  wird dann um  $g$  inkrementiert. Das Programm fährt dann mit Schritt **43** fort.

**[0051]** Bei den Schritten **43–49** bestimmt das Programm einen Wert  $\Delta_+$  für die Verzögerung. In dem Bereich von  $\Delta_-$  bis  $\Delta_+$  können Daten direkt aus dem Speicher gelesen werden.

**[0052]** Bei Schritt **43** werden Daten in den Speicher geschrieben. Das Programm fährt mit Schritt **44** fort.

**[0053]** Bei Schritt **44** werden Daten aus dem Speicher gelesen. Das Programm fährt mit Schritt **45** fort.

**[0054]** Bei Schritt **45** werden die Daten, die aus dem Speicher gelesen werden, mit den Daten verglichen, die in den Speicher geschrieben werden. Wenn die gelesenen und geschriebenen Daten identisch sind, fährt das Programm mit Schritt **46** fort. Wenn die gelesenen und geschriebenen Daten unterschiedlich sind, fährt das Programm mit Schritt **48** fort.

**[0055]** Bei Schritt **46** wurde bestimmt, dass der aktuelle Wert von  $\Delta$  immer noch zu zumindest einem korrekten Lesen der Daten aus dem Speicher führt. Es ist optional möglich, zu prüfen, ob der aktuelle Wert von  $\Delta$  ein korrektes Lesen von mehr als einer Schreib/Lese-Operation ermöglicht. Dies kann durchgeführt werden unter Verwendung von Programmschritten ähnlich zu den Schritten **36–41**: Dieser Zuverlässigkeitstest ist jedoch nicht verbindlich und kann übersprungen werden. Der aktuelle Wert von  $\Delta$  wird dann mit dem Maximalwert  $\Delta_{\max}$  verglichen. Wenn  $\Delta = \Delta_{\max}$ , fährt das Programm mit Schritt **49** fort; ansonsten fährt das Programm mit Schritt **47** fort.

**[0056]** Bei Schritt **47** wird die Verzögerung  $\Delta$  um  $g$  inkrementiert. Das Programm fährt mit Schritt **43** fort.

**[0057]** Bei Schritt **48** wurde ein Wert von  $\Delta$ , der zumindest ein inkorrektes Lesen der Daten in dem Speicher ergibt, erreicht. Bei diesem Schritt wurde bestimmt, dass die Werte von  $\Delta$  zwischen  $\Delta_-$  und  $\Delta_- - g$ , d. h. der aktuelle Wert von  $\Delta$  minus einem Inkrement, ein korrektes Lesen in dem Speicher sicherstellen. Der Wert  $\Delta - g$  wird als  $\Delta_+$  gespeichert. Das Programm fährt dann mit Schritt **50** fort.

**[0058]** Bei Schritt **49** wurde bestimmt, dass die Werte von  $\Delta$  zwischen  $\Delta_-$  und  $\Delta_{\max}$  zu einem korrekten Lesen der Daten in dem Speicher führen. Der Wert  $\Delta_{\max}$  wird als  $\Delta_+$  gespeichert. Das Programm fährt dann mit Schritt **50** fort.

**[0059]** Durch Schritt **50** wurde sichergestellt, dass Werte von  $\Delta$  zwischen  $\Delta_-$  und  $\Delta_+$  zu einem korrekten Lesen der Daten führen. Die Verzögerung  $\Delta$  kann dann auf einen Wert innerhalb dieses Bereichs programmiert werden, z. B. den Wert am nächsten zu  $(\Delta_+ - \Delta_-)/2$ .

**[0060]** Das Verfahren aus [Fig. 4](#) ermöglicht ein einfaches und schnelles Einstellen der Verzögerung  $\Delta$ . Andere Verfahren sind möglich; das Verfahren aus [Fig. 4](#) kann ebenfalls modifiziert werden. Zum Beispiel, in dem Flussdiagramm aus [Fig. 4](#), folgt jedem Leseschritt ein Schrebschritt; die Informationen, die in den Speicher geschrieben werden, können für jede Schreib/Lese-Operation variieren, um eine korrekte statistische Prüfung des Speichers sicherzustellen; es wäre jedoch ebenfalls möglich, nur einen Schreibschritt zu haben und immer dieselben Daten zu lesen. Es ist ebenfalls möglich, durch Bestimmen von  $\Delta_+$  zu beginnen und dann  $\Delta_-$  zu bestimmen, wobei die notwendigen Änderungen für einen Fachmann auf dem Gebiet offensichtlich sind.

**[0061]** Bei einem bevorzugten Ausführungsbeispiel der Erfindung wird der gesamte Bereich von Verzögerungswerten geprüft, um sicherzustellen, ob verschiedene geeignete Lesefenster existieren  $[\Delta_-; \Delta_+]$ ; wenn dies der Fall ist, wird vorzugsweise ein Wert von  $\Delta$  in dem größten Fenster ausgewählt. [Fig. 5](#) zeigt ein Flussdiagramm für dieses Verfahren.

**[0062]** Bei dem ersten Schritt **60** ist die Verzögerung  $\Delta$  auf den Minimalwert  $\Delta_{\min}$  eingestellt. Ein Parameter  $j$  ist auf 1 eingestellt. Das Programm fährt mit Schritt **61** fort.

**[0063]** Bei Schritt **61** wird ein Lesebereich oder ein Fenster  $[\Delta_-; \Delta_+]$  bestimmt, z. B. unter Verwendung der Schritte **31–49** aus [Fig. 4](#). Das Programm fährt mit Schritt **62** fort.

**[0064]** Bei Schritt **62** werden die aktuellen Werte von  $\Delta_-$  und  $\Delta_+$  als  $\Delta_{-j}$  und  $\Delta_{+j}$  gespeichert. Das Programm fährt dann mit Schritt **63** fort.

**[0065]** Bei Schritt **63** wird  $\Delta_+$  mit  $\Delta_{\max}$  verglichen. Wenn  $\Delta_+$  gleich  $\Delta_{\max}$  ist, gibt es kein weiteres geeignetes Fenster. In diesem Fall fährt das Programm mit Schritt **65** fort. Wenn dies nicht der Fall ist, fährt das Programm mit Schritt **64** fort.

**[0066]** Bei Schritt **64** wird  $j$  um 1 inkrementiert und  $\Delta$  wird um  $g$  inkrementiert. Das Programm fährt dann mit Schritt **61** fort.

**[0067]** Bei Schritt **65**, für alle möglichen Werte von  $j$ , wird die Differenz  $\Delta_{+j} - \Delta_{-j}$  berechnet. Die größte Differenz wird bestimmt. Dies liefert das größte Lesefenster. Das Programm fährt dann mit Schritt **66** fort.

**[0068]** Bei Schritt 66 wird die Verzögerung  $\Delta$  bei einem Wert innerhalb dieses größten Lesefensters programmiert, z. B. bei dem Wert am nächsten zu  $(\Delta_{t_j} - \Delta_{-j})/2$ , wobei  $j$  der Index des größten Lesefensters ist, wie bei Schritt 65 bestimmt wird.

**[0069]** Das Verfahren aus [Fig. 5](#) stellt sicher, dass der Wert für die Verzögerung in dem größten möglichen Bereich ausgewählt wird, der zum Lesen der Daten aus dem Speicher geeignet ist.

**[0070]** Die Beschreibung des besten Modus zum Ausführen der Erfindung wurde nur als ein Beispiel gegeben. Andere Ausführungsbeispiele der Erfindung können verwendet werden; z. B. kann ein anderes Verfahren als das, das in [Fig. 4](#) gezeigt ist, zum Programmieren der Strobe-Signalverzögerung verwendet werden. Es ist möglich, eine andere Programmierungseinrichtung 20 als ein Register in der Speichersteuerung zu verwenden, wenn andere geeignete Programmierungsfähigkeiten vorgesehen sind.

**[0071]** Zusätzlich zum Einprogrammieren eines bestimmten Werts für die Strobe-Signalverzögerung an vorbestimmten Punkten während der Systemoperation kann die Verzögerungsprogrammierungseinheit 25 angeordnet sein, um den programmierten Verzögerungswert inkrementell einzustellen, abhängig von Abweichungen bei der Versorgungsspannung und/oder der Temperatur, um dadurch ein unerwünschtes Driften des Strobe-Signals während der Verwendung der Speichersteuerung zu kompensieren.

**[0072]** Dies kann implementiert werden, durch Verwenden einer Schaltung zum Messen des Werts eines Parameters, der empfindlich gegenüber den Signalverzögerungscharakteristika in dem Speicherteilsystem ist. Beispielsweise könnte der gemessene Parameter die Anzahl von Invertern in einer Kette aus Invertern sein, die benötigt werden, um eine vorbestimmte Signalverzögerung zu erzeugen. Die Einheit 25 weist ferner eine Einrichtung auf, die auf Änderungen bei dem gemessenen Parameterwert über Zeit anspricht, um eine geeignete Änderung bei der Verzögerung zu bestimmen, die in der programmierbaren Verzögerung 20 eingestellt ist; diese Einrichtung könnte die Form einer Nachschlagttabelle annehmen. Sobald eine geeignete Änderung bei der Verzögerung bestimmt wurde, ändert die Einheit 25 die programmierte Verzögerung um den geeigneten Betrag.

**[0073]** Obwohl die einfachste Möglichkeit zum Erzeugen des Strobe-Signals das Verzögern von entweder dem MEMCLK- oder dem CTRL-Signal ist, wie oben beschrieben wurde, wird darauf hingewiesen, dass andere Wege möglich sind. Zum Beispiel könnte eine separate Taktorschaltung verwendet werden, um das Strobe-Signal zu erzeugen, wobei diese Takt-

schaltung mit dem MEMCLK-Signal in einer gewünschten Phasenbeziehung zu demselben durch eine geeignete Phasenregelschleife synchronisiert ist.

## Patentansprüche

1. Ein System, das zumindest ein Speichermodul (3, 4, 5) und eine Speichersteuerung (19) aufweist, wobei die Speichersteuerung folgende Merkmale aufweist:

- eine Taktleitung (7) für ein Taktsignal;

- eine Datenempfangseinrichtung (2) zum Verbinden mit dem zumindest einen Speichermodul (3, 4, 5);

- eine Datenzwischenspeicherungseinrichtung (6), die mit der Datenempfangseinrichtung (2) verbunden ist, zum Zwischenspeichern von Daten unter der Steuerung eines Strobe-Signals; und

- eine programmierbare Einrichtung (20) zum Liefern des Strobe-Signals in programmierte Zeitgebungsbeziehung zu dem Taktsignal, **dadurch gekennzeichnet**, dass das System folgende Merkmale aufweist:

- eine erste Einrichtung zum periodischen Messen des Werts eines Parameters, der die Signalverzögerungscharakteristika in dem System anzeigt, um Abweichungen in demselben zu erfassen, und

- eine zweite Einrichtung, die auf Abweichungen in den Signalverzögerungscharakteristika anspricht, die durch die erste Einrichtung erfasst werden, um die Programmierung der programmierbaren Einrichtung zu ändern, um die programmierte Zeitgebungsbeziehung für die Abweichungen zu kompensieren.

2. Ein System gemäß Anspruch 1, bei dem die programmierbare Einrichtung (20) eine programmierbare Verzögerungseinrichtung aufweist, die wirksam zwischen die Taktleitung (7) und die Datenzwischenspeicherungseinrichtung (6) geschaltet ist.

3. Ein System gemäß Anspruch 1, das ferner folgende Merkmale aufweist:

- eine Speichersteuerungsleitung (8) für ein Speicherlesesignal, und

- eine Einrichtung zum Erzeugen des Speicherlesesignals in zeitlich abgestimmter Beziehung zu dem Taktsignal;

- wobei die programmierbare Einrichtung (20) eine programmierbare Verzögerungseinrichtung ist, die wirksam zwischen die Speichersteuerungsleitung und die Datenzwischenspeicherungseinrichtung geschaltet ist.

4. Ein System gemäß einem der vorhergehenden Ansprüche, bei dem die programmierbare Einrichtung (20) ein programmierbares Register zum Einstellen der programmierten Zeitgebungsbeziehung aufweist.

5. Ein System gemäß Anspruch 4, bei dem die

Programmierungseinrichtung das Programmieren nach dem Einschalten des Systems bewirkt.

6. Ein System gemäß einem der vorhergehenden Ansprüche, bei dem die programmierbare Einrichtung eine Einrichtung aufweist, die angeordnet ist, um die folgenden Schritte auszuführen:

- (a) – Programmieren der programmierbaren Einrichtung auf einen gegebenen Wert;

- (b) – Verwenden der Speichersteuerung zum Schreiben von Daten in die Speichereinrichtung;

- (c) – Verwenden der Speichersteuerung zum Lesen der Daten, die in die Speichereinrichtung geschrieben sind;

- (d) – Bestimmen, ob die Daten, die bei Schritt (b) gelesen werden, identisch zu den Daten sind, die bei Schritt (c) geschrieben werden;

- (e) – Wiederholen der Schritte (a) bis (d), bis Schritt (d) ein positives Ergebnis für zumindest einen gegebenen Wert ergibt;

- (f) – Programmieren der programmierbaren Einrichtung auf einen des zumindest einen gegebenen Werts.

7. Ein System gemäß Anspruch 6, das so angeordnet ist, dass der Schritt (e) das Inkrementieren des gegebenen Werts aufweist, und sobald Schritt (d) ein positives Ergebnis ergeben hat, Schritte (a) bis (d) wiederholt werden, bis Schritt (d) ein negatives Ergebnis ergibt.

8. Ein System gemäß Anspruch 6, das so angeordnet ist, dass Schritt (e) das Dekrementieren des gegebenen Werts aufweist, und sobald Schritt (d) ein positives Ergebnis ergeben hat, Schritte (a) bis (d) wiederholt werden, bis Schritt (d) ein negatives Ergebnis ergibt.

9. Ein System gemäß Anspruch 7 oder Anspruch 8, das so angeordnet ist, dass Schritt (f) das Auswählen eines Werts in einem Bereich von Werten aufweist, für die Schritt (d) ein positives Ergebnis ergibt.

10. Ein System gemäß Anspruch 6, das so angeordnet ist, dass Schritt (e) für alle möglichen programmierbaren Werte wiederholt wird.

11. Ein System gemäß Anspruch 10, das so angeordnet ist, dass Schritt (f) Folgendes aufweist:

- (g) Bestimmen von Bereichen von Werten, für die Schritt (d) ein positives Ergebnis ergibt;

- (h) Bestimmen des größten dieser Bereiche von Werten;

und bei dem die programmierbare Einrichtung auf einen Wert programmiert ist, der in dem größten der Bereiche enthalten ist.

(für den benannten Staat DE)

12. Ein Verfahren zum Verbessern der Zuverlässigkeit des Lesens von Daten in einer Speichersteu-

erung aus zumindest einem Speichermodul innerhalb eines Systems, wobei die Speichersteuerung eine Datenempfangseinrichtung (2) zum Verbinden mit dem zumindest einen Speichermodul (3, 4, 5) und eine Datenzwischenspeicherungseinrichtung (6), die mit der Datenempfangseinrichtung (2) verbunden ist, aufweist, zum Zwischenspeichern von Daten unter der Steuerung des Lese-Strobe-Signals, wobei das Verfahren folgenden Schritt aufweist:

- Programmieren in einer programmierbaren Einrichtung innerhalb der Speichersteuerung einer Verzögerung zwischen einem Taktsignal (10) und einem Lese-Strobe-Signal aufweist;

wobei das Verfahren durch folgende Schritte gekennzeichnet ist:

- periodisches Messen des Werts eines Parameters, der die Signalverzögerungscharakteristika in dem System anzeigt, um Abweichungen in demselben zu erfassen; und

- Ansprechen auf Abweichungen bei den Signalverzögerungscharakteristika, die durch die erste Einrichtung erfasst werden, um die Programmierung der Verzögerung zu ändern, um die programmierte Zeitgebungsbeziehung für die Abweichungen zu kompensieren.

13. Ein Verfahren gemäß Anspruch 12, bei dem das Programmieren beim Einschalten der Speichersteuerung ausgeführt wird.

14. Ein Verfahren gemäß Anspruch 12, bei dem das Programmieren ausgeführt wird, um Spannungsabweichungen zu kompensieren.

15. Ein Verfahren gemäß Anspruch 12, bei dem das Programmieren ausgeführt wird, um Abweichungen bei der Verarbeitungslast zu kompensieren.

16. Ein Verfahren gemäß Anspruch 12, bei dem das Programmieren ausgeführt wird, um Temperaturabweichungen zu kompensieren.

Es folgen 3 Blatt Zeichnungen

## Anhängende Zeichnungen

FIGUR 3

FIGUR 5

FIGUR 4