|                                     |                        |

|-------------------------------------|------------------------|

| <b>DOMANDA DI INVENZIONE NUMERO</b> | <b>102021000022565</b> |

| <b>Data Deposito</b>                | <b>31/08/2021</b>      |

| <b>Data Pubblicazione</b>           | <b>28/02/2023</b>      |

Classifiche IPC

| <b>Sezione</b> | <b>Classe</b> | <b>Sottoclasse</b> | <b>Gruppo</b> | <b>Sottogruppo</b> |

|----------------|---------------|--------------------|---------------|--------------------|

| G              | 06            | F                  | 11            | 10                 |

| <b>Sezione</b> | <b>Classe</b> | <b>Sottoclasse</b> | <b>Gruppo</b> | <b>Sottogruppo</b> |

|----------------|---------------|--------------------|---------------|--------------------|

| G              | 06            | F                  | 11            | 22                 |

Titolo

Sistema di elaborazione, relativo circuito integrato, dispositivo e procedimento

**DESCRIZIONE** dell'invenzione industriale dal titolo:

"Sistema di elaborazione, relativo circuito integrato, dispositivo e procedimento"

di: STMicroelectronics Application GmbH, di nazionalità tedesca, Bahnhofstrasse 18, 85609 Aschheim, Germania; STMicroelectronics International N.V., di nazionalità svizzera, Chemin du Champ-des-Filles 39, 1228 Plan-les-Ouates, Geneva, Svizzera

Inventori designati: Vivek Mohan SHARMA, Roberto COLOMBO

Depositata il: 31 agosto 2021

\* \* \*

#### **TESTO DELLA DESCRIZIONE**

##### **Campo Tecnico**

Le forme di attuazione della presente descrizione sono relative alla gestione degli errori nei sistemi di elaborazione, come i microcontrollori.

##### **Sfondo**

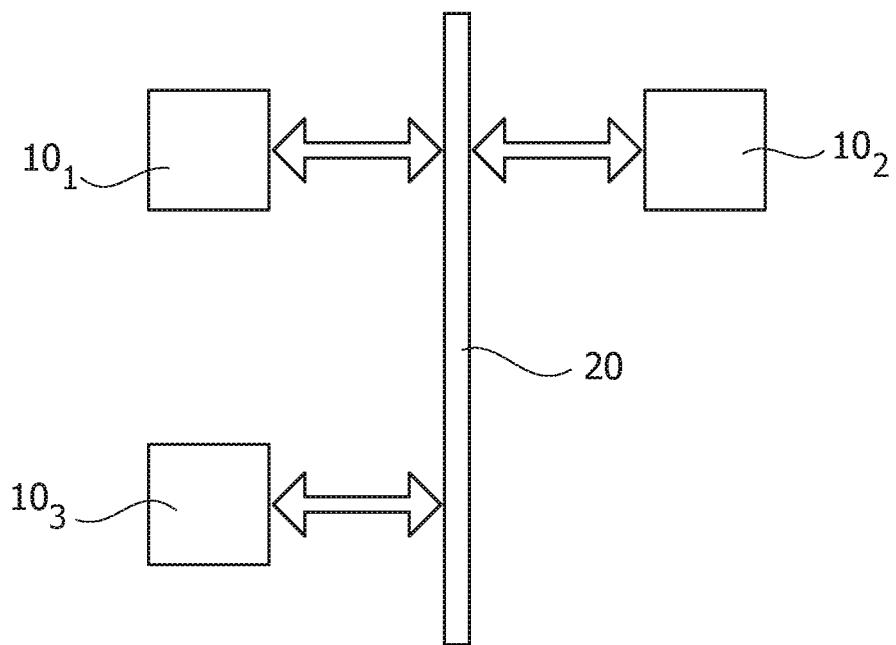

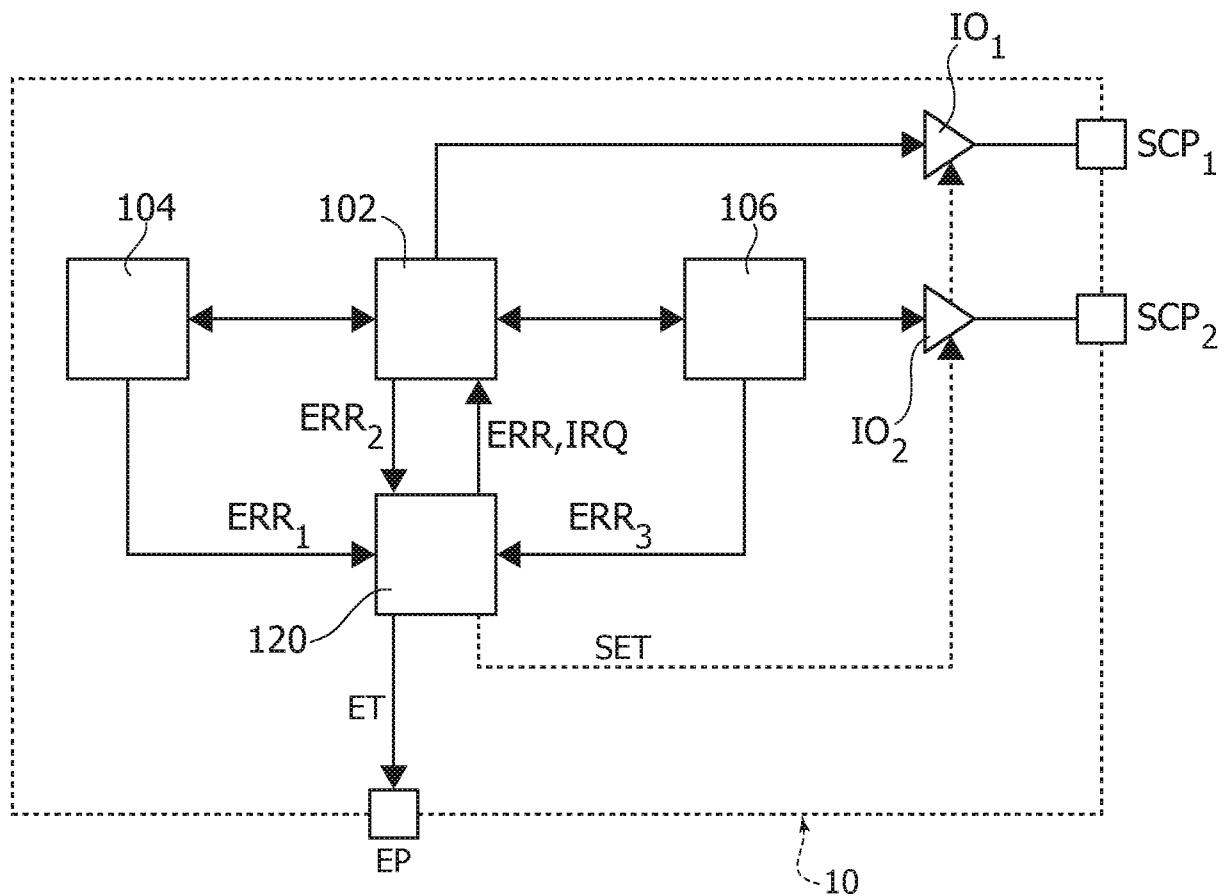

La Figura 1 rappresenta un tipico sistema elettronico, come il sistema elettronico di un veicolo, comprendente una pluralità di sistemi di elaborazione 10, come sistemi embedded o circuiti integrati, per es., una FPGA (Field Programmable Gate Array), un DSP (Digital Signal Processor) o un microcontrollore (per es., dedicato al mercato automotive).

Per esempio, nella Figura 1 sono rappresentati tre sistemi di elaborazione 10<sub>1</sub>, 10<sub>2</sub> e 10<sub>3</sub> connessi attraverso un sistema di comunicazione 20 adatto. Per esempio, il sistema di comunicazione può comprendere un bus di controllo del veicolo, come un bus CAN (Controller Area Network), ed eventualmente un bus multimediale, come un bus MOST (Media Oriented Systems Transport), connesso al bus di

controllo del veicolo attraverso un gateway. Tipicamente, i sistemi di elaborazione 10 sono situati in differenti posizioni del veicolo e possono comprendere, per es., una Unità di Controllo del Motore ("Engine Control Unit"), una Unità di Controllo della Trasmissione (TCU, "Transmission Control Unit"), un Sistema Frenante Antiblocco (ABS, "Anti-lock Braking System"), un modulo di controllo della scocca (BCM, "Body Control Module") e/o un sistema audio multimediale e/o di navigazione. Di conseguenza, uno o più dei sistemi di elaborazione 10 possono anche implementare funzioni di controllo e di regolazione in tempo reale ("real-time"). Questi sistemi di elaborazione sono identificati di solito come Unità di Controllo Elettroniche (ECU, "Electronic Control Unit").

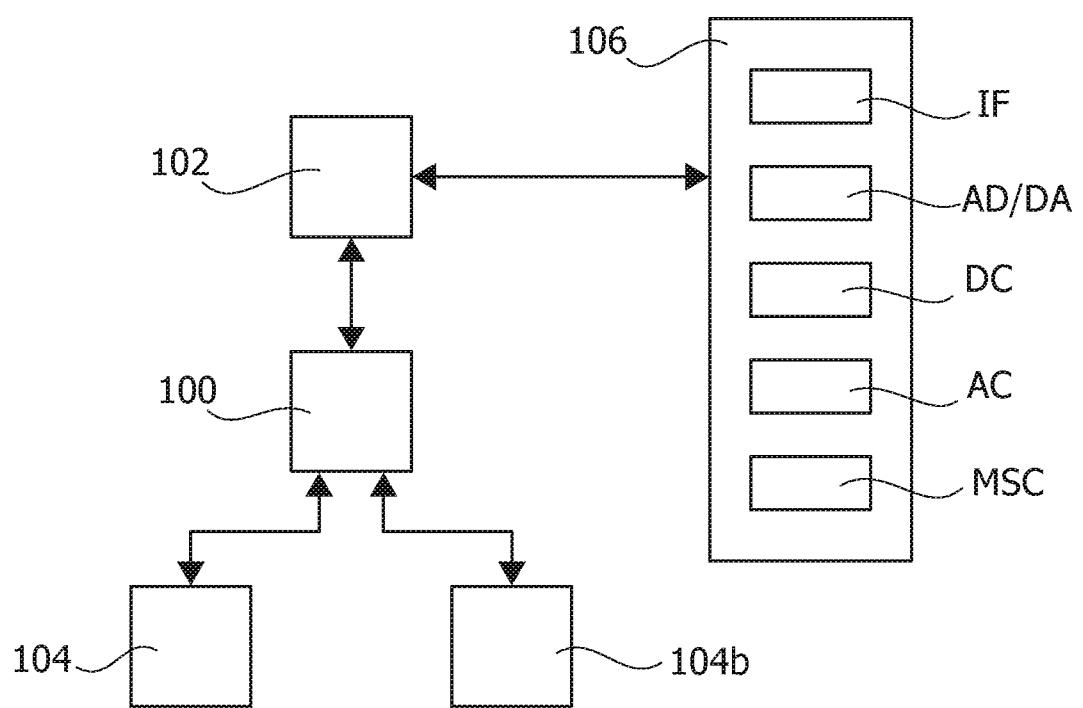

La Figura 2 rappresenta uno schema a blocchi di un esempio di un sistema di elaborazione 10 digitale, come un microcontrollore, che può essere usato in uno qualsiasi dei sistemi di elaborazione 10 della Figura 1.

Nell'esempio considerato, il sistema di elaborazione 10 comprende un microprocessore 102, di solito l'Unità di Elaborazione Centrale (CPU, "Central Processing Unit"), programmato mediante istruzioni software. Di solito, il software eseguito dal microprocessore 102 è memorizzato in una memoria di programma 104 non volatile, come una memoria Flash o una EEPROM. Così, la memoria 104 è configurata per memorizzare il firmware dell'unità di elaborazione 102, in cui il firmware comprende le istruzioni software che devono essere eseguite dal microprocessore 102. Generalmente, la memoria non volatile 104 può anche essere usata per memorizzare altri dati, come i dati di configurazione, per es., i dati di calibrazione.

Il microprocessore 102 ha di solito associata anche una memoria volatile 104b, come una memoria ad accesso casuale (RAM, "Random-Access-Memory"). Per esempio, la memoria 104b può essere usata per memorizzare dati temporanei.

Come rappresentato nella Figura 2, di solito la comunicazione con le memorie 104 e/o 104b è effettuata mediante uno o più controllori di memoria 100. Il controllore (i controllori) di memoria 100 può essere integrato (possono essere integrati) nel microprocessore 102 o connesso (connessi) al microprocessore 102 mediante un canale di comunicazione, come un bus di sistema del sistema di elaborazione 10. Similmente, le memorie 104 e/o 104b possono essere integrate con il microprocessore 102 in un singolo circuito integrato, o le memorie 104 e/o 104b possono essere sotto forma di un circuito integrato separato e connesso al microprocessore 102, per es., mediante le piste di una scheda a circuito stampato (PCB, "Printed Circuit Board").

Nell'esempio considerato, il microprocessore 102 può avere associate una o più periferiche/risorse (hardware) 106, selezionate tra il gruppo di:

- una o più interfacce di comunicazione IF, per es. per scambiare dati tramite il sistema di comunicazione 20, come una interfaccia UART (Universal Asynchronous Receiver/Transmitter), Bus SPI (Serial Peripheral Interface), I<sup>2</sup>C (Inter-Integrated Circuit), bus CAN (Controller Area Network), e/o una interfaccia Ethernet e/o una interfaccia di debug; e/o

- uno o più convertitori analogico/digitali AD e/o convertitori digitale/analogici DA; e/o

- uno o più componenti digitali DC dedicati, come contatori e/o timer hardware, o un coprocessore crittografico; e/o

- uno o più componenti analogici AC, come comparatori, sensori, come un sensore di temperatura, ecc.; e/o

- uno o più componenti a segnali misti MSC, come un dispositivo di pilotaggio ("driver") PWM (Pulse-Width Modulation).

Generalmente, componenti digitali DC dedicati possono corrispondere anche a una FPGA integrata nel sistema di elaborazione 10. Per esempio, in questo caso, la memoria 104 può comprendere anche i dati di programma per una tale FPGA.

Di conseguenza, il sistema di elaborazione digitale 10 può supportare differenti funzionalità. Per esempio, il comportamento del microprocessore 102 è determinato dal firmware memorizzato nella memoria 104, per es., le istruzioni software che devono essere eseguite da un microprocessore 102 di un microcontrollore 10. Così, installando un firmware differente, lo stesso (microcontrollore) hardware può essere usato per differenti applicazioni.

A questo riguardo, ci si aspetta che le future generazioni di tali sistemi di elaborazione 10, per es., microcontrollori atti a essere usati nelle applicazioni automotive, presentino un aumento della complessità, dovuto principalmente al numero crescente di funzionalità richieste (nuovi protocolli, nuove caratteristiche, ecc.) e ai vincoli stringenti delle condizioni di esecuzione (per es., un consumo di potenza più basso, maggiore velocità e potenza di calcolo, ecc.).

Per esempio, recentemente sono stati proposti sistemi di elaborazione multi-core 10 più complessi. Per esempio, tali sistemi di elaborazione multi-core possono essere usati per eseguire (in parallelo) alcuni dei sistemi di elaborazione 10 rappresentati nella Figura 1, come alcune ECU di un veicolo.

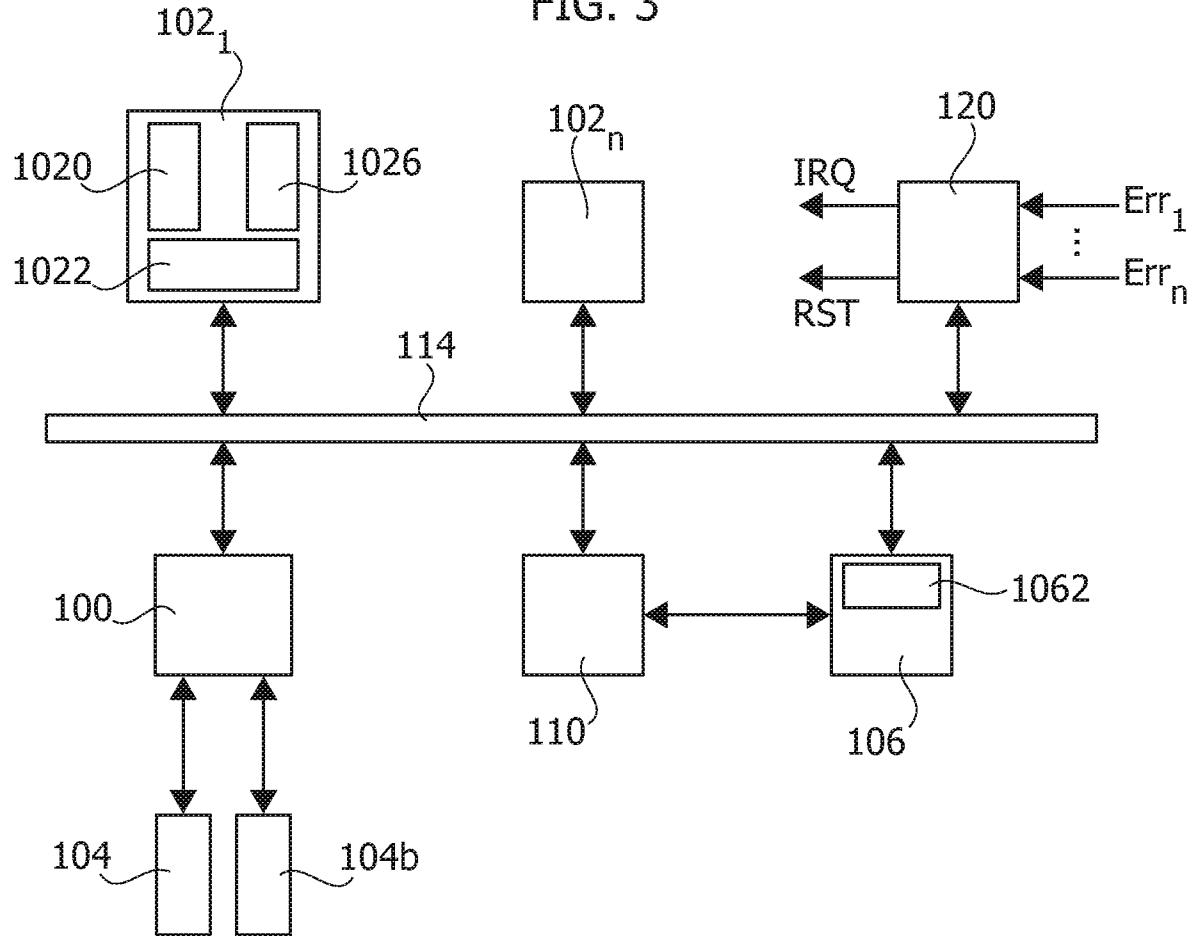

La Figura 3 rappresenta un esempio di un sistema di elaborazione multi-core 10. Specificamente, nell'esempio considerato, il sistema di elaborazione 10 comprende una pluralità di  $n$  core di elaborazione 102<sub>1</sub>...102<sub>n</sub> connessi a un sistema di comunicazione (on-chip) 114. Per esempio, nel contesto dei sistemi di controllo in tempo reale, i core di elaborazione 102<sub>1</sub>...102<sub>n</sub> possono essere core ARM Cortex®-R52. Generalmente, il sistema di comunicazione 114 può comprendere uno o più sistemi di bus, per es., basati sull'architettura di bus AXI (Advanced extensible Interface), e/o un NoC (Network-on-Chip).

Per esempio, come rappresentato nell'esempio del core di elaborazione 102<sub>1</sub>, ciascun core di elaborazione 102 può comprendere un microprocessore 1020 e un'interfaccia di comunicazione 1022 configurata per gestire la comunicazione tra il microprocessore 1020 e il sistema di comunicazione 114. Tipicamente, l'interfaccia 1022 è un'interfaccia master configurata per inoltrare una data richiesta (di lettura o di scrittura) dal microprocessore 1020 al sistema di comunicazione 114, e per inoltrare una risposta opzionale dal sistema di comunicazione 114 al microprocessore 1020. Tuttavia, l'interfaccia di comunicazione 1022 può anche comprendere un'interfaccia slave. Per esempio, in questo modo, un primo microprocessore 1020 può inviare una richiesta a un secondo microprocessore 1020 (mediante l'interfaccia di

comunicazione 1022 del primo microprocessore, il sistema di comunicazione 114 e l'interfaccia di comunicazione 1022 del secondo microprocessore).

Generalmente, ciascun core di elaborazione 102<sub>1</sub>...102<sub>n</sub> può comprendere anche ulteriori risorse locali, come una o più memorie locali 1026, identificata di solito come TCM (Tightly Coupled Memory).

Come menzionato in precedenza, tipicamente i core di elaborazione 102<sub>1</sub>...102<sub>n</sub> sono disposti per scambiare dati con una memoria non volatile 104 e/o una memoria volatile 104b. In un sistema di elaborazione multi-core 10, spesso queste memorie sono memorie di sistema, cioè, condivise per i core di elaborazione 102<sub>1</sub>...102<sub>n</sub>. Come menzionato in precedenza, ciascuno dei core di elaborazione 102<sub>1</sub>...102<sub>n</sub> può comprendere, tuttavia, una o più memorie locali 1026 aggiuntive.

Per esempio, come rappresentato nella Figura 3, il sistema di elaborazione 10 può comprendere uno o più controllori di memoria 100 configurati per connettere almeno una memoria non volatile 104 e almeno una memoria volatile 104b al sistema di comunicazione 114. Come menzionato in precedenza, una o più delle memorie 104 e/o 104b possono essere integrate nel circuito integrato del sistema di elaborazione 10 o connesse all'esterno del circuito integrato.

Come menzionato in precedenza, il sistema di elaborazione 10 può comprendere una o più risorse 106, come una o più interfacce di comunicazione o coprocessori (per es., un coprocessore crittografico). Le risorse 106 sono connesse di solito al sistema di comunicazione 114 mediante una rispettiva interfaccia di comunicazione 1062. In generale, l'interfaccia di comunicazione 1062 comprende

almeno un'interfaccia slave. Per esempio, in questo modo, un core di elaborazione 102 può inviare una richiesta a una risorsa 106 e la risorsa restituisce i dati forniti. Generalmente, una o più delle interfacce di comunicazione 1062 possono comprendere anche una rispettiva interfaccia master. Per esempio, una tale interfaccia master può essere utile nel caso in cui la risorsa debba iniziare una comunicazione al fine di scambiare dati mediante una richiesta (di lettura e/o scrittura) con un altro circuito connesso al sistema di comunicazione 114, come una risorsa 106 o un core di elaborazione 102. Per esempio, a questo scopo, il sistema di comunicazione 114 può comprendere in effetti un Bus ad Alte Prestazioni (AHB, "High-performance Bus") AMBA (Advanced Microcontroller Bus Architecture), e un Bus Periferico Avanzato (APB, "Advanced Peripheral Bus") usato per connettere le risorse/periferiche 106 al bus AHB AMBA.

Spesso tali sistemi di elaborazione 10 comprendono anche uno o più controllori di Accesso Diretto in Memoria (DMA, "Direct-Memory-Access") 110. Per esempio, come rappresentato nella Figura 3, un controllore DMA 110 può essere usato per scambiare direttamente dati con una memoria, per es., la memoria 104b, in base a richieste ricevute da una risorsa 106. Per esempio, in questo modo, un'interfaccia di comunicazione IF può leggere direttamente i dati (mediante il controllore DMA 110) dalla memoria 104b e può trasmettere questi dati, senza dovere scambiare ulteriori dati con un'unità di elaborazione 102. Generalmente, un controllore DMA 110 può comunicare con la memoria o le memorie mediante il sistema di comunicazione 114 o mediante uno o più canali di comunicazione dedicati.

A questo riguardo, indipendentemente dalla complessità del sistema di elaborazione 10 (per es., rispetto al numero dei core di elaborazione 102 e/o al numero e al tipo delle risorse 106), un tipico sistema di elaborazione 10 comprende anche un circuito di raccolta dei guasti e di gestione degli errori 120.

Per esempio, la domanda di brevetto europeo n. EP 3 534 261 A1 descrive possibili forme di attuazione di un circuito di raccolta dei guasti e di gestione degli errori 120, che è incorporato qui tramite citazione a questo scopo.

Specificamente, come rappresentato nella Figura 4, almeno uno dei circuiti 102, 104 e 106 può generare uno o più segnali di errore  $ERR_1, \dots, ERR_m$ . Per esempio, tali segnali di errore  $ERR$  possono essere generati da almeno uno tra:

- una memoria 104 che supporta una funzione di rilevazione di errori e di correzione opzionale, che genera un segnale di errore  $ERR_1$  quando i dati letti dalla memoria 104 contengono errori e/o quando i dati non hanno potuto essere scritti nella memoria;

- un core di elaborazione 102 configurato per generare un segnale di errore  $ERR_2$  in risposta a un malfunzionamento hardware e/o software; e

- un'interfaccia di comunicazione configurata per generare un segnale di errore  $ERR_3$ , corrispondente a un segnale di errore hard indicativo di un malfunzionamento hardware e/o a un segnale di errore soft indicativo di un errore di trasmissione di dati.

Nell'esempio considerato, i vari segnali di errore  $ERR_1, \dots, ERR_m$  sono forniti al circuito di raccolta dei guasti e di gestione degli errori 120. In risposta ai

segnali di errore  $ERR_1, \dots, ERR_m$ , il circuito di raccolta dei guasti e di gestione degli errori 120 può eseguire varie operazioni.

Per esempio, il circuito di raccolta dei guasti e di gestione degli errori 120 può essere configurato per generare almeno uno tra:

- un segnale di interruzione ("interrupt") IRQ fornito a un core di elaborazione 102;

- un segnale di richiesta di reset RST fornito a un circuito di gestione di reset del sistema di elaborazione 10;

- un segnale ET fornito a un terminale EP del sistema di elaborazione 10, per es., al fine di segnalare l'errore a un circuito esterno; e

- un segnale SET usato per impostare il livello di uscita di uno o più terminali critici per la sicurezza SCP del sistema di elaborazione 10.

Specificamente, a causa di un errore, i circuiti del sistema di elaborazione 10 possono non funzionare correttamente, generando eventualmente segnali scorretti ai pin/pad del sistema di elaborazione 10. Alcuni dei pin/pad del sistema di elaborazione 10a possono così essere pin/pad critici per la sicurezza, cioè, pin/pad che possono generare situazioni critiche quando pilotati scorrettamente. Per esempio, nella Figura 4 è rappresentato schematicamente un primo pin critico per la sicurezza  $SCP_1$ , che è pilotato da un core di elaborazione 102, e un secondo pin critico per la sicurezza  $SCP_2$ , che è pilotato da una risorsa/periferica 106, come un'interfaccia di comunicazione o un dispositivo di pilotaggio a semi-ponte PWM.

Generalmente, ciascun pin/pad di ingresso/uscita del sistema di elaborazione 10 ha associato di solito un rispettivo circuito di pilotaggio IO, che è configurato per pilotare il rispettivo pin/pad in funzione del segnale ricevuto dal rispettivo blocco, per es., il sistema di elaborazione 102 e le risorse hardware 106. Generalmente, tra i circuiti di pilotaggio IO e i blocchi del sistema di elaborazione 10a può anche essere disposta una logica dedicata, come uno o più multiplexer, che permette una configurazione della mappatura dei pin.

Di conseguenza, in linea con la descrizione del documento EP 3 534 261 A1, il circuito di pilotaggio IO di un pin/pad critico per la sicurezza SCP può essere configurato per impostare il livello di uscita del rispettivo pin a un dato stato di sicurezza in risposta a un segnale SET. Il livello di uscita, come uno stato di alta impedenza o un dato livello logico (alto o basso), può dipendere dalle necessità delle applicazioni specifiche. Preferibilmente, un tale "stato di sicurezza" è conforme alla specifica ISO2626.

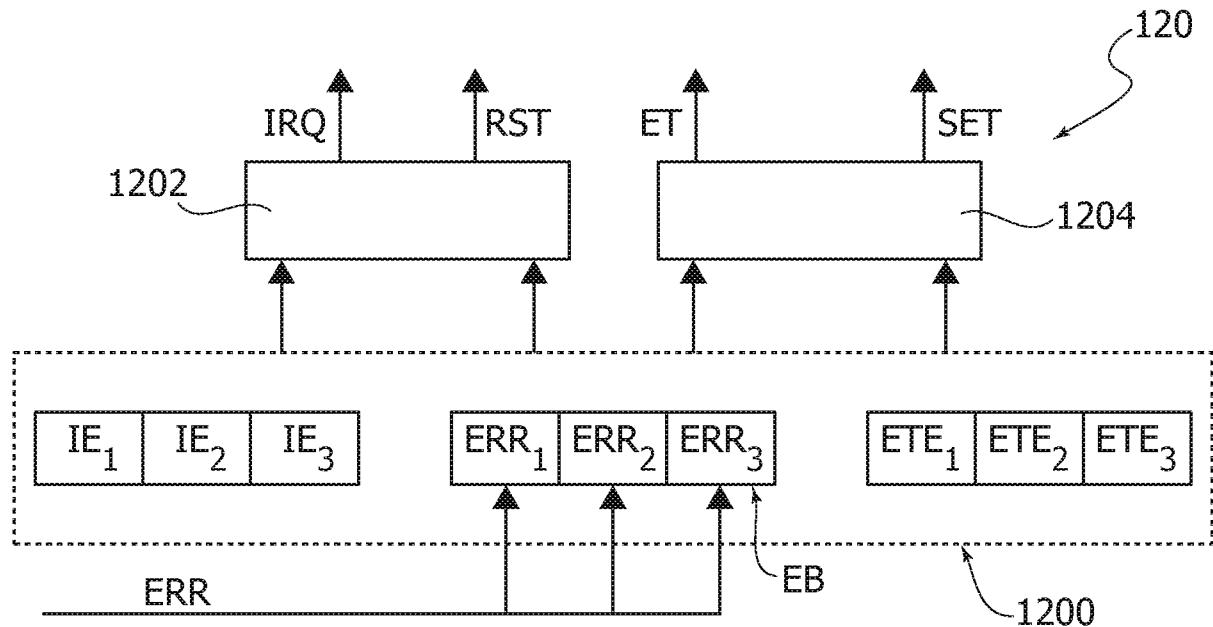

La Figura 5 rappresenta una possibile implementazione del circuito di raccolta dei guasti e di gestione degli errori 120.

Nell'esempio considerato, il circuito di raccolta dei guasti e di gestione degli errori 120 comprende un registro 1200. Specificamente, nell'esempio considerato, il registro 1200 comprende uno o più bit di errore EB per memorizzare il valore dei segnali di errore ERR. Per esempio, considerando il caso di esempio di tre segnali di errore  $ERR_1..ERR_3$ , il registro 1200 può comprendere un numero corrispondente di bit di errore EB.

Nell'esempio considerato, il circuito di raccolta dei guasti e di gestione degli errori 120 comprende un circuito di reazione interna 1202. Specificamente, il circuito di reazione interna 1202 può essere configurato per generare il segnale di interrupt IRQ e/o il segnale di richiesta di reset RST in funzione del contenuto dei bit di errore EB del registro 1200. I bit di errore EB sono puramente opzionali e il circuito di reazione interna 1202 può anche generare direttamente il segnale di interrupt IRQ e/o il segnale di richiesta di reset RST in funzione del segnale (dei segnali) di errore ERR.

Similmente, il circuito di raccolta dei guasti e di gestione degli errori 120 comprende un circuito di reazione esterna 1204. Specificamente, il circuito di reazione esterna 1204 può essere configurato per generare il segnale di innesco ("trigger") di errore ET e/o il segnale SET in funzione del contenuto dei bit di errore EB del registro 1200. Di nuovo, i bit di errore EB sono puramente opzionali e il circuito di reazione esterna 1204 può anche generare direttamente il segnale ET e/o il segnale SET in funzione del segnale (dei segnali) di errore ERR.

In generale, il comportamento dei circuiti di reazione 1202 e/o 1204 può anche essere programmabile, per es., impostando uno o più bit di configurazione nel registro 1200. Per esempio, nell'esempio considerato, il registro 1200 comprende:

- un rispettivo bit di abilitazione di interrupt IE per ciascuno dei segnali di errore  $ERR_1..ERR_3$ , cioè, il segnale di interrupt IRQ è asserito quando anche il rispettivo bit di abilitazione di interrupt IE di un segnale di errore ERR asserito è asserito;

- un rispettivo bit di abilitazione di innesco di errore ETE per ciascuno dei segnali di errore  $ERR_1..ERR_3$ , cioè, il segnale di innesco di errore ET è asserito quando anche il rispettivo bit di abilitazione di innesco di errore ETE di un segnale di errore ERR asserito è asserito.

Similmente, il registro 1200 può comprendere rispettivi bit di abilitazione di reset per il segnale di richiesta di reset REQ e/o rispettivi bit di abilitazione per il segnale di sicurezza SET.

Al fine di semplificare lo scambio di dati tra l'unità di elaborazione 102 e il registro 1200, il registro 1200 può essere indirizzabile direttamente dall'unità di elaborazione 102, il che è rappresentato schematicamente nella Figura 3, dove il circuito di raccolta dei guasti e di gestione degli errori 120 è connesso al sistema di comunicazione 114.

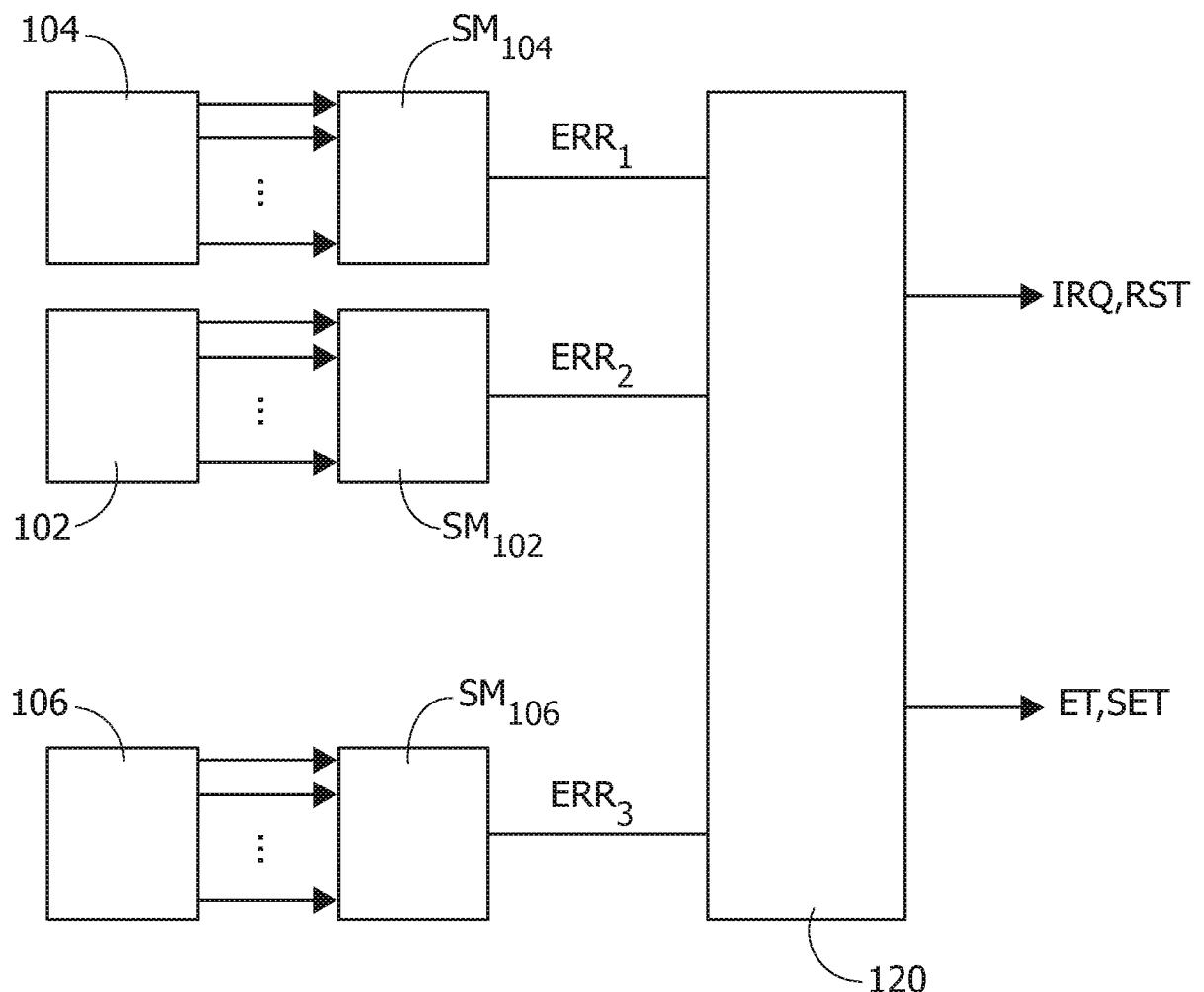

Tipicamente, come rappresentato nella Figura 6, i segnali di errore ERR hardware sono generati da circuiti di monitoraggio di sicurezza SM dedicati. Per esempio, tali circuiti di monitoraggio di sicurezza possono comprendere circuiti logici combinatori e/o sequenziali, che monitorano il funzionamento di un dato circuito. Generalmente, tali circuiti di monitoraggio di sicurezza SM possono anche comprendere componenti analogici, per es., al fine di rilevare una condizione di fuori campo ("out-of-range") per un segnale analogico, come una tensione di alimentazione interna o un segnale indicativo della temperatura di funzionamento del sistema di elaborazione o di uno specifico circuito del sistema di elaborazione.

Per esempio, la Figura 6 rappresenta un circuito di monitoraggio di sicurezza  $SM_{104}$  configurato per monitorare uno o più segnali della memoria 104, un circuito di

monitoraggio di sicurezza SM<sub>102</sub> configurato per monitorare uno o più segnali di un core di elaborazione 102 e un circuito di monitoraggio di sicurezza SM<sub>106</sub> configurato per monitorare uno o più segnali di una risorsa/periferica 106. Generalmente, il circuito di monitoraggio di sicurezza può anche essere integrato nel rispettivo circuito.

Di conseguenza, tipicamente ciascun circuito di monitoraggio di sicurezza SM monitora uno o più segnali generati dal e/o forniti al circuito associato, e determina se il comportamento del segnale (dei segnali) è normale o indica un errore. In generale, le operazioni effettuate da un dato circuito di monitoraggio di sicurezza SM dipendono dal circuito associato e possono comprendere, per es.:

- un'analisi combinatoria, per es., combinando i segnali del circuito associato al fine di determinare se i livelli di segnale sono congruenti;

- un'analisi sequenziale, per es., confrontando l'evoluzione nel tempo di uno o più segnali con uno o più segnali di riferimento;

- un'analisi di uno o più segnali analogici, per es., confrontando il valore di un segnale analogico con uno o più valori di riferimento; o

- una combinazione delle analisi precedenti al fine di implementare un'analisi di comportamento anomalo più complessa.

Per esempio, il circuito di monitoraggio di sicurezza SM<sub>104</sub> può comprendere un circuito di rilevazione di errori della memoria 104, che calcola (mediante operazioni logiche combinatorie e opzionalmente sequenziali) un codice di correzione di errore per i dati letti dalla memoria e confronta (mediante operazioni logiche combinatorie) il

codice di correzione di errore calcolato con un codice di correzione di errore letto dalla memoria.

Di conseguenza, in risposta alla determinazione di un comportamento anomalo, il circuito di monitoraggio di sicurezza SM può asserire un rispettivo segnale di errore ERR, che segnala l'errore al sistema di raccolta dei guasti 120.

In considerazione di ciò che precede, è chiaro che anche i circuiti di monitoraggio di sicurezza possono essere circuiti complessi, che possono essere soggetti a malfunzionamenti. Questo si applica in particolare ai circuiti di monitoraggio di sicurezza per le memorie o ad altri circuiti di monitoraggio di sicurezza comprendenti un circuito configurato per verificare un codice di correzione di errore (ECC, "Error Correction Code").

#### Sintesi

In considerazione di quanto precede, uno scopo delle varie forme di attuazione della presente descrizione è di fornire soluzioni per monitorare il funzionamento di un circuito di monitoraggio di sicurezza comprendente un circuito configurato per verificare un codice di correzione di errore (ECC).

Secondo una o più forme di attuazione, uno o più degli scopi precedenti sono raggiunti per mezzo di un sistema di elaborazione avente le caratteristiche esposte specificamente nelle rivendicazioni che seguono. Le forme di attuazione concernono inoltre un relativo circuito integrato, dispositivo e procedimento.

Le rivendicazioni sono parte integrante dell'insegnamento tecnico della descrizione qui fornita.

Come menzionato in precedenza, varie forme di attuazione della presente descrizione sono relative a un

sistema di elaborazione, per es., implementato in un circuito integrato, come un microcontrollore. Specificamente, il sistema di elaborazione comprende un circuito configurato per fornire un dato numero  $N$  di bit di dati e un dato numero  $K$  di bit di codice di correzione di errore (ECC). Il circuito ha associato o comprende un circuito di rilevazione di errori.

Specificamente, in varie forme di attuazione, il circuito di rilevazione di errori è configurato per ricevere i bit di dati e i bit di ECC. In seguito, il circuito di rilevazione di errori calcola ulteriori bit di ECC in funzione dei bit di dati secondo il codice ECC usato. In varie forme di attuazione, il codice ECC è atto a correggere fino a un dato numero massimo di bit scorretti. Per esempio, in varie forme di attuazione, il codice ECC può essere un Codice di Correzione di Errore Singolo (SEC, "Single-Error Correct") Rilevazione di Errore Doppio (DED, "Double-Error Detect").

In varie forme di attuazione, il circuito di rilevazione di errori genera quindi una sindrome confrontando i bit di ECC calcolati con i bit di ECC ricevuti, in cui la sindrome ha  $K$  bit. Di conseguenza, il circuito di rilevazione di errori può confrontare la sindrome con una pluralità di sindromi di riferimento indicative di errori correggibili. Specificamente, il circuito di rilevazione di errori è configurato per confrontare la sindrome almeno con  $N + K$  sindromi di riferimento di ribaltamento di bit singolo, in cui ciascuna sindrome di riferimento di ribaltamento di bit singolo è associata a un rispettivo errore di ribaltamento di bit singolo. Di conseguenza, in risposta alla determinazione che la sindrome corrisponde a una sindrome di riferimento

di ribaltamento di bit singolo, il circuito di rilevazione di errori può asserire un primo segnale di errore, per es., indicativo di un errore correggibile. Inoltre, il circuito di rilevazione di errori può asserire un bit di una firma di ribaltamento di bit corrispondente all'errore di ribaltamento di bit singolo indicato dalla rispettiva sindrome di riferimento di ribaltamento di bit singolo. Di conseguenza, la firma di ribaltamento di bit ha un dato numero di  $N + K$  bit e indica la posizione di uno o più bit scorretti nei bit di dati e nei bit di ECC.

Per esempio, in varie forme di attuazione, il circuito può comprendere un circuito di correzione di errore. Specificamente, quando il primo segnale di errore è asserito, il circuito di correzione di errore può generare bit di dati corretti invertendo ciascun bit dei bit di dati per il quale il corrispondente bit della firma di ribaltamento di bit è asserito.

Di conseguenza, il circuito può essere, per esempio, un controllore di memoria del sistema di elaborazione. Specificamente, un tale controllore di memoria può ricevere una richiesta di lettura da un microprocessore e/o da un controllore DMA del sistema di elaborazione, in cui la richiesta di lettura comprende un dato indirizzo. Di conseguenza, il controllore di memoria può leggere il dato numero  $N$  di bit di dati e il dato numero  $K$  di bit di ECC dal dato indirizzo associato a una memoria trattata dal controllore di memoria. Quando il primo segnale di errore è deasserito, il controllore di memoria può quindi fornire i bit di dati al microprocessore e/o al controllore DMA. Per contro, quando il primo segnale di errore è asserito, il controllore di memoria può fornire i bit di dati corretti al microprocessore e/o al controllore DMA.

In varie forme di attuazione, il sistema di elaborazione comprende inoltre un circuito di test configurato per fornire, durante una modalità di test, una sequenza di configurazioni ("pattern") al circuito di rilevazione di errori, ciascuna configurazione comprendendo bit di dati e bit di ECC, e monitorare il primo segnale di errore e la firma di ribaltamento di bit rispettivi.

Specificamente, in varie forme di attuazione, il circuito di test è configurato per ottenere una prima configurazione, la prima configurazione corrispondendo a una data sequenza di bit di dati e di bit di ECC calcolati in funzione dei bit di dati secondo lo schema/codice ECC usato, cioè, la prima configurazione non comprende errori di ECC. Per esempio, la prima configurazione può essere cablata in hardware ("hard-wired") o programmabile. In seguito, il circuito di test fornisce la prima configurazione al circuito di rilevazione di errori e verifica se il primo segnale di errore è deasserito e tutti i bit della firma di ribaltamento di bit sono deasseriti. Di conseguenza, il circuito di test può asserire uno o più segnali di errore in risposta alla determinazione che il primo segnale di errore è asserito e/o almeno un bit della firma di ribaltamento di bit è asserito.

In varie forme di attuazione, il circuito di test ottiene una sequenza di  $N + K$  ulteriori firme di ribaltamento di bit, ciascuna ulteriore firma di ribaltamento di bit avendo asserito un bit singolo. Inoltre, il circuito di test ottiene per ciascuna ulteriore firma di ribaltamento di bit una rispettiva seconda configurazione, in cui ciascuna seconda configurazione corrisponde a una configurazione che ha un bit singolo ribaltato rispetto a una configurazione di riferimento

nelle posizioni del bit singolo asserito della rispettiva ulteriore firma di ribaltamento di bit. La configurazione di riferimento corrisponde a una data sequenza di bit di dati e di bit di ECC calcolati in funzione dei rispettivi bit di dati secondo il dato schema di ECC, per cui ciascuna seconda configurazione corrisponde a una configurazione con un errore di bit singolo correggibile. Per esempio, la configurazione di riferimento per le seconde configurazioni può corrispondere alla prima configurazione.

In varie forme di attuazione, il circuito di test è configurato per generare le  $N + K$  seconde configurazioni, per es., mediante un circuito logico sequenziale, effettuando le seguenti fasi per ciascuna seconda configurazione. Dapprima, il circuito di test ottiene la configurazione di riferimento e genera la rispettiva ulteriore firma di ribaltamento di bit, in cui l'ulteriore firma di ribaltamento di bit ha asserito un bit singolo. In seguito, il circuito di test genera la rispettiva seconda configurazione invertendo il bit della configurazione di riferimento per cui il corrispondente bit dell'ulteriore firma di ribaltamento di bit è asserito. Per esempio, il circuito di test può generare tale ulteriore firma di ribaltamento di bit mediante un contatore e un decodificatore one-hot, o un registro a scorrimento avente un bit singolo asserito. Di conseguenza, in varie forme di attuazione, il bit singolo è posizionato in tutte le posizioni possibili della firma di ribaltamento di bit, cioè, al circuito di rilevazione di errori sono fornite  $N + K$  seconde configurazioni.

In varie forme di attuazione, il circuito di test fornisce ciascuna seconda configurazione al circuito di rilevazione di errori e verifica se il primo segnale di

errore è asserito e la firma di ribaltamento di bit corrisponde alla rispettiva ulteriore firma di ribaltamento di bit. Di conseguenza, il circuito di test può asserire uno o più segnali di errore in risposta alla determinazione che il primo segnale di errore è deasserito e/o la firma di ribaltamento di bit non corrisponde alla rispettiva ulteriore firma di ribaltamento di bit.

In varie forme di attuazione, il codice ECC usato può anche essere atto a rilevare un dato numero massimo di bit scorretti, in cui il dato numero massimo di bit scorretti rilevabili corrisponde al dato numero di bit scorretti correggibili più uno. Per esempio, come menzionato in precedenza, il codice ECC può essere un codice SECDED. In questo caso, il circuito di rilevazione di errori può essere configurato per impostare un secondo segnale di errore a un dato livello logico in risposta alla determinazione che i bit di dati e i bit di ECC hanno il dato numero massimo di bit scorretti rilevabili.

In questo caso, il circuito di test può anche ottenere una terza configurazione, in cui la terza configurazione corrisponde a una data sequenza di bit di dati e di bit di ECC che ha un dato numero di bit ribaltati rispetto alla prima configurazione o alla configurazione di riferimento, in cui il dato numero di bit invertiti/ribaltati corrisponde al numero massimo di bit scorretti rilevabili, per cui la terza configurazione rappresenta una configurazione con un errore non correggibile. Il circuito di test fornisce quindi la terza configurazione al circuito di rilevazione di errori e verifica se il primo segnale di errore è asserito, il secondo segnale di errore è impostato al dato livello logico e tutti i bit della firma di ribaltamento di bit sono deasseriti. Di conseguenza, il

circuito di test può asserire l'uno o più segnali di errore in risposta alla determinazione che il primo segnale di errore è deasserito, il secondo segnale di errore non è impostato al dato livello logico e/o almeno un bit della firma di ribaltamento di bit è asserito.

In varie forme di attuazione, lo stesso circuito di test può testare più circuiti di correzione di errore. Specificamente, in varie forme di attuazione, la pluralità di circuiti di rilevazione di errori riceve in parallelo la sequenza di configurazioni fornita dal circuito di test. In questo caso, può essere usata una pluralità di porte logiche OR per generare un primo segnale di errore combinato e una prima firma di ribaltamento di bit combinata combinando, rispettivamente, i primi segnali di errore e le firme di ribaltamento di bit forniti dalla pluralità di circuiti di rilevazione di errori. Similmente, può essere usata una pluralità di porte logiche AND per generare un secondo segnale di errore combinato e una seconda firma di ribaltamento di bit combinata combinando, rispettivamente, i primi segnali di errore e le firme di ribaltamento di bit forniti dalla pluralità di circuiti di rilevazione di errori.

In questo caso, il circuito di test è configurato per asserire l'uno o più segnali di errore quando uno qualsiasi tra i segnali di errore combinati o la firma di ribaltamento di bit combinata non soddisfa le verifiche precedenti, cioè, il circuito di test asserisce l'uno o più segnali di errore in risposta alla determinazione che:

- per la prima configurazione, il primo segnale di errore combinato è asserito e/o almeno un bit della prima firma di ribaltamento di bit combinata è asserito, e/o il secondo segnale di errore combinato è asserito e/o almeno

un bit della seconda firma di ribaltamento di bit combinata è asserito, e/o

- per ciascuna delle seconde configurazioni, il primo segnale di errore combinato è deasserito e/o la prima firma di ribaltamento di bit combinata non corrisponde alla rispettiva ulteriore firma di ribaltamento di bit, e/o il secondo segnale di errore combinato è deasserito e/o la seconda firma di ribaltamento di bit combinata non corrisponde alla rispettiva ulteriore firma di ribaltamento di bit.

#### Breve descrizione delle figure

Forme di attuazione della presente descrizione saranno ora descritte con riferimento ai disegni annessi, che sono forniti puramente a titolo di esempio non limitativo, e nei quali:

- la Figura 1 rappresenta un esempio di un sistema elettronico comprendente una pluralità di sistemi di elaborazione;

- le Figure 2 e 3 rappresentano esempi di sistemi di elaborazione;

- la Figura 4 rappresenta un esempio di un sistema di elaborazione comprendente un circuito di raccolta dei guasti e di gestione degli errori;

- la Figura 5 rappresenta un esempio del circuito di raccolta dei guasti e di gestione degli errori della Figura 4;

- la Figura 6 rappresenta un esempio della connessione tra una pluralità di circuiti di monitoraggio di sicurezza e il circuito di raccolta dei guasti e di gestione degli errori;

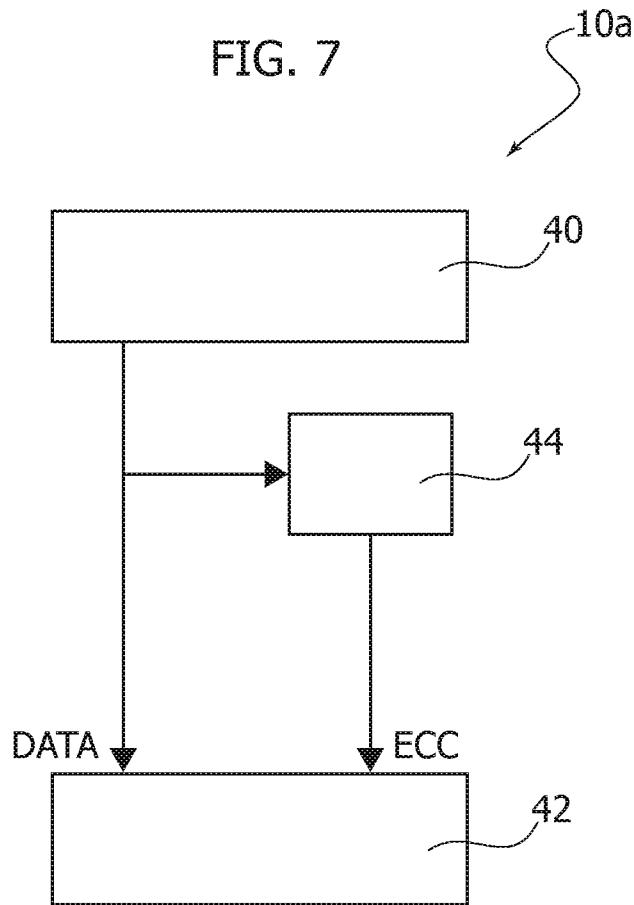

- la Figura 7 rappresenta una forma di attuazione di un sistema di elaborazione configurato per generare bit di ECC in funzione di bit di dati;

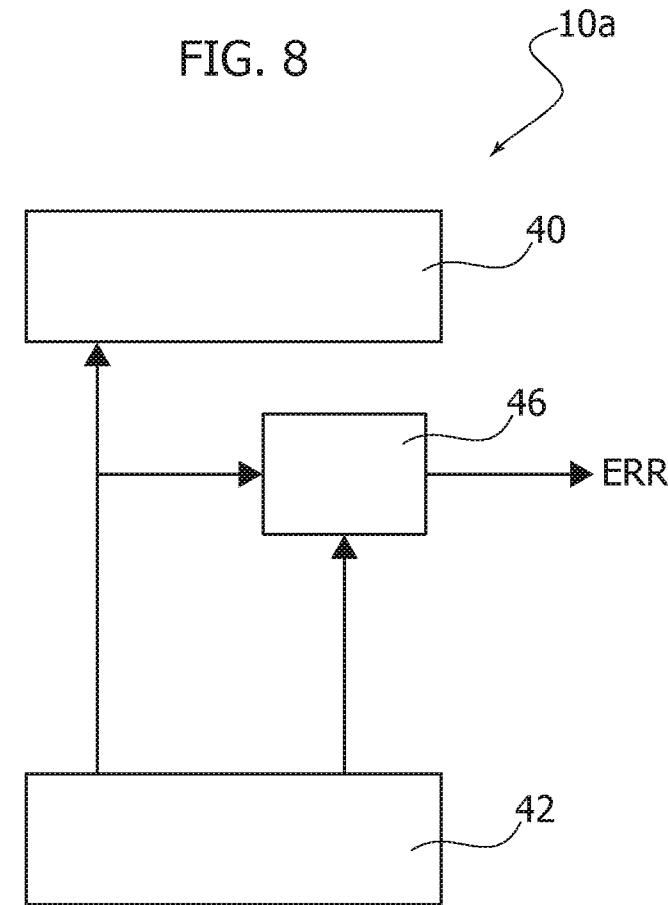

- la Figura 8 rappresenta una forma di attuazione di un sistema di elaborazione configurato per usare i bit di ECC al fine di rilevare e opzionalmente correggere gli errori nei bit di dati;

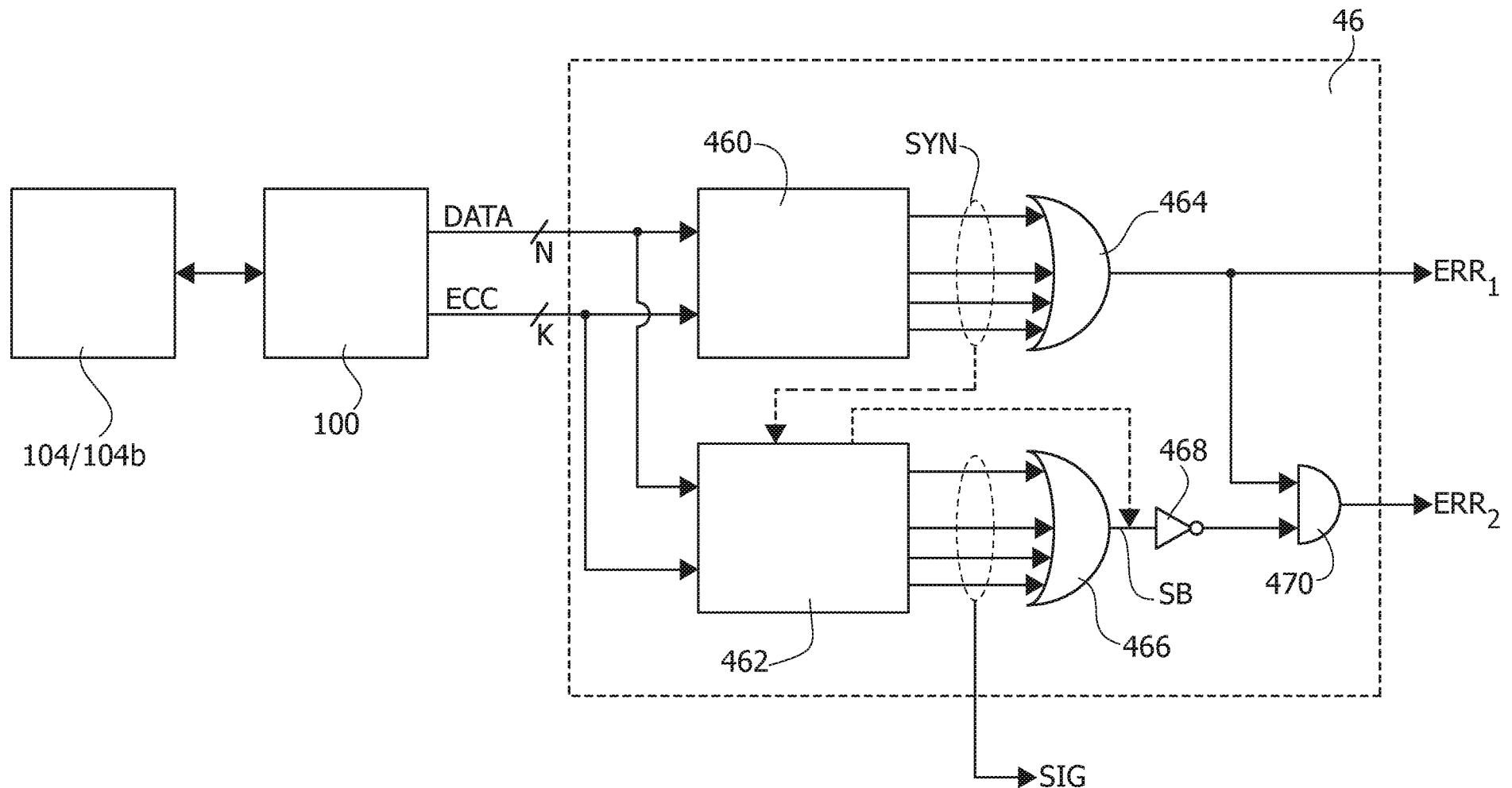

- la Figura 9 rappresenta una forma di attuazione di un circuito di rilevazione di errori atto a essere usato nel sistema di elaborazione della Figura 8;

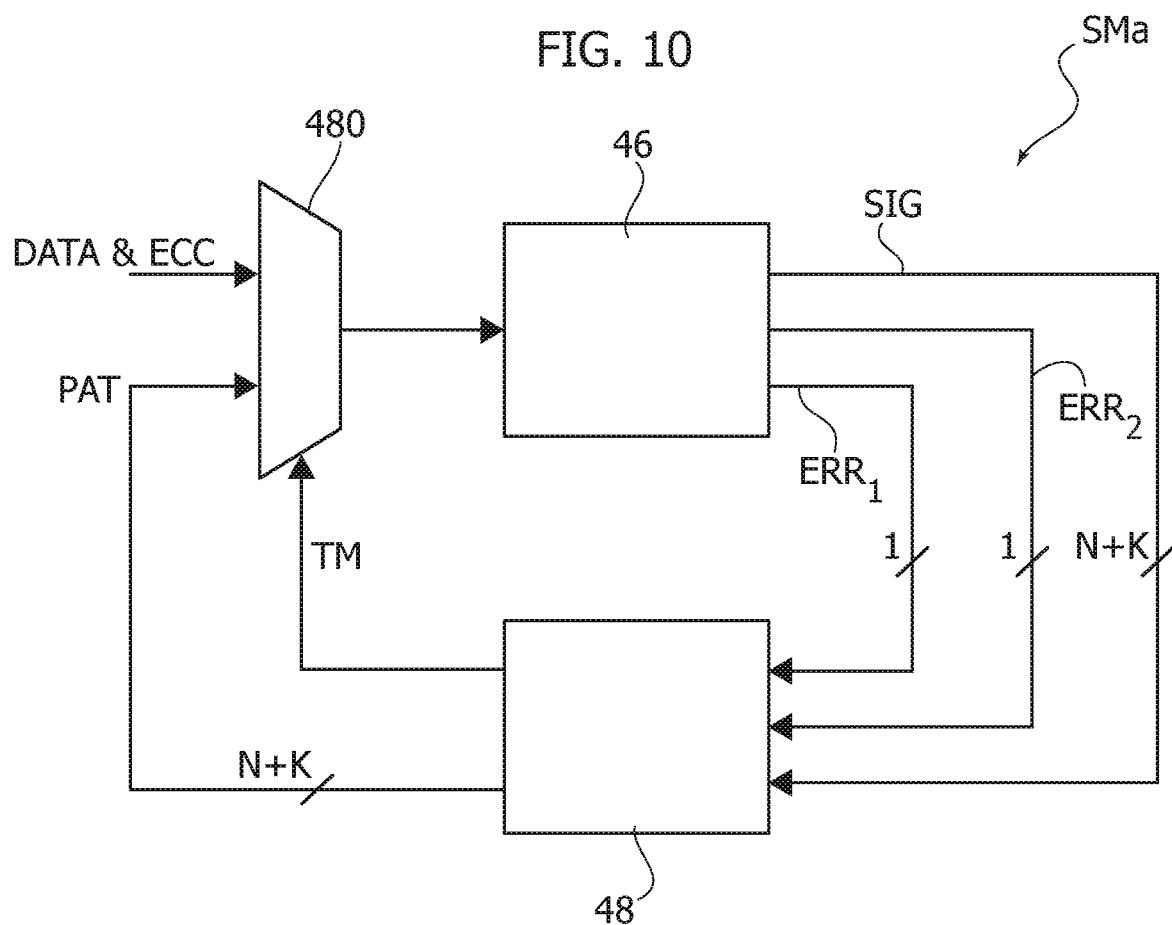

- la Figura 10 rappresenta una forma di attuazione di un circuito di monitoraggio di sicurezza comprendente un circuito di rilevazione di errori e un circuito di test configurato per testare la rilevazione di errori;

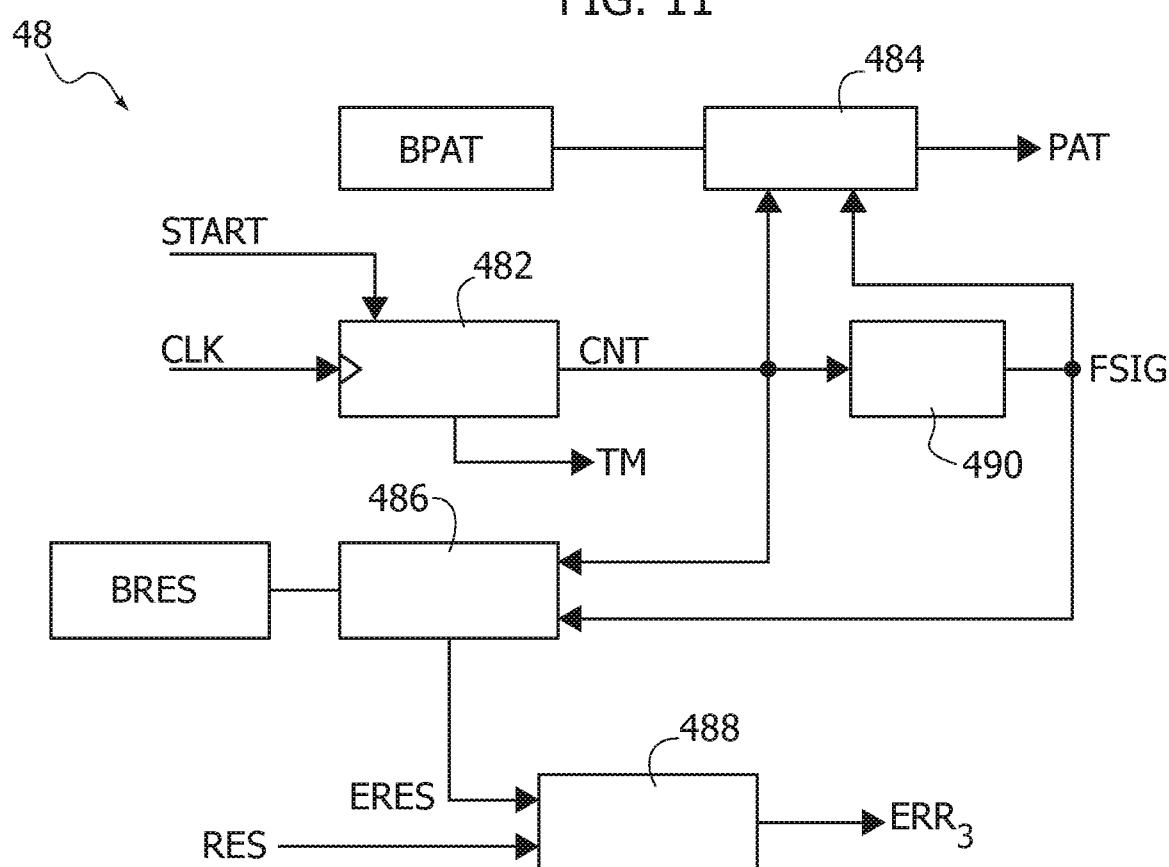

- la Figura 11 rappresenta una forma di attuazione del circuito di test della Figura 10;

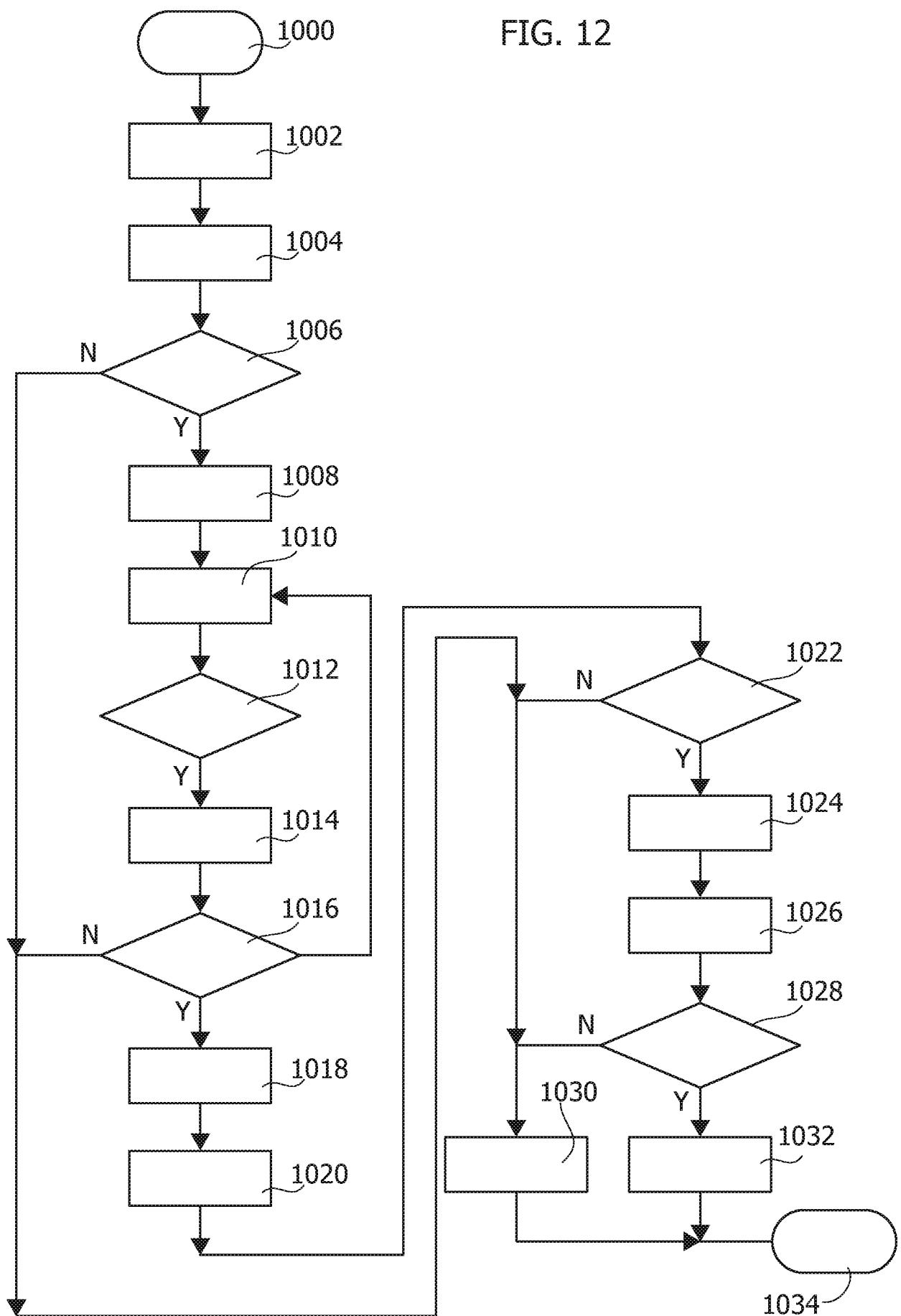

- la Figura 12 rappresenta una forma di attuazione del funzionamento del circuito di test della Figura 10; e

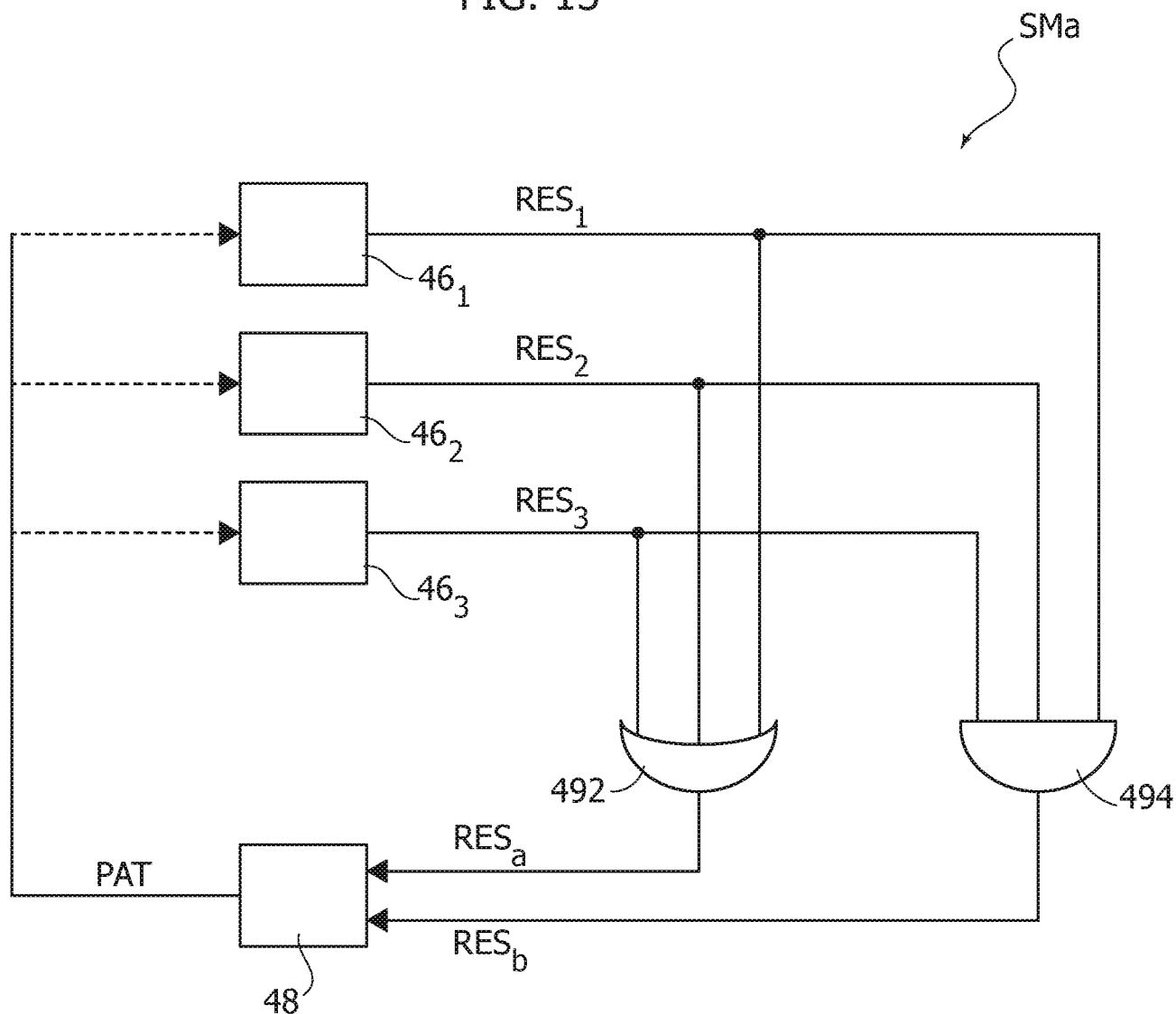

- la Figura 13 rappresenta una seconda forma di attuazione di un circuito di test configurato per testare una pluralità di circuiti di rilevazione di errori.

#### Descrizione Dettagliata

Nella descrizione che segue, sono illustrati numerosi dettagli specifici, allo scopo di fornire una comprensione approfondita delle forme di attuazione. Le forme di attuazione possono essere attuate senza uno o più dei dettagli specifici o con altri procedimenti, componenti, materiali, ecc. In altri casi, operazioni, materiali o strutture ben note non sono rappresentate o descritte in dettaglio per evitare di rendere poco chiari certi aspetti delle forme di attuazione.

Un riferimento a "una forma di attuazione" in tutta questa descrizione intende indicare che una particolare configurazione, struttura, o caratteristica descritta con riferimento alla forma di attuazione è compresa in almeno una forma di attuazione. Così, le frasi come "in una forma di attuazione" o simili che compaiono in vari punti in tutta questa descrizione non fanno necessariamente riferimento tutte alla stessa forma di attuazione. Inoltre, particolari conformazioni, strutture o caratteristiche possono essere combinate in un modo adeguato qualsiasi in una o più forme di attuazione.

I riferimenti usati qui sono forniti semplicemente per convenienza e non definiscono l'ambito o il significato delle forme di attuazione.

Nelle Figure da 7 a 13 che seguono, le parti, gli elementi o i componenti che sono già stati descritti con riferimento alle Figure da 1 a 6 sono indicati con gli stessi riferimenti usati precedentemente in tali Figure; la descrizione di tali elementi descritti precedentemente non sarà ripetuta in seguito al fine di non rendere troppo pesante la presente descrizione dettagliata.

Come menzionato in precedenza, varie forme di attuazione della presente descrizione sono relative a un sistema di elaborazione configurato per monitorare il funzionamento di un circuito di monitoraggio di sicurezza comprendente un circuito di rilevazione di errori, cioè, un circuito configurato per verificare un codice di correzione di errore (ECC). Specificamente, varie forme di attuazione sono relative a un circuito di monitoraggio di sicurezza SMe configurato per testare un tale circuito di ECC.

La Figura 7 e la Figura 8 rappresentano un generico sistema di elaborazione 10a comprendente un dispositivo

master 40 e un dispositivo slave 42, in cui il dispositivo master 40 e il dispositivo slave 42 usano un tradizionale schema di protezione di ECC.

Specificamente, nella Figura 7 il circuito master 40 trasmette dati DATA al dispositivo slave 42. Specificamente, il dispositivo slave 42 riceve i bit di dati DATA e i bit di codice di correzione di errore ECC aggiuntivi generati da un circuito di generazione di codice di correzione di errore 44 configurato per generare i bit ECC in funzione dei bit di dati DATA.

Per esempio, in varie forme di attuazione, il dispositivo master 40 può essere un core di elaborazione 102, in particolare un microprocessore 1020, o un controllore DMA 110. Per contro, il dispositivo slave 42 può essere una memoria come una memoria non volatile 104 o una memoria volatile 104b, per es., una memoria RAM. Per esempio, il circuito di generazione di codice di correzione di errore 44 può essere integrato nel controllore di memoria 100 della memoria 42. Per una descrizione generale di questi circuiti, e di un rispettivo sistema di elaborazione 10, si può fare riferimento alla descrizione precedente delle Figure da 1 a 3. Per esempio, il microprocessore 1020 o il controllore DMA 110 (dispositivo master 40) può inviare una richiesta di scrittura comprendente i dati DATA mediante il sistema di comunicazione 114 al controllore di memoria 100. Il controllore di memoria 100 può quindi calcolare, mediante il rispettivo circuito di generazione di codice di correzione di errore 44, i bit ECC e può scrivere i bit di dati DATA e i bit ECC nella memoria, per es., a un indirizzo di memoria incluso nella richiesta di scrittura.

Per contro, nella Figura 8 il circuito master 40 riceve dati DATA forniti dal dispositivo slave 42. Specificamente, il dispositivo slave 42 fornisce i bit di dati DATA e i bit di codice di correzione di errore ECC aggiuntivi.

Per esempio, a questo scopo, il microprocessore 1020 o il controllore DMA 110 (dispositivo master 40) può inviare una richiesta di lettura mediante il sistema di comunicazione 114 al controllore di memoria 100. Il controllore di memoria 100 può quindi leggere i bit di dati DATA e i bit ECC dalla memoria, per es., da un indirizzo di memoria incluso nella richiesta di lettura, e può trasmettere i bit di dati DATA al microprocessore 1020 o al controllore DMA 110.

Tuttavia, come rappresentato nella Figura 8, in questo caso, un circuito di rilevazione di errori 46 è configurato per verificare i bit DATA e ECC, e generare eventualmente uno o più segnali di errore ERR. Per esempio, l'uno o più segnali di errore ERR possono essere forniti al circuito master 40 e/o a un circuito di raccolta dei guasti e di gestione degli errori 120. Si può fare riferimento alla descrizione delle Figure da 4 a 6 a questo riguardo.

Per esempio, il circuito di rilevazione di errori 46 può essere integrato nel controllore di memoria 100. Specificamente, nel caso di un semplice circuito di rilevazione di errori 46, questo circuito verifica solo la correttezza dei bit DATA e ECC. Tuttavia, il circuito di rilevazione di errori 46 può anche fornire informazioni concernenti la posizione dell'errore, che può così essere usata da un circuito di correzione di errore per correggere gli errori nei bit di dati DATA. Generalmente, il circuito di correzione di errore può essere integrato con il

circuito di rilevazione di errori in un circuito di rilevazione di errori e di correzione 46, o il circuito di correzione di errore può essere un circuito separato. Di conseguenza, il circuito 46 può fornire effettivamente bit di dati DATA corretti al dispositivo master 40.

Inoltre, tali schemi di ECC possono anche essere usati per le comunicazioni scambiate mediante il sistema di comunicazione 114. Per esempio, un master del bus, come l'interfaccia 1022 può aggiungere i bit di ECC a una richiesta inviata al sistema di comunicazione 1144. Di conseguenza, il circuito slave di ricezione, come l'interfaccia slave 1062, può verificare i bit di ECC al fine di rilevare errori nella richiesta trasmessa. Generalmente, tali bit di ECC possono essere verificati mediante un rispettivo circuito di rilevazione di errori per ciascuna delle informazioni di indirizzo, di dati e di controllo di una richiesta, o una combinazione di queste informazioni.

Generalmente, il numero K di bit di ECC dipende dal numero N di bit di dati e dallo schema di ECC, per es., quanti bit possono essere riparati. Così, a seconda della complessità del codice di correzione di errore (ECC) implementato, il circuito 46 è attivo a rilevare fino a un dato numero di bit ribaltati ed eventualmente a ripararli. Per esempio, nel campo dei microcontrollori atti a essere usati nel mercato automotive, lo schema di ECC adottato è di solito attivo a rilevare fino a due bit erronei e a riparare un bit erroneo, cosiddetto codice di Correzione di Errore Singolo (SEC) Rilevazione di Errore Doppio (DED). Per una descrizione generale dei codici di rilevazione di errori e opzionalmente di correzione, si può fare riferimento alla corrispondente pagina Web "Error detection

*and correction*" di Wikipedia, per es., la versione del 6 maggio 2021, il cui contenuto è incorporato qui tramite citazione.

Come menzionato in precedenza, le soluzioni qui descritte possono essere applicate in una qualsiasi situazione in cui sono usati dei bit di codice di correzione di errore ECC, per es., nel contesto di un Codice SECDED, come è il caso, per es., per un microcontrollore basato su ARM Cortex R52. Per esempio, una possibile implementazione di un codice SECDED è descritta nella Nota Applicativa XAPP383 "Single Error Correction and Double Error Detection (SECDED) with CoolRunner-II™ CPLDs", v1.1, 1° agosto 2003. Un altro possibile circuito di rilevazione e di correzione di errore che usa un codice SECDED è descritto nel documento US 8,381,083 B2. Questo documento descrive anche che i bit ECC possono essere calcolati anche per altri dati, per es., sia per i dati DATA sia per il rispettivo indirizzo.

La Figura 9 rappresenta a questo riguardo una forma di attuazione di un circuito di rilevazione di errori 46 atto a essere usato in uno schema SECDED, per es., come usato in un microcontrollore ARM Cortex R52.

Specificamente, nella forma di attuazione considerata, il circuito di rilevazione di errori 46 comprende un circuito di calcolo della sindrome 460 configurato per:

- ricevere i bit di dati DATA e i bit di ECC;

- calcolare i bit di ECC per i bit di dati DATA ricevuti; e

- confrontare i bit di ECC calcolati con i bit di ECC ricevuti.

Nel caso di un codice SEC, il risultato di questo confronto, detta sindrome SYN, è indicativo della posizione

del bit scorretto nel caso di un errore di bit singolo. Di conseguenza, la sindrome SYN corrisponde a una sequenza di bit avente K bit.

Di conseguenza, nel caso in cui la sindrome SYN sia differente da una sequenza di K bit impostati a zero, cioè, differente dal valore 0, è rilevato un errore. Per esempio, questo è rappresentato schematicamente nella Figura 9, dove una porta logica 464, come una porta logica OR, è usata per generare un segnale di errore  $ERR_1$  in funzione della sindrome SYN, cioè, il segnale di errore  $ERR_1$  è asserito quando almeno uno dei bit della sindrome SYN è asserito. Tuttavia, nel caso di un codice SEC, il circuito di calcolo della sindrome 460 non è in grado di rilevare errori di bit doppi. In effetti, il segnale di errore  $ERR_1$  sarà asserito sia per un errore di bit singolo sia per un errore di bit doppio.

Di conseguenza, in varie forme di attuazione, il circuito di verifica di codice di correzione di errore 46 comprende anche un circuito 462 configurato per rilevare specificamente errori di bit singoli. Per esempio, nel caso più semplice, il circuito di rilevazione di errori di bit singoli 46 può verificare una parità pari o dispari, generando con ciò un segnale SB che indica che si è verificato un errore di bit singolo. Per esempio, in questo caso, i bit ECC possono comprendere uno o più bit di parità dedicati che possono anche non essere forniti al circuito di calcolo della sindrome 460.

Tuttavia, spesso tali circuiti di rilevazione di errori di bit singoli 462 non sono in grado di distinguere tra dati corretti ed errori di bit doppi. Così, combinando il segnale di errore  $ERR_1$  (che indica un errore di bit singolo o un errore di bit doppio) e il segnale SB (che

indica un errore di bit singolo), è possibile generare mediante un circuito logico combinatorio un segnale  $ERR_2$  che indica che si è verificato un errore di bit doppio, per es., asserendo il segnale di errore  $ERR_2$  quando il segnale di errore  $ERR_1$  è asserito e il segnale  $SB$  è deasserrito. Per esempio, nella forma di attuazione considerata, il circuito logico combinatorio comprende un inverter 468 e una porta logica AND 470.

Di conseguenza, il circuito di rilevazione di errori 46 può essere configurato per usare la sindrome  $SYN$  e il bit  $SB$  per generare una firma di errore di bit singolo  $SIG$  avente  $N+K$  bit. Per esempio, nella forma di attuazione considerata, questa operazione è implementata nel circuito di rilevazione di errori di bit singoli 462.

Specificamente, nel caso di un errore di bit singolo, cioè, il segnale  $SB$  è asserito, il circuito 46/462 è configurato per asserire il bit del segnale  $SIG$  corrispondente alla posizione indicata dalla sindrome  $SYN$ , mentre gli altri bit del segnale  $SIG$  sono deasserriti.

Nel caso in cui il circuito 462 non fornisca direttamente il segnale  $SB$ , un corrispondente segnale  $SB$  può così essere generato mediante una combinazione logica dei bit del segnale  $SIG$ , per es., mediante una porta logica OR 466, perché dovrebbe essere asserito al massimo soltanto uno dei bit del segnale  $SIG$ .

Generalmente, possono anche essere usati altri schemi di ECC al fine di generare la firma di ribaltamento di bit  $SIG$ , che potrebbe indicare anche che dovrebbe essere ribaltato più di un bit, per es., nel caso di un codice di Correzione di Errore Doppio. Similmente, in questo caso, i segnali di errore  $ERR_1$  e  $ERR_2$  potrebbero indicare in generale che si è verificato un errore (segnali di errore

ERR<sub>1</sub>) e opzionalmente che l'errore è correggibile oppure no (segnali di errore ERR<sub>2</sub>).

Generalmente, queste soluzioni hanno in comune che la sindrome SYN è confrontata con una pluralità di sindromi di riferimento, in cui ciascuna sindrome di riferimento corrisponde a una data firma di ribaltamento di bit. Così, nel caso in cui la sindrome SYN corrisponda a una sindrome di riferimento, il circuito di rilevazione di errori può asserire i rispettivi bit della firma di errore SIG. Per esempio, nel caso di un codice SECDED, il circuito di rilevazione di errori userebbe N + K sindromi di riferimento, ciascuna corrispondente a un rispettivo errore di bit singolo. Per esempio, la verifica delle firme di riferimento e l'impostazione della firma SIG (e dei segnali di errore) possono essere implementate mediante un circuito logico combinatorio.

A questo riguardo, usando un codice ECC SECDED adeguato, ciascuna sindrome di riferimento associata a un errore di bit singolo può anche avere una configurazione univoca in confronto a errori di ribaltamento di bit doppi. Di conseguenza, in generale, il circuito di rilevazione di errori può:

- non segnalare un errore (per es., deasserendo entrambi i segnali di errore ERR<sub>1</sub> e ERR<sub>2</sub>) quando i bit della sindrome SYN sono tutti deasseriti;

- segnalare un errore correggibile (per es., asserendo il segnale di errore ERR<sub>1</sub> e deasserendo il segnale di errore ERR<sub>2</sub>) quando la sindrome SYN corrisponde a una delle sindromi di riferimento (per es., di errore di bit singolo), asserendo anche i rispettivi bit della firma di ribaltamento di bit SIG; e

- segnalare un errore non correggibile (per es., asserendo il segnale di errore  $ERR_1$  e il segnale di errore  $ERR_2$ ) quando almeno un bit della sindrome  $SYN$  è asserito e la sindrome  $SYN$  non corrisponde ad alcuna delle sindromi di riferimento.

Di conseguenza, in varie forme di attuazione, i segnali  $ERR_1$ ,  $ERR_2$  e  $SIG$  possono essere forniti a un circuito di correzione di errore, per es., implementato nel controllore di memoria 100, che così può:

- nel caso in cui non sia segnalato alcun errore (per es., il segnale  $ERR_1$  è deasserrito e il segnale  $ERR_2$  è deasserrito) fornire i dati  $DATA$  originali al dispositivo master richiedente, per es., inviando i dati  $DATA$  al sistema di comunicazione 114;

- nel caso di un errore di bit correggibile (per es., il segnale  $ERR_1$  è asserito e il segnale  $ERR_2$  è deasserrito) ribaltare il livello logico del rispettivo (dei rispettivi) bit, in particolare nel caso di un bit di dati  $DATA$ , come indicato dalla firma  $SIG$ , e fornire i dati  $DATA$  corretti al dispositivo master 40 richiedente; e

- nel caso di un errore di bit non correggibile (per es., il segnale  $ERR_1$  è asserito e il segnale  $ERR_2$  è asserito), segnalare un errore al dispositivo master richiedente e/o a un circuito di raccolta dei guasti e di gestione degli errori 120.

Di conseguenza, nella forma di attuazione considerata, il circuito di rilevazione di errori 46 rappresenta un circuito di monitoraggio di sicurezza. A questo riguardo, il circuito di monitoraggio di sicurezza è effettivamente abbastanza complesso e, a causa di un malfunzionamento del circuito 46, errori nei dati  $DATA$  possono non essere

rilevati o possono essere segnalati errori anche quando i dati DATA sono corretti.

Gli inventori hanno così osservato che il funzionamento del circuito 46 dovrebbe essere verificato. A questo riguardo, gli inventori hanno osservato che la protezione di un circuito di monitoraggio di sicurezza SM potrebbe essere fatta con strategie differenti, per es.:

- duplicando il circuito di monitoraggio di sicurezza 46 e verificando se entrambi i circuiti forniscono la stessa uscita, o

- eseguendo qualche software specifico allo scopo di simulare la funzionalità di monitoraggio di sicurezza, per es., scrivendo dati forniti nella memoria 104/104b e leggendo poi di nuovo i dati dalla memoria 104/104b.

Ciascuna di queste soluzioni ha suoi vantaggi e svantaggi. Per esempio, una duplicazione del circuito di monitoraggio di sicurezza aumenta l'area del dispositivo e richiede uno o più circuiti di monitoraggio di sicurezza per verificare la coerenza dei segnali di uscita generati dal monitor di sicurezza e dalla sua versione ridondante. Per contro, un test software richiede lo sviluppo e la verifica del test e spesso non è possibile verificare l'intero circuito di monitoraggio di sicurezza.

Inoltre, il sistema di elaborazione 10a potrebbe essere configurato per permettere un auto-test integrato logico o LBIST (Logic Built-In Self-Test), che è un modo per stimolare i nodi interni del circuito di monitoraggio di sicurezza e verificare i segnali forniti dal circuito di monitoraggio di sicurezza. Tuttavia, una tale soluzione LBIST richiede uno sforzo nello stadio di sviluppo di backend, che può consumare risorse e tempo di progetto, poiché la copertura LBIST potrebbe essere ottenuta soltanto dopo

vari tentativi che richiedono tempo. Inoltre, la copertura target di solito è ottenuta inserendo dei punti di test LBIST, il che significa anche un aumento dell'area.

La Figura 10 rappresenta una forma di attuazione di un circuito di monitoraggio di sicurezza SMA secondo la presente descrizione.

Specificamente, anche in questo caso il circuito di monitoraggio di sicurezza comprende una rilevazione di errori 46 configurata per ricevere  $N$  bit di dati DATA e  $K$  bit di ECC. Inoltre, il circuito di rilevazione di errori 46 è configurato per generare, in funzione dei bit DATA e ECC ricevuti:

- una pluralità di segnali di errore che indicano se si è verificato un errore (per es., il segnale  $ERR_1$ ) e se l'errore può essere corretto oppure no (per es., il segnale  $ERR_2$ ); e

- una firma di ribaltamento di bit SIG che indica, nel caso di un errore correggibile, quale bit o quali bit dei bit di dati DATA e dei bit di ECC sono scorretti e così dovrebbero essere ribaltati/corretti.

Come descritto in precedenza, il circuito di rilevazione di errori 46 di solito è un circuito logico combinatorio configurato per generare i livelli logici dei segnali di errore e la firma di ribaltamento di bit SIG in funzione dei livelli logici dei segnali DATA e ECC.

Generalmente, al fine di testare la funzionalità completa del circuito 46, dovrebbero essere fornite al circuito 46 tutte le combinazioni di ingressi possibili. Tuttavia, di solito questo è infattibile, perché sarebbe necessario testare troppe combinazioni logiche. Tuttavia, gli inventori hanno osservato che di solito è sufficiente che ciascun bit di ingresso della logica combinatoria sia

stimolato sia con uno zero logico sia con un uno logico, e che ciascuna uscita della logica combinatoria 46 sia testata per un cambiamento di bit da zero a uno o viceversa.

Specificamente, in varie forme di attuazione, il circuito di monitoraggio di sicurezza SMa comprende a questo scopo un circuito di test hardware 48 configurato per:

- generare una data configurazione di bit PAT di  $N+K$  bit, che è fornita selettivamente agli ingressi DATA e ECC del circuito di rilevazione di errori 46 durante una modalità di test, per es., mediante un multiplexer 480 pilotato dal circuito di test 48 mediante un segnale di modalità di test TM, e

- ricevere e verificare i segnali risultanti RES generati dal circuito di rilevazione di errori 46, cioè, i segnali di errore e la firma SIG.

Per esempio, la modalità di test può essere avviata quando il sistema di elaborazione 10a è acceso e/o in risposta a dati eventi, come un innesto di errore ET segnalato dal circuito di raccolta dei guasti e di gestione degli errori 120 (si veda, per es., la descrizione della Figura 5).

Come menzionato in precedenza, in varie forme di attuazione, il circuito di test 48 è configurato per generare una sequenza di configurazioni PAT selezionata al fine di assicurare che, nel caso di un circuito di rilevazione di errori 46 che funziona correttamente, ciascun ingresso e ciascuna uscita del circuito di rilevazione di errori 46 sia impostato almeno una volta a zero e sia impostato almeno una volta a uno. Per esempio, al fine di generare la sequenza di configurazioni PAT e

verificare il rispettivo risultato RES fornito dal circuito di rilevazione di errori 46, il circuito di test 48 può essere un circuito logico sequenziale che implementa una macchina a stati finiti.

Specificamente, in varie forme di attuazione, il circuito di test 48 è configurato per generare tre tipi di configurazioni:

- una o più prime configurazioni/configurazioni base, che non comprendono un errore nei bit DATA e ECC, cioè, i bit ECC corrispondono ai bit calcolati per i bit di dati DATA secondo lo schema di ECC usato dal circuito di rilevazione di errori 46;

- una pluralità di seconde configurazioni comprendenti errori correggibili, come un bit singolo ribaltato rispetto alla prima configurazione/configurazione base; e

- opzionalmente almeno una terza configurazione comprendente errori non correggibili, come due bit ribaltati rispetto alla prima configurazione/configurazione base.

Così, prendendo in considerazione che tutti i bit di ingresso devono essere testati, in varie forme di attuazione, il circuito di test 48 è configurato per generare (almeno) le seguenti configurazioni PAT per uno schema SECDED:

- una configurazione base (con bit DATA e ECC corretti);

- $N+K$  configurazioni, ciascuna di loro contenendo, in una posizione di bit differente, un ribaltamento di bit singolo rispetto alla configurazione base; e

- una configurazione con due bit ribaltati rispetto alla configurazione base.

Di conseguenza, in varie forme di attuazione, il circuito di test 48 è configurato per determinare, per ciascuna delle configurazioni precedenti, il rispettivo risultato atteso e per confrontare il risultato atteso con il risultato RES ricevuto dal circuito di rilevazione di errori 46.

Di conseguenza, in varie forme di attuazione, le configurazioni generate dal circuito di test 48 (e, similmente, i risultati attesi) sono predeterminate. Per esempio, questo permette che il circuito di test 48 sia implementato con un circuito logico sequenziale, che può generare una sequenza di configurazioni predeterminata o può ottenere le configurazioni da una memoria di sola lettura o ROM (Read Only Memory). Questo comporta anche che non deve essere usato alcun codificatore di ECC del sistema di elaborazione 10a per generare le configurazioni. In effetti, tali codificatori di ECC, per es., implementati nel (nei) core di elaborazione 102 possono non essere disponibili durante l'operazione di auto-test del sistema di elaborazione 10a. Specificamente, in varie forme di attuazione, indipendentemente dallo schema di ECC usato, le configurazioni sono selezionate al fine di generare (almeno) tutti i possibili ribaltamenti di bit singoli per ciascun segnale di ingresso e di uscita, e in particolare per i segnali di DATA e di ECC forniti al circuito di rilevazione di errori 46 e la firma di ribaltamento di bit SIG ricevuta dal circuito di rilevazione di errori 46. Per esempio, a questo scopo, il circuito di test può generare configurazioni predeterminate, che dovrebbero testare tutti i possibili  $(N + K)$  errori di ribaltamento di bit singolo nel segnale della firma SIG.

La Figura 11 rappresenta una possibile forma di attuazione del circuito di test 48.

Specificamente, nella forma di attuazione considerata, invece di memorizzare tutte le configurazioni, il circuito di test 48 memorizza solo una configurazione base BPAT. Specificamente, la configurazione base BPAT può essere cablata in hardware ("hardwired"), o può essere programmabile, per es., mediante un microprocessore 1020 o in funzione di dati di configurazione distribuiti mediante un modulo di configurazione hardware del sistema di elaborazione 10a.

Inoltre, nella forma di attuazione considerata, il circuito di test 48 comprende un contatore hardware digitale 482. Specificamente, in varie forme di attuazione, il contatore 482 è configurato, quando abilitato (per es., mediante un segnale di inizio START), a incrementare un valore di conteggio CNT da un valore iniziale a un valore massimo corrispondente al numero di configurazioni da testare. Per esempio, in questo caso, il segnale di modalità di test TM può essere asserito quando il contatore 482 è in funzione.

Di conseguenza, in questo caso, la configurazione base BPAT e il valore di conteggio CNT possono essere forniti a un circuito 484 configurato per generare la configurazione PAT per il ciclo corrente (come indicato dal valore di conteggio CNT) da fornire al circuito di rilevazione di errori 46 in funzione della configurazione base BPAT e del valore di conteggio CNT.

Similmente, nella forma di attuazione considerata, il circuito di test 48 memorizza un risultato base BRES corrispondente ai valori dei segnali (segnali di errore e firma di ribaltamento di bit SIG) che ci si aspetta che

siano forniti dal circuito di rilevazione di errori 46 per la configurazione base BPAT. Per esempio, considerando che la configurazione base BPAT non dovrebbe comprendere errori, il risultato base BRES può avere tutti i bit impostati bassi, per es., mediante un cablaggio hardware ("hardwiring").

Di conseguenza, in questo caso, il risultato base BRES e il valore di conteggio CNT possono essere forniti a un circuito 488 configurato per generare il risultato atteso ERES per il ciclo corrente (come indicato dal valore di conteggio CNT) in funzione del risultato base BRES e del valore di conteggio CNT. Di conseguenza, un comparatore digitale 488 può essere configurato per confrontare il risultato atteso ERES con il risultato RES (cioè, i segnali di errore e la firma SIG) fornito dal circuito di rilevazione di errori 46, e per assegnare un segnale di errore  $ERR_3$  nel caso in cui le sequenze di bit non corrispondano.

Specificamente, in varie forme di attuazione, il circuito di test 48 comprende un circuito 490 configurato per generare una firma di ribaltamento di bit FSIG che indica la posizione dei bit che dovrebbero essere ribaltati dal circuito 484 per il ciclo di test corrente.

Specificamente, in varie forme di attuazione, quando è emulato un errore di ribaltamento di bit singolo, il valore di conteggio CNT può essere usato per generare una firma di test FSIG codificata one-hot. In alternativa, al fine di testare errori di bit singoli, il circuito 490 può anche comprendere un registro a scorrimento avente un bit singolo impostato alto. Di conseguenza, un tale registro a scorrimento rappresenta sostanzialmente un contatore codificato one-hot, cioè, i circuiti 482 e 490 possono

anche essere implementati con un singolo registro a scorrimento/contatore codificato one-hot, in cui la firma FSIG può corrispondere a un sottoinsieme dei bit del contatore codificato one-hot.

Di conseguenza, in varie forme di attuazione, la firma FSIG indica la posizione del (dei) bit che deve essere ribaltato (che devono essere ribaltati) dal circuito 484. Per esempio, in questo caso, il circuito 484 può essere implementato con una pluralità di porte logiche XOR, ciascuna porta logica XOR ricevendo un rispettivo bit della configurazione base BPAT e della firma FSIG. Generalmente, nel caso di una configurazione base BPAT cablata in hardware, può anche essere usato un circuito logico ottimizzato. Generalmente, invece di usare la configurazione base BPAT, il circuito di test 48 può anche ottenere una configurazione di riferimento differente senza errori e può generare le configurazioni correggibili combinando la configurazione di riferimento con la firma FSIG.

A questo riguardo, per errori correggibili, la firma FSIG corrisponde anche alla firma attesa SIG, cioè, il circuito 486 può usare la firma FSIG per generare il risultato atteso ERES.

In seguito, sarà descritta ora una possibile forma di attuazione delle configurazioni PAT generate dal circuito di test 48, che, per es., possono essere usate per un microcontrollore basato su ARM Cortex R52. Specificamente, nella forma di attuazione considerata, senza perdere di generalità, il circuito di rilevazione di errori 46 è configurato per ricevere  $N = 64$  bit di dati DATA e  $K = 8$  bit di ECC, cioè, le configurazioni PAT hanno 72 bit.

Per esempio, in varie forme di attuazione, tutti i bit di dati della configurazione base BPAT sono impostati a "0". Nello schema di ECC ARM, questo comporta che i bit di ECC siano impostati a 0x3 per la configurazione base BPAT. Tuttavia, può anche essere usata una qualsiasi altra configurazione base (senza errori). Di conseguenza, quando è fornita la configurazione base BPAT, la firma SIG e i bit di errore  $ERR_1$  e  $ERR_2$  (cioè, il risultato RES) dovrebbero avere tutti i bit impostati bassi, cioè, il risultato base BRES ha tutti i bit impostati a "0".

In seguito, il circuito di test 48 può testare gli errori di bit correggibili, per es., gli  $N+K$  errori di bit singoli nel caso di uno schema SECDED. Come menzionato in precedenza, il circuito 490 può generare in questo caso la firma di ribaltamento di bit FSIG, che può essere usata per ribaltare i rispettivi bit della configurazione base BPAT o di un'altra configurazione di riferimento (senza errori).

Per queste configurazioni, il circuito di test 48 può verificare se il segnale di errore  $ERR_1$  è asserito, il segnale di errore  $ERR_2$  è deasserrito e la firma SIG corrisponde alla firma FSIG. Per esempio, in seguito si ipotizzerà che i bit ECC corrispondano ai bit più significativi (MSB, "Most-Significant Bit") della firma SIG. Qui di seguito, c'è la lista di possibili configurazioni di bit singoli:

- configurazione PAT (bit di dati 0 ribaltato):

DATA = 0x0000\_0000\_0000\_0001, ECC = 0x3; risultato atteso

ERES:  $ERR_1 = 1$ ,  $ERR_2 = 0$ , SIG = 0x00\_0000\_0000\_0001;

- configurazione PAT (bit di dati 1 ribaltato):

DATA = 0x0000\_0000\_0000\_0002, ECC = 0x3; risultato atteso

ERES:  $ERR_1 = 1$ ,  $ERR_2 = 0$ , SIG = 0x00\_0000\_0000\_0002;

```

- configurazione PAT (bit di dati 2 ribaltato):

DATA = 0x0000_0000_0000_0004, ECC = 0x3; risultato atteso

ERES: ERR1 = 1, ERR2 = 0, SIG = 0x00_0000_0000_0004;

...

- configurazione PAT (bit di dati 63 ribaltato):

DATA = 0x8000_0000_0000_0000, ECC = 0x3; risultato atteso

ERES: ERR1 = 1, ERR2 = 0, SIG = 0x00_8000_0000_0000;

- configurazione PAT (bit di ECC 0 ribaltato):

DATA = 0x0000_0000_0000_0000, ECC = 0x2; risultato atteso

ERES: ERR1 = 1, ERR2 = 0, SIG = 0x01_0000_0000_0000;

- configurazione PAT (bit di ECC 1 ribaltato):

DATA = 0x0000_0000_0000_0000, ECC = 0x1; risultato atteso

ERES: ERR1 = 1, ERR2 = 0, SIG = 0x02_0000_0000_0000;

- configurazione PAT (bit di ECC 2 ribaltato):

DATA = 0x0000_0000_0000_0000, ECC = 0x7; risultato atteso

ERES: ERR1 = 1, ERR2 = 0, SIG = 0x04_0000_0000_0000;

...

- configurazione PAT (bit di ECC 7 ribaltato):

DATA = 0x0000_0000_0000_0000, ECC = 0x83; risultato atteso

ERES: ERR1 = 1, ERR2 = 0, SIG = 0x80_0000_0000_0000.

```

Infine, l'una o più configurazioni di errori non correggibili possono essere generate asserendo il rispettivo numero di bit del segnale FSIG, cioè, ribaltando i rispettivi bit della configurazione PAT, per es., ribaltando due bit nel caso di uno schema SECDED. In alternativa, le configurazioni di errori non correggibili possono essere fisse o programmabili. Per esempio, per questa configurazione non correggibile (queste configurazioni non correggibili), il circuito di test 48 può verificare se il segnale di errore ERR<sub>1</sub> è asserito, il segnale di errore ERR<sub>2</sub> è asserito e la firma SIG ha tutti i bit impostati a "0". Per esempio, una possibile

configurazione di errore di bit doppio può essere la seguente configurazione PAT (bit di dati 0 ribaltato e ECC bit 0 ribaltato): DATA = 0x0000\_0000\_0000\_0001, ECC = 0x2; risultato atteso ERES: ERR<sub>1</sub> = 1, ERR<sub>2</sub> = 1, SIG = 0x00\_0000\_0000\_0000.

La Figura 12 rappresenta a questo riguardo una forma di attuazione del funzionamento del circuito di test 48 nel caso di uno schema SECDED. Specificamente, come descritto in precedenza, in questo caso il circuito di test 48 è configurato per:

- generare una prima configurazione senza errori (per es., la configurazione base BPAT) e verificare il risultato RES fornito dal circuito di rilevazione di errori 46;

- generare una sequenza di seconde configurazioni con un ribaltamento di bit singolo e verificare ogni volta il risultato RES; e

- generare una o più terze configurazioni con un ribaltamento di bit doppio e verificare ogni volta il risultato RES.

Per esempio, la prima configurazione/configurazione base BPAT e la terza configurazione/configurazione (le terze configurazioni/configurazioni) di ribaltamento di bit doppio possono essere fisse o programmabili. Per contro, la seconda configurazione/configurazione di ribaltamento di bit singolo può essere determinata nel circuito di test 48, per es., mediante il circuito 490, e/o anche le configurazioni di ribaltamento di bit singolo possono essere fisse o programmabili e possono così anche essere indipendenti dalla configurazione base BPAT. Per esempio, come descritto in precedenza, il circuito di test 48 può essere configurato per generare le configurazioni di ribaltamento di bit singolo, per es., invertendo un

rispettivo bit della configurazione base BPAT in funzione della firma FSIG, in cui la firma FSIG può essere generata mediante un registro a scorrimento avente impostato alto un bit singolo, o mediante un decodificatore one-hot del valore di conteggio CNT, o altre soluzioni digitali simili. Generalmente, la selezione delle specifiche configurazioni può dipendere dallo schema di ECC usato e/o dalla specifica implementazione del circuito di rilevazione di errori 46.

Di conseguenza, dopo una fase di inizio 1000, che è attivata, per es., in risposta al segnale di inizio START, il circuito di test 48 genera la configurazione base in una fase 1002 e fornisce in una fase 1004 la configurazione base al circuito di rilevazione di errori 46. In una fase 1006, il circuito di test confronta quindi il risultato RES fornito dal circuito di rilevazione di errori 46 con il risultato atteso ERES, per es., verifica se i segnali di errore  $ERR_1$  e  $ERR_2$  sono impostati a zero, e tutti i bit della firma SIG sono impostati a zero.

Nel caso in cui il risultato RES non corrisponda al risultato atteso ERES (uscita "N" della fase di verifica 1006), il circuito di test 48 procede a una fase 1030 in cui il circuito di test asserisce il segnale di errore  $ERR_3$ , e la procedura termina a una fase di arresto 1034.

Per contro, nel caso in cui il risultato RES corrisponda al risultato atteso ERES (uscita "Y" della fase di verifica 1006), il circuito di test 48 genera in una fase 1008 la prima configurazione di ribaltamento di bit, per es., avente il primo bit della configurazione base BPAT o di un'altra configurazione di riferimento ribaltato, e il circuito di test 48 fornisce in una fase 1010 la configurazione di ribaltamento di bit singolo corrente al circuito di rilevazione di errori 46. Di conseguenza, in

una fase 1012, il circuito di test confronta quindi il risultato RES fornito dal circuito di rilevazione di errori 46 con il risultato atteso ERES, per es., verifica se il segnale di errore  $ERR_1$  è impostato a uno, il segnale di errore  $ERR_2$  è impostato a zero, e il corrispondente bit della firma SIG è impostato a uno, per es., confrontando la firma SIG con la firma FSIG.

Nel caso in cui il risultato RES non corrisponda al risultato atteso ERES (uscita "N" della fase di verifica 1012), il circuito di test 48 procede alla fase 1030 in cui il circuito di test asserisce il segnale di errore  $ERR_3$ , e la procedura termina a una fase di arresto 1034.

Per contro, nel caso in cui il risultato RES corrisponda al risultato atteso ERES (uscita "Y" della fase di verifica 1012), il circuito di test 48 genera in una fase 1014 la prossima configurazione di ribaltamento di bit singolo, per es., facendo scorrere il bit "1" della firma FSIG. In seguito, il circuito di test verifica in una fase 1016 se la configurazione di ribaltamento di bit singolo corrente era l'ultima configurazione di ribaltamento di bit singolo, per es., in base al valore di conteggio CNT o usando un registro a scorrimento nel circuito 490 e rilevando che il bit impostato a "1" ha raggiunto la posizione di bit  $N+K+1$ .

Di conseguenza, nel caso in cui la configurazione di ribaltamento di bit singolo corrente non fosse l'ultima configurazione di ribaltamento di bit singolo (uscita "N" della fase di verifica 1016), il circuito di test 48 ritorna alla fase 1010, in cui il circuito di test fornisce la configurazione di ribaltamento di bit singolo corrente al circuito di rilevazione di errori 46.

Per contro, nel caso in cui la configurazione di ribaltamento di bit singolo corrente fosse l'ultima configurazione di ribaltamento di bit singolo (uscita "Y" della fase di verifica 1016), il circuito di test 48 genera la configurazione di ribaltamento di bit doppio in una fase 1018 e fornisce in una fase 1020 la configurazione di ribaltamento di bit doppio al circuito di rilevazione di errori 46. Di conseguenza, in una fase 1022, il circuito di test confronta quindi il risultato RES fornito dal circuito di rilevazione di errori 46 con il risultato atteso ERES, per es., verifica se i segnali di errore  $ERR_1$  e  $ERR_2$  sono impostati a uno, e tutti i bit della firma SIG sono impostati a zero.

Nel caso in cui il risultato RES non corrisponda al risultato atteso ERES (uscita "N" della fase di verifica 1022), il circuito di test 48 procede alla fase 1030 in cui il circuito di test asserisce il segnale di errore  $ERR_3$ , e la procedura termina a una fase di arresto 1034.

Per contro, nel caso in cui il risultato RES corrisponda al risultato atteso ERES (uscita "Y" della fase di verifica 1022), il circuito di test 48 deasserisce in una fase 1032 il segnale di errore  $ERR_2$ , e la procedura termina a una fase di arresto 1034. Generalmente, la fase 1032 è puramente opzionale, perché il segnale di errore  $ERR_2$  può anche essere deasserito di default.

Generalmente, il circuito di test 48 può anche testare più configurazioni di ribaltamento di bit doppio. Per esempio, come rappresentato nella Figura 12, nel caso in cui il risultato RES corrisponda al risultato atteso ERES (uscita "Y" della fase di verifica 1022), il circuito di test 48 può generare un'ulteriore configurazione di ribaltamento di bit doppio in una fase 1024 e può fornire,

in una fase 1026, l'ulteriore configurazione di ribaltamento di bit doppio al circuito di rilevazione di errori 46. Di conseguenza, in una fase 1028, il circuito di test può quindi confrontare il risultato RES fornito dal circuito di rilevazione di errori 46 con il risultato atteso ERES, per es., può verificare se i segnali di errore  $ERR_1$  e  $ERR_2$  sono impostati a uno, e tutti i bit della firma SIG sono impostati a zero.

Nel caso in cui il risultato RES non corrisponda al risultato atteso ERES (uscita "N" della fase di verifica 1028), il circuito di test 48 procede alla fase 1030 in cui il circuito di test asserisce il segnale di errore  $ERR_3$ , e la procedura termina a una fase di arresto 1034.

Per contro, nel caso in cui il risultato RES corrisponda al risultato atteso ERES (uscita "Y" della fase di verifica 1028), il circuito di test 48 procede alla fase 1032 o direttamente alla fase di arresto 1034.

La Figura 13 rappresenta un'ulteriore forma di attuazione, in cui lo stesso circuito di test 48 è configurato per testare più circuiti di rilevazione di errori 46, come circuiti di rilevazione di errori  $46_1$ ,  $46_2$  e  $46_3$ .

Generalmente, in questo caso, il circuito di test 48 può essere connesso, per es., mediante multiplexer sequenzialmente a uno dei circuiti di rilevazione di errori  $46_1$ ,  $46_2$  e  $46_3$ .

Per contro, nella Figura 13, il circuito di test 48 fornisce la stessa configurazione PAT in parallelo a tutti i circuiti di rilevazione di errori  $46_1$ ,  $46_2$  e  $46_3$ . Specificamente, nella forma di attuazione considerata, i risultati  $RES_1$ ,  $RES_2$  e  $RES_3$  forniti al circuito di rilevazione di errori  $46_1$ ,  $46_2$  e  $46_3$  sono combinati mediante

una porta logica OR 492 per generare un primo segnale di risultato  $RES_a$  e mediante una porta logica AND 492 per generare un secondo segnale di risultato  $RES_b$ . Specificamente, nel caso in cui il circuito di rilevazione di errori  $46_1$ ,  $46_2$  e  $46_3$  funzioni correttamente, sia il primo segnale di risultato  $RES_a$  sia il secondo segnale di risultato  $RES_b$  dovrebbero corrispondere al risultato atteso ERES descritto precedentemente. Di conseguenza, in varie forme di attuazione, il circuito di test può essere configurato per confrontare ciascuno del primo segnale di risultato  $RES_a$  e del secondo segnale di risultato  $RES_b$  con il segnale di risultato atteso ERES.