(19) 대한민국특허청(KR)

(12) 등록특허공보(B1)

(45) 공고일자 2013년02월25일

(11) 등록번호 10-1236150

(24) 등록일자 2013년02월18일

(51) 국제특허분류(Int. Cl.)

*G01C 19/56* (2006.01)

(21) 출원번호 10-2007-7027219

(22) 출원일자(국제) 2006년04월24일

심사청구일자 2011년04월13일

(85) 번역문제출일자 2007년11월22일

(65) 공개번호 10-2008-0005445

(43) 공개일자 2008년01월11일

(86) 국제출원번호 PCT/US2006/015411

(87) 국제공개번호 WO 2006/116271

국제공개일자 2006년11월02일

(30) 우선권주장

(73) 특허권자

허니웰 인터내셔널 인코포레이티드

미국 뉴저지 모리스타운 콜롬비아로드 101

(72) 발명자

템마 닉 안소니

미국, 미네소타 55418, 미네아폴리스, 메인 스트리트 노스이스트3609

(74) 대리인

특허법이씨에에스

(30) 우선권주장

10/908,034 2005년04월26일 미국(US)

심사관 : 김형근

(54) 발명의 명칭 기계식 발진기 제어 전자장치

(57) 요약

주파수를 갖는 정현 구동 신호를 구비한 기계식 발진기를 위한 제어 시스템은 기계식 발진기 신호에 대한 분수배 주파수를 갖는다. 구동 신호는 기계식 발진기로부터의 신호와 동상이며 이 신호와 겹쳐진다. 감지 신호는 발진기로부터의 광오프일 수 있으며 발진기에 의해 감지된 파라미터를 얻기 위하여 복조될 수 있다. 발진기에 대한 구동 신호는 감지 신호를 수신하고 복조하는 동안 선택되거나 제거될 수 있다.

## 대 표 도

## 특허청구의 범위

### 청구항 1

기계식 발진기의 팩오프에 연결된 제1 위상 동기 루프(271); 및

상기 제1 위상 동기 루프의 출력에 연결된 제2 위상 동기 루프(272);

를 포함하며,

상기 제2 위상 동기 루프는 상기 기계식 발진기의 모터 팩오프로부터의 신호(212, 251)의 분수배 주파수를 갖는 정현파 신호를 출력할 수 있는 기계식 발진기 제어 시스템(10, 210).

### 청구항 2

제1항에 있어서,

상기 정현파 신호와 상기 기계식 발진기의 팩오프로부터 신호는 서로에 대하여 겹쳐지는 것을 특징으로 하는 기계식 발진기 제어 시스템.

### 청구항 3

제2항에 있어서,

상기 정현파 신호의 에지 또는 교차점은 상기 기계식 발진기의 팩오프로부터의 신호의 에지 또는 교차점과 일치하는 것을 특징으로 하는 기계식 발진기 제어 시스템.

### 청구항 4

삭제

### 청구항 5

삭제

### 청구항 6

삭제

### 청구항 7

삭제

### 청구항 8

삭제

### 청구항 9

삭제

### 청구항 10

삭제

### 청구항 11

삭제

청구항 12

삭제

청구항 13

삭제

청구항 14

삭제

청구항 15

삭제

청구항 16

삭제

청구항 17

삭제

청구항 18

삭제

청구항 19

삭제

청구항 20

삭제

청구항 21

삭제

청구항 22

삭제

청구항 23

삭제

청구항 24

삭제

청구항 25

삭제

청구항 26

삭제

청구항 27

삭제

## 청구항 28

삭제

### 명세서

#### 기술 분야

[0001] 본 발명은 전자 제어에 관한 것으로, 특히, 전자 장치에 깨끗하거나 잡음이 없는 전자 신호를 제공하는 것에 관한 것이다. 더욱 상세하게는, 본 발명은 마이크로가공 전기기계(micromachined electromechanical, MEMS) 자이로스코프의 제어 및 구동을 위하여 이러한 신호를 제공하는 것에 관한 것이다.

#### 발명의 상세한 설명

##### [요약]

[0003] 복조 신호를 생성하는 마이크로 컨트롤러에 클럭 주파수를 제공하기 위하여 전압 제어 발진기(voltage controlled oscillator, VCO)를 사용하기 위한 접근 방법은 많은 오류를 피할 수 있다. 센서와 루프 필터(loop filter)의 주파수와 관계없이 동일한 코드가 마이크로 컨트롤러 상에서 실행되고, 이는 복조기로부터 나오는 신호가 위상 에러가 없는 루프 동기를 제공하기 위한 것이며, 스위치에서의 딜레이가 자동적으로 보상되게 하는 것을 보장할 수 있다. 디지털 VCO에 의한 설명은 출력에서의 디지털이 1과 0으로만 이루어져 있기 때문에 정밀하지 않을 수 있다. VCO는 아날로그 신호가 VCO에 입력되고 주파수가 정량화되지는 않지만 발진기의 범위 내의 임의의 값을 취할 수 있다는 의미에서 아날로그일 수 있다. 전자 장치의 개략도가 본 발명의 구현을 예시한다. 그러나, 제어 전자 장치의 아날로그 부분의 아날로그 양태는 신호 처리를 이용하여 디지털화될 수 있다.

#### 실시예

[0025] 항공 등급의 성능을 갖는 저비용의 마이크로 가공 전기기계(MEMS) 자이로스코프에 대한 요구가 있을 수 있다. 이러한 성능에 대한 전제 조건은 자이로스코프를 위한 정밀한 제어 전자 장치이다. 디지털 신호 처리기(Digital Signal Processor, DSP)를 이용한 구현은 센서의 주파수를 설명하고 적절한 자이로스코프용 모터 구동 신호를 생성하는 소프트웨어로 소정의 고정된 클럭 주파수에서 실행되는 DSP를 포함한다. DSP로부터의 모터 또는 발진기 구동 신호는 디지털로 생성된 합성 정현파 또는 사인파일 수 있다. 모터 구동 신호는 모터 퍽오프(pickoff) 신호와 동기화될 수 있다. 또한, 모터 구동 신호는 모터 퍽오프 신호의 분수배(fractional multiple) 주파수일 수 있다. 이러한 구현은 디지털 시스템에서 전이가 클럭 신호의 에지에서만 일어난다는 사실과 관련된 오류를 가질 수 있다. 또한, 데이터 대기시간 및 자이로스코프로부터의 아날로그 신호를 디지털 정보로 변환하는데 사용하는 아날로그-디지털 변환기의 제한된 정밀도 때문에 오차가 있을 수 있다. 데이터 대기시간 및/또는 오차는 디지털 신호 처리를 이용하여 효과적으로 보상되거나 제거될 수 있다.

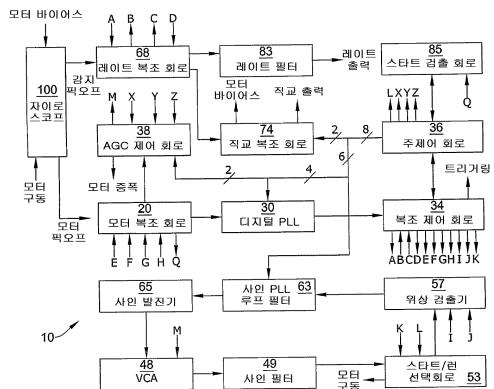

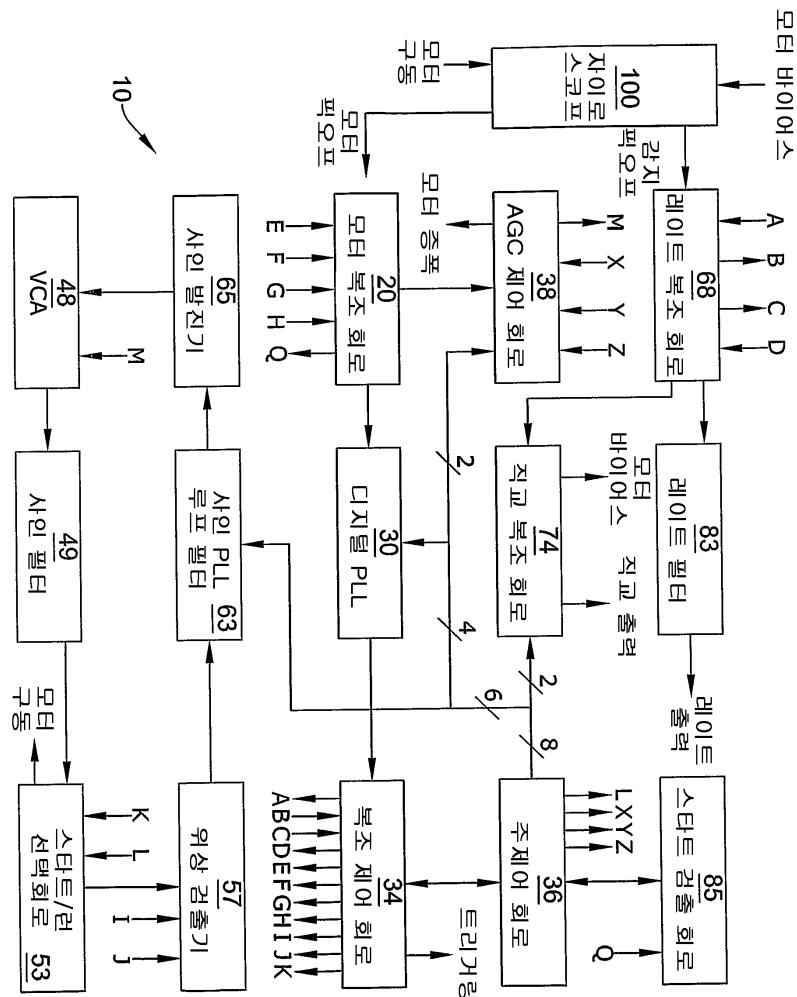

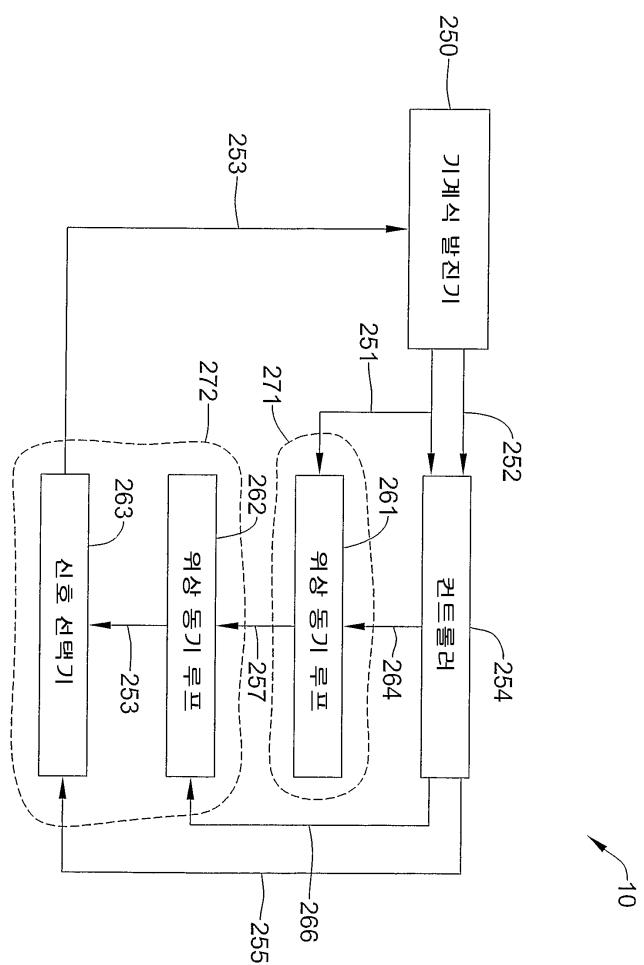

[0026] 도 1 내지 16은 자이로스코프 제어 전자 회로(10)의 블록도 및 회로도이다. 회로(10)의 동작 방법에 대한 개관을 위하여, 모든 루프가 단락되고 모든 것이 이미 동작하고 있다는 가정으로부터 시작할 수 있다. 도 1은 전체 회로(10)에 대한 블록도이다. 도 2 내지 14는 회로도가 전자 회로(10)의 개념을 제공할 수 있게 합쳐질 수 있도록 식별 가능한 서로의 연결부를 갖는 다양한 회로들을 도시한다. 회로(10)의 구성은 도 1에 도시된다; 그러나, 본 발명을 구현하는데 사용될 수 있는 도 17의 회로(210)와 같은 이 구성에 대한 변형물이 있을 수 있다.

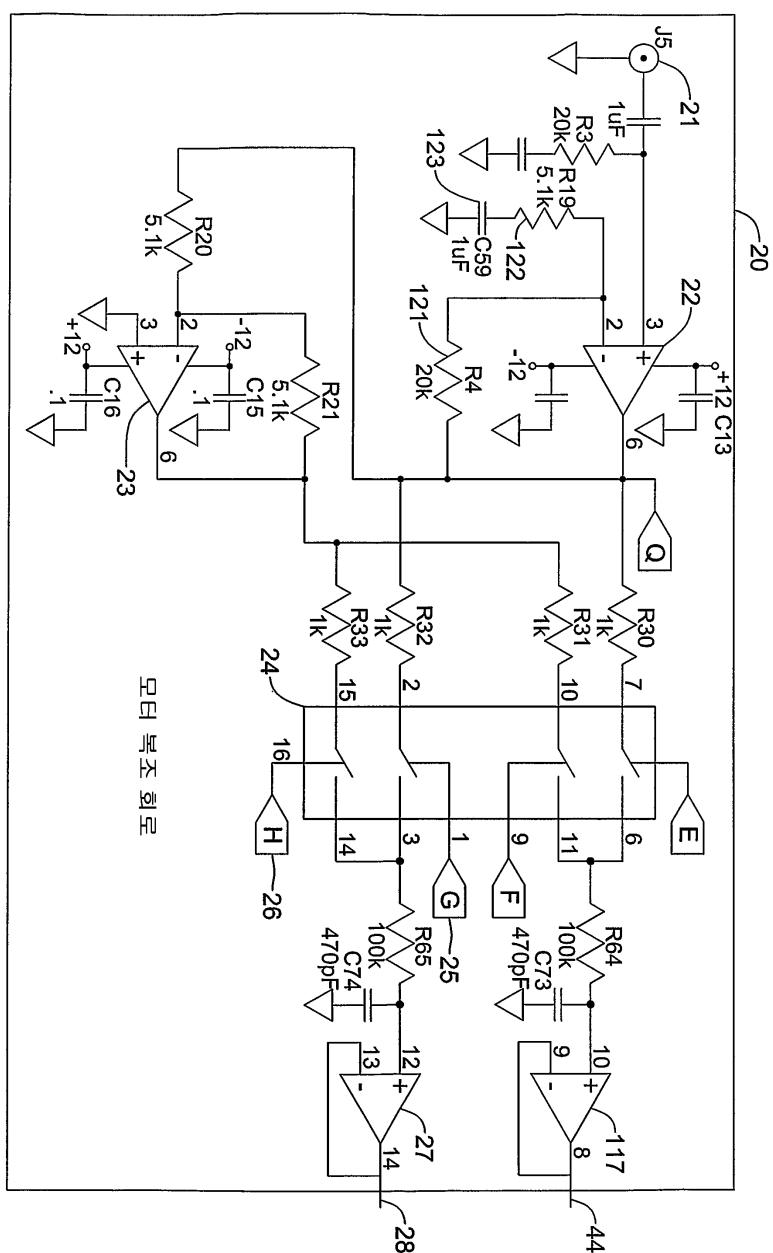

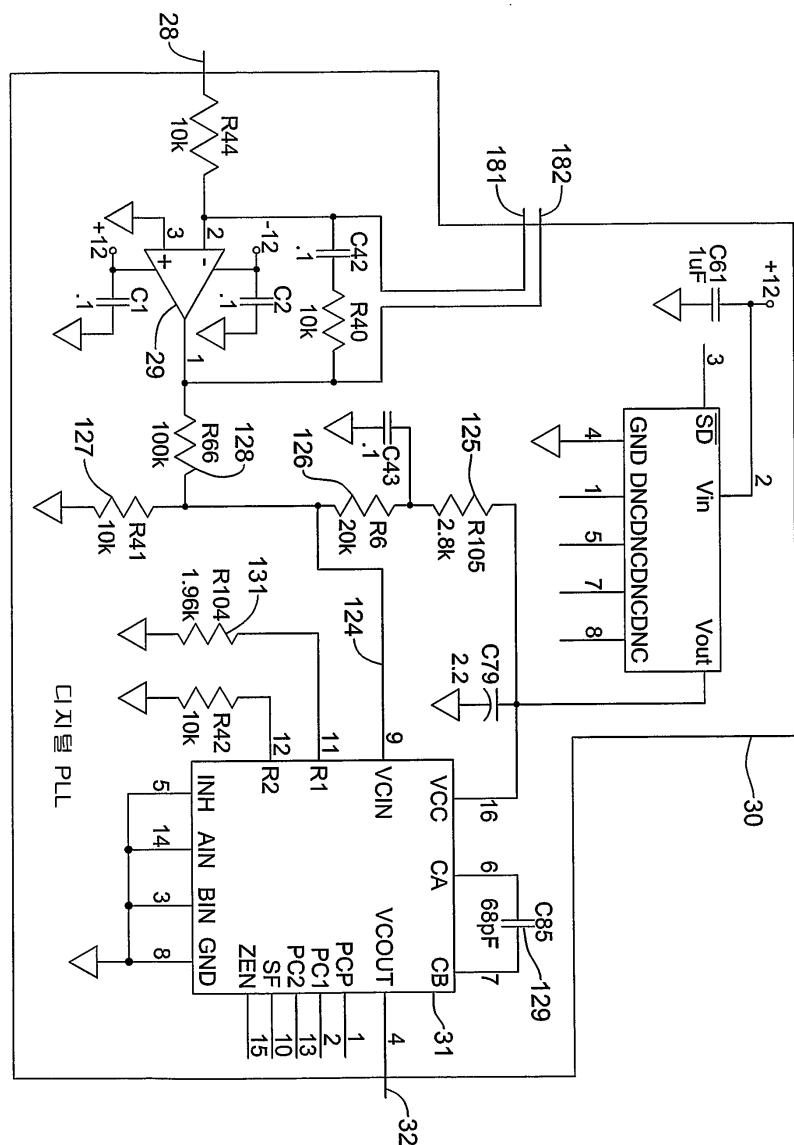

[0027] 도 2에서, 모터 퍽오프 신호는 입력부(21, J5)에서 유입될 수 있으며, 도 2의 모터 복조 회로(20)의 증폭기(22)에 의해 증폭될 수 있다. 증폭기(23)는 이 신호의 반전 신호를 제공할 수 있다. 이 신호는 동기 복조기 역할을 하는 장치(24)로 갈 수 있으며, 따라서 그 하부 절반은 위상 동기 루프에서의 위상 검출기 역할을 한다. 신호(25, G) 및 신호(26, H)는 직교 복조를 위한 직교 스위칭 신호를 제공할 수 있다. 장치(24)의 출력은 증폭기(27)로 갈 수 있다. 출력(28)은 위상 동기 루프에서 루프 필터 역할을 하는 증폭기(29)로 갈 수 있다. 증폭기(29)는 도 3의 디지털 PLL 회로(30)의 증폭기(29)일 수 있다. 증폭기(29)는 적분기일 수 있기 때문에, 모터의 주파수가 전압 제어 발진기의 공주 주파수(free running frequency)와 같지 않더라도 이 증폭기는 정상 상태 위상 오차를 가지지 않는 위상 동기 루프 종류일 수 있다. 증폭기(29)의 출력은 장치(31)의 전압 제어 발진기

에 영향을 미치는 전압일 수 있다. 장치(31) 자체는 위상 동기 루프이지만, 사용되는 그 전체는 VCO일 수 있으며, 따라서, 이것은 위상 동기 루프 역할을 하지 않을 수 있다. 이 VCO의 출력(32)은 도 4의 복조 제어 회로(34)의 장치(33)의 클럭 주파수를 제어할 수 있다. 장치(33)는 모든 스위칭 신호를 생성할 수 있다. 따라서, 0 위상 에러를 갖는 모터 구동신호에 위상 동기된 모터 구동 주파수 및 모터 구동 주파수의 1/2에서의 완전한 스위칭 신호 합성이 있을 수 있다.

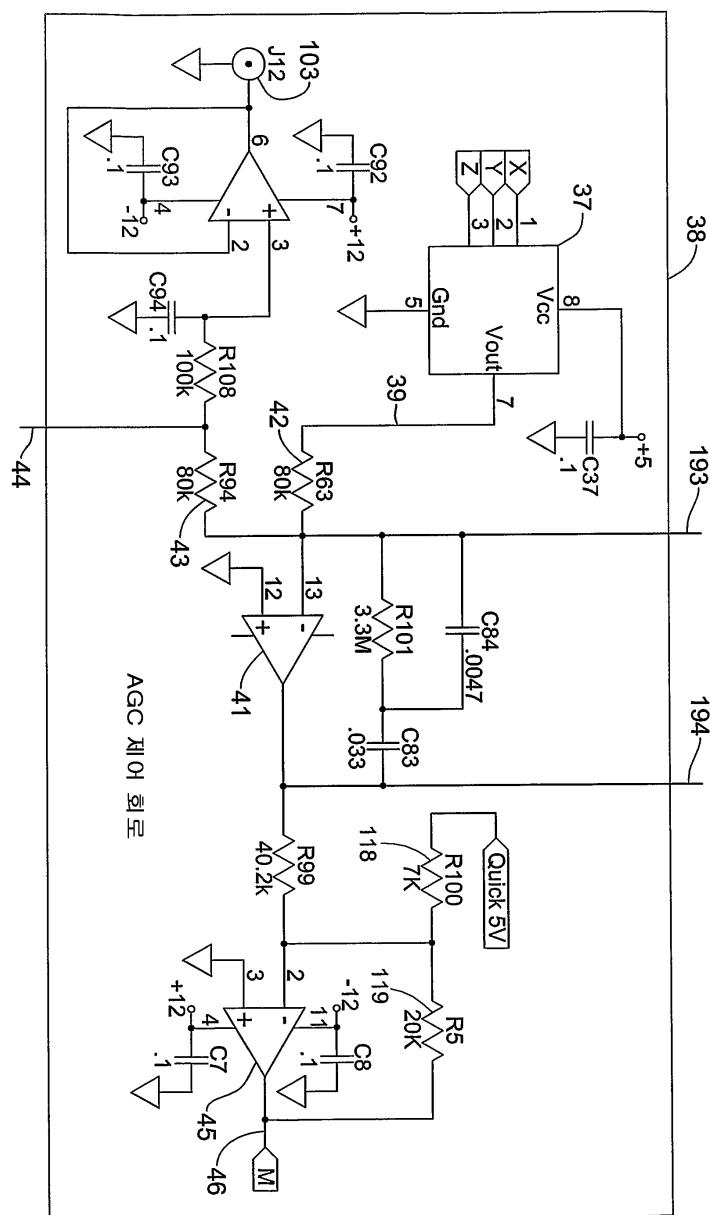

[0028] 장치(24)의 상부 절반은 모터 핀오프로부터의 신호를 다시 복조할 수 있지만 이 복조는 동상일(in phase) 수 있으며, 따라서 모터 구동 신호의 크기를 나타내는 DC 신호를 생성할 수 있다. 컴퓨터가 도 5의 주 제어 회로(36)의 장치(35)(즉, 제어 마이크로 컨트롤러)로 데이터를 보내고, 마이크로 컨트롤러(35)가 D/A 컨버터(37)의 출력(39)이 2 볼트가 되도록 도 6의 AGC 제어 회로(38)의 D/A 변환기(37)에 데이터를 보낸다고 가정할 수 있다. 증폭기(41)는 저항(42, 즉 R63)을 통해(D/A 변환기(37)로부터) 흐르고 저항(43, 즉 R94)을 통해(회로(20)의 동상 복조기로부터 선(44)을 통해) 흐르는 전류를 비교할 수 있다. 이 전류들이 동일하지 않고 반대라면, 증폭기(41)의 출력은 변경될 수 있다. 또한, 이것은 증폭기(45)의 출력(46)에서의 전압을 변경시킬 수 있으며, 이는 도 7의 회로(48)의 전압 제어 증폭기(voltage controlled amplifier, VCA)(47)의 이득을 변경한다. 따라서, 사인파 발진기로부터의 신호는 사인 필터(49)와 선(52)을 통한 도 8의 모터 구동 출력(51), 스타트/런 선택 회로(53)의 장치(59) 및 증폭기(54)로 가기 전에 VCA에 의해 조정될 수 있다. 따라서, AGC 시스템(38)은 모터 복조 회로(20)의 입력(21)에서 모터 핀오프 신호의 특정 크기를 검사할 수 있으며, 이 크기가 얻어질 때까지 VCA(48)를 조정할 수 있다.

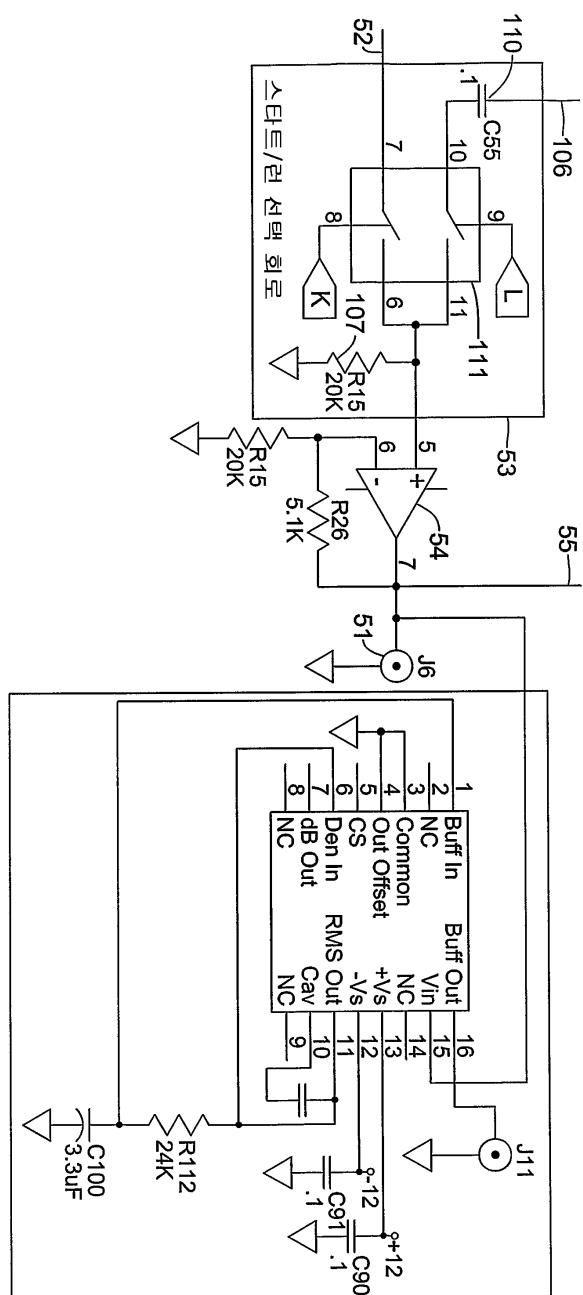

[0029] 선(55)을 통한 출력(51, 즉 J6)에서의 모터 구동 신호는 도 9의 위상 검출기(57)의 증폭기(56)에 의해 반전될 수 있으며, 장치(58)는 다른 복조기 역할을 할 수 있다. 장치(33)는 모터 구동 주파수의 절반에 있는 장치(61)를 통해 스위칭 신호(I, J)를 제공할 수 있다. 이 복조기는 제2 위상 동기 루프에서의 위상 검출기 역할을 할 수 있다. 도 9의 사인 PLL 루프 필터 회로(63)의 증폭기(62)는 이러한 위상 동기 루프를 위한 루프 필터일 수 있으며, 또한, 0의 정상 상태 위상 오차를 갖는 종류를 구비할 수 있다. 이 루프 필터의 출력(64)은 사인파 발진기(65)의 주파수를 제어할 수 있다. 다른 PLL의 경우와 같이, 사인파는 복조기로부터의 스위칭 신호에 직교되어 동기될 수 있다. 장치(33)는 그 직교 관계를 고려하고 입력(21)에서 모터 핀오프로부터의 신호에 대한 적합한 관계를 보유하는 모터 주파수의 1/2로 사인파를 공급하는 방법으로 위상을 갖는 스위칭 신호를 생성한다.

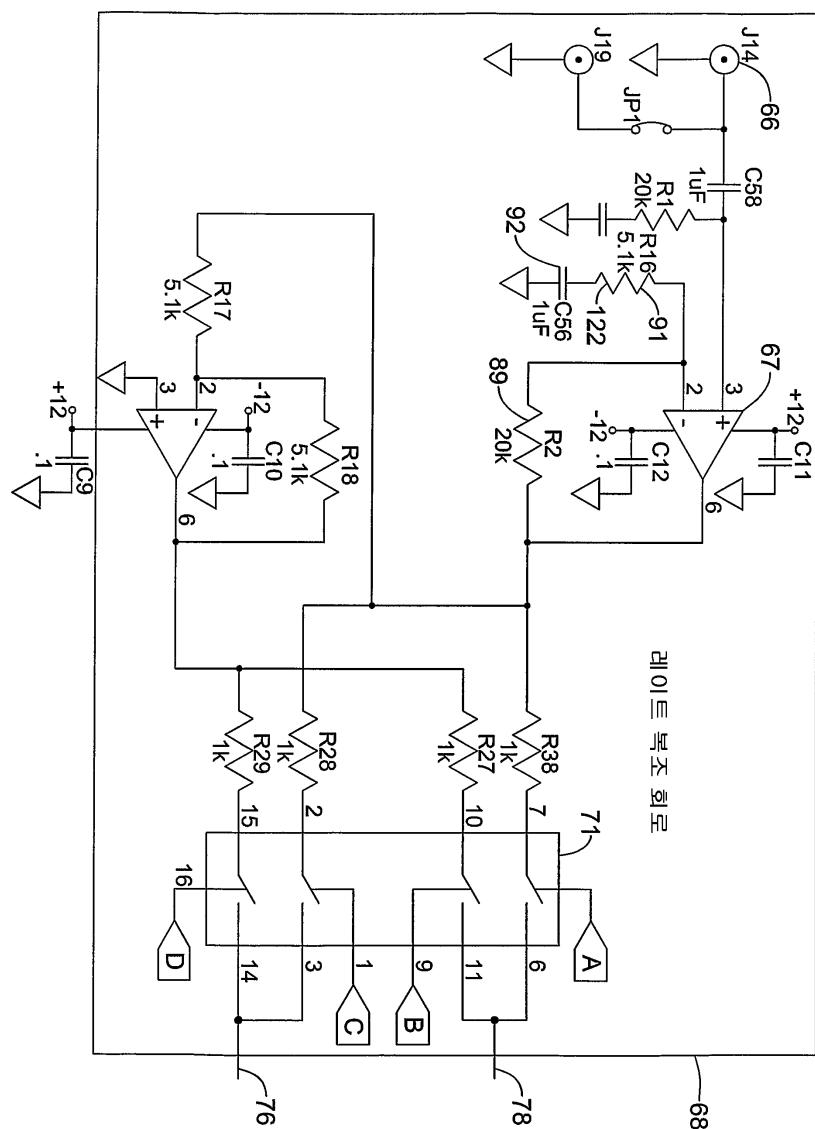

[0030] 레이트 신호(rate signal)는 입력(66, 즉 J14)으로 들어와서 도 11의 레이트 복조 회로(68)의 증폭기(67)에 의해 증폭될 수 있다. 증폭기(69)는 이 신호의 반전 신호를 제공할 수 있다. 장치(71)는 입력(21)의 모터 핀오프 신호에 대하여 수행된 바와 같이 동상 및 직교 복조 모두에 대한 동기 복조기 역할을 할 수 있다. 장치(75)로부터의 신호(C 및 D)는 직교 복조를 위한 직교 스위칭 신호를 제공할 수 있으며, 선(76) 상의 복조된 신호는 도 12의 직교 복조 회로의 출력(73, 즉 J4)에서 모터 바이어스 신호를 제공하기 위하여 증폭기(77)를 경유하여 적분기(72)를 통해서 진행한다. 장치(75)로부터의 신호(A 및 B)는 레이트 복조를 위한 동상의 스위칭 신호를 제공할 수 있으며, 장치(71)로부터의 선(78) 상의 복조된 신호는 도 13의 레이트 필터 회로(83)의 출력(82, 즉 J3)에서 레이트 출력 신호를 제공하기 위하여 증폭기(79)를 경유하여 증폭기(81)를 통해 진행할 수 있다.

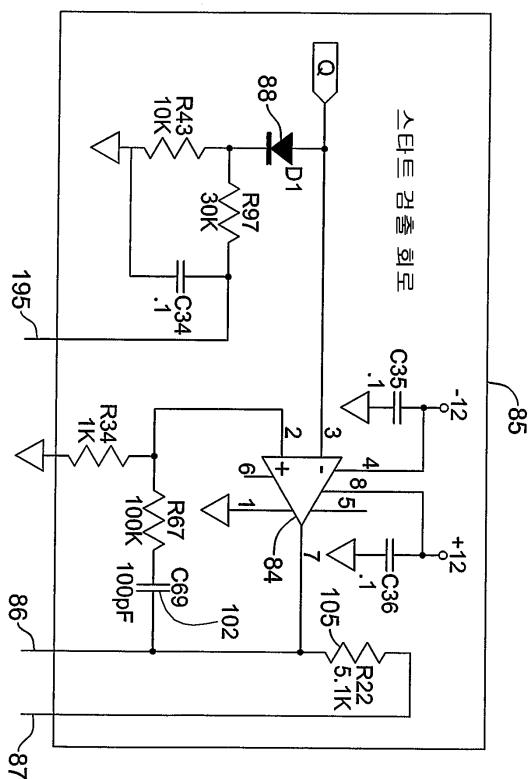

[0031] 입력(21, 즉 J5)으로부터의 증폭된 모터 핀오프 신호는 증폭기(22)의 출력에서 나와 도 14의 스타트 검출 회로(85)의 비교기(84)로 Q 신호로서 갈 수 있다. 비교기(84)는 신호를 선(86 및 87)을 통해 마이크로 컨트롤러(35)로 가는 구형파로 변환할 수 있어, 마이크로 컨트롤러는 의사 구형파(pseudo square wave) 구동을 동기화할 수 있으며, 적합한 크기까지 신호를 구동할 수 있다. 다이오드(88, D1)와 관련된 네트워크는 증폭기(22)로부터의 모터 핀오프 신호의 크기에 관련된 DC 신호를 제공할 수 있다. 마이크로 컨트롤러(35)가 적절한 레벨을 검출할 때, 사인파 구동으로 스위칭될 수 있다.

[0032] 다음은 자이로스코프 제어 전자장치에 대한 전체 회로의 다양한 부분의 상세에 대한 설명이다. 도 11의 레이트 복조 회로(68)에 대하여, 신호는 증폭기(67)의 비반전 입력에 연결된 AC일 수 있다.  $1 \mu\text{F}$ 의 커패시터(92, 즉 C56)의 임피던스는 저항(91, 즉 R16)의 임피던스에 비하여 매우 낮기 때문에, 이득은 저항(89, 즉 R2)과 저항(91, 즉 R16)의 비(즉,  $20\text{k}\Omega \div 5.1\text{k}\Omega$ )에 1을 더한 것일 수 있다. 커패시터(92, 즉 C56)는 증폭기(67)의 이득을 DC에서 1로 만들기 위하여 있으며, 따라서 출력 오프셋은 입력 오프셋 전압에 주로 종속한다. 더 낮은 신호 레벨을 갖는 센서를 사용하는 경우, 매우 높은 이득이 사용되어야만 한다면 이 단(stage)의 이득을 증가시키고 보상되지 않은 연산 증폭기로 스위칭될 수 있다.

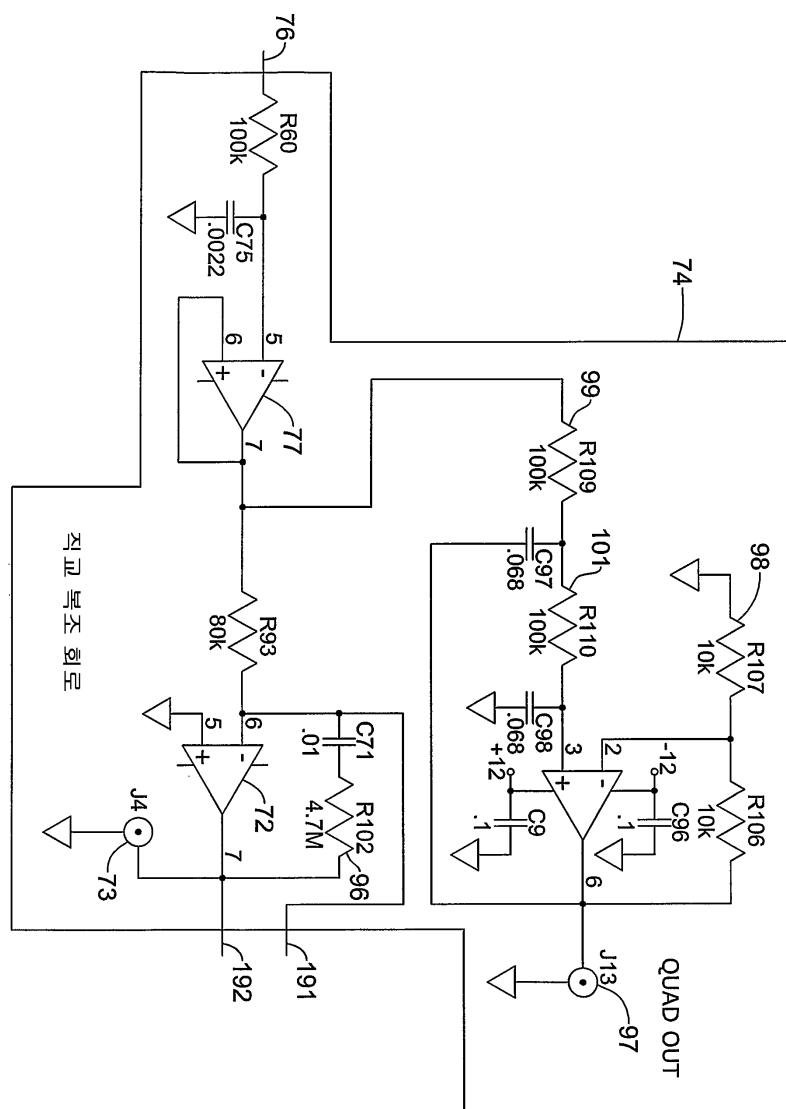

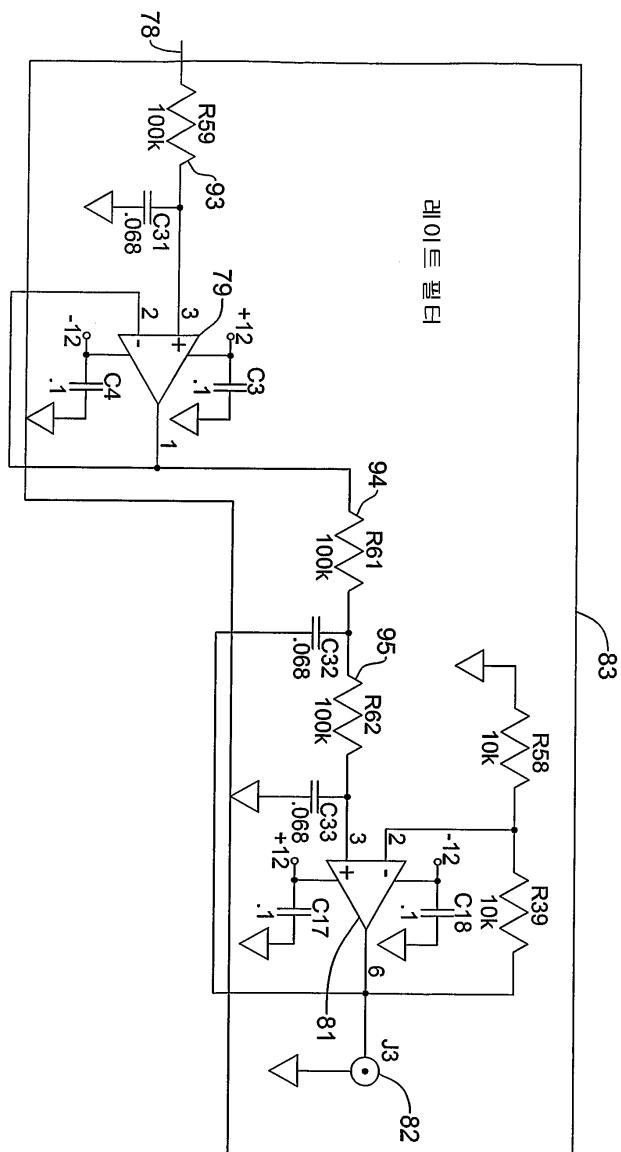

[0033] 도 13의 레이트 필터(83)는 3차 버터워스 필터일 수 있다. 개략도는 23.5Hz의 원 차단 주파수 성분을 도시하지

만, 250Hz의 주파수 대역을 원할 수 있다. 235Hz로 대역을 증가시키기 위해서, 100k $\Omega$ 의 저항(93, 즉 R59), 저항(94, 즉 R61) 및 저항(95, 즉 R62)은 각각 10k $\Omega$  저항으로 대체될 수 있다. 이 대신에, 258Hz의 대역을 얻기 위해 10k $\Omega$  저항이 100k $\Omega$  저항(93, 94, 95)의 상부에(즉, 병렬로) 설치될 수 있다.

[0034] 직교 복조 회로(74)는 레이트 채널로부터의 복조된 직교 신호가 DC 성분을 가지지 않을 때까지 출력(73)에서의 모터 바이어스를 조정하는 적분기일 수 있다. 적분기 주위의 부품들은 고속 응답 및 적합한 감쇠 응답을 위하여 선택될 수 있다. 전체적인 효과가 좋게 나타나더라도, 원하지 않는 AC 신호량이 모터 바이어스 신호에서 나타날 수 있으며, 따라서, 4.7M $\Omega$  저항(96, 즉 R102)을 가로질러 커패시터를 놓을 수 있다. 470 내지 1000 pF 사이의 값이 좋을 것이다. 또한, 직교 널 루프(quadrature null loop)가 활성화될 때 접지되며, 이에 따라 관심 대상이 아니기 때문에, 잘 알려진 목적을 위하여 복조된 신호는 3극 로우 패스 필터를 지나고 직교 출력(97, 즉 J13)으로 갈 수 있다. 제1 극(77)은 직교 널 루프를 불안정하게 할 수 있는 위상 시프트를 추가하는 것을 방지하기 위하여 더 높은 주파수(723Hz)에 있을 수 있다. 이것은 제1 극이 많은 역할을 하지 않기 때문에 필터를 2극 필터와 유사하게 작용하도록 할 수 있다. 이 때문에 그리고 저항(98, 즉 R107)의 값을 10k $\Omega$ 에서 17.4k $\Omega$ 로 증가시켜서 제거될 수 있는 이득 피크를 갖기 때문에, 제2차 부분은 바르게 설정되지 않을 수 있다. 100k $\Omega$ 의 저항(99, 즉 R109) 및 저항(101, 즉 R110)은 248Hz 대역을 주기 위하여 9.5k $\Omega$  저항으로 대체될 수 있지만, 10k $\Omega$  저항을 사용하는 것은 235Hz를 주며, 10k $\Omega$ 의 저항을 100k $\Omega$ 의 저항(99 및 101)의 상부에(즉, 병렬로) 놓는 것은 레이트 필터(83)의 경우와 같이 258Hz를 줄 수 있다.

[0035] 스타트 검출 회로(85)는 모터 핀오프 신호에서 구형파를 만들어 구형파를 선(86 및 87)을 통해 주 제어 회로(36)의 장치(35)에 공급할 수 있어, 의사 구형파 구동을 모터 핀오프로부터의 신호에 위상 동기할 수 있다. 비교기(84)는 DC 히스테리시스를 이용할 때 (100pF의 커패시터(102, 즉 C69)를 제거함으로써) 발생할 수 있는 위상 시프트를 야기시키지 않으면서 발진을 방지하기 위하여 AC 히스테리시스를 가질 수 있다. 다이오드(88, D 1)를 갖는 네트워크는 모터 핀오프 신호(Q)의 크기를 나타내는 DC 신호를 생성하는데 사용될 수 있다. AGC 제어 회로(38)의 잭(103, 즉 J12)에서 나오는 모터의 크기가 같은 것일 수 있지만, 다이오드 네트워크는 모든 루프가 스타트 모드에 동기되지 않았을 때 작동하여야만 한다.

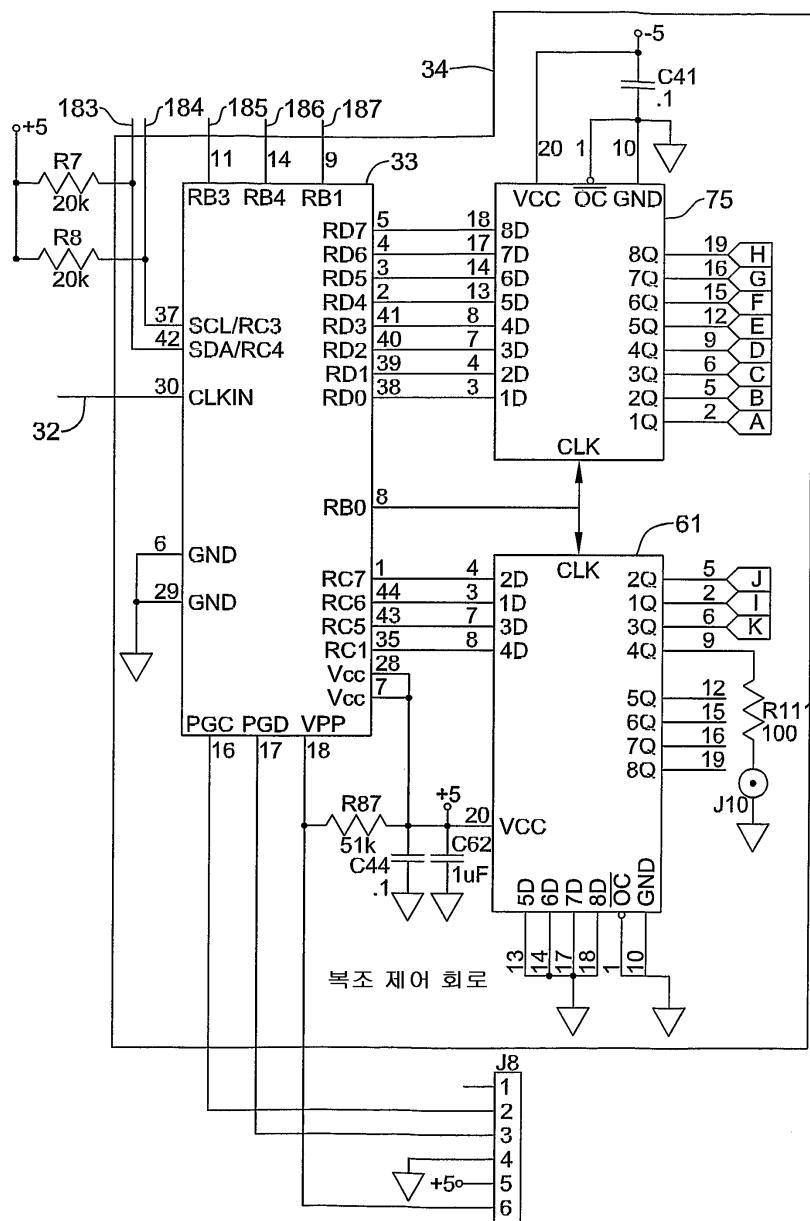

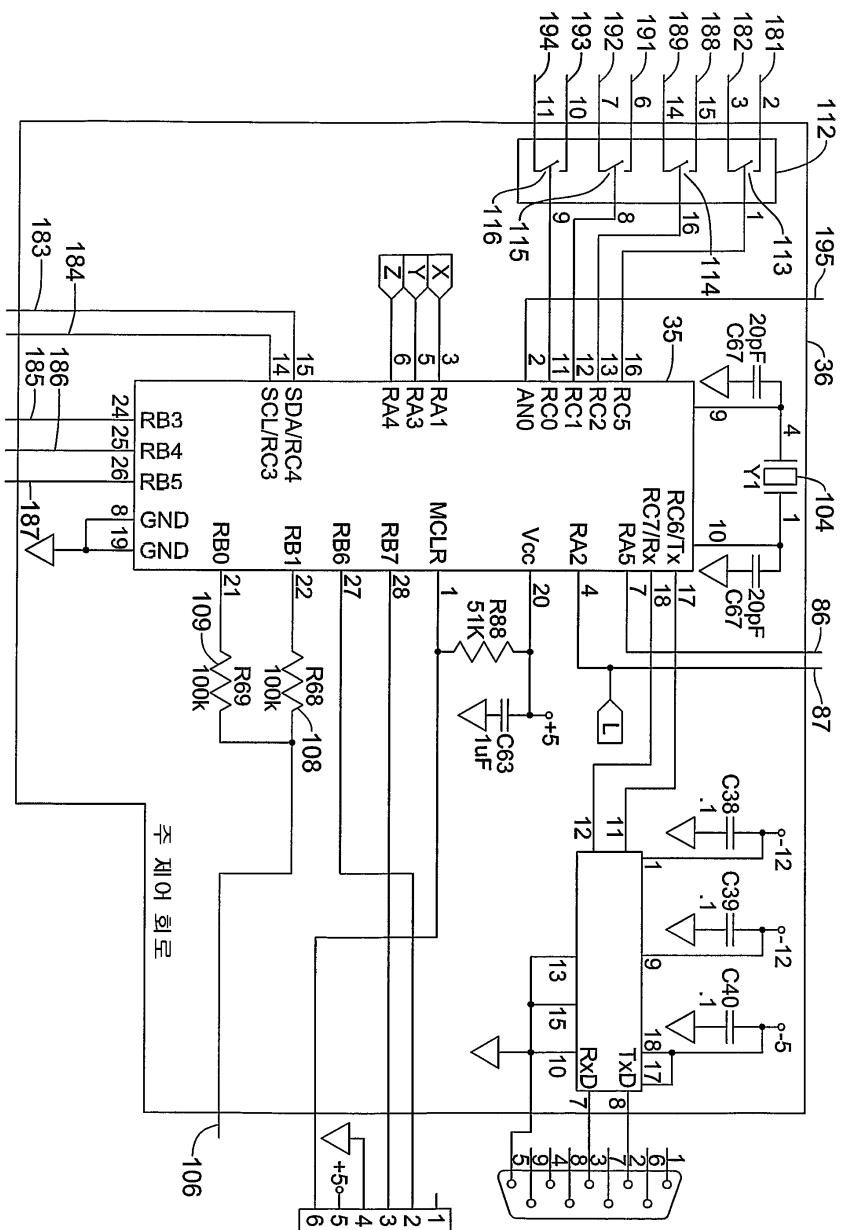

[0036] 도 5의 주 제어 회로(36)는 18.432MHz 크리스탈(104)에서 실행되는 16F876A 마이크로 컨트롤러(35)를 가질 수 있다. 주파수는 10kHz 센서를 사용할 때 다른 마이크로 컨트롤러가 실행되는 주파수인 4MHz와 떨어져서 이 주파수의 고조파가 유지되도록 선택될 수 있다. 주 제어 회로(36)에서 복조 제어 회로(34)로 가는 여러 가지 신호가 있다. 스타트/런 제어는 복조 제어 회로(34)가 제어되는 스타트/런 선택 회로(53)의 일부를 어떻게 다루어야 하는지를 알려준다; 좌/우 제어는 왼쪽 또는 오른쪽 핀오프 신호 중 하나를 수용하기 위하여 복조기의 일부에 대하여 어느 극성을 사용하여야 하는지를 복조 제어 회로에 알려준다; 그리고, 사이클 모드 선(cycle mode line)은 복조 제어 회로에 사이클 스kip 방법을 사용해야 하는지 아닌지에 대한 여부를 알려준다. 또한, 주 제어 회로(36)는 스타트/런 선택 회로(53)의 일부를 제어할 수 있다. 스타트 모드에서, 마이크로컨트롤러(35)의 RA2의 출력(L)은 의사 구형파 구동을 모터 구동 증폭기(54)에 연결할 수 있으며, 동일한 신호는 5.1k $\Omega$  저항(105, 즉 R22)을 풀업(pull-up)하기 위하여 +5V를 제공할 수 있다. 이것은 회로가 스타트 모드일 때만 비교기(84)의 출력이 활성화되도록 함으로써 회로 보드 상에서 노이즈를 감소시키도록 수행될 수 있다. 마이크로 컨트롤러(35)의 출력(RB0 및 RB1)은 출력이 모두 로우이거나, 서로 상이하거나, 또는 모두 하이인 것 중 하나를 출력하게 함으로써 의사 구형파를 생성하는데 사용될 수 있다. 출력(RB0, 즉 RB1)은 각각 100k $\Omega$  저항(108, 즉 R68 및 109, 즉 R69)을 통해 선(106)에 연결될 수 있으며, 이 선(106)은 0.1  $\mu$ F 커패시터(110, 즉 C55)와 스타트/런 선택 회로(53)의 장치(111)를 통해 증폭기(54)로 간다. 이것은 증폭기(54)에 의해 증폭될 때 너무 크지 않도록 20k $\Omega$  저항(107, 즉 R15)(54에 의해)에 의해 감쇠된 3 레벨 파형을 공급할 수 있다. 의사 구형파 구동의 주파수는 마이크로 컨트롤러(35) 상의 EEPROM 레지스터 중 하나의 내용에 의해 결정된다. 주파수는 4,608,000/[4\*(수 + 22)]일 수 있지만, 주파수를 변경하기 위한 선택 사항을 사용하는 경우 소프트웨어가 알아낼 수 있기 때문에 이것을 알 필요는 없다. 주 제어 회로(36)는 장치(112)의 4개의 스위치가 개방되는지 또는 단락되는지를 결정할 수 있으며, 이것은 스위치(113)의 디지털 PLL(30)의 루프, 스위치(114)의 사인 PLL 루프 필터(63), 스위치(115)의 직교 복조 회로(74) 및 스위치(116)의 AGC 제어 회로(38)가 활성화되는지 또는 아이들(idle) 상태가 되는지를 결정할 수 있다.

[0037] 복조 제어 회로(34)는 장치(31)로부터 선(32)을 따른 전압 제어 발진기로부터 주파수를 취하여 모터 핀오프(21) 주파수 및 모터 구동(51) 주파수 모두에서 복조기에 대한 제어 신호를 생성한다. 주 제어 회로(36)로부터 나오는 3개의 신호가 있다. 스타트/런 제어는 복조 제어 회로가 제어되는 스타트/런 선택 회로(53)를 어떻게 다루어야 하는지를 알려준다; 좌/우 제어는 왼쪽 또는 오른쪽 핀오프 신호 중 하나를 수용하기 위하여 복조기의 일

부에 대하여 어느 극성을 사용하여야 하는지를 복조 제어 회로에 알려준다; 그리고, 사이클 모드 선(cycle mode line)은 복조 제어 회로에 사이클 스윕 방법을 사용해야 하는지 아닌지에 대한 여부를 알려준다. 가정은 12C 버스를 사용하는 마이크로 컨트롤러 사이의 통신에 대하여 이루어질 수 있다. 하나의 가능성 있는 사용은 클럭과 제어 신호 상의 분배비를 설정하는 것일 수 있다. 이러한 특징을 사용하더라도, 4개의 분배비 중 하나를 선택하고 12C 방식을 사용하지 않기 위하여 2개의 디지털 선으로서 핀을 사용할 수 있다.

[0038] AGC 제어 회로(38)에 대하여, 모터 핀오프(21) 신호에 대한 동상의 복조는 모터 구동 신호의 크기를 나타내는 증폭기(117)의 출력(44)에서 DC 전압을 제공할 수 있다. 이 신호는 추가로 필터링되어 출력(103, 즉 J12)(MRT Amp OUT)으로 보내어 질 수 있다. 또한, 신호는 증폭기(41)가 DAC(37)로부터 선(39)를 따라 저항(42, 즉 R6 3)을 통해 나오는 전류와 비교하는 전류를 저항(43, 즉 R94)을 통해 공급할 수 있다. 적분기(41)의 출력은 컴퓨터에 의해 설정될 수 있는 원하는 크기와 동일한 감지된 크기를 얻기 위하여 어느 곳이라도 갈 수 있다. 주제어 회로(36)가 적분기(41)에 가로질러 있는 스위치(116)를 단락하면, 그 출력은 대략 0 볼트일 수 있으며, 따라서, 증폭기(45)의 출력은 저항(118, 즉 R100) 및 저항(119, 즉 R5)에 의해 결정될 수 있다. 값은 AGC가 비활성 상태에 있을 때, VCA(48)의 이득이 신호(M)를 통해 적절하도록 선택될 수 있다. 이것은 다른 센서에 대하여 변경될 수 있는 종류이다. 예를 들어, 이득이 센서를 과구동하면, 루프가 동기되고 부품들을 작동하는 것이 힘들 것이다.

[0039] 모터 복조 회로(20)에 비하여, 모터 핀오프 입력(21)으로부터의 신호는 증폭기(22)의 비반전 입력에 AC 연결될 수 있다.  $1.0\mu F$  커패시터(123, 즉 C59)의 임피던스가 저항(122, 즉 R19)의 임피던스에 비하여 매우 작기 때문에, 이득은  $20k\Omega$  저항(121, 즉 R4) 및  $5.1k\Omega$  저항(122, 즉 R19)의 비(즉 R4/R19)에 1을 더한 것일 수 있다. 커패시터(123, 즉 C59)는 증폭기의 이득을 DC에서 1에 동일하게 하도록 제공될 수 있으며, 이에 따라, 출력 오프셋은 입력 오프셋 전압에 주로 종속할 수 있다. 더 낮은 신호 레벨을 갖는 센서를 사용하면, 이 단계의 이득을 증가시키고 매우 큰 이득을 위하여 보상되지 않은 연상 증폭기로 스위칭되기를 원할 수 있다.

[0040] 디지털 PLL(30)에 대하여, 증폭기(29)는 디지털 PLL용 루프 필터일 수 있다. 장치(112)의 스위치(113)가 루프 필터를 가로질러 단락될 때, 출력은 접지에 있을 수 있다. 그 다음, 선(124)을 따른 전압 제어 발진기(31, 핀 9)의 입력으로의 전압은 상부의  $2.8k\Omega$  저항(125, 즉 R105)과  $20k\Omega$  저항(126, 즉 R6)의 직렬 조합 및 하부의  $10k\Omega$  저항(127, 즉 R41) 및  $100k\Omega$  저항(128, 즉 R66)의 병렬 조합에 의해 형성된 감쇠기에 의해 결정될 수 있다. 복조 제어 회로(34)에서의 코드는 모터 핀오프 주파수가 대략  $10kHz$ 일 때 장치(31)의 VCO 주파수가 대략  $4MHz$ 가 되도록 작성될 수 있다. 가정은 센서 주파수가 상당히 변한다면 복조 제어 회로에서의 코드를 변경한다는 것일 수 있다. 이것이 불편하기 때문에, 아마도 주파수에서의 큰 변경을 위하여  $85pF$ 의 커패시터(129, 즉 C85)의 값을 변경하고 약간의 개조를 위하여는 저항(127, 즉 R41)의 값을 변경할 수 있을 것이다. 74HC4046A 칩은 장치(31)의 74HC4046 칩과는 다른 특성을 가질 수 있다. A 버전은 더 빠르며, 이에 따라 더 높은 주파수 센서를 수용하기 위하여 단순히 빨라지기를 원할 수 있다. 다른 선택 사항은  $1.96k\Omega$  저항(131, 즉 R104)의 값을 변경하여 주파수를 변경할 수 있다. 입력에서의 전압을 전압 범위의 중심(즉, 2.5 볼트) 근처에 유지시키는 것이 좋을 수 있기 때문에, 이것은 입력에서의 전압 분배기 네트워크 근처에서 동작하는 것보다 더 편할 수 있다.

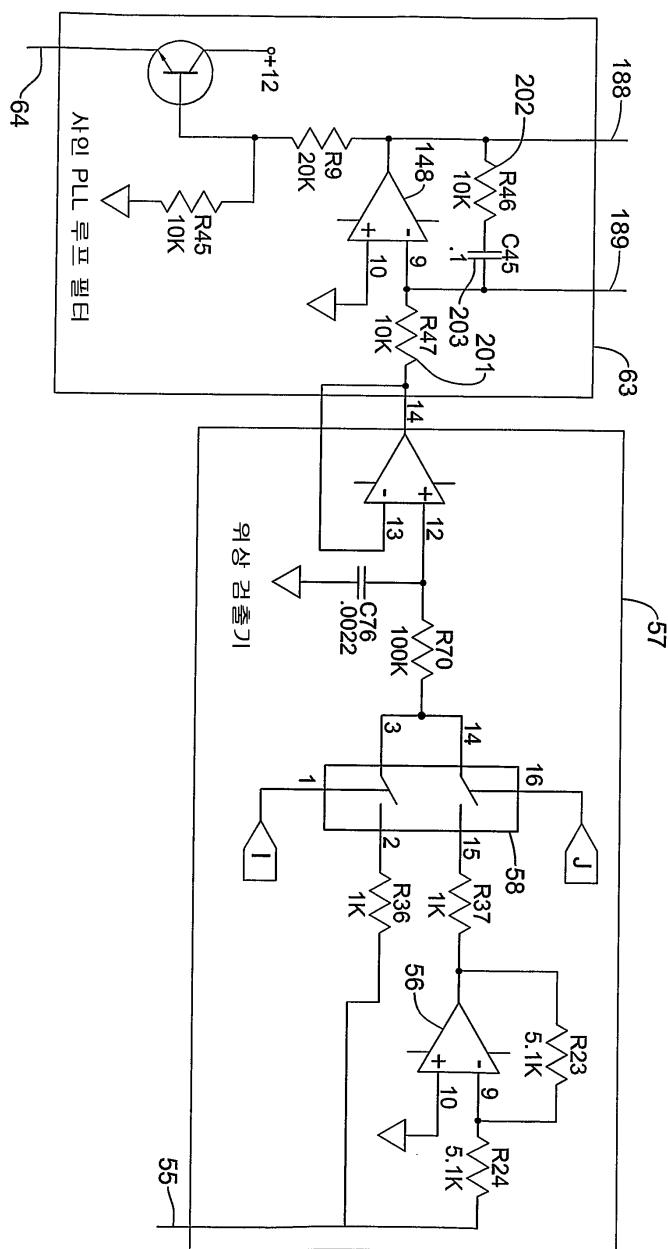

[0041] 사인파 발진기(65)는 3단 위상 시프트 발진기일 수 있다. 각각 60도의 위상 시프트를 제공하는 3개의 위상 시프트 단(132, 133, 134)과 180도의 위상 시프트를 제공하는 인버터(135)가 있을 수 있으며, 필요에 따라 루프 주위 전체로 360도를 만들 수 있다. 단들(132, 133, 134, 135)은 LM13700 칩을 사용할 수 있다. 상호 컨택턴스 증폭기는 전류 제어 저항과 같은 역할을 할 수 있다. 제1 단(132)에서, 선(136, 핀 16)으로의 전류는 선(138, 핀 13) 및 선(139, 핀 14)에 걸린 차분 전압에 비하여 선(137, 핀 12)으로 나오는 전류의 이득을 제어할 수 있다.  $1000pF$ 의 커패시터(176, 즉 C64)는 60도의 위상 시프트를 갖는 RC 로우 패스부를 형성하기 위하여 전류 제어 저항과 함께 동작할 수 있다. 달링턴 트랜지스터 쌍(141)은 신호를 버퍼링할 수 있으며, 따라서, 단들은 서로 부하를 주지 않는다. 제1 단(132)으로부터의 신호는 선(142)으로부터 정류기(143)로 갈 수 있으며, 적분기(144)는 정류기(143)의 평균 DC 출력을  $470k\Omega$  저항(145, 즉 R103) 및  $30k\Omega$  저항(146, 즉 R98)이 제공하는 대략 0.3V이 기준전압에 비교하고, 그 다음 오차 전압을 적분할 수 있다. 적분기(144)의 출력은 위상 시프트 발진기의 인버터 단(135)에서 선(147)을 통해 이득을 제어할 수 있으며, 이에 따라 사인파의 크기가 왜곡을 최소화하기 위하여 매우 낮은 레벨로 제어된다. 적분기를 가로지르는 스위치(114)가 단락되기 때문에 증폭기(148)의 출력이 접지되는 때인 비동기 상태에 PLL 회로(63)가 있을 때, 사인파 발진기(65)는 모터 구동 주파수로 발진하도록 설정될 수 있다. 발진기(65)의 주파수는  $1000pF$ 의 커패시터(137, 즉 C64), 커패시터(149, 즉 C65) 및 커패시터(151, 즉 C66)의 값을 변경하거나(그러나 그 값을 동일하게 유지하면서),  $51k\Omega$  저항(152, 즉 R82), 저항(153, 즉 R83) 및 저항(154, 즉 R84)의 값을 변경함으로써(그러나 그 값을 동일하게

유지하면서) 조정될 수 있다. 선(136, 핀 16) 또는 선(155, 핀 1)으로의 전류에 대한 최대 정격은 대략  $2\text{mA}$ 이다. 이 부분들이 매우 약하기 때문에  $2\text{mA}$ 는 이것들을 손상시킬 수 있다. 심지어  $1\text{mA}$ 도 이들을 통과하도록 해서는 안된다. 저항(152, 즉 R82)으로  $51\text{k}\Omega$ 을 사용하여, 전원 공급 회로가 선(136, 핀 16)으로 공급할 수 있는 최대 전류는 대략  $0.5\text{ mA}$ 이며, 이는 적절한 것으로 보인다. 주파수를 2배로 하기 위해서는, 커패시터의 값을 절반으로 할 수 있다. 발진기(65)의 주파수는(아이들 상태에서) 위상 동기 루프가 신속하고 신뢰성 있게 동기 되도록 모터 주파수에 가까워야만 한다.

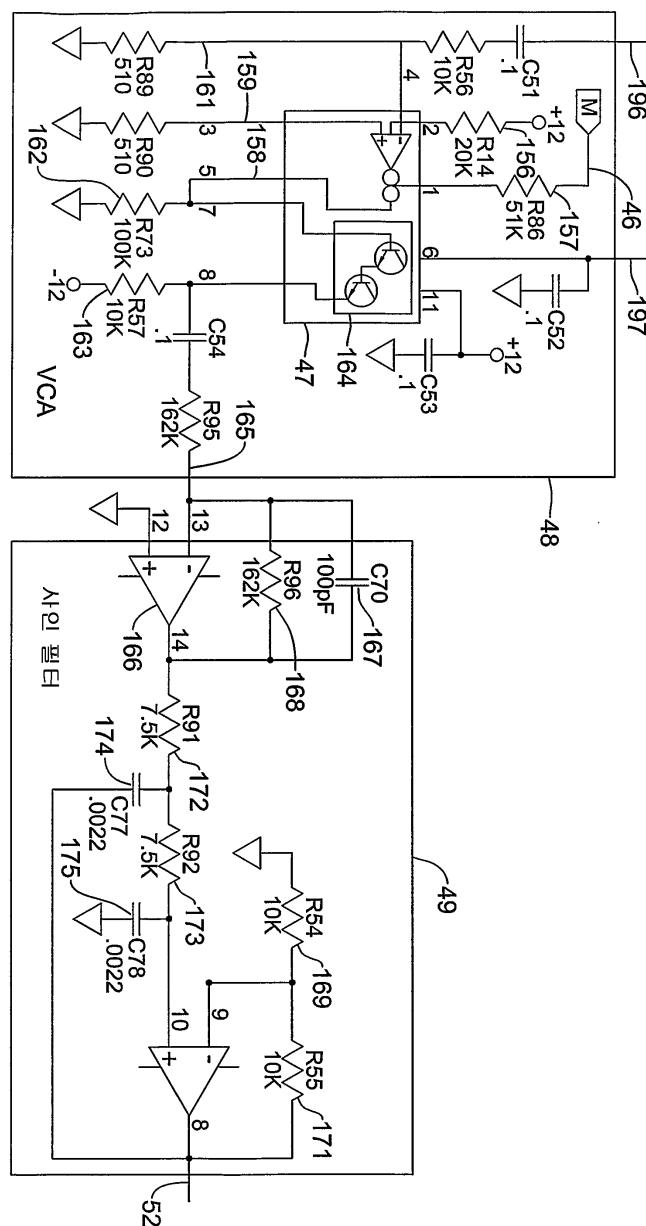

[0042] VCA(48)는 장치(47)로 LM13700 상호 컨덕턴스 증폭기를 사용할 수 있다.  $20\text{k}\Omega$  저항(156, 즉 R14)은 왜곡을 줄이기 위해 선형화 다이오드(linearizing diode)를 바이어스할 수 있다.  $51\text{k}\Omega$ 의 저항(157, 즉 R86)을 통한 전류는 선(159, 핀 3) 및 선(161, 핀 4) 사이의 차동 전압에 대한 선(158, 핀 5)에서 나오는 전류의 비를 제어할 수 있다.  $100\text{k}\Omega$  저항(162, 즉 R73)은 전류를 전압으로 바꿀 수 있으며, 이 신호는 V+에 연결된 콜렉터와  $10\text{k}\Omega$  저항(163, 즉 R57)을 이용하여 -12 볼트로 바이어스된 이미터를 갖는 트랜지스터(164)에 의해 버퍼링될 수 있다.

[0043] VCA(48)의 출력(165)은 사인 필터(49)로 갈 수 있다. 사인 필터(49)는 사인파의 왜곡을 줄일 수 있다. 연산 증폭기(166)는 필수적인 신호 반전을 제공하는데 사용되었으며,  $100\text{pF}$ 의 커패시터(167)는 필터의 제1 극을 얻기 위하여  $162\text{k}\Omega$ 의 피드백 저항(168, 즉 R96)을 가로질러 배치될 수 있다. 저항(169, 즉 R54) 및 저항(171, 즉 R55)은  $10\text{k}\Omega$ 의 동일한 값을 가지며, 상이한 센서를 수용하기 위하여 주파수가 변경되어도 이 비는 변경되지 않는다.  $7.5\text{k}\Omega$ 의 저항(172, 즉 R91)은 저항(173, 즉 R92)과 대략 동일하며,  $0.0022\mu\text{F}$ 의 커패시터(174, 즉 C77)는 커패시터(175, 즉 C78)와 대략 동일하다. 성분값을 살펴보면, 필터는  $10\text{kHz}$  대역으로 설정될 수 있으며,  $10\text{kHz}$  센서가  $5\text{kHz}$ 의 구동 주파수를 갖기 때문에 조정될 수 있다. 일부 성분값을 변경할 수 있으며 또는 2차 고조파의  $80\text{ dB}$  억제를 얻지 못하며 사이클 스윕이 기본적인 설계에 옵션을 추가할 수 있다고 여길 수 있다. 2차 고조파의  $80\text{ dB}$  억제를 얻는 것(본 명세서에서 요구되는 바와 같은)은 어려울 수 있다. 발진기가 자유롭게 동작할 때 사인파 발진기(65) 및 사인 필터(49)가 이를 얻을 수 있지만, 스펙트럼의 순도는 사인파 위상 동기 루프가 동기화될 때만 유지가능하다. 이것은 루프 필터의 출력이 사이클 내에서 주파수에 영향을 미치게 하려고 시도함으로써 과정에 영향을 줄 수 있기 때문이다. 전압 제어 발진기에 대한 입력에서 AC 신호에 대한 모든 추적을 필터링 하려고 한다면, 위상 동기 루프의 제어를 할 수 없을 뿐만 아니라 동기도 되지 않을 것이다. 이것은 사이클 스윕 옵션을 포함하는 것을 유발하는 것이다. 이 옵션이 활성화되면, 레이트 신호가 복조될 때 사인파 구동이 존재하지 않기 때문에 왜곡이 불가피할 수 있다.

[0044] 스타트/런 회로(53)에 비하여, L로 표시된 신호는 어떠한 신호와도 동기화되지 않았기 때문에, 주 제어 회로(36)로부터 나온다. K로 표시된 신호는 복조 제어 회로(34)로부터 공급된 장치의 래치로부터 나올 수 있다. 연속모드가 배타적으로 사용된다면, 신호(K)는 하나가 런 모드(run mode)인 것을 나타내는 일정한 신호일 수 있기 때문에 이러한 래치로부터 나와서는 안될 것이다. 그러나, 사이클 스윕 모드가 레이트 신호가 복조되고 있을 때 구동 신호를 공백으로 하는데 사용되는 경우 구동 신호와의 동기화에 이용될 수 있기 때문에, 신호(K)는 래치로부터 나올 수 있다. 스위치의 "온(on)" 저항은 신호 레벨의 함수일 수 있으며, 이 저항은 저항(107, 즉 R15)과 함께 전압 분배기 역할을 하도록 작용한다. 스위치 저항이 저항(107, 즉 R15)의  $20\text{k}\Omega$ 의 저항값에 비하여 낮기 때문에 출력이 입력에 매우 가깝지만, 스위치 저항이 신호 레벨의 함수라는 사실은 스타트/런 선택 회로에 공급하는 사인파가 완벽하더라도 왜곡을 생성하는 메카니즘을 제공할 수 있다. 이것은 사이클 스윕 모드를 사용하기 위한 다른 유인일 수 있으며, 왜곡을 걱정하지 않을 수 있다.

[0045] 위상 검출기(57)는 모터 복조 회로(20) 및 레이트 복조 회로(68)에서 사용되는 동일한 종류의 복조기일 수 있다. 이러한 방법을 수행하는 이유는 제어 신호와 스위치의 응답(개방 또는 단락) 사이의 딜레이가 있을 수 있다는 점이다. 디지털 PLL 회로(30)에서, 루프 필터가 어떠한 DC 전압도 디지털 PLL의 복조기로부터 나오지 않는다는 것을 알 수 있다. 이렇게 하기 위해서, 마이크로 컨트롤러에 대한 클럭은 입력(21)에서의 모터 퍽오프 신호에 주파수가 동기화될 수 있으며, 또한, 스위치에서의 딜레이를 보상하기 위하여 위상이 자동으로 앞서게 될 수 있다. PLL에서 동일한 스위치와 동일한 복조기가 사용될 수 있기 때문에, 스위칭 신호의 타이밍은 사인파 PLL의 스위치에서의 딜레이를 고려할 수 있어, 사인파는 모터 퍽 오프 신호에 비하여 적절하게 겹쳐진 상태(in registration)에 있게 된다. 완전하게 다른 위상 검출기가 2개의 상이한 위상 동기 루프에서 사용되는 경우일 수 있기 때문에, 타이밍 오차는 절대적인 지연보다는 스위치 딜레이에서의 차이와 관련될 수 있다.

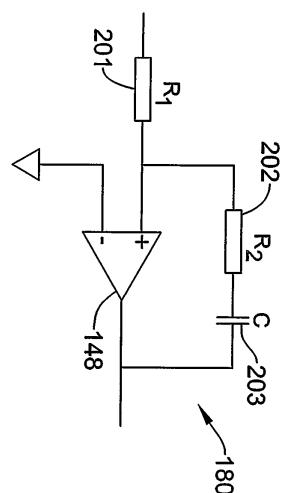

[0046] 도 9의 사인 PLL 루프 필터(63)에 비교하여 위상 동기 루프는 실제로 설계되어야 한다; 일반적으로 제어 루프를 조정하여 적절하게 동작하도록 하지는 못한다. 그러나, 필수 사항은 차동 증폭기(148) 저항(201, 즉  $R_1$ ), 저항(202, 즉  $R_2$ ) 및 커패시터(203, 즉 C)를 포함하는 도 15의 개략도(180)로 명백하게 나타난다. 입력은 저항

(201)을 통해 증폭기(200)의 비반전 입력으로 갈 수 있다. 증폭기의 반전 입력은 접지 또는 기준 단자에 연결될 수 있다. 증폭기의 출력으로부터 증폭기의 비반전 입력으로 직렬로 연결된 커패시터(203) 및 저항(202)을 포함하는 피드백 루프가 있을 수 있다.  $K_\phi$ 는 V/rad 단위의 위상 검출 변환 이득일 수 있다.  $K_0$ 는 rad/sec/V 단위의 VCO 변환 이득일 수 있다. 식 " $\omega_n = (K_0 \cdot K_\phi) / (R_1 \cdot C)^{1/2}$ " 및 " $R_2 = 2 / (C \cdot \omega_n)$ "이 사용될 수 있다.  $K_\phi$  및  $K_0$ 는 측정될 수 있으며, 즉  $R_1$  및  $\omega_n$ 의 적절한 값이 선택될 수 있다.  $C$  및  $R_2$ 는 첫번째 식 및 두번째 식을 각각 이용하여 계산될 수 있다. 이 접근 방식은 제동계수(damping factor)를 추측할 수 있다. 제동은 식 " $\zeta = (R_2 \cdot (C/2)) \cdot \omega_n$ "에 의해 계산될 수 있다.  $R_2$ 가 너무 낮다면, 루프는 미흡 제동이며 안정적이지 않다.  $R_2$ 가 너무 높다면, 불필요한 큰 AC 신호가 정현 전압 제어 발진기에 공급되어 왜곡을 야기할 수 있다.

[0047]

초기의 배치와 성분값들은 실험 회로판 방식에 기초할 수 있다. 범용의 개조가 실험 회로판에서 정상적인 기판 방법으로 변환하여 구현될 수 있다. 이러한 변화는 동작 주파수에 관계없이 모든 기판 상에서 이루어져야 한다. 이것은 실험 회로판에서 이루어진 방법으로부터의 실험 회로판 과정 이후에 이루어지는 방법으로의 치환에 대한 대부분 경미한 조정이다.

[0048]

이 변경은: 저항(118, 즉 R100)을 14k $\Omega$ 으로 변경하는 것; +5 볼트와 DAC(37, 편 3)의 Z 신호 단자 사이에 20k $\Omega$  풀업 저항을 놓는 것; 저항(127, 즉 R41)(디지털 PLL(30)에서)의 값을 20k $\Omega$ 으로 변경하는 것; 저항(93, 즉 R59), 저항(94, 즉 R61) 및 저항(95, 즉 R62)을 248Hz 대역을 얻기 위하여 9.5k $\Omega$ 의 값으로 변경하는 것; 저항(98, 즉 R107)을 17.4k $\Omega$ 의 값으로 변경하는 것; 저항(99, 즉 R109) 및 저항(101, 즉 R110)을 248Hz 대역을 얻기 위하여 9.5k $\Omega$ 의 값으로 변경하는 것; 및 저항(96, 즉 R102)을 가로질러 470pF의 커패시터를 놓는 것을 포함한다.

[0049]

다음의 개조 세트는 주파수에 전용일 수 있다. 제1 기판 상에, 커패시터(137, 즉 C64), 커패시터(149, 즉 C65) 및 커패시터(151, 즉 C66)의 값은 사인파 발진기(65)가 5kHz 부근에서 아이들링하게 하도록 2200pF으로 변경될 수 있다. 아이들 주파수는 루프가 동기화되도록 동작 주파수 근처에 적절하게 있을 수 있다. 주파수를 더 높게 하기 위해서는 커패시터의 값을 더 작게 만들 수 있다. 정밀한 조정을 위하여, 저항(152, 즉 R82), 저항(153, 즉 R83) 및 저항(154, 즉 R84)의 값이 일치하면서 변경될 수 있지만, 원래의 51k $\Omega$ 보다 더 작게 되어서는 안된다. 장치(31)의 74HC4046A 칩의 아이들 주파수는 커패시터(129, 즉 C85)의 값을 변경함으로써 조정될 수 있다. 주파수는 저항(131, 즉 R104)의 값을 변경함으로써 정밀 조정될 수 있다. 사인 필터(49)의 주파수는 저항(168, 즉 R96), 저항(172, 즉 R91) 및 저항(173, 즉 R92)의 값을 동일한 비율로 변경함으로써 조정될 수 있다. 원래 값은 일반적으로 10kHz로 설정되었다.

[0050]

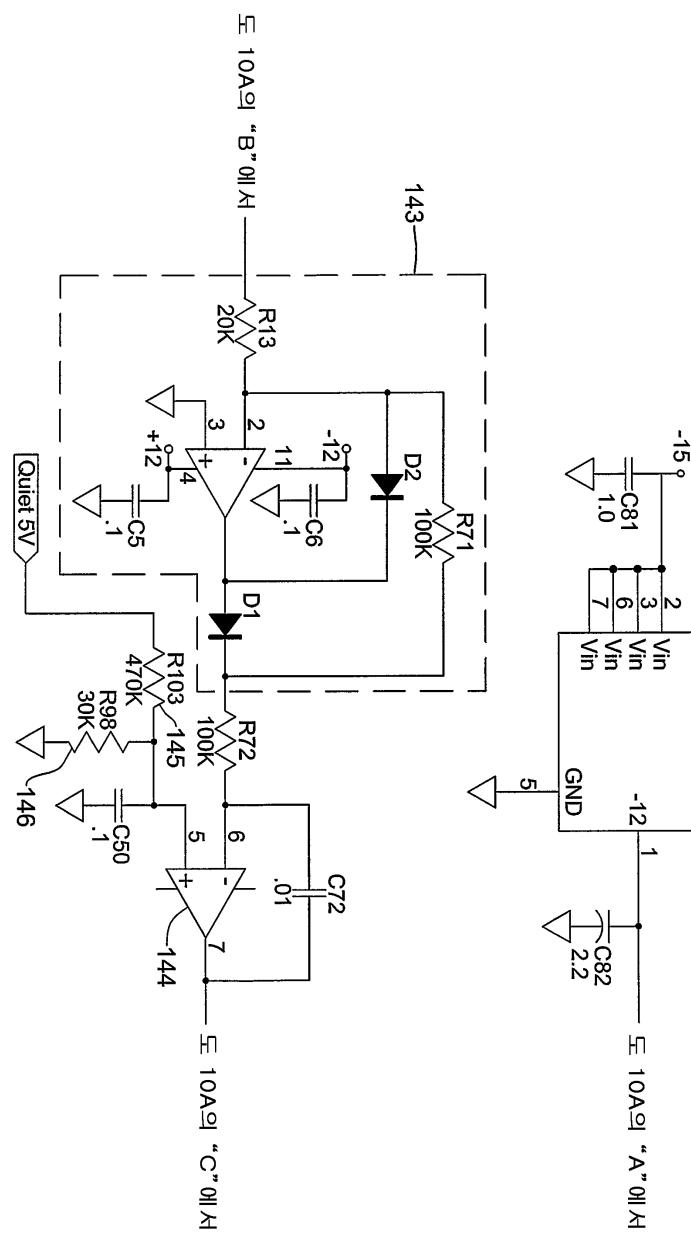

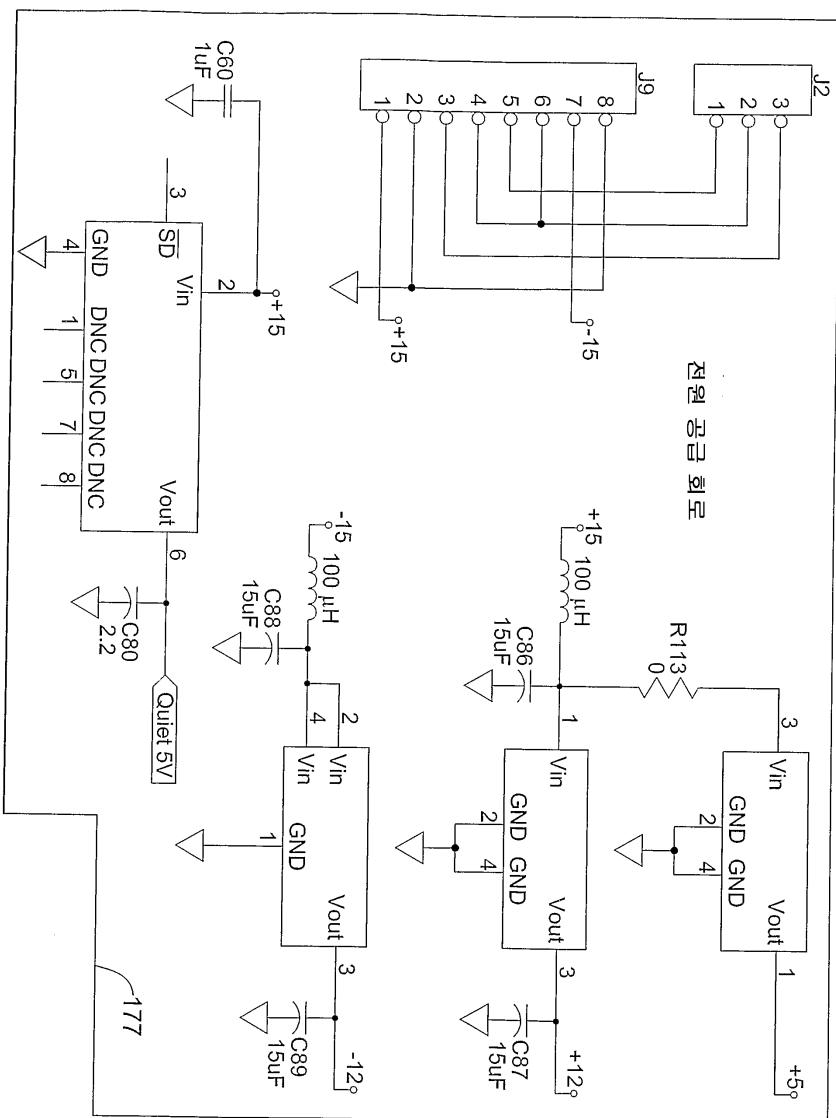

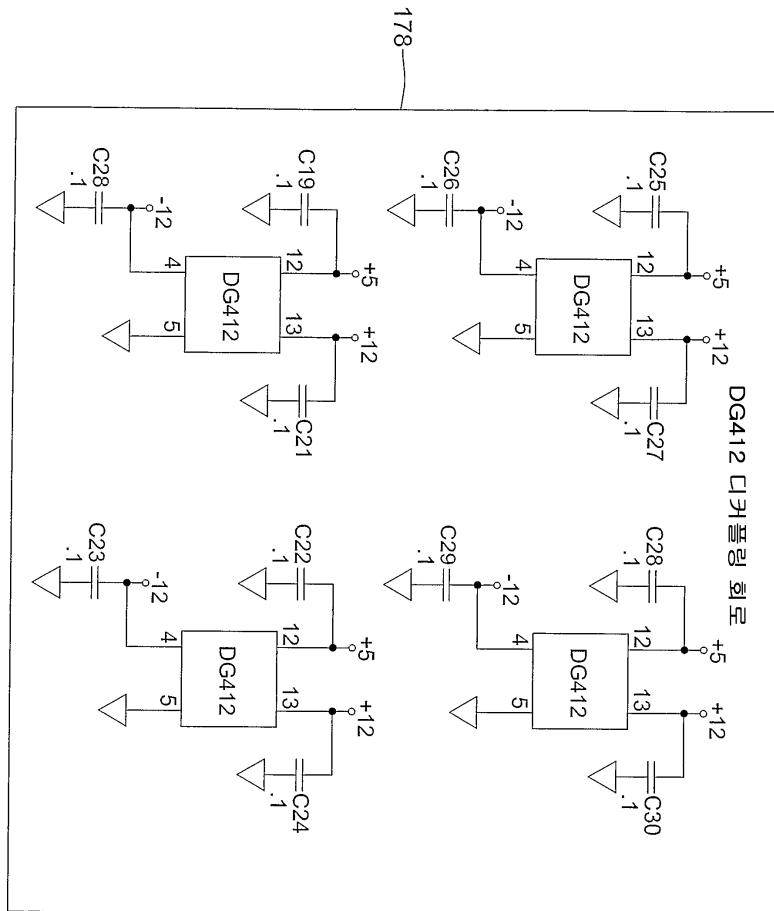

도 16은 본 발명의 회로에 다양한 전압을 공급하기 위한 회로를 갖는 전원 공급 회로(177)를 도시한다. 회로(178)는 장치(112)(DG412)를 위해 사용될 수 있는 디커플링을 제공한다.

[0051]

도 2 내지 14의 회로에서, 문자 부호(A, B, 즉 C, D, E, F, G, H, I, J, K, L, M, Q, X, Y 및 Z)로 표시된 신호 및 숫자 부호(28, 32, 44, 52, 55, 64, 76, 78, 86, 87, 106, 181, 182, 183, 184, 185, 186, 187, 188, 189, 191, 192, 193, 194, 195, 196 및 197) 표시된 교차하는 선에 의해 도시된 다양한 연결부가 있을 수 있다.

[0052]

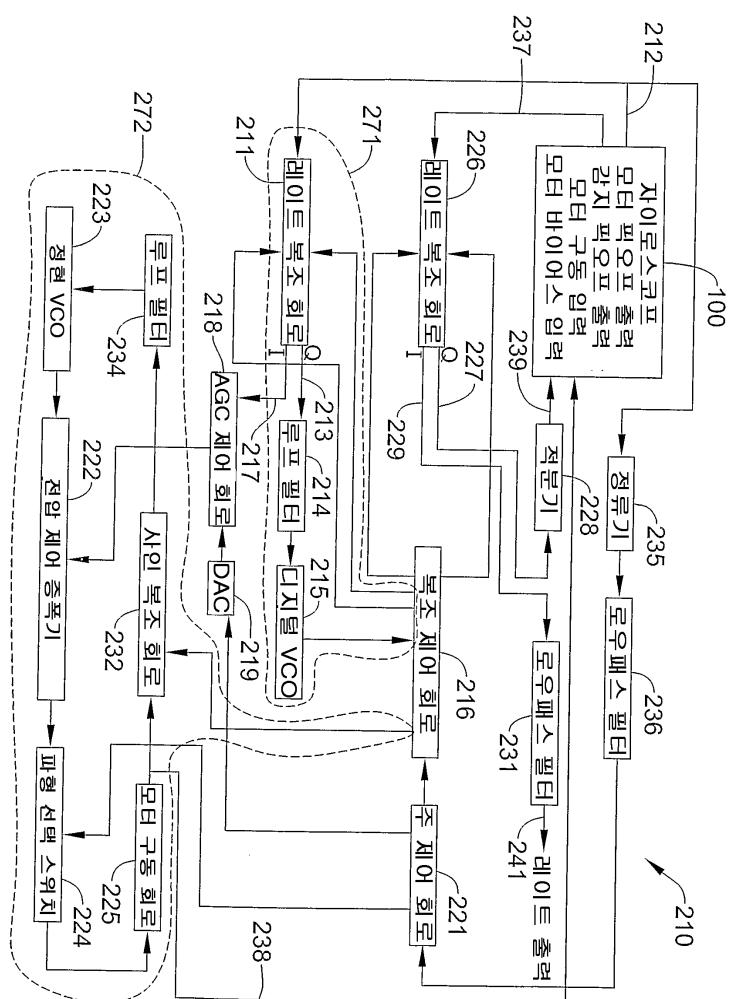

도 17은 본 발명을 구현하는 회로(210)의 다른 블록도를 도시한다. 회로(210)는 모터 구동이 자이로스코프(100) 제어 시스템에서의 잡음 레벨을 감소하도록 높은 순도의 사인파를 사용할 수 있다. 모터 픽오프 신호(212)가 자이로스코프(100)로부터 나와 동기 모터 복조 회로(211)로 가는 곳에서 시작할 수 있다. 모터 복조 회로(211)의 직교 출력(213)은 위상 동기 루프(Phase Locked Loop, PLL)의 위상 검출기 역할을 할 수 있다. 위상 검출기로부터, 신호는 루프 필터(214)를 통해 복조 신호를 제공하는 마이크로 컨트롤러(복조 제어 회로)를 위한 클럭 신호를 제공하는 디지털 전압 제어 발진기(215)로 갈 수 있다. 복조 회로(211), 루프 필터(214) 및 VCO(215)의 조합은 위상 동기 루프와 같이 동작할 수 있다. 루프 필터(214)가 적분기이기 때문에, 모터의 주파수가 전압 제어 발진기(215)의 공주 주파수와 동일하지 않더라도 정상 상태 위상 오차를 갖지 않는 종류의 위상 동기 회로일 수 있다. (이 경우의 공주 주파수는 적분기가 단락될 때 존재하는 주파수로 간주될 수 있으며, 가끔은 주마이크로 컨트롤러(221)가 배치될 수 있다.) 따라서, 마이크로 컨트롤러(216)는 스위치에서의 딜레이를 보상하기까지 하는 거의 완벽한 복조 신호 합성을 제공할 수 있다. 모터 복조 회로(211)의 동상 출력은 모터 구동 신호(238)의 크기를 나타내는 DC 신호를 생성할 수 있다. 자동 이득 제어 회로(AGC, 218)는 복조 회로로부터의 DC 신호를 주 마이크로 컨트롤러(221)가 조정하는 디지털 아날로그 변환기(DAC, 219)의 DC 신호와 비교할 수 있으며, 그 차이의 적분은 전압 제어 증폭기(VCA, 222)의 이득을 변경하는데 사용될 수 있다. 사인파 발

진기(223)로부터의 신호는 사인 필터(224) 및 모터 구동 회로(225)에 들어가기 전에 VCA(222)에 의해 조정될 수 있다. 따라서, AGC 시스템(218)은 모터 핵오프 신호(212)의 특정 크기를 검사할 수 있으며, 그 다음 특정 크기가 얻어질 때까지 모터 구동 신호(238)의 크기를 조정할 수 있다.

[0053] 감지 핵오프 신호(237)는 자이로스코프(100)에서 나와서 동기 레이트 복조기(226)로 갈 수 있다. 직교 복조는 모터 바이어스 신호(239)를 제공하기 위하여 적분기(228)을 통해 진행하는 신호(227)를 제공할 수 있다. 동상 복조(229)는 필터(231)에 의해 필터링될 때 자이로스코프(100)의 회전 레이트를 나타내는 출력(241)인 신호를 제공할 수 있다.

[0054] 정현 모터 구동 신호(238)을 생성하기 위하여, 다른 위상 동기 루프가 사용될 수 있다. 복조 제어 회로(216)는 복조 회로(211, 226, 232)에 사용된 스위칭 신호의 주파수의 1/2 또는 그 스위칭 신호의 다른 분수배 주파수에 있는 스위칭 신호 세트를 제공할 수 있다. 또한, 스위칭 신호는 모터 구동을 위해 생성된 사인파가 자이로스코프(100)로부터 나오는 신호에 대하여 적절한 관계를 보유하도록 다른 스위칭 신호에 대하여 적절한 타이밍 관계를 가질 수 있다. 사인 복조 회로(232), 루프 필터(234) 및 정현 VCO(223)는 제2 위상 동기 루프를 구성할 수 있다.

[0055] 또한, 모터 핵오프로부터의 신호(212)는 정류기(235) 및 로우 패스 필터(236)로 가며, 그 다음 주 마이크로 컨트롤러(221) 상의 아날로그-디지털 변환기로 간다. 정류기 회로(235)는 신호가 위상 동기 루프가 알맞게 동기 되도록 충분한 크기로 언제 구축되었는지를 검출하기 위하여 스타트-업 동안 사용될 수 있다. 기동을 위하여, 주 마이크로 컨트롤러(221)는 사인파를 모터 구동 회로에 연결하는 것 대신에 주 마이크로 컨트롤러(221)로부터의 신호를 모터 구동 회로(225)에 연결하기 위하여 과형 선택 스위치(224)에 디지털 신호를 보내도록 다른 마이크로 컨트롤러(주 마이크로 컨트롤러에 의해 제어될 수 있는)를 지시할 수 있다. 그 다음, 주 마이크로 컨트롤러(221)는 3 레벨을 가지며 3 레벨만을 사용할 때 가능한 정도로 사인파를 닮은 신호를 생성할 수 있다. 일련의 상이한 주파수를 대량 갖는 센서를 시뮬레이션하기 위한 알고리즘이 사용될 수 있다. 자이로스코프(100) 내에서의 관성 질량체가 진동하기 시작하면, 비교기는 신호를 구형파로 변환할 수 있으며, 주 마이크로 컨트롤러(221)는 이것을 동기화를 위해 사용할 수 있다. 모터 구동 신호(238)의 위상을 모터 핵오프 신호(212)에 대하여 적절히 조정함으로써, 마이크로 컨트롤러는 상당한 크기까지 센서를 구동할 수 있다. 그 다음, 주 마이크로 컨트롤러(221)는 신호의 주파수를 측정하고 이 정보를 모터 구동 신호(238)의 펄스폭을 조정하는데 사용할 수 있다. 위상과 펄스폭 모두를 센서의 주파수에 이상적으로 맞게 하여, 주 마이크로 컨트롤러(221)는 크기를 적절한 크기까지 크게 구동할 수 있다. 그 다음, 주 마이크로 컨트롤러(221)는 위상 동기 루프 모두를 동기시키고 과형 선택 스위치(224)를 사용하여 정현 구동으로 변경하도록 다른 마이크로 컨트롤러를 지시할 수 있다.

[0056] 주 마이크로 컨트롤러(221)가 과형 선택 스위치(224)를 직접 제어하지 않고, 그 대신에 다른 마이크로 컨트롤러가 제어하도록 하는 이유는 과형 선택 스위치(224)를 위한 다른 용도가 있기 때문이다. 이 목적을 위하여, 주 마이크로 컨트롤러(221)는 과형 대신에 접지에서의 DC 레벨을 제공할 수 있다. 그 다음, 과형 선택 회로(224)는 모터 구동 신호(238)의 교대하는 사이클 상의 사인파 및 접지 사이클 선택하는데 사용되며, 이것은 과형 선택 신호가 궁극적으로 주 마이크로 컨트롤러(221) 대신에 복조 회로(216)로부터 나오는 이유이다. 주 마이크로 컨트롤러는 이 동작 모드를 사용할 시간을 다른 마이크로 컨트롤러에 지시할 수 있지만, 다른 마이크로 컨트롤러는 이 모드를 사용하도록 지시받게 되면, 사이클 스kip 신호와 함께 모든 복조 신호를 생성할 수 있다. 이것이 수행되는 이유는, 모터 구동 신호(238) 과형의 2차 고조파는 레이트 출력 신호에서 오차를 생성하는 방법으로 레이트 복조 회로(226)에 의해 복조될 수 있기 때문이다. 레이트 복조 회로(226)는 모터 구동 회로(225)가 턴오프된 때에만 신호(237)를 복조하기 때문에, 이 문제는 제거될 수 있다. 이러한 성능이 없이는, 모터 구동(238) 과형의 2차 고조파를 억제하기 위한 필요 조건이 너무 엄격하여 이러한 억제가 용이하게 얻는 것이 어려울 수 있다.

[0057] 도 18의 MEMS 진동형 자이로스코프(또는 기계적 발진기, 250)에 대한 구동 과형은 일반적으로 사인파로 시작하지 않는다. 또한, 자이로스코프의 관성 질량체를 공진 주파수에서의 구동 신호로 구동하려고 하는 것은 발생할 수 있는 높은 Q 때문에 매우 많은 양의 호출 신호를 포함한다는 문제점이 있다. 더하여, 감지 레이트(251)의 핵오프는 전부가 아니더라도 얻거나 구별하기 쉬운 것이 아닐 수 있다. 해결책은 적절한 위상을 가지며 자이로스코프 모터의 10kHz 진동 레이트와 겹쳐진 완만한 5kHz 사인파를 갖는 자이로스코프 모터(250, 즉, 진동형 관성 질량체 또는 기계식 발진기)를 구동하는 것이다.

[0058] 먼저, 모터 구동 신호(253)을 위한 동기 신호를 위하여 모터 핵오프(251)를 볼 수 있다. 감지 핵오프(252)는 지구의 표면 또는 우주의 일부 양태에 대한 자이로스코프의 회전 레이트를 나타내는 출력일 수 있다.

- [0059] 구동 신호(253)에 대하여, 완만한 사인파가 필요할 수 있으며 발진기로부터 얻어질 수 있다. 이 신호는 모터 주파수의 1/2, 즉 5kHz에 있어야만 하며, 10kHz 모터 핀오프 신호(251)에 위상 동기되어야만 한다. 또한, 마이크로 컨트롤러(254)의 명령 클럭은 명령 신호 사이의 에지가 모터 구동 신호(253)의 사이클의 에지 또는 마지막에 발생하도록 모터 핀오프 신호(251) 상에 동기될 수 있다. 모터 핀오프 신호의 사이클의 에지에서 명령 신호의 에지가 각각 발생할 수 있도록 마이크로 컨트롤러(254)의 클럭을 제어하기 위한 전압 제어 발진기(VCO)가 있을 수 있다. 이것은 자이로스코프(250)의 관성 질량체 상에서 구동 신호의 정전기적 푸시의 최대 효과를 얻기 위한 것이다.

- [0060] 구동 신호(253)는 5kHz의 주파수에 있을 수 있으며, 발생할 수 있는 임의의 2차 고조파를 최소화하기 위하여 자이로스코프(250)의 관성 질량체 진동의 10kHz에서 감지된 신호에 동기화된다. 자이로스코프는 발생하는 임의의 2차 고조파로부터 더 잘 구별하기 위하여 5kHz의 사인파(253)를 이용하여 구동될 수 있다. 그러나, 관성 질량체 양 측의 빗 형상의 구동 소자들이 서로 완벽하게 동일하지 않고 이에 따라 자이로스코프(250)의 관성 질량체 상에 약간 비대칭의 구동력을 발생시킬 수 있기 때문에, 고조파가 없는 순수한 사인파는 여전히 고조파를 발생시킨다.

- [0061] 감지 신호(252)(자이로스코프의 회전 레이트 정보를 갖는)가 자이로스코프(250)로부터 읽혀질 수 있는 반면, 마이크로 컨트롤러(254)로부터의 제어 신호(255)는 구동 신호(253)를 공백으로 만들 수(blank out) 있다. 공백화(blanking)는 구동 신호(253)의 하나 이상의 사이클이 0이 되는 것을 의미한다. 예를 들어, 2개의 사이클마다 공백이 될 수 있다. 또는, 3개의 사이클마다 공백이 될 수 있다. 마이크로 컨트롤러(254)는 자이로스코프(250)에 대한 임의의 개수의 구동 신호를 허용하고 임의의 개수의 구동 신호(253)를 공백으로 만들도록 프로그래밍될 수 있다. 스위치 또는 공백화 회로(263)가 신호 선택기로 간주될 수 있다. 신호 선택기의 적어도 일부는 마이크로 컨트롤러(254)의 외부에 있을 수 있다.

- [0062] 자이로스코프(250)의 구동 메카니즘이 자이로스코프를 구동하기 위한 인력에 의해 구동 신호(253)의 극성에 대하여 중립일 수 있기 때문에, 5kHz는 양호한 주파수이다.

- [0063] 자이로스코프 관성 질량체의 10kHz의 공진 및 대응하는 핀오프 신호(251)는 자이로스코프의 구동 및 감지 시스템에 대한 주 클럭으로 간주될 수 있다. 감지 핀오프 신호(252)는 자이로스코프의 회전 레이트의 크기를 나타내는 크기를 갖는다. 따라서, 회전이 없는 상태에서, 크기는 이론적으로 0일 수 있다. 따라서, 매우 작은 크기를 갖는 신호에 대한 크기를 적절한 정밀도로 결정하기 위한 필요때문에, 구동 신호(253)는 감지 핀오프 신호(252)를 읽는 동안 공백이 되어야만 한다.

- [0064] 자이로스코프를 구동하고 감지하기 위한 시스템(10)은 본질적으로 아날로그이지만 디지털화될 수 있다. 후자는 모터 핀오프(251) 및 감지 핀오프(252)로부터 아날로그 입력을 받기 위하여 아날로그-디지털 변환기(ADC)를 필요로 할 수 있다. 디지털 처리가 24 비트 해상도로 초당 96,000 샘플링으로 신호를 변환할 수 있다. 디지털화된 시스템은 부동 소수점의 정밀도로 동작하며, 디지털 신호 처리기(DSP)로 구현될 수 있다.

- [0065] 위상 동기 루프에서 소정의 상이한 주파수들이 있을 수 있으며, 따라서, 기본 주파수만을 유지하면서 다른 주파수들을 제거하는데 필터가 필요할 수 있다. 또한, 사이클 내에서 신호의 주파수를 변경하는 것은 왜곡을 유발할 수 있으며, 따라서, 주파수는 신호의 사이클의 에지 또는 마지막에서 변경되거나 조정되어야만 한다.

- [0066] 컨트롤러(254)로부터의 스위칭 신호 중에서 일부는 10kHz에 있고 다른 것은 5kHz에 있을 수 있다. 이 신호들은 주요 주 클럭으로 간주될 수 있는 모터 핀오프(252)로부터의 10kHz와 "완벽하게" 정렬될 수 있다.

- [0067] 5kHz 신호(257)는 제1 루프(261)에서 제2 루프로 제공될 수 있다. 제2 루프(262)는 제1 루프(261)로부터의 5kHz 신호에 동기되거나 또는 이와 "완벽하게" 겹쳐져 있는 5kHz에서의 사인파 신호를 제공하기 위하여 사인 발진기와 결합될 수 있다.

- [0068] 제1 위상 동기 루프 신호는 모터 핀오프 신호(251)에 맞추어져 있을 수 있다. 이 루프(261)로부터 5kHz 및 10kHz의 스위칭 신호가 올 수 있다. 5kHz 신호(257)는 자이로스코프를 구동하기 위하여 사인파 신호(253)를 제공하는 제2 위상 동기 루프(262)로 갈 수 있다. 공백화는 회로의 마지막에 그러나 신호(253)가 모터 구동 입력으로 가기 직전에 올 수 있다. 공백화는 컨트롤러(254)로부터의 출력에 의해 트리거링 될 수 있다. 제1 마이크로 프로세서는 제1 위상 동기 루프와 관련된 제2 마이크로 프로세서로 스킵 또는 비-스킵 모드를 나타내는 신호를 보낼 수 있다. 그 다음, 제2 프로세서는 자이로스코프로부터의 감지 신호(252)를 읽는 동안 구동 회로를 공백화하기 위하여 공백화 회로(263)에 신호(255)를 공급할 수 있다.

- [0069] 제2 루프(262)로부터의 사인파 신호(253)는 3단의 로우 패스 필터에 의해 제공된 완만함을 가질 수 있다. 출력은 인버터를 통해 제2 루프의 사인파 발진기에 대한 피드백 신호로서 입력으로 갈 수 있다.

- [0070] 주 마이크로 컨트롤러(254)는 들어오는 핵오프 신호(251)와 동기하여 스위치를 제어할 수 있다. 또한, 위상 동기 루프 출력 신호(257, 253)는 핵오프 신호(251)와 동기되어 있을 수 있다. 여기서 동기되어 있다는 것은 신호의 에지가 서로 정렬되어 있으며, 사인파와 같은 0을 교차하는 신호(zero crossing signal)의 교차점과 정렬되어 있다는 것을 의미한다. 예를 들어, 주파수의 변화는 에지 또는 교차점에서 발생하여야만 한다. 전체 클럭 사이클 또는 반 사이클의 중간에서 변경되거나 스위칭되는 것이 없어야만 한다. 이 접근 방식은 신호 사이에서 지터(jitter)를 방지할 수 있다.

- [0071] 전압 제어 발진기는 위상 동기 루프(261, 262)의 일부일 수 있다. 루프가 동기되면, 클럭 신호는 자이로스코프의 들어오는 모터 핵오프 신호와 같은 중요한 이벤트와 정렬될 수 있다. 핵오프 신호는 주 클럭 신호일 수 있다. 주 컨트롤러(254)의 클럭은 핵 오프 신호(251)에 맞추어질 수 있다.

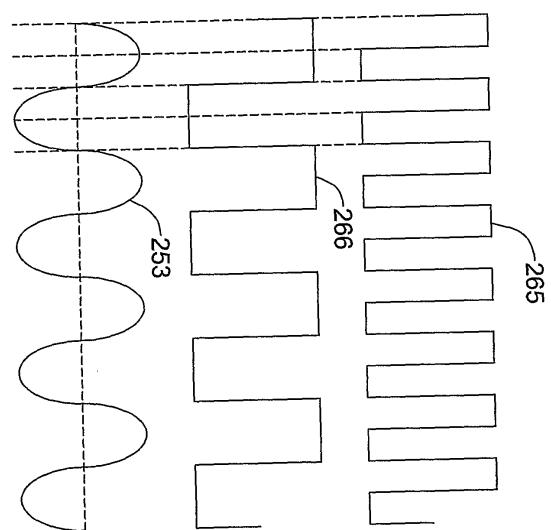

- [0072] 스위치 딜레이는 개방 또는 단락에 관계 없이 보상될 수 있다. 이것은 위상 동기 루프에 의해 달성될 수 있다. 이러한 방법으로, 제1 위상 동기 루프(261)는 스위치의 평균 딜레이를 보상할 수 있다. 마이크로 컨트롤러 또는 위상 동기 루프는 각각 구형파 신호(265, 266)일 수 있는 10kHz 스위치 신호 및 5kHz 스위치 신호를 생성할 수 있다. 5kHz 신호(266)는 제2 위상 동기 루프로 입력될 수 있다. 제2 위상 동기 루프(262)의 출력 신호(253)로부터 생성된 사인파는 스위치 신호와 동기되어 있으며 이 신호와 겹쳐질 수 있다.

- [0073] 또한, 5kHz 신호(265)는 10kHz 신호(266)와 적절하게 겹쳐질 수 있다.(즉, 동상이지만, 해당 파형의 해당 에지 및/교차점에서 정렬될 수 있다). 도 19에서와 같이, 신호(265, 266)의 에지는 서로에 대해, 그리고 사인파(253)의 교차점과 정렬될 수 있다. 각 신호의 다른 파의 위치에 대한 한 파의 위치는 신호가 서로에 대하여 적절하게 겹쳐져 있는지를 나타낸다. 도 17의 제1 루프에서 점선 안의 회로(271)는 도 18의 블록도의 회로(271)에 대응한다. 유사하게, 도 17의 제2 루프에서 점선 안의 회로(272)는 도 18의 블록도의 회로(272)에 대응한다.

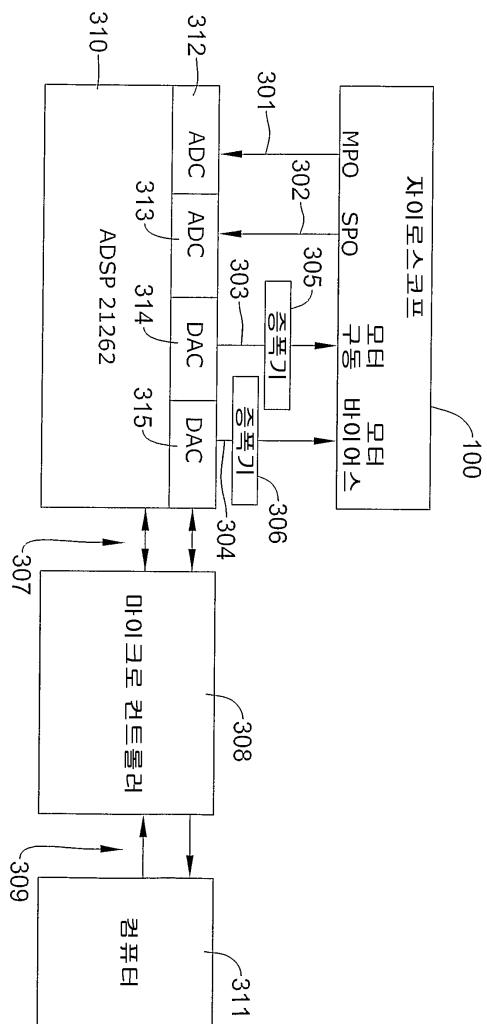

- [0074] 도 20은 기계식 발진기(250) 또는 자이로스코프(100)의 제어 전자 장치에 대한 디지털 버전을 나타낸다. 자이로스코프(100)의 모터 핵오프 출력(301)은 예로써 마이애미 노르우드의 아날로그 디바이스 Inc.에 의해 제조된 모델명 ADSP 21262일 수 있는 디지털 신호 처리기(DSP)의 아날로그-디지털 변환기(ADC, 312)에 연결될 수 있다. 자이로스코프(100)의 감지 핵오프 출력(302)은 디지털 신호 처리기(310)의 아날로그-디지털 변환기(313)로 연결될 수 있다. 디지털-아날로그 변환기를 포함하는 DSP(310)의 모터 구동 출력(303)은 증폭기(305)를 통해 자이로스코프(100)의 모터 구동 입력에 연결될 수 있다. 모터 또는 발진기 구동 신호는 모터 또는 발진기의 감지 핵오프 신호의 분수배 주파수를 가지며 모터 핵오프 신호와 동기되며 그리도/또는 모터 핵오프 신호와 겹쳐진 디지털로 생성된 합성 정현 또는 사인파 신호일 수 있다. 구동 신호는 필요에 따라 다른 신호일 수 있으며, DSP에 의해 생성될 수 있다. 다양한 스위칭의 딜레이 또는 타이밍은 원하는 바에 따라 디지털로 보상되거나 DSP에 의해 결정될 수 있다. DSP(310)의 모터 바이어스 출력(304)은 증폭기(306)를 통해 자이로스코프(100)의 모터 바이어스 입력으로 연결될 수 있다. DSP(310)와 마이크로 컨트롤러(308) 사이에 연결된 8비트 쌍방향 데이터버스(307)가 있을 수 있다. 마이크로 컨트롤러(308)와 컴퓨터(311) 사이에 RS 232 인터페이스 연결(309)이 있을 수 있다.

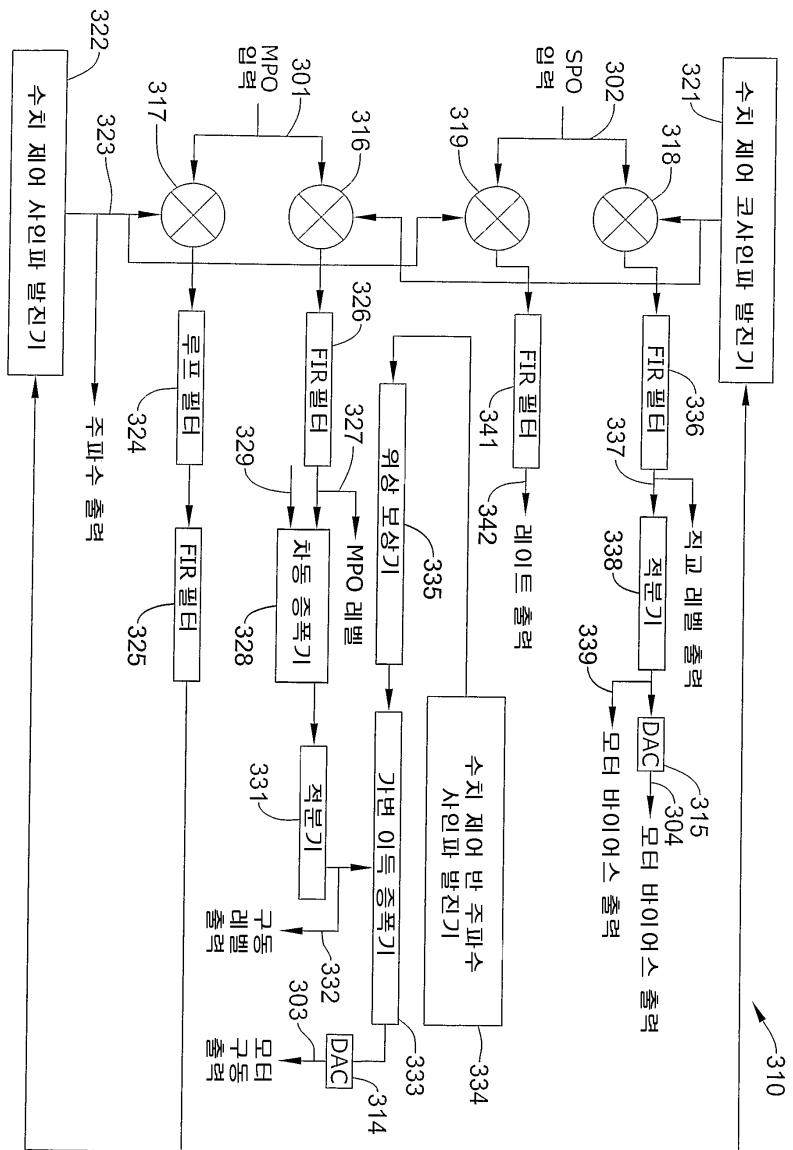

- [0075] 도 21은 DSP(310)의 개략도이다. 자이로스코프(100)의 모터 핵오프 신호 출력(301)은 ADC(312)를 통해 곱셈기(316, 317, multiplier)에 연결될 수 있다. 자이로스코프(100)의 모터 감지 핵오프 출력(302)은 ADC(313)를 통해 곱셈기(318, 319)에 연결될 수 있다. 수치 제어 코사인파 발진기(321)는 곱셈기(318, 316)에 연결될 수 있다. 수치 제어 사인파 발진기(322)는 곱셈기(317, 319)에 연결될 수 있다. 곱셈기(317)의 출력은 루프 필터(324)로 갈 수 있다. 루프 필터(324)의 출력은 유한 임펄스 응답(filter impulse response, FIR) 필터(325)로 갈 수 있다. 필터(325)의 출력은 수치 제어 코사인파 발진기(321) 및 수치 제어 사인파 발진기(322)로 갈 수 있다.

- [0076] 곱셈기(316)의 출력은 FIR 필터(326)로 갈 수 있다. 필터(326)는 차동 증폭기(328)의 입력으로 연결된 모터 핵오프 레벨 출력(327)을 가질 수 있다. 또한, 차동 증폭기의 입력은 기준 레벨(329)일 수 있다. 차동 증폭기(328)의 출력은 적분기(331)로 갈 수 있다. 적분기(331)로부터의 구동 레벨 출력(332)은 가변 이득 증폭기(333)로 갈 수 있다. 수치 제어 반 주파수(또는 다른 분수배 주파수) 사인파 발진기(334)는 위상 보상기(335)에 연결된 출력을 가질 수 있다. 위상 보상기(335)의 출력은 가변 이득 증폭기(333)로 갈 수 있다. 가변 이득

증폭기의 출력은 모터 구동 출력(303)을 출력하는 DAC(314)로 갈 수 있다.

[0077] 곱셈기(318)의 출력은 FIR 필터(336)로 갈 수 있다. FIR 필터(336)는 적분기(338)에 직교 널 출력(337)을 제공할 수 있다. 모터 바이어스 출력(339)은 증폭기를 통해 자이로스코프(100)의 아날로그 모터 바이어스 출력(304)을 제공할 수 있는 DAC(315)로 갈 수 있다. 곱셈기(319)의 출력은 FIR 필터(341)로 갈 수 있다. FIR 필터(341)은 레이트 출력(342)을 제공할 수 있다.

[0078] DSP(310)의 수치적 출력은 데이터 버스(307)와 인터페이스(309)를 통해 마이크로 컨트롤러(308) 및 컴퓨터(311)에 디지털로 통신될 수 있다. 이 출력은 주파수 출력(323), 모터 핵오프 레벨(327), 구동 레벨 출력(332), 직교 레벨 출력(337), 모터 바이어스 출력(339) 및 레이트 출력(342)을 포함할 수 있다.

[0079] 본 명세서에서, 다른 방법 또는 다른 시제로 기재된다 하더라도, 이론적이거나 예상할 수 있는 성질을 가질 수 있다.

[0080] 본 발명이 적어도 하나의 예시적인 일례에 대하여 설명되었지만, 많은 수정물 및 변형물이 본 명세서를 속독함에 따라 본 발명의 기술 분야에서 통상의 지식을 가진 자에게 자명할 것이다. 따라서, 첨부된 청구 범위가 이러한 수정물 및 변형물을 포함하도록 종래 기술과 대비하여 가능한 한 넓게 해석되도록 의도되었다.

### 도면의 간단한 설명

[0004] 도 1은 자이로스코프 제어 전자 장치의 블록도이다;

[0005] 도 2는 모터 복조기의 개략도이다;

[0006] 도 3은 디지털 위상 동기 루프 회로의 개략도이다;

[0007] 도 4는 복조기 제어 회로의 개략도이다;

[0008] 도 5는 주제어 회로의 개략도이다;

[0009] 도 6은 자동 이득 제어 회로의 개략도이다;

[0010] 도 7은 전압 제어 증폭기 및 사인 필터의 개략도이다;

[0011] 도 8은 스타트/런 선택 회로 및 관련 회로의 개략도이다;

[0012] 도 9는 사인 위상 동기 루프 필터 및 위상 검출기의 개략도이다;

[0013] 도 10은 사인파 발진기의 개략도이다;

[0014] 도 11은 레이트(rate) 복조기의 개략도이다;

[0015] 도 12는 직교 복조 회로의 개략도이다;

[0016] 도 13은 레이트 필터의 개략도이다;

[0017] 도 14는 스타트 검출기의 개략도이다;

[0018] 도 15는 도 9의 사인 위상 동기 루프 필터의 일부에 대한 개략도이다;

[0019] 도 16은 전원 공급 회로 및 디커플링 회로의 개략도이다;

[0020] 도 17은 다른 버전의 자이로스코프 제어 전자 장치의 개략도이다;

[0021] 도 18은 자이로스코프 제어 시스템의 루프 전자 장치에 대한 기본 도면이다;

[0022] 도 19는 시스템에서의 일부 신호 사이의 관계를 도시한다;

[0023] 도 20은 기계식 발진기 또는 자이로스코프의 제어 전자 장치를 위한 디지털 신호 처리기를 갖는 확장된 디지털 버전에 대한 블록도이다; 그리고,

[0024] 도 21은 제어 전자 장치에 대한 디지털 신호 처리기에 대한 도면이다.

도면

도면1

도면2

모티 복조회로

도면3

도면4

도면5

도면6

도면7

도면8

도면9

### 도면 10A

도면10B

도면11

도면12

도면13

도면14

도면15

## 도면 16A

도면16B

도면17

도면18

도면19

도면20

도면21