(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6680436号

(P6680436)

(45) 発行日 令和2年4月15日(2020.4.15)

(24) 登録日 令和2年3月24日(2020.3.24)

(51) Int.Cl.

**A63F 7/02 (2006.01)**

F 1

A 6 3 F 7/02 3 2 O

A 6 3 F 7/02 3 2 6 Z

請求項の数 4 (全 37 頁)

(21) 出願番号 特願2018-78858 (P2018-78858)

(22) 出願日 平成30年4月17日 (2018.4.17)

(62) 分割の表示 特願2016-74897 (P2016-74897)

分割

原出願日 平成28年4月4日 (2016.4.4)

(65) 公開番号 特開2018-108527 (P2018-108527A)

(43) 公開日 平成30年7月12日 (2018.7.12)

審査請求日 平成31年1月29日 (2019.1.29)

(73) 特許権者 391010943

株式会社藤商事

大阪府大阪市中央区内本町一丁目1番4号

(74) 代理人 100100376

弁理士 野中 誠一

(72) 発明者 大澤 孝政

愛知県江南市古知野町朝日250番地 サ

ン電子株式会社内

審査官 柴田 和雄

最終頁に続く

(54) 【発明の名称】遊技機

## (57) 【特許請求の範囲】

## 【請求項 1】

所定の抽選処理の抽選結果に対応する画像演出を実行する遊技機であって、

画像演出を中心統括的に制御する画像演出制御手段と、画像演出を構成する静止画及び

/又は動画の構成要素となるCGデータを記憶するデータ記憶手段と、データ記憶手段から

読み出したCGデータに基づいて、表示装置に出力すべき画像データを生成する画像生成手段と、を有して構成され、

所定の動作周期で間欠的に機能して、表示装置の表示内容を特定する描画リストを画像生成手段に出力する画像演出制御手段による第1手段と、

第1手段によって生成された描画リストを解釈して、必要時には、一フレームを構成するためには必要なCGデータ、又は、連続する複数フレームを構成するために必要なCGデータをデータ記憶手段から読み出し、第1バッファ領域に一時記憶すると共に、描画リストを書き換える画像生成手段による第2手段と、

所定の動作周期で間欠的に機能して、第1手段によって生成された描画リスト、又は第2手段により書き換えられた描画リストに基づいて、表示装置の表示画面を構成する画像データを、第2バッファ領域に生成する画像生成手段による第3手段と、

所定の動作周期で間欠的に機能して、第3手段が生成した画像データを一動作周期遅れて読み出して表示装置に出力する画像生成手段による第4手段と、を有して構成され、

第2手段は、第1手段が描画リストを出力したその動作周期において、第1手段が出力した描画リストに対応する動作を実行するよう構成されていることを特徴とする遊技機。

10

20

**【請求項 2】**

描画リストには、画像データの生成に先行して、第2バッファ領域をクリアすることを指示する命令が記載されている請求項1に記載の遊技機。

**【請求項 3】**

第3手段は、第2手段により書き換えられた描画リストを、内蔵メモリよりアクセス速度が遅いが、データ記憶手段を構成するCGメモリよりアクセス速度が速い外付けメモリから取得するよう構成されている請求項1又は2に記載の遊技機。

**【請求項 4】**

画像データは、画像生成手段の内部回路において二系統のLVDS信号に分割された後、デュアルリンク接続で表示装置に伝送される請求項1～3の何れかに記載の遊技機。

10

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は、遊技動作に起因する抽選処理を行い、その抽選結果に対応する画像演出を実行する遊技機に関し、特に、迫力ある画像演出を安定して実行できる遊技機に関する。

**【背景技術】****【0002】**

パチンコ機などの弾球遊技機は、遊技盤に設けた図柄始動口と、複数の表示図柄による一連の図柄変動態様を表示する図柄表示部と、開閉板が開閉される大入賞口などを備えて構成されている。そして、図柄始動口に設けられた検出スイッチが遊技球の通過を検出すると入賞状態となり、遊技球が賞球として払出された後、図柄表示部では表示図柄が所定時間変動される。その後、7・7・7などの所定の態様で図柄が停止すると大当たり状態となり、大入賞口が繰返し開放されて、遊技者に有利な遊技状態を発生させている。

20

**【0003】**

このような遊技状態を発生させるか否かは、図柄始動口に遊技球が入賞したことを条件に実行される大当たり抽選で決定されており、上記の図柄変動動作は、この抽選結果を踏まえたものとなっている。例えば、抽選結果が当選状態である場合には、リーチアクションなどと称される演出動作を20秒前後実行し、その後、特別図柄を整列させている。一方、ハズレ状態の場合にも、同様のリーチアクションが実行されることがあり、この場合には、遊技者は、大当たり状態になることを強く念じつつ演出動作の推移を注視することになる。そして、図柄変動動作の終了時に、停止ラインに所定図柄が揃えば、大当たり状態であることが遊技者に保証されたことになる。

30

**【先行技術文献】****【特許文献】****【0004】**

【特許文献1】特開2013-009741号公報

【特許文献2】特開2012-245164号公報

【特許文献3】特開2012-055507号公報

【特許文献4】特開2012-055371号公報

【特許文献5】特開2008-228969号公報

40

【特許文献6】特開2006-026185号公報

【特許文献7】特開2005-052258号公報

【特許文献8】特開2004-313562号公報

**【発明の概要】****【発明が解決しようとする課題】****【0005】**

この種の遊技機では、各種の演出を複雑化かつ豊富化したいところ、特に、画像演出については、その要請が高く、斬新な画像演出を実行する遊技機についても各種提案されている（特許文献1～8）。

**【0006】**

50

しかし、迫力ある画像演出を安定して実行できる新たな構成が望まれるところである。

【0010】

この発明は、上記の問題点に鑑みてなされたものであって、迫力ある画像演出を安定して実行できる構成を有する遊技機を提供することを目的とする。

【課題を解決するための手段】

【0011】

上記の目的を達成するため、本発明は、所定の抽選処理の抽選結果に対応する画像演出を実行する遊技機であって、画像演出を中心統括的に制御する画像演出制御手段と、画像演出を構成する静止画及び／又は動画の構成要素となるCGデータを記憶するデータ記憶手段と、データ記憶手段から読み出したCGデータに基づいて、表示装置に出力すべき画像データを生成する画像生成手段と、を有して構成され、所定の動作周期で間欠的に機能して、表示装置の表示内容を特定する描画リストを画像生成手段に出力する画像演出制御手段による第1手段と、第1手段によって生成された描画リストを解釈して、必要時には、一フレームを構成するために必要なCGデータ、又は、連続する複数フレームを構成するために必要なCGデータをデータ記憶手段から読み出し、第1バッファ領域に一時記憶すると共に、描画リストを書き換える画像生成手段による第2手段と、所定の動作周期で間欠的に機能して、第1手段によって生成された描画リスト、又は第2手段により書き換えられた描画リストに基づいて、表示装置の表示画面を構成する画像データを、第2バッファ領域に生成する画像生成手段による第3手段と、所定の動作周期で間欠的に機能して、第3手段が生成した画像データを一動作周期遅れて読み出して表示装置に出力する画像生成手段による第4手段と、を有して構成され、第2手段は、第1手段が描画リストを出力したその動作周期において、第1手段が出力した描画リストに対応する動作を実行するよう構成されている。

10

【発明の効果】

【0017】

上記した本発明の遊技機によれば、迫力ある画像演出を安定して実行することができる。

20

【図面の簡単な説明】

【0018】

30

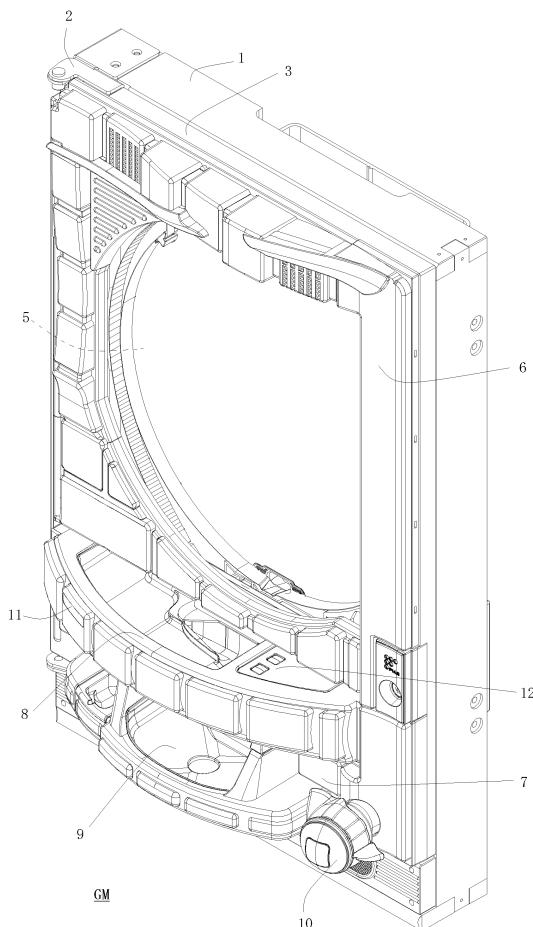

【図1】実施例に示すパチンコ機の斜視図である。

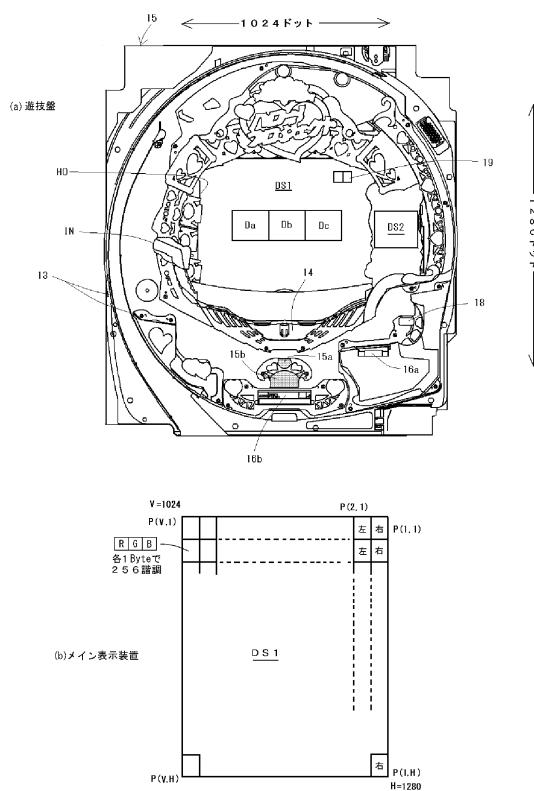

【図2】図1のパチンコ機の遊技盤を示す正面図と、メイン表示装置の構成を図示したものである。

【図3】実施例のパチンコ機の全体構成を示すブロック図である。

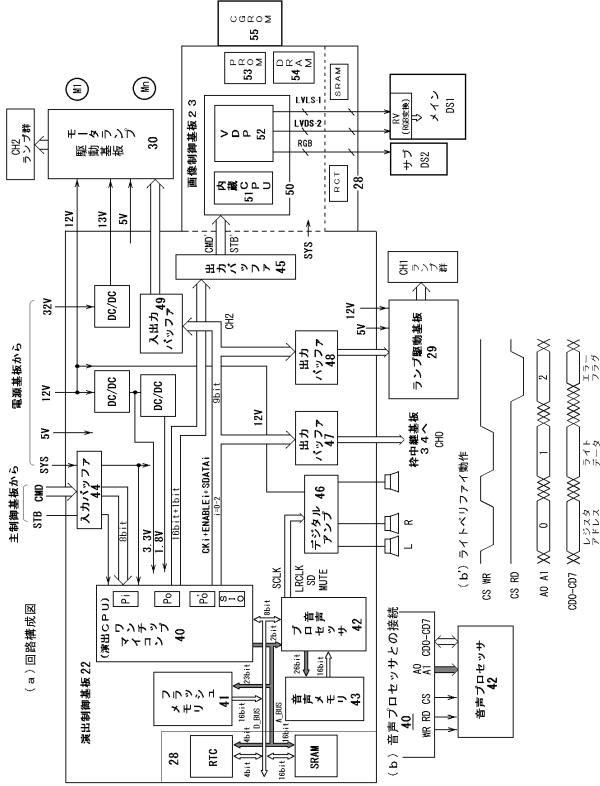

【図4】演出制御部と画像制御部の回路構成を例示するブロック図である。

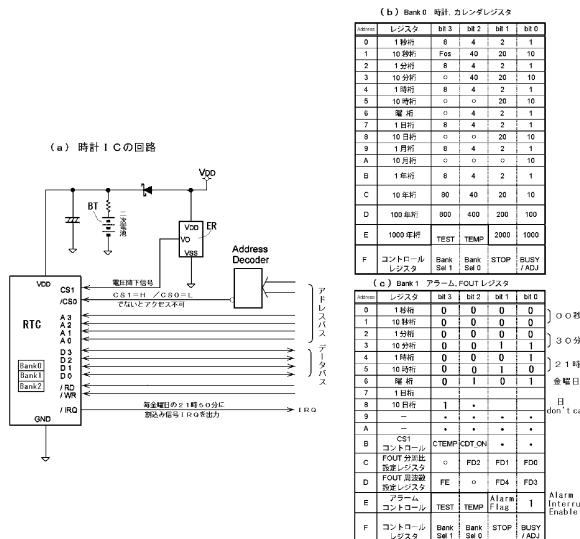

【図5】時計ICの構成を説明する図面である。

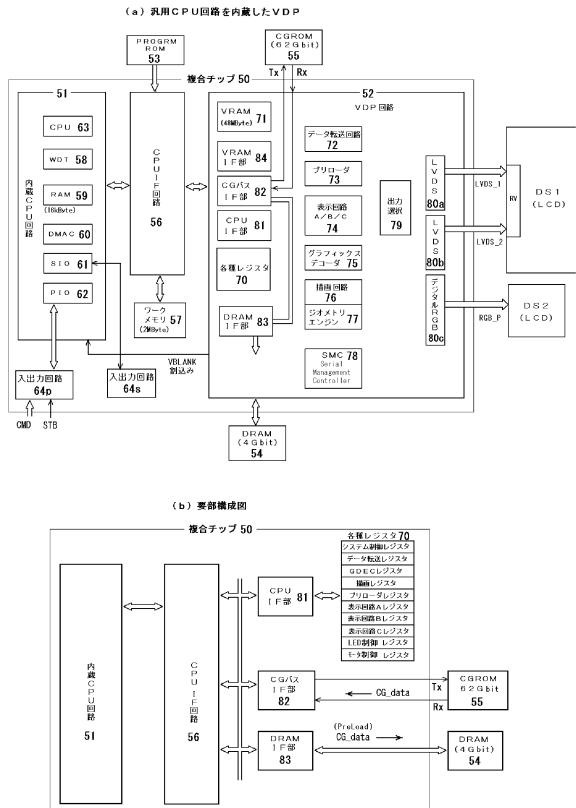

【図6】画像演出を担当する複合チップの内部構成を示すブロック図である。

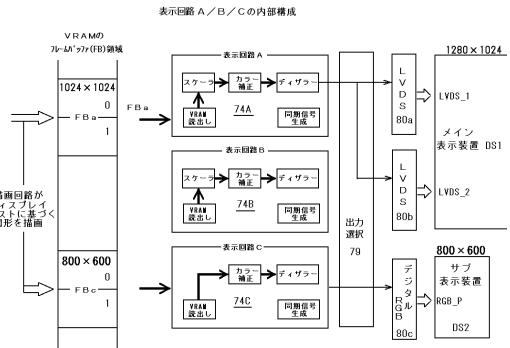

【図7】表示回路の動作を説明する図面である。

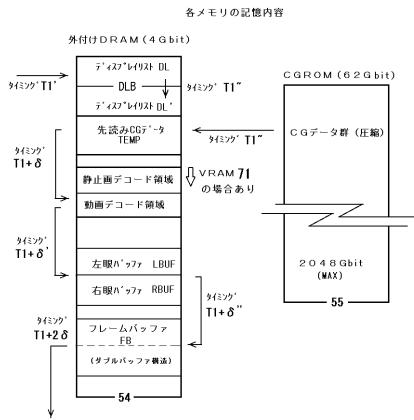

【図8】メモリの記憶内容と、画像演出を実現する動作手順を説明する図面である。

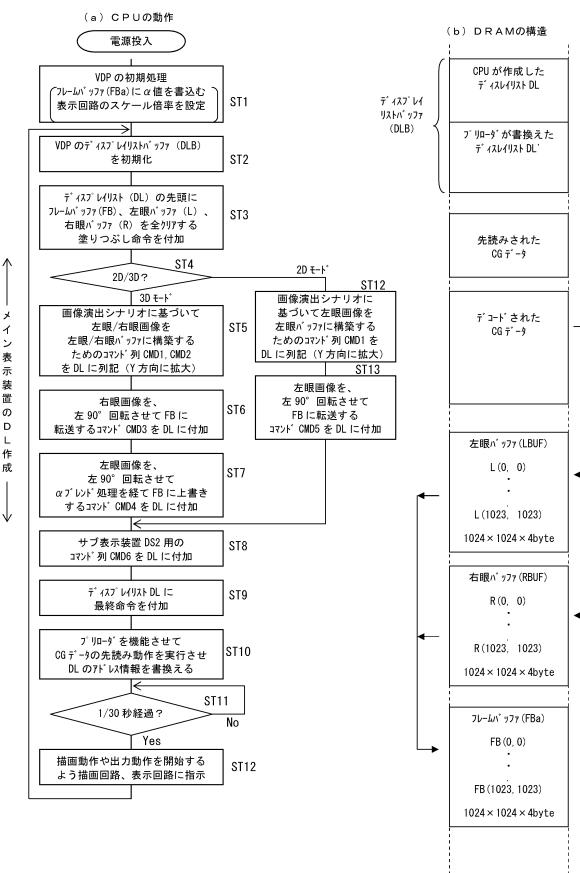

【図9】VDP回路を制御する画像制御CPUの動作を説明するフローチャートと関連図である。

40

【図10】VDP回路の内部動作を説明するフローチャートとタイムチャートである。

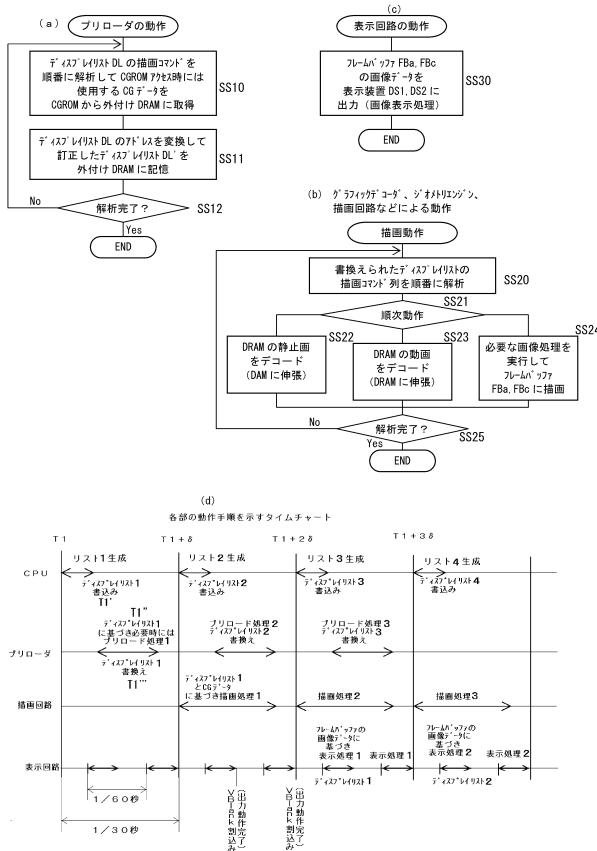

【図11】メイン表示装置の一フレーム画像の生成過程の前半部分を説明する図面である。

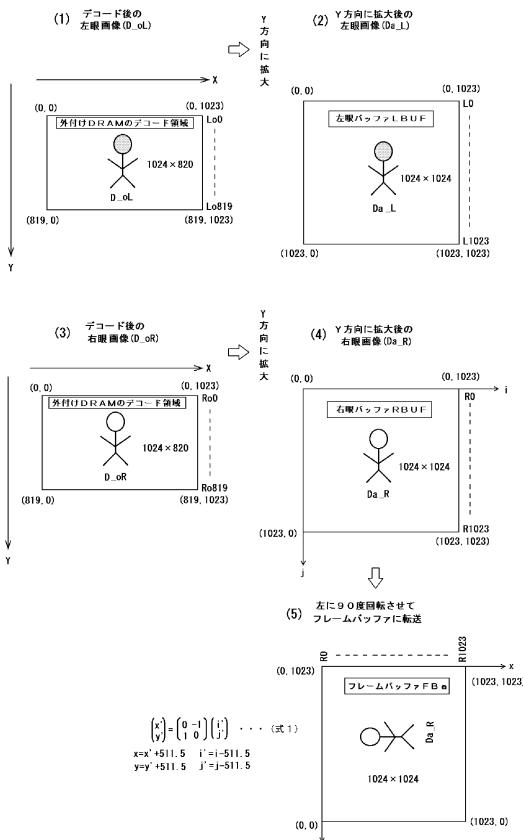

【図12】メイン表示装置の一フレーム画像の生成過程の後半部分を説明する図面である。

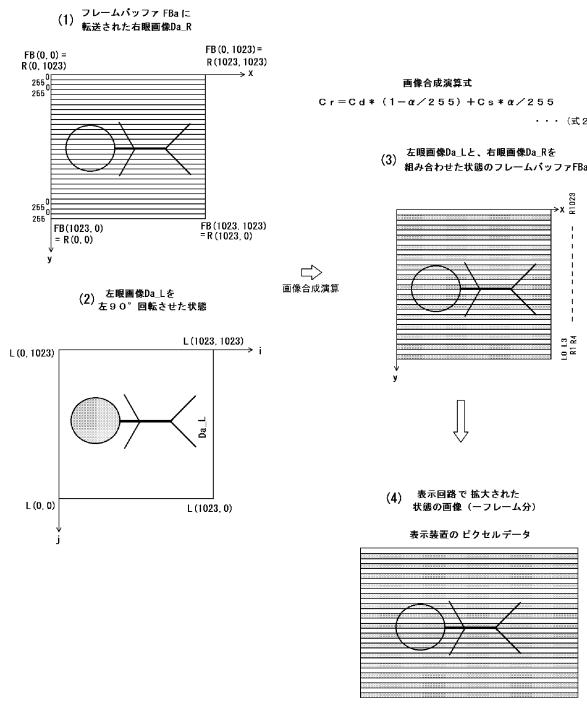

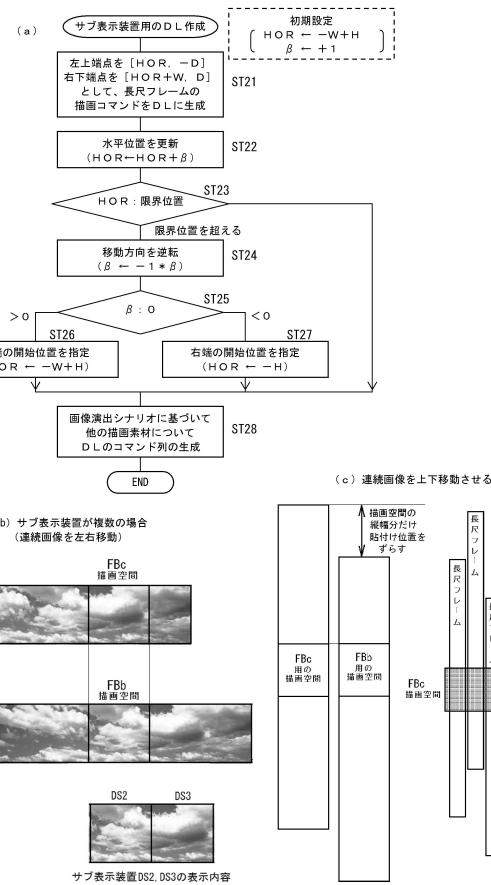

【図13】サブ表示装置の背景画像を移動させるためのディスプレイリストを説明する図面である。

【図14】サブ表示装置の背景画像の移動動作を説明する図面である。

【図15】別の実施例について、メイン表示装置の一フレーム画像の生成過程を説明する

50

図面である。

【図16】更に別の実施例を説明する図面である。

【発明を実施するための形態】

【0019】

以下、実施例に基づいて本発明を詳細に説明する。図1は、本実施例のパチンコ機GMを示す斜視図である。このパチンコ機GMは、島構造体に着脱可能に装着される矩形枠状の木製外枠1と、外枠1に固着されたヒンジ2を介して開閉可能に枢着される前枠3とで構成されている。この前枠3には、遊技盤5が、裏側からではなく、表側から着脱自在に装着され、その前側には、ガラス扉6と前面板7とが夫々開閉自在に枢着されている。

【0020】

ガラス扉6の外周には、LEDランプなどによる電飾ランプが、略C字状に配置されている。一方、ガラス扉6の上部左右位置と下側には、全3個のスピーカが配置されている。上部に配置された2個のスピーカは、各々、左右チャネルR,Lの音声を出力し、下側のスピーカは重低音を出力するよう構成されている。

【0021】

前面板7には、発射用の遊技球を貯留する上皿8が装着され、前枠3の下部には、上皿8から溢れ出し又は抜き取った遊技球を貯留する下皿9と、発射ハンドル10とが設けられている。発射ハンドル10は発射モータと連動しており、発射ハンドル10の回動角度に応じて動作する打撃槌によって遊技球が発射される。

【0022】

上皿8の外周面には、遊技者の左手で操作できる位置に操作ボタン11が設けられており、遊技者は、発射ハンドル10から右手を離すことなく、必要に応じて、操作ボタン11を操作することができる。この操作ボタン11は、通常時は、メイン表示装置DS1について、2D表示と3D表示をトグル的に切り替える用途に使用される。すなわち、遊技者が3D表示に疲れたような場合、操作ボタン11を押圧すると、メイン表示装置DS1の画像が自動的に2D表示に変更され、もう一度、操作ボタン11を押圧すると3D表示に戻るよう構成されている。

【0023】

なお、この操作ボタン11は、遊技者を遊技に参加させるためのチャンスボタンを兼ねており、ゲーム状態がボタンチャンス状態となって、内蔵ランプが点灯された後は、遊技者が参加する遊技用途に使用される。

【0024】

上皿8の右部には、カード式球貸し機に対する球貸し操作用の操作パネル12が設けられ、カード残額を3桁の数字で表示する度数表示部と、所定金額分の遊技球の球貸しを指示する球貸しスイッチと、ゲーム終了時にカードの返却を指令する返却スイッチとが設かれている。

【0025】

図2に示すように、遊技盤5の表面には、金属製の外レールと内レールとからなるガイドレール13が環状に設けられ、その略中央には、中央開口HOが設けられている。そして、中央開口HOの可能には、不図示の可動演出体が隠蔽状態で収納されており、可動予告演出時には、その可動演出体が上昇して露出状態となることで、所定の信頼度の予告演出を実現している。ここで、予告演出とは、遊技者に有利な大当たり状態が招来することを不確定に報知する演出であり、予告演出の信頼度とは、大当たり状態が招来する確率を意味している。

【0026】

中央開口HOには、19インチ程度の大型の液晶カラーディスプレイ(LCD)で構成されたメイン表示装置DS1が配置され、その表面側にはレンチキュラーレンズが配置されている。したがって、遊技者は、3D表示による迫力ある画像演出を楽しむことができる。

【0027】

10

20

30

40

50

また、メイン表示装置 D S 1 の右側には、5インチ程度の小型の液晶カラーディスプレイで構成されたサブ表示装置 D S 2 が配置され、2D表示による予告演出などが実行される。

#### 【0028】

特に限定されるものではないが、メイン表示装置 D S 1 は、ピクセル配列 P ( i , j ) が、P ( 1 , 1 ) ~ P ( 1 0 2 4 , 1 2 8 0 ) の表示画面を有し、この横 1 2 8 0 × 縦 1 0 2 4 ピクセルの表示画面を 90° 右回転させることで、表示画面を縦長に配置している。なお、図示の状態では、役物や装飾フレームに隠れている部分があるので、メイン表示装置 D S 1 の表示画面が横長に見えるが、実際には、縦 1 2 8 0 × 横 1 0 2 4 ピクセル P ( i , j ) の縦長形状であって、描画走査線は、図示の上下方向に走査される。

10

#### 【0029】

そして、メイン表示装置 D S 1 の前面にレンチキュラーレンズが配置されていることに対応して、配置状態の縦方向（走査方向）を右側から評価した奇数列（1列、3列、5列・・・）が、右眼用の画像（以下右眼画像と称す）であり、偶数列（2列、4列、6列・・・）が左眼用の画像（以下左眼画像と称す）となる。また、各ピクセル P ( i , j ) は、R B G 三色が、各々 8 bit で輝度制御されることで、R G B 三色とも 256 諧調を実現している。

#### 【0030】

このように構成されたメイン表示装置 D S 1 は、大当たり状態に係わる特定図柄を変動表示すると共に背景画像や各種のキャラクタなどをアニメーション的に 3D 表示する装置である。この表示装置 D S 1 は、中央部に特別図柄表示部 D a ~ D c と右上部に普通図柄表示部 1 9 を有している。そして、特別図柄表示部 D a ~ D c では、大当たり状態の招来を期待させるリーチ演出が実行されることがあり、特別図柄表示部 D a ~ D c 及びその周りでは、適宜な動画などによる予告演出が実行される。

20

#### 【0031】

サブ表示装置 D S 2 は、通常時には、左右に往復移動する背景画（簡易動画）が、他のスライド画像の背面側に表示され、必要時には、可動して画像予告演出を実行するよう構成されている。すなわち、実施例のサブ表示装置 D S 2 は、単なる表示装置ではなく、予告演出を実行する可動演出体としても機能している。

#### 【0032】

30

ここで、サブ表示装置 D S 2 が可動する予告演出は、その信頼度が、出現個数などに応じて適宜に高く設定されており、遊技者は、大きな期待感をもってサブ表示装置 D S 2 に注目することになる。なお、サブ表示装置 D S 2 の表示画面は、横 8 0 0 × 縦 6 0 0 ピクセルを有して構成され、各ピクセル P ( i , j ) は、R B G 三色が各々 8 bit で輝度制御されることで、R G B 三色とも 256 諧調を実現している。

#### 【0033】

遊技盤 5 の構成に戻って説明を続けると、遊技球が落下移動する遊技領域には、第 1 図柄始動口 1 5 a、第 2 図柄始動口 1 5 b、第 1 大入賞口 1 6 a、第 2 大入賞口 1 6 b、普通入賞口 1 7、及び、ゲート 1 8 が配設されている。これらの入賞口 1 5 ~ 1 8 は、それぞれ内部に検出スイッチを有しており、遊技球の通過を検出できるようになっている。

40

#### 【0034】

第 1 図柄始動口 1 5 a の上部には、導入口 I N から進入した遊技球がシーソー状又はルーレット状に移動した後に、第 1 図柄始動口 1 5 に入賞可能に構成された演出ステージ 1 4 が配置されている。そして、第 1 図柄始動口 1 5 に遊技球が入賞すると、特別図柄表示部 D a ~ D c の変動動作が開始されるよう構成されている。

#### 【0035】

第 2 図柄始動口 1 5 b は、左右一対の開閉爪を備えた電動式チューリップで開閉されるよう構成され、普通図柄表示部 1 9 の変動後の停止図柄が当り図柄を表示した場合には、所定時間だけ、若しくは、所定個数の遊技球を検出するまで、開閉爪が開放されるようになっている。

50

**【0036】**

なお、普通図柄表示部19は、普通図柄を表示するものであり、ゲート18を通過した遊技球が検出されると、普通図柄が所定時間だけ変動し、遊技球のゲート18の通過時点において抽出された抽選用乱数値により決定される停止図柄を表示して停止する。

**【0037】**

第1大入賞口16aは、前後方向に進退するスライド盤を有して構成され、第2大入賞口16bは、下端が軸支されて前方に開放する開閉板を有して構成されている。第1大入賞口16aや第2大入賞口16bの動作は、特に限定されないが、この実施例では、第1大入賞口16aは、第1図柄始動口15aに対応し、第2大入賞口16bは、第1図柄始動口15bに対応するよう構成されている。10

**【0038】**

すなわち、第1図柄始動口15aに遊技球が入賞すると、特別図柄表示部D<sub>a</sub>～D<sub>c</sub>の変動動作が開始され、その後、所定の大当たり図柄が特別図柄表示部D<sub>a</sub>～D<sub>c</sub>に整列すると、第1大当たりたる特別遊技が開始され、第1大入賞口16aのスライド盤が、前方に開放されて遊技球の入賞が容易化される。

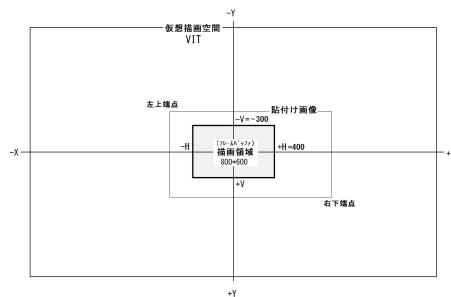

**【0039】**

一方、第2図柄始動口15bへの遊技球の入賞によって開始された変動動作の結果、所定の大当たり図柄が特別図柄表示部D<sub>a</sub>～D<sub>c</sub>に整列すると、第2大当たりたる特別遊技が開始され、第2大入賞口16bの開閉板が開放されて遊技球の入賞が容易化される。特別遊技（大当たり状態）の遊技価値は、整列する大当たり図柄などに対応して種々相違するが、何れの遊技価値が付与されるかは、遊技球の入賞タイミングに応じた抽選結果に基づいて予め決定される。20

**【0040】**

典型的な大当たり状態では、大入賞口16の開閉板が開放された後、所定時間が経過し、又は所定数（例えば10個）の遊技球が入賞すると開閉板が閉じる。このような動作は、最大で例えば15回まで継続され、遊技者に有利な状態に制御される。なお、特別図柄表示部D<sub>a</sub>～D<sub>c</sub>の変動後の停止図柄が特別図柄のうちの特定図柄であった場合には、特別遊技の終了後のゲームが高確率状態（確変状態）となるという特典が付与される。

**【0041】**

図3は、上記した各動作を実現するパチンコ機GMの全体回路構成を示すブロック図であり、図4はその一部を詳細に図示したものである。30

**【0042】**

図3に示す通り、このパチンコ機GMは、AC24Vを受けて各種の直流電圧や、電源異常信号ABN1、ABN2やシステムリセット信号（電源リセット信号）SYSなどを出力する電源基板20と、遊技制御動作を中心統括的に担う主制御基板21と、主制御基板21から受けた制御コマンドCMDに基づいてランプ演出及び音声演出などを実行する演出制御基板22と、演出制御基板22から受けた制御コマンドCMD'に基づいて2つの表示装置DS1, DS2を駆動する画像制御基板23と、主制御基板21から受けた制御コマンドCMD"に基づいて払出モータMを制御して遊技球を払い出す払出制御基板24と、遊技者の操作に応答して遊技球を発射させる発射制御基板25と、を中心に構成されている。40

**【0043】**

図示の通り、主制御基板21が出力する制御コマンドCMDは、演出制御基板22に伝送される。また、主制御基板21が出力する制御コマンドCMD"は、主基板中継基板32を経由して、払出制御基板24に伝送される。

**【0044】**

制御コマンドCMD, CMD', CMD"は、何れも16ビット長であるが、主制御基板21や払出制御基板24が関係する制御コマンドは、8ビット長毎に2回に分けてパラレル送信されている。一方、演出制御基板22から画像制御基板23に伝送される制御コマンドCMD'は、16ビット長をまとめてパラレル伝送されている。そのため、可動予50

告演出を含む予告演出を、多様化して多数の制御コマンドを連続的に送受信するような場合でも、迅速にその処理を終えることができ、他の制御動作に支障を与えない。

#### 【0045】

図示の通り、本実施例では、画像制御基板23及び演出制御基板22からアクセス可能な液晶インターフェイス基板28が設けられている。そして、液晶インターフェイス基板28は、現在時刻を計時可能な時計回路（リアルタイムクロック）RTCと、遊技実績情報を記憶するメモリ素子（Static Random Access Memory）SRAMが搭載されている。

#### 【0046】

また、画像制御基板23は、液晶インターフェイス基板28を経由して、メイン表示装置DS1とサブ表示装置DS2を駆動している。ここで、液晶インターフェイス基板28と、画像制御基板23とは、配線ケーブルを経由することなく、雄型コネクタと雌型コネクタとを直結されている。同様に、演出制御基板23と液晶インターフェイス基板28についても、配線ケーブルを経由することなく、雄型コネクタと雌型コネクタとを直結されている。そのため、各電子回路の回路構成を複雑高度化しても基板全体の収納空間を最小化できると共に、接続ラインを最短化することで耐ノイズ性を高めることができる。

10

#### 【0047】

これら主制御基板21、演出制御基板22、画像制御基板23、及び払出制御基板24には、ワンチップマイコンなどのコンピュータ回路がそれぞれ搭載されている。そこで、これらの制御基板21～24と液晶インターフェイス基板28に搭載された回路、及びその回路によって実現される動作を機能的に総称して、本明細書では、主制御部21、演出制御部22、画像制御部23、及び払出制御部24と言うことがある。なお、主制御部21に対して、演出制御部22、画像制御部23、及び払出制御部24の全部又は一部がサブ制御部となる。

20

#### 【0048】

このパチンコ機GMは、図3の破線で囲む枠側部材GM1と、遊技盤5の背面に固定された盤側部材GM2とに大別されている。枠側部材GM1には、ガラス扉6や前面板7が接着された前枠3と、その外側の木製外枠1とが含まれており、機種の変更に拘わらず、長期間にわたって遊技ホールに固定的に設置される。一方、盤側部材GM2は、機種変更に対応して交換され、新たな盤側部材GM2が、元の盤側部材の代わりに枠側部材GM1に取り付けられる。なお、枠側部材1を除く全てが、盤側部材GM2である。

30

#### 【0049】

図3の破線枠に示す通り、枠側部材GM1には、電源基板20と、払出制御基板24と、発射制御基板25と、枠中継基板35とが含まれており、これらの回路基板が、前枠3の適所に各々固定されている。一方、遊技盤5の背面には、主制御基板21、演出制御基板22、画像制御基板23が、表示装置DS1, DS2やその他の回路基板と共に固定されている。そして、枠側部材GM1と盤側部材GM2とは、一箇所に集中配置された接続コネクタC1～C4によって電気的に接続されている。

#### 【0050】

電源基板20は、接続コネクタC2を通して、主基板中継基板32に接続され、接続コネクタC3を通して、電源中継基板33に接続されている。電源基板20には、交流電源の投入と遮断とを監視する電源監視部MNTが設けられている。電源監視部MNTは、交流電源が投入されたことを検知すると、所定時間だけシステムリセット信号SYSをLレベルに維持した後に、これをHレベルに遷移させる。

40

#### 【0051】

また、電源監視部MNTは、交流電源の遮断を検知すると、電源異常信号ABN1, ABN2を、直ちにLレベルに遷移させる。電源異常信号ABN1, ABN2は、電源投入後に速やかにHレベルとなる。

#### 【0052】

ところで、本実施例のシステムリセット信号は、交流電源に基づく直流電源によって生成されている。そのため、交流電源の投入（通常は電源スイッチのON）を検知してHレ

50

ベルに増加した後は、直流電源電圧が異常レベルまで低下しない限り、Hレベルを維持する。したがって、直流電源電圧が維持された状態で、交流電源が瞬停状態となっても、システムリセット信号SYSがCPUをリセットすることはない。なお、電源異常信号ABN1, ABN2は、交流電源の瞬停状態でも出力される。

#### 【0053】

主基板中継基板32は、電源基板20から出力される電源異常信号ABN1、バックアップ電源BAK、及びDC5V, DC12V, DC32Vを、そのまま主制御部21に出力している。一方、電源中継基板33は、電源基板20から受けたシステムリセット信号SYSや、交流及び直流の電源電圧を、そのまま演出制御部22に出力している。そして、演出制御部22は、受けたシステムリセット信号SYSを、そのまま画像制御部23に出力している。10

#### 【0054】

一方、払出制御基板24は、中継基板を介することなく、電源基板20に直結されており、主制御部21が受けると同様の電源異常信号ABN2や、バックアップ電源BAKを、その他の電源電圧と共に直接的に受けている。

#### 【0055】

電源基板20が出力するシステムリセット信号SYSは、電源基板20に交流電源24Vが投入されたことを示す電源リセット信号であり、この電源リセット信号によって演出制御部22のワンチップマイコン40と画像制御部23の内蔵CPU回路は、その他の回路素子やVDPを含む内部回路と共に電源リセットされるようになっている。20

#### 【0056】

但し、このシステムリセット信号SYSは、主制御部21と払出制御部24には、供給されておらず、各々の回路基板21, 24のリセット回路RSTにおいて電源リセット信号(CPUリセット信号)が生成されている。そのため、例えば、接続コネクタC2がガタついたり、或いは、配線ケーブルにノイズが重畠しても、主制御部21や払出制御部24のCPUが異常リセットされるおそれはない。なお、演出制御部22と画像制御部23は、主制御部21からの制御コマンドに基づいて、従属的に演出動作を実行することから、回路構成の複雑化を回避するために、電源基板20から出力されるシステムリセット信号SYSを利用している。

#### 【0057】

主制御部21や払出制御部24に設けられたリセット回路RSTは、各々ウォッチドッグタイマを内蔵しており、各制御部21, 24のCPUから、定時的なクリアパルスを受けない限り、各CPUは強制的にリセットされる。

#### 【0058】

また、この実施例では、RAMクリア信号CLRは、主制御部21で生成されて主制御部21と払出制御部24のワンチップマイコンに伝送されている。ここで、RAMクリア信号CLRは、各制御部21, 24のワンチップマイコンの内蔵RAMの全領域を初期設定するか否かを決定する信号であって、係員が操作する初期化スイッチSWのON/OFF状態に対応した値を有している。

#### 【0059】

主制御部21及び払出制御部24は、電源基板20から電源異常信号ABN1, ABN2を受けることによって、停電や営業終了に先立って、必要な終了処理を開始するようになっている。また、バックアップ電源BAKは、営業終了や停電により交流電源24Vが遮断された後も、主制御部21と払出制御部24のワンチップマイコンの内蔵RAMのデータを保持するDC5Vの直流電源である。したがって、主制御部21と払出制御部24は、電源遮断前の遊技動作を電源投入後に再開できることになる(電源バックアップ機能)。このパチンコ機では少なくとも数日は、各ワンチップマイコンのRAMの記憶内容が保持されるよう設計されている。

#### 【0060】

図3に示す通り、主制御部21は、主基板中継基板32を経由して、払出制御部24に

10

20

30

40

50

制御コマンドCMD”を送信する一方、払出制御部24からは、遊技球の払出動作を示す賞球計数信号や、払出動作の異常に係わるステータス信号CONや、動作開始信号BGNを受信している。ステータス信号CONには、例えば、補給切れ信号、払出不足エラー信号、下皿満杯信号が含まれる。動作開始信号BGNは、電源投入後、払出制御部24の初期動作が完了したことを主制御部21に通知する信号である。

#### 【0061】

また、主制御部21は、遊技盤中継基板31を経由して、遊技盤5の各遊技部品に接続されている。そして、遊技盤上の各入賞口16～18に内蔵された検出スイッチのスイッチ信号を受ける一方、電動式チューリップなどのソレノイド類を駆動している。ソレノイド類や検出スイッチは、主制御部21から配電された電源電圧VB(12V)で動作するよう構成されている。また、図柄始動口15への入賞状態などを示す各スイッチ信号は、電源電圧VB(12V)と電源電圧Vcc(5V)とで動作するインタフェイスICで、TTLレベル又はCMOSレベルのスイッチ信号に変換された上で、主制御部21に伝送される。

#### 【0062】

先に説明した通り、演出制御基板22と画像制御基板23と液晶インタフェイス基板28とはコネクタ連結によって一体化されており、演出制御部22は、電源中継基板33を経由して、電源基板20から各レベルの直流電圧(5V, 12V, 32V)と、システムリセット信号SYSを受けている(図3及び図4(a)参照)。

#### 【0063】

また、演出制御部22は、主制御部21から制御コマンドCMDとストローブ信号STBとを受けている。そして、演出制御部22は、ランプ駆動基板36及びランプ駆動基板29やモータランプ駆動基板30に搭載されたドライバICに、ランプ駆動信号SDATAを、クロック信号CKに同期してシリアル传送することで、多数のLEDランプや電飾ランプで構成されたランプ群を駆動して、制御コマンドCMDに基づくランプ演出を実現している。

#### 【0064】

本実施例の場合、ランプ演出は、三系統のランプ群CH0～CH2によって実行されており、ランプ駆動基板36は、枠中継基板34, 35を経由して、CH0のランプ駆動信号SDATA0を、クロック信号CK0に同期して受けている(クロック同期式シリアル通信)。なお、シリアル信号として传送される一連のランプ駆動信号SDATA0は、動作制御信号ENABLE0がアクティブルレベルに変化したタイミングで、ドライバICからランプ群CH0に出力されることで一斉に点灯状態が更新される。

#### 【0065】

以上の点は、ランプ駆動基板29についても同様であり、ランプ駆動基板29のドライバICは、ランプ群CH1のランプ駆動信号SDATA1を、クロック信号CK1に同期して受け、動作制御信号ENABLE1がアクティブルレベルに変化したタイミングで、ランプ群CH1の点灯状態を一斉に更新している。

#### 【0066】

一方、モータランプ駆動基板30に搭載されたドライバICは、クロック同期式で传送されるランプ駆動信号を受けてランプ群CH2を駆動すると共に、クロック同期式で传送されるモータ駆動信号を受けて、複数のステッピングモータで構成された演出モータ群M1～Mnを駆動している。なお、ランプ駆動信号とモータ駆動信号は、一連のシリアル信号SDATA2であって、クロック信号CK1に同期してシリアル传送され、これを受けたドライバICは、動作制御信号ENABLE2がアクティブルレベルに変化するタイミングで、ランプ群CH2やモータ群M1～Mnの駆動状態を更新する。

#### 【0067】

また、演出制御部22は、画像制御部23に対して、制御コマンドCMD'及びストローブ信号STB'、電源基板20から受けたシステムリセット信号SYSと、2種類の直流電圧(12V, 5V)とを出力している。そして、画像制御部23では、制御コマン

10

20

30

40

50

D C M D'に基づいて表示装置D S 1, D S 2を駆動して各種の画像演出を実行している。

#### 【0068】

図3及び図4(a)に示す通り、画像制御部23は、汎用ワンチップマイコンと同等の内部構成を有する内蔵C P U回路(画像演出制御装置)51と、V D P(Video Display Processor)52と、を内蔵した複合チップ50を中心に構成されている。また、内蔵C P Uの制御プログラムを記憶する制御メモリ(P R O M)53と、大量のデータを高速にアクセス可能なD R A M(Dynamic Random Access Memory)54と、画像制御に必要な大量のC Gデータを記憶するC G R O M55とが搭載されている。

#### 【0069】

そして、C G R O M55から読み出したC Gデータに基づいてV D P52が生成した画像データは、第1と第2のL V D S信号(LVDS\_1, LVDS\_2)と、R G Bパラレル信号RGB\_Pとして、液晶インターフェイス基板28に伝送される。

#### 【0070】

第1と第2のL V D S信号LVDS\_1, LVDS\_2は、メイン表示装置D S 1用の画像データであって、図2(b)に関して説明した通り、 $1280 \times 1024$ ピクセルで構成された一フレームを特定している。そして、本実施例では、この $1280 \times 1024$ 個のピクセルデータを確実に伝送するべく、ドットクロック $108\text{MHz}$ の画像データを、V D Pの内部回路(出力選択部79)において二系統のL V D S信号(LVDS\_a, LVDS\_b)に分割して、各々、 $1/60$ 秒に $640 \times 1024$ ピクセル( $= 655, 360$ )の画像データを、デュアルリンク接続でメイン表示装置D S 1に伝送している。

#### 【0071】

そのため、二系統のL V D S信号(LVDS\_a, LVDS\_b)のドットクロックは、各々、 $54\text{MHz}$ 程度に抑制されることになる。そして、メイン表示装置D S 1には、L V D S受信部R Vが内蔵されており(図4参照)、二系統のL V D S信号(LVDS\_a, LVDS\_b)から抽出された各 $640 \times 1024$ ピクセル分の画像データを纏めることで、一フレーム $1280 \times 1024$ ピクセル分のR G B画像データを再生している。

#### 【0072】

ところで、本実施例の場合、 $1280 \times 1024$ ピクセルは、左眼用の $1280 \times 512$ ピクセルと、右眼用の $1280 \times 512$ ピクセルに区分され、縦方向 $1280$ 個のピクセル列が、左眼用ピクセル列と右眼用ピクセル列として図2の左右方向に隣接している。一方、デュアルリンク接続では、走査方向(図2の縦方向)に評価して奇数ピクセルが、例えば、L V D S信号LVDS\_aで伝送され、その上下に隣接する偶数ピクセルが、L V D S信号LVDS\_bで伝送されるので、各L V D S信号(LVDS\_a, LVDS\_b)は、左眼用と右眼用の画像データが混在した状態となる。

#### 【0073】

次に、R G Bパラレル信号RGB\_Pは、各8ビットで全24ビット長のR G B信号と、同期信号とを含んだパラレル信号である。図2(b)に関して説明した通り、表示装置D S 2は、 $800 \times 600$ ピクセルであり、そのドットクロックは $54\text{MHz}$ 程度となる。

#### 【0074】

続いて、図4(a)に基づいて、演出制御部22の構成を更に詳細に説明する。図4(a)に示す通り、演出制御部22は、音声演出・ランプ演出・演出可動体による予告演出・データ転送などの処理を実行するワンチップマイコン40(演出制御C P U40)と、演出制御C P U40の制御プログラムや各種の演出データE Nを記憶する制御メモリ(flash memory)41と、内蔵レジスタR G 0 ~ R G nに設定される演出制御C P U40の指示に基づいて音声信号を再生して出力する音声プロセッサ42と、再生される音声信号の元データである圧縮音声データなどを記憶する音声メモリ43と、音声プロセッサ42から出力される音声信号を受けるデジタルアンプ46と、を備えて構成されている。

#### 【0075】

本実施例の場合、制御メモリ41に記憶されている演出データE Nには、ランプ演出や

10

20

30

40

50

音声演出の演出進行を管理するシナリオデータと、LEDの点滅態様を決定するランプ駆動データと、モータの回転態様を決定するモータ駆動データと、が含まれている。なお、ランプ駆動データやモータ駆動データは、1ビットずつ時間順次に出力されることで、ランプ駆動シリアル信号やモータ駆動シリアル信号となる。

#### 【0076】

ワンチップマイコン40には、複数のシリアル入出力ポートSIOと、複数のパラレル入出力ポートPIOとが内蔵されている。ここで、シリアル入出力ポートSIOには、CHiのランプ駆動信号又はモータ駆動信号SDATAiをクロック信号CKiに同期して出力するシリアル出力ポートSoiと、モータ群M1～Mnの原点センサ信号（シリアル信号）をクロック信号CK3に同期して受けるシリアルポートSiとが含まれている。なお、i=0～2であって、三系統のランプ群CH0～CH2や、CH2のランプ群と共に駆動されるモータ群M1～Mnに対応している。10

#### 【0077】

一方、パラレル入出力ポートPIOは、出力ポートPo, Po' と入力ポートPiに区分され、入力ポートPiには、主制御部21からの制御コマンドCMD及びストローブ信号STBが入力される。一方、出力ポートPo'からは動作制御信号ENABLE0～ENABLE2が出力され、出力ポートPoからは、制御コマンドCMD'及びストローブ信号STB'が出力されるよう構成されている。詳細には、主制御基板21から出力された制御コマンドCMD及びストローブ信号（割込み信号）STBが、バッファ44において、ワンチップマイコン40の電源電圧3.3Vに対応する論理レベルに降圧された後、入力ポートPiに8ビット単位で二回に分けて供給される。また、割込み信号STBは、演出制御CPU40の割込み端子に供給され、受信割込み処理によって、演出制御部22は、制御コマンドCMDを取得するよう構成されている。20

#### 【0078】

演出制御部22が取得する制御コマンドCMDには、（1）異常報知その他の報知用制御コマンドなどの他に、（2）図柄始動口への入賞に起因する各種演出動作の概要特定する制御コマンド（変動パターンコマンド）や、図柄種別を指定する制御コマンド（図柄指定コマンド）が含まれている。変動パターンコマンドで特定される演出動作の概要には、演出開始から演出終了までの演出総時間と、大当たり抽選における当否結果とが含まれている。30

#### 【0079】

また、図柄指定コマンドには、大当たり抽選の結果に応じて、大当たりの場合には、大当たり種別に関する情報（15R確変、2R確変、15R通常、2R通常など）を特定する情報が含まれ、ハズレの場合には、ハズレを特定する情報が含まれている。変動パターンコマンドで特定される演出動作の概要には、演出開始から演出終了までの演出総時間と、大当たり抽選における当否結果とが含まれている。なお、これらに加えて、リーチ演出や予告演出の有無などを含めて変動パターンコマンドで特定しても良いが、この場合でも、演出内容の具体的な内容は特定されていない。

#### 【0080】

そのため、演出制御部22では、変動パターンコマンドを取得すると、これに続いて演出抽選を行い、取得した変動パターンコマンドで特定される演出概要を更に具体化している。例えば、リーチ演出や予告演出について、その具体的な内容が決定される。そして、決定された具体的な遊技内容にしたがい、LED群などの点滅によるランプ演出や、スピーカによる音声演出の準備動作を行うと共に、画像制御部23に対して、ランプやスピーカによる演出動作に同期した画像演出に関する制御コマンドCMD'を出力する。40

#### 【0081】

このような演出動作に同期した画像演出を実現するため、演出制御部22は、出力ポートPoを通して、画像制御部23に対するストローブ信号（割込み信号）STB'と共に、16ビット長の制御コマンドCMD'を出力している。なお、演出制御部22は、図柄指定コマンドや、異常報知用制御コマンドや、その他の制御コマンドを受信した場合は、50

その8ビット単位の制御コマンドを、16ビット長に纏めた状態で、割込み信号S T B'と共に画像制御部23に向けて出力している。

#### 【0082】

先に説明した通り、本実施例の音声プロセッサ42は、演出制御C P U 4 0から内蔵レジスタ（音声制御レジスタ）R G 0～R G nに受ける指示（音声コマンドS N Dによる設定値）に基づいて、音声メモリ43をアクセスして、必要な音声信号を再生して出力している。図示の通り、音声プロセッサ42と、音声メモリ43とは、26ビット長の音声アドレスバスと、16ビット長の音声データバスで接続されている。そのため、音声メモリ43には、1Gビット（=  $2^{26} * 16$ ）のデータが記憶可能となる。

#### 【0083】

本実施例の場合、音声メモリ43に記憶された圧縮音声データは、13ビット長のフレーズ番号（000H～1FFFH）で特定されるフレーズ（phrase）圧縮データであり、一連の背景音楽の一曲分（B G M）や、ひと纏まりの演出音（予告音）などが、最高8192種類（=  $2^{13}$ ）、各々、フレーズ番号に対応して記憶されている。そして、このフレーズ番号は、演出制御C P U 4 0から音声プロセッサ42の音声制御レジスタR G 0～R G nに伝送される音声コマンドS N Dの設定値によって特定される。

10

#### 【0084】

音声コマンドS N Dは、複数（2又は3）バイト長であって、音声プロセッサ42に内蔵された多数の音声制御レジスタR G 0～R G nの何れかR G iに、所定の設定値を伝送するWrite用途で使用される。但し、本実施例の音声コマンドS N Dは、フレーズ番号などの設定値を書込むWrite用途だけでなく、所定の音声制御レジスタR G iからステータス情報（エラー情報）S T Sを読み出すRead用途でも使用される。なお、アクセス対象となる所定の音声制御レジスタR G iは、1バイト長のレジスタアドレスで特定される。

20

#### 【0085】

音声制御レジスタR G iへの設定値の設定（Write）は、必ずしも、音声制御レジスタ毎に個別的に実行する必要はなく、音声メモリ43に格納されているS A Cデータを指定して、一群の音声制御レジスタR G i～R G jに対する一連の設定動作を完了させることもできる。

#### 【0086】

S A Cデータとは、音声制御レジスタR G iのレジスタアドレス（1バイト）と、その音声制御レジスタR G iへの設定値（複数バイト）とを対応させた最大512個（最大1024バイト）の集合体を意味する。本実施例では、このようなS A Cデータが、必要組だけ、予め音声メモリ43に記憶されており、一組のS A Cデータは、单一のI D情報である13ビット程度のS A C番号で特定されるようになっている。

30

#### 【0087】

したがって、本実施例の場合、Write用途の音声コマンドS N Dは、S A C番号を指定して一組のS A Cデータを特定するか、或いは、設定値とレジスタアドレスとを個別的に特定することになる。

#### 【0088】

図4（b）に接続関係の要部を記載している通り、演出制御C P U 4 0と音声プロセッサ42は、1バイトデータを送受信可能なパラレル信号線（データバス）C D 0～C D 7と、動作管理データを送信可能な2ビット長の動作管理データ線（アドレスバス）A 0～A 1と、読み書き（read/write）動作を制御可能な2ビット長の制御信号線W R , R Dと、音声プロセッサ42を選択するチップセレクト信号線C Sとで接続されている。

40

#### 【0089】

パラレル信号線C D 0～C D 7は、演出制御C P U 4 0のデータバスで実現され、また、動作管理データ線A 0～A 1は、演出制御C P U 4 0のアドレスバスで実現されており、各々、演出制御C P U 4 0に接続されている。そして、演出制御C P U 4 0が、プログラム処理によって、例えば、I O R E A D動作やI O W R I T E動作を実行すると、制御信号W R , R Dやチップセレクト信号C Sが適宜に変化して、パラレル信号線C D 0～C

50

D7で特定される音声制御レジスタRGiとの読み書き(R/W)動作が実現される。

#### 【0090】

具体的には、図4(b')のタイムチャートに示す通りであり、音声制御レジスタRGiのレジスタアドレスと、音声制御レジスタRGiへの書込みデータは、各々、パラレル信号線CD0～CD7を通してパラレル伝送される。そして、パラレル伝送された1バイトが、レジスタアドレスであるか、それとも、書込みデータ(ライトデータ)であるかは、動作管理データA0～A1によって特定される。

#### 【0091】

したがって、図4(b)に示す通り、動作管理データ(アドレスデータA0～A1)を、[00][01]と推移させる一方で、データバスの1バイトデータを、[音声制御レジスタRGiのレジスタアドレス][音声制御レジスタRGiへの書込みデータ]と推移させることで、所定の音声コマンドSNDが送信される。なお、SAC番号(13ビット)を送信する場合のように、書込みデータが複数バイト長の場合には、[01]の動作管理データA0～A1を、[00][01][01][01]と繰り返しつつ、複数バイトの書込みデータを送信する。

10

#### 【0092】

このようにして送信された音声コマンドは、通信異常がない限り、その後、実効化される。但し、複数バイト長のデータが互いに整合しないなど、通信異常が認められる場合には、その音声コマンドSNDが実効化させることはない。そして、音声制御レジスタRGnのエラーフラグがセットされるが、このエラーフラグ(ステイタス情報STS)は、アドレスバスの動作管理データA0～A1を、[01]から[10]に推移させることで、演出制御CPU40がRead動作によって受信することができる。

20

#### 【0093】

このように、この実施例では、動作管理データA0～A1を、[00][01]・・[01][10]と推移させる最終サイクルにおいて、複数ビット長のエラー情報(異常時はFFH)を取得することができる。そして、正当にパラレル送信できなかった音声コマンドSNDを再送することで、音声演出を適切に進行させることができる。したがって、本実施例の構成によれば、音声演出が突然、途絶えるような不自然さを確実に解消することができる。

#### 【0094】

30

なお、図4(b)の構成では、演出制御CPU40は、エラー情報を含んだステイタス情報STSを、音声プロセッサ42からパラレル受信しているが、何ら、この構成に限定されるものではない。すなわち、音声プロセッサ42が通信エラーを認識すると、演出制御CPU40に割込み信号を出力する構成を探るのも好適であり、この場合には、演出制御CPU40の割込み処理プログラムにおいて、通信エラーが生じた音声コマンドを再送すればよい。このような構成を探れば、殆どの場合に無駄な処理となる、エラーフラグ(ステイタス情報STS)の取得処理、すなわち、動作管理データA0～A1を[10]に遷移させる処理を省略することができる。

#### 【0095】

40

図3及び図4(a)に示す通り、本実施例では、デジタルアンプ46の出力によって、遊技機上部の左右スピーカと、遊技機下部のスピーカとを駆動している。そのため、音声プロセッサ42は、3チャネルの音声信号を生成する必要があり、これをパラレル伝送すると、音声プロセッサ42とデジタルアンプ46との配線が複雑化する。

#### 【0096】

そこで、本実施例では、音質の劣化を防止すると共に、配線の複雑化を回避するため、音声プロセッサ42とデジタルアンプ46との間は、4本の信号線で接続されており、具体的には、転送クロック信号SCLKと、チャネル制御信号LRCLKと、2ビット長のシリアル信号SD1, SD2との合計4ビットの信号線に抑制されている。

#### 【0097】

ここで、SD1は、遊技機上部に配置された左右スピーカのステレオ信号R, Lを特定

50

する P C M データについてのシリアル信号であり、 S D 2 は、遊技機下部に配置された重低音スピーカのモノラル信号を特定する P C M データについてのシリアル信号である。そして、音声プロセッサ 4 2 は、チャネル制御信号 L R C L K を L レベルに維持した状態で、左チャネルの音声信号 L を伝送し、チャネル制御信号 L R C L K を H レベルに維持した状態で、右チャネルの音声信号 R を伝送する。重低音スピーカは、本実施例では 1 個であるので、モノラル音声信号が伝送されているが、ステレオ音声信号として伝送できるのは勿論である。

#### 【 0 0 9 8 】

何れにしても本実施例では、4 種類の音声信号を 4 本のケーブルで伝送可能であるので、最小のケーブル本数によってノイズによる音声劣化のない信号伝達が可能となる。すなわち、シリアル伝送であるのでパラレル伝送より圧倒的にケーブル本数が少ない。

10

#### 【 0 0 9 9 】

このようなシリアル信号 S D 1 , S D 2 は、クロック信号 S C L K の立上りエッジに同期して、デジタルアンプ 4 6 に取得される。そして、デジタルアンプ 4 6 内部で、所定ビット長毎にパラレル変換され、 D A 変換後に D 級増幅されて各スピーカに供給されている。

#### 【 0 1 0 0 】

図 4 ( a ) に関して説明を続けると、演出制御基板 2 2 には、ワンチップマイコン 4 0 のシリアル入出力ポート S I O のシリアル出力ポート S o i から出力されるシリアルデータ S D A T A i とクロック信号 C K i を転送するバッファ回路 4 7 ~ 4 9 が設けられている ( i = 0 ~ 2 ) 。

20

#### 【 0 1 0 1 】

出力バッファ 4 7 は、シリアル出力ポート S o 0 が出力するランプ駆動信号 S D A T A 0 とクロック信号 C K 0 を、ランプ駆動基板 3 6 のシフトレジスタ回路 ( ドライバ I C ) に転送している。また、出力バッファ 4 8 は、シリアル出力ポート S o 1 が出力するランプ駆動信号 S D A T A 1 とクロック信号 C K 1 を、ランプ駆動基板 2 9 のドライバ I C に転送している。なお、各ランプ駆動基板 2 9 , 3 6 に搭載されたドライバ I C が、 C H 0 と C H 1 のランプ群を点灯駆動することは先に説明した通りである。

#### 【 0 1 0 2 】

一方、バッファ回路 4 9 は、入出力バッファとして機能しており、シリアル出力ポート S o 2 が出力するシリアル信号 S D A T A 2 を、クロック信号 C K 2 と共にモータランプ駆動基板 3 0 に転送している。また、一群の演出モータ M 1 ~ M n の原点位置を示す原点センサ信号 ( シリアル信号 ) を、クロック信号 C K 3 に同期してワンチップマイコン 4 0 のシリアル入力ポート S i に転送している。

30

#### 【 0 1 0 3 】

本実施例の場合、バッファ回路 4 9 が転送するシリアル信号 S D A T A 2 は、ランプ群 C H 2 を点灯させるためのランプ駆動信号 ( シリアル信号 ) と、演出モータ M 1 ~ M n を回転させるためのモータ駆動信号 ( シリアル信号 ) とが連続するよう構成されている。そして、モータランプ駆動基板 3 0 では、これら一連のシリアル信号を 1 6 ビット長毎に分断すると共に、各 1 6 ビット長をパラレル信号に変換して、ランプ演出と可動予告演出を実行している。具体的には、制御コマンド C M D に対応して抽選決定された演出動作として、一連のランプ演出を実行すると共に、モータ駆動信号を受信した場合には、演出モータ M 1 ~ M n を回転させて適宜な可動予告演出を実行している。

40

#### 【 0 1 0 4 】

次に、図 4 ( a ) の左側に示す通り、本実施例では、演出制御 C P U 4 0 のデータバスとアドレスバスは、液晶インタフェイス基板 2 8 にも及んでいる。説明の便宜上、図 4 ( a ) の左側に、この関係を図示しているが、時計回路 R T C は、演出制御 C P U 4 0 のアドレスバスの下位 4 ビットと、データバスの下位 4 ビットとで C P U に接続されており、任意にアクセス可能に構成されている。また、遊技実績情報を記憶するメモリ素子 S R A M は、演出制御 C P U 4 0 のアドレスバスの 1 6 ビットと、データバスの下位 1 6 ビット

50

とで、演出制御 C P U 4 0 のランダムアクセスを可能にしている。

#### 【 0 1 0 5 】

時計回路 R T C は、現在年月日や現在時刻を計時する時計 I C (リアルタイムクロック) であり、メモリ素子 S R A M と共に、演出制御基板 2 2 から受ける電源電圧で充電される二次電池 B T で永続的に動作している。すなわち、遊技機に電源が投入されている状態で、二次電池 B T (図 5 ) が充電される一方、遊技機の電源が遮断された後は、充電状態の二次電池 B T に基づいて、時計回路 R T C の計時動作が継続され、演出データも永続的に記憶保持される (バックアップ動作) 。

#### 【 0 1 0 6 】

図 5 に示す通り、実施例の時計回路 R T C は、4 ビットのデータバスと、4 ビットのデータバスと、R e a d / W r i t e 動作用のコントロールバス R D + W R とを通して、演出制御 C P U 4 0 に接続されている。そして、演出制御 C P U 4 0 は、遊技動作に関する重要な遊技情報を、時計回路 R T C から取得した年月日情報及び曜日情報や時刻情報を付加して、メモリ素子 S R A M に記憶するようにしている。10

#### 【 0 1 0 7 】

この時計回路 R T C は、C S 1 と C S 0 バーの2種類のチップセレクト端子を有しており、各端子への入力電圧が正常レベルであることを条件に、演出制御 C P U 4 0 からのアクセスを許可するようになっている。ここで、C S 0 バー端子は、アドレスデコーダの出力を受ける通常のチップセレクト端子である。一方、C S 1 端子は、電源異常検出部 E R の出力 (電圧降下信号) V o を受けており、C S 1 端子が異常レベルの出力 V o を受けた場合には、時計回路 R T C の異常検出フラグ F o s が自動的にセットされるようになっている。20

#### 【 0 1 0 8 】

本実施例の場合、この異常検出フラグ F o s は、他の異常検出フラグ T E M P と共に、電源投入時に演出制御 C P U 4 0 によって判定され、仮に、異常検出フラグ F o s がセット状態であれば、その時の年月日及び時刻が報知されるようになっている。そのため、もし、時計機能の異常が認められた場合には、これに素早く対処することができる。

#### 【 0 1 0 9 】

なお、電源遮断時に二次電池 B T の電圧が降下しても、二次電池 B T の電圧レベルは、電源復帰によって素早く回復して C S 1 端子が正常レベルに戻るので、演出制御 C P U 4 0 からのアクセスが許可されることになる。したがって、異常検出フラグ F o s の判定処理を設ける本実施例の構成を探らない場合には、時計回路 R T C の異常を永続的に検出できないおそれがある。30

#### 【 0 1 1 0 】

また、実施例の時計回路 R T C は、一週間に一回、例えば、毎金曜日の 2 1 時 5 0 分に、割込み信号 I R Q を出力するよう構成されおり、割込み信号 I R Q を受けた演出制御 C P U 4 0 では、それまでにメモリ素子 S R A M に蓄積した遊技情報や異常情報について、適宜に集計するようにしている。

#### 【 0 1 1 1 】

集計する遊技情報は、大当たり状態に関する履歴情報をまとめたものであり、例えば、(1) 大当たり状態となるまでに要した図柄始動口への入賞回数、(2) 大当たり状態の図柄や、確変か否かの大当たり状態の集計値や統計値、(3) 大当たり状態に至った予告演出やリーチ演出の種類、(4) 連チャン回数、(5) 連チャンによる払出球数の時間的な増加推移、などが含まれる。そして、これらの集計情報や統計情報は、遊技者の求めに応じて適宜に報知される。遊技者の指示は、例えば、デモ演出中の操作ボタン 1 1 の押圧で特定され、報知内容は表示装置 D S 1 に表示される。40

#### 【 0 1 1 2 】

一方、集計する異常情報には、例えば、(1) ドア開放回数、(2) 違法行為を検出する検知センサの検出種別や検出回数や検出時刻、(3) 閉塞状態の図柄始動口 1 5 や大入賞口 1 6 を針金などで無理に開放しようとする行為の検出回数や検出頻度や検出時刻など

が含まれる。そして、これらの集計情報は、係員による特別な操作に対応して、表示装置 D S 1 に表示される。

#### 【 0 1 1 3 】

図 5 ( a ) に示す通り、実施例の時計回路 R T C は、B a n k 0 ~ B a n k 2 の 3 つの内部レジスタテーブルを内蔵して構成されている。但し、B a n k 2 のレジスタテーブルは、時刻設定や年月日設定に関するものであるので、図 5 ( b ) と図 5 ( c ) に、B a n k 0 と B a n k 1 のレジスタテーブルだけ記載している。何れにしても、各レジスタテーブルは、4 バイト × 16 個のレジスタで構成されおり、内部回路が計時した現在年月日と現在時刻は、B a n k 0 のレジスタテーブル ( 図 5 ( b ) ) に書込まれるよう構成されている。

10

#### 【 0 1 1 4 】

図 5 ( b ) に示すように、B a n k 0 のレジスタテーブルにおいて、1 番レジスタのビット 3 は、異常検出フラグ F o s であり、14 番レジスタのビット 2 は、内蔵温度センサが異常温度を検出したことを示す温度異常フラグ T E M P である。そして、本実施例では、演出制御部 22 の C P U リセット時に、異常検出フラグ F o s の値を判定することで、異常な計時動作の継続を防止している。また、時計回路 R T C を演出制御 C P U 4 0 に近接配置すると共に、適宜な時間間隔で、温度異常フラグ T E M P の値を繰り返し判定することで、演出制御 C P U 4 0 の温度異常を素早く検出している。

#### 【 0 1 1 5 】

また、B a n k 0 のレジスタテーブルにおいて、15 番レジスタのビット 0 は、レジスタテーブルが更新中であることを示す B u s y フラグである。そして、本実施例では、B u s y フラグが非 B u s y 状態 ( 更新完了 ) であることを条件に、B a n k 0 のレジスタテーブルから、現在年月日と現在時刻を取得している。そのため、本実施例では、更新動作中の中途半端、又は不合理な時計情報を取得するおそれがなく、メモリ素子 S R A M に記憶される時計情報の正当性が担保される。例えば、1 時 5 9 分 5 9 秒から 2 時 0 分 0 秒に更新中の時計情報を取得すると、1 時 0 分 0 秒の時計情報を取得してしまうおそれがある。

20

#### 【 0 1 1 6 】

また、B a n k 1 のレジスタテーブルは、割込み信号 I R Q の発生時刻を設定可能に構成されている。そこで、本実施例では、B a n k 1 の 1 番レジスタのビット 0 に 1 をセットすることで割込み発生を指示し ( Interrupt Enable ) 、B a n k 1 の 0 番レジスタ～8 番レジスタに、金曜の曜日指定と、21 時 30 分 00 秒の時刻情報を設定している。

30

#### 【 0 1 1 7 】

続いて、画像制御部 23 について図 6 ～図 8 を参照しつつ詳細に説明する。先ず、図 6 ( a ) は、画像制御部 23 を構成する複合チップ 5 0 について、関連する回路素子も含めて図示した回路ブロック図である。図示の通り、実施例の複合チップ 5 0 には、内蔵 C P U 回路 5 1 と V D P 回路 5 2 とが内蔵されている。そして、内蔵 C P U 回路 5 1 と V D P 回路 5 2 とは、互いの送受信データを中継する C P U I F 回路 5 6 を通して接続されると共に、V D P 回路 5 2 から内蔵 C P U 回路 5 1 に対して、V ブランク割込み信号 ( V B L A N K ) が供給されるようになっている。

40

#### 【 0 1 1 8 】

V ブランク割り込み信号は、メイン表示装置 D S 1 の垂直同期信号に対応するもので、メイン表示装置 D S 1 の一フレーム分の画像データの出力が完了したタイミングを 1 / 60 秒毎に規定している。この実施例では、3 つの表示回路 7 4 A / 7 4 B / 7 4 C のうち、表示回路 7 4 B は機能せず、表示回路 7 4 C は、表示回路 7 4 A に同期して動作するよう構成されているので、垂直同期信号 ( V ブランク割り込み信号 ) は、表示回路 7 4 A の出力動作が終わったことを意味することになる。

#### 【 0 1 1 9 】

V ブランク割り込みに基づくシーケンス動作については後述するが、C P U I F 回路 5 6 には、図 6 に示す通り、制御プログラムや、必要な制御データを不揮発的に記憶する制

50

御メモリ (PROGRAM\_ROM) 53と、2Mバイト程度の記憶容量を有するワークメモリ (RAM) 57とが接続され、各々、内蔵CPU回路51からアクセス可能に構成されている。

#### 【0120】

内蔵CPU回路51は、汎用のワンチップマイコンと同等の性能を有する回路であり、制御メモリ53の制御プログラムに基づき画像演出を統括的に制御する画像制御CPU63と、プログラムが暴走状態になるとCPUを強制リセットするウォッチドッグタイマ (WDT) 58と、16kバイト程度の記憶容量を有してCPUの作業領域として使用されるRAM59と、CPUを経由しないでデータ転送を実現するDMAC (Direct Memory Access Controller) 60と、複数の入力ポートSi及び出力ポートSoを有するシリアル入出力ポート (SIO) 61と、複数の入力ポートPi及び出力ポートPoを有するパラレル入出力ポート (PIO) 62と、を有して構成されている。 10

#### 【0121】

なお、便宜上、本明細書では、入出力ポートとの表現を使用するが、画像制御部23において、入出力ポートには、独立して動作する入力ポートと出力ポートとが含まれている。この点は、以下に説明する入出力回路64pや入出力回路64sについても同様である。

#### 【0122】

パラレル入出力ポート62は、入出力回路64pを通して外部機器（演出制御基板22）に接続されており、画像制御CPU63は、入力回路64p及びパラレル入力ポートPiを経由して、演出制御部22が出力する制御コマンドCMD' と割込み信号STB' を受信するようになっている。一方、この実施例では、シリアル入出力ポート61と、DMAC60については、これらを使用していない。 20

#### 【0123】

次に、VDP回路52について説明すると、VDP回路52には、画像演出を構成する静止画や動画の構成要素となる圧縮データを記憶するGROM55と、4Gb程度の記憶容量を有する外付けDRAM (Dynamic Random Access Memory) 54と、メイン表示装置DS1と、サブ表示装置DS2とが接続されている。

#### 【0124】

本実施例の場合、DRAM54は、画像制御CPU63から直接アクセスできるよう構成されているので、画像制御CPU63は、表示装置DS1, DS2の各フレームを特定するディスプレイリストDLを、直接、DRAM54に書き込んでいる。なお、図8のタイミングT1' の右向き矢印は、画像制御CPU63によるディスプレイリストDLの書き込み動作の完了タイミングを示している。 30

#### 【0125】

GROM55は、62Gb程度の記憶容量のNAND型フラッシュメモリで構成されたフラッシュSSD (solid state drive) で構成されており、シリアル伝送によって必要な圧縮データを取得するよう構成されている。そのため、パラレル伝送において不可避的に生じるスキューリング (ビットデータ毎の伝送速度の差) の問題が解消され、極限的な高速伝送動作が可能となる。 40

#### 【0126】

なお、NAND型のフラッシュメモリは、ハードディスクより機械的に安定であり、且つ高速アクセスが可能である一方で、シーケンシャルアクセスメモリであるため、DRAMやSRAM (Static Random Access Memory) に比較するとアクセス速度に劣り、アクセス速度は、内蔵VRAM71 > 外付けDRAM54 > GROM55の順番に遅くなる。但し、本実施例では、一群の圧縮データ (CGデータ) を、描画動作に先行して外付けDRAM54に読み出しておくプリロード動作を実行するので、描画動作時におけるCGデータの円滑なランダムアクセスを実現することができる。

#### 【0127】

図6(a)に示す通り、VDP回路52は、詳細には、VDPの動作を規定する各種の 50

動作パラメータが設定されるレジスタ群70と、48Mバイト程度のV R A M (Video RAM) 71と、チップ内部の各部間のデータ送受信及びチップ外部とのデータ送受信を制御するデータ転送回路72と、プリロード動作を実行するプリローダ73と、外付けD R A M 54のフレームバッファF Bに生成された画像データを読み出して、適宜な画像処理を並列的に実行する複数系統の表示回路74と、C G R O M 55から読み出した圧縮データをデコードするグラフィックスデコーダ75と、デコード後の静止画データや動画データを適宜に組み合わせて各表示装置D S 1, D S 2の一フレーム分の画像データを生成する描画回路76と、描画回路76の動作の一部として、適宜な座標変換によって立体画像を生成するジオメトリエンジン77と、シリアルデータ送受信可能なS M C部78と、表示回路74の出力を適宜に選択出力する出力選択部79と、出力選択部79が出力する画像データをL V D S信号に変換する2系統のL V D S部80a, 80bと、出力選択部79が出力する画像データをデジタルR G B信号のままパラレル出力するデジタルR G B部80cと、C P U I F回路56とのデータ送受信を中継するC P U I F部81と、C G R O M 55からのデータ受信を中継するC GバスI F部82と、外付けD R A M 54とのデータ送受信を中継するD R A M I F部83と、V R A M 71とのデータ送受信を中継するV R A M I F部84と、を有して構成されている。10

#### 【0128】

そして、3D表示を実現するため、左眼用の一フレーム画像を生成する左眼バッファL B U Fや、右眼用の一フレーム画像を生成する右眼バッファR B U Fを使用するので、本実施例では、便宜上、フレームバッファF Bも含め、必要な作業領域を、全て、外付けD R A M 54に確保している。但し、アクセス速度は、外付けD R A M 54よりV R A M 71の方が速いので、図8に示す静止画デコード領域や動画デコード領域も含め、左眼バッファL B U F、右眼バッファR B U F、及び、フレームバッファF Bについては、V R A M 71に確保する方がプログラム処理速度の点で有利である。したがって、処理速度とメモリ容量との関係で、外付けD R A M 54と、V R A M 71とを適宜に使い分けるのが好ましい。20

#### 【0129】

次に、図6(b)には、C P U I F部81、C GバスI F部82、及び、D R A M I F部83と、レジスタ群70、C G R O M 55、及びD R A M 54との関係が図示され、特に、レジスタ群70については、その一部が具体的に記載されている。図示の通り、C G R O M 55とC GバスI F部82は、シリアル回線で接続されており、アドレス情報T Xの送信に対応して、C G R O M 55がシーケンシャルアクセスされ、一群のC Gデータ(圧縮データ)R Xが、順次読み出されるようになっている。30

#### 【0130】

図6(a)に示すデータ転送回路72は、V D P回路内部のリソース(記憶媒体)と外部記憶媒体を、転送元ポート又は転送先ポートとして、これらの間でデータ転送動作を実行する回路である。転送元ポートには、C P Uバス、C Gバス、外部D R A Mバスに接続された記憶媒体(リソース)が含まれる。同様に、転送先ポートには、C P Uバス、C Gバス、外部D R A Mバスに接続された記憶媒体が含まれる。また、データ転送回路72は、一群の描画コマンドによって一フレーム分の表示画像を特定するディスプレイリストD Lを、描画回路76や、プリローダ73に送信する動作も担当している。40

#### 【0131】

一方、プリローダ73は、データ転送回路72によって送信されたディスプレイリストD Lを解釈して、その中で参照しているC G R O M 55上のC Gデータを、予め指定されているD R A M 54のプリロード領域T E M Pに転送する回路である。また、このとき、プリローダ73は、C Gデータの参照先を、転送後のアドレスに書換えた修正ディスプレイリストD L'を出力する。図8のタイミングT 1"の下向き矢印は、その動作を示しており、書換えた修正ディスプレイリストD L'は、データ転送回路72によって描画回路76に送信され、描画動作が実効化される。

#### 【0132】

50

本実施例では、プリローダレジスタ（図6（b）参照）への設定値に基づき、外付けDRAM54に、十分な記憶領域のプリロード領域TEMPを設定している。また、プリロード領域への転送履歴が、最大512個まで記憶可能に構成されている。そのため、512区画されたプリロード領域TEMPの記憶領域を使い切らない限り、プリロードされた圧縮データは、その後の処理において再利用することができる（キャッシング機能）。

#### 【0133】

そのため、プリロード処理を使用する本実施例では、必要な圧縮データが、プリロード領域TEMPに存在しない場合に限り、CGROM55をアクセスすることになる。なお、プリロード領域TEMPに十分な記憶領域が確保されているので、複数フレーム分のCGデータを一気にプリロードしても何も問題が生じない。

10

#### 【0134】

描画回路76は、プリローダ73によって書き換えられた修正ディスプレイリストDL'の描画コマンドを順番に解析して、グラフィックスデコーダ75や、ジオメトリエンジン77などと協働して、外付けDRAM54に確保されたフレームバッファFBに、表示装置DS1, DS2の一フレーム分の画像を完成させる回路である。

#### 【0135】

すなわち、描画回路76は、修正ディスプレイリストDL'の描画コマンドを解析するDisplaylist Analyzer（以下、DLアナライザという）と、頂点の座標変換や照明演算を実行するGeometry Pipelineと、トライアングル描画時のソース（source）アドレスとデスティネーション（destination）アドレスを生成するTriangle Rasterizerと、テクスチャをサンプリングし、バイリニアフィルタリングを実行するTexture Samplerと、画素間演算用のフレームバッファとZバッファを取得するFramebuffer Samplerと、ブレンダなどの処理を施して、フレームバッファFBに書き込む画素データを生成するピクセルジェネレータ（Pixel Generator）などを含んで構成されている。

20

#### 【0136】

ここで、ディスプレイリストDL/ DL'は、描画する順番に記載された一群の描画コマンドで構成されており、メイン表示装置DS1とサブ表示装置DS2について、一フレームのどの位置に、どのような画像（描画素材）を描画するかを規定するコマンドも含まれ、描画すべき画像のCGROMなどの記憶位置（ソースアドレス）も特定されている。

#### 【0137】

30

そして、描画回路76のDLアナライザは、このようなディスプレイリストDL/ DL'を解釈して、他のGeometry Pipeline、Triangle Rasterizer、Texture Sampler、Framebuffer Sampler、ピクセルジェネレータと協働して、外付けDRAM54に確保されたフレームバッファFBa, FBcに、表示装置DS1, DS2の各一フレーム分の画像データを完成させている。

#### 【0138】

後述するように、3D又は2D表示されるメイン表示装置DS1の一フレームは、左眼バッファLBUFや右眼バッファRBUFに、静止画や動画を構成する各種の描画素材を配置した後、これら各バッファLBUF, RBUFの画像データを、フレームバッファFBaで複合させることで完成される。一方、2D表示されるサブ表示装置の一フレームは、フレームバッファFBcに、簡易動画を含んだ各種の描画素材を配置することで完成される。

40

#### 【0139】

各表示装置DS1, DS2のフレームバッファFBa, FBcは、何れも、描画処理領域と表示処理領域に機能的に区分されたダブルバッファであり、2つの領域（描画処理領域0と表示処理領域1）を、交互に用途を切り換えて使用している。すなわち、描画回路76が、2つの領域の何れか一方の領域に、画像データが書込んでいるとき、表示回路74は、他方の領域の画像データを読み出して出力している。

#### 【0140】

本実施例の場合、メイン表示装置DS1は、1280×1024ピクセルを有し、サブ

50

表示装置 D S 2 は、 $800 \times 600$  ピクセルを有して構成され、各ピクセル P ( i , j ) は、 R B G 三色が各々 8 b i t で表現されることで、 256 諧調を実現している。そこで、サブ表示装置 D S 2 用のフレームバッファ F B c は、描画処理領域と表示処理領域とも、サブ表示装置 D S 2 の表示画面に対応して、 $800 \times 600$  ピクセルの画像データを格納できるよう構成されている。

#### 【 0 1 4 1 】

一方、メイン表示装置 D S 1 用のフレームバッファ F B a や、その補助バッファたる左眼バッファ L B U F 及び右眼バッファ R B U F は、メイン表示装置 D S 1 の表示画面 ( $1280 \times 1024$  ピクセル) と同一ではなく、それより小さい  $1024 \times 1024$  ピクセルの画像データを格納できるよう構成されている（図 7、図 11(5) 参照）。これは、本実施例では、フレームバッファ F B a に生成された画像データを、表示回路 74 A において拡大して、 $1280 \times 1024$  ピクセルの画像データにするためである。10

#### 【 0 1 4 2 】

これらフレームバッファ F B a , F B c や補助バッファ L B U F , R B U F について更に説明すると、全てのピクセル P ( i , j ) は、フレームバッファ F B a , F B c や補助バッファ L B U F , R B U F において、 R G B 各色を特定する合計 3 バイトと、 値を特定する チャンネルの 1 バイトとで、合計 4 バイトで特定されている。

#### 【 0 1 4 3 】

ここで、 値とは、各ピクセル位置に設定された透過度情報であって、上書きする新規画像 ( source ) と、上書きされる元画像 ( destination ) との透明度を規定する ブレンド処理を特定する値である。本実施例の場合、 値は、 1 バイト構成であるので、 値の上限値が 255 となる。20

#### 【 0 1 4 4 】

また、本実施例では、表示装置 D S 1 , D S 2 の一フレームは、最大状態では、 3 種類又はそれ以上の画像（動画と静止画）で構成されている。すなわち、表示装置 D S 1 , D S 2 では、最大状態では、一又は複数の動画が再生される一方で、これに重ねて、時間的に変化する静止画が、背景画と共に表示されるよう構成されている。

#### 【 0 1 4 5 】

静止画の基本形状は、スプライト画像として予め C G R O M 5 5 に記憶されており、この基本形状を、適宜に拡大 / 縮小 / 回転 / 変形させると共に、配置位置を変更させることで、時間的な変化を実現している。なお、背景画は、完成状態で C G R O M 5 5 に記憶されている。30

#### 【 0 1 4 6 】

一方、動画は、本実施例の場合には、一般動画と簡易動画とに区分されている。本実施例の簡易動画は、表示画面の縦横ピクセル数より、横方向又は縦方向に十分に長い一枚の長尺フレームで構成されており、この長尺フレームの使用領域、つまり、表示装置に表示される使用範囲を、時間的に変化させることで、滑らかなムービー動作を実現している。

#### 【 0 1 4 7 】

この意味において、簡易動画は、実際には、長尺フレームの静止画に他ならないが、本実施例では、左右方向に円滑に往復移動する背景画像として、簡易動画を活用している。なお、本実施例では、メイン表示装置 D S 1 で 3 D 表示を実現するので、簡易動画は、便宜上、サブ表示装置 D S 2 だけで再生され、メイン表示装置 D S 1 で簡易動画が再生されることはない。40

#### 【 0 1 4 8 】

以上の簡易動画を除いた一般動画は、時間的に滑らかに変化するいわゆるムービーであって、複数枚のフレームが、 M P E G 符号化方式などの動画圧縮手法で圧縮されて C G R O M 5 5 に記憶されている。より詳細に説明すると、本実施例の一般動画は、 I フレームと P フレームとで構成された I P ストリーム動画を意味する。

#### 【 0 1 4 9 】

ここで、 I P ストリーム動画を構成する P フレームは、過去フレームから予測したデー50

タとの差分をエンコードする P ピクチャ (Predictive Picture) で構成されたフレームを意味し、圧縮率が高いものの、順次再生が必須となる。一方、I フレームは、他のフレームに依存することなく、単独でエンコード可能な I ピクチャ (Intra Picture) で構成されたフレームを意味する。なお、このように構成された一般動画は、メイン表示装置 D S 1 だけでなく、必要に応じて、サブ表示装置 D S 2 でも再生される。

#### 【 0 1 5 0 】

上記した静止画と動画に対応して、グラフィックスデコーダ 7 5 は、静止画デコーダと動画デコーダに区分され、所定の圧縮アルゴリズムでエンコード（圧縮）された静止画と動画を、各々に対応する伸張アルゴリズムでデコード（伸張）している。例えば、静止画は、1 枚の静止画を構成する画像データ毎に所定のアルゴリズムで圧縮され、I P ストリーム動画の P フレームは、一連の動画を実現する複数枚の静止画データが、フレーム間のデータ差分値などに基づいて圧縮されている。簡易動画は、長尺フレームの静止画で構成されているので、静止画デコーダでデコードされる。

#### 【 0 1 5 1 】

ところで、メイン表示装置 D S 1 で再生される静止画や一般動画は、 $1280 \times 1024$  ピクセルの表示画面に表示されるにも拘らず、C G R O M 5 5において、各々、原則として、横 $1024 \times$ 縦 $820$ ピクセルを超えないよう抑制されている。これは、メイン表示装置 D S 1 には、左眼用画像と右眼用画像が必要であることに対応して、可能な限り、C G データのデータ量を抑制するためであり、単純計算では、C G データのデータ量は $64\%$  ( $820 / 1280$ ) に抑制される。なお、例外的に $1024 \times 820$ ピクセルを超える画像は、後述するクリッピング処理の対象となる。

#### 【 0 1 5 2 】

上記の通り、縦横に縮小化されて C G R O M 5 5 に圧縮記憶されているメイン表示装置 D S 1 用の C G データ ( $1024 \times 820$  ピクセル分) は、グラフィックスデコーダ 7 5 によるデコード処理の後、描画回路 7 6 のピクセルジェネレータで Y (縦) 方向に拡大されて、 $1024 \times 1024$  ピクセルの画像データとなる (図 1 1 (2)、図 1 1 (4) 参照)。そして、その後、表示回路 7 4 Aにおいて、X (横) 方向に拡大されることで、メイン表示装置 D S 1 の $1280 \times 1024$  ピクセル分の画像データとなる。

#### 【 0 1 5 3 】

一方、サブ表示装置 D S 2 で再生される静止画や一般動画の C G データは、原則として、 $800 \times 600$  ピクセルを超えないよう構成され、V D P 回路 5 2 の内部回路で拡大されることなく使用される。但し、簡易動画については、先に説明した通り、 $800 \times 600$  ピクセルを大きく超える一枚の長尺フレームとして C G R O M 5 5 に圧縮記憶されている。そして、これら $800 \times 600$  ピクセルを超える画像は、後述するクリッピング処理の対象となる。

#### 【 0 1 5 4 】

このように、C G R O M 5 5 には、表示装置 D S 1 , D S 2 のピクセル数に一致しない各種寸法の C G データ (描画素材) が、動画又は静止画として格納されており、これらを適宜に組み合わせて、各表示装置の一フレームを完成させる必要がある。特に、メイン表示装置 D S 1 では 3 D 表示が必要となるので、左眼画像と右眼画像の複合処理も必要となる。また、サブ表示装置 D S 2 では、簡易動画を適切に再生する必要もある。

#### 【 0 1 5 5 】

そこで、本実施例では、外付け D R A M 5 4 に、フレームバッファ F B a , F B c とは別に、描画処理用の作業領域を適宜に確保している。具体的には、図 8 に示す通りであり、左眼画像を生成する作業領域である左眼バッファ L B U F と、右眼画像を生成する作業領域である右眼バッファ R B U F とが、各々、外付け D R A M 5 4 に確保されている。

#### 【 0 1 5 6 】

左眼バッファ L B U F と、右眼バッファ R B U F は、 $1024 \times 1024$  ピクセル分の画像データを格納できるフレームバッファ F B a と同一の記憶容量を有しており、メイン表示装置 D S 1 用の描画素材を配置すべき描画領域となっている。そして、これらの描画

10

20

30

40

50

領域（L B U F , R B U F ）の周りには、各描画領域を包含する十分に大きい仮想描画空間 V I T が、各々、仮想的に配置されている。また、フレームバッファ F B a , F B c は、表示装置 D S 1 , D S 2 用の描画素材を配置すべき描画領域であり、これらの描画領域（F B a , F B c ）の周りにも、仮想描画空間 V I T が仮想的に配置されている。

#### 【 0 1 5 7 】

仮想描画空間 V I T は、各種の描画素材（各種寸法の C G データ）を、任意位置に任意姿勢で貼付けて、表示装置 D S 1 , D S 2 の一フレームを完成させるための描画演算用の仮想空間である。そして、描画コマンドによって仮想描画空間 V I T に貼付けた描画素材のうち、描画領域からはみ出した部分は、クリッピング処理で自動的に排除されるようになっている。10

#### 【 0 1 5 8 】

例えば、図 1 4 は、サブ表示装置 D S 2 用の描画領域（フレームバッファ F B c ）と、仮想描画空間 V I T との包含関係を図示したものである。図示の通り、横 ± X と縦 ± Y で特定される矩形状の仮想描画空間 V I T の中央に、横 ± H ( 8 0 0 ピクセル分 ) と、縦 ± V ( 6 0 0 ピクセル分 ) で特定される矩形状のフレームバッファ F B c が、描画領域として存在している。

#### 【 0 1 5 9 】

そして、ディスプレイコマンド D L には、仮想描画空間 V I T の任意の座標 ( i , j ) に、任意の描画素材を貼付ける描画コマンドを列記するようになっている。また、例えば、図 1 4 に示すように、描画素材が矩形状の場合には、仮想描画空間 V I T の座標 ( i , j ) において、左上端点と右下端点を指定すれば良いよう構成されている。先に説明した通り、仮想描画空間 V I T に貼付けられた画像（描画素材）のうち、真の描画領域たる 8 0 0 × 6 0 0 ピクセル分の画像データだけがフレームバッファ F B c に配置される。20

#### 【 0 1 6 0 】

そこで、本実施例では、このクリッピング動作を有効活用して、サブ表示装置 D S 2 で再生される簡易動画を、描画領域 F B c より十分に幅広の長尺フレームで構成し、仮想描画空間 V I T における貼付け位置を適宜に移動させることで簡易的な動画再生（背景画像の往復移動）を実現している。すなわち、多数フレームで構成される動画に代えて、一枚の長尺フレームを適宜に区分再生することで C G R O M のメモリ容量の抑制を図っており、この場合については、図 1 3 に関して更に後述する。30

#### 【 0 1 6 1 】

また、本実施例では、仮想描画空間に矩形状の描画素材を貼付ける場合に、描画素材の縦横寸法と、貼付け領域の縦横寸法を、必ずしも一致させる必要はない。そして、描画素材と、貼付け領域の縦横寸法が一致しない描画コマンドを指定した場合には、貼付け領域の縦横寸法が優先されるようになっている。

#### 【 0 1 6 2 】

例えば、描画コマンドで指定される貼付け領域が、描画素材より広い場合には、描画回路 7 6 のピクセルジェネレータによって描画素材が自動的に拡大され、逆に、指定される貼付け領域が狭い場合は、ピクセルジェネレータによって、描画素材が自動的に縮小されるようになっている。40

#### 【 0 1 6 3 】

そこで、本実施例では、貼付け領域より小さい左眼画像や右眼画像を、仮想描画空間の貼付け領域（L B U F , R B U F ）に配置する場合に、自動拡大動作を活用している。具体的には、先に説明した通りであり、1 0 2 4 × 8 2 0 ピクセル分のメイン表示装置用の画像データを、ピクセルジェネレータによる自動拡大動作に基づいて、1 0 2 4 × 1 0 2 4 ピクセル分の画像データに拡大している。

#### 【 0 1 6 4 】

また、本実施例では、矩形状の描画素材を、左 9 0 ° 回転させて仮想描画空間に貼付けることもできるよう構成されている。例えば、横 W × 縦 D の描画素材を貼付ける場合に、描画コマンドで貼付け領域の左上端点を ( a 1 , b 1 ) と指定し、右下端点を ( a 1 + W

, b<sub>1</sub> + D)に設定すれば、同一姿勢で貼付けられるが、左上端点を(a<sub>1</sub>, b<sub>1</sub>)、右下端点を(a<sub>1</sub> + D, b<sub>1</sub> + W)に設定すれば、左90°回転した状態で仮想描画空間に貼付けられる。

#### 【0165】

以上、描画回路76や、ディスプレイリストDLの描画コマンドについて詳細に説明したので、次に、表示回路74について説明する。表示回路74は、フレームバッファFBの画像データを読み出して、最終的な画像処理を施した上で出力する回路である。図7に示す通り、表示回路74での画像処理には、スケーラが機能してフレーム画像を拡大／縮小するスケーリング処理と、微妙なカラー補正処理と、画像全体の量子化誤差が最小化するディザリング処理と、が含まれている。

10

#### 【0166】

本実施例では、上記の動作を並列的に実行する複数の表示回路74A/74Cが設けられており、各表示回路74A/74Cは、各々に対応するフレームバッファFBa/FBcの画像データを読み出して、上記の最終画像処理を実行している。

#### 【0167】

先に説明した通り、表示回路74Aにおけるスケーリング処理を経ることで、フレームバッファFBaに生成された1024×1024ピクセル分の画像データが、1280×1024ピクセル分の画像データとなる。なお、図8のタイミングT1+2の矢印は、表示回路74A/74Cの読み出し動作を示している。

20

#### 【0168】

そして、表示回路74A/74Cでの画像処理を経たでデジタルRGBデータ(1ピクセルで合計24ビット)が、水平同期信号や垂直同期信号と共に、出力選択回路79に向けて出力される。なお、図6や図7に示す通り、VDP回路52には、並列的に動作する三系統の表示回路74A/75B/74Cが設けられているが、本実施例では、表示回路74Bを使用していない。

30

#### 【0169】

出力選択部79は、表示回路74Aの出力信号を、LVDS部80aとLVDS部80bに伝送し、表示回路74Cの出力信号を、デジタルRGB部80cに出力している。そして、LVDS部80aとLVDS部80bは、画像データ(合計24ビットのデジタルRGBデータ)をLVDS信号に変換して、クロック信号を传送する一対を加えた全五対の差動信号LVDS\_1,LVDS\_2を、デュアルリンク接続でメイン表示装置DS1に传送している。同様に、デジタルRGB部80cは、同期信号などを付加したRGBパラレル信号RG\_B\_Pを、サブ表示装置DS2に传送している。

30

#### 【0170】

次に、SMC部78(Serial Management Controller)は、LEDコントローラとMotorコントローラとを内蔵した複合コントローラである。そして、外部基板に搭載したLED/Motorドライバ(シフトレジスタを内蔵するドライバI<sub>C</sub>)に対して、クロック信号に同期してLED駆動信号やモータ駆動信号を出力する一方、適宜なタイミングで、ラッチパルスを出力可能に構成されている。

40

#### 【0171】

上記したVDP回路52の内部回路及びその動作に関し、内部回路が実行すべき動作内容は、画像制御CPU63が、レジスタ群70に設定する動作パラメータ(設定値)で規定され、VDP回路52の実行状態は、レジスタ群70の動作ステータス値をREADすることで特定できるようになっている。

#### 【0172】

レジスタ群70は、画像制御CPU63のメモリマップ上、1Mバイト程度のメモリ空間(0～FFF\_F\_FH)にマッピングされた多数のレジスタを意味し、画像制御CPU63は、CPUIF部81を経由して動作パラメータのWRITE(設定)動作と、動作ステータス値のREAD動作を実行するようになっている(図6(b)参照)。

50

#### 【0173】

レジスタ群 70 には、割り込み動作などシステム動作に関する初期設定値が書込まれる「システム制御レジスタ」と、画像制御 C P U 6 3 と V D P 回路 5 2 の内部回路との間のデータ転送回路 7 2 によるデータ転送処理に関する設定値などが書込まれる「データ転送レジスタ」と、グラフィックスデコーダ 7 5 のエラー発生などを含む実行状況を特定可能な「G D E C レジスタ」と、描画コマンドや描画回路 7 6 に関する設定値が書込まれる「描画レジスタ」と、プリローダ 7 3 の動作に関する設定値が書込まれる「プリローダレジスタ」と、三区分された表示回路 7 4 A / B / C の各動作に関する設定値が書込まれる「表示レジスタ」と、L E D コントローラ ( S M C 部 7 8 ) に関する設定値が書込まれる「L E D 制御レジスタ」と、M o t o r コントローラ ( S M C 部 7 8 ) に関する設定値が書込まれる「モータ制御レジスタ」とが含まれており、これらの制御レジスタは、各々複数バイト長で構成されている。10

#### 【 0 1 7 4 】

より詳細には、「プリローダレジスタ」には、(1) プリロード領域 T E M P を D R A M 5 4 に設定するか、V R A M 7 1 に設定するかの設定、(2) プリロード領域 T E M P の先頭アドレス、(3) プリロード領域 T E M P を、何フレーム分使用するかの設定、(4) 一フレーム当たりのデータサイズなどが設定される。

#### 【 0 1 7 5 】

また、「データ転送レジスタ」には、データ転送元やデータ転送先が設定され、「表示レジスタ」には、表示回路 7 4 A / C に対応して、フレームバッファ F B a / F B c の開始位置及びバッファサイズや、各フレームバッファ F B a / F B c において、時間的に切り換わる描画処理領域と表示処理領域の切換指示 (bank flip) や、スケーラの縦横拡大率などが設定される。また、「描画レジスタ」「プリローダレジスタ」「データ転送レジスタ」には、描画動作、プリロード動作、データ転送動作について、各動作の実行開始が指示される。20

#### 【 0 1 7 6 】

何れにしても、画像制御 C P U 6 3 が、レジスタ群 7 0 の何れかに適宜な設定値を書込むことで、V D P 回路 5 2 の内部動作が実現される。したがって、画像制御 C P U 6 3 は、適宜な時間間隔で更新されるディスプレイリスト D L / D L' と、上記したレジスタ群 7 0 を構成するレジスタへの設定値に基づいて、ディスプレイリスト D L / D L' に基づく画像演出を実現することになる。なお、この実施例では、ランプ演出やモータ演出は、演出制御基板 2 2 の演出制御 C P U 4 0 が担当するので、S M C 部 7 8 を使用することはなく、L E D 制御レジスタやモータ制御レジスタに設定値が書込まれることもない。30

#### 【 0 1 7 7 】

図 8 に記載の通り、プリローダ 7 3 を有効活用する本実施例では、外付け D R A M 5 4 には、プリローダ 7 3 が先読みした C G R O M 5 5 の圧縮データを一時記憶するプリロード領域 T E M P や、プリローダ 7 3 が書き換えた修正ディスプレイリスト D L' の格納領域 (ディスプレイリストバッファ D L B ) が確保されている。また、D R A M 5 4 には、グラフィックスデコーダ 7 5 が、プリロード領域 T E M P の圧縮データをデコードしたデコード結果の格納領域として、静止画デコード領域と動画デコード領域とが確保されている。40

#### 【 0 1 7 8 】

先に説明した通り、外付け D R A M 5 4 には、表示装置 D S 1 , D S 2 のフレームバッファ F B a , F B c や、左眼バッファ L B U F 及び右眼バッファ R B U F も配置されている。先に説明した通り、左眼バッファ L B U F と、右眼バッファ R B U F は、各々、メイン表示装置 D S 1 のフレームバッファ F B a と同一容量 (1 0 2 4 × 1 0 2 4 ピクセル分) であって、デコード後の C G データ (最大 1 0 2 4 × 8 2 0 ピクセル分) を、Y 方向に 1 0 2 4 / 8 2 0 倍に拡大して記憶している (図 1 1 ( 2 ) 、図 1 1 ( 4 ) 参照)。

#### 【 0 1 7 9 】

以上を踏まえて、図 6 ( b ) や図 8 に関して確認的に説明する。プリローダ 7 3 は、グラフィックスデコーダ 7 5 のデコード処理に先行して、C G R O M 5 5 から C G データを50

読み出し、読み出した CG データを、 CG バス I F 部 8 2 D R A M I F 部 8 3 を経由して、 D R A M 5 4 のプリロード領域 T E M P に格納する。図 6 ( b ) の矢印や、図 8 のタイミング T 1 " の左向き矢印は、この先読み（プリロード）動作を示している。

#### 【 0 1 8 0 】

そして、プリロード領域 T E M P に読み出された CG データは、その後、グラフィックステコーダ 7 5 によってデコードされ、メイン表示装置 D S 1 の一フレーム分の画像データについては、左眼バッファ L B U F や右眼バッファ R B U F を経由して、フレームバッファ F B a に完成される。

#### 【 0 1 8 1 】

図 8 のタイミング T 1 + の矢印は、グラフィックスデコーダ 7 5 のデコード処理を示し、タイミング T 1 + ' や T 1 + " の矢印は、フレームバッファ F B a に一フレーム分の画像データが生成されるまでの動作を示している。なお、サブ表示装置 D S 2 の一フレーム分の画像データについては、左眼バッファ L B U F や右眼バッファ R B U F を経由することなく、直接、フレームバッファ F B c に完成される。

#### 【 0 1 8 2 】

続いて、図 9 ~ 図 1 2 に基づいて、画像制御 C P U 6 3 と V D P 回路 5 2 の内部動作を説明する。先ず、図 9 は、画像制御 C P U 6 3 の動作を説明するフローチャートである。C P U リセット後、画像制御 C P U 6 3 は、V D P 回路 5 2 のレジスタ群 7 0 を含んだ内部回路を適宜に初期設定する（ S T 1 ）。

#### 【 0 1 8 3 】

この初期設定（ S T 1 ）には、表示回路 7 4 A のスケーリング処理について、表示レジスタの設定処理が含まれてあり、フレームバッファ F B a に生成された  $1024 \times 1024$  ピクセル分の画像データが、  $1280 \times 1024$  ピクセル分の画像データに拡大されるよう初期設定される。

#### 【 0 1 8 4 】

また、この初期設定（ S T 1 ）には、左眼用画像と右眼用画像とを重ねるための ブレンド処理のための 値を、フレームバッファ F B a の チャンネルに固定値として書込む処理も含まれる。

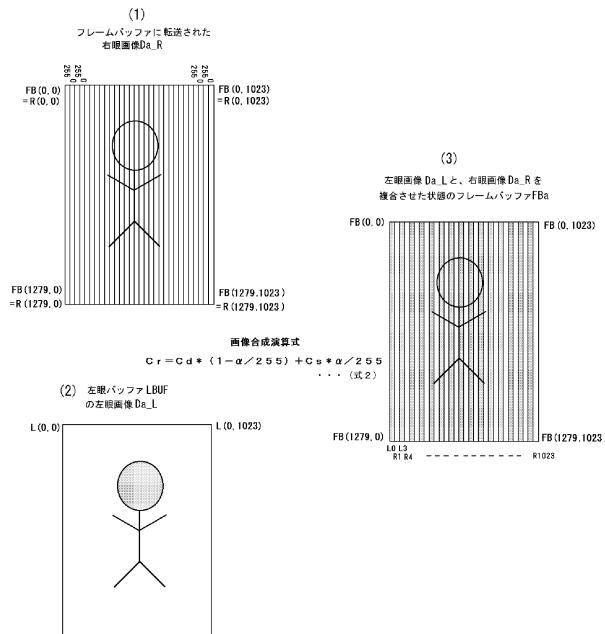

#### 【 0 1 8 5 】

具体的には、図 1 2 ( 1 ) に示す通りであり、フレームバッファ F B a の一行目である F B ( 0 , 0 ) ~ F B ( 0 , 1 0 2 3 ) の チャンネルに、 値として 0 を書込み、フレームバッファ F B a の二行目である F B ( 1 , 0 ) ~ F B ( 1 , 1 0 2 3 ) の チャンネルに、 値として 2 5 5 を書込む。以下同様であって、図 1 2 ( 1 ) に示す奇数行目の チャンネルには、 値 0 を書込み、偶数行目の チャンネルには、 値 2 5 5 を書込む。

#### 【 0 1 8 6 】

この 値は、左眼用画像と右眼用画像とを重ねるための ブレンド処理で使用され、具体的には、  $C_r = C_d * (1 - / 255) + C_s * / 255$  の演算が実行される。この演算式において、 C d は、上書きされる元画像（ Destination ）の R G B 情報、 C s は、上書きする新規画像（ Source ）の R G B 情報、 C r は、 ブレンド処理後の R G B 情報である。なお、 2 5 5 は、 1 バイト構成（ n = 8 ）の 値の上限値であり、データ構成に対応して変化する（  $2^n - 1$  ）。

#### 【 0 1 8 7 】

先に説明した通り、 値は、図 1 2 ( 1 ) に示す奇数行では 0 、偶数行では 2 5 5 であるので、結局、奇数ピクセル行に対応するフレームバッファ F B a では、 C r = C d の関係より、元画像（ Destination ）がそのまま残り、一方、偶数ピクセル行に対応するフレームバッファ F B a は、 C r = C s の関係より、元画像（ Destination ）が消滅して、上書きされる新規画像（ Source ）だけが記憶されることになる。この演算動作は、右眼画像と、左眼画像を生成するために使用されるが、その詳細については、図 1 1 ~ 図 1 2 に関して後述する。

#### 【 0 1 8 8 】

10

20

30

40

50

ところで、左眼用画像と右眼用画像とを重ねるための ブレンド処理を除いた、通常のブレンド処理は、左眼バッファ L B U F や右眼バッファ R B U F やフレームバッファ F B c において実行され、その演算式は、例えば、 $C_r = C_d * (1 - A_s / 255) + C_s * A_s / 255$  となる。ここで、A s は、上書きする新規画像 (Source) 側の 値であつて、図 12 (1) に示すフレームバッファ F B a の固定値 (= 0 / 255) が使用されることはない。

#### 【0189】

値の設定を含む初期化処理 (S T 1) が終われば、次に、画像制御 C P U 6 3 は、外付け D R A M 5 4 に確保されたディスプレイリストバッファ D L B を初期化した上で (S T 2)、ディスプレイリスト D L の作成を開始する。先ず、そして、ディスプレイリスト D L の先頭に、作業領域を全クリアするための描画コマンドとして、塗りつぶし命令を書込む (S T 3)。本実施例の場合、この塗りつぶし命令でクリアされる作業領域は、フレームバッファ F B a, F B c と、左眼バッファ L B U F と、右眼バッファ R B U F とである。

#### 【0190】

そのため、ディスプレイリスト D L を解釈して実行する描画回路 7 6 では、その先頭に記載されている塗りつぶし命令に基づいて、上記の作業領域を全クリアすることになる。そのため、例えば、表示画面が縮小化されるような画像演出においても、それ以前の画像データが、その後の表示画面に表示されるおそれがない。

#### 【0191】

続いて、画像制御 C P U 6 3 は、メイン表示装置 D S 1 のディスプレイリスト D L の作成に関して、操作スイッチ 1 1 の押圧回数に基づいて、そのタイミングが、2 D 表示モードか 3 D 表示モードかが判定される (S T 4)。

#### 【0192】

そして、そのタイミングが 3 D 表示モードであれば、画像演出シナリオに基づいて、左眼用画像と右眼用画像を構成する一又は複数の描画素材を、左眼バッファ L B U F と右眼バッファ R B U F の仮想描画空間 V I T に貼付けるためのコマンド列 C M D 1, C M D 2 をディスプレイリスト D L に列記する (S T 5)。

#### 【0193】

ここで、ディスプレイリスト D L の作成時で参照される画像演出シナリオは、演出制御 C P U 4 0 から受けた制御コマンド C M D ' で特定される画像演出を具体化したものである。すなわち、画像演出シナリオには、一定時間継続される一連の動画や、描画位置や配置姿勢や拡大縮小率が適宜に規定される静止画（背景画像や予告画像を含む）について、(1) 一連の動画演出の開始時刻や終了時刻、(2) どの静止画を、どの時刻に、どの位置に、どのように描くか、などが規定されている。

#### 【0194】

そして、コマンド列 C M D 1, C M D 2 には、デコード領域の左眼画像データや右眼画像データを、各々、Y 方向に 1024 / 820 倍に拡大して、左眼バッファ L B U F と右眼バッファ R B U F に配置する描画コマンドが含まれている。また、コマンド列 C M D 1, C M D 2 に、ブレンド処理が含まれる場合は、source 側の 値 (A s) を使用して、例えば、 $C_r = C_d * (1 - A_s / 255) + C_s * A_s / 255$  の演算がされる点も、先に説明した通りである。

#### 【0195】

何れにしても、これらのコマンド列 C M D 1, C M D 2 が、V D P 回路において、逐次解釈されて実行されると、C G R O M 5 5 の一又は複数の必要な C G データが先読みされ、各々、デコードされた後に適宜に組み合わせることで、左眼バッファ L B U F と右眼バッファ R B U F に、メイン表示装置 D S 1 の一フレーム分の左眼画像と右眼画像が構築されることになる。

#### 【0196】

図 11 (1) と、図 11 (3) は、デコード領域に展開された左眼画像 D\_oL 及び右眼画

10

20

30

40

50

像D\_oRを模式的に示しており、何れも、本実施例では、C G R O M 5 5に記憶されているC Gデータに対応して、原則として、 $1024 \times 820$ ピクセル分、又はそれ以下の画像データとなっている。そして、これらの画像データ(D\_oL, D\_oR)が、Y方向に $1024 / 820$ 倍に拡大されて、左眼バッファL B U Fと右眼バッファR B U Fに配置されて、図11(2)と図11(4)に示す左眼画像Da\_L及び右眼画像Da\_Rとなる。

#### 【0197】

左眼バッファL B U Fと右眼バッファR B U Fに、左眼画像Da\_Lと右眼画像Da\_Rを完成させるためのコマンド列CMD1, CMD2の列記が終われば、次に、右眼バッファR B U Fの全体を、左 $90^\circ$ 回転させてフレームバッファF B aに転送させるための描画コマンドCMD3を、ディスプレイリストDLに付加する(ST6)。

10

#### 【0198】

図11(5)は、描画コマンドCMD3の実行により、左 $90^\circ$ 回転させて転送させた、フレームバッファF B aの右眼画像Da\_Rを示している。この実施例では、右眼バッファR B U FとフレームバッファF B aは、各々、 $1024 \times 1024$ ピクセル分の記憶容量を有しているので、図11に示す式(1)の座標変換式に基づいて、右眼バッファR B U Fにおけるピクセル位置P s(i', j')の画像情報が、フレームバッファF B aのピクセル位置P d(x', y')の画像情報となる。なお、座標変換式は、回転中心を原点(0, 0)とする左 $90^\circ$ 回転式であるので、P s(i', j')とP d(x', y')の座標位置も、原点(0, 0)に対応して座標変換されている。

#### 【0199】

もっとも、実際の描画コマンドとしては、右眼バッファR B U Fの全体画像をsourceとし、フレームバッファF B aをdestinationとする転送コマンドにおいて、destination先の左上端点と右下端点を、左 $90^\circ$ 回転用に設定するだけで足り、そのような描画コマンドの実行によって、上記した座標変換が自動的に実現される。

20

#### 【0200】

ステップST6の処理が終われば、画像制御CPU63は、図11(2)に示す左眼バッファL B U Fの左眼画像Da\_Lを、左 $90^\circ$ 回転させた状態で、図11(5)に示すフレームバッファF B aの右眼画像Da\_Rとの間で、図12の(式2)に示すブレンド処理を実行して、フレームバッファF B aに上書きする描画コマンドCMD4を、ディスプレイリストDLに付加する(ST7)。

30

#### 【0201】

図12の(式2)に示す通り、このブレンド処理では、 $C_r = C_d * (1 - / 255) + C_s * / 255$ の演算が実行されるが、C dは、図11(5)や図12(1)に示すフレームバッファF B aの右眼画像Da\_R(左 $90^\circ$ 回転状態)についてのピクセルRGBデータである。また、C sは、フレームバッファF B aに上書きされる左眼バッファL B U Fの左眼画像Da\_L(図11(2)参照)についてのピクセルRGBデータである。

#### 【0202】

なお、図12(1)では、初期状態で設定された値も示されている。また、図12(2)は、図11(2)に示す左眼バッファL B U Fの左眼画像Da\_Lを左 $90^\circ$ 回転させた状態を示す参考図である。

40

#### 【0203】

そして、図12(1)に示す右眼画像Da\_Rと、図12(2)に示す左眼画像Da\_Lとの間で、上記した $C_r = C_d * (1 - / 255) + C_s * / 255$ の演算が実行されることで、値=0の奇数ピクセル行では、 $C_r = C_d$ の関係より元の右眼画像Da\_Rがそのまま残り、値=255の偶数ピクセル行では、 $C_r = C_s$ の関係より新規の左眼画像Da\_Lだけが記憶されることになる。

#### 【0204】

図12(3)は、この演算結果について模式的に図示したものであり、左眼画像Da\_Lを網掛けで示している。このようにして完成されたフレームバッファF B aの複合画像( $1024 \times 1024$ ピクセル分)は、その後、表示回路74Aのスケーラで、X方向に12

50

80 / 1024倍に拡大されることで、図12(4)に示す複合画像となる。先に説明した通り、スケーラの拡大倍率は、初期処理において(ST1)、表示レジスタに設定されている。

#### 【0205】

以上、3D表示モードの動作時における、ディスプレイリストDLの構築手順を説明したが、2D表示モードの動作時には、ステップST12に示す通り、画像制御CPU63は、画像演出シナリオを解析して左眼画像Da\_Lを左眼バッファLBUFに構築するためのコマンド列CMD1をディスプレイリストDLに列記する。

#### 【0206】

先に説明した通り、コマンド列CMD1には、デコード領域の左眼画像D\_oLを、Y方向に1024 / 820倍に拡大して、左眼バッファLBUFに配置する描画コマンドも含まれている。

#### 【0207】

次に、左眼バッファLBUFの左眼画像Da\_Lを、左90°回転させてフレームバッファFBaに転送する描画コマンドCMD5をディスプレイリストDLに付加する(ST13)。これらの処理から明らかな通り、2D表示モードでは、右眼画像Da\_Rが使用されることなく、左眼画像Da\_Lだけで表示画面が構築されることになる。

#### 【0208】

以上の通り、2D表示モードか3D表示モードかに応じて、メイン表示装置DS1について、適切なディスプレイリストDLを生成した後、画像制御CPU63は、サブ表示装置DS2についてのディスプレイリストDLを生成する(ST8)。サブ表示装置DS2のディスプレイリストDLについては、図13に示す通りであり、その詳細は後述する。

#### 【0209】

そして、ディスプレイリストDLの終結を特定する描画コマンド(EODL)を付加した後(ST9)、今回作成したディスプレイリストDLに関してプリローダ73の先読み動作を開始させる(ST10)。図8のタイミングT1'は、ディスプレイリストバッファDLBに、ディスプレイリストDLが完成したステップST9の処理後のタイミングを示している。

#### 【0210】

プリローダ73の先読み動作の開始指示は、具体的には、ディスプレイリストバッファDLBなどを特定する「プリローダレジスタ」に対する設定値に基づいて実現される。図10(a)に示す通り、プリローダ73は、今回、画像制御CPU63が作成したディスプレイリストDLに関して、必要なCGデータを外付けDRAM54に読み出し(SS10)、参照アドレスを書き換えた修正ディスプレイリストDL'を、ディスプレイリストバッファDLBの該当領域に格納する(SS11)。図8のタイミングT1''は、これらの動作を示している。

#### 【0211】

次に、図9に戻って、画像制御CPU63の動作説明を続けると、ステップST10の処理に続いて、画像制御CPU63は、1/60秒毎に生じるメイン表示装置DS1のVブランク割り込みの発生を待つ(ST11)。特に限定されるものではないが、この実施例では、1/30秒(=)毎に、ディスプレイリストDLを更新するので、Vブランク割り込みを二回受けるとステップST12の処理に移行することになる。

#### 【0212】

具体的には、画像制御CPU63は、新規の描画動作や表示動作を開始するべく描画回路76や表示回路74に動作開始を指示する(ST12)。なお、これらの動作は、描画レジスタや表示レジスタに所定の設定値を設定することで実現される。そして、その後は、次の表示画面を特定するディスプレイリストDLについてステップST2～ST10の処理を実行することになる。

#### 【0213】

このように、本実施例の画像制御CPU63は、所定時間( )毎にディスプレイリス

10

20

30

40

50

TDLを更新するが、プリローダ73、描画回路76、及び、表示回路74についても、画像制御CPU63からの動作指示に基づいて、所定時間( )毎に、図10(a)～図10(c)のように間欠的に動作する。

#### 【0214】

図10(d)は、各部の動作手順を説明するタイムチャートであり、画像制御CPU63は、所定時間( )毎に、ディスプレイリストDL1, DL2, DL3…を作成し、プリローダ73は、ディスプレイリストDLを適宜に書き換えて修正ディスプレイリストDL'を生成することを示している。

#### 【0215】

そして、修正ディスプレイリストDL'は、一周期後のタイミング(+ )で、描画回路76に解釈実行され、フレームバッファFBa, FBcに、必要な画像データが生成され、生成されたフレームバッファFBa, FBcの画像データは、更に一周期後のタイミング(+ )で、表示回路74によって出力される。

10

#### 【0216】

例え、タイミングT1からT1'までの処理で、外付けDRAM54に生成されたディスプレイリストDL1は、タイミングT1"から開始されるプリローダ73の動作によって実効化され、必要なCGデータが、CGROM55から外付けDRAM54に読み出されると共に、修正ディスプレイリストDL1'が、外付けDRAM54生成される。

#### 【0217】

そして、その後のタイミングT1+から開始される描画回路76の処理によって、修正ディスプレイリストDL1'が解釈されて、フレームバッファFBa, FBcに、必要な画像データが生成される。描画回路の動作は、図10(b)に示す通りであり、修正ディスプレイリストDL1'に記載されている描画コマンドを順番に解析して(SS20)、描画コマンドが指定する静止画や動画について、グラフィックスデコーダ75やジオメトリエンジン77を機能させる。描画回路76は、書換え後の修正ディスプレイリストDL1'を処理するので、静止画や動画に関するCGデータの参照先は、外付けDRAM54である。

20

#### 【0218】

そして、グラフィックスデコーダ75によってデコードされた静止画データや動画データは、各々、外付けDRAM54に確保されている静止画データ領域や動画データ領域に伸張展開される(SS22～SS23)。

30

#### 【0219】

次に、デコード後の静止画データや動画データが、描画コマンドによって規定される描画様式で、外付けDRAM54のフレームバッファFBの所定位置に書き込まれることで描画処理が実行される(SS24)。なお、描画様式には、フレームバッファFBにおける描画位置が含まれるが、スプライト画像などの場合には、更に、描画姿勢や拡大縮小率などが規定される場合があり、ジオメトリエンジン77が機能する。

#### 【0220】

描画回路76がフレームバッファFBの描画処理領域に生成した画像データ(DL1で特定される画像データ)は、タイミングT1+2から開始される動作周期において、描画処理領域と表示処理領域が切り替わり(bank flip)、表示回路74によって出力される。この動作は、図10(c)に示す通りである。

40

#### 【0221】

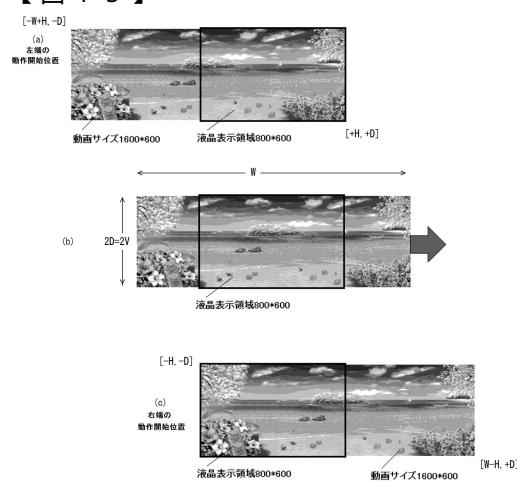

続いて、図13に基づいて、サブ表示装置DS2のディスプレイリストDLの作成手順を説明する。サブ表示装置DS2における画像演出は、図15(b)に示す背景画像を、左右方向に移動させつつ、その上に、適宜な描画素材を貼付けることで実現されている。

#### 【0222】

図15(b)に示す通り、実施例の背景画像は、横(=W)が1600ピクセル、縦(=2D)が600ピクセルの長尺フレームで構成されている。そして、この長尺フレームを、フレームバッファFBcの仮想描画空間VITに貼付ける場合に、その貼付け位置を

50

適宜に移動することで、円滑に移動する簡易動画の動作を実現している。

#### 【0223】

先に説明した通り、仮想描画空間VITに貼付けられた長尺フレームのうち、実際にフレームバッファFBcに登録されるのは、仮想描画空間VITの中央に定義される描画領域 $2H \times 2V$ に位置する $800 \times 600$ ピクセル分の画像データだけである。

#### 【0224】

以上を踏まえて説明を続けると、サブ表示装置用DS2のディスプレイリストDLの作成においては、最初に、長尺フレームの貼付け位置を特定する必要がある(ST21)。そこで、本実施例では、仮想描画空間VIT上の座標位置を特定する変数として、水平変数HORと増分変数 $\Delta$ を使用し、長尺フレームの貼付け位置の上端点を(HOR, -D)とし、右下端点を(HOR + W, D)としている。そして、この貼付け位置に、長尺フレームを貼付ける描画コマンドをディスプレイリストDLに記載する(ST21)。10

#### 【0225】

なお、水平変数HORは、動作開始時に、 $HOR = -W + H$ に初期設定され、増分変数 $\Delta$ は、例えば、 $\Delta = +5$ に初期設定されている。ここで、 $\Delta = +5$ は、長尺フレームの貼付け位置を、1/30秒毎に、右方向に5ピクセル移動させることを意味する。1/30秒は、ディスプレイリストDLの更新周期を意味する。

#### 【0226】

ステップST21の処理が終われば、 $HOR = HOR + \Delta$ の演算によって、水平変数HORの値を更新し(ST22)、更新後の水平変数HORの値が、限界位置を超えるか否かを判定する(ST23)。水平変数HORの限界位置は、図15(a)に示す左限界位置と、図15(c)に示す右限界位置であり、具体的には、左限界位置を左に超えるか、右限界位置を右に超えるかが判定される(ST23)。20

#### 【0227】

そして、何れかの限界位置を超える場合には、 $HOR = HOR - \Delta$ の演算によって、増分変数 $\Delta$ の符号を逆転させる。例えば、増分変数 $\Delta$ が、+5から-5に書き換えられた場合には、その後は、長尺フレームの貼付け位置が、1/30秒毎に、左方向に5ピクセル移動することを意味する。

#### 【0228】

次に、増分変数 $\Delta$ の正負符号に基づき、限界位置を超えた水平変数HORの値を、左端開始位置(-W + H)に書き換えるか、或いは、右端開始位置(-H)に書き換える(ST26, ST27)。以上の処理によって、その後のディスプレイリストに記載される描画コマンド(ST21)に基づき、長尺フレームの貼付け位置が適宜に移動することになる。30

#### 【0229】

以上の処理によって、背景画の左右方向の移動動作が特定されるので、次に、背景画に重ねて表示すべき他の描画素材を特定する描画コマンド列をディスプレイリストに列記する(ST28)。したがって、最初に仮想描画空間VITに貼付けた長尺フレームの一部が消滅すると共に、後で配置される描画素材ほど優先されることになる。

#### 【0230】

そのため、フレームバッファFBcに上書きされる描画素材に関して、必要に応じて、ブレンド処理が実行される。ブレンド処理は、フレームバッファFBcの画像をCdとし、上書き素材の画像をCsとして、例えば、 $C_r = Cd * (1 - As / 255) + Cs * As / 255$ の演算で実現される。なお、Asは、source側である上書き素材のA値である。40

#### 【0231】

具体的には、図15(a)の位置から右方向の移動を開始して、図15(c)の状態に至り、その後、左方向に移動して図15(a)の状態に至る背景画(簡易動画)の往復運動が繰り返される。例えば、 $\Delta = \pm 5$ の場合には、 $800 / 5 = 160$ であるので、 $160 / 30 = 5.3$ 秒程度を要して往路移動が完了し、続いて、5.3秒程度を要して復路50

移動が完了する周期 10.6 秒程度の往復運動が実現される。

#### 【0232】

例えば、一般動画の場合には、各フレームを 30 f p s (frame per second) 程度の速度で更新する必要があるので、10.6 秒間の動画を実現するには、 $30 \times 10.6$  枚のフレームデータが必要になるところ、本実施例では、 $1600 \times 600$  ピクセル分の長尺フレーム一枚で足り、CGROM の容量抑制に効果的に貢献する。因みに、 $30 \times 10.6$  枚の動画フレームデータは、MPEG などの動画圧縮処理を経ない状態では、 $30 \times 10.6 \times 800 \times 600$  ピクセル分の画像データとなり、本実施例のデータ量抑制効果 ( $= 15 \times 10.6$  倍) の高さが確認される。

#### 【0233】

また、プリロード領域 TEMP における CG データのキャッシング機能を活用することで、CGROM55 を繰り返しアクセスする必要もなくなる。

#### 【0234】

ところで、これまで説明した実施例では、サブ表示装置を 1 個としたが、2 個又はそれ以上のサブ表示装置を配置するのも好適である。そして、同形のサブ表示装置 DS2, DS3 を、上下又は左右に隣接配置するような場合には、同じ長尺フレームについて、その貼付け位置を、各仮想描画空間において適宜にずらすことで、上下又は左右に連続する画像を表示することもできる。

#### 【0235】

図 13 (b) は、サブ表示装置 DS2 のフレームバッファ F B b と、サブ表示装置 DS3 のフレームバッファ F B c に各々対応する 2 つの描画領域と、長尺フレームとの相対位置関係を図示したものである。この場合には、長尺フレームの仮想描画空間への貼付け位置を、描画領域の横幅分だけずらすことで、2 つの表示装置 DS2, DS3 に、左右に連続する画像を表示することができる。そして、描画領域の横幅分の相対関係を維持しつつ、各仮想描画空間への貼付け位置を時間的に変化させれば、左右に移動する簡易動画を実現することができる。

#### 【0236】

また、図 13 (c) は、同形のサブ表示装置 DS2, DS3 を、上下に隣接配置した場合を例示しており、長尺フレームの仮想描画空間への貼付け位置を、描画領域の縦幅分だけずらすことで、2 つの表示装置 DS2, DS3 に、上下に連続する画像を表示することができる。なお、一フレームを完成させる上で、長尺フレームの貼付け回数は一回に限定されず、一の表示装置の仮想描画空間に、単一の長尺フレームを複数回、隣接して貼付けても良い。

#### 【0237】

図 13 (c) の右側は、このような貼付け状態を示しており、单一の長尺フレームを左右方向に隣接させ、且つ、貼付け位置を上下方向にずらせて貼付けることで、例えば、サブ表示装置 DS2 において、特別図柄 3 個の変動動作が実現される。なお、この実施態様では、長尺フレームの下部位置には、これに続くべき、長尺フレームの上部位置の図柄が記載されている。そして、表示装置 DS2 に、長尺フレームの最下部を表示した後、最上部を表示するよう、貼付け位置を仮想描画空間の上方に切換えることで、スロットマシンの回転リールが回転する場合のような、自然な回転動作を表示することができる。

#### 【0238】

また、4 個のサブ表示装置を左右上下に隣接配置すると共に、長尺フレームの仮想描画空間への貼付け位置を適宜にずらすことで、4 倍の大きさの表示画面に、4 倍の画像を表示して適宜に移動させることもできる。この移動動作は、往復動作に限定されず、規則的又は不規則な回転動作も含まれる。また、長尺フレームに代えて、描画領域より縦横に大きい大型フレームを使用するのも好適である。

#### 【0239】

以上、実施例について詳細に説明したが、具体的な記載内容は特に本発明を限定するものではない。例えば、上記した実施例では、フレームバッファ F B a の補助バッファとし

10

20

30

40

50

て、左眼バッファ L B U F と、右眼バッファ R B U F を用意して、左眼画像を左眼バッファ L B U F に構築し、右眼画像を右眼バッファ R B U F に構築したが、何ら限定されない。

#### 【 0 2 4 0 】

例えは、フレームバッファ F B a に、直接、右眼画像を構築する構成を探れば、右眼バッファ R B U F が不要となり、逆に、フレームバッファ F B a に、直接、左眼画像を構築すれば、左眼バッファ L B U F が不要となる。この場合、フレームバッファ F B a の右眼画像に、左眼バッファ L R B U F の左眼画像を複合させる ブレンド処理か、或いは、フレームバッファ F B a の左眼画像に、右眼バッファ R B U F の右眼画像を複合させる ブレンド処理が必要となる。

10

#### 【 0 2 4 1 】

この ブレンド処理において、 $C_r = C_d * (1 - / 255) + C_s * / 255$  の演算式を探る場合には、フレームバッファ F B a に構築した画像 C d (Destination) に対して、左眼画像又は右眼画像のいずれを、新規画像 C s (Source) とするかに応じて、図 9 に示す初期処理 (S T 1) では、フレームバッファ F B a の チャンネルに、最適値 (0 / 255) を設定することになる。

#### 【 0 2 4 2 】

なお、この構成では、右眼画像又は左眼画像を構築する過程で、フレームバッファ F B a において、 ブレンド処理が必要となる場合がある。しかし、この ブレンド処理は、 source 側の 値 (A s) を使用するので、フレームバッファ F B a の チャンネルが上書き破損されることはない。すなわち、右眼画像又は左眼画像を構築するための ブレンド処理では、例えは、 $C_r = C_d * (1 - A_s / 255) + C_s * A_s / 255$  の演算式が使用される。

20

#### 【 0 2 4 3 】

また、上記した実施例のメイン表示装置 D S 1 は、横長の表示画面で構成されており、この表示画面を右 90° 回転させて縦長に配置したが、何ら限定されるものではない。すなわち、縦長の表示画面を有するメイン表示装置の場合には、左 90° 回転用の描画コマンドは不要であり、左眼バッファ L B U F の左眼画像 Da\_L と、右眼バッファ R B U F からフレームバッファ F B a に転送された右眼画像 Da\_R について、 ブレンド処理をすれば足りることになる。

30

#### 【 0 2 4 4 】

また、上記した実施例では、C G R O M 5 5 の画像データのデータ量を抑制するため、メイン表示装置で表示する画像が、原則として、1024 × 820 ピクセルを超えないよう抑制されているが、この点も何ら限定されない。例えは、メイン表示装置 D S 1 で表示する画像を、表示画面のピクセル数 (縦 1280 × 横 1024) に対応して、縦 1280 × 横 1024 ピクセル、又はこれ以下にすれば、描画コマンドによる描画演算処理が単純化される。

#### 【 0 2 4 5 】

図 15 は、そのように簡素化した場合の関係を図示したものである。すなわち、図 15 (1) は、縦 1280 × 横 1024 ピクセル分のフレームバッファ F B a に、直立状態の右眼画像 Da\_R を配置した状態を示している。但し、このような直立配置の構成を探る場合には、初期処理 (図 9 の S T 1) において、フレームバッファ F B a の縦方向の奇数列 (1 列、 3 列、 ...) の チャンネルに、 値 = 255 が記憶され、フレームバッファ F B a の縦方向の偶数列 (2 列、 4 列、 ...) の チャンネルに、 値 = 0 が記憶されている必要がある。

40

#### 【 0 2 4 6 】

そして、図 15 (2) は、縦 1280 × 横 1024 ピクセル分の左眼バッファ L B U F に、左眼画像 Da\_L を配置した状態を示し、図 15 (3) は、 ブレンド処理後のフレームバッファ F B a の画像を示している。この場合の ブレンド処理も、 $C_r = C_d * (1 - / 255) + C_s * / 255$  の演算によって実現される。

50

## 【0247】

このような構成においても、左眼バッファ L B U F、又は右眼バッファ R B U Fを省略できるのは勿論である。また、長尺フレーム又は大型フレームを使用して、メイン表示装置 D S 1において簡易動画を再生することも何ら禁止されない。この場合、メイン表示装置 D S 1は、3D表示モードであるか2D表示モードであるかを問わない。

## 【0248】

また、上記の実施例では、遊技者が操作ボタン 11を押圧することで、2D表示と3D表示を切り替える構成としたが、この構成に代え、又は、この構成に加えて、係員のボタン操作（不図示の設定ボタンの操作）に応じて、表示モードを切り替える構成としても良い。以上、ここまで、専ら、弾球遊技機に関して説明したが、本発明は、弾球遊技機に限らず、回胴遊技機など、画像演出を伴う他の遊技機においても好適に活用できることは勿論である。10

## 【符号の説明】

## 【0249】

|                 |                                    |

|-----------------|------------------------------------|

| G M             | 遊技機                                |

| D S 1 , D S 2   | 表示装置                               |

| 5 1             | 画像演出制御手段（内蔵 C P U 回路 / C P U 6 3 ） |

| 5 2             | 画像生成手段                             |

| S T 1           | 第1手段                               |

| S T 5 ~ S T 1 3 | 第2手段                               |

20

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

---

フロントページの続き

(56)参考文献 特許第5 9 0 9 5 6 9 ( J P , B 1 )

特開2 0 1 7 - 0 2 3 3 2 9 ( J P , A )

特開2 0 1 4 - 0 6 8 8 4 5 ( J P , A )

特開2 0 1 4 - 1 2 1 4 7 6 ( J P , A )

(58)調査した分野(Int.Cl. , DB名)

A 6 3 F 7 / 0 2