**(12) STANDARD PATENT**

**(19) AUSTRALIAN PATENT OFFICE**

**(11) Application No. AU 2017382316 B2**

(54) Title

**Integrated photodetector with direct binning pixel**

(51) International Patent Classification(s)

**H01L 27/146** (2006.01)      **H01L 27/148** (2006.01)

**G01N 21/64** (2006.01)

(21) Application No: **2017382316**      (22) Date of Filing: **2017.12.22**

(87) WIPO No: **WO18/119347**

(30) Priority Data

(31) Number

**62/438,051**      (32) Date

**2016.12.22**      (33) Country

**US**

(43) Publication Date: **2018.06.28**

(44) Accepted Journal Date: **2023.02.09**

(71) Applicant(s)

**Quantum-Si Incorporated**

(72) Inventor(s)

**Rothberg, Jonathan M.;Fife, Keith G.;Boisvert, David**

(74) Agent / Attorney

**Davies Collison Cave Pty Ltd, Level 15 1 Nicholson Street, MELBOURNE, VIC, 3000, AU**

(56) Related Art

**WO 2016/022998 A2**

**EP 2487897 A1**

**US 2016/0041095 A1**

(12) INTERNATIONAL APPLICATION PUBLISHED UNDER THE PATENT COOPERATION TREATY (PCT)

CORRECTED VERSION

(19) World Intellectual Property Organization

International Bureau

(43) International Publication Date

28 June 2018 (28.06.2018)

(10) International Publication Number

**WO 2018/119347 A9**

(51) International Patent Classification:

*H01L 27/146* (2006.01)      *G01N 21/64* (2006.01)

*H01L 27/148* (2006.01)

(74) Agent: PRITZKER, Randy, J. et al.; Wolf, Greenfield & Sacks, P.C., 600 Atlantic Avenue, Boston, MA 02210-2206 (US).

(21) International Application Number:

PCT/US2017/068089

(81) Designated States (unless otherwise indicated, for every kind of national protection available): AE, AG, AL, AM, AO, AT, AU, AZ, BA, BB, BG, BH, BN, BR, BW, BY, BZ, CA, CH, CL, CN, CO, CR, CU, CZ, DE, DJ, DK, DM, DO, DZ, EC, EE, EG, ES, FI, GB, GD, GE, GH, GM, GT, HN, HR, HU, ID, IL, IN, IR, IS, JO, JP, KE, KG, KH, KN, KP, KR, KW, KZ, LA, LC, LK, LR, LS, LU, LY, MA, MD, ME, MG, MK, MN, MW, MX, MY, MZ, NA, NG, NI, NO, NZ, OM, PA, PE, PG, PH, PL, PT, QA, RO, RS, RU, RW, SA, SC, SD, SE, SG, SK, SL, SM, ST, SV, SY, TH, TJ, TM, TN, TR, TT, TZ, UA, UG, US, UZ, VC, VN, ZA, ZM, ZW.

(22) International Filing Date:

22 December 2017 (22.12.2017)

(84) Designated States (unless otherwise indicated, for every kind of regional protection available): ARIPO (BW, GH, GM, KE, LR, LS, MW, MZ, NA, RW, SD, SL, ST, SZ, TZ, UG, ZM, ZW), Eurasian (AM, AZ, BY, KG, KZ, RU, TJ, TM), European (AL, AT, BE, BG, CH, CY, CZ, DE, DK, EE, ES, FI, FR, GB, GR, HR, HU, IE, IS, IT, LT, LU, LV, MC, MK, MT, NL, NO, PL, PT, RO, RS, SE, SI, SK, SM,

(25) Filing Language: English

(26) Publication Language: English

(30) Priority Data:

62/438,051      22 December 2016 (22.12.2016) US

(71) Applicant: QUANTUM-SI INCORPORATED [US/US];

530 Old Whitfield Street, Guilford, CT 06437 (US).

(72) Inventors: ROTHBERG, Jonathan, M.; 215 Uncas Point Road, Guilford, CT 06437 (US). FIFE, Keith, G.; 635 Matadero Avenue, Palo Alto, CA 94306 (US). BOISVERT, David; 18900 Graystone Lane, San Jose, CA 95120 (US).

(54) Title: INTEGRATED PHOTODETECTOR WITH DIRECT BINNING PIXEL

FIG. 3

(57) Abstract: An integrated circuit includes a photodetection region configured to receive incident photons. The photodetection region is configured to produce a plurality of charge carriers in response to the incident photons. The integrated circuit includes at least one charge carrier storage region. The integrated circuit also includes a charge carrier segregation structure configured to selectively direct charge carriers of the plurality of charge carriers directly into the at least one charge carrier storage region based upon times at which the charge carriers are produced.

---

TR), OAPI (BF, BJ, CF, CG, CI, CM, GA, GN, GQ, GW, KM, ML, MR, NE, SN, TD, TG).

**Published:**

— *with international search report (Art. 21(3))*

**(48) Date of publication of this corrected version:**

30 August 2018 (30.08.2018)

**(15) Information about Correction:**

see Notice of 30 August 2018 (30.08.2018)

20 Dec 2022

2017382316

## INTEGRATED PHOTODETECTOR WITH DIRECT BINNING PIXEL

### CROSS-REFERENCE TO RELATED APPLICATIONS

This application claims priority to U.S. provisional application serial no. 62/438,051, 5 titled "INTEGRATED PHOTODETECTOR WITH DIRECT BINNING PIXEL," filed December 22, 2016, which is hereby incorporated by reference in its entirety.

This application is related to U.S. non-provisional application serial no. 14/821,656, titled "INTEGRATED DEVICE FOR TEMPORAL BINNING OF RECEIVED PHOTONS," filed August 7, 2015, which is hereby incorporated by reference in its entirety.

### BACKGROUND

Photodetectors are used to detect light in a variety of applications. Integrated photodetectors have been developed that produce an electrical signal indicative of the intensity of incident light. Integrated photodetectors for imaging applications include an 5 array of pixels to detect the intensity of light received from across a scene. Examples of integrated photodetectors include charge coupled devices (CCDs) and Complementary Metal Oxide Semiconductor (CMOS) image sensors.

It is desired to overcome or alleviate one or more difficulties of the prior art, or to at least provide a useful alternative.

### SUMMARY

In accordance with some embodiments of the present invention there is provided an integrated circuit, comprising:

a photodetection region configured to receive incident photons, the photodetection 25 region being configured to produce a plurality of charge carriers in response to the incident photons;

at least one charge carrier storage region; and

a charge carrier segregation structure configured to selectively direct charge carriers 30 of the plurality of charge carriers directly into the at least one charge carrier storage region based upon times at which the charge carriers are produced, and to aggregate, in the at least one charge carrier storage region, charge carriers produced in response to a plurality of excitation light pulses.

In accordance with some embodiments of the present invention there is provided an integrated circuit, comprising:

a direct binning pixel, comprising:

a photodetection region configured to receive incident photons, the photodetection region being configured to produce a plurality of charge carriers in response to the incident photons;

at least one charge carrier storage region; and

a charge carrier segregation structure configured to selectively direct charge carriers of the plurality of charge carriers into the at least one charge carrier storage region based upon times at which the charge carriers are produced, and to aggregate, in the at least one charge carrier storage region, charge carriers produced in response to a plurality of excitation light pulses.

In accordance with some embodiments of the present invention there is provided an integrated circuit, comprising:

a plurality of pixels, a first pixel of the plurality of pixels being a direct binning pixel comprising:

a photodetection region configured to receive incident photons, the photodetection region being configured to produce a plurality of charge carriers in response to the incident photons;

a plurality of charge carrier storage regions; and

a charge carrier segregation structure configured to selectively direct charge carriers of the plurality of charge carriers directly into respective charge carrier storage regions of the plurality of charge carrier storage regions based upon times at which the charge carriers are produced, and to aggregate, in the plurality of charge carrier storage regions, charge carriers produced in response to a plurality of excitation light pulses.

In accordance with some embodiments of the present invention there is provided a photodetection method, comprising:

(A) receiving incident photons at a photodetection region of a direct binning pixel; and

20 Dec 2022

(B) selectively directing charge carriers of a plurality of charge carriers produced in response to the incident photons directly from the photodetection region into at least one charge carrier storage region of the direct binning pixel based upon times at which the charge carriers are produced, and aggregating, in the at least one charge carrier storage region, 5 charge carriers produced in response to a plurality of excitation light pulses.

2017382316

2017382316

Also described herein is an integrated circuit, comprising: a photodetection region configured to receive incident photons, the photodetection region being configured to produce a plurality of charge carriers in response to the incident photons; at least one charge carrier storage region; and a charge carrier segregation structure configured to selectively direct charge carriers of the plurality of charge carriers directly into the at least one charge carrier storage region based upon times at which the charge carriers are produced.

Also described herein is an integrated circuit, comprising: a direct binning pixel, comprising: a photodetection region configured to receive incident photons, the photodetection region being configured to produce a plurality of charge carriers in response to the incident photons; at least one charge carrier storage region; and a charge carrier segregation structure configured to selectively direct charge carriers of the plurality of charge carriers into the at least one charge carrier storage region based upon times at which the charge carriers are produced.

Also described herein is an integrated circuit, comprising: a plurality of pixels, a first pixel of the plurality of pixels being a direct binning pixel comprising: a photodetection region configured to receive incident photons, the photodetection region being configured to produce a plurality of charge carriers in response to the incident photons; a plurality of charge carrier storage regions; and a charge carrier segregation structure configured to selectively direct charge carriers of the plurality of charge carriers directly into respective charge carrier storage regions of the plurality of charge carrier storage regions based upon times at which the charge carriers are produced, and to aggregate, in the plurality of charge carrier storage regions, charge carriers produced in a plurality of measurement periods.

Also described herein is a photodetection method, comprising: (A) receiving incident photons at a photodetection region; and (B) selectively directing charge carriers of a plurality of charge carriers produced in response to the incident photons directly from the photodetection region into at least one charge carrier storage region based upon times at which the charge carriers are produced.

20 Dec 2022

2017382316 2017382316

The charge carrier segregation structure may comprise at least one electrode at a boundary between the photodetection region and a first charge carrier storage region of the at least one charge carrier storage region.

5 The charge carrier segregation structure may comprise a single electrode at the boundary between the photodetection region and the first charge carrier storage region.

In some embodiments, no charge carrier capture region is present in the direct binning pixel and/or no charge carrier capture region is present between the photodetection region and a charge carrier storage region.

10 Charge carriers may be transferred to the at least one charge carrier storage region without capturing the carriers between the photodetection region and the at least one charge carrier storage region.

15 A charge carrier rejection region may discard charge carriers produced in the photodetection region during a rejection period.

5 The discarded charge carriers may be removed from the photodetection region in a different direction from a direction in which carriers are directed from the photodetection region toward a charge carrier storage region.

A charge carrier rejection region may discard charge carriers produced in the photodetection region during a rejection period by changing a voltage of an electrode at a boundary between the photodetection region and the charge carrier rejection region.

20 Single photons may be transferred to the at least one charge carrier storage region and aggregated in the at least one charge carrier storage region.

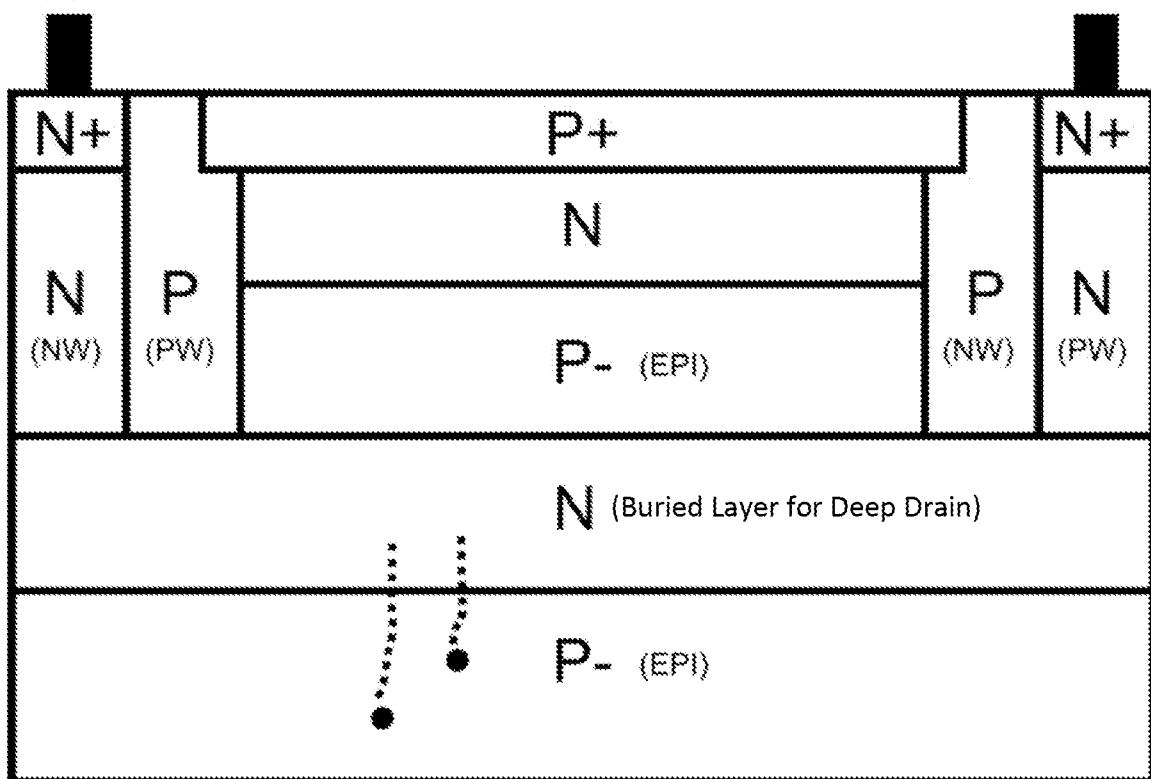

Charge carriers deeper than one micron below a surface of a semiconductor substrate may be rejected.

25 Charge carriers deeper than one micron below the surface of a semiconductor substrate may be rejected at least partially by an implant below a photodiode of the photodetection region.

The implant may provide a deep shield or a deep drain.

The implant may be N-type or P+-type.

30 Charge carriers deeper than one micron below the surface of a semiconductor substrate may be rejected by a drift field below the surface of the semiconductor substrate.

The photodetection region may be formed in an epitaxial region that is less than two microns deep.

The photodetection region may be an epitaxial region comprising a photodiode.

Charge carriers in the photodiode may be transferred to a rejection region during a rejection period, then a first potential barrier to a first charge carrier storage region may be lowered, then a second potential barrier to a second charge carrier storage region may be lowered.

5 The first potential barrier may be controlled by a first electrode and the second potential barrier may be controlled by a second electrode.

10 The at least one charge carrier storage region may comprise a plurality of charge carrier storage regions.

15 The foregoing summary is provided by way of illustration and is not intended to be limiting.

#### BRIEF DESCRIPTION OF DRAWINGS

Some embodiments of the present invention are hereinafter described, by way of example only, with reference to the accompanying drawings. In the drawings, each identical 5 or nearly identical component that is illustrated in various figures is represented by a like reference character. For purposes of clarity, not every component may be labeled in every drawing. The drawings are not necessarily drawn to scale, with emphasis instead being placed on illustrating various aspects of the techniques and devices described herein.

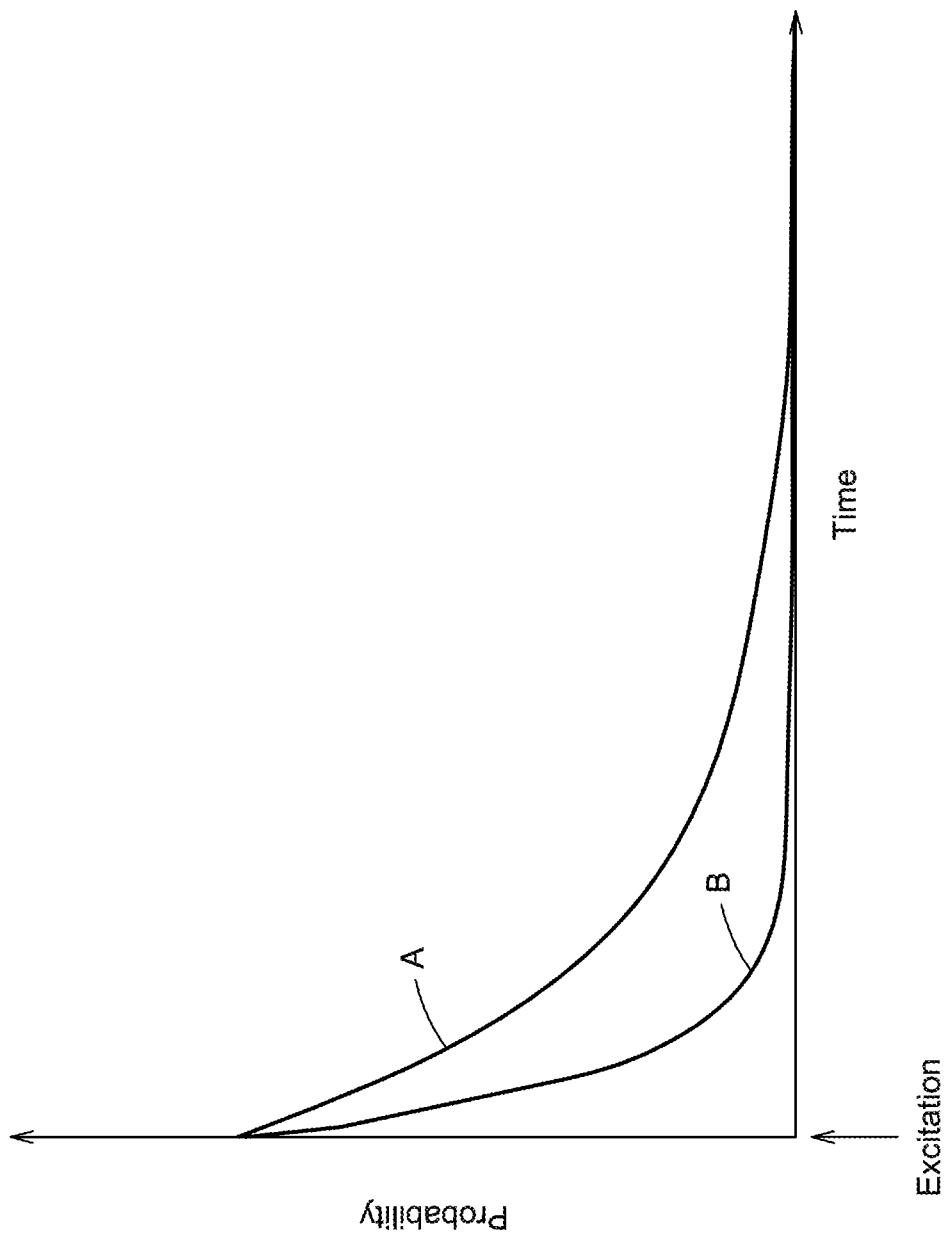

20 FIG. 1A plots the probability of a photon being emitted as a function of time for two markers with different lifetimes.

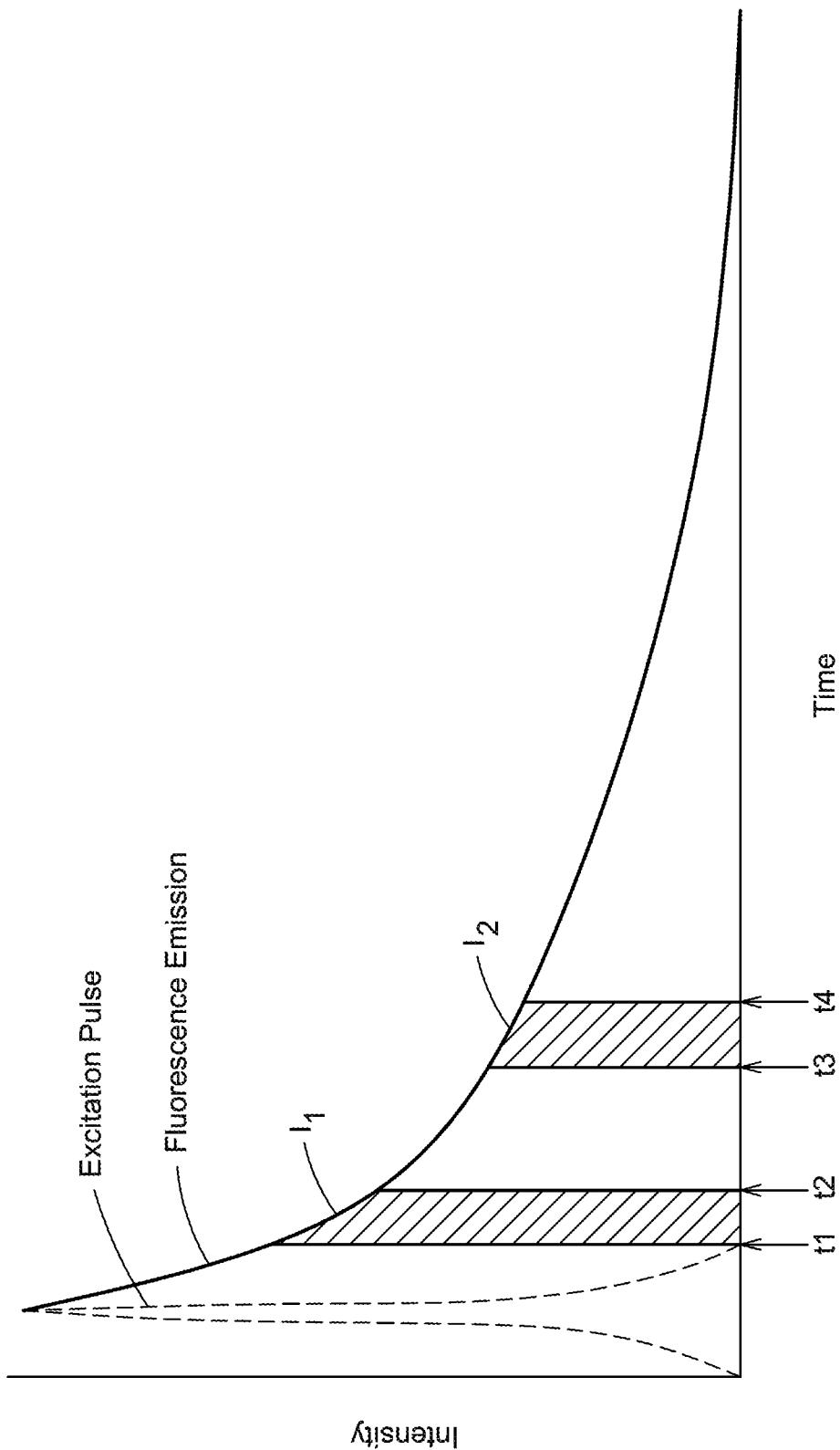

FIG. 1B shows example intensity profiles over time for an example excitation pulse (dotted line) and example fluorescence emission (solid line).

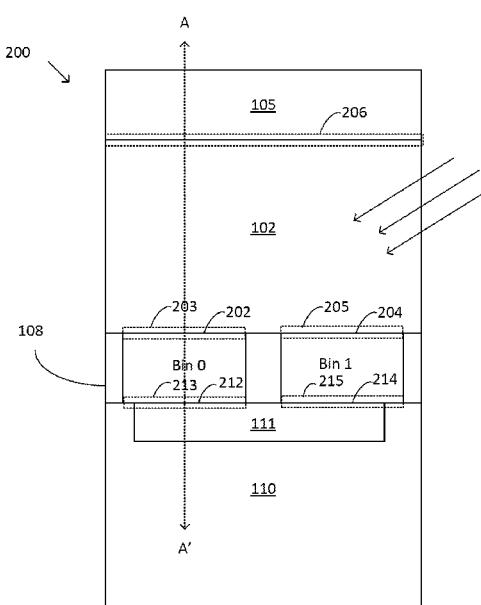

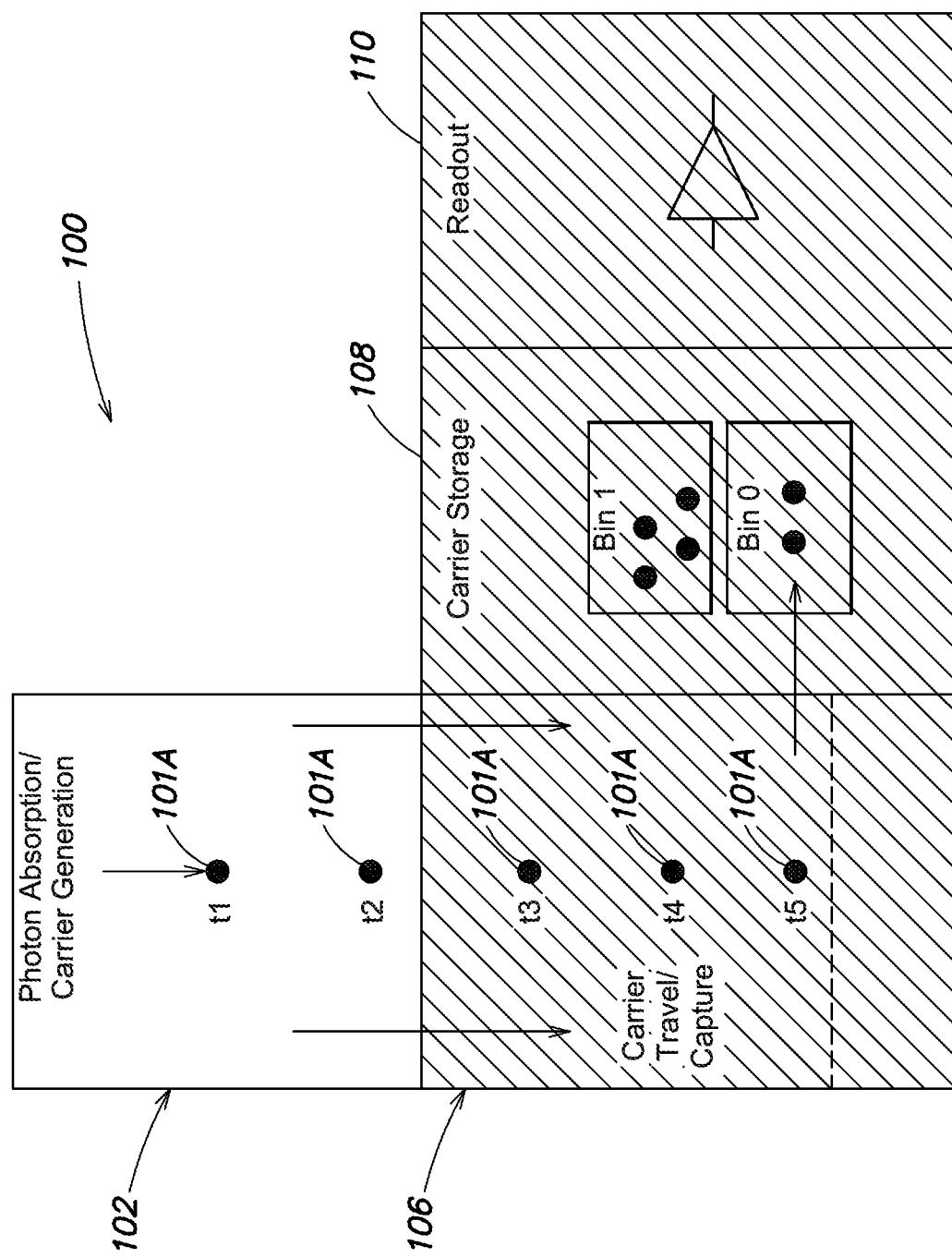

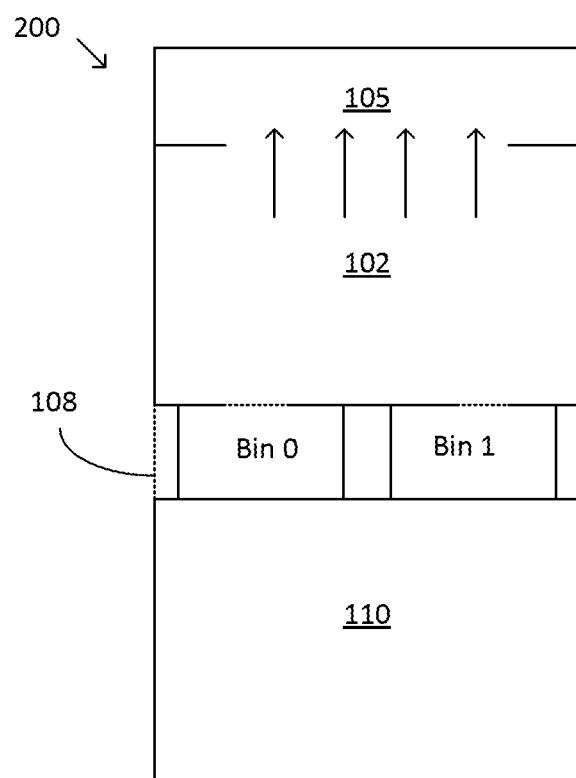

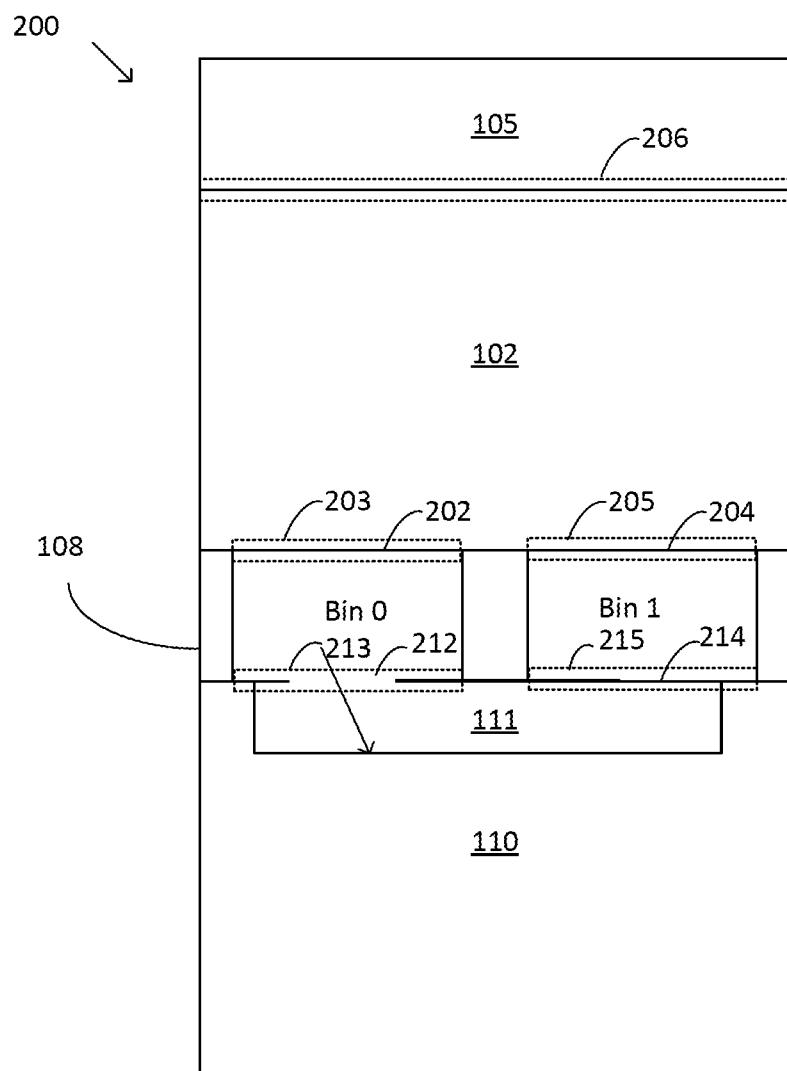

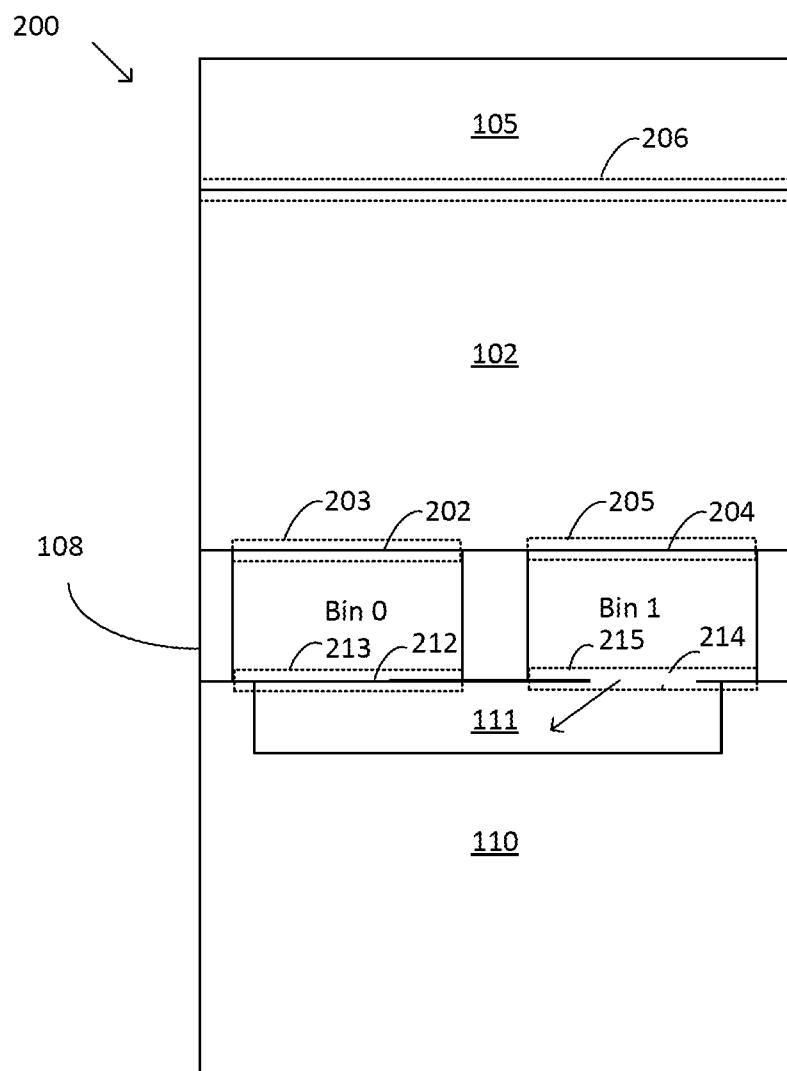

FIG. 2A shows a diagram of a pixel of an integrated photodetector.

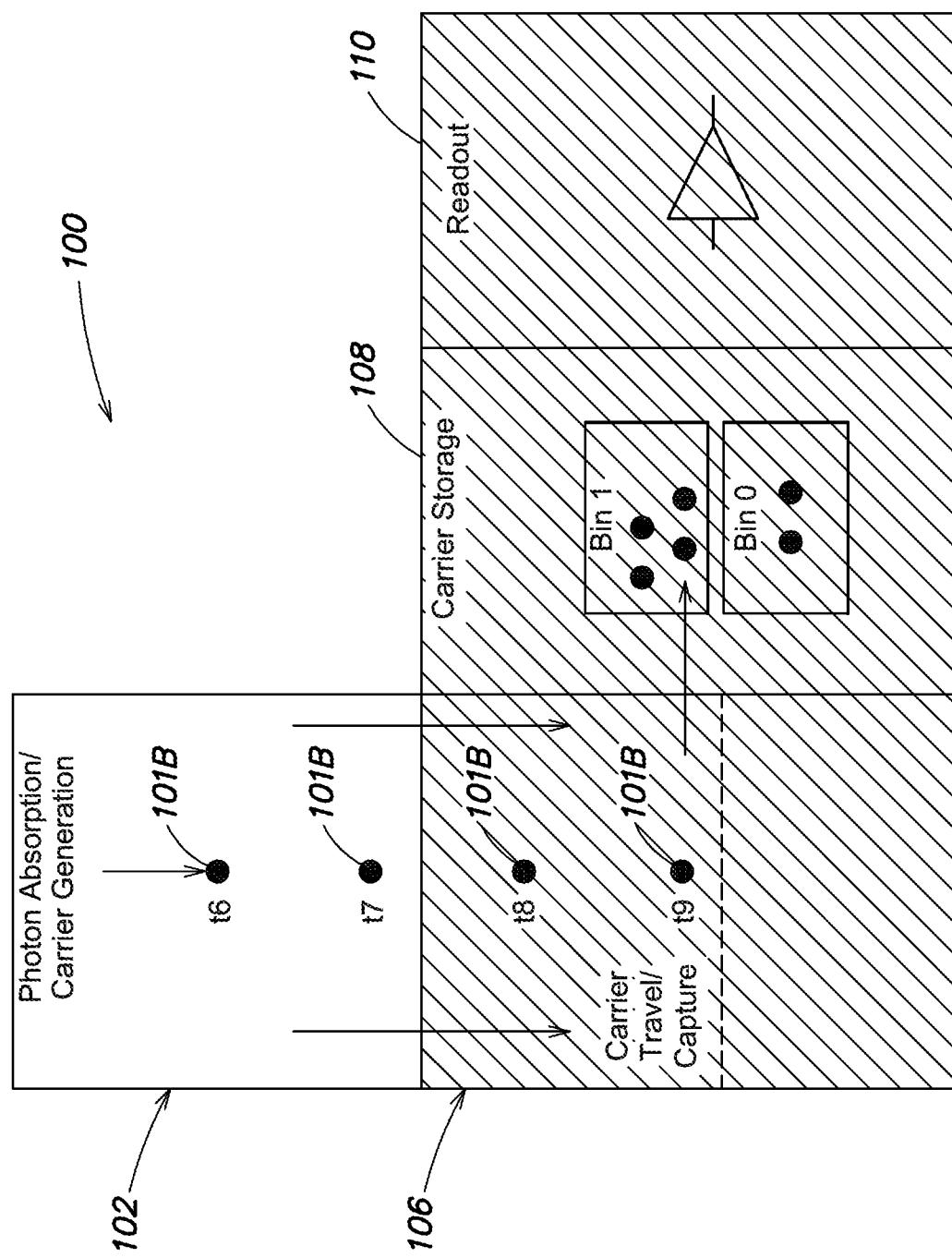

5 FIG. 2B illustrates capturing a charge carrier at a different point in time and space than in FIG. 2A.

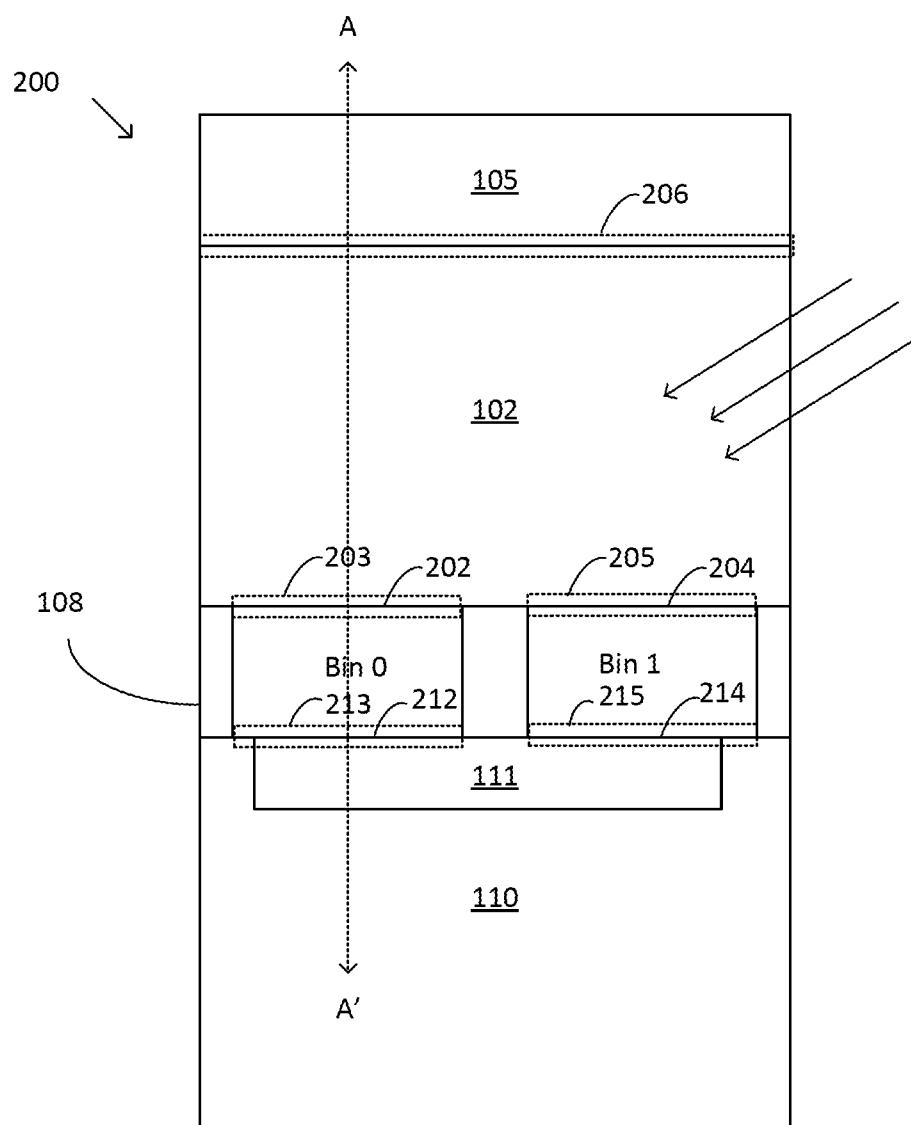

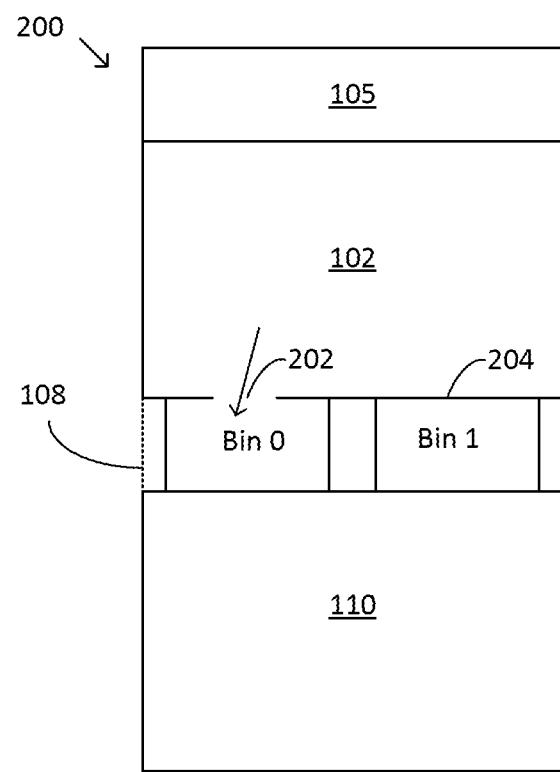

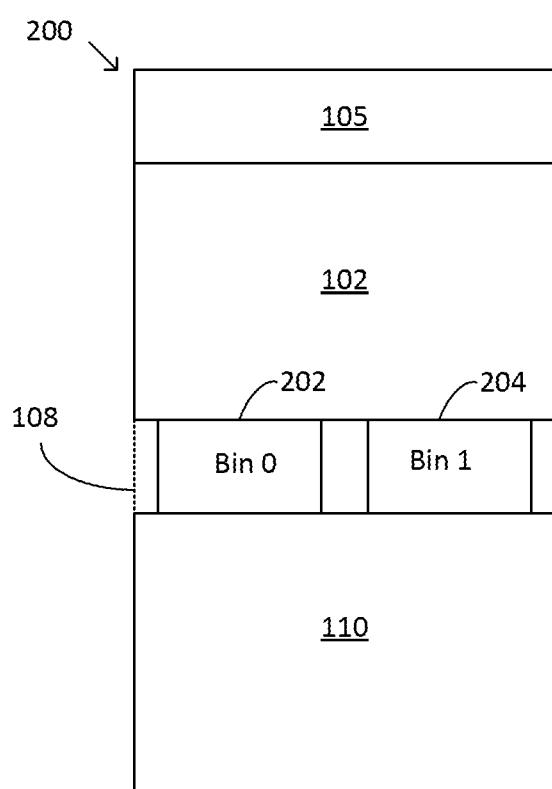

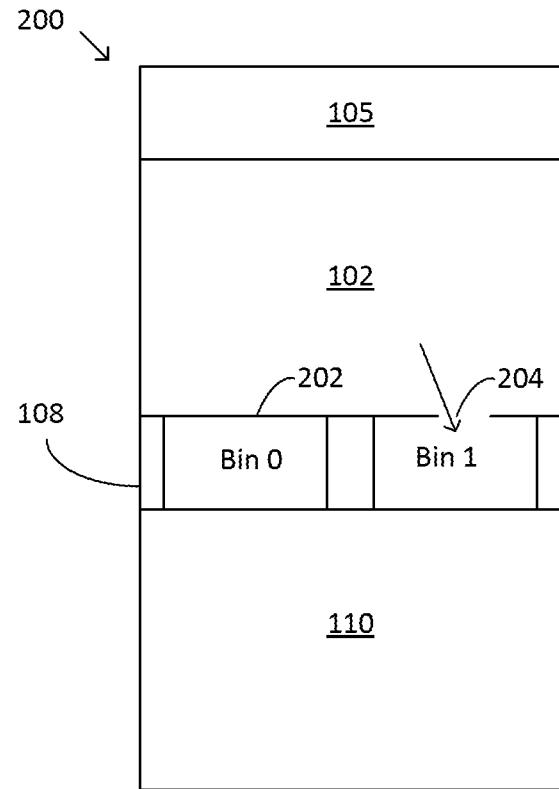

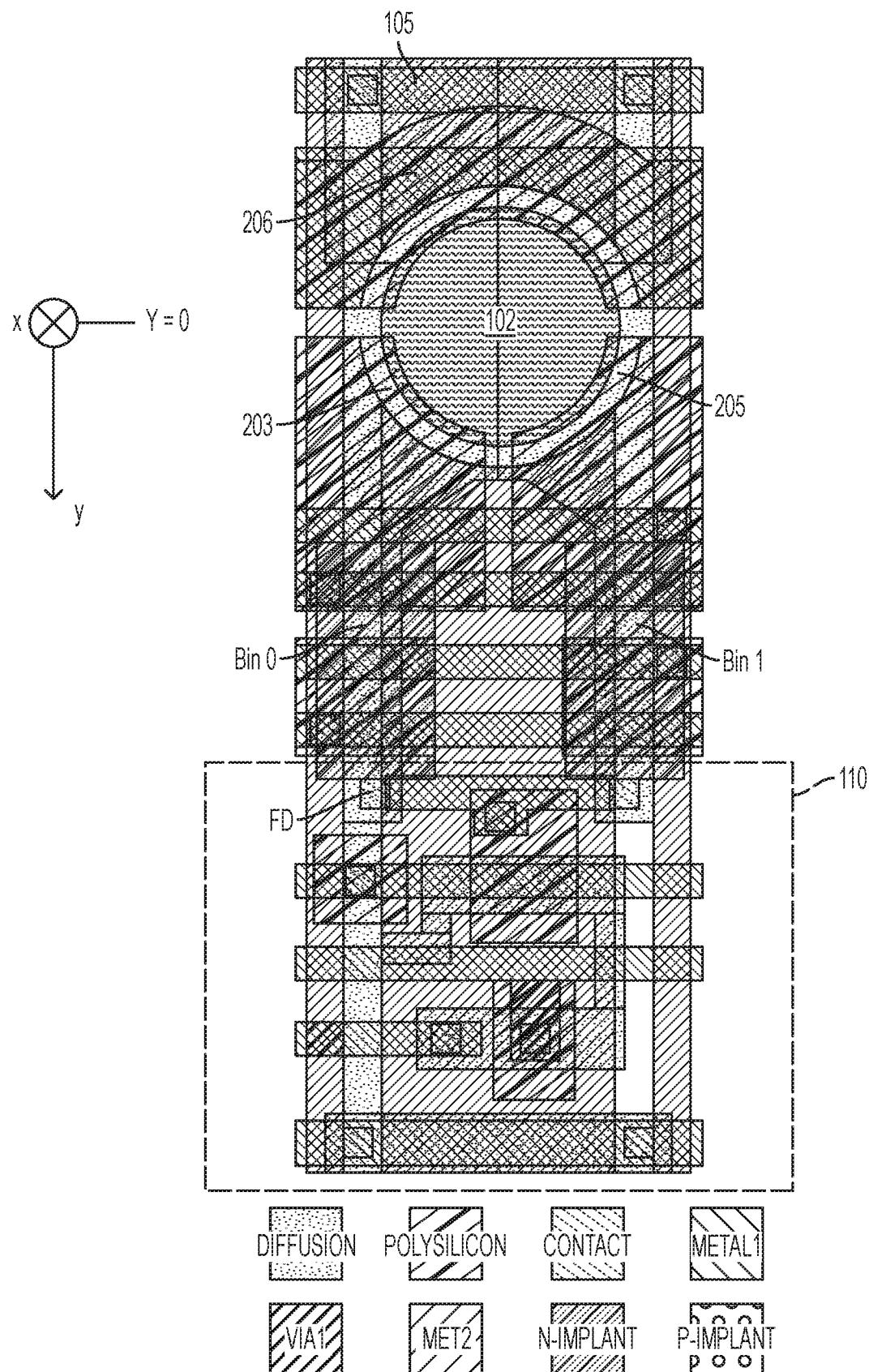

FIG. 3 shows an example of a direct binning pixel.

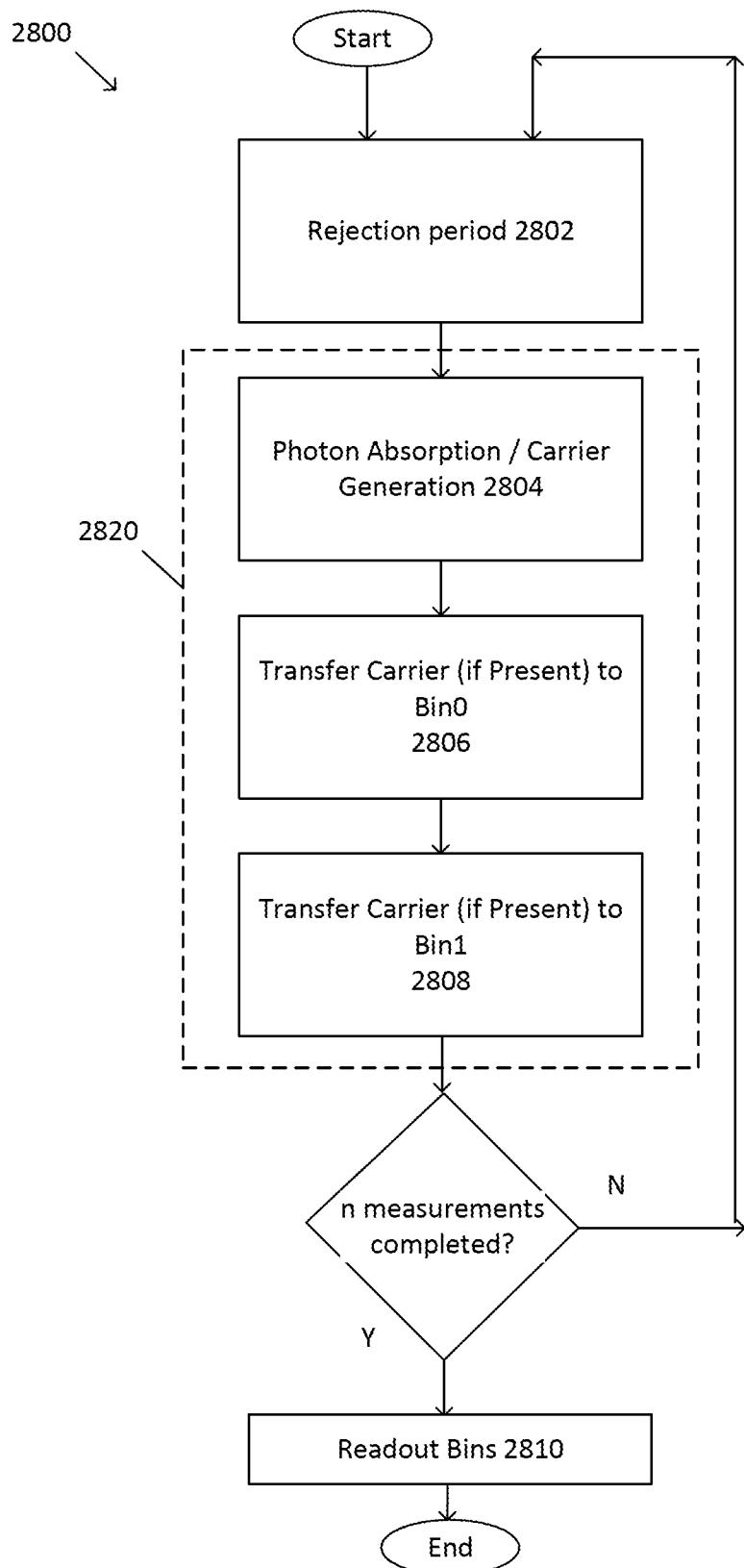

FIG. 4 shows a flowchart of a method of operating a direct binning pixel.

FIG. 5A-F show the direct binning pixel at various stages of the method of FIG. 4.

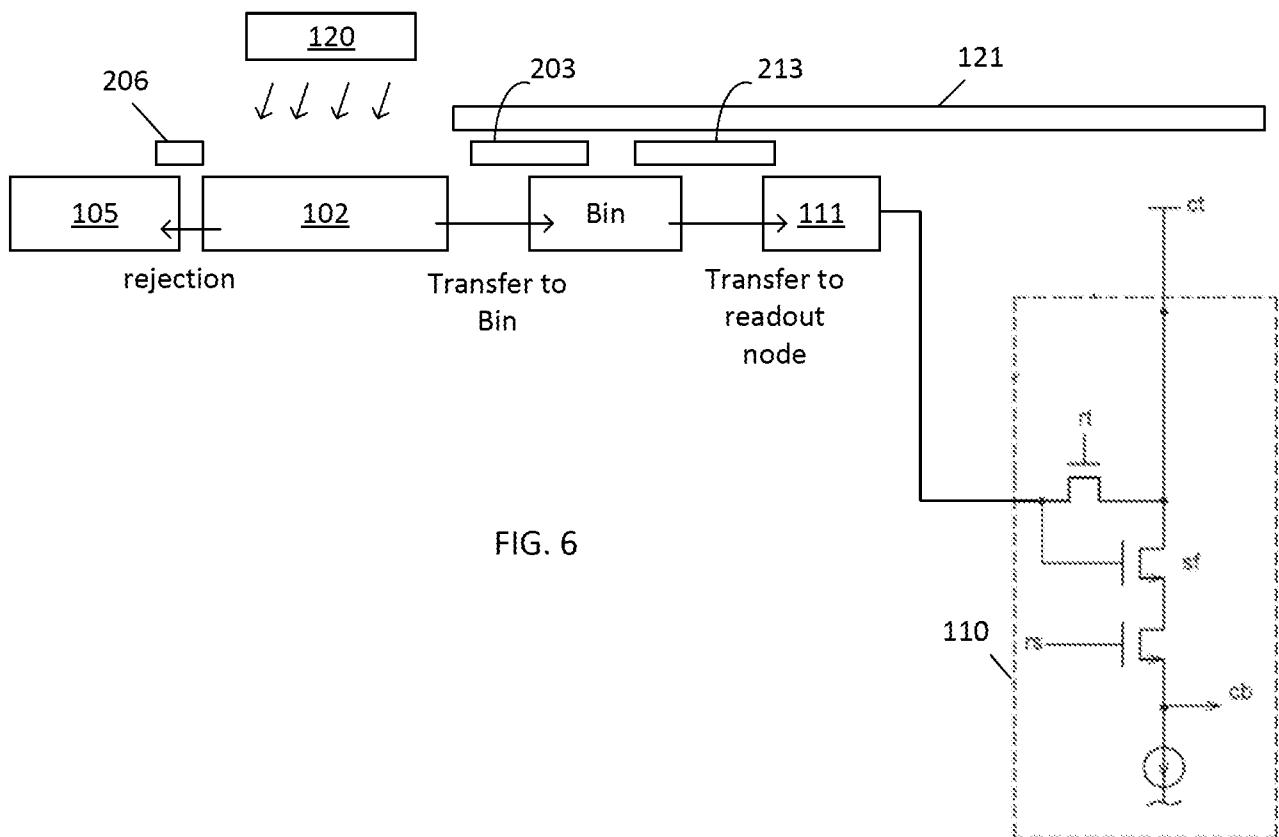

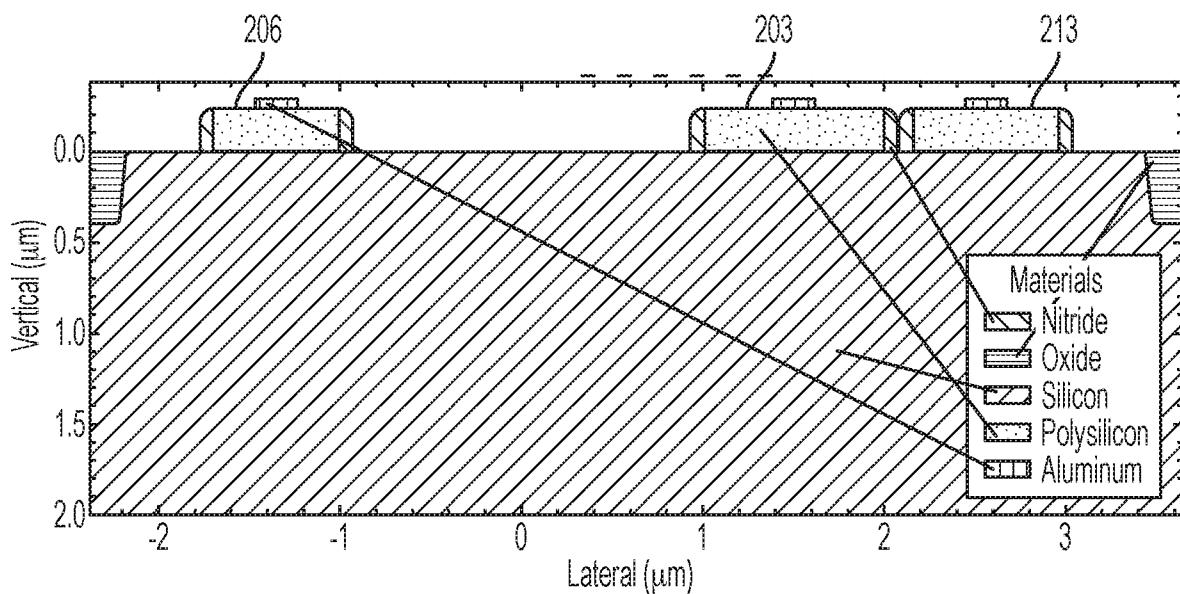

FIG. 6 shows a cross-sectional view of a direct binning pixel.

10 FIG. 7 shows a split-doped electrode having a p+ region and an n+ region.

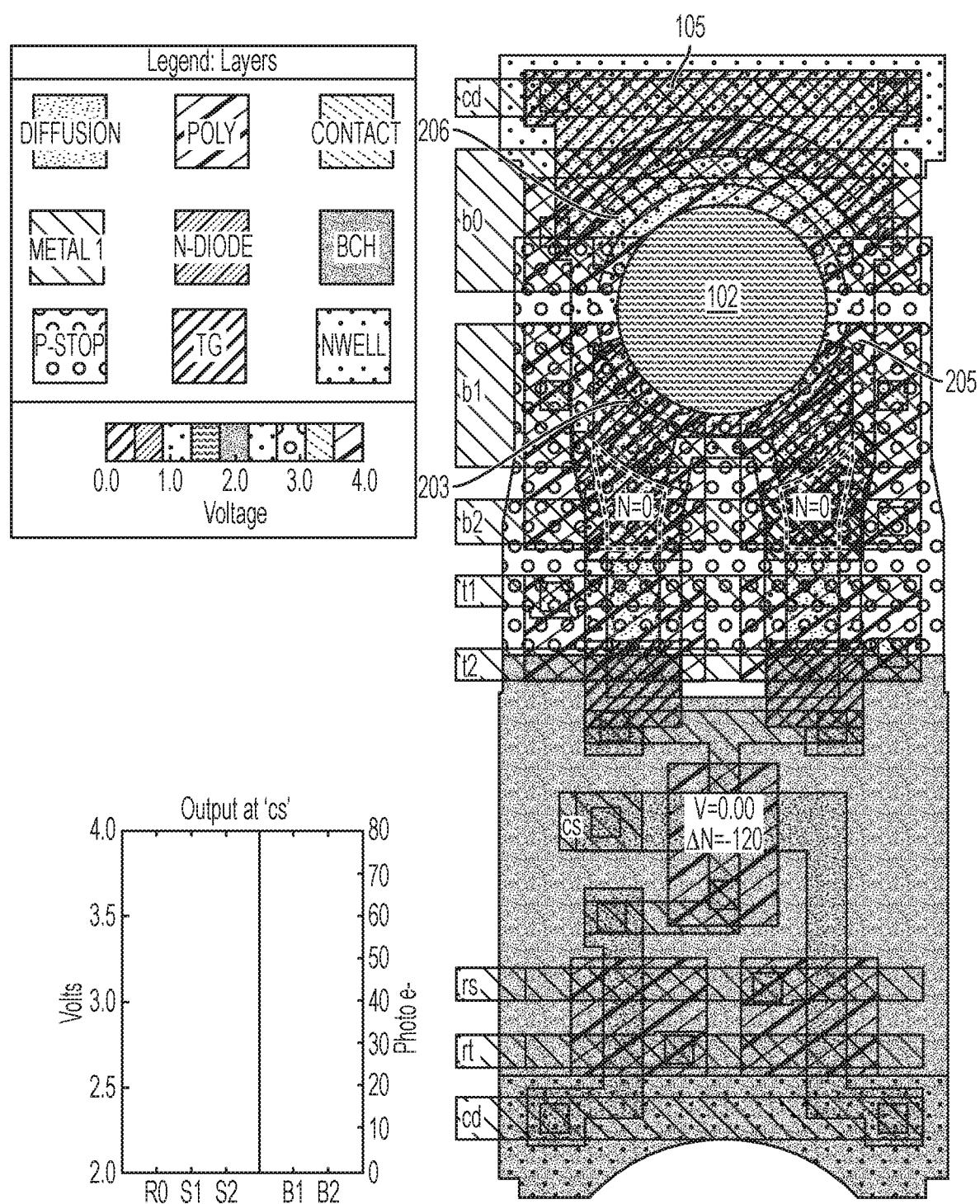

FIG. 8 shows a plan view of an example of a direct binning pixel.

FIG. 9 shows a plan view of another example of a direct binning pixel.

FIG. 10 shows the potential in the direct binning pixel during the rejection period.

15 FIG. 11 shows the potential in the direct binning pixel during a period in which potential barriers to the rejection region and the bins are raised.

FIG. 12 shows the potential in the direct binning pixel in a period where charge may be transferred to a bin.

FIG. 13 shows transfer of the charge stored in a bin to the floating diffusion FD by lowering a potential barrier produced by a transfer gate.

20 FIG. 14 illustrates resetting the floating diffusion FD.

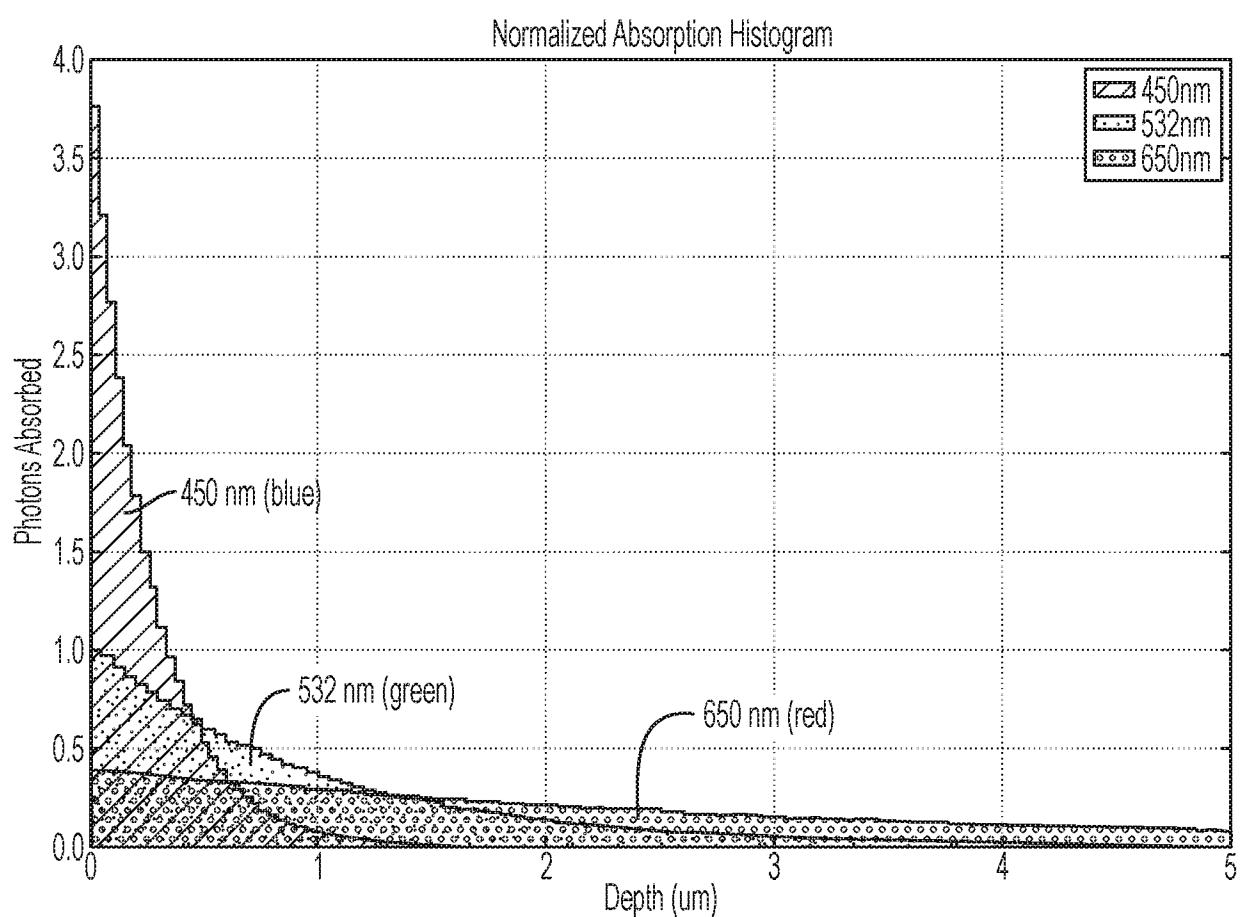

FIG. 15 shows a plot of absorption depth as a function of wavelength.

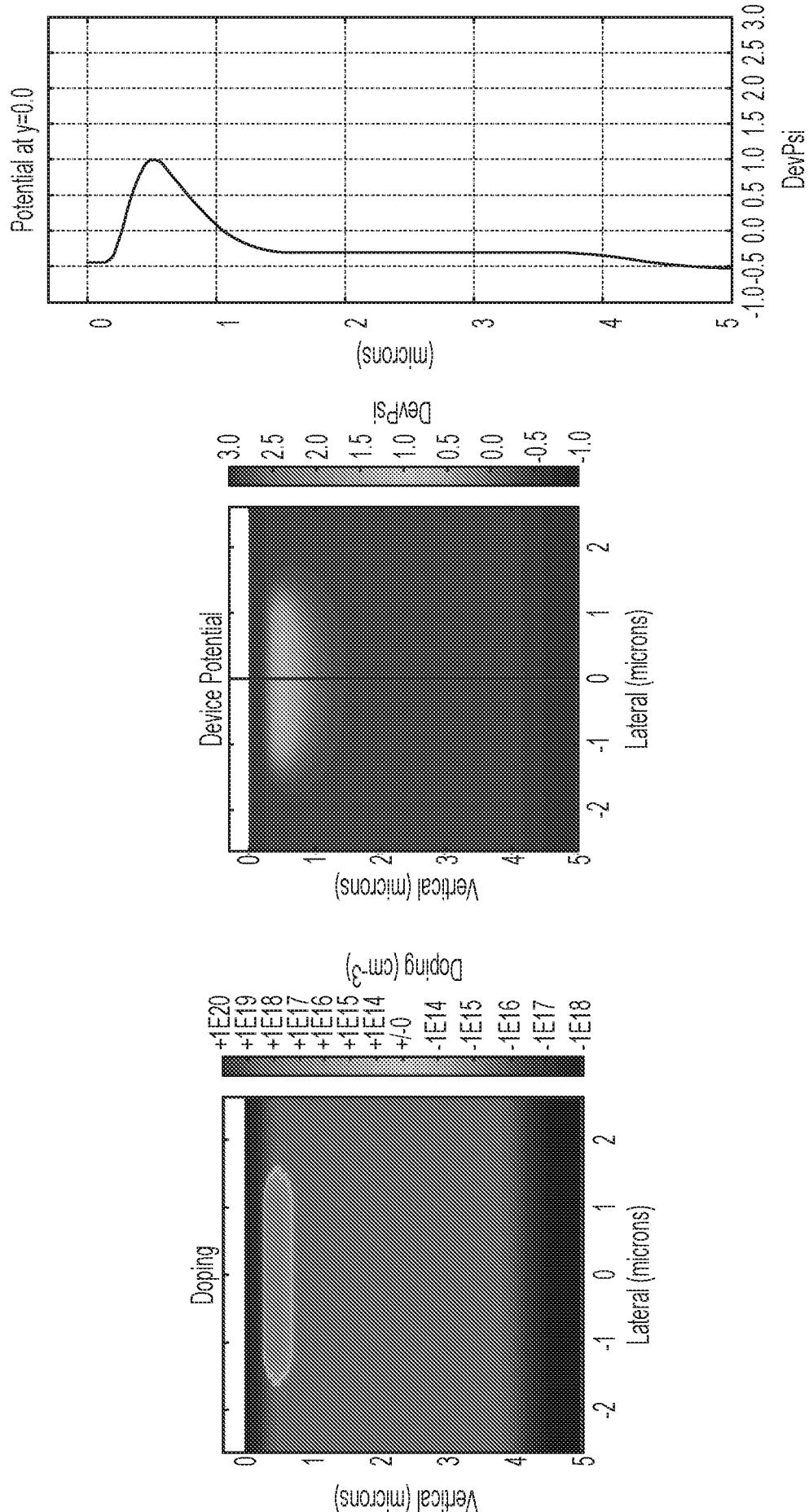

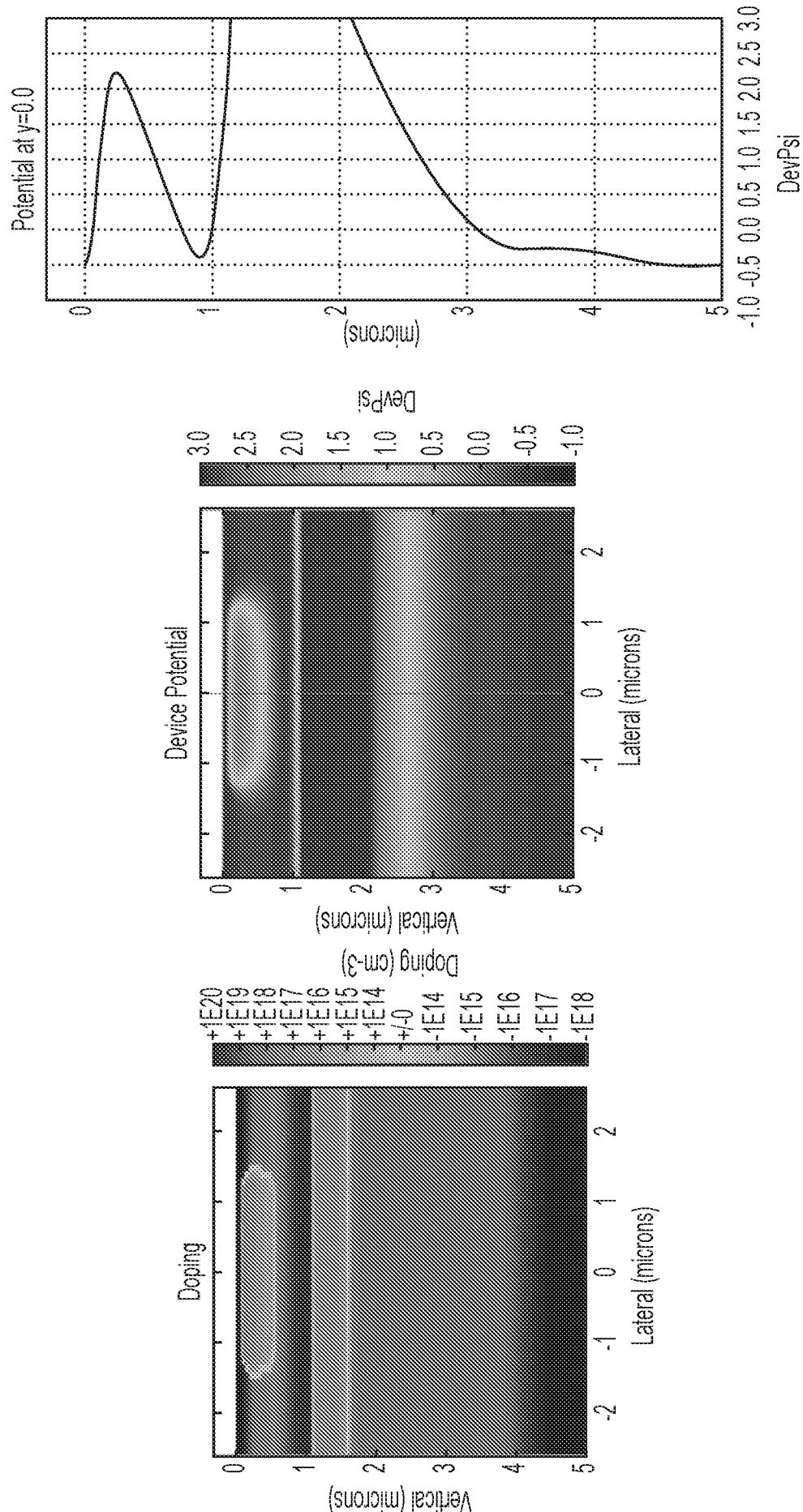

FIG. 16 shows the doping profile and potential for an example of a photodiode.

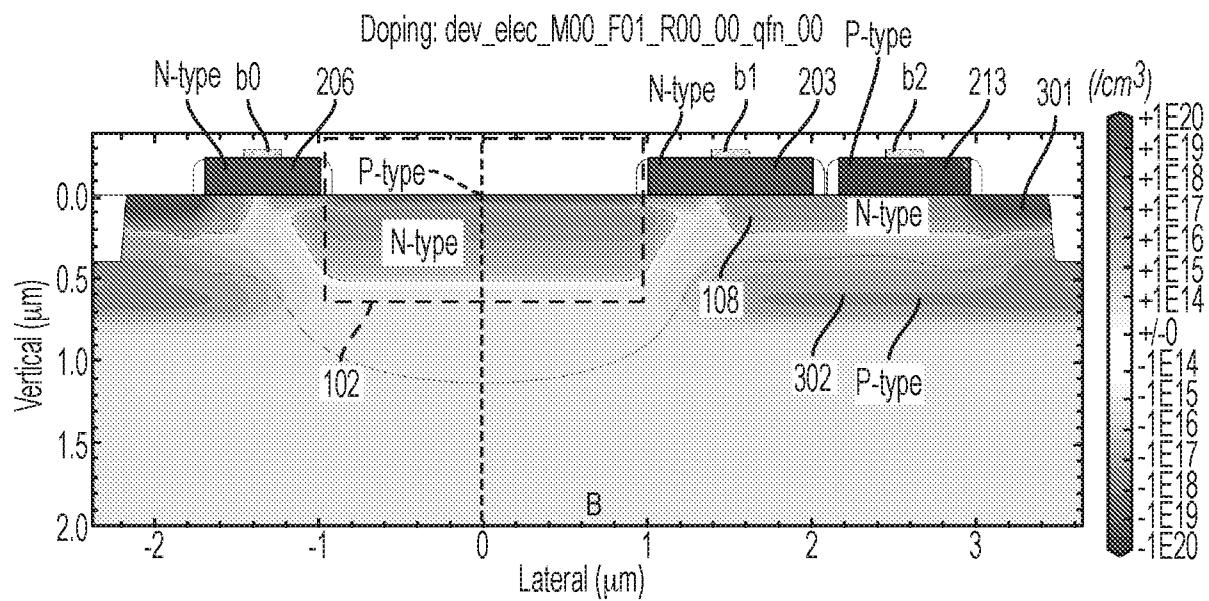

FIG. 17 shows a deep doped region that may prevent deep-generated carriers from reaching the surface.

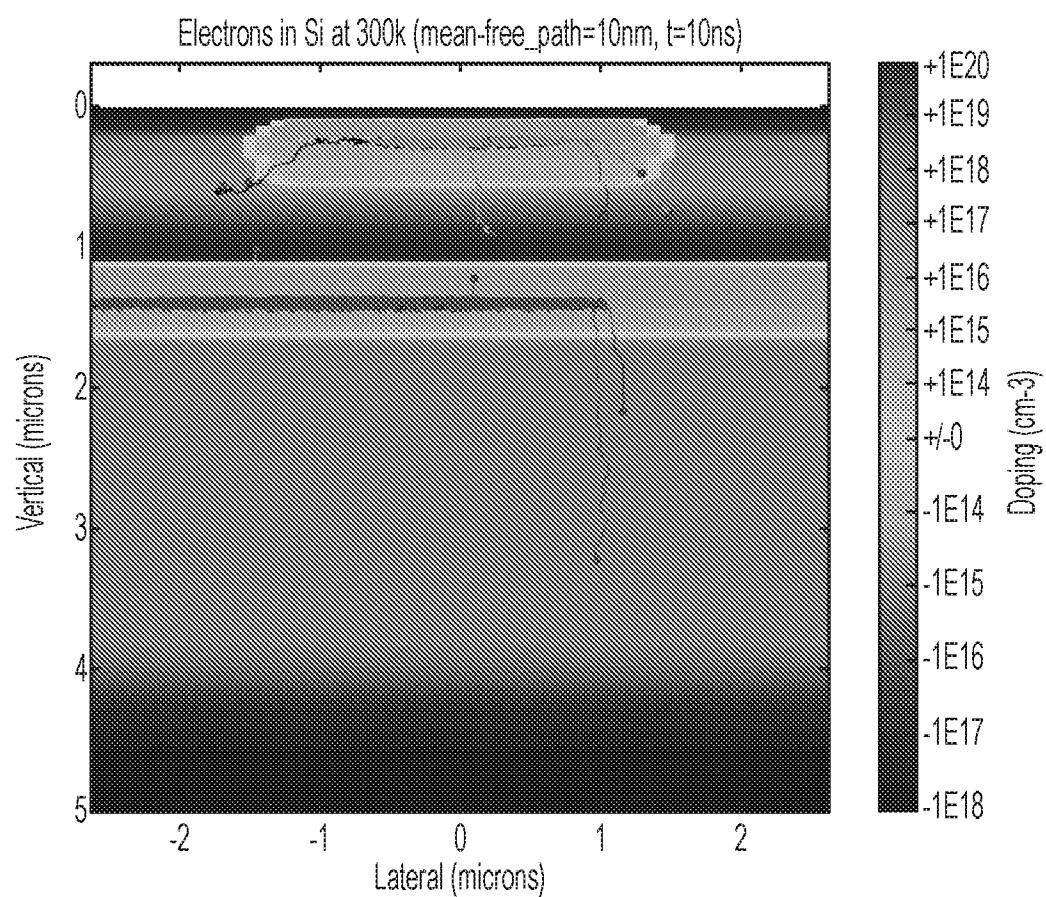

25 FIG. 18 shows a simulation of the electron motion for 10 ns, illustrating carriers are drawn into the deep n-well region.

FIG. 19 shows an N-type buried layer (deep drain) is biased at high potential.

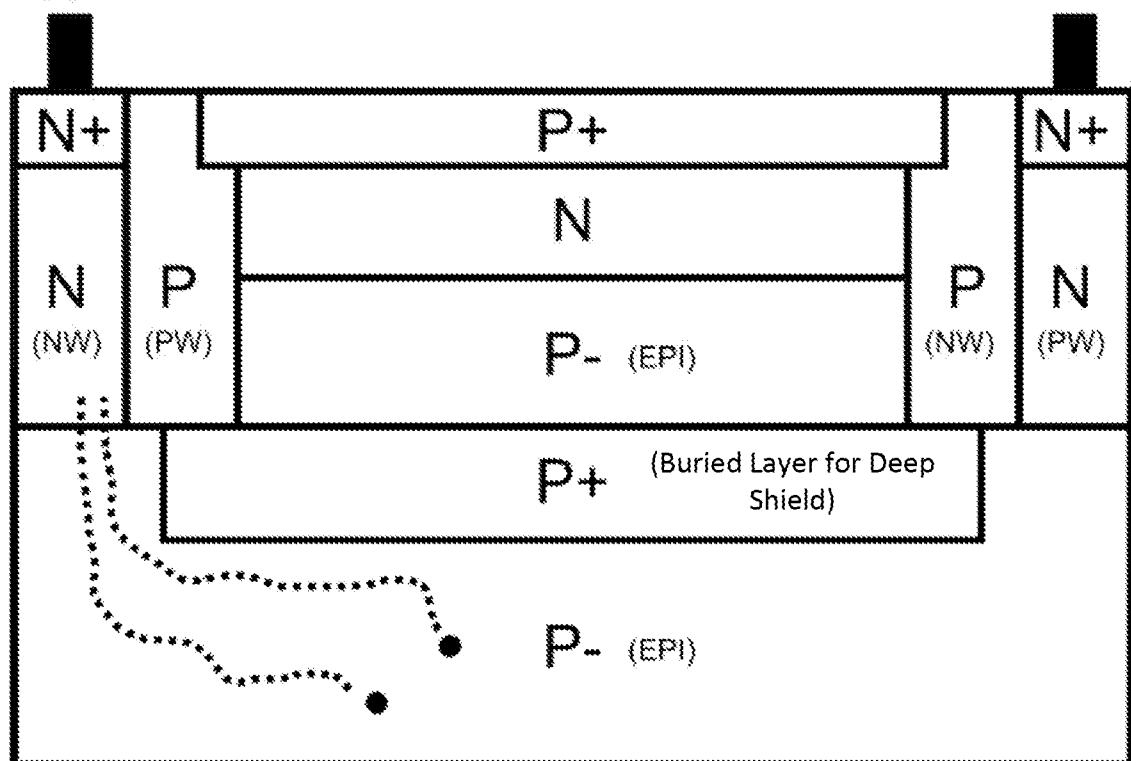

FIG. 20 shows a P+-type buried layer (deep shield) in contact with the substrate.

30 FIG. 21 shows examples of materials from which the integrated circuit may be fabricated.

FIG. 22 shows an example of a doping profile for a direct binning pixel, according to some embodiments.

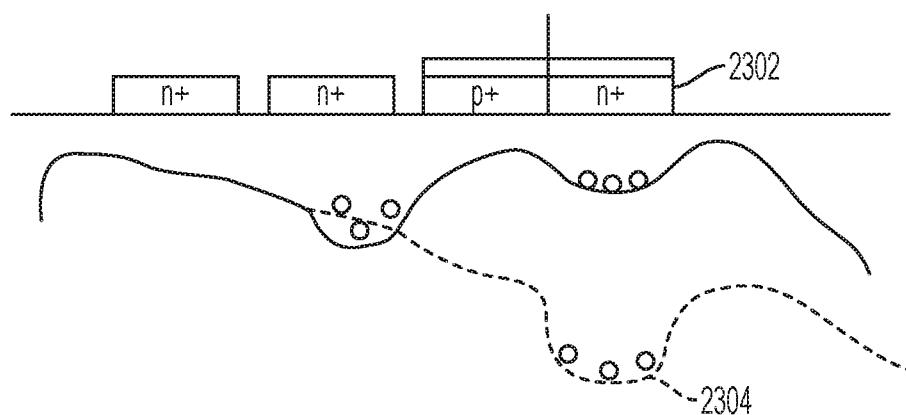

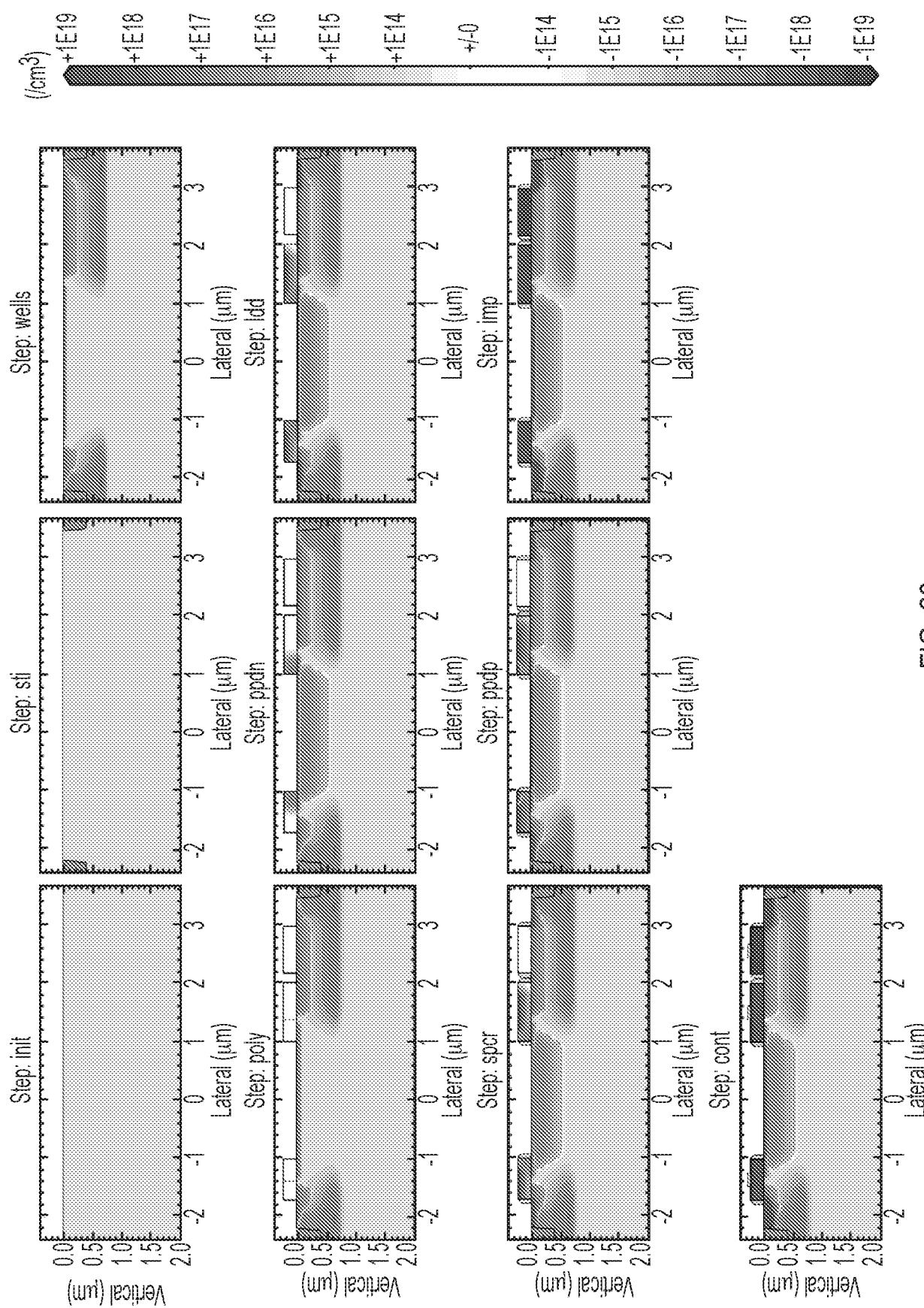

FIG. 23 shows an exemplary process sequence for forming the direct binning pixel with the doping profile illustrated in FIG. 22.

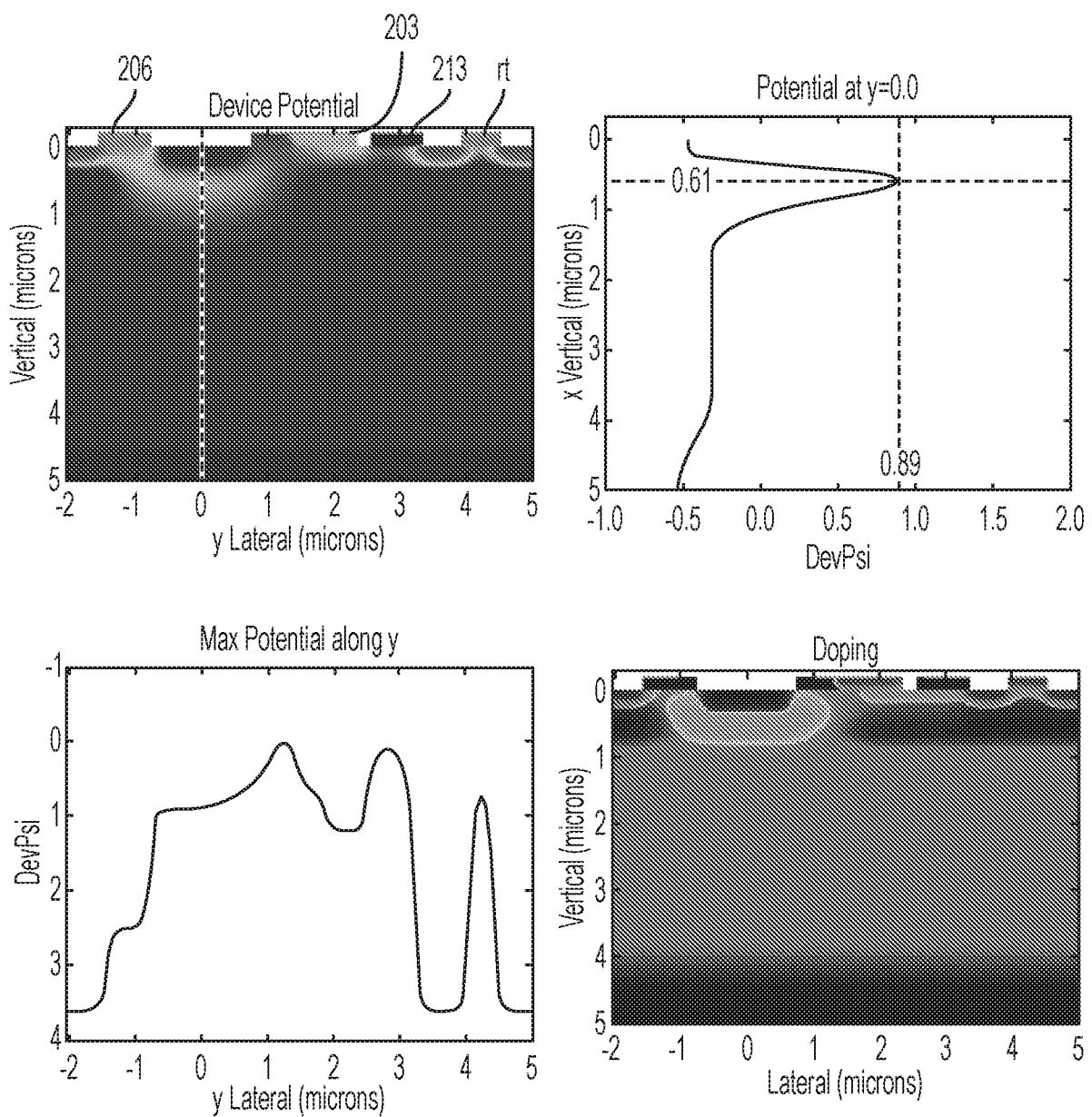

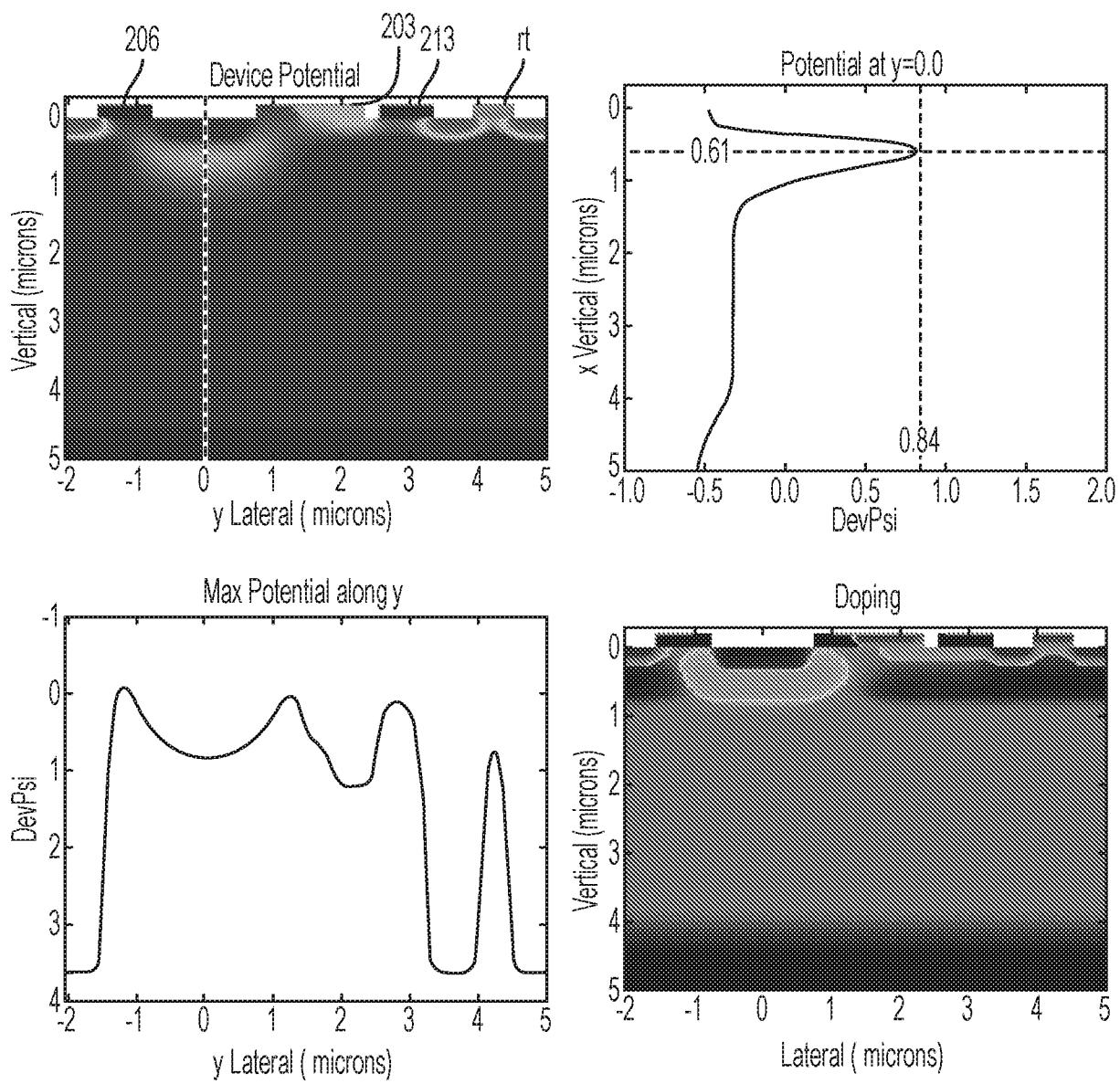

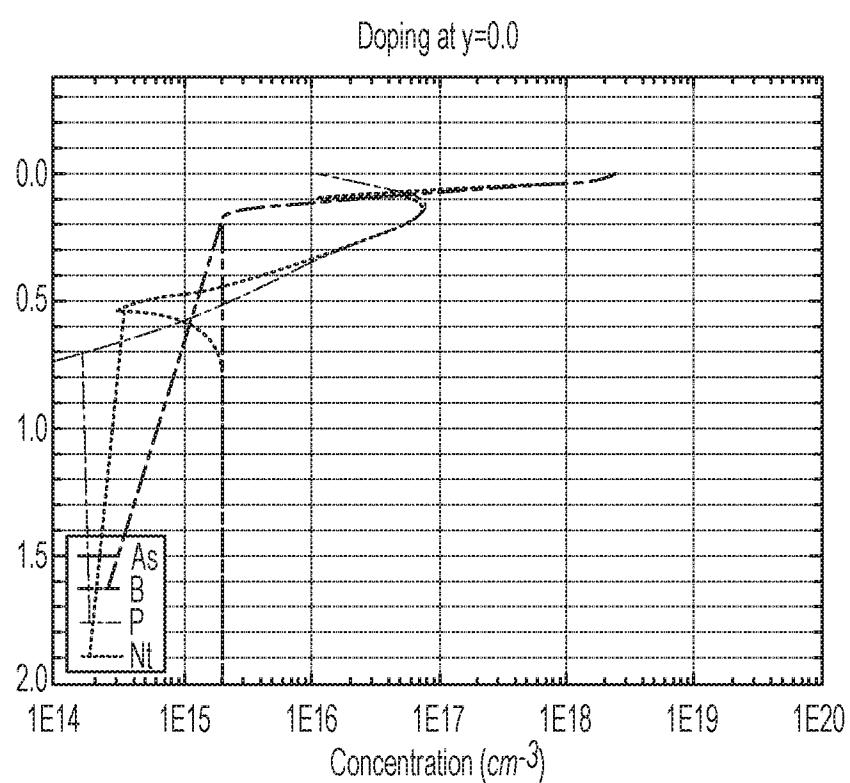

FIG. 24 shows a plot of an exemplary doping profile for arsenic, boron, phosphorous, and nitrogen along the line  $y = 0$  of FIG. 22.

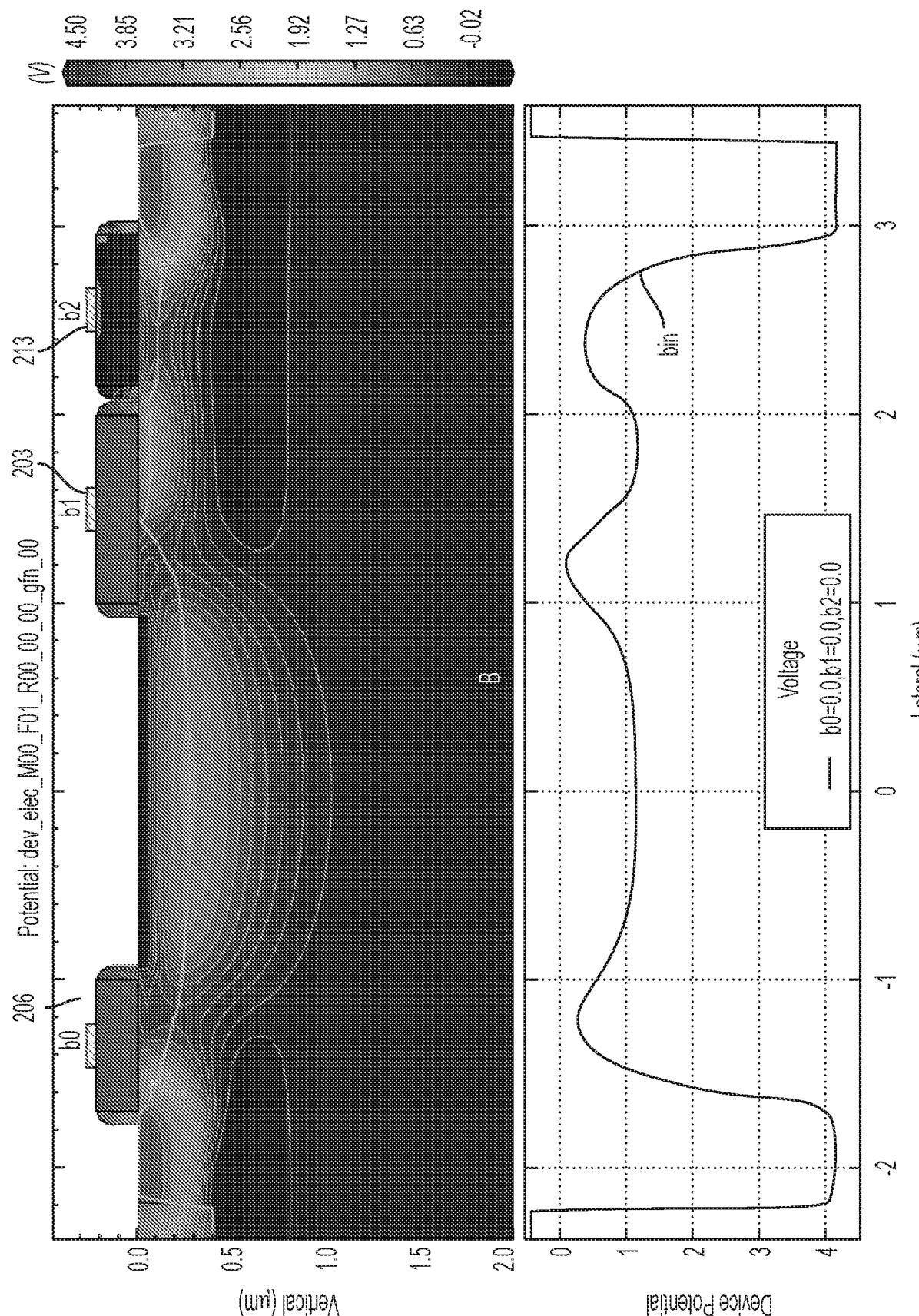

5 FIG. 25 shows a plot of electric potential in the pixel of FIG. 23 when all the barriers are closed by setting the voltages of all electrodes to 0V.

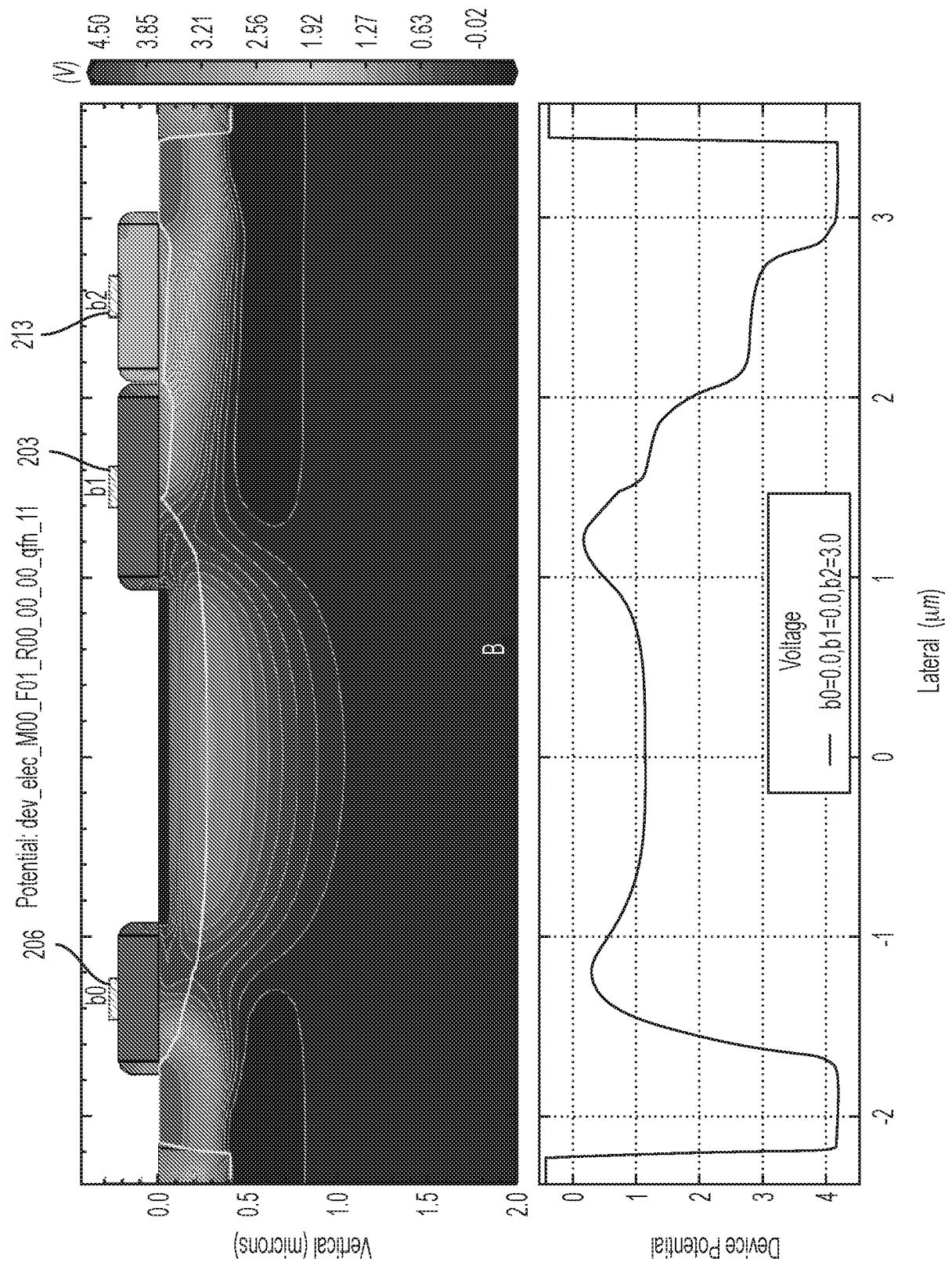

FIG. 26 shows a plot of the electric potential in the pixel of FIG. 23 when the voltage of electrode 213 is set to 3V.

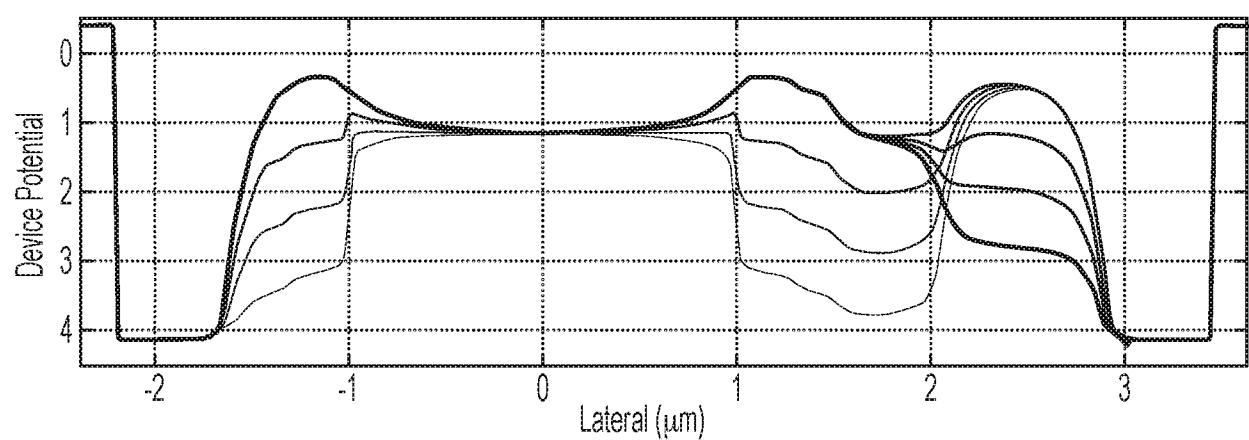

10 FIG. 27 shows curves of potential within the substrate as the voltages of the electrodes are varied.

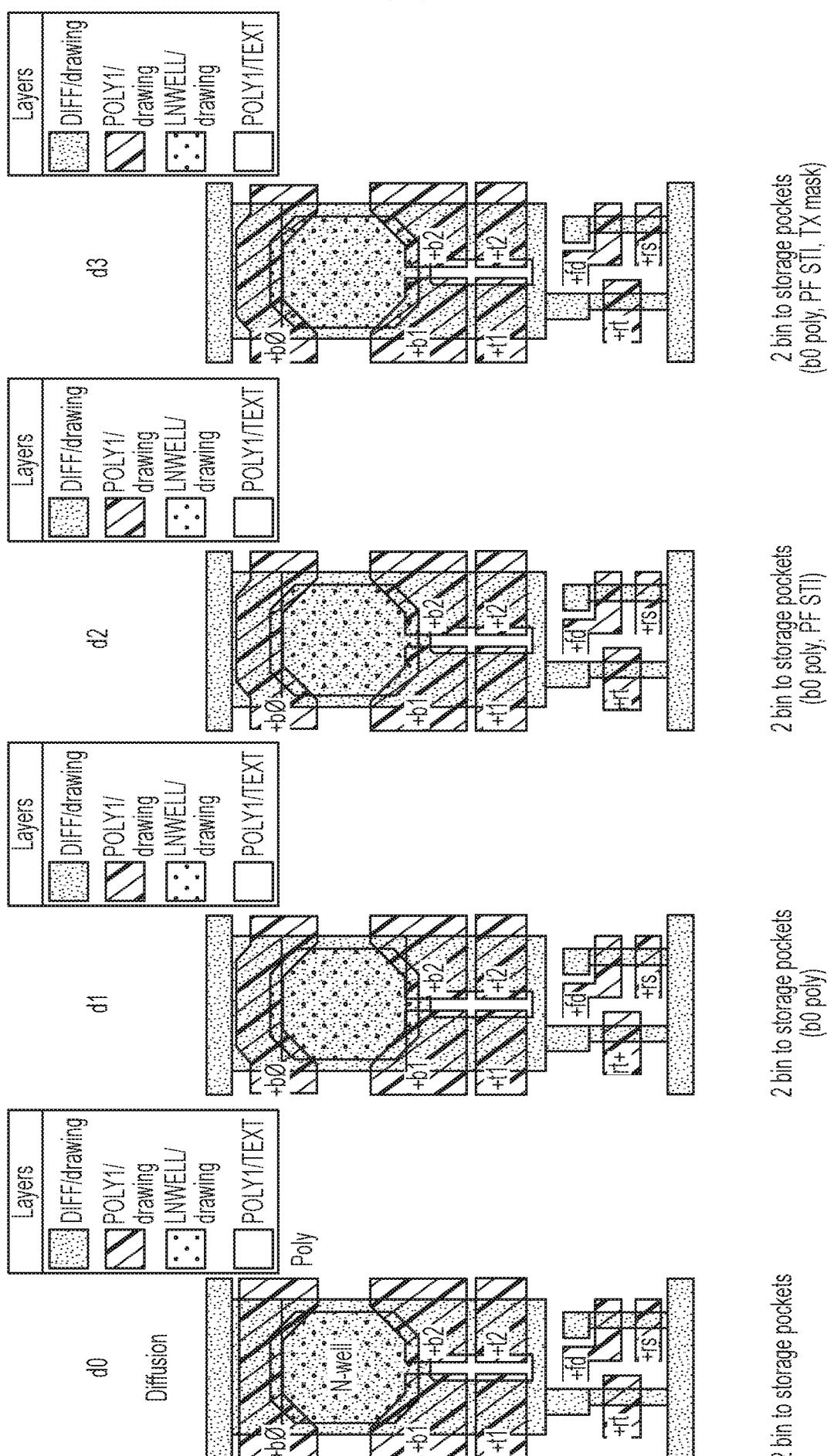

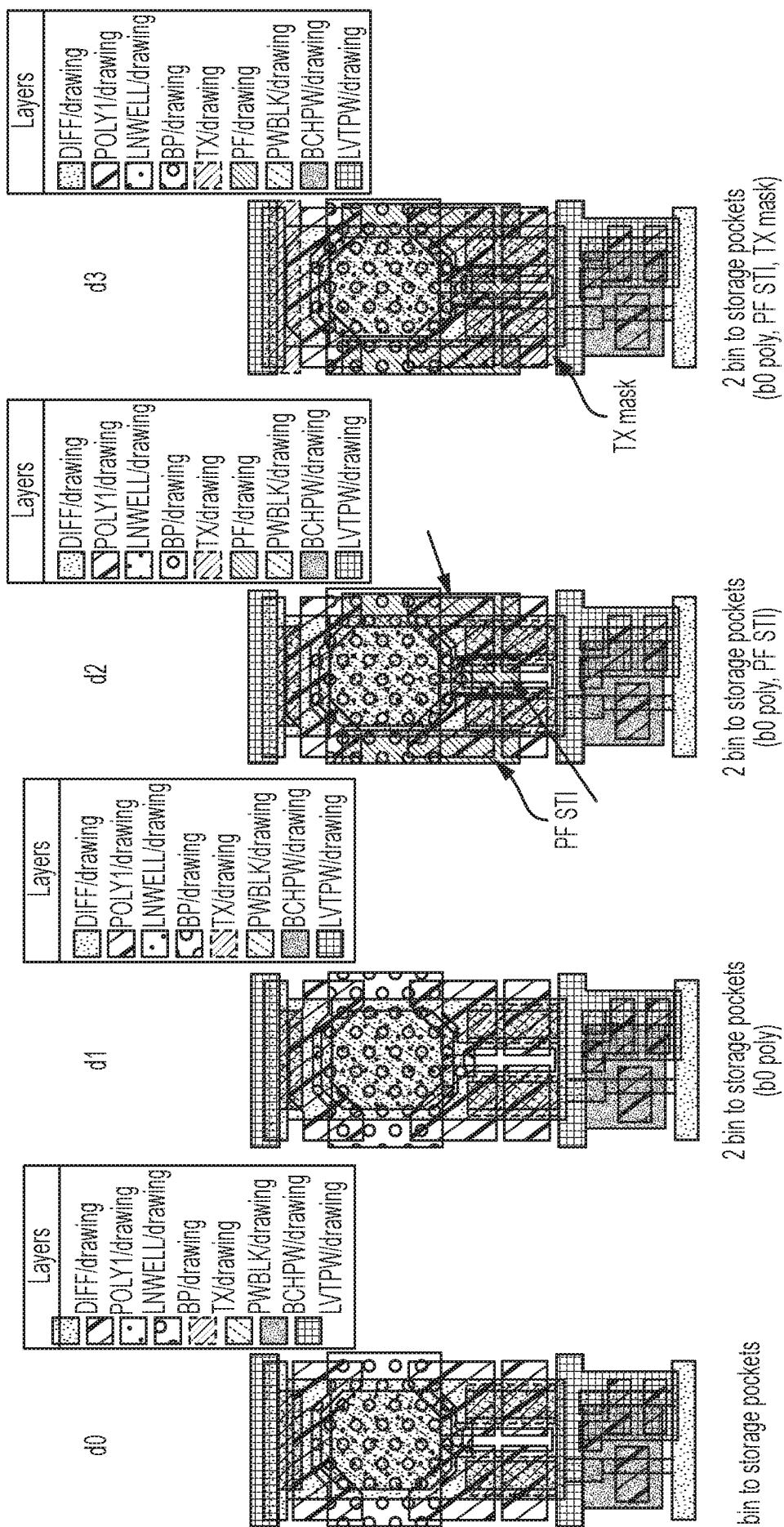

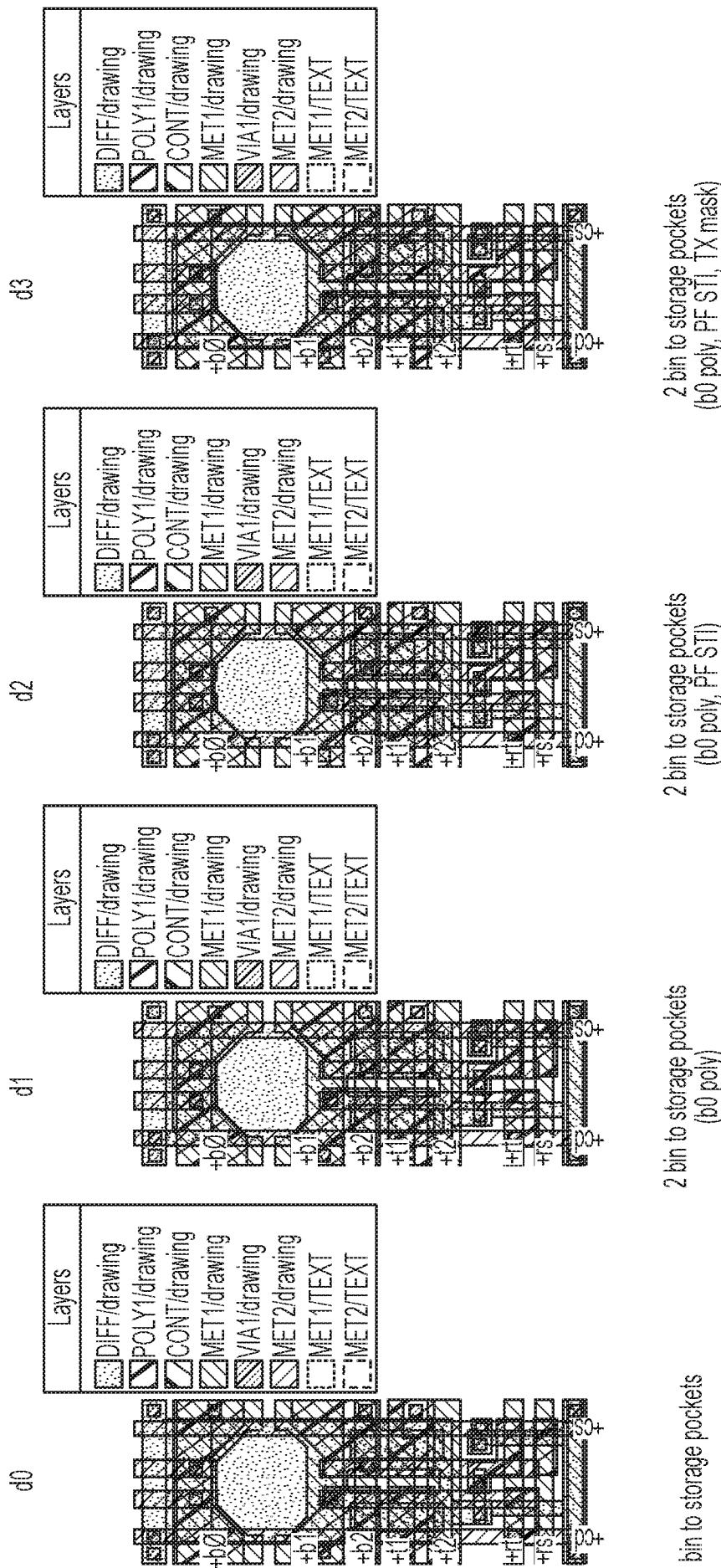

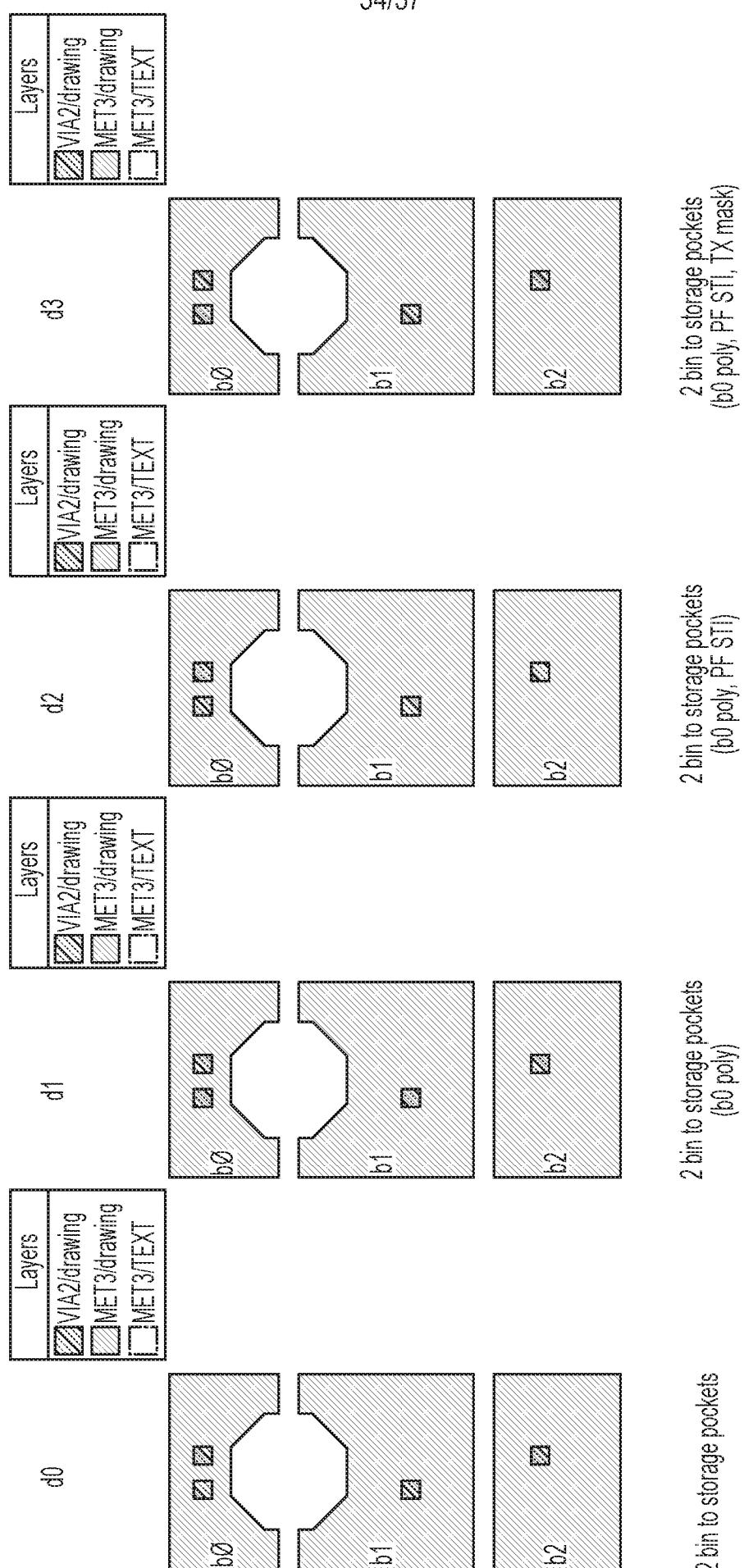

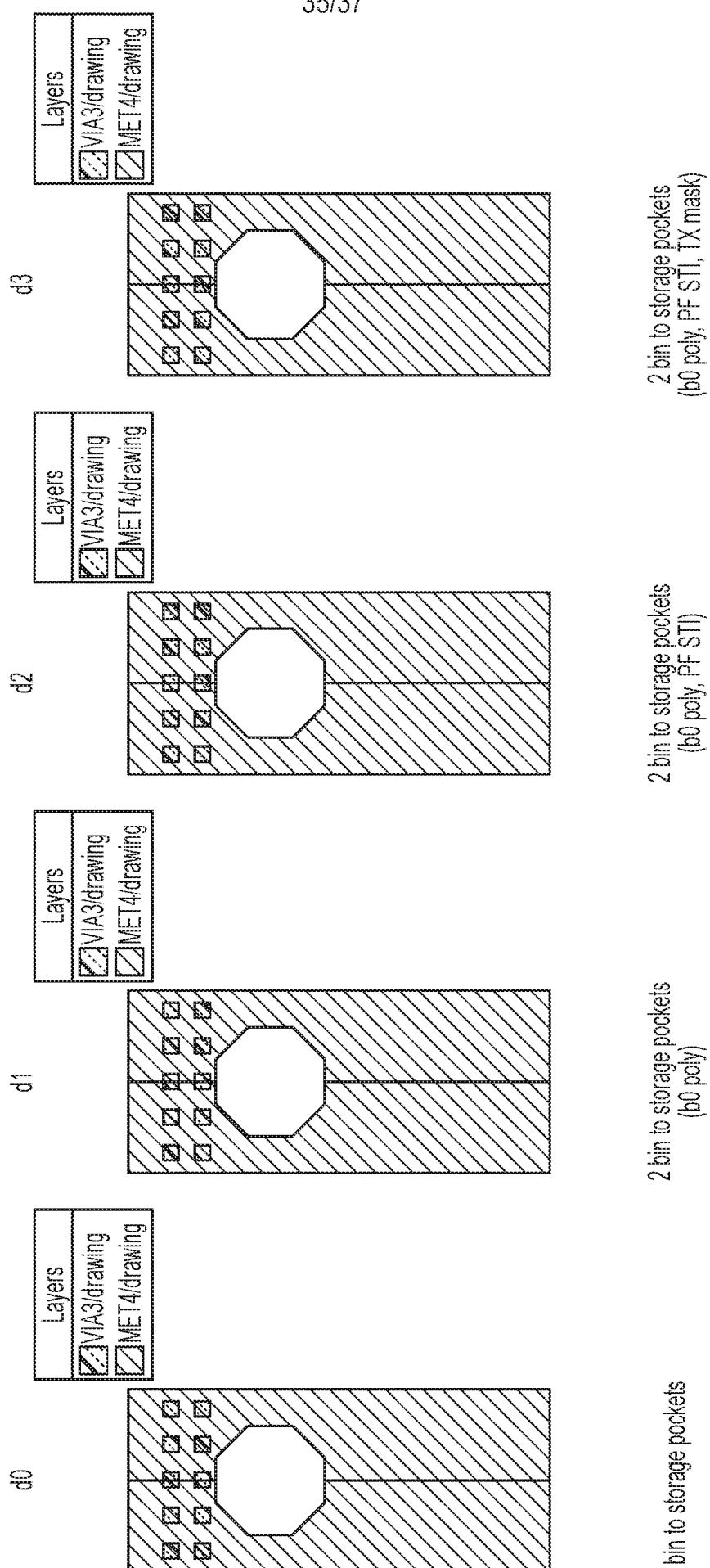

FIGS. 28-32 show an exemplary process of forming the photodetector and four different pixel designs d0-d3. FIG. 28 shows a first level, FIG. 29 shows a second level, FIG. 30 shows a third level, FIG. 31 shows a fourth level and FIG. 32 shows a fifth level.

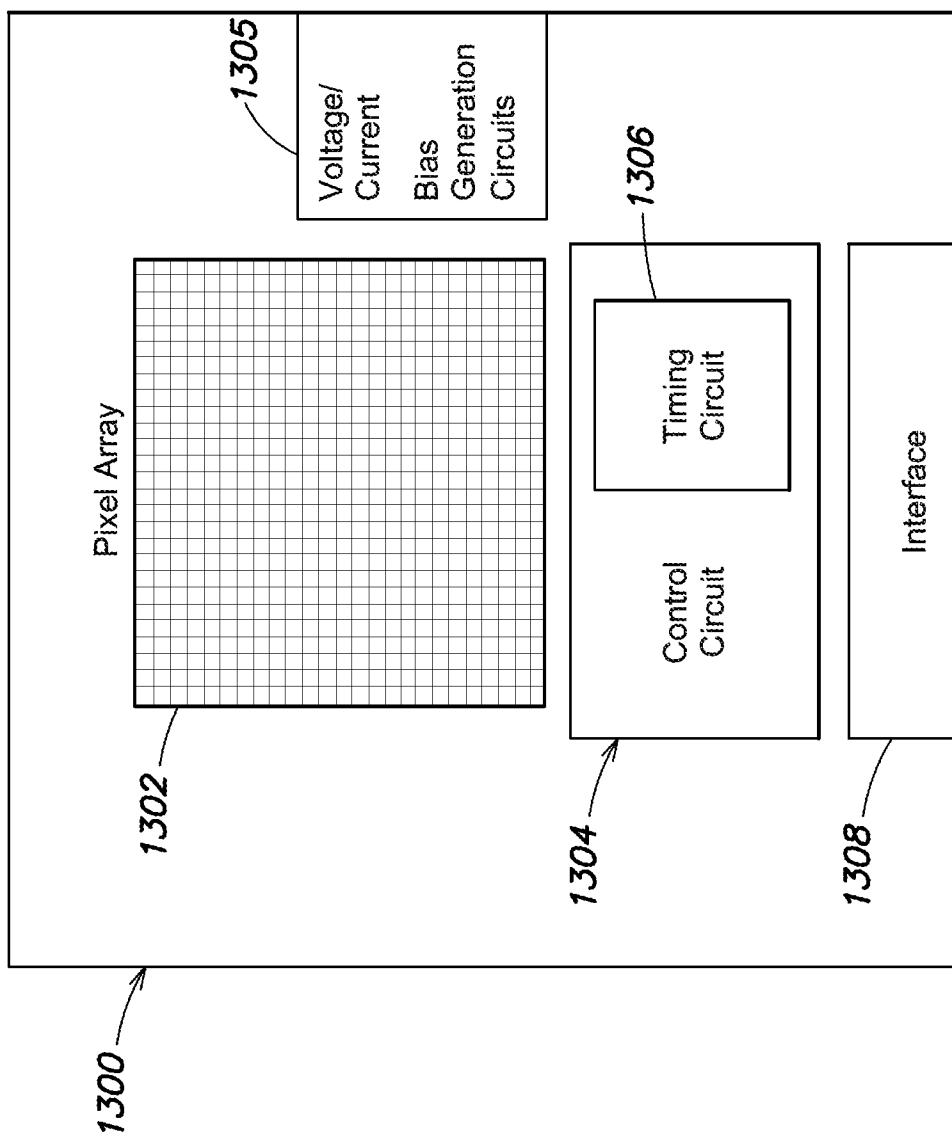

FIG. 33 shows a diagram of a chip architecture.

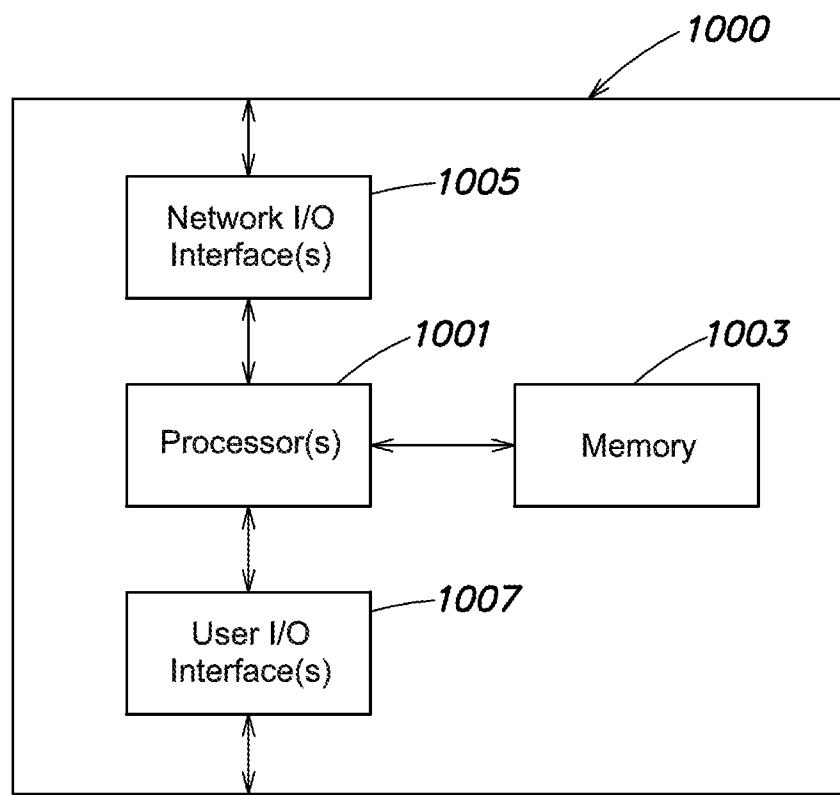

15 FIG. 34 is a block diagram of an illustrative computing device.

## DETAILED DESCRIPTION

Described herein is an integrated photodetector that can accurately measure, or “time-bin,” the timing of arrival of incident photons. In some embodiments, the integrated photodetector can measure the arrival of photons with nanosecond or picosecond resolution. Such a photodetector may find application in a variety of applications including molecular detection/quantitation, which may be applied to sequencing of nucleic acids (e.g., DNA sequencing). Such a photodetector can facilitate time-domain analysis of the arrival of incident photons from luminescent molecules used to label nucleotides, thereby enabling identification and sequencing of nucleotides based upon luminance lifetimes. Other examples of applications of the integrated photodetector include fluorescence lifetime imaging and time-of-flight imaging, as discussed further below.

### **Discussion of Time Domain Measurements for Molecular Detection/Quantitation**

30 Detection and quantitation of biological samples may be performed using biological assays (“bioassays”). Bioassays conventionally involve large, expensive laboratory equipment requiring research scientists trained to operate the equipment and perform the bioassays. Bioassays are conventionally performed in bulk such that a large amount of a particular type of sample is necessary for detection and quantitation. Some bioassays are

performed by tagging samples with luminescent markers that emit light of a particular wavelength. The samples are illuminated with a light source to cause luminescence, and the luminescent light is detected with a photodetector to quantify the amount of light emitted by the markers. Bioassays using luminescent tags and/or reporters conventionally involve 5 expensive laser light sources to illuminate samples and complicated luminescent detection optics and electronics to collect the light from the illuminated samples.

In some embodiments, an integrated photodetector as described herein can detect the luminance characteristics of biological and/or chemical sample(s) in response to excitation. More specifically, such an integrated photodetector can detect the temporal characteristics of 10 light received from the sample(s). Such an integrated photodetector can enable detecting and/or discriminating the luminance lifetime, e.g., the fluorescence lifetime, of light emitted by a luminescent molecule in response to excitation. In some embodiments, identification and/or quantitative measurements of sample(s) can be performed based on detecting and/or discriminating luminance lifetimes. For example, in some embodiments sequencing of a 15 nucleic acid (e.g., DNA, RNA) may be performed by detecting and/or discriminating luminance lifetimes of luminescent molecules attached to respective nucleotides. Each luminescent molecule may be directly attached (e.g., bonded) to a corresponding nucleotide or indirectly attached to a corresponding nucleotide via a linker molecule that is bonded to the nucleotide and the luminescent molecule.

20 In some embodiments, an integrated photodetector having a number of photodetection structures and associated electronics, termed “pixels,” can enable measurement and analysis of a plurality of samples in parallel (e.g., hundreds, thousands, millions or more), which can reduce the cost of performing complex measurements and rapidly advance the rate of discoveries. In some embodiments, each pixel of the photodetector may detect light from a 25 sample, which may be a single molecule or more than one molecule. In some embodiments, such an integrated photodetector can be used for dynamic real time applications such as nucleic acid (e.g., DNA, RNA) sequencing.

#### Detection/Quantitation of Molecules Using Luminance Lifetimes

An integrated circuit having an integrated photodetector according to aspects of the 30 present application may be designed with suitable functions for a variety of detection and imaging applications. As described in further detail below, such an integrated photodetector can have the ability to detect light within one or more time intervals, or “time bins.” To collect information regarding the time of arrival of the light, charge carriers are generated in

response to incident photons and can be segregated into respective time bins based upon their time of arrival.

An integrated photodetector according to some aspects of the present application may be used for differentiating among light emission sources, including luminescent molecules, such as fluorophores. Luminescent molecules vary in the wavelength of light they emit, the temporal characteristics of the light they emit (e.g., their emission decay time periods), and their response to excitation energy. Accordingly, luminescent molecules may be identified or discriminated from other luminescent molecules based on detecting these properties. Such identification or discrimination techniques may be used alone or in any suitable combination.

In some embodiments, an integrated photodetector as described in the present application can measure or discriminate luminance lifetimes, such as fluorescence lifetimes. Fluorescence lifetime measurements are based on exciting one or more fluorescent molecules, and measuring the time variation in the emitted luminescence. The probability of a fluorescent molecule to emit a photon after the fluorescent molecule reaches an excited state decreases exponentially over time. The rate at which the probability decreases may be characteristic of a fluorescent molecule, and may be different for different fluorescent molecules. Detecting the temporal characteristics of light emitted by fluorescent molecules may allow identifying fluorescent molecules and/or discriminating fluorescent molecules with respect to one another. Luminescent molecules are also referred to herein as luminescent markers, or simply “markers.”

After reaching an excited state, a marker may emit a photon with a certain probability at a given time. The probability of a photon being emitted from an excited marker may decrease over time after excitation of the marker. The decrease in the probability of a photon being emitted over time may be represented by an exponential decay function  $p(t) = e^{-t/\tau}$ , where  $p(t)$  is the probability of photon emission at a time,  $t$ , and  $\tau$  is a temporal parameter of the marker. The temporal parameter  $\tau$  indicates a time after excitation when the probability of the marker emitting a photon is a certain value. The temporal parameter,  $\tau$ , is a property of a marker that may be distinct from its absorption and emission spectral properties. Such a temporal parameter,  $\tau$ , is referred to as the luminance lifetime, the fluorescence lifetime or simply the “lifetime” of a marker.

FIG. 1A plots the probability of a photon being emitted as a function of time for two markers with different lifetimes. The marker represented by probability curve B has a probability of emission that decays more quickly than the probability of emission for the

marker represented by probability curve A. The marker represented by probability curve B has a shorter temporal parameter,  $\tau$ , or lifetime than the marker represented by probability curve A. Markers may have fluorescence lifetimes ranging from 0.1-20 ns, in some embodiments. However, the techniques described herein are not limited as to the lifetimes of the marker(s) used.

The lifetime of a marker may be used to distinguish among more than one marker, and/or may be used to identify marker(s). In some embodiments, fluorescence lifetime measurements may be performed in which a plurality of markers having different lifetimes are excited by an excitation source. As an example, four markers having lifetimes of 0.5, 1, 10 2, and 3 nanoseconds, respectively, may be excited by a light source that emits light having a selected wavelength (e.g., 635nm, by way of example). The markers may be identified or differentiated from each other based on measuring the lifetime of the light emitted by the markers.

Fluorescence lifetime measurements may use relative intensity measurements by 15 comparing how intensity changes over time, as opposed to absolute intensity values. As a result, fluorescence lifetime measurements may avoid some of the difficulties of absolute intensity measurements. Absolute intensity measurements may depend on the concentration of fluorophores present and calibration steps may be needed for varying fluorophore concentrations. By contrast, fluorescence lifetime measurements may be insensitive to the 20 concentration of fluorophores.

Luminescent markers may be exogenous or endogenous. Exogenous markers may be 25 external luminescent markers used as a reporter and/or tag for luminescent labeling. Examples of exogenous markers may include fluorescent molecules, fluorophores, fluorescent dyes, fluorescent stains, organic dyes, fluorescent proteins, enzymes, and/or quantum dots. Such exogenous markers may be conjugated to a probe or functional group (e.g., molecule, ion, and/or ligand) that specifically binds to a particular target or component. Attaching an exogenous tag or reporter to a probe allows identification of the target through 30 detection of the presence of the exogenous tag or reporter. Examples of probes may include proteins, nucleic acids such as DNA molecules or RNA molecules, lipids and antibody probes. The combination of an exogenous marker and a functional group may form any suitable probes, tags, and/or labels used for detection, including molecular probes, labeled probes, hybridization probes, antibody probes, protein probes (e.g., biotin-binding probes), enzyme labels, fluorescent probes, fluorescent tags, and/or enzyme reporters.

While exogenous markers may be added to a sample or region, endogenous markers may be already part of the sample or region. Endogenous markers may include any luminescent marker present that may luminesce or “autofluoresce” in the presence of excitation energy. Autofluorescence of endogenous fluorophores may provide for label-free and noninvasive labeling without requiring the introduction of endogenous fluorophores. Examples of such endogenous fluorophores may include hemoglobin, oxyhemoglobin, lipids, collagen and elastin crosslinks, reduced nicotinamide adenine dinucleotide (NADH), oxidized flavins (FAD and FMN), lipofuscin, keratin, and/or protoporphyrins, by way of example and not limitation.

Differentiating between markers by lifetime measurements may allow for fewer wavelengths of excitation light to be used than when the markers are differentiated by measurements of emission spectra. In some embodiments, sensors, filters, and/or diffractive optics may be reduced in number or eliminated when using fewer wavelengths of excitation light and/or luminescent light. In some embodiments, labeling may be performed with markers that have different lifetimes, and the markers may be excited by light having the same excitation wavelength or spectrum. In some embodiments, an excitation light source may be used that emits light of a single wavelength or spectrum, which may reduce the cost. However, the techniques described herein are not limited in this respect, as any number of excitation light wavelengths or spectra may be used. In some embodiments, an integrated photodetector may be used to determine both spectral and temporal information regarding received light. In some embodiments a quantitative analysis of the types of molecule(s) present may be performed by determining a temporal parameter, a spectral parameter, or a combination of the temporal and spectral parameters of the emitted luminescence from a marker.

An integrated photodetector that detects the arrival time of incident photons may reduce additional optical filtering (e.g., optical spectral filtering) requirements. As described below, an integrated photodetector according to the present application may include a drain to remove photogenerated carriers at particular times. By removing photogenerated carriers in this manner, unwanted charge carriers produced in response to an excitation light pulse may be discarded without the need for optical filtering to prevent reception of light from the excitation pulse. Such a photodetector may reduce overall design integration complexity, optical and/or filtering components, and/or cost.

In some embodiments, a fluorescence lifetime may be determined by measuring the time profile of the emitted luminescence by aggregating collected charge carriers in one or more time bins of the integrated photodetector to detect luminance intensity values as a function of time. In some embodiments, the lifetime of a marker may be determined by

5 performing multiple measurements where the marker is excited into an excited state and then the time when a photon emits is measured. For each measurement, the excitation source may generate a pulse of excitation light directed to the marker, and the time between the excitation pulse and subsequent photon event from the marker may be determined. Additionally or alternatively, when an excitation pulse occurs repeatedly and periodically, the time between

10 when a photon emission event occurs and the subsequent excitation pulse may be measured, and the measured time may be subtracted from the time interval between excitation pulses (i.e., the period of the excitation pulse waveform) to determine the time of the photon absorption event.

By repeating such experiments with a plurality of excitation pulses, the number of

15 instances a photon is emitted from the marker within a certain time interval after excitation may be determined, which is indicative of the probability of a photon being emitted within such a time interval after excitation. The number of photon emission events collected may be based on the number of excitation pulses emitted to the marker. The number of photon emission events over a measurement period may range from 50-10,000,000 or more, in some

20 embodiments, however, the techniques described herein are not limited in this respect. The number of instances a photon is emitted from the marker within a certain time interval after excitation may populate a histogram representing the number of photon emission events that occur within a series of discrete time intervals or time bins. The number of time bins and/or the time interval of each bin may be set and/or adjusted to identify a particular lifetime and/or

25 a particular marker. The number of time bins and/or the time interval of each bin may depend on the sensor used to detect the photons emitted. The number of time bins may be 1, 2, 3, 4, 5, 6, 7, 8, or more, such as 16, 32, 64, or more. A curve fitting algorithm may be used to fit a curve to the recorded histogram, resulting in a function representing the probability of a photon to be emitted after excitation of the marker at a given time. An exponential decay

30 function, such as  $p(t) = e^{-t/\tau}$ , may be used to approximately fit the histogram data. From such a curve fitting, the temporal parameter or lifetime may be determined. The determined lifetime may be compared to known lifetimes of markers to identify the type of marker present.

A lifetime may be calculated from the intensity values at two time intervals. FIG. 1B shows example intensity profiles over time for an example excitation pulse (dotted line) and example fluorescence emission (solid line). In the example shown in FIG. 1B, the photodetector measures the intensity over at least two time bins. The photons that emit 5 luminescence energy between times  $t_1$  and  $t_2$  are measured by the photodetector as intensity  $I_1$  and luminescence energy emitted between times  $t_3$  and  $t_4$  are measured as  $I_2$ . Any suitable number of intensity values may be obtained although only two are shown in FIG. 1B. Such intensity measurements may then be used to calculate a lifetime. When one fluorophore 10 is present at a time, then the time binned luminescence signal may be fit to a single exponential decay. In some embodiments, only two time bins may be needed to accurately identify the lifetime for a fluorophore. When two or more fluorophores are present, then individual lifetimes may be identified from a combined luminescence signal by fitting the luminescence signal to multiple exponential decays, such as double or triple exponentials. In some embodiments two or more time bins may be needed in order to accurately identify more 15 than one fluorescence lifetime from such a luminescence signal. However, in some instances with multiple fluorophores, an average fluorescence lifetime may be determined by fitting a single exponential decay to the luminescence signal.

In some instances, the probability of a photon emission event and thus the lifetime of a marker may change based on the surroundings and/or conditions of the marker. For 20 example, the lifetime of a marker confined in a volume with a diameter less than the wavelength of the excitation light may be smaller than when the marker is not in the volume. Lifetime measurements with known markers under conditions similar to when the markers are used for labeling may be performed. The lifetimes determined from such measurements with known markers may be used when identifying a marker.

25

### Sequencing Using Luminance Lifetime Measurements

Individual pixels of an integrated photodetector may be capable of fluorescence 30 lifetime measurements used to identify fluorescent tags and/or reporters that label one or more targets, such as molecules or specific locations on molecules. Any one or more molecules of interest may be labeled with a fluorophore, including proteins, amino acids, enzymes, lipids, nucleotides, DNA, and RNA. When combined with detecting spectra of the emitted light or other labeling techniques, fluorescence lifetime may increase the total number of fluorescent tags and/or reporters that can be used. Identification based on lifetime

may be used for single molecule analytical methods to provide information about characteristics of molecular interactions in complex mixtures where such information would be lost in ensemble averaging and may include protein-protein interactions, enzymatic activity, molecular dynamics, and/or diffusion on membranes. Additionally, fluorophores 5 with different fluorescence lifetimes may be used to tag target components in various assay methods that are based on presence of a labeled component. In some embodiments, components may be separated, such as by using microfluidic systems, based on detecting particular lifetimes of fluorophores.

Measuring fluorescence lifetimes may be used in combination with other analytical 10 methods. For an example, fluorescence lifetimes may be used in combination with fluorescence resonance energy transfer (FRET) techniques to discriminate between the states and/or environments of donor and acceptor fluorophores located on one or more molecules. Such measurements may be used to determine the distance between the donor and the 15 acceptor. In some instances, energy transfer from the donor to the acceptor may decrease the lifetime of the donor. In another example, fluorescence lifetime measurements may be used in combination with DNA sequencing techniques where four fluorophores having different lifetimes may be used to label the four different nucleotides (A, T, G, C) in a DNA molecule with an unknown sequence of nucleotides. The fluorescence lifetimes, instead of emission spectra, of the fluorophores may be used to identify the sequence of nucleotides. By using 20 fluorescence lifetime instead of emission spectra for certain techniques, accuracy and measurement resolution may increase because artifacts due to absolute intensity measurements are reduced. Additionally, lifetime measurements may reduce the complexity and/or expense of the system because fewer excitation energy wavelengths are required and/or fewer emission energy wavelengths need be detected.

25 The methods described herein may be used for sequencing of nucleic acids, such as DNA sequencing or RNA sequencing. DNA sequencing allows for the determination of the order and position of nucleotides in a target nucleic acid molecule. Technologies used for DNA sequencing vary greatly in the methods used to determine the nucleic acid sequence as well as in the rate, read length, and incidence of errors in the sequencing process. A number 30 of DNA sequencing methods are based on sequencing by synthesis, in which the identity of a nucleotide is determined as the nucleotide is incorporated into a newly synthesized strand of nucleic acid that is complementary to the target nucleic acid. Many sequencing by synthesis methods require the presence of a population of target nucleic acid molecules (e.g., copies of

a target nucleic acid) or a step of amplification of the target nucleic acid to achieve a population of target nucleic acids. Improved methods for determining the sequence of single nucleic acid molecules is desired.

There have been recent advances in sequencing single nucleic acid molecules with

5 high accuracy and long read length. The target nucleic acid used in single molecule sequencing technology, for example the SMRT technology developed by Pacific Biosciences, is a single stranded DNA template that is added to a sample well containing at least one component of the sequencing reaction (e.g., the DNA polymerase) immobilized or attached to a solid support such as the bottom of the sample well. The sample well also contains

10 deoxyribonucleoside triphosphates, also referred to as “dNTPs,” including adenine, cytosine, guanine, and thymine dNTPs, that are conjugated to detection labels, such as fluorophores. Preferably each class of dNTPs (e.g. adenine dNTPs, cytosine dNTPs, guanine dNTPs, and thymine dNTPs) are each conjugated to a distinct detection label such that detection of the signal indicates the identity of the dNTP that was incorporated into the newly synthesized

15 nucleic acid. The detection label may be conjugated to the dNTP at any position such that the presence of the detection label does not inhibit the incorporation of the dNTP into the newly synthesized nucleic acid strand or the activity of the polymerase. In some embodiments, the detection label is conjugated to the terminal phosphate (the gamma phosphate) of the dNTP.

Any polymerase may be used for single molecule DNA sequencing that is capable of

20 synthesizing a nucleic acid complementary to a target nucleic acid. Examples of polymerases include *E. coli* DNA polymerase I, T7 DNA polymerase, bacteriophage T4 DNA polymerase φ29 (psi29) DNA polymerase, and variants thereof. In some embodiments, the polymerase is a single subunit polymerase. Upon base pairing between a nucleobase of a target nucleic acid and the complementary dNTP, the polymerase incorporates the dNTP into the newly

25 synthesized nucleic acid strand by forming a phosphodiester bond between the 3' hydroxyl end of the newly synthesized strand and the alpha phosphate of the dNTP. In examples in which the detection label conjugated to the dNTP is a fluorophore, its presence is signaled by excitation and a pulse of emission is detected during the step of incorporation. For detection labels that are conjugated to the terminal (gamma) phosphate of the dNTP, incorporation of

30 the dNTP into the newly synthesized strand results in release the beta and gamma phosphates and the detection label, which is free to diffuse in the sample well, resulting in a decrease in emission detected from the fluorophore.

The techniques described herein are not limited as to the detection or quantitation of molecules or other samples, or to performing sequencing. In some embodiments, an integrated photodetector may perform imaging to obtain spatial information regarding a region, object or scene and temporal information regarding the arrival of incident photons 5 using the region, object or scene. In some embodiments, the integrated photodetector may perform luminescence lifetime imaging of a region, object or sample, such as fluorescence lifetime imaging.

### **Additional Applications**

10 Although the integrated photodetector described herein may be applied to the analysis of a plurality of biological and/or chemical samples, as discussed above, the integrated photodetector may be applied to other applications, such as imaging applications, for example. In some embodiments, the integrated photodetector may include a pixel array that performs imaging of a region, object or scene, and may detect temporal characteristics of the 15 light received at individual pixels from different regions of the region, object or scene. For example, in some embodiments the integrated photodetector may perform imaging of tissue based on the temporal characteristics of light received from the tissue, which may enable a physician performing a procedure (e.g., surgery) to identify an abnormal or diseased region of tissue (e.g., cancerous or pre-cancerous). In some embodiments, the integrated photodetector 20 may be incorporated into a medical device, such as a surgical imaging tool. In some embodiments, time-domain information regarding the light emitted by tissue in response to a light excitation pulse may be obtained to image and/or characterize the tissue. For example, imaging and/or characterization of tissue or other objects may be performed using fluorescence lifetime imaging.

25 Although the integrated photodetector may be applied in a scientific or diagnostic context such as by performing imaging or analysis of biological and/or chemical samples, or imaging tissue, as described above, such an integrated photodetector may be used in any other suitable contexts. For example, in some embodiments, such an integrated photodetector may image a scene using temporal characteristics of the light detected in 30 individual pixels. An example of an application for imaging a scene is range imaging or time-of-flight imaging, in which the amount of time light takes to reach the photodetector is analyzed to determine the distance traveled by the light to the photodetector. Such a technique may be used to perform three-dimensional imaging of a scene. For example, a

scene may be illuminated with a light pulse emitted from a known location relative to the integrated photodetector, and the reflected light detected by the photodetector. The amount of time that the light takes to reach the integrated photodetector at respective pixels of the array is measured to determine the distance(s) light traveled from respective portions of the 5 scene to reach respective pixels of the photodetector. In some embodiments, the integrated photodetector may be incorporated into a consumer electronic device such as a camera, cellular telephone, or tablet computer, for example, to enable such devices to capture and process images or video based on the range information obtained.

In some embodiments, the integrated photodetector described in the present 10 application may be used to measure low light intensities. Such a photodetector may be suitable for applications that require photodetectors with a high sensitivity, such as applications that may currently use single photon counting techniques, for example. However, the techniques described herein are not limited in this respect, as the integrated photodetector described in the present applications may measure any suitable light intensities.

15

#### Additional Luminescence Lifetime Applications

##### Imaging and Characterization Using Lifetimes

As mentioned above, the techniques described herein are not limited to labeling, detection and quantitation using exogenous fluorophores. In some embodiments, a region, 20 object or sample may be imaged and/or characterized using fluorescence lifetime imaging techniques though use of an integrated photodetector. In such techniques, the fluorescence characteristics of the region, object or sample itself may be used for imaging and/or characterization. Either exogenous markers or endogenous markers may be detected through lifetime imaging and/or characterization. Exogenous markers attached to a probe may be 25 provided to the region, object, or sample in order to detect the presence and/or location of a particular target component. The exogenous marker may serve as a tag and/or reporter as part of a labeled probe to detect portions of the region, object, or sample that contains a target for the labeled probe. Autofluorescence of endogenous markers may provide a label-free and noninvasive contrast for spatial resolution that can be readily utilized for imaging without 30 requiring the introduction of endogenous markers. For example, autofluorescence signals from biological tissue may depend on and be indicative of the biochemical and structural composition of the tissue.

Fluorescence lifetime measurements may provide a quantitative measure of the conditions surrounding the fluorophore. The quantitative measure of the conditions may be in addition to detection or contrast. The fluorescence lifetime for a fluorophore may depend on the surrounding environment for the fluorophore, such as pH or temperature, and a change in the value of the fluorescence lifetime may indicate a change in the environment surrounding the fluorophore. As an example, fluorescence lifetime imaging may map changes in local environments of a sample, such as in biological tissue (e.g., a tissue section or surgical resection). Fluorescence lifetime measurements of autofluorescence of endogenous fluorophores may be used to detect physical and metabolic changes in the tissue.

5 As examples, changes in tissue architecture, morphology, oxygenation, pH, vascularity, cell structure and/or cell metabolic state may be detected by measuring autofluorescence from the sample and determining a lifetime from the measured autofluorescence. Such methods may be used in clinical applications, such as screening, image-guided biopsies or surgeries, and/or endoscopy. In some embodiments, an integrated photodetector of the present application

10 15 may be incorporated into a clinical tool, such as a surgical instrument, for example, to perform fluorescence lifetime imaging. Determining fluorescence lifetimes based on measured autofluorescence provides clinical value as a label-free imaging method that allows a clinician to quickly screen tissue and detect small cancers and/or pre-cancerous lesions that are not apparent to the naked eye. Fluorescence lifetime imaging may be used for detection

20 and delineation of malignant cells or tissue, such as tumors or cancer cells which emit luminescence having a longer fluorescence lifetime than healthy tissue. For example, fluorescence lifetime imaging may be used for detecting cancers on optically accessible tissue, such as gastrointestinal tract, bladder, skin, or tissue surface exposed during surgery.

In some embodiments, fluorescence lifetimes may be used for microscopy techniques to provide contrast between different types or states of samples. Fluorescence lifetime imaging microscopy (FLIM) may be performed by exciting a sample with a light pulse, detecting the fluorescence signal as it decays to determine a lifetime, and mapping the decay time in the resulting image. In such microscopy images, the pixel values in the image may be based on the fluorescence lifetime determined for each pixel in the photodetector collecting the field of view.

### Imaging a Scene or Object Using Temporal Information

As discussed above, an integrated photodetector as described in the present application may be used in scientific and clinical contexts in which the timing of light emitted may be used to detect, quantify, and or image a region, object or sample. However, the 5 techniques described herein are not limited to scientific and clinical applications, as the integrated photodetector may be used in any imaging application that may take advantage of temporal information regarding the time of arrival of incident photons. An example of an application is time-of-flight imaging.

10 *Time-of-Flight Applications*

In some embodiments, an integrated photodetector may be used in imaging techniques that are based on measuring a time profile of scattered or reflected light, including time-of-flight measurements. In such time-of-flight measurements, a light pulse may be emitted into a region or sample and scattered light may be detected by the integrated photodetector.

15 The scattered or reflected light may have a distinct time profile that may indicate characteristics of the region or sample. Backscattered light by the sample may be detected and resolved by their time of flight in the sample. Such a time profile may be a temporal point spread function (TPSF). The time profile may be acquired by measuring the integrated intensity over multiple time bins after the light pulse is emitted. Repetitions of light pulses 20 and accumulating the scattered light may be performed at a certain rate to ensure that all the previous TPSF is completely extinguished before generating a subsequent light pulse. Time-resolved diffuse optical imaging methods may include spectroscopic diffuse optical tomography where the light pulse may be infrared light in order to image at a further depth in the sample. Such time-resolved diffuse optical imaging methods may be used to detect 25 tumors in an organism or in part of an organism, such as a person's head.

Additionally or alternatively, time-of-flight measurements may be used to measure distance or a distance range based on the speed of light and time between an emitted light pulse and detecting light reflected from an object. Such time-of-flight techniques may be used in a variety of applications including cameras, proximity detection sensors in 30 automobiles, human-machine interfaces, robotics and other applications that may use three-dimensional information collected by such techniques.

### Integrated Photodetector for Time Binning Photogenerated Charge Carriers

Some embodiments relate to an integrated circuit having a photodetector that produces charge carriers in response to incident photons and which is capable of discriminating the timing at which the charge carriers are generated by the arrival of incident photons with respect to a reference time (e.g., a trigger event). In some embodiments, a charge carrier segregation structure segregates charge carriers generated at different times and directs the charge carriers into one or more charge carrier storage regions (termed “bins”) that aggregate charge carriers produced within different time periods. Each bin stores charge carriers produced within a selected time interval. Reading out the charge stored in each bin can provide information about the number of photons that arrived within each time interval. Such an integrated circuit can be used in any of a variety of applications, such as those described herein.

An example of an integrated circuit having a photodetection region and a charge carrier segregation structure will be described. In some embodiments, the integrated circuit may include an array of pixels, and each pixel may include one or more photodetection regions and one or more charge carrier segregation structures, as discussed below.

#### Overview of Pixel Structure and Operation

FIG. 2A shows a diagram of a pixel 100, according to some embodiments. Pixel 100 includes a photon absorption/carrier generation region 102 (also referred to as a photodetection region), a carrier travel/capture region 106, a carrier storage region 108 having one or more charge carrier storage regions, also referred to herein as “charge carrier storage bins” or simply “bins,” and readout circuitry 110 for reading out signals from the charge carrier storage bins.

The photon absorption/carrier generation region 102 may be a region of semiconductor material (e.g., silicon) that can convert incident photons into photogenerated charge carriers. The photon absorption/carrier generation region 102 may be exposed to light, and may receive incident photons. When a photon is absorbed by the photon absorption/carrier generation region 102 it may generate photogenerated charge carriers, such as an electron/hole pair. Photogenerated charge carriers are also referred to herein simply as “charge carriers.”

An electric field may be established in the photon absorption/carrier generation region 102. In some embodiments, the electric field may be “static,” as distinguished from the

changing electric field in the carrier travel/capture region 106. The electric field in the photon absorption/carrier generation region 102 may include a lateral component, a vertical component, or both a lateral and a vertical component. The lateral component of the electric field may be in the downward direction of FIG. 2A, as indicated by the arrows, which 5 induces a force on photogenerated charge carriers that drives them toward the carrier travel/capture region 106. The electric field may be formed in a variety of ways.

In some embodiments one or more electrodes may be formed over the photon absorption/carrier generation region 102. The electrode(s) may have voltages applied thereto to establish an electric field in the photon absorption/carrier generation region 102. 10 Such electrode(s) may be termed “photogate(s).” In some embodiments, photon absorption/carrier generation region 102 may be a region of silicon that is fully depleted of charge carriers.

In some embodiments, the electric field in the photon absorption/carrier generation region 102 may be established by a junction, such as a PN junction. The semiconductor 15 material of the photon absorption/carrier generation region 102 may be doped to form the PN junction with an orientation and/or shape that produces an electric field that induces a force on photogenerated charge carriers that drives them toward the carrier travel/capture region 106. Producing the electric field using a junction may improve the quantum efficiency with respect to use of electrodes overlying the photon absorption/carrier generation region 102 20 which may prevent a portion of incident photons from reaching the photon absorption/carrier generation region 102. Using a junction may reduce dark current with respect to use of photogates. It has been appreciated that dark current may be generated by imperfections at the surface of the semiconductor substrate that may produce carriers. In some embodiments, the P terminal of the PN junction diode may be connected to a terminal that sets its voltage. 25 Such a diode may be referred to as a “pinned” photodiode. A pinned photodiode may promote carrier recombination at the surface, due to the terminal that sets its voltage and attracts carriers, which can reduce dark current. Photogenerated charge carriers that are desired to be captured may pass underneath the recombination area at the surface. In some embodiments, the lateral electric field may be established using a graded doping 30 concentration in the semiconductor material.

In some embodiments, an absorption/carrier generation region 102 that has a junction to produce an electric field may have one or more of the following characteristics:

- 1) a depleted n-type region that is tapered away from the time varying field,

- 2) a p-type implant surrounding the n-type region with a gap to transition the electric field laterally into the n-type region, and/or

- 3) a p-type surface implant that buries the n-type region and serves as a recombination region for parasitic electrons.

5 In some embodiments, the electric field may be established in the photon absorption/carrier generation region 102 by a combination of a junction and at least one electrode. For example, a junction and a single electrode, or two or more electrodes, may be used. In some embodiments, one or more electrodes may be positioned near carrier travel/capture region 106 to establish the potential gradient near carrier travel/capture region 10

10 106, which may be positioned relatively far from the junction.

As illustrated in FIG. 2A, a photon may be captured and a charge carrier 101A (e.g., an electron) may be produced at time t1. In some embodiments, an electrical potential gradient may be established along the photon absorption/ carrier generation region 102 and the carrier travel/capture region 106 that causes the charge carrier 101A to travel in the 15 downward direction of FIG. 2A (as illustrated by the arrows shown in FIG. 2A). In response to the potential gradient, the charge carrier 101A may move from its position at time t1 to a second position at time t2, a third position at time t3, a fourth position at time t4, and a fifth position at time t5. The charge carrier 101A thus moves into the carrier travel/capture region 106 in response to the potential gradient.

20 The carrier travel/capture region 106 may be a semiconductor region. In some embodiments, the carrier travel/capture region 106 may be a semiconductor region of the same material as photon absorption/carrier generation region 102 (e.g., silicon) with the exception that carrier travel/capture region 106 may be shielded from incident light (e.g., by an overlying opaque material, such as a metal layer).

25 In some embodiments, and as discussed further below, a potential gradient may be established in the photon absorption/carrier generation region 102 and the carrier travel/capture region 106 by electrodes positioned above these regions. However, the techniques described herein are not limited as to particular positions of electrodes used for producing an electric potential gradient. Nor are the techniques described herein limited to 30 establishing an electric potential gradient using electrodes. In some embodiments, an electric potential gradient may be established using a spatially graded doping profile and/or a PN junction. Any suitable technique may be used for establishing an electric potential gradient

that causes charge carriers to travel along the photon absorption/carrier generation region 102 and carrier travel/capture region 106.

A charge carrier segregation structure may be formed in the pixel to enable segregating charge carriers produced at different times. In some embodiments, at least a portion of the charge carrier segregation structure may be formed over the carrier travel/capture region 106. The charge carrier segregation structure may include one or more electrodes formed over the carrier travel/capture region 106, the voltage of which may be controlled by control circuitry to change the electric potential in the carrier travel/capture region 106.

The electric potential in the carrier travel/capture region 106 may be changed to enable capturing a charge carrier. The potential gradient may be changed by changing the voltage on one or more electrodes overlying the carrier travel/capture region 106 to produce a potential barrier that can confine a carrier within a predetermined spatial region. For example, the voltage on an electrode overlying the dashed line in the carrier travel/capture region 106 of FIG. 2A may be changed at time  $t_5$  to raise a potential barrier along the dashed line in the carrier travel/capture region 106 of FIG. 2A, thereby capturing charge carrier 101A. As shown in FIG. 2A, the carrier captured at time  $t_5$  may be transferred to a bin "bin0" of carrier storage region 108. The transfer of the carrier to the charge carrier storage bin may be performed by changing the potential in the carrier travel/capture region 106 and/or carrier storage region 108 (e.g., by changing the voltage of electrode(s) overlying these regions) to cause the carrier to travel into the charge carrier storage bin.

Changing the potential at a certain point in time within a predetermined spatial region of the carrier travel/capture region 106 may enable trapping a carrier that was generated by photon absorption that occurred within a specific time interval. By trapping photogenerated charge carriers at different times and/or locations, the times at which the charge carriers were generated by photon absorption may be discriminated. In this sense, a charge carrier may be "time binned" by trapping the charge carrier at a certain point in time and/or space after the occurrence of a trigger event. The time binning of a charge carrier within a particular bin provides information about the time at which the photogenerated charge carrier was generated by absorption of an incident photon, and thus likewise "time bins," with respect to the trigger event, the arrival of the incident photon that produced the photogenerated charge carrier.

FIG. 2B illustrates capturing a charge carrier at a different point in time and space. As shown in FIG. 2B, the voltage on an electrode overlying the dashed line in the carrier travel/capture region 106 may be changed at time t9 to raise a potential barrier along the dashed line in the carrier travel/capture region 106 of FIG. 2B, thereby capturing carrier 5 101B. As shown in FIG. 2B, the carrier captured at time t9 may be transferred to a bin “bin1” of carrier storage region 108. Since charge carrier 101B is trapped at time t9, it represents a photon absorption event that occurred at a different time (i.e., time t6) than the photon absorption event (i.e., at t1) for carrier 101A, which is captured at time t5.

10 Direct Binning Pixel

FIG. 3 shows an example of a pixel 200 in which charge carriers generated in the photon absorption/carrier generation region 102 may be directly transferred to a charge storage bin in charge carrier storage region 108. Such a pixel is termed a “direct binning pixel.” As shown in FIG. 3, pixel 200 does not include a carrier travel/capture region 106. 15 Rather than capturing carriers in carrier travel/capture region 106, charge carriers may be directly transferred from photon absorption/carrier generation region 102 into a bin of charge carrier storage region 108. The bin to which a charge carrier is transferred is based on the time of arrival of a photon in photon absorption/carrier generation region 102 that produces the charge carrier. The area of a direct binning pixel may be reduced at least in part due to 20 omission of carrier travel/capture region 106. Advantageously, in some embodiments, a direct binning pixel may take up a smaller area on of a semiconductor chip, which may enable forming many pixels on the chip, such as thousands or millions of pixels, or more. Providing a large number of pixels on a chip may enable performing a large number of measurements in parallel, or performing imaging with high spatial resolution. Alternatively 25 or additionally, a direct binning pixel may have reduced power consumption. Since charging and discharging each electrode of the pixel may consume power, pixel 200 may have reduced power consumption due to the presence of fewer electrodes, i.e., the electrodes for capturing charge carriers in carrier travel/capture region 106 can be omitted.

FIG. 3 shows an example of a pixel 200 having two bins in charge carrier storage 30 region 108: bin 0 and bin 1. As discussed above, bin 0 may aggregate charge carriers received in one period following a trigger event, and bin 1 may aggregate charge carriers received in a later time period with respect to a trigger event. However, charge storage region 108 may have any number of bins, such as one bin, three bins, four bins, or more.

The photon absorption / carrier generation region 102 may include a semiconductor region, which may be formed of any suitable semiconductor, such as silicon, for example. In some embodiments, the photon absorption/carrier generation region 102 may include a photodiode, such as a pinned photodiode. The photodiode may be fully depleted. In some 5 embodiments, the photodiode may remain essentially depleted of electrons at all times. In some embodiments, the photodiode is configured to collect single photons. In such embodiments, a single photoelectron may be generated and confined in the photodiode. If formed by a CMOS process, the photodiode may be fully depleted by potentials available within devices produced by a CMOS process. Electrodes 203, 205 and 206 may be coupled to 10 the diode at least partially surrounding the perimeter of the diode, as shown in more detail in FIG. 8. However, it should be noted that this the embodiment depicted in FIG. 8 is merely one example of a geometry suitable for electrodes 203, 205 and 206. The electrodes 203 and 205 may allow rapid charge transfer of confined carriers. Prior to discussing transfer of charge carriers to the bins, the rejection of unwanted carriers by transfer of the unwanted 15 carriers into a rejection region 105 will be described.

Referring again to FIG. 3, direct binning pixel 200 may include a rejection region 105 to drain or otherwise discard charge carriers produced in photon absorption/carrier generation region 102 during a rejection period. A rejection period may be timed to occur during a trigger event, such as an excitation light pulse. Since an excitation light pulse may produce a 20 number of unwanted charge carriers in photon absorption/carrier generation region 102, a potential gradient may be established in pixel 200 to drain such charge carriers to rejection region 105 during a rejection period. As an example, rejection region 105 may include a high potential diffusion area where electrons are drained to a supply voltage. Rejection region 105 may include an electrode 206 that charge couples region 102 directly to rejection region 105. 25 In some embodiments, the electrode 206 may overlie the semiconductor region. The voltage of the electrode 206 may be varied to establish a desired potential gradient in photon absorption/carrier generation region 102. During a rejection period, the voltage of the electrode 206 may be set to a level that draws carriers from the photon absorption/carrier generation region 102 into the electrode 206, and out to the supply voltage. For example, the 30 voltage of the electrode 206 may be set to a positive voltage to attract electrons, such that they are drawn away from the photon absorption/carrier generation region 102 to rejection region 105. During a rejection period, electrodes 203 and 205 may be set to a potential that forms potential barriers 202 and 204 to prevent the unwanted charge carriers from reaching

the bins. Rejection region 105 may be considered a “lateral rejection region” because it allows transferring carriers laterally from region 102 to a drain. In some embodiments the rejection is in the opposite direction from the photodetection region with respect to the storage bins.

5 Following the rejection period, a photogenerated charge carrier produced in photon absorption/carrier generation region 102 may be time-binned. Individual charge carriers may be directed to a bin based on their time of arrival. To do so, the electrical potential between photon absorption/carrier generation region 102 and charge carrier storage region 108 may be changed in respective time periods to establish a potential gradient that causes the

10 photogenerated charge carriers to be directed to respective time bins. For example, during a first time period a potential barrier 202 formed by electrode 203 may be lowered, and a potential gradient may be established from photon absorption/carrier generation region 102 to bin 0, such that a carrier generated during this period is transferred to bin 0. Then, during a second time period, a potential barrier 204 formed by electrode 205 may be lowered, and a

15 potential gradient may be established from photon absorption/carrier generation region 102 to bin 1, such that a carrier generated during this later period is transferred to bin 1.

FIG. 4 shows a flowchart of a method 2800 of operating pixel 200 that includes performing a plurality of measurements 2820, according to some embodiments. In some embodiments, a “measurement” may include receiving a photon and transferring the captured

20 carrier to a charge storage node corresponding to a particular time period or bin. A measurement may be repeated a plurality of times to gather statistical information about the times at which photons arrive at the photodetector. Such a method may be performed at least partially by an integrated device as described herein.

Step 2802 may be timed to occur during a trigger event. A trigger event may be an

25 event that serves as a time reference for time binning arrival of a photon. The trigger event may be an optical pulse or an electrical pulse, for example, and could be a singular event or a repeating, periodic event. In the context of fluorescence lifetime detection, the trigger event may be the generation of a light excitation pulse to excite a fluorophore. In the context of time-of-flight imaging, the trigger event may be a pulse of light (e.g., from a flash) emitted by

30 an imaging device comprising the integrated photodetector. The trigger event can be any event used as a reference for timing the arrival of photons or carriers.

The generation of the light excitation pulse may produce a significant number of photons, some of which may reach the pixel 200 and may produce charge carriers in the

photon absorption/carrier generation area 102. Since photogenerated carriers from the light excitation pulse are not desired to be measured, they may be rejected by directing them to a drain. This can reduce the amount of unwanted signal that otherwise may need to be prevented from arriving by complex optical components, such as a shutter or filter, which 5 may add additional design complexity and/or cost.

Step 2802 corresponds to a rejection period. The operation of pixel 200 during step 2802 is illustrated in FIG. 5A. In step 2802, the pixel 200 is operated to reject charge carriers produced in region 102 by transferring them to rejection region 105. For example, step 2802 10 may include controlling electrode 206 to produce a potential gradient that drives charge carriers produced in region 102 to rejection region 105. Carriers are rejected by directing them in the upward direction of FIG. 5A.

In step 2804, photon absorption and carrier generation may be performed in region 102. As discussed above, in some applications the probability of receiving a photon and generating a carrier in response to a trigger event may be low (e.g., about 1 in 10,000). 15 Accordingly, step 2804 may not be performed for each trigger event, as often no photons may be received in response to a trigger event. However, in some embodiments, the quantity of photons received may be higher.

During step 2804, a potential barrier exists between photodetection region 102 and rejection region 105 to prevent photogenerated charge carriers from being rejected. During 20 step 2804, a potential barrier 202 to bin 0 may be lowered, as shown in FIG. 5B, or may be raised, as shown in FIG. 5C. If the potential barrier 202 to bin 0 is lowered, a charge carrier may pass directly to bin 0 (step 2806). If the potential barrier 202 to bin 0 is raised, a charge carrier may be confined in region 102 until step 2806.

In step 2806, a carrier (if present) is transferred to bin 0. The potential barrier 202 to 25 bin 0 is lowered or remains lowered. If a photogenerated charge carrier is produced in the time period following step 2802, the lowering of the potential barrier 202 allows the charge carrier to be transferred to bin 0. The potential barrier 202 may be raised or lowered by controlling the voltage of an electrode 203 at the boundary between region 102 and bin 0 (FIG. 3, FIG. 5B). Such an electrode may be positioned over the semiconductor region that 30 controls the potential in the semiconductor region. In some embodiments, only a single electrode 203 may be disposed at the boundary between region 102 and bin 0 to control the potential barrier 202 that allows or prevents transfer of a charge carrier to bin 0. However, in some embodiments, the potential barrier 202 may be produced by more than one electrode.

Unlike charge carrier capture region 106 of FIG. 2A, the electrode(s) 206 that produce potential barrier 202 may not trap a charge carrier at a location outside of a bin. Rather, the electrode(s) 206 may control a potential barrier 202 to either allow or prevent a charge carrier from entering bin 0. Also, unlike charge carrier capture region 106, which produces a 5 number of potential barriers between region 102 and a bin, the potential barrier 202 may be a single potential barrier between region 102 and bin 0. The same or similar characteristics as described in this paragraph may be present in bin 1, potential barrier 204 and the electrode(s) 205 that produce potential barrier 204.

In some embodiments, after the rejection period a potential gradient may be formed 10 that only allows charge to flow in one direction, that is, in the direction from region 102 to a time bin. Charge flows to one of the bins in the downward direction of FIGS. 5A-D. A suitable potential gradient may be established in the semiconductor region to cause generated carriers to travel through the semiconductor region in the downward direction of the figures toward carrier storage region 108. Such a potential gradient may be established in any 15 suitable way, such as using a graded doping concentration and/or one or more electrodes at selected potentials. Accordingly, a photogenerated charge carrier produced in region 102 after step 2802 is transferred to bin 0, thus time binning the arrival of the photogenerated charge carrier in bin 0.

Following step 2806, the potential barrier 202 to bin 0 is raised, as illustrated in FIG. 20 5C. Optionally, both the potential barrier 202 to bin 0 and the potential barrier 204 to bin 1 may be raised for a period of time. If both barrier 202 and barrier 204 are raised, a charge carrier produced following step 2806 may be confined in region 102 until step 2808.

In step 2808, a carrier (if present) is transferred to bin 1, as illustrated in FIG. 5D. The potential barrier 204 to bin 1 is lowered. If a photogenerated charge carrier is produced 25 in the time period following step 2806, the lowering of the potential barrier 204 allows the charge carrier to be transferred to bin 1. The potential barrier 204 may be raised or lowered by controlling the voltage of an electrode 205 at the boundary between region 102 and bin 1. Such an electrode may be positioned over the semiconductor region. Accordingly, a photogenerated charge carrier produced in region 102 after step 2806 is transferred to bin 1, 30 thus time binning the arrival of the photogenerated charge carrier in bin 1. Following step 2808, the potential barrier 202 may be raised.

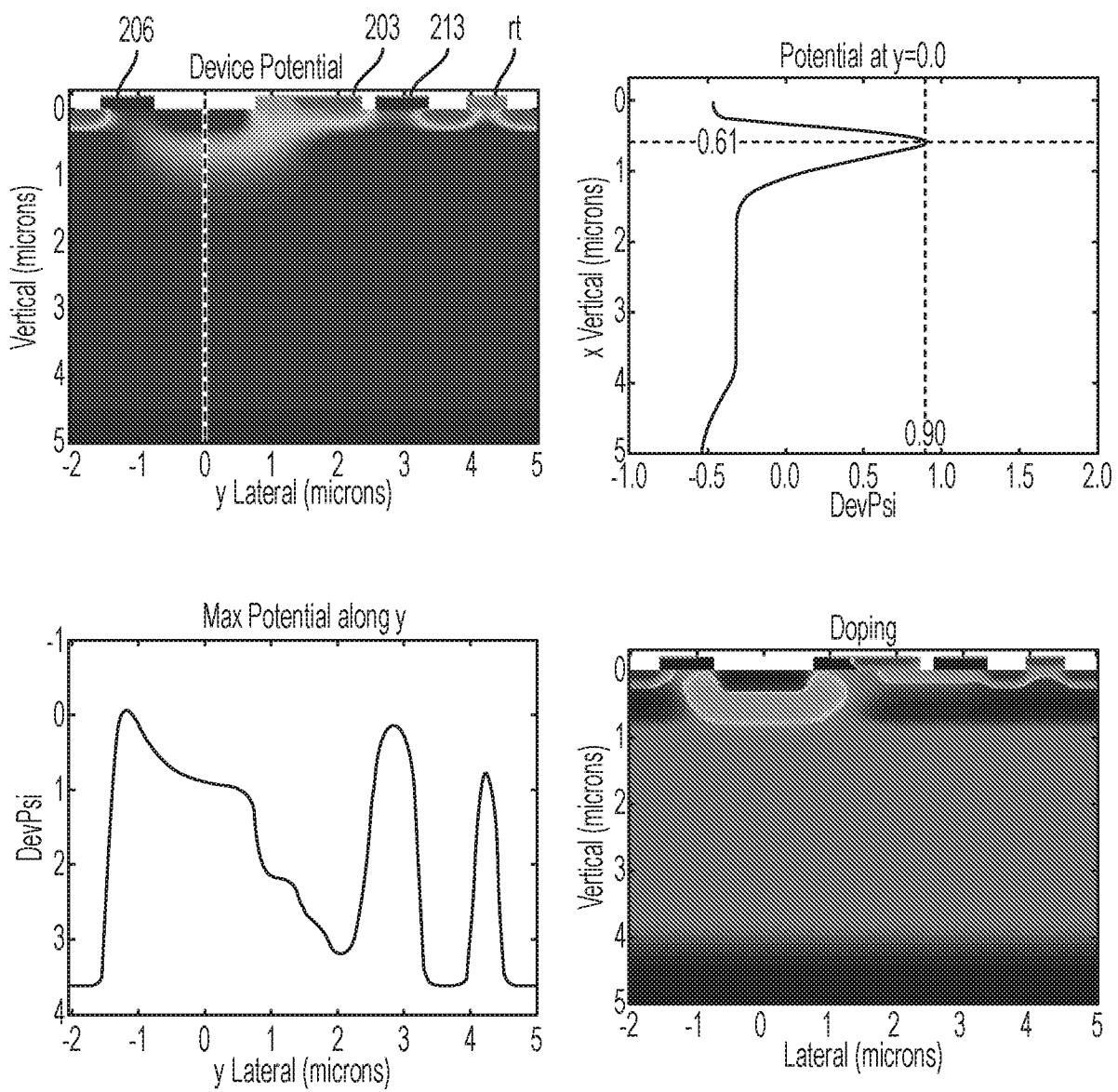

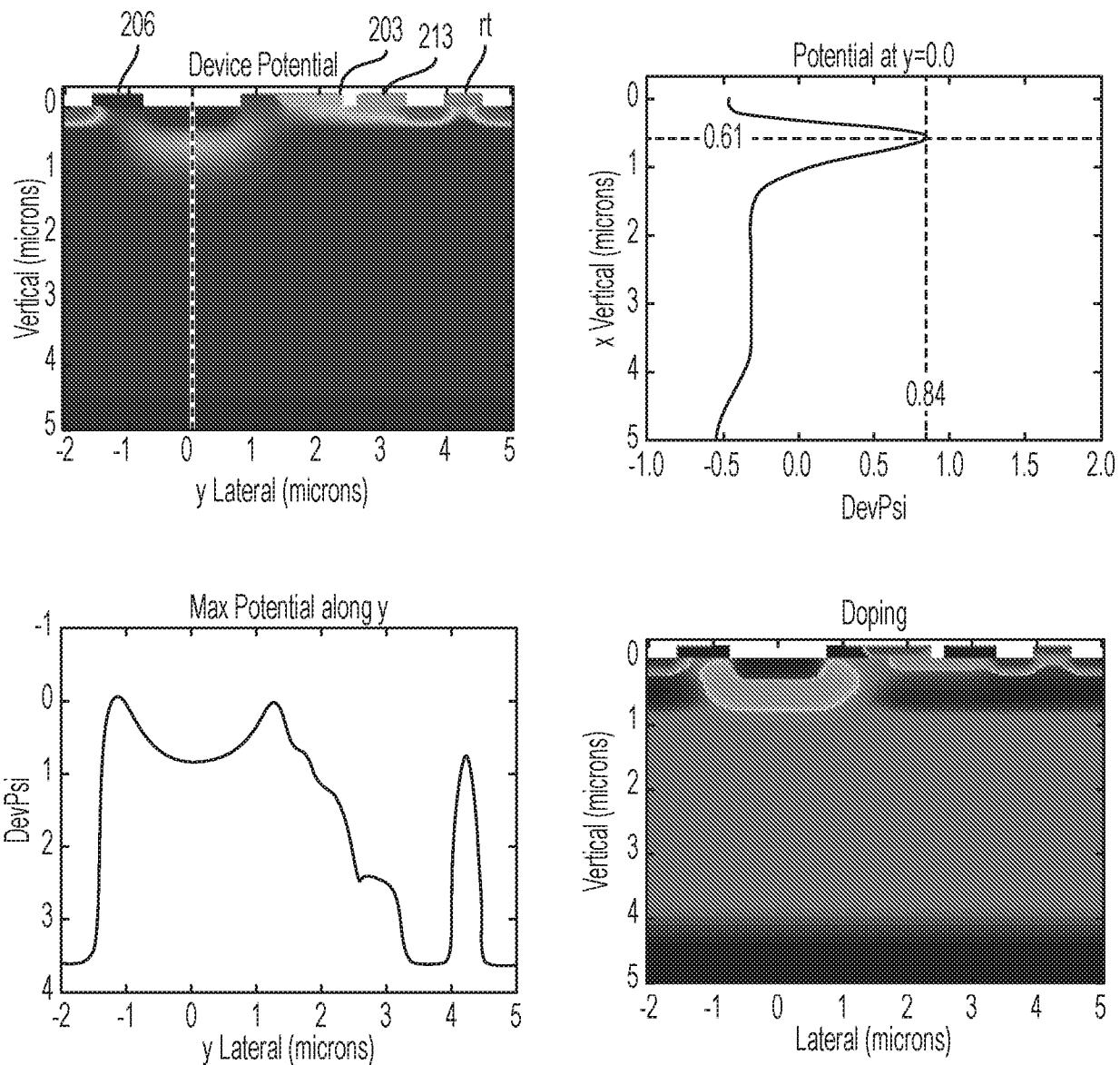

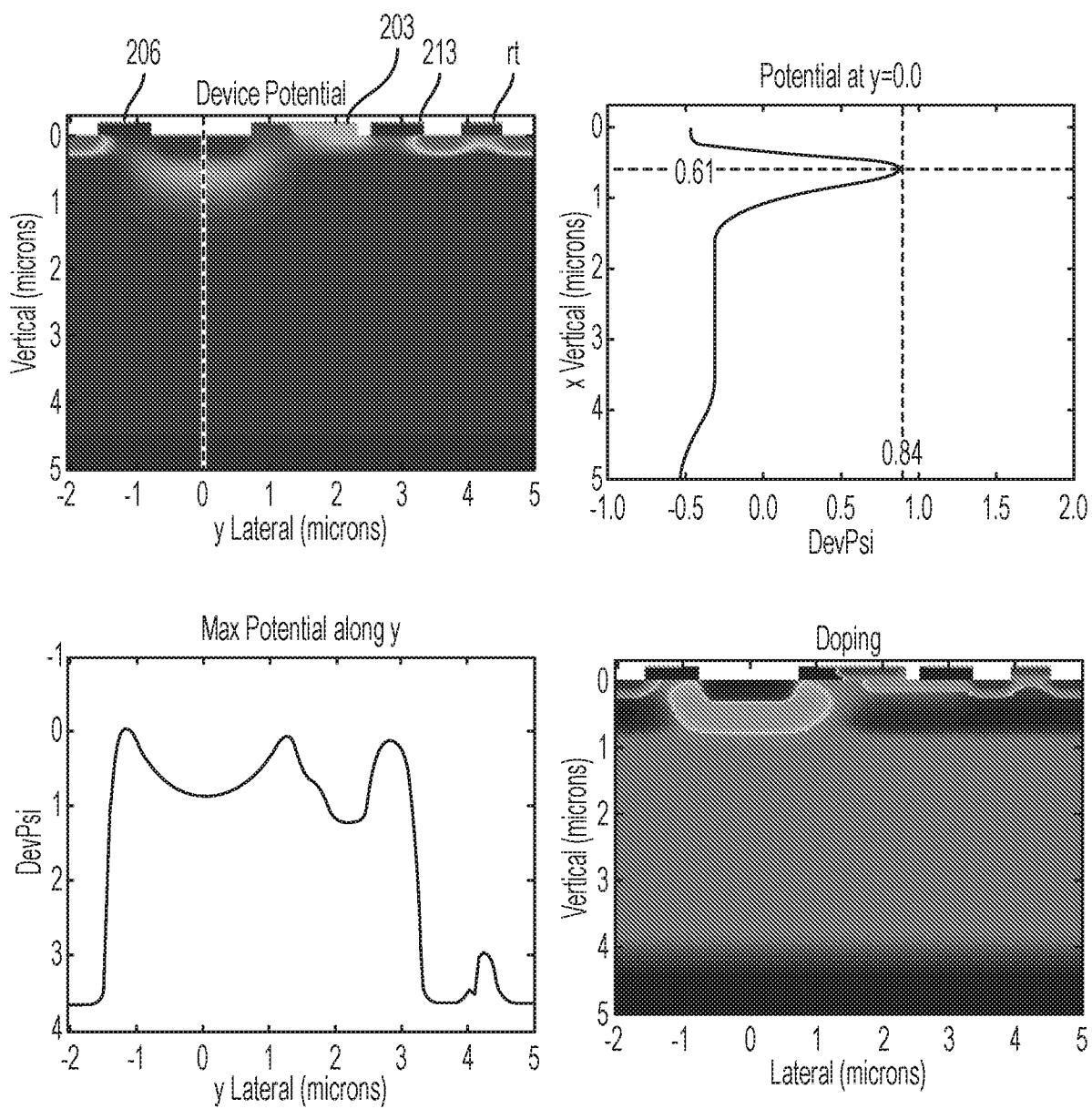

Following step 2808 the measurement 2820 may be repeated  $n-1$  times to obtain information (e.g., statistical information) regarding the time periods at which photons tend to