(19)日本国特許庁(JP)

**(12)特許公報(B2)**

(11)特許番号

**特許第7673807号**

**(P7673807)**

(45)発行日 令和7年5月9日(2025.5.9)

(24)登録日 令和7年4月28日(2025.4.28)

(51)国際特許分類

|        |                |     |        |      |   |

|--------|----------------|-----|--------|------|---|

| H 02 M | 1/00 (2007.01) | F I | H 02 M | 1/00 | H |

| H 02 M | 7/48 (2007.01) |     | H 02 M | 1/00 | E |

|        |                |     | H 02 M | 1/00 | R |

|        |                |     | H 02 M | 7/48 | M |

請求項の数 12 (全20頁)

(21)出願番号 特願2023-535166(P2023-535166)

(86)(22)出願日 令和4年5月25日(2022.5.25)

(86)国際出願番号 PCT/JP2022/021431

(87)国際公開番号 WO2023/286464

(87)国際公開日 令和5年1月19日(2023.1.19)

審査請求日 令和5年6月28日(2023.6.28)

(31)優先権主張番号 特願2021-115321(P2021-115321)

(32)優先日 令和3年7月12日(2021.7.12)

(33)優先権主張国・地域又は機関

日本国(JP)

(73)特許権者 000005234

富士電機株式会社

神奈川県川崎市川崎区田辺新田1番1号

(74)代理人 110000877

弁理士法人 R Y U K A 国際特許事務所

清水 直樹

神奈川県川崎市川崎区田辺新田1番1号

(72)発明者 富士電機株式会社内

審査官 武内 大志

最終頁に続く

(54)【発明の名称】 制御装置およびスイッチング装置

**(57)【特許請求の範囲】****【請求項1】**

主スイッチング素子に短絡が生じたことに応じて、当該主スイッチング素子に流れる電流を制限する保護動作を行う保護部と、

駆動信号に応じて前記主スイッチング素子を駆動制御する駆動制御部への電源供給が停止され、かつ、前記主スイッチング素子に生じた前記短絡が解消するまで前記保護部に保護動作を継続させる保護動作制御部と、

を備える制御装置。

**【請求項2】**

前記保護動作制御部は、

前記短絡が生じた場合に、前記短絡が解消したこと、および、前記電源供給が停止されたことを含む第1解除条件が満たされるまで、前記保護動作を実行すべき旨の情報を保持する第1保持部を有する、請求項1に記載の制御装置。

**【請求項3】**

前記保護動作制御部は、

前記短絡が生じた場合に、前記短絡が解消したこと、および、前記電源供給が再開される場合の基準操作が行われたことを含む第1解除条件が満たされるまで、前記保護動作を実行すべき旨の情報を保持する第1保持部を有する、請求項1に記載の制御装置。

**【請求項4】**

前記保護動作制御部は、前記第1解除条件が満たされることに応じて前記第1保持部を

リセットするリセット部を有する、請求項 2 に記載の制御装置。

**【請求項 5】**

前記第 1 解除条件は、前記主スイッチング素子をオン状態とする前記駆動信号が供給されていないこと、および、前記保護動作の開始から基準時間以上が経過していることをさらに含む、請求項 2 に記載の制御装置。

**【請求項 6】**

前記保護部は、前記主スイッチング素子が基準温度よりも高温になったこと、前記主スイッチング素子に基準電流よりも大きい電流が流れたこと、および、前記電源供給による供給電圧が基準電圧よりも低下したこと、の少なくとも 1 つの異常が生じたことに応じても前記保護動作を行い、

前記保護動作制御部は、前記少なくとも 1 つの異常が生じた場合に、生じた異常が解消したこと、前記主スイッチング素子をオン状態とする前記駆動信号が供給されていないこと、および、前記保護動作の開始から基準時間以上が経過していることを含み、前記電源供給が停止されていることを条件に含まない第 2 解除条件が満たされるまで、前記保護動作を実行すべき旨の情報を保持する第 2 保持部を有する、請求項 2 に記載の制御装置。

**【請求項 7】**

前記保護動作制御部は、前記駆動制御部とは別の電源から電源供給を受ける、請求項 2 に記載の制御装置。

**【請求項 8】**

前記保護動作制御部は、前記駆動制御部と共に電源から電源供給を受けることに応じて、前記保護動作を継続させるか否かの情報を保持する第 3 保持部を有する、請求項 1 に記載の制御装置。

**【請求項 9】**

前記主スイッチング素子に流れる電流に応じたパラメータを測定する測定部と、測定されたパラメータに応じて前記主スイッチング素子に短絡が生じたことを検知する検知部と、

をさらに備える、請求項 1 に記載の制御装置。

**【請求項 10】**

前記保護動作が実行される場合にアラーム信号を出力する出力部をさらに備える、請求項 1 に記載の制御装置。

**【請求項 11】**

前記駆動制御部をさらに備える、請求項 1 から 10 の何れか一項に記載の制御装置。

**【請求項 12】**

請求項 11 に記載の制御装置と、前記主スイッチング素子とを備えるスイッチング装置。

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

本発明は、制御装置およびスイッチング装置に関する。

**【背景技術】**

**【0002】**

従来、主スイッチング素子に短絡が生じた場合には、主スイッチング素子のゲート電圧を制限するなどの保護動作が行われており、短絡の解消に応じて保護動作を解除している（例えば、特許文献 1, 2 参照）。

特許文献 1 特開 2011 - 259233 号公報

特許文献 2 特開平 11 - 4150 号公報

**【解決しようとする課題】**

**【0003】**

しかしながら、短絡の解消に応じて単純に保護動作を解除すると、改めて短絡が生じて素子破壊を引き起こす虞がある。

**【一般的開示】**

10

20

30

40

50

**【 0 0 0 4 】**

上記課題を解決するために、本発明の第1の態様においては、制御装置が提供される。制御装置は、主スイッチング素子に短絡が生じたことに応じて、当該主スイッチング素子に流れる電流を制限する保護動作を行う保護部を備えてよい。制御装置は、駆動信号に応じて主スイッチング素子を駆動制御する駆動制御部への電源供給が停止されるまで保護部に保護動作を継続させる保護動作制御部を備えてよい。

**【 0 0 0 5 】**

保護動作制御部は、短絡が生じた場合に、短絡が解消したこと、および、電源供給が停止されたことを含む第1解除条件が満たされるまで、保護動作を実行すべき旨の情報を保持する第1保持部を有してよい。

10

**【 0 0 0 6 】**

保護動作制御部は、短絡が生じた場合に、短絡が解消したこと、および、電源供給が再開される場合の基準操作が行われたことを含む第1解除条件が満たされるまで、保護動作を実行すべき旨の情報を保持する第1保持部を有してよい。

**【 0 0 0 7 】**

保護動作制御部は、第1解除条件が満たされることに応じて第1保持部をリセットするリセット部を有してよい。

**【 0 0 0 8 】**

第1解除条件は、主スイッチング素子をオン状態とする駆動信号が供給されていないこと、および、保護動作の開始から基準時間以上が経過していることをさらに含んでよい。

20

**【 0 0 0 9 】**

保護部は、主スイッチング素子が基準温度よりも高温になったこと、主スイッチング素子に基準電流よりも大きい電流が流れしたこと、および、電源供給による供給電圧が基準電圧よりも低下したこと、の少なくとも1つの異常が生じたことに応じても保護動作を行つてよい。保護動作制御部は、少なくとも1つの異常が生じた場合に、生じた異常が解消したこと、主スイッチング素子をオン状態とする駆動信号が供給されていないこと、および、保護動作の開始から基準時間以上が経過していることを含み、電源供給が停止されていることを条件に含まない第2解除条件が満たされるまで、保護動作を実行すべき旨の情報を保持する第2保持部を有してよい。

**【 0 0 1 0 】**

30

保護動作制御部は、駆動制御部とは別の電源から電源供給を受けてよい。

**【 0 0 1 1 】**

保護動作制御部は、駆動制御部と共に電源から電源供給を受けることに応じて、保護動作を継続させるか否かの情報を保持する第3保持部を有してよい。

**【 0 0 1 2 】**

制御装置は、主スイッチング素子に流れる電流に応じたパラメータを測定する測定部を備えてよい。制御装置は、測定されたパラメータに応じて主スイッチング素子に短絡が生じたことを検知する検知部を備えてよい。

**【 0 0 1 3 】**

制御装置は、保護動作が実行される場合にアラーム信号を出力する出力部をさらに備えてよい。

40

**【 0 0 1 4 】**

制御装置は、駆動制御部をさらに備えてよい。

**【 0 0 1 5 】**

また、本発明の第2の態様においては、スイッチング装置が提供される。スイッチング装置は、第1の態様の制御装置を備えてよい。スイッチング装置は、主スイッチング素子とを備えてよい。

**【 0 0 1 6 】**

なお、上記の発明の概要は、本発明の必要な特徴の全てを列挙したものではない。また、これらの特徴群のサブコンビネーションもまた、発明となりうる。

50

**【図面の簡単な説明】****【0017】**

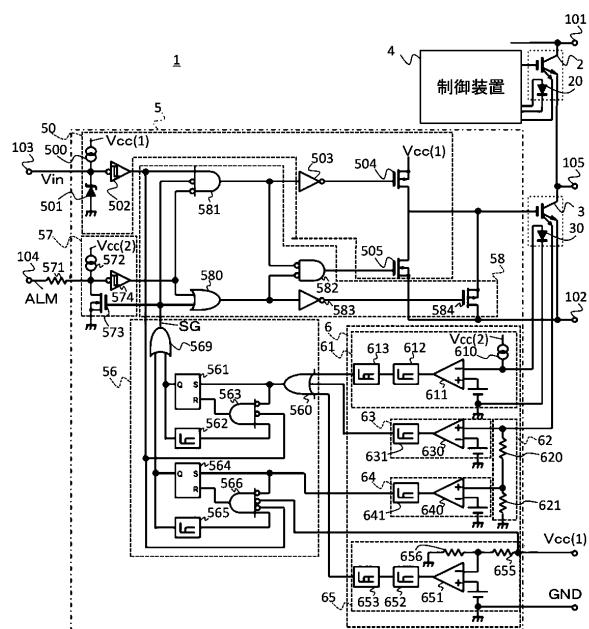

【図1】第1実施形態に係るスイッチング装置1を示す。

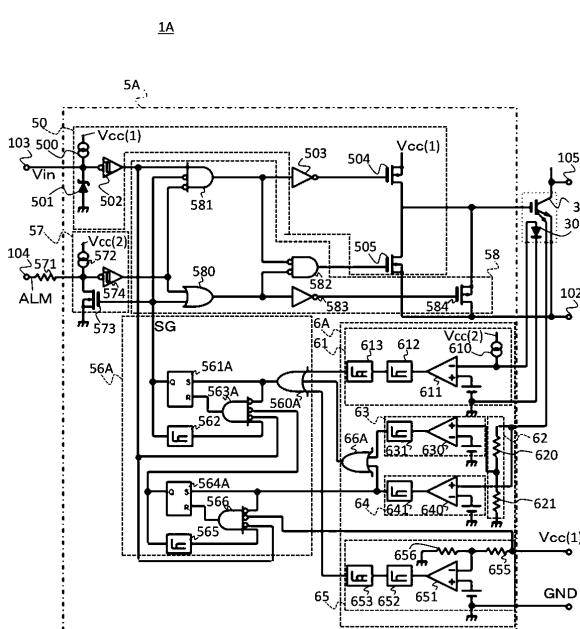

【図2】第2実施形態に係るスイッチング装置1Aを示す。

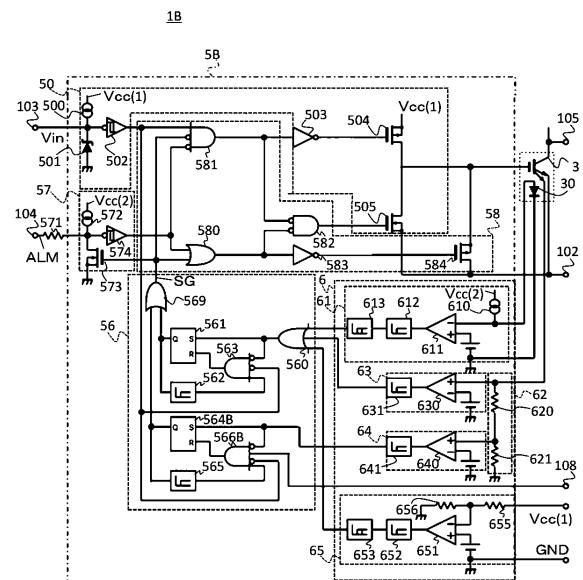

【図3】第3実施形態に係るスイッチング装置1Bを示す。

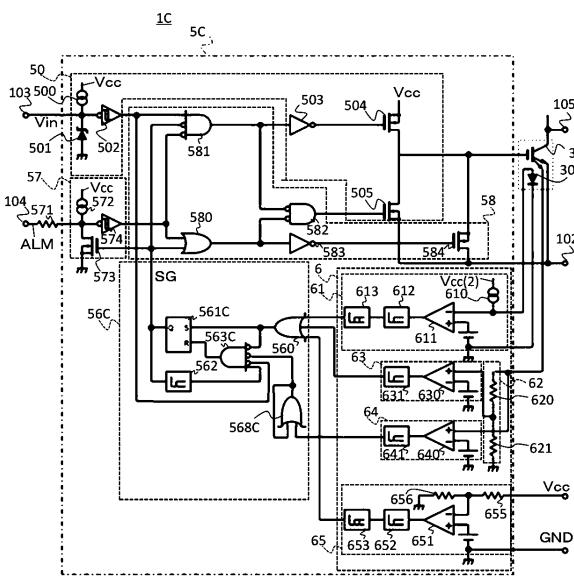

【図4】第4実施形態に係るスイッチング装置1Cを示す。

**【発明を実施するための形態】****【0018】**

以下、発明の実施の形態を通じて本発明を説明するが、以下の実施形態は請求の範囲にかかる発明を限定するものではない。また、実施形態の中で説明されている特徴の組み合10

わせの全てが発明の解決手段に必須であるとは限らない。

**【0019】****[1. 第1実施形態]****[1.1. スイッチング装置]**

図1は、本実施形態に係るスイッチング装置1を示す。スイッチング装置1は、モータ駆動用または電力供給用に用いられる装置であってよく、例えば正側端子101および負側端子102から供給される直流電力を交流電力に変換して電源出力端子105から出力するインバータ装置などの電力変換装置であってよい。また、スイッチング装置1は、異常時に自動で保護動作を行うIPM(インテリジェントパワーモジュール)であってよい。

20

。スイッチング装置1は、正側および負側の主スイッチング素子2,3と、正側および負側の制御装置4,5とを備えてよい。なお、負側端子102は一例としてグランドに接続されてよい。スイッチング装置1には、正側端子101や負側端子102、電源出力端子105に加えて、駆動信号Vinが入力される入力端子103や、アラーム信号ALMを出力するアラーム端子104などが設けられてよい。

**【0020】****[1.1.1. 主スイッチング素子2,3]**

主スイッチング素子2,3は、正側端子101および負側端子102の間に直列に順次接続されている。例えば、主スイッチング素子2,3は、それぞれ正側端子101の側にコレクタ端子が接続され、負側端子102の側にエミッタ端子が接続される。主スイッチング素子2,3は、スイッチング装置における上アームおよび下アームを構成してよく、

30

主スイッチング素子2および主スイッチング素子3の中点には電源出力端子105が接続されてよい。

**【0021】**

主スイッチング素子2,3は、対応する制御装置4,5に接続されるセンスエミッタ端子を有してよい。また、主スイッチング素子2,3の近傍(本実施形態では一例として、主スイッチング素子2,3と同一のチップ内)には、主スイッチング素子2,3の過熱を検知するためのサーマルダイオード20,30が配置されてよく、サーマルダイオード20,30それぞれのアノード端子およびカソード端子とも制御装置4,5に接続されてよい。

**【0022】**

なお、本実施形態では一例として、主スイッチング素子2,3はIGBTであり、正側端子101の側がカソードである寄生ダイオード(図示せず)を有してよい。これに加えて、または、これに代えて、主スイッチング素子2,3のそれぞれには、正側端子101の側がカソードとなるよう還流ダイオード(図示せず)が逆並列に接続されてよい。主スイッチング素子2,3はMOSFETまたはバイポーラトランジスタなど、他構造の半導体素子でもよい。

**【0023】****[1.1.2. 制御装置4,5]**

制御装置4,5は、主スイッチング素子2,3を制御する。正側の制御装置4は主スイッチング素子2を制御対象とし、負側の制御装置5は主スイッチング素子3を制御対象と

40

。

してよい。なお、制御装置 4，5 は同様の構成であるため、本実施形態では負側の制御装置 5 について説明を行い、正側の制御装置 4 については説明を省略する。

#### 【 0 0 2 4 】

制御装置 5 は、主スイッチング素子 3 を制御する。制御装置 5 は、駆動制御部 50 と、異常検知部 6 と、保護動作制御部 56 と、アラーム出力部 57 と、保護部 58 とを有する。なお、駆動制御部 50 と、保護動作制御部 56 とは、別々の電源から電源供給を受けてよく、例えば制御装置 5 における各構成のうち、駆動制御部 50 と、他の構成とは、別々の電源から電源供給を受けてよい。本実施形態では一例として、駆動制御部 50 は一の電源から電圧（制御電圧とも称する） $V_{cc}(1)$  の電源供給を受けてよく、制御装置 5 における他の構成は他の電源から電圧（制御電圧とも称する） $V_{cc}(2)$  の電源供給を受けてよい。なお、電圧 $V_{cc}(1)$  と電圧 $V_{cc}(2)$  は、同じ電圧であってもよいし、異なる電圧であってもよい。

10

#### 【 0 0 2 5 】

##### [ 1 . 1 . 2 ( 1 ) . 駆動制御部 50 ]

駆動制御部 50 は、入力端子 103 に入力される駆動信号 $V_{in}$  に応じて主スイッチング素子 3 を駆動制御する。駆動信号 $V_{in}$  は外部から入力されてよく、主スイッチング素子 3 をオン状態とする信号、および、オフ状態とする信号を含んでよい。例えば、駆動信号 $V_{in}$  は、主スイッチング素子 2, 3 に同期整流方式でスイッチングを行わせてよく、一例として主スイッチング素子 2, 3 の両方がオフとなるデッドタイムを挟んで主スイッチング素子 2, 3 を逐一的に（一例として交互に）接続状態とするよう設定されてよい。なお、本実施形態では一例として、駆動信号 $V_{in}$  はローレベルの場合に主スイッチング素子 3 をオンにすることを指示し、ハイレベルの場合に主スイッチング素子 3 をオフにすることを指示する。

20

#### 【 0 0 2 6 】

駆動制御部 50 は、電流源 500 と、ツエナーダイオード 501 と、反転型シュミットトリガ回路 502 と、NOT ゲート 503 と、スイッチング素子 504 と、スイッチング素子 505 とを有する。

#### 【 0 0 2 7 】

電流源 500 は、主スイッチング素子 3 をオン状態とする駆動信号 $V_{in}$  が入力端子 103 に入力されていない場合に入力端子 103 の電位をハイレベルに維持する。ツエナーダイオード 501 は、入力端子 103 の側にカソード端子を向けて、入力端子 103 とグランドとの間に接続され、入力端子 103 から制御装置 5 に対して過電圧が加わるのを防止する。反転型シュミットトリガ回路 502 は、入力端子 103 に接続されており、ヒステリシスをもって駆動信号 $V_{in}$  のハイレベル / ローレベルを反転させる。反転型シュミットトリガ回路 502 は、反転した駆動信号 $V_{in}$  を、後述の保護部 58 における AND ゲート 581, 582などを介して NOT ゲート 503、スイッチング素子 505 に供給してよい。

30

#### 【 0 0 2 8 】

NOT ゲート 503 は、保護部 58 の AND ゲート 581 と、スイッチング素子 504 との間に設けられる。NOT ゲート 503 は、AND ゲート 581 からの出力信号をさらに反転してスイッチング素子 504 に供給してよい。

40

#### 【 0 0 2 9 】

スイッチング素子 504 は制御電圧 $V_{cc}(1)$  の電源と主スイッチング素子 3 のゲートとの間に接続されている。スイッチング素子 504 は、ターンオン用のスイッチング素子であり、制御電圧 $V_{cc}(1)$  の電源と主スイッチング素子 3 のゲートとの間を導通させることで主スイッチング素子 3 をターンオンする。スイッチング素子 504 は、NOT ゲート 503 から供給される信号がローレベルの場合にターンオンされてよい。なお、本実施形態では一例として、スイッチング素子 504 は、P 型の MOSFET であるが、他構造の半導体素子でもよい。

#### 【 0 0 3 0 】

50

スイッチング素子 505 は主スイッチング素子 3 のゲートと負側端子 102との間に接続されている。スイッチング素子 505 は、ターンオフ用のスイッチング素子であり、主スイッチング素子 3 のゲートと負側端子 102との間を導通させることで主スイッチング素子 3 をターンオフする。スイッチング素子 505 は、AND ゲート 582 から供給される信号がハイレベルの場合にターンオンされてよい。なお、本実施形態では一例として、スイッチング素子 505 は、N 型の MOSFET であるが、他構造の半導体素子でもよい。

#### 【0031】

##### [ 1 . 1 . 2 ( 2 ) . 異常検知部 6 ]

異常検知部 6 は、保護動作を行うべき異常を検知する。本実施形態では一例として、異常には、主スイッチング素子 3 の短絡、主スイッチング素子 3 の過熱、主スイッチング素子 3 の過電流、および、制御電圧低下が含まれる。主スイッチング素子 3 の過熱とは、主スイッチング素子 3 が基準温度よりも高温になることであってよい。主スイッチング素子 3 の過電流とは、主スイッチング素子 3 に基準電流よりも大きい電流が流れることであってよい。制御電圧低下とは、駆動制御部 50 への電源供給による供給電圧 Vcc (1) が基準電圧よりも低下することであってよい。異常検知部 6 は、過熱検知部 61 と、測定部 62 と、過電流検知部 63 と、短絡検知部 64 と、制御電圧低下検知部 65 とを有する。

10

#### 【0032】

##### [ 1 . 1 . 2 ( 2 - 1 ) . 過熱検知部 61 ]

過熱検知部 61 は、主スイッチング素子 3 の過熱を検知する。過熱検知部 61 は、電流源 610 と、コンパレータ 611 と、ローパスフィルタ 612 と、ヒステリシスバッファ 613 とを有する。

20

#### 【0033】

電流源 610 は、サーマルダイオード 30 のアノード端子と、コンパレータ 611 の反転入力端子との間に接続されており、サーマルダイオード 30 に順方向の電流を流す。サーマルダイオード 30 の順方向電圧は、サーマルダイオード 30 が基準温度よりも高温の場合には、サーマルダイオード 30 が基準温度の場合よりも低くてよい。これにより、主スイッチング素子 3 が過熱状態である場合には、非過熱状態である場合よりも低い電圧がコンパレータ 611 の反転入力端子に印加される。コンパレータ 611 の非反転入力端子には、基準電位が接続される。コンパレータ 611 の基準電位は、主スイッチング素子 3 が基準温度の場合の反転入力端子の電位と等しくてよい。これにより、主スイッチング素子 3 が過熱状態となることに応じてコンパレータ 611 の出力信号がハイレベルとなる。コンパレータ 611 は、ローパスフィルタ 612 およびヒステリシスバッファ 613 を介して出力信号を保護動作制御部 56 に供給してよい。

30

#### 【0034】

ローパスフィルタ 612 はコンパレータ 611 からの出力信号に含まれる高周波成分を除去してよい。ヒステリシスバッファ 613 は、ヒステリシスをもってコンパレータ 611 からの出力信号をバッファリングし、出力信号のばたつきを防止してよい。

#### 【0035】

##### [ 1 . 1 . 2 ( 2 - 2 ) . 測定部 62 ]

測定部 62 は、主スイッチング素子 3 に流れる電流に応じたパラメータを測定する。主スイッチング素子 3 に流れる電流は、スイッチング素子 3 に流れる電流の瞬時値であってよい。本実施形態においては一例として、測定部 62 は、主スイッチング素子 3 のセンスエミッタ端子とグランドとの間に直列に接続された 2 つの抵抗 620, 621 を有してよい。測定部 62 は、センスエミッタ電流が抵抗 620, 621 の両方を流れることに応じて検出される電圧を過電流検知部 63 に供給し、センスエミッタ電流がグランド側の抵抗 621 を流れることに応じて検出される電圧を短絡検知部 64 に供給してよい。

40

#### 【0036】

##### [ 1 . 1 . 2 ( 2 - 3 ) . 過電流検知部 63 ]

過電流検知部 63 は、主スイッチング素子 3 の過電流を検知する。過電流検知部 63 は、測定部 62 により測定されたパラメータに応じて主スイッチング素子 3 に過電流が流れ

50

たことを検知してよい。過電流とは、基準電流（一例として主スイッチング素子3の定格電流）より大きい電流であってよく、主スイッチング素子3が短絡した場合に流れる電流よりも小さい電流であってよい。過電流検知部63は、コンパレータ630と、ローパスフィルタ631とを有する。

#### 【0037】

コンパレータ630の非反転入力端子には測定部62の抵抗620と、主スイッチング素子3のセンスエミッタ端子との間の接続点が接続され、コンパレータ630の反転入力端子には基準電位が接続される。コンパレータ630の基準電位は、主スイッチング素子3に流れる電流が上述の基準電流である場合の非反転入力端子の電位と等しくてよい。これにより、主スイッチング素子3が過電流状態となることに応じてコンパレータ630の出力信号がハイレベルとなる。コンパレータ630は、ローパスフィルタ631を介して出力信号を保護動作制御部56に供給してよい。ローパスフィルタ631はコンパレータ630からの出力信号に含まれる高周波成分を除去してよい。

#### 【0038】

##### [ 1 . 1 . 2 ( 2 - 4 ) . 短絡検知部 64 ]

短絡検知部64は、主スイッチング素子3の短絡を検知する。短絡検知部64は、測定部62により測定されたパラメータに応じて主スイッチング素子3に短絡が生じたことを検知してよい。短絡検知部64は、コンパレータ640と、ローパスフィルタ641とを有する。

#### 【0039】

コンパレータ640の非反転入力端子には測定部62の抵抗620, 621の間の接続点が接続され、コンパレータ640の反転入力端子には基準電位が接続される。コンパレータ640の基準電位は、主スイッチング素子3が短絡状態となっていない場合での非反転入力端子の電位より高くてよく、主スイッチング素子3が短絡状態となった場合での非反転入力端子の電位よりも低くてよい。これにより、主スイッチング素子3が短絡状態となることに応じてコンパレータ640の出力信号がハイレベルとなる。コンパレータ640は、ローパスフィルタ641を介して出力信号を保護動作制御部56に供給してよい。ローパスフィルタ641はコンパレータ640からの出力信号に含まれる高周波成分を除去してよい。

#### 【0040】

##### [ 1 . 1 . 2 ( 2 - 5 ) . 制御電圧低下検知部 65 ]

制御電圧低下検知部65は、制御電圧低下を検知する。本実施形態では一例として、制御電圧低下検知部65は、制御電圧Vcc(1)が低下したこと検知してよい。制御電圧低下検知部65は、抵抗655, 656と、コンパレータ651と、ローパスフィルタ652と、ヒステリシスバッファ653とを有する。

#### 【0041】

抵抗655, 656は、制御電圧Vcc(1)とグランドとの間に直列に接続される。抵抗655, 656の間の接続点はコンパレータ651の反転入力端子に接続されてよく、コンパレータ651の非反転入力端子には基準電位が接続されてよい。コンパレータ651の基準電位は、制御電圧Vcc(1)が基準電圧である場合の反転入力端子の電位と等しくてよい。基準電圧は一例として、駆動制御部50が正常に動作する制御電圧Vcc(1)の最小電圧であってよい。これにより、制御電圧Vcc(1)が基準電圧よりも低下することに応じてコンパレータ651の出力信号がハイレベルとなる。コンパレータ651は、ローパスフィルタ652およびヒステリシスバッファ653を介して出力信号を保護動作制御部56に供給してよい。

#### 【0042】

ローパスフィルタ652およびヒステリシスバッファ653は、過熱検知部61のローパスフィルタ612およびヒステリシスバッファ613と同様のものであってよい。

#### 【0043】

##### [ 1 . 1 . 2 ( 3 ) . 保護動作制御部 56 ]

10

20

30

40

50

保護動作制御部 56 は、主スイッチング素子 3 の短絡、主スイッチング素子 3 の過熱、主スイッチング素子 3 の過電流、および、制御電圧低下のうちの何れかの異常が生じたことに応じて保護部 58 に保護動作を行わせる。保護動作制御部 56 は、保護部 58 に供給する保護制御信号 SG をハイレベルにすることで保護動作を行わせて良い。保護動作制御部 56 は、OR ゲート 560 と、SR 型フリップフロップ 561 と、遅延回路 562 と、AND ゲート 563 と、SR 型フリップフロップ 564 と、遅延回路 565 と、AND ゲート 566 と、OR ゲート 569 を有する。

#### 【0044】

[ 1 . 1 . 2 ( 3 - 1 ) . OR ゲート 560 ]

OR ゲート 560 は、過熱検知部 61、過電流検知部 63 および制御電圧低下検知部 65 の出力端子に接続される。OR ゲート 560 は、過熱検知部 61、過電流検知部 63 および制御電圧低下検知部 65 からの出力信号の論理和をとってよい。OR ゲート 560 は、演算結果を SR 型フリップフロップ 561 に供給してよい。

10

#### 【0045】

[ 1 . 1 . 2 ( 3 - 2 ) . SR 型フリップフロップ 561 ]

SR 型フリップフロップ 561 は、OR ゲート 560 の出力端子に接続される。SR 型フリップフロップ 561 は、第 2 保持部の一例であり、主スイッチング素子 3 の過熱、主スイッチング素子 3 の過電流、および、制御電圧低下のうち少なくとも 1 つの異常が生じた場合に、後述の第 2 解除条件が満たされるまで、保護動作を実行すべき旨の情報を保持する。SR 型フリップフロップ 561 は、セット状態となることによって、保護動作を実行すべき旨の情報の保持を行い、リセットされることで、当該情報をリセットしてよい。

20

#### 【0046】

SR 型フリップフロップ 561 のセット端子には OR ゲート 560 の出力端子が接続されてよく、SR 型フリップフロップ 561 は OR ゲート 560 からの信号がハイレベルとなることに応じてセットされてよい。これにより、主スイッチング素子 3 の過熱、主スイッチング素子 3 の過電流、および、制御電圧低下のうち少なくとも 1 つの異常が生じることにより SR 型フリップフロップ 561 がセットされる。

#### 【0047】

SR 型フリップフロップ 561 のリセット端子には後述の AND ゲート 563 の出力端子が接続されてよく、SR 型フリップフロップ 561 は AND ゲート 563 からの出力信号がハイレベルとなることに応じてリセットされてよい。

30

#### 【0048】

SR 型フリップフロップ 561 は、セット状態でハイレベルの信号を出力し、リセット状態でローレベルの信号を出力してよい。SR 型フリップフロップ 561 は、OR ゲート 569 および遅延回路 562 に出力信号を供給してよい。

#### 【0049】

[ 1 . 1 . 2 ( 3 - 3 ) . 遅延回路 562 ]

遅延回路 562 は、SR 型フリップフロップ 561 の出力端子に接続される。遅延回路 562 は、SR 型フリップフロップ 561 によるハイレベルの信号出力の開始から基準時間が以上が経過している場合にハイレベルとなる信号を出力してよい。本実施形態では一例として遅延回路 562 は、SR 型フリップフロップ 561 によるハイレベルの出力信号が基準時間以上に継続する場合にハイレベルとなる信号を出力してよく、SR 型フリップフロップ 561 の出力信号と、SR 型フリップフロップ 561 の出力信号を基準時間だけ遅延させた信号との論理積をとる。遅延回路 562 は、出力信号を AND ゲート 563 に供給してよい。基準時間は、遅延回路 562 に対して任意に設定される時間であってよい。一例として、基準時間は、アラーム出力部 57 がアラーム信号 ALM を出力するべき最小の時間であってよい。

40

#### 【0050】

[ 1 . 1 . 2 ( 3 - 4 ) . AND ゲート 563 ]

AND ゲート 563 は、OR ゲート 560、遅延回路 562 および反転型シュミットト

50

リガ回路 502 と、SR型フリップフロップ 561 のリセット端子との間に設けられる。ANDゲート 563 は、第2解除条件が満たされることに応じて SR型フリップフロップ 561 をリセットする。

#### 【0051】

第2解除条件は、主スイッチング素子3の過熱、主スイッチング素子3の過電流、および、制御電圧低下のうち、生じた異常が解消したこと、主スイッチング素子3をオン状態とする駆動信号Vi<sub>n</sub>が供給されていないこと、および、保護動作の開始から基準時間以上が経過していることを含む。ここで、第2解除条件では、後述の第1解除条件と異なり、駆動制御部50への電源供給が停止されていることが条件に含まれない。異常が解消したことは、異常が生じていない状態にあることであってよい。主スイッチング素子3をオン状態とする駆動信号Vi<sub>n</sub>が供給されていないとは、駆動信号Vi<sub>n</sub>の供給が停止されることであってもよいし、主スイッチング素子3をオフ状態とする駆動信号Vi<sub>n</sub>が供給されていることであってもよい。

10

#### 【0052】

本実施形態では一例として、ANDゲート563は、ORゲート560からの出力信号（本実施形態では一例として、過熱検知部61、過電流検知部63および制御電圧低下検知部65からの出力信号の論理和）の反転信号と、反転型シユミットトリガ回路502からの出力信号（本実施形態では一例として、反転した駆動信号Vi<sub>n</sub>）の反転信号と、遅延回路562からの出力信号との論理積をとることで、第2解除条件が満たされるか否かを検知してよい。ANDゲート563は、演算結果をSR型フリップフロップ561のリセット端子に供給してよい。

20

#### 【0053】

##### [1.1.2(3-5).SR型フリップフロップ564]

SR型フリップフロップ564は、短絡検知部64の出力端子に接続される。SR型フリップフロップ564は、第1保持部の一例であり、短絡が生じた場合に、後述の第1解除条件が満たされるまで、保護動作を実行すべき旨の情報を保持する。SR型フリップフロップ564は、セット状態となることによって、保護動作を実行すべき旨の情報の保持を行い、リセットされることで、当該情報をリセットしてよい。

#### 【0054】

SR型フリップフロップ564のセット端子には短絡検知部64の出力端子が接続されてよく、SR型フリップフロップ564は短絡検知部64からの信号がハイレベルとなることに応じてセットされてよい。これにより、主スイッチング素子3の短絡が生じることによりSR型フリップフロップ564がセットされる。

30

#### 【0055】

SR型フリップフロップ564のリセット端子には後述のANDゲート566の出力端子が接続されてよく、SR型フリップフロップ564は、ANDゲート566からの出力信号がハイレベルとなることに応じてリセットされてよい。

#### 【0056】

SR型フリップフロップ564は、セット状態でハイレベルの信号を出力し、リセット状態でローレベルの信号を出力してよい。SR型フリップフロップ564は、ORゲート569および遅延回路565に出力信号を供給してよい。

40

#### 【0057】

##### [1.1.2(3-6).遅延回路565]

遅延回路565は、SR型フリップフロップ564の出力端子に接続される。遅延回路565は、SR型フリップフロップ564によるハイレベルの信号出力の開始から基準時間が経過している場合にハイレベルとなる信号を出力してよい。本実施形態では一例として遅延回路565は、SR型フリップフロップ564によるハイレベルの出力信号が基準時間以上に継続する場合にハイレベルとなる信号を出力してよく、SR型フリップフロップ564の出力信号と、SR型フリップフロップ564の出力信号を基準時間だけ遅延させた信号との論理積をとる。遅延回路565は、出力信号をANDゲート566に供

50

給してよい。基準時間は、遅延回路 565 に対して任意に設定される時間であってよい。一例として、基準時間は、アラーム出力部 57 がアラーム信号 A L M を出力するべき最小の時間であってよい。

#### 【0058】

[ 1 . 1 . 2 ( 3 - 7 ) . AND ゲート 566 ]

AND ゲート 566 は、短絡検知部 64、制御電圧低下検知部 65、遅延回路 565 および反転型シュミットトリガ回路 502 と、SR 型フリップフロップ 564 のリセット端子との間に設けられる。AND ゲート 566 は、リセット部の一例であり、第 1 解除条件が満たされることに応じて SR 型フリップフロップ 564 をリセットする。

#### 【0059】

第 1 解除条件は、短絡が解消したこと、および、駆動制御部 50 への電源供給が停止されたことを含む。これにより、短絡が生じた場合には、駆動制御部 50 への電源供給が停止されるまで保護部 58 の保護動作が継続される。短絡が解消したとは、短絡が生じていない状態にあることであってよい。電源供給が停止されたことは、電源供給が停止された状態にあることであってもよいし、電源供給が一旦停止されたことであってもよい。第 1 解除条件は、主スイッチング素子 3 をオン状態とする駆動信号 V in が供給されていないこと、および、保護動作の開始から基準時間以上が経過していることをさらに含んでよい。

#### 【0060】

本実施形態では一例として、AND ゲート 566 は、短絡検知部 64 からの出力信号の反転信号と、制御電圧低下検知部 65 の抵抗 655, 656 によって検出される電圧信号の反転信号と、反転型シュミットトリガ回路 502 からの出力信号（本実施形態では一例として、反転した駆動信号 V in の反転信号と、遅延回路 565 からの出力信号との論理積をとつてよい。ここで、制御電圧低下検知部 65 の抵抗 655, 656 によって検出される電圧信号は、駆動制御部 50 への電源供給が停止されない限りハイレベルであってよく、電源供給が停止される場合にはローレベルであってよい。AND ゲート 566 は、演算結果を SR 型フリップフロップ 564 のリセット端子に供給してよい。

#### 【0061】

[ 1 . 1 . 2 ( 3 - 8 ) . OR ゲート 569 ]

OR ゲート 569 は、SR 型フリップフロップ 561, 564 の出力端子に接続される。OR ゲート 569 は、SR 型フリップフロップ 561, 564 の出力信号の論理和をとつてよい。OR ゲート 569 は、演算結果の信号を保護制御信号 SG として保護部 58 と、アラーム出力部 57 とに供給してよい。

#### 【0062】

[ 1 . 1 . 2 ( 4 ) . アラーム出力部 57 ]

アラーム出力部 57 は、出力部の一例であり、保護動作が実行される場合にアラーム端子 104 からアラーム信号 A L M を出力する。アラーム信号 A L M は、保護動作が実行されていない場合にはハイレベルであってよく、保護動作が実行されている場合にローレベルとなることでオペレータに警報を行ってよい。アラーム端子 104 には抵抗 571 が接続されてよい。アラーム出力部 57 は、電流源 572 と、スイッチング素子 573 と、反転型シュミットトリガ回路 574 とを有する。

#### 【0063】

電流源 572 は、アラーム端子 104 と接続されており、抵抗 571 を介してアラーム端子 104 から外部に電流を流すことで、アラーム端子 104 から出力されるアラーム信号 A L M をハイレベルに維持する。スイッチング素子 573 は、電流源 572 およびアラーム端子 104 の間の接続点と、グランドとの間に接続されている。スイッチング素子 573 は、ノーマリーオフであり、保護動作を実行させる場合に保護動作制御部 56 からの保護制御信号 SG がハイレベルとなることに応じてターンオンされ、電流源 572 からの電流をグランドに流す。これにより、アラーム端子 104 から出力されるアラーム信号 A L M がローレベルになる。スイッチング素子 573 は、一例として N 型の MOSFET であってよい。反転型シュミットトリガ回路 574 は、アラーム端子 104 に接続されてお

10

20

30

40

50

り、ヒステリシスをもってアラーム信号 A L M のハイレベル / ローレベルを反転させる。アラーム信号 A L M がローレベルからハイレベルに切り替わる場合の第 1 の閾値は、ハイレベルからローレベルに切り替わる場合の第 2 の閾値よりも高くてよい。これにより、保護動作制御部 5 6 からの保護制御信号 S G がハイレベルからローレベルに切り替わった場合でも、アラーム信号 A L M が第 2 の閾値を超えて確実にハイレベルとなるまでは反転型シュミットトリガ回路 5 7 4 の出力はハイレベルに維持される。反転型シュミットトリガ回路 5 7 4 は、反転したアラーム信号 A L M を保護部 5 8 に供給してよい。

#### 【 0 0 6 4 】

##### [ 1 . 1 . 2 ( 5 ) . 保護部 5 8 ]

保護部 5 8 は、過熱や過電流、短絡、制御電圧低下などの異常が検知されたことに応じて、主スイッチング素子 3 に流れる電流を制限する保護動作を行う。保護部 5 8 は、過熱検知部 6 1 や過電流検知部 6 3 、短絡検知部 6 4 、制御電圧低下検知部 6 5 により異常が検知されたことに応じて保護動作を行ってよい。保護部 5 8 は、O R ゲート 5 8 0 と、A N D ゲート 5 8 1 , 5 8 2 と、N O T ゲート 5 8 3 と、スイッチング素子 5 8 4 とを有する。

10

#### 【 0 0 6 5 】

O R ゲート 5 8 0 は、保護動作制御部 5 6 およびアラーム出力部 5 7 の出力端子に接続される。O R ゲート 5 8 0 は、保護動作制御部 5 6 からの保護制御信号 S G と、アラーム出力部 5 7 の反転型シュミットトリガ回路 5 7 4 によるアラーム信号 A L M の反転信号との論理和をとってよい。O R ゲート 5 8 0 は、演算結果を A N D ゲート 5 8 2 およびN O T ゲート 5 8 3 に供給してよい。

20

#### 【 0 0 6 6 】

A N D ゲート 5 8 1 は、駆動制御部 5 0 の反転型シュミットトリガ回路 5 0 2 、保護動作制御部 5 6 およびアラーム出力部 5 7 の出力端子に接続される。A N D ゲート 5 8 1 は、駆動制御部 5 0 の反転型シュミットトリガ回路 5 0 2 により反転された駆動信号 V i n と、保護動作制御部 5 6 からの保護制御信号 S G を反転した信号と、アラーム出力部 5 7 の反転型シュミットトリガ回路 5 7 4 によるアラーム信号 A L M の反転信号をさらに反転した信号との論理積をとってよい。

#### 【 0 0 6 7 】

これにより、保護制御信号 S G により保護動作の実行が指示されている場合、および / または、アラーム信号 A L M により警報が行われている場合には、A N D ゲート 5 8 1 の出力は、反転型シュミットトリガ回路 5 0 2 の出力信号、ひいては駆動信号 V i n に関わらずローレベルとなる。また、保護制御信号 S G により保護動作の実行が指示されておらず、かつ、アラーム信号 A L M により警報が行われていない場合には、A N D ゲート 5 8 1 の出力は、反転型シュミットトリガ回路 5 0 2 の出力と一致する。

30

#### 【 0 0 6 8 】

A N D ゲート 5 8 1 は、N O T ゲート 5 0 3 を介して、主スイッチング素子 3 のターンオン用のスイッチング素子 5 0 4 に出力信号を供給してよい。これにより、保護制御信号 S G により保護動作の実行が指示されている場合、および / または、アラーム信号 A L M により警報が行われている場合には、駆動信号 V i n に関わらず、スイッチング素子 5 0 4 がオフ状態に維持される。また、保護制御信号 S G により保護動作の実行が指示されておらず、かつ、アラーム信号 A L M により警報が行われていない場合には、駆動信号 V i n に応じてスイッチング素子 5 0 4 が制御される。

40

A N D ゲート 5 8 1 は、出力信号を A N D ゲート 5 8 2 にも供給してよい。

#### 【 0 0 6 9 】

A N D ゲート 5 8 2 は、A N D ゲート 5 8 1 およびO R ゲート 5 8 0 の出力端子に接続される。A N D ゲート 5 8 2 は、A N D ゲート 5 8 1 の出力信号の反転信号と、O R ゲート 5 8 0 の出力信号の反転信号との論理積をとってよい。

#### 【 0 0 7 0 】

これにより、保護制御信号 S G により保護動作の実行が指示されている場合、および /

50

または、アラーム信号 A L M により警報が行われている場合には、A N D ゲート 5 8 2 の出力は、A N D ゲート 5 8 1 の出力信号、ひいては反転型シュミットトリガ回路 5 0 2 の出力信号や駆動信号 V i n に関わらずローレベルとなる。また、保護制御信号 S G により保護動作の実行が指示されておらず、かつ、アラーム信号 A L M により警報が行われていない場合には、A N D ゲート 5 8 2 の出力は、A N D ゲート 5 8 1 の出力信号の反転信号、ひいては反転型シュミットトリガ回路 5 0 2 の出力の反転信号や駆動信号 V i n と一致する。

#### 【 0 0 7 1 】

A N D ゲート 5 8 2 は、主スイッチング素子 3 のターンオフ用のスイッチング素子 5 0 5 に出力信号を供給してよい。これにより、保護制御信号 S G により保護動作の実行が指示されている場合、および / または、アラーム信号 A L M により警報が行われている場合には、駆動信号 V i n に関わらず、スイッチング素子 5 0 5 がオフ状態に維持される。また、保護制御信号 S G により保護動作の実行が指示されておらず、かつ、アラーム信号 A L M により警報が行われていない場合には、駆動信号 V i n に応じてスイッチング素子 5 0 5 が制御される。

#### 【 0 0 7 2 】

N O T ゲート 5 8 3 は、O R ゲート 5 8 0 の出力端子に接続されており、O R ゲート 5 8 0 の出力信号を反転する。N O T ゲート 5 8 3 は、スイッチング素子 5 8 4 に出力信号を供給してよい。

#### 【 0 0 7 3 】

スイッチング素子 5 8 4 は、主スイッチング素子 3 のゲートと負側端子 1 0 2 との間に、スイッチング素子 5 0 5 と並列に接続されている。スイッチング素子 5 8 4 は、主スイッチング素子 3 をソフトシャットダウンするためのスイッチング素子であり、主スイッチング素子 3 のゲートと負側端子 1 0 2 との間を導通させることで主スイッチング素子 3 をターンオフする。スイッチング素子 5 8 4 のスイッチング速度は、スイッチング素子 5 0 5 のスイッチング速度よりも低くてよい。スイッチング素子 5 0 5 は、N O T ゲート 5 8 3 から供給される信号がローレベルの場合にターンオンされてよい。なお、本実施形態では一例として、スイッチング素子 5 0 5 は、P 型のM O S F E T であるが、他構造の半導体素子でもよい。

#### 【 0 0 7 4 】

以上のスイッチング装置 1 によれば、短絡が生じたことより行われる保護動作は、駆動制御部 5 0 への電源供給が停止されるまで継続される。従って、短絡の原因が除去されずに保護動作が解除されてしまうのを防止し、保護動作の解除による素子の二次的な破壊を防止することができる。

#### 【 0 0 7 5 】

また、短絡が生じた場合に、短絡が解消したこと、および、電源供給が停止されたことを含む第 1 解除条件が満たされるまで、保護動作を実行すべき旨の情報がS R 型フリップフロップ 5 6 4 に保持される。従って、短絡の原因が除去されずに保護動作が解除されてしまうのを確実に防止することができる。

#### 【 0 0 7 6 】

また、第 1 解除条件が満たされることに応じてS R 型フリップフロップ 5 6 4 がリセットされるので、第 1 解除条件が満たされた場合に保護動作を解除して正常状態での運転を再開することができる。

#### 【 0 0 7 7 】

また、第 1 解除条件には、主スイッチング素子 3 をオン状態とする駆動信号 V i n が供給されていないことがさらに含まれるので、主スイッチング素子 3 がオフである状態で保護動作を解除して、運転を再開することができる。また、第 1 解除条件には、保護動作の開始から基準時間以上が経過していることが含まれるので、基準時間内で連続して短絡が生じてしまうのを防止することができる。また、少なくとも基準時間が経過するまでは保護動作が解除されないため、アラーム信号 A L M を基準時間に亘って継続して出力させる

10

20

30

40

50

ことができる。

#### 【0078】

また、主スイッチング素子3の過熱、主スイッチング素子3の過電流、および、制御電圧低下の少なくとも1つの異常が生じた場合には、第2解除条件が満たされるまで、保護動作を実行すべき旨の情報がSR型フリップフロップ561に保持される。そして、第2解除条件は、異常が解消したこと、主スイッチング素子3をオン状態とする駆動信号Vi nが供給されていないこと、および、保護動作の開始から基準時間以上が経過していることを含み、電源供給が停止されていることを条件に含まない。従って、主スイッチング素子3の過熱や過電流、制御電圧Vcc(1)の低下による保護動作では、電源供給の停止を条件とせずに速やかに保護動作を解除して、正常状態での運転を再開することができる。

10

#### 【0079】

また、保護動作が実行される場合にアラーム信号ALMが出力されるので、異常を報知して異常要因の除去や電源供給の停止を促すことができる。

#### 【0080】

また、保護動作制御部56は駆動制御部50とは別の電源から電源供給を受けるので、駆動制御部50への電源供給が停止した場合にも制御を継続することができる。

#### 【0081】

##### [2. 第2実施形態]

図2は、第2実施形態に係るスイッチング装置1Aを示す。スイッチング装置1Aの制御装置5Aは、異常検知部6Aと、保護動作制御部56Aとを備える。なお、図2や、後述の図3、図4では、主スイッチング素子2や、その制御装置の図示を省略している。また、本実施形態や、後述の他の実施形態において、図1に示されたスイッチング装置1と略同一のものには同一の符号を付け、説明を省略する。

20

#### 【0082】

異常検知部6Aは、過電流検知部63および短絡検知部64の出力端子に接続されたORゲート66Aを有する。ORゲート66Aは、過電流検知部63および短絡検知部64の出力信号の論理和をとって、演算結果を保護動作制御部56Aに供給してよい。

#### 【0083】

保護動作制御部56Aは、ORゲート560A、SR型フリップフロップ564A、ANDゲート563AおよびSR型フリップフロップ561Aを有してよい。

30

#### 【0084】

ORゲート560Aは、過熱検知部61、ORゲート66Aおよび制御電圧低下検知部65の出力端子に接続される。ORゲート560Aは、過熱検知部61、ORゲート66Aおよび制御電圧低下検知部65からの出力信号の論理和をとってよい。ORゲート560Aは、演算結果をSR型フリップフロップ561Aのセット端子に供給してよい。これにより、過熱検知部61、過電流検知部63、短絡検知部64および制御電圧低下検知部65からの出力信号の論理和がとられ、何れかの出力信号がハイレベルとなることに応じてSR型フリップフロップ561Aがセットされる。

#### 【0085】

SR型フリップフロップ564Aは、短絡検知部64およびANDゲート566の出力端子に接続される。SR型フリップフロップ564Aは、上述の第1実施形態におけるSR型フリップフロップ564と同様に、短絡検知部64からの信号がハイレベルとなることに応じてセットされ、ANDゲート566からの出力信号がハイレベルとなることに応じてリセットされてよい。SR型フリップフロップ564Aは、セット状態でハイレベルの信号を、リセット状態でローレベルの信号を、遅延回路565およびANDゲート563Aに供給してよい。

40

#### 【0086】

ANDゲート563Aは、ORゲート560、遅延回路562、反転型シュミットトリガ回路502およびSR型フリップフロップ564Aと、SR型フリップフロップ561Aのリセット端子との間に設けられる。ANDゲート563Aは、第3解除条件が満たさ

50

れることに応じて S R 型フリップフロップ 5 6 1 A をリセットする。

【 0 0 8 7 】

第 3 解除条件は、駆動制御部 5 0 への電源供給が停止されていることを条件に含まず、上述の第 2 解除条件に加えて、S R 型フリップフロップ 5 6 4 A の出力がローレベルになっていることを含む。これにより、これまでに短絡が生じていない場合には、S R 型フリップフロップ 5 6 4 A の出力信号がローレベルであるため、A N D ゲート 5 6 3 A は、第 3 解除条件の残りの条件、つまり第 2 解除条件が満たされることに応じて S R 型フリップフロップ 5 6 1 A をリセットする。一方、短絡がいったん生じた場合には、第 1 解除条件が満たされるまでは、S R 型フリップフロップ 5 6 4 A の出力信号がハイレベルであるため、A N D ゲート 5 6 3 A は、第 3 解除条件の残りの条件、つまり第 2 解除条件が満たされるか否かに関わらず、S R 型フリップフロップ 5 6 1 A のリセットを行わない。短絡がいったん生じ、第 1 解除条件が満たされた場合には、S R 型フリップフロップ 5 6 4 A の出力信号がローレベルであるため、A N D ゲート 5 6 3 A は、第 3 解除条件の残りの条件、つまり第 2 解除条件が満たされることに応じて S R 型フリップフロップ 5 6 1 A をリセットする。

【 0 0 8 8 】

本実施形態では一例として、A N D ゲート 5 6 3 A は、O R ゲート 5 6 0 A からの出力信号の反転信号と、反転型シュミットトリガ回路 5 0 2 からの出力信号の反転信号と、遅延回路 5 6 2 からの出力信号と、S R 型フリップフロップ 5 6 4 A の出力信号の反転信号との論理積をとることで、第 3 解除条件が満たされるか否かを検知してよい。A N D ゲート 5 6 3 A は、演算結果を S R 型フリップフロップ 5 6 1 A のリセット端子に供給してよい。

【 0 0 8 9 】

S R 型フリップフロップ 5 6 1 A は、O R ゲート 5 6 0 A および A N D ゲート 5 6 2 A の出力端子に接続される。S R 型フリップフロップ 5 6 1 A は、上述の第 1 実施形態における S R 型フリップフロップ 5 6 1 と同様に、O R ゲート 5 6 0 A からの信号がハイレベルとなることに応じてセットされ、A N D ゲート 5 6 6 A からの出力信号がハイレベルとなることに応じてリセットされてよい。S R 型フリップフロップ 5 6 1 A は、セット状態でハイレベルの信号を、リセット状態でローレベルの信号を、遅延回路 5 6 2 および駆動制御部 5 0 に供給してよい。

【 0 0 9 0 】

以上のスイッチング装置 1 A によっても、上記第 1 実施形態におけるスイッチング装置 1 と同様の効果を得ることができる。

【 0 0 9 1 】

[ 3 . 第 3 実施形態 ]

図 3 は、第 3 実施形態に係るスイッチング装置 1 B を示す。スイッチング装置 1 B は、操作検出端子 1 0 8 と、制御装置 5 B とを備える。

【 0 0 9 2 】

操作検出端子 1 0 8 は、電源供給が再開される場合の基準操作の入力を検出する。基準操作は、駆動制御部 5 0 に対する電源供給の開始を指示する操作（一例として電源ボタンに対する操作）や、スイッチング装置 1 B や制御装置 5 B の起動後に実行されるべき初期化を指示する操作などであってよい。基準操作が行われた場合には、ハイレベルの信号が操作検出端子 1 0 8 から制御装置 5 B に供給されてよい。

【 0 0 9 3 】

制御装置 5 B は、S R 型フリップフロップ 5 6 4 B と、A N D ゲート 5 6 6 B とを有する。

S R 型フリップフロップ 5 6 4 B は、短絡検知部 6 4 の出力端子に接続される。S R 型フリップフロップ 5 6 4 B は、本実施形態に係る第 1 解除条件が満たされるまで、保護動作を実行すべき旨の情報を保持する。

【 0 0 9 4 】

10

20

30

40

50

ここで、本実施形態における第1解除条件は、短絡が生じた場合に、短絡が解消したこと、および、電源供給が再開される場合の基準操作が行われたことを含む。これにより、短絡が生じた場合には、電源供給が再開される場合の基準操作が行われるまで保護部58の保護動作が継続される。第1解除条件は、主スイッチング素子3をオン状態とする駆動信号Vinが供給されていないこと、および、保護動作の開始から基準時間以上が経過していることをさらに含んでよい。

#### 【0095】

S R型フリップフロップ564Bのリセット端子にはANDゲート566Bが接続されてよく、S R型フリップフロップ564Bは、ANDゲート566Bからの出力信号がハイレベルとなることに応じてリセットされてよい。S R型フリップフロップ564Bは、出力信号を遅延回路565およびORゲート569に供給してよい。10

#### 【0096】

ANDゲート566Bは、短絡検知部64、操作検出端子108、遅延回路565および反転型シュミットトリガ回路502と、S R型フリップフロップ564Bのリセット端子との間に設けられる。ANDゲート566Bは、第1解除条件が満たされたことに応じてS R型フリップフロップ564Bをリセットする。本実施形態では一例として、ANDゲート566Bは、短絡検知部64からの出力信号の反転信号と、操作検出端子108からの信号と、反転型シュミットトリガ回路502からの出力信号（本実施形態では一例として、反転した駆動信号Vin）の反転信号と、遅延回路565からの出力信号との論理積をとってよい。ANDゲート566は、演算結果をS R型フリップフロップ564Bのリセット端子に供給してよい。20

#### 【0097】

以上のスイッチング装置1Bによれば、短絡が生じた場合に、短絡が解消したこと、および、電源供給が再開される場合の基準操作が行われたことを含む第1解除条件が満たされるまで、保護動作を実行すべき旨の情報がS R型フリップフロップ564Bに保持される。従って、短絡の原因が除去されずに保護動作が解除されてしまうのを確実に防止することができる。

#### 【0098】

また、第1解除条件が満たされることに応じてS R型フリップフロップ564Bがリセットされるので、第1解除条件が満たされた場合に保護動作を解除して正常状態での運転を再開することができる。30

#### 【0099】

なお、本実施形態においてS R型フリップフロップ564Bは出力信号をORゲート569に供給することとして説明したが、第2実施形態におけるS R型フリップフロップ564Aと同様にして、出力信号をANDゲート563に供給してもよい。

#### 【0100】

##### [4. 第4実施形態]

図4は、第4実施形態に係るスイッチング装置1Cを示す。

#### 【0101】

スイッチング装置1Cにおける制御装置5Cの保護動作制御部56Cは、駆動制御部50と共に通の電源から電源供給を受ける。例えば制御装置5Cにおける各構成は、共通の電源から電圧Vccの電源供給を受けてよい。保護動作制御部56Cは、ORゲート568Cと、S R型フリップフロップ561Cと、ANDゲート563Cとを有する。40

#### 【0102】

ORゲート568Cは、短絡検知部64とANDゲート563Cとの間に設けられ、短絡検知部64により短絡が検知される場合のハイレベルの出力信号をラッチする。ORゲート568Cは、短絡検知部64の出力信号と、ORゲート568C自身の出力信号との論理和をとってよい。これにより、短絡検知部64からの出力信号が一旦ハイレベルになると、ORゲート568Cの出力信号はハイレベルに維持される。ORゲート568Cは、出力信号をANDゲート563Cに供給してよい。50

**【0103】**

S R型フリップフロップ 5 6 1 C は、 O Rゲート 5 6 0 および A N Dゲート 5 6 3 C の出力端子に接続される。 S R型フリップフロップ 5 6 1 C は、 第 3 保持部の一例であり、 保護動作制御部 5 6 C が駆動制御部 5 0 と共に電源から電源供給を受けることに応じて、 保護動作を継続させるか否かの情報を保持する。 S R型フリップフロップ 5 6 1 C は、 セット状態となることによって、 保護動作を実行すべき旨の情報の保持を行い、 リセットされることで、 当該情報をリセットしてよい。

**【0104】**

S R型フリップフロップ 5 6 1 C は、 上述の第 1 実施形態における S R型フリップフロップ 5 6 1 と同様に、 O Rゲート 5 6 0 からの信号がハイレベルとなることに応じてセットされ、 A N Dゲート 5 6 3 C からの出力信号がハイレベルとなることに応じてリセットされてよい。 S R型フリップフロップ 5 6 1 C は、 O Rゲート 5 6 9 および遅延回路 5 6 2 に出力信号を供給してよい。

10

**【0105】**

A N Dゲート 5 6 3 C は、 O Rゲート 5 6 0 、 遅延回路 5 6 2 、 反転型シュミットトリガ回路 5 0 2 および O Rゲート 5 6 8 C と、 S R型フリップフロップ 5 6 1 C のリセット端子との間に設けられる。 A N Dゲート 5 6 3 C は、 第 4 解除条件が満たされたことに応じて S R型フリップフロップ 5 6 1 C をリセットする。

**【0106】**

第 4 解除条件は、 上述の第 2 解除条件に加えて、 O Rゲート 5 6 8 C の出力がローレベルになっていることを含む。 これにより、 これまでに短絡が生じていない場合には、 O Rゲート 5 6 8 C の出力信号がローレベルであるため、 A N Dゲート 5 6 3 C は、 第 4 解除条件の残りの条件、 つまり第 2 解除条件が満たされたことに応じて S R型フリップフロップ 5 6 1 C をリセットする。 一方、 短絡がいったん生じた場合には、 O Rゲート 5 6 8 C の出力信号がハイレベルに維持されるため、 A N Dゲート 5 6 3 C は、 第 4 解除条件の残りの条件、 つまり第 2 解除条件が満たされたか否かに関わらず、 S R型フリップフロップ 5 6 1 C のリセットを行わない。 従って、 短絡がいったん生じた場合には、 S R型フリップフロップ 5 6 1 C は、 電源供給が維持される限りセット状態に維持され、 電源供給が停止されることに応じてリセットされる。

20

**【0107】**

本実施形態では一例として、 A N Dゲート 5 6 3 C は、 O Rゲート 5 6 0 からの出力信号の反転信号と、 反転型シュミットトリガ回路 5 0 2 からの出力信号の反転信号と、 遅延回路 5 6 2 からの出力信号と、 O Rゲート 5 6 8 C からの出力信号の反転信号との論理積をとることで、 第 4 解除条件が満たされたか否かを検知してよい。 A N Dゲート 5 6 3 C は、 演算結果を S R型フリップフロップ 5 6 1 C のリセット端子に供給してよい。

30

**【0108】**

以上のスイッチング装置 1 C によれば、 保護動作制御部 5 6 C が駆動制御部 5 0 と共に電源から電源供給を受けることに応じて、 保護動作を継続させるか否かの情報を S R型フリップフロップ 5 6 1 C に保持される。 従って、 駆動制御部 5 0 への電源供給が停止されるまで確実に保護部 5 8 に保護動作を継続させることができる。 また、 電源供給が停止された場合に情報をリセットされるため、 保護動作を解除し、 正常状態での運転を再開することができる。

40

**【0109】****[ 5 . 変形例 ]**

なお、 上記の実施形態においては、 制御装置 5 は駆動制御部 5 0 およびアラーム出力部 5 7 を有することとして説明したが、 これらの少なくとも 1 つを有しなくてもよい。 また、 異常検知部 6 は過熱検知部 6 1 と、 過電流検知部 6 3 と、 制御電圧低下検知部 6 5 とを有することとして説明したが、 これらの少なくとも 1 つを有しなくてもよい。

**【0110】**

また、 主スイッチング素子 3 に流れる電流に応じたパラメータとして、 主スイッチング

50

素子3のセンスエミッタ電流が抵抗620, 621に流れることに応じて検出される電圧を用いることとして説明したが、主スイッチング素子3のエミッタ電流が抵抗に流れることに応じて検出される電圧など、他のパラメータを用いてもよい。

#### 【0111】

また、保護部58は、短絡や過電流などの異常が生じた場合に主スイッチング素子3をソフトシャットダウンすることとして説明したが、主スイッチング素子3のゲート電圧を、定常オン状態でのゲート電圧よりも低い基準電圧に低下させて維持してもよい。

#### 【0112】

以上、本発明を実施の形態を用いて説明したが、本発明の技術的範囲は上記実施の形態に記載の範囲には限定されない。上記実施の形態に、多様な変更または改良を加えることが可能であることが当業者に明らかである。その様な変更または改良を加えた形態も本発明の技術的範囲に含まれ得ることが、請求の範囲の記載から明らかである。

#### 【0113】

請求の範囲、明細書、および図面中において示した装置、システム、プログラム、および方法における動作、手順、ステップ、および段階等の各処理の実行順序は、特段「より前に」、「先立って」等と明示しておらず、また、前の処理の出力を後の処理で用いるの限り、任意の順序で実現しうることに留意すべきである。請求の範囲、明細書、および図面中の動作フローに関して、便宜上「まず、」、「次に、」等を用いて説明したとしても、この順で実施することが必須であることを意味するものではない。

#### 【符号の説明】

#### 【0114】

- 1 スイッチング装置

- 2 主スイッチング素子

- 3 主スイッチング素子

- 4 制御装置

- 5 制御装置

- 6 異常検知部

- 20 サーマルダイオード

- 30 サーマルダイオード

- 50 駆動制御部

- 56 保護動作制御部

- 57 アラーム出力部

- 58 保護部

- 61 過熱検知部

- 62 測定部

- 63 過電流検知部

- 64 短絡検知部

- 65 制御電圧低下検知部

- 66 O R ゲート

- 101 正側端子

- 102 負側端子

- 103 入力端子

- 104 アラーム端子

- 105 電源出力端子

- 108 操作検出端子

- 500 電流源

- 501 ツエナーダイオード

- 502 反転型シュミットトリガ回路

- 503 NOTゲート

- 504 スイッチング素子

10

20

30

40

50

|       |               |    |

|-------|---------------|----|

| 5 0 5 | スイッチング素子      |    |

| 5 6 0 | OR ゲート        |    |

| 5 6 1 | SR型フリップフロップ   |    |

| 5 6 2 | 遅延回路          |    |

| 5 6 3 | AND ゲート       |    |

| 5 6 4 | SR型フリップフロップ   |    |

| 5 6 5 | 遅延回路          |    |

| 5 6 6 | AND ゲート       |    |

| 5 6 8 | OR ゲート        |    |

| 5 6 9 | OR ゲート        | 10 |

| 5 7 1 | 抵抗            |    |

| 5 7 2 | 電流源           |    |

| 5 7 3 | スイッチング素子      |    |

| 5 7 4 | 反転型シュミットトリガ回路 |    |

| 5 8 0 | OR ゲート        |    |

| 5 8 1 | AND ゲート       |    |

| 5 8 2 | AND ゲート       |    |

| 5 8 3 | NOT ゲート       |    |

| 5 8 4 | スイッチング素子      |    |

| 6 1 0 | 電流源           | 20 |

| 6 1 1 | コンパレータ        |    |

| 6 1 2 | ローパスフィルタ      |    |

| 6 1 3 | ヒステリシスバッファ    |    |

| 6 2 0 | 抵抗            |    |

| 6 2 1 | 抵抗            |    |

| 6 3 0 | コンパレータ        |    |

| 6 3 1 | ローパスフィルタ      |    |

| 6 4 0 | コンパレータ        |    |

| 6 4 1 | ローパスフィルタ      |    |

| 6 5 1 | コンパレータ        | 30 |

| 6 5 2 | ローパスフィルタ      |    |

| 6 5 3 | ヒステリシスバッファ    |    |

| 6 5 5 | 抵抗            |    |

【図面】

【図 1】

【図 2】

10

20

【図 3】

【図 4】

30

40

50

---

フロントページの続き

- (56)参考文献

- 特開平5 - 267580 (JP, A)

実公平5 - 34029 (JP, Y2)

特開平11 - 4150 (JP, A)

特開2014 - 103820 (JP, A)

特開2013 - 258858 (JP, A)

特開2012 - 143125 (JP, A)

特開2003 - 88093 (JP, A)

特開2020 - 150660 (JP, A)

特開2000 - 324846 (JP, A)

特開2012 - 50163 (JP, A)

特開2007 - 28733 (JP, A)

- (58)調査した分野 (Int.Cl., DB名)

- H02M 1 / 00

H02M 7 / 48