(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4206693号

(P4206693)

(45) 発行日 平成21年1月14日(2009.1.14)

(24) 登録日 平成20年10月31日(2008.10.31)

(51) Int.Cl.

F 1

**G09G 3/30 (2006.01)**

**G09G 3/20 (2006.01)**

**H01L 51/50 (2006.01)**

GO9G 3/30 J

GO9G 3/20 611H

GO9G 3/20 624B

GO9G 3/20 641A

GO9G 3/20 641D

請求項の数 12 (全 21 頁) 最終頁に続く

(21) 出願番号

特願2002-142365 (P2002-142365)

(22) 出願日

平成14年5月17日 (2002.5.17)

(65) 公開番号

特開2003-330415 (P2003-330415A)

(43) 公開日

平成15年11月19日 (2003.11.19)

審査請求日

平成17年5月6日 (2005.5.6)

(73) 特許権者 000005108

株式会社日立製作所

東京都千代田区丸の内一丁目6番6号

(74) 代理人 100100310

弁理士 井上 学

(72) 発明者 景山 寛

東京都国分寺市東恋ヶ窪一丁目280番地

株式会社日立製作所中央研究所内

(72) 発明者 秋元 肇

東京都国分寺市東恋ヶ窪一丁目280番地

株式会社日立製作所中央研究所内

審査官 濱本 祐広

最終頁に続く

(54) 【発明の名称】 画像表示装置

## (57) 【特許請求の範囲】

## 【請求項 1】

基板上に、複数の画素と、該画素に表示信号であるアナログ電圧信号を入力するための複数の信号線が形成され、前記画素のそれぞれには電流によって発光強度が変化する発光素子と、該発光素子を駆動するための画素回路が形成された画像表示装置であって、前記画素回路には、前記発光素子への電流を、供給および遮断の2状態で制御するスイッチ手段と、表示信号である前記アナログ電圧信号とは無関係に前記スイッチ手段を前記2状態のいずれかにプリセットするプリセット手段と、表示信号である前記アナログ電圧信号に従って前記スイッチ手段の状態を反転するリセット手段を具備し、前記スイッチ手段は、前記発光素子への電流を供給および遮断する少なくとも1つの薄膜トランジスタと、該薄膜トランジスタのゲート電極電圧を保持するキャパシタで構成され、前記リセット手段は、前記アナログ電圧信号を記憶する記憶手段であるキャパシタを具備し、前記リセット手段は少なくとも1つの薄膜トランジスタを具備し、前記スイッチ手段を構成する薄膜トランジスタのゲート電極に、前記リセット手段が具備する薄膜トランジスタのソース電極あるいはドレイン電極が接続し、前記信号線の他に三角波電圧信号を供給する三角波供給配線を具備し、前記信号線に供給されるアナログ電圧信号と前記三角波供給配線に供給される三角波電圧信号のいずれかを選択して前記キャパシタに供給する選択手段を具備し、前記選択手段は、前記三角波供給配線と、前記信号線にそれぞれ接続する2つの薄膜トランジスタで構成され、前記リセット手段のキャパシタの一方の電極は、前記リセット手段が具備する薄膜トランジスタのゲート電極に、もう一方の電極は、前記選択手段を構成する

10

20

2つの薄膜トランジスタに接続していることを特徴とする画像表示装置。

**【請求項 2】**

請求項 1 の画像表示装置であって、前記画素回路は薄膜トランジスタを用いて形成されていることを特徴とする画像表示装置。

**【請求項 3】**

請求項 1 の画像表示装置であって、前記画素回路は  $n$  チャネル型あるいは  $p$  チャネル型のいずれか一方の薄膜トランジスタのみを用いて形成されていることを特徴とする画像表示装置。

**【請求項 4】**

請求項 1 の画像表示装置であって、前記リセット手段は、前記リセット手段が具備する薄膜トランジスタのスレッショルド電圧をキャンセルするためのスレッショルド電圧キャンセル手段を具備し、前記スレッショルド電圧キャンセル手段は、前記リセット手段が具備する薄膜トランジスタのゲート電極 - ソース電極間あるいはゲート電極 - ドレイン電極間の短絡と開放を制御するもう一つの薄膜トランジスタで構成されていることを特徴とする画像表示装置。10

**【請求項 5】**

請求項 1 の画像表示装置であって、前記プリセット手段は、プリセット信号を伝えるプリセット信号配線と、前記スイッチ手段を構成する前記キャパシタを充電あるいは放電するための少なくとも 1 つの薄膜トランジスタで構成されることを特徴とする画像表示装置。20

**【請求項 6】**

請求項 1 の画像表示装置であって、前記画素回路には、前記発光素子に供給する電流を一定に保つための定電流回路を具備していることを特徴とする画像表示装置。

**【請求項 7】**

基板上に、複数の画素と、該画素に表示信号であるアナログ電圧信号を入力するための複数の信号線が形成され、前記画素のそれぞれには電流によって発光強度が変化する発光素子と、該発光素子を駆動するための画素回路が形成された画像表示装置であって、前記画素回路には、前記発光素子への電流を、供給および遮断の 2 状態で制御するスイッチ手段と、表示信号である前記アナログ電圧信号とは無関係に前記スイッチ手段を前記 2 状態のいずれかにプリセットするプリセット手段と、表示信号である前記アナログ電圧信号に従って前記スイッチ手段の状態を反転するリセット手段を具備し、前記スイッチ手段は、前記発光素子への電流を供給および遮断する少なくとも 1 つの薄膜トランジスタと、該薄膜トランジスタのゲート電極電圧を保持するキャパシタで構成され、前記リセット手段は、前記アナログ電圧信号を記憶する記憶手段であるキャパシタを具備し、前記リセット手段は少なくとも 1 つの薄膜トランジスタを具備し、前記スイッチ手段を構成する薄膜トランジスタのゲート電極に、前記リセット手段が具備する薄膜トランジスタのソース電極あるいはドレイン電極が接続し、前記リセット手段が具備するキャパシタの一方の電極は、前記リセット手段が具備する薄膜トランジスタのゲート電極に、もう一方の電極は、前記信号線とに接続しており、前記信号線には、前記アナログ電圧信号と三角波電圧信号が時間的に分割して供給されていることを特徴とする画像表示装置。30

**【請求項 8】**

請求項 7 の画像表示装置であって、前記画素回路は薄膜トランジスタを用いて形成されていることを特徴とする画像表示装置。

**【請求項 9】**

請求項 7 の画像表示装置であって、前記画素回路は  $n$  チャネル型あるいは  $p$  チャネル型のいずれか一方の薄膜トランジスタのみを用いて形成されていることを特徴とする画像表示装置。

**【請求項 10】**

請求項 7 画像表示装置であって、前記リセット手段は、前記リセット手段が具備する薄膜トランジスタのスレッショルド電圧をキャンセルするためのスレッショルド電圧キャン40

50

セル手段を具備し、前記スレッショルド電圧キャンセル手段は、前記リセット手段が具備する薄膜トランジスタのゲート電極 - ソース電極間あるいはゲート電極 - ドレイン電極間の短絡と開放を制御するもう一つの薄膜トランジスタで構成されていることを特徴とする画像表示装置。

**【請求項 1 1】**

請求項 7 の画像表示装置であって、前記プリセット手段は、プリセット信号を伝えるプリセット信号配線と、前記スイッチ手段を構成する前記キャパシタを充電あるいは放電するための少なくとも 1 つの薄膜トランジスタで構成されることを特徴とする画像表示装置。

**【請求項 1 2】**

10

請求項 7 の画像表示装置であって、前記画素回路には、前記発光素子に供給する電流を一定に保つための定電流回路を具備していることを特徴とする画像表示装置。

**【発明の詳細な説明】**

**【0 0 0 1】**

**【発明の属する技術分野】**

本発明は画像表示装置に関する。特に本発明は画素に発光素子がある画像表示装置に関する。

**【0 0 0 2】**

**【従来の技術】**

画素に発光素子を使用した画像表示装置として、エレクトロルミネッセンス（以下、EL と略す）素子を用いた EL ディスプレイが報告されている。さらに、アクティブマトリクス型の EL ディスプレイでは、信号や電流を伝える配線をマトリクス状に配線し、画素には EL 素子の他に、アクティブ素子である薄膜トランジスタ（以下 TFT と略す）で形成した画素回路を内蔵している。画素回路が EL 素子の発光輝度を制御する方法として、画素回路が EL 素子へ供給する時間を変調する方法があり、SID'00 DIGEST pp924-927のFig 1, Fig2, Fig6に報告されている。

20

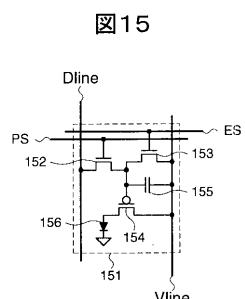

EL 素子を使った従来の画素を図 15 に示す。画素 151 は、画素回路と EL 素子 156 によって構成され、画素回路は TFT 152 ~ 154、キャパシタ 155 によって構成されている。

また、画素 151 には、表示信号であるデジタル信号を入力する信号線 D Line、EL 素子 156 に電流を供給する配線 V Line、D Line の信号をキャパシタ 155 に書き込む信号を供給する信号線 PS、キャパシタ 155 をリセットする信号を供給する信号線 ES が接続している。

30

画素 151 は次のような駆動方法によって多階調の輝度を発生することができる。たとえば 6 ビット階調 = 64 階調の輝度を発生する場合、1 枚の画像を表示する期間である 1 フレーム期間を 6 つのサブフレーム期間に分け、6 つのサブフレーム期間の各期間において、以下の動作を行う。

サブフレームの始めて、信号線 D 1 に表示信号であるデジタル電圧信号 b<sub>x</sub> を供給し、信号線 PS に H レベルのパルスを供給することで TFT 152 が ON になり、デジタル電圧信号 b<sub>x</sub> はキャパシタ 155 に記憶される。

40

サブフレーム期間中はキャパシタ 155 がデジタル電圧信号 b<sub>x</sub> を記憶しており、その電圧 b<sub>x</sub> が L レベルの場合には TFT 154 が ON であるので EL 素子 156 は点灯し、H レベルの場合には TFT 154 が OFF であるので EL 素子 156 は消灯する。

所定の点灯時間が経過した後、信号線 ES に H レベルにパルスが供給され、TFT 153 が ON になりキャパシタ 155 をリセットし、TFT 154 は OFF になる。

前記の所定の点灯時間を、各サブフレーム期間で 32 : 16 : 8 : 4 : 2 : 1 の比率になるように設定し、デジタル電圧信号 b<sub>x</sub> として表示データの各ビットに対応した電圧を MSB から順に供給することで、1 フレーム期間では画素の平均輝度は表示データに比例したものになる。なお、H レベル、L レベルはデジタル電圧信号の 2 値の電圧の意味である。

50

画素 151 を 2 次元的に配列し、各画素に順番に表示信号を書き込むことによって画像を表示することができる。

このように、EL 素子の発光時間によって平均輝度を制御する方法では、EL 素子 156 を流れる電流は表示信号に依存しないため、線形性のよい多階調表示が得やすい利点があり、EL ディスプレイは滑らかに明るさが変化する画像を表示することができる。

#### 【0003】

##### 【発明が解決しようとする課題】

図 15 のようにして、1 フレーム期間を複数のサブフレームに分けて表示信号を書き込むと、各画素に表示信号を書き込む回数が多くなる。たとえば、6 ビット（64 階調）の画像を表示する場合は 6 回、8 ビット（256 階調）の画像を表示する場合は 8 回表示信号を書き込む必要がある。それに反比例して画素に表示信号を書き込む時間は短くなる。すると、画素数が多い高解像度のディスプレイでは書き込み時間が制限されるため、1 フレームに何度も表示信号を書き込むことができなくなる。

また、1 フレーム期間に点灯する時間が複数存在すると、動画像を目で追従するときに擬似輪郭あるいは False Pixel と呼ばれるノイズが発生することが報告されている。

さらに、ビットの重みで点灯時間を分割しているので、基本的に画素の平均輝度は表示信号に比例する。そのため、補正をする場合、画像のビット数よりもさらに多くのサブフレームが必要になるため非常に困難である。

本発明では、1 フレーム期間に各画素に書き込む回数を少なくしたので高解像度化が容易である。1 フレーム期間に点灯期間は 1 度であり、擬似輪郭は発生しない。さらに、補正を容易に実現する。

#### 【0004】

##### 【課題を解決するための手段】

本発明の画像表示装置の画素回路には、発光素子への電流を、供給および遮断の 2 状態で制御するスイッチ手段と、表示信号であるアナログ電圧信号とは無関係に前記スイッチ手段を 2 状態のいずれかにプリセットするプリセット手段と、表示信号であるアナログ電圧信号に従ってスイッチ手段の状態を反転するリセット手段を具備している。

#### 【0005】

##### 【発明の実施の形態】

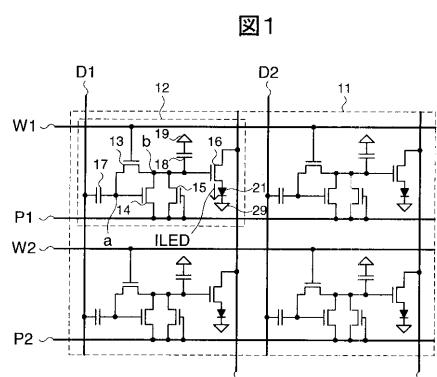

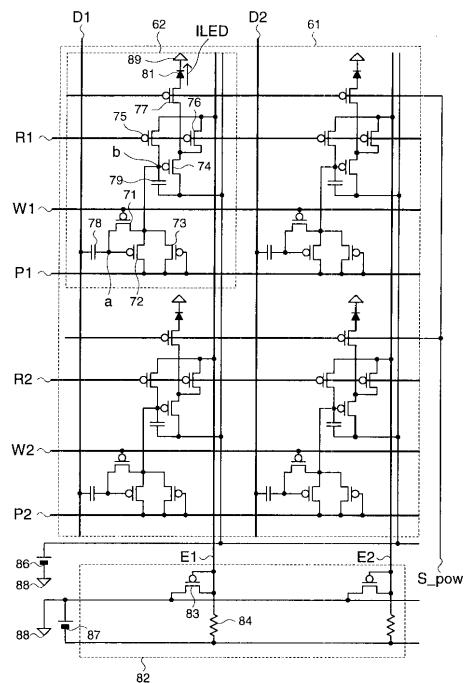

(1) 図 1 に本発明の第一の実施例の画素およびその周辺の回路図を示す。画像を表示する表示領域 11 には 2 次元的に画素 12 が複数配列されている。画素 12 は、TFT13 ~ 16、キャパシタ 17、18 で構成される画素回路と、EL 素子 21 で構成されている。EL 素子 21 の陰極は共通電極 29 に接続されている。TFT13 ~ 16 は全て n チャネル型の薄膜トランジスタである。表示領域 11 には、表示信号を含むアナログ電圧信号を伝える信号線 D1、D2、EL 素子 21 に流す電流を供給する配線 E1、E2 と、画素 12 の画素回路を制御する信号線 W1、W2、P1、P2 がマトリクス状に配線されている。キャパシタ 18 の一端は電極 19 に接続されている。電極 19 は外部で接地された配線で構成するか、共通電極 29 に接続するか、あるいは配線 E1 に接続している。

TFT16 はスイッチ手段であり、配線 E1 から EL 素子 21 への電流の供給と遮断を制御する。キャパシタ 18 はスイッチ手段である TFT16 のゲート電圧を保持することで TFT16 の ON / OFF の状態を記憶する。TFT15 はプリセット手段であり、信号線 P1 にポジティブパルスが入力された時にキャパシタ 18 に電圧をプリセットする。TFT14 はリセット手段であり、ゲート電圧がスレッショルド電圧を超えるか否かによってキャパシタ 18 の電圧のリセットを制御する。TFT13 は TFT14 のスレッショルド電圧キャンセル手段である。キャパシタ 17 は信号線 D1 の表示信号であるアナログ電圧信号と TFT14 のスレッショルド電圧の差電圧を記憶する記憶手段である。

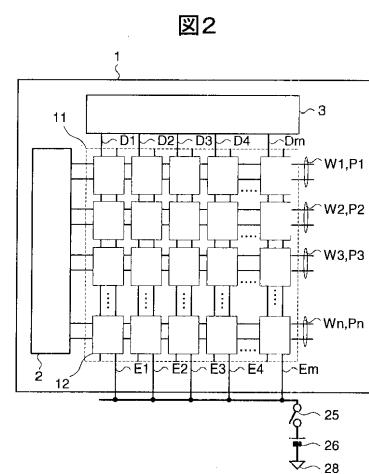

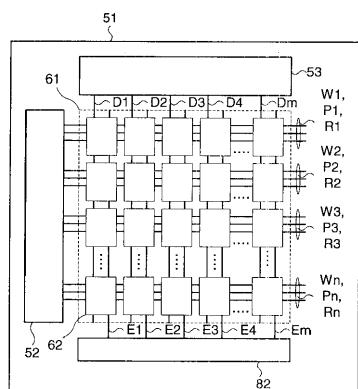

図 2 に本発明の第一および第二の実施例の構成図を示す。ガラス基板 1 の表面には、表示領域 11 があり、複数の画素 12 が形成されている。本発明の第一の実施例では、ガラス

10

20

30

40

50

基板 1 の表面には、信号線 W 1 ~ W n、P 1 ~ P n、D 1 ~ D m、配線 E 1 ~ E m と、信号線 W 1 ~ W n、P 1 ~ P n へ制御信号を発生する走査回路 2、信号線 D 1 ~ D m の信号を発生する信号回路 3 が配置されている。走査回路 2、信号回路 3 はそれぞれ TFT でガラス基板 1 上に形成するか、あるいは半導体 LSI を取り付けることによって構成される。走査回路 2 は表示領域 1 1 の両側に配置することで、信号線 W 1 ~ W n、P 1 ~ P n への信号の供給能力を上げることができる。また、信号回路 3 は表示領域に対して紙面上下方向いずれの辺に配置してもかまわない。

基板 1 の外部にある電源 2 6 は、接地電極 2 8 と配線 E 1 ~ E m の全てに接続している。配線 E 1 ~ E m は基板 1 の表面あるいは外部で互いに接続しており、基板 1 の表面で接続している場合は、配線 E 1 ~ E m 間で隣接する配線を短絡する配線を多数作成し、配線 E 1 ~ E m を 1 つの網目状の電極として形成してもよい。

10

電源 2 6 と配線 E 1 ~ E m の間にはスイッチ 2 5 があり、電源 2 6 からの電流供給を制御している。そのため、スイッチは電源 2 6 と接地電極 2 8 の間にあってもかまわない。あるいは、スイッチ 2 5 は TFT で作成して配線 E 1 ~ E m と各画素 1 2 の接続点に並列に配置してもかまわない。

図 2 には記載していないが、表示領域 1 1 を覆うように共通電極 2 9 が形成されており、全ての画素 1 2 の EL 素子 2 1 に接続している。また、共通電極 2 9 は接地電極 2 8 と電気的に接続している。画素 1 2 の EL 素子 2 1 の発光は、ガラス基板 1 からガラス基板の背面方向に透過し、図 2 の図面の背面から表示画像を見ることができる。共通電極 2 9 を透明にした場合は、図 2 の図面の正面からでも表示画像を見ることができる。EL 素子には有機 EL ダイオードを使用することができる。また、EL 素子 2 1 のそれぞれに、赤、緑、青の発光材料を用いることで、カラー表示をすることもできる。

20

ところで、図 1 では表示領域 1 1 に画素 1 2 を  $2 \times 2$  の 4 つしか記述しなかったが、実用的にはさらに多くあり、カラー VGA (640 画素 × RGB 3 色 × 480 画素) の解像度場合、紙面横方向の画素数は  $m = 1920$  になり、紙面縦方向の画素数は  $n = 480$  になる。同様に信号線 D 1 ~ D m、配線 E 1 ~ E m は 1920 本、信号線 W 1 ~ W n、P 1 ~ P n は 480 本になる。

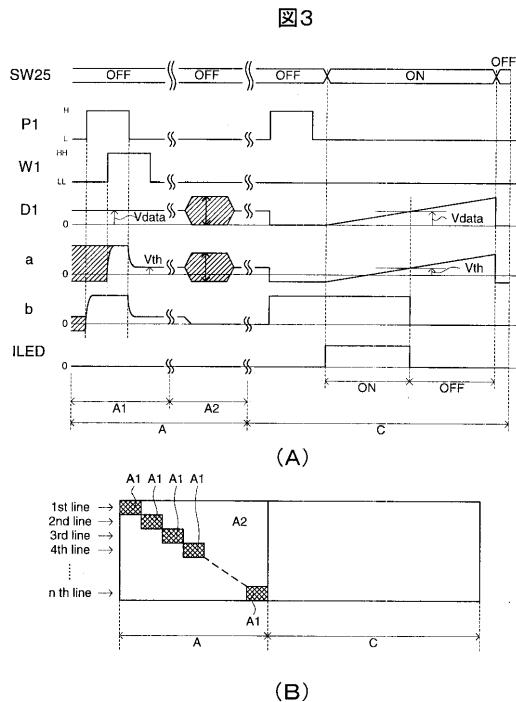

図 3 (A) に本発明の第一の実施例の駆動電圧波形、動作電圧波形、および動作電流波形を示す。また、図 3 (B) は 1 フレーム期間における図 3 (A) の波形のタイミングチャートを示す。

30

図 3 (A) の横軸は時間である。波線の部分では時間の連続性がないことを意味している。SW 2 5 はスイッチ 2 5 の ON / OFF 動作の状態を示している。W 1、P 1、D 1 は各信号線に入力する電圧を縦軸に表している。a、b は各ノードで発生する電圧を縦軸に表している。ILED は EL 素子 2 1 に流れる電流を縦軸に表している。いずれも図面上方向が + 方向である。W 1、P 1 の信号はそれぞれ 2 値のロジック電圧であり、D 1 の信号はアナログ電圧である。W 1 において HH レベルは TFT 1 3 が ON になる電圧、LL レベルは TFT 1 3 が OFF になる電圧である。P 1 において、H レベルは TFT 1 6 を ON にするのに十分な電圧、L レベルは TFT 1 6 を OFF にするのに十分な電圧を意味する。また、信号線 D 1 およびノード a、b のアナログ電圧は L レベル電圧を基準電圧 0 V として記述する。図 3 (A) の斜線部分は複数の値を取り得るか、あるいは動作に無関係であることを示している。なお、図 3 (A) の W 1、P 1、D 1 の記号の数字 "1" は、1 列目、1 行目の画素 1 2 に供給する信号を意味する数字であるので、ほかの画素の場合には対応する列と行に数字は変更になる。

40

図 3 (B) のタイミングチャートは縦軸を表示領域 1 1 のライン番号を、横軸に 1 フレーム期間内の時間を表している。ここで、ライン番号は表示領域の上側から何行目の画素 1 2 であるかを表している。

1 フレーム期間は、画素に表示信号を書き込む期間 A と、EL 素子が発光して画像を表示する期間 C に分かれている。さらに期間 A は、自分の画素に表示信号を書き込む期間 A 1 と自分以外の画素に表示信号を書き込む期間 A 2 に分かれている。期間 A において期間 A 1 が 1 番ラインから順番に 2 番ライン、3 番ラインと割り当てられ、期間 A の最後で n 番

50

ラインに割り当てられる。期間 A 1 以降の残りの時間は期間 A 2 である。

期間 A ではスイッチ 2 5 は OFF であり、TFT 1 6 の ON / OFF 状態にかかわらず EL 素子 2 1 には電流は流れず、EL 素子 2 1 は点灯していない。

期間 A 1 において、信号線 D 1 には表示信号であるアナログ電圧信号 V data を供給すると、接続するキャパシタ 1 7 の一端にも同電圧が供給される。はじめに P 1 を H レベルにすると、TFT 1 5 を通してノード b に H レベルの電圧が供給される。次に W 1 を HH レベルにすると TFT 1 3 が ON になり、ノード a は H レベルになる。その後、P 1 を L レベルにすると TFT 1 4 を通して電流が流れ、ノード a とノード b には TFT 1 4 のドレイン - ソース電極間の ON / OFF がちょうど切り替わるときのゲート電極 - ソース電極間の電圧であるスレッショルド電圧 V th が残留し、キャパシタ 1 7 のもう一端に印加される。最後に、W 1 を LL レベルにするとノード a はノード b と切り離され、キャパシタ 1 7 は表示信号であるアナログ電圧 V data と、TFT 1 4 のスレッショルド電圧である V th の差電圧 "V data - V th" を記憶する。10

期間 A 2 では、他のラインの画素に書き込みをしているので、W 1 、 P 1 は変化しない。このとき、信号線 D 1 の電圧は変化するが、TFT 1 4 が OFF であるためキャパシタ 1 7 が記憶した V data - V th の電圧は保存されている。

期間 C においては、画素 1 2 は点灯動作をする。期間 C の始めに、P 1 に H レベルのパルスを供給する。すると、TFT 1 5 を通してキャパシタ 1 8 に H レベルの電圧が印加され、TFT 1 6 は ON になる。P 1 が L レベルになった後も、キャパシタ 1 8 が H レベルの電圧を記憶しているので、TFT 1 6 は ON の状態を保持する。なお、P 1 ~ P m 全てにパルスが供給され、全ての画素が同様な動作をする（プリセット動作）。20

次に、スイッチ 2 5 を ON にして電源 2 6 から TFT 1 6 に電流を供給する。キャパシタ 1 8 には H レベルの電圧が記憶されているので、TFT 1 6 は ON であり、EL 素子 2 1 に電流が供給されて EL 素子 2 1 は発光する。一方、信号線 D 1 には、表示信号であるアナログ電圧のとり得る範囲の最低電圧から最高電圧へ一様に増加する三角波を入力する。期間 C において時間が経過すると、信号線 D 1 の電圧は三角波に従い徐々に上昇するので、画素 1 2 のノード a の電圧も上昇する。信号線 D 1 の電圧と、各画素 1 2 に期間 A 1 の時に書き込んだ電圧 V data とが等しくなったとき、ノード a の電圧がちょうど TFT 1 4 のスレッショルド電圧 V th になって、TFT 1 4 は OFF から ON に変化し、キャパシタ 1 8 の電荷が TFT 1 4 を通して放電され、ノード b の電位は L レベルになる。すると TFT 1 6 は OFF になり、TFT 1 6 を流れる電流が 0 になって EL 素子 1 2 は消灯する（リセット動作）。30

信号線 D 1 に三角波を入力するとき、信号線 P 1 は L レベルに固定にする必要がある。なぜならば、TFT 1 4 のスレッショルド電圧 V th は P 1 が TFT 1 4 のソース電極の電圧を基準としているからである。つまり、信号線 P 1 の L レベルの電圧は、三角波に対して基準電圧となっている。

最後にスイッチ 2 5 を再び OFF にすることで、期間 C は終了する。

以上のように期間 C において TFT 1 6 を ON にするプリセット動作は表示信号にかかわらず期間 C の始めに行われ、TFT 1 6 を OFF にするリセット動作のタイミングは、表示信号であるアナログ電圧 V data に依存する。したがって、アナログ電圧 V data によって EL 素子 2 1 の ON と OFF 時間の比率を、スイッチ 2 5 が ON である時間の 0 % から 100 % まで変化できる。40

EL 素子 2 1 が発光状態のときに EL 素子 2 1 の発光輝度がほぼ一定になるように、電源 2 6 から電流を供給することで、画素 1 2 の平均輝度はこの ON / OFF の時間比率、すなわち表示信号であるアナログ電圧 V data によって制御することができる。

したがって、表示信号であるアナログ電圧信号 V data によって各画素の平均輝度を多段階に制御することができるので、本発明の第一の実施例によって階調のある画像を表示することができる。

さらに、信号線 D 1 に入力する三角波の傾斜角度に変化をつけるだけで、アナログ電圧信号 V data - 平均輝度の関係に対して容易に 補正をすることもできる。なお、図示50

された三角波に代えて、階段状に電圧が増加する電圧波形のように時間経過に対して電圧が不連続に増加する波形を用いてもよい。

さらに、1フレーム内にEL素子が発光している時間は必ず連続しており、動画像を表示しても擬似輪郭は発生しない。

さらに、1フレーム期間で各画素12に表示信号を書き込む回数は1回であるので、書き込み回数が少なく、高解像度化が容易である。

したがって本発明の第一の実施例によって、補正が容易で、動画に対して擬似輪郭が発生せず、高解像度化が容易なELディスプレイを構成することができる。

本発明の第一の実施例の第一の変形例として、TFT16をpチャネル型の薄膜トランジスタで形成する構成をすることもできる。この場合、TFT16はゲート電位がHレベルのときにOFF、Lレベルの時にONになるので、期間Cにおけるプリセット動作によりOFFになり、リセット動作により反転してON状態になる。つまり、期間CにおけるEL素子の点灯、消灯期間が反転する。結果として、画素12の平均輝度はこのON/OFFの時間比率、すなわち表示信号であるアナログ電圧Vdataによって制御することができるので、本発明の第一の実施例と等価である。

本発明の第一の実施例の第二の変形例として、プリセット動作を開始するHパルスとを供給する配線と、三角波の基準となる電圧を供給する配線を分けて構成することもできる。

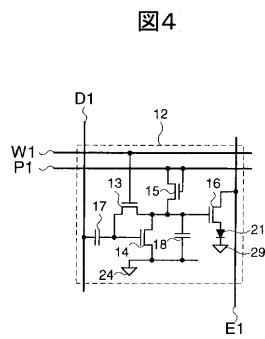

図4に本発明の第一の実施例の第二の変形例の画素の回路図を示す。画素12を構成するTFT13～16、キャパシタ17、18、EL素子21は図1と全く同じであるが、TFT14のソース電極と、キャパシタ18の一端が電極24に接続する構成になっている点が図1と異なる。電極24は複数の画素12を接続する配線で形成されており、信号線D1に供給される三角波の基準となる電圧が外部から供給されている。本発明の第一の実施例の第二の変形例でも、図3と同様の動作波形で動作することができ、第一の実施例としての効果を得ることができる。

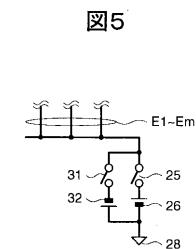

本発明の第一の実施例の第三の変形例として、図2に示した電源26とスイッチ25と並列に、図5に示すように電源26とは逆極性の電源32とスイッチ31で構成した回路を負荷することができる。スイッチ25をOFFの期間にスイッチ31をONにすることで、EL素子21に残留している電荷を取り除くことができる。

本発明の第一の実施例の第四の変形例として、EL素子の陽極と陰極の向きを逆にして電流ILEDを逆向きに流して点灯することもできる。その場合、電源26の陽極と陰極を逆向きにして接続して逆方向の電流を供給する。

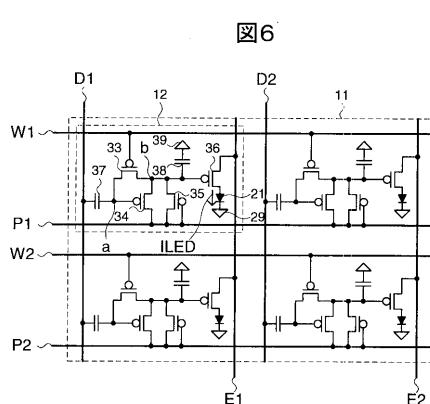

(2) 図6に本発明の第二の実施例の画素およびその周辺の回路図を示す。本発明の第一の実施例がnチャネルTFTを基本として構成されているのに対し、本発明の第二の実施例はpチャネルTFTを基本として構成されている。画像を表示する表示領域11には2次元的に画素12が複数配列されている。画素12は、TFT33～36、キャパシタ37、38で構成される画素回路と、EL素子21で構成されている。EL素子21の陰極は共通電極29に接続されている。TFT33～36は全てpチャネル型の薄膜トランジスタである。表示領域11には、表示信号を含むアナログ電圧信号を伝える信号線D1、D2、EL素子21に流す電流を供給する配線E1、E2と、画素12の画素回路を制御する信号線W1、W2、P1、P2がマトリクス状に配線されている。キャパシタ38の一端は電極39に接続されている。電極39は外部で接地された配線で構成するか、共通電極29に接続するか、あるいは配線E1に接続している。

TFT36はスイッチ手段であり、配線E1からEL素子21への電流の供給と遮断を制御する。キャパシタ38はスイッチ手段であるTFT36のゲート電圧を保持することでTFT36のON/OFFの状態を記憶する。TFT35はプリセット手段であり、信号線P1にネガティブパルスが入力された時にキャパシタ38に電圧をプリセットする。TFT34はリセット手段であり、ゲート電圧がスレッショルド電圧を超えるか否かによってキャパシタ38の電圧のリセットを制御する。TFT33はTFT34のスレッショルド電圧キャンセル手段である。キャパシタ37は信号線D1の表示信号であるアナログ電圧信号とTFT34のスレッショルド電圧の差電圧を記憶する記憶手段である。

10

20

30

40

50

図2に本発明の第一および第二の実施例の構成図を示す。本発明の第二の実施例は第一の実施例と比べて画素12内部が異なるが、画素12の外部の構成は同じであるので、図2についての説明は、本発明の第一の実施例と全く同になるのでここでは省略する。

ところで、図6では表示領域11に画素12を $2 \times 2$ の4つしか記述しなかったが、実用的にはさらに多くあり、カラーVGA(640画素×RGB3色×480画素)の解像度場合、紙面横方向の画素数はm=1920になり、紙面縦方向の画素数はn=480になる。同様に信号線D1～Dm、配線E1～Emは1920本、信号線W1～Wn、P1～Pnは480本になる。

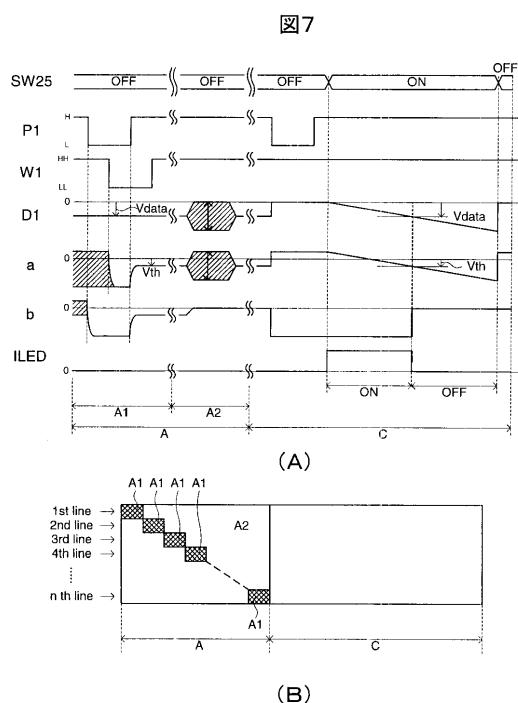

図7(A)に本発明の第一の実施例の駆動電圧波形、動作電圧波形、および動作電流波形を示す。また、図7(B)は1フレーム期間における図7(A)の波形のタイミングチャートを示す。

10

図7(A)の横軸は時間である。波線の部分では時間の連續性がないことを意味している。SW25はスイッチ25のON/OFF動作の状態を示している。W1、P1、D1は各信号線に入力する電圧を縦軸に表している。a、bは各ノードで発生する電圧を縦軸に表している。ILEDはEL素子21に流れる電流を縦軸に表している。いずれも図面上方向が+方向である。W1、P1の信号はそれぞれ2値のロジック電圧であり、D1の信号はアナログ電圧である。W1においてLLレベルはTFT33がONになる電圧、HHレベルはTFT33がOFFになる電圧である。P1において、LレベルはTFT36をONにするのに十分な電圧、HレベルはTFT36をOFFにするのに十分な電圧を意味する。また、信号線D1およびノードa、bのアナログ電圧はHレベル電圧を基準電圧0Vとして記述する。図7(A)の斜線部分は複数の値を取り得るか、あるいは動作に無関係であることを示している。なお、図7(A)のW1、P1、D1の記号の数字"1"は、1列目、1行目の画素12に供給する信号を意味する数字であるので、ほかの画素の場合には対応する列と行に数字は変更になる。

20

図7(B)のタイミングチャートは縦軸を表示領域11のライン番号を、横軸に1フレーム期間内の時間を表している。ここで、ライン番号は表示領域の上側から何行目の画素12であるかを表している。

1フレーム期間は、画素に表示信号を書き込む期間Aと、EL素子が発光して画像を表示する期間Cに分かれている。さらに期間Aは、自分の画素に表示信号を書き込む期間A1と自分以外の画素に表示信号を書き込む期間A2に分かれている。期間Aにおいて期間A1が1番ラインから順番に2番ライン、3番ラインと割り当てられ、期間Aの最後でn番ラインに割り当てられる。期間A1以降の残りの時間は期間A2である。

30

期間Aではスイッチ25はOFFであり、TFT36のON/OFF状態にかかわらずEL素子21には電流は流れず、EL素子21は点灯していない。

期間A1において、信号線D1には表示信号であるアナログ電圧信号Vdataを供給すると、接続するキャパシタ37の一端にも同電圧が供給される。はじめにP1をLレベルにすると、TFT35を通してノードbにLレベルの電圧が供給される。次にW1をLLレベルにするとTFT33がONになり、ノードaはLレベルになる。その後、P1をHレベルにするとTFT34を通して電流が流れ、ノードaとノードbにはTFT34のドレイン-ソース電極間のON/OFFがちょうど切り替わるときのゲート-ソース電極間の電圧であるスレッショルド電圧Vthが残留し、キャパシタ37のもう一端に印加される。最後に、W1をHHレベルにするとノードaはノードbと切り離され、キャパシタ37は表示信号であるアナログ電圧Vdataと、TFT34のスレッショルド電圧であるVthの差電圧"Vdata - Vth"を記憶する。

40

期間A2では、他のラインの画素に書き込みをしているので、W1、P1は変化しない。このとき、信号線D1の電圧は変化するが、TFT34がOFFであるのでキャパシタ37が記憶したVdata - Vthの電圧は保存されている。

期間Cにおいては、画素12は点灯動作をする。期間Cの始めに、P1にLレベルのパルスを供給する。すると、TFT35を通してキャパシタ39にLレベルの電圧が印加され、TFT36はONになる。P1がHレベルになった後も、キャパシタ39がLレベルの

50

電圧を記憶しているので、TFT36はONの状態を保持する。なお、P1～Pm全てにパルスが供給され、全ての画素が同様な動作をする（プリセット動作）。

次に、スイッチ25をONにして電源26からTFT36に電流を供給する。キャパシタ38にはLレベルの電圧が記憶されているので、TFT36はONであり、EL素子21に電流が供給されてEL素子21は発光する。一方、信号線D1には、表示信号であるアナログ電圧のとり得る範囲の最高電圧から最低電圧へ一様に減少する三角波を入力する。期間Cにおいて時間が経過すると、信号線D1の電圧は三角波に従い徐々に下降するので、画素12のノードaの電圧も下降する。信号線D1の電圧と、各画素12に期間A1の時に書き込んだ電圧Vdataとが等しくなったとき、ノードaの電圧が

ちょうどTFT34のスレッショルド電圧Vthになって、TFT34はOFFからONに変化し、キャパシタ38の電荷がTFT34を通して放電され、ノードbの電位はHレベルになる。するとTFT36はOFFになり、TFT36を流れる電流が0になってEL素子12は消灯する（リセット動作）。 10

信号線D1に三角波を入力するとき、信号線P1はHレベルに固定にする必要がある。なぜならば、TFT34のスレッショルド電圧VthはP1はTFT34のソース電極の電圧を基準としているからである。つまり、信号線P1のHレベルの電圧は、三角波に対して基準電圧となっている。

最後にスイッチ25を再びOFFにすることで、期間Cは終了する。

以上のように期間CにおいてTFT16をONにするプリセット動作は表示信号にかかわらず期間Cの始めに行われ、TFT16をOFFにするリセット動作のタイミングは、表示信号であるアナログ電圧Vdataに依存する。したがって、アナログ電圧VdataによってEL素子21のONとOFF時間の比率を、スイッチ25がONである時間の0%から100%まで変化できる。 20

EL素子21が発光状態のときにEL素子21の発光輝度がほぼ一定になるように、電源26から電流を供給することで、画素12の平均輝度はこのON/OFFの時間比率、すなわち表示信号であるアナログ電圧Vdataによって制御することができる。

したがって、表示信号であるアナログ電圧信号Vdataによって各画素の平均輝度を多段階に制御することができるので、本発明の第一の実施例によって階調のある画像を表示することができる。

さらに、信号線D1に入力する三角波の傾斜角度に変化をつけるだけで、アナログ電圧信号Vdata - 平均輝度の関係に対して容易に補正をすることもできる。 30

さらに、1フレーム内にEL素子が発光している時間は必ず連続しており、動画像を表示しても擬似輪郭は発生しない。

さらに、1フレーム期間で各画素12に表示信号を書き込む回数は1回であるので、書き込み回数が少なく、高解像度化が容易である。

したがって本発明の第二の実施例によって、補正が容易で、動画に対して擬似輪郭が発生せず、高解像度化が容易なELディスプレイを構成することができる。

本発明の第二の実施例の第一の変形例として、TFT36をnチャネル型の薄膜トランジスタで形成する構成をすることもできる。この場合、TFT36はゲート電位がLレベルのときにOFF、Hレベルの時にONになるので、期間Cにおけるプリセット動作によりOFFになり、リセット動作により反転してON状態になる。つまり、期間CにおけるEL素子の点灯、消灯期間が反転する。結果として、画素12の平均輝度はこのON/OFFの時間比率、すなわち表示信号であるアナログ電圧Vdataによって制御することができるので、本発明の第二の実施例と等価である。 40

また、本発明の第二の実施例は、本発明の第一の実施例の第二、第三、第四の変形例と同様な構造をとることができる。

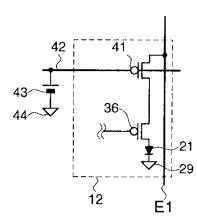

本発明の第二の実施例の第五の変形例として、図8に示すように画素12内で配線E1とスイッチ手段であるTFT36との間にpチャネル型のTFT41を挿入した構成をとることができ。TFT41のゲート電極は表示領域11の外部に配線42に接続され、基準電圧源43の片方の電極に接続している。基準電源のもう片方の電極は接地電極44に 50

接続する。接地電極 4 4 は共通電極 2 9 に接続するか、あるいは図 2 に示した電源 2 6 の陽極に接続する。基準電圧源 4 3 は TFT 4 1 が定電流を発生する飽和領域で動作するゲート電圧を発生し、配線 4 2 を通して TFT 4 1 に供給する。

これによって、TFT 3 6 が ON 状態のときに EL 素子 2 1 を流れるは、電流 EL 素子 2 1 の持つ電圧 - 電流特性の変化による影響を受けにくくなり、より安定した輝度を得ることができる。

(3) 図 9 に本発明の第三の実施例の画素およびその周辺の回路図を示す。本発明の第三の実施例では、EL 素子が点灯するときの電流を安定するために、画素内に定電流を発生する回路を構成している。表示領域 6 1 には 2 次元的に画素 6 2 が複数配列され、画素 6 2 は、TFT 7 1 ~ 7 7 、キャパシタ 7 8 、7 9 で構成される画素回路と、EL 素子 8 1 で構成されている。また、EL 素子 8 1 の陰極は共通電極 8 9 に接続されている。TFT 7 1 ~ 7 7 は全て p チャネル型の薄膜トランジスタである。表示領域 6 1 には、表示信号を含むアナログ電圧信号を伝える信号線 D 1 、D 2 、基準電流を供給する配線 E 1 、E 2 と、画素 6 2 の画素回路を制御する信号線 W 1 、W 2 、P 1 、P 2 、R 1 、R 2 とがマトリクス状に配線されている。また、EL 素子 8 1 に電流を供給する電源 8 6 と、EL 素子 2 1 への電流供給を制御する信号線 S\_pow とが全ての画素 6 2 に接続している。

10

TFT 7 4 はスイッチ手段であり、配線 E 1 から EL 素子 8 1 への電流の供給と遮断を制御する。キャパシタ 7 9 はスイッチ手段である TFT 7 4 のゲート電圧を保持することで TFT 7 4 の ON / OFF の状態を記憶する。TFT 7 5 はプリセット手段であり、信号線 R 1 にネガティブパルスが入力された時にキャパシタ 7 9 に電圧をプリセットする。

20

TFT 7 2 はリセット手段であり、ゲート電圧がスレッショルド電圧を超えるか否かによってキャパシタ 7 9 の電圧のリセットを制御する。TFT 7 1 は TFT 7 2 のスレッショルド電圧キャンセル手段である。キャパシタ 7 8 は信号線 D 1 の表示信号であるアナログ電圧信号と TFT 7 2 のスレッショルド電圧の差電圧を記憶する記憶手段である。また、TFT 7 4 ~ 7 7 とキャパシタ 7 9 は定電流回路を構成しており、キャパシタ 7 9 は TFT 7 4 が ON 状態のときに TFT 7 4 が定電流を発生するのに必要なゲート電圧を記憶する働きもする。

表示領域の外部には基準電流源 8 2 があり、基準電流源 8 2 は定電流を発生するための抵抗器 8 4 と、配線 E 1 、E 2 に高電圧が発生するのを防止するための保護ダイオードである TFT 8 3 が紙面横方向に複数配列して構成され、基準電流を発生するための電源 8 7 と、定電流を供給する配線 E 1 、E 2 に接続している。また、電源 8 7 の陽極は接地電極 8 8 に接続し、接地電極 8 8 と共に電極 8 9 は電気的に接続している。

30

なお、電源 8 7 が発生する高い負電圧が E 1 、E 2 に発生するのを防止するため、保護ダイオード回路として TFT 8 3 を設けている。

図 10 に本発明の第三実施例の構成図を示す。ガラス基板 5 1 の表面には、表示領域 6 1 があり、複数の画素 6 2 が形成されている。また、ガラス基板 5 1 の表面には、信号線 W 1 ~ W n 、P 1 ~ P n 、R 1 ~ R n 、信号線 D 1 ~ D m 、配線 E 1 、E 2 と、信号線 W 1 ~ W n 、P 1 ~ P n 、R 1 ~ R n の制御信号を発生する走査回路 5 2 、信号線 D 1 ~ D m の信号を発生する信号回路 5 3 、配線 E 1 ~ E m に基準電流を発生する基準電流源 8 2 が配置されている。走査回路 5 2 、信号回路 5 3 、基準電流源 8 2 はそれぞれ TFT でガラス基板 5 1 上に形成するか、あるいは半導体 LSI を取り付けることによって構成される。走査回路 5 2 は表示領域 6 1 の両側に配置することで、信号線 P 1 ~ P n 、W 1 ~ W n 、R 1 ~ R n への信号の供給能力を上げることができる。また、信号回路 5 3 と基準電流源 8 2 は表示領域 6 1 に対して紙面上下方向いずれの辺に配置してもかまわない。図 10 には記載していないが、表示領域 6 1 を覆うように共通電極 8 9 が形成されており、画素 6 2 の EL 素子 8 1 の陰極に接続している。画素 6 2 の EL 素子 8 1 の発光は、ガラス基板 5 1 からガラス基板の背面方向に透過し、図 10 の図面の背面から表示画像を見ることができる。共通電極 8 9 を透明にした場合は、図 10 の図面の正面からでも表示画像を見る能够である。EL 素子には有機 EL ダイオードを使用することができる。また、EL 素子 8 1 のそれぞれに、赤、緑、青の発光材料を用いることで、カラー表示をすることも

40

できる。

ところで、図9では表示領域61に画素62を $2 \times 2$ の4つしか記述していないが、実用的にはさらに多くあり、カラーVGA(640画素×RGB3色×480画素)の解像度場合、紙面横方向の画素数はm=1920になり、紙面縦方向の画素数はn=480になる。同様に信号線D1～Dm、配線E1～Emは1920本、信号線P1～Pn、W1～Wn、R1～Rnは480本になる。

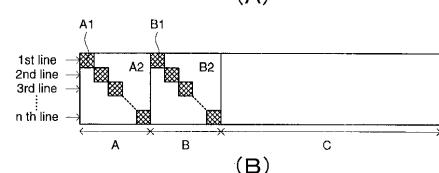

図11(A)に本発明の第三の実施例の駆動電圧波形、動作電圧波形、および動作電流波形を示す。また、図11(B)は1フレーム期間における図11(A)の波形のタイミングチャートを示す。

図11(A)の横軸は時間である。波線の部分では時間の連續性がないことを意味している。S\_pow、R1、P1、W1、D1は各信号線に入力する電圧を縦軸に表している。a、bは各ノードで発生する電圧を縦軸に表している。ILEDはEL素子81に流れる電流を縦軸に表している。いずれも図面上方向が+方向である。S\_pow、R1、P1、W1の信号は2値のロジック電圧であり、D1の信号はアナログ電圧である。S\_pow、R1、W1においてLLレベルはTFT71、TFT75～77をONにする電圧よりも低い電圧であり、HHレベルはOFFにする電圧よりも高い電圧である。P1においてHレベルはTFT74をOFFにするのに十分低い電圧、LレベルはHレベルに対して高い電圧であることを意味する。また、信号線D1およびノードa、bのアナログ電圧はHレベルの電圧を基準電圧0Vとして記述する。図11(A)の斜線部分は複数の値を取り得るか、あるいは動作に無関係であることを示している。なお、図11(A)のR1、P1、W1、D1の記号の数字"1"は、1列目、1行目の画素62に供給する信号を意味する数字であるので、ほかの画素の場合には対応する列と行に数字は変更になる。

図11(B)のタイミングチャートは縦軸を表示領域61のライン番号を、横軸に1フレーム期間内の時間を表している。ここで、ライン番号は表示領域の上側から何行目の画素62であるかを表している。

1フレーム期間は、画素に表示信号を書き込む期間A、画素に基準電流を書き込む期間B、EL素子が発光して画像を表示する期間Cに分かれている。さらに期間Aは、自分の画素に表示信号を書き込む期間A1と自分以外の画素に表示信号を書き込む期間A2に分かれ、期間Bは、自分の画素に基準信号を書き込む期間B1と自分以外の画素に電基準電流を書き込む期間B2に分かれている。期間Aにおいて期間A1が1番ラインから順番に2番ライン、3番ラインと割り当てられ、期間Aの最後でn番ラインに割り当てられる。期間A1以降の残りの時間は期間A2である。同じく、期間Bにおいて期間B1が1番ラインから順番に2番ライン、3番ラインと割り当てられ、期間Bの最後でn番ラインに割り当てられる。期間B1以降の残りの時間は期間B2である。

期間A1では、画素回路のTFT71～73とキャパシタ78が動作する。信号線D1には表示信号であるアナログ電圧信号Vdataを供給すると、接続するキャパシタ78の一端にも同電圧Vdataが供給される。はじめにP1をLレベルにすると、TFT73を通してノードbに電圧が供給される。次にW1をLLレベルにするとTFT71がONになり、ノードaもLレベルになる。その後、P1をHレベルにするとTFT72を通して電流が流れ、ノードaとノードbにはTFT72のドレイン-ソース電極間のON/OFFがちょうど切り替わるときのゲート-ソース電極間の電圧であるスレッショルド電圧Vthが残留し、キャパシタ78のもう一端に印加される。最後に、W1をHHレベルにするとノードaはノードbと切り離され、キャパシタ78はVdata-Vthの電圧を記憶する。

期間A2では、他のラインの画素に表示信号を書き込んでいるので、R1、P1、W1は変化しない。このとき、信号線D1の電圧は変化するが、TFT71がOFFであるのでキャパシタ78が記憶したVdata-Vthの電圧は保存されている。

期間Bにおいて、基準電流源82は、配線E1から基準電流源82へ向かって流れる電流irefが発生している。電流irefは、電源87の電圧を十分高くすることで、iref = Vx/Rx (Vx:電源87の電圧、Rx:抵抗器84の抵抗値) の定電流を得る

10

20

30

40

50

ことができる。抵抗器 84 は薄膜トランジスタのソース電極やドレイン電極に使われるポリシリコン膜や、ゲート電極に使われる金属配線を細長く加工することで形成することができる。

期間 B1 では、画素回路の TFT74 ~ 76 とキャパシタ 79 が動作する。期間 B1 では R1 を LL レベルにして、TFT75、76 を ON にする。すると、電源 86 - TFT76 - TFT74 - 配線 E1 - 基準電流源 82 の経路で定電流  $i_{ref}$  が流れる。このとき TFT74 は飽和領域で動作し、TFT74 のゲート - ソース電極間に TFT74 がドレイン - ソース電極間に電流  $i_{ref}$  を流すのに必要な電圧  $V_{ref}$  が発生し、キャパシタ 79 に印加される。その後、R1 が HH レベルになり、TFT75、76 が OFF になると TFT74 を流れる電流は 0 になるが、キャパシタ 79 は、電圧  $V_{ref}$  を記憶している。

10

期間 B2 では、他のラインの画素に電流  $i_{ref}$  を書き込んでいるが、制御信号 R1 が HH レベルであるので、TFT75、76 が OFF 状態を保ち、キャパシタ 79 の電圧は保存されている。

以上のように期間 Bにおいて、全ての画素のキャパシタ 79 に電圧  $V_{th}$  がプリセットされる（プリセット動作）。

期間 C では、S\_pow を LL レベルにするので TFT77 が ON になり、電源 86 - TFT74 - TFT77 - EL 素子 81 - 共通電極 89 の経路で電流が流れ、EL 素子 81 は発光する。このとき、全ての画素回路において、TFT74 はキャパシタ 79 が記憶した電圧  $V_{ref}$  によって定電流  $i_{ref}$  を発生し、EL 素子 81 に定電流  $i_{ref}$  が流れ、EL 素子 21 は均一な強度で発光する。一方、信号線 D1 には、表示信号であるアナログ電圧のとり得る範囲の最高電圧から最低電圧へ変化する三角波を入力する。期間 Cにおいて時間が経過すると、信号線 D1 の電圧は三角波に従い徐々に下降するので、画素 62 のノード a の電圧も下降する。信号線 D1 の電圧と、各画素 62 に期間 A1 の時に書き込んだ電圧  $V_{data}$  とが等しくなったとき、ノード a の電圧が TFT72 のスレッショルド電圧  $V_{th}$  になって、TFT72 は OFF から ON に変化し、キャパシタ 79 に電荷が TFT72 を通して充電され、ノード b の電位は H レベルになる。すると  $i_{ref}$  を流していた TFT74 は OFF になり、TFT74 を流れる電流が 0 になって EL 素子 81 は消灯する（リセット動作）。

20

信号線 D1 に三角波を入力するとき、信号線 P1 は H レベルに固定にする必要がある。なぜならば、TFT72 のスレッショルド電圧  $V_{th}$  は P1 は TFT72 のソース電極の電圧を基準としているからである。つまり、信号線 P1 の H レベルの電圧は、三角波に対して基準電圧となっている。

30

最後にスイッチ S\_pow を再び HH レベルにすることで、TFT77 は OFF になり、期間 C は終了する。

以上のようにプリセット動作は表示信号にかかわらず期間 B の間に完了し、TFT74 を OFF にするリセット動作のタイミングは、表示信号であるアナログ電圧  $V_{data}$  に依存する。したがって、アナログ電圧  $V_{data}$  によって EL 素子 81 の ON と OFF 時間の比率を、S\_pow が LL レベルである時間の 0 % から 100 % まで変化できる。

EL 素子 81 が発光状態のとき、発光輝度は電流  $i_{ref}$  によって一定に保たれているので、画素 62 の平均輝度はこの ON / OFF の時間比率に比例する。すなわち、画素 62 の平均輝度は表示信号であるアナログ電圧  $V_{data}$  によって制御することができる。

40

したがって、表示信号であるアナログ電圧信号  $V_{data}$  によって各画素の平均輝度を多段階に制御することができるので、本発明の第三の実施例によって階調のある画像を表示することができる。

さらに、信号線 D1 に入力する三角波の傾斜角度に変化をつけるだけで、アナログ電圧信号  $V_{data}$  - 平均輝度の関係に対して容易に 補正をすることもできる。なお、図示された三角波に代えて、階段状に電圧が増加する電圧波形のように時間経過に対して電圧が不連続に増加する波形を用いてもよい。

さらに、1 フレーム内に EL 素子が発光している時間は必ず連続しており、動画像を表示

50

しても擬似輪郭は発生しない。

さらに、1フレーム期間で各画素112に表示信号と基準電流を書き込む回数が合計2回であるので、書き込み回数が少なく、高解像度化が容易である。

したがって本発明の第一の実施例によって、補正が容易で、動画に対して擬似輪郭が発生せず、高解像度化が容易なELディスプレイを構成することができる。

また、本発明の第三の実施例を構成する薄膜トランジスタはpチャネル型であったが、本発明の第一の実施例と第二の実施例の関係と同様にして、本発明の第三の実施例と同様な実施例をnチャネル型の薄膜トランジスタで構成することができるのは明らかである。

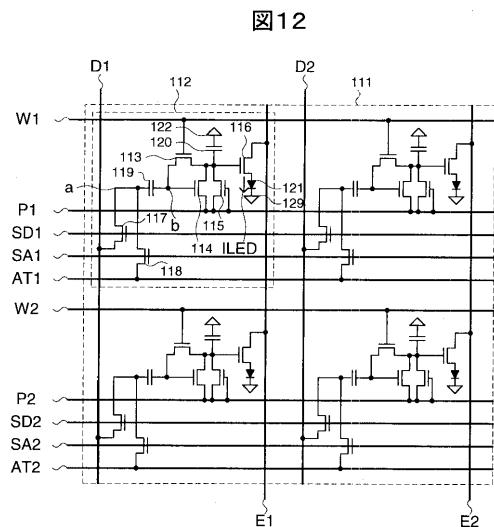

(4) 図12に本発明の第四の実施例の画素およびその周辺の回路図を示す。本発明の第四の実施例では、画素に表示信号を書き込む時間をより長くすることができる構造になっている。画像を表示する表示領域111には2次元的に画素112が複数配列されている。

10

#### 【0006】

画素112は、TFT113～118、キャパシタ119、120で構成される画素回路と、EL素子121で構成されている。EL素子121の陰極は共通電極129に接続されている。TFT113～118は全てnチャネル型の薄膜トランジスタである。表示領域111には、表示信号を含むアナログ電圧信号を伝える信号線D1、D2、EL素子121に流す電流を供給する配線E1、E2と、画素12の画素回路を制御する信号線W1、W2、P1、P2、SD1、SD2、SA1、SA2、三角波電圧信号を供給する信号線AT1、AT2がマトリクス状に配線されている。キャパシタ120の一端は電極122に接続されている。電極122は外部で接地された配線で構成するか、共通電極129に接続するか、あるいは配線E1に接続している。

20

TFT116はスイッチ手段であり、配線E1からEL素子121に電流の供給と遮断を制御する。キャパシタ120はスイッチ手段であるTFT116のゲート電圧を保持することでTFT116のON/OFFの状態を記憶する。TFT115はプリセット手段であり、信号線P1にポジティブパルスが入力された時にキャパシタ120に電圧をプリセットする。TFT114はリセット手段であり、ゲート電圧がスレッショルド電圧を超えるか否かによってキャパシタ120の電圧のリセットを制御する。TFT113はTFT114のスレッショルド電圧キャンセル手段である。キャパシタ119は信号線D1の表示信号であるアナログ電圧信号とTFT114のスレッショルド電圧の差電圧を記憶する記憶手段である。TFT117は信号線D1の表示信号であるアナログ電圧信号を選択してキャパシタ119に供給する選択スイッチである。TFT118は信号線AT1の三角波電圧を選択してキャパシタ119に供給する選択スイッチである。

30

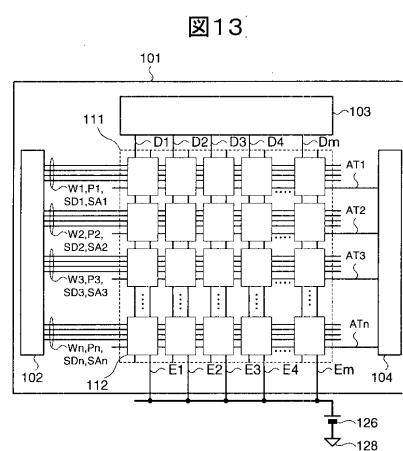

図13に本発明の第四の実施例の構成図を示す。ガラス基板101の表面には、表示領域111があり、複数の画素112が形成されている。また、ガラス基板101の表面には、信号線W1～Wn、P1～Pn、SD1～SDn、SA1～SAN、AT1～ATn、D1～Dm、配線E1～Emと、信号線W1～Wn、P1～Pn、SD1～SDn、SA1～SANへ制御信号を発生する走査回路102、信号線D1～Dmの信号を発生する信号回路103、信号線AT1～ATnに三角波電圧を発生する三角波発生回路104が配置されている。走査回路102、信号回路103、三角波発生回路104はそれぞれTFTでガラス基板101上に形成するか、あるいは半導体LSIを取り付けることによって構成される。走査回路102および三角波発生回路104は表示領域111の両側に配置することで、信号線W1～Wn、P1～Pn、SD1～SDn、SA1～SAN、AT1～ATnへの信号の供給能力を上げることができる。また、信号回路103は表示領域に対して紙面上下方向いずれの辺に配置してもかまわない。

40

基板101の外部にある電源126は、接地電極128と配線E1～Emの全てに接続している。配線E1～Emは基板1の表面あるいは外部で互いに接続しており、基板101の表面で接続している場合は、配線E1～Em間で隣接する配線を短絡する配線を多数作成し、配線E1～Emを1つの網目状の電極として形成してもよい。

図13には記載していないが、表示領域111を覆うように共通電極129が形成されて

50

おり、全ての画素 112 の E L 素子 121 に接続している。また、共通電極 129 は接地電極 128 と電気的に接続している。画素 112 の E L 素子 121 の発光は、ガラス基板 101 からガラス基板の背面方向に透過し、図 13 の図面の背面から表示画像を見ることができる。共通電極 129 を透明にした場合は、図 13 の図面の正面からでも表示画像を見ることができる。E L 素子には有機 E L ダイオードを使用することができる。また、E L 素子 121 のそれぞれに、赤、緑、青の発光材料を用いることで、カラー表示をすることもできる。

ところで、図 12 では表示領域 111 に画素 112 を  $2 \times 2$  の 4 つしか記述しなかったが、実用的にはさらに多くあり、カラー V G A (640 画素 × R G B 3 色 × 480 画素) の解像度場合、紙面横方向の画素数は  $m = 1920$  になり、紙面縦方向の画素数は  $n = 480$  になる。同様に信号線 D1 ~ Dm、配線 E1 ~ Em は 1920 本、信号線 W1 ~ Wn、P1 ~ Pn、SD1 ~ SDn、SA1 ~ SAN、AT1 ~ ATn は 480 本になる。

10

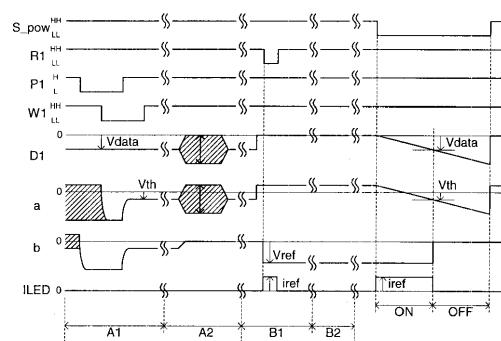

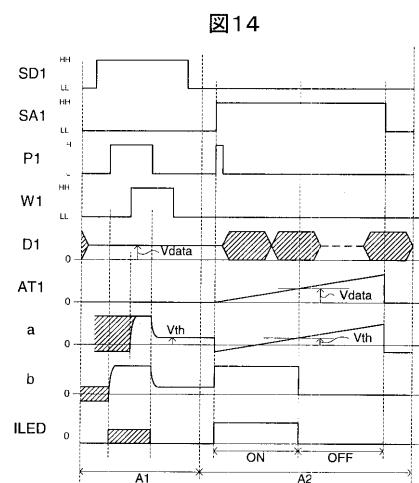

図 14 (A) に本発明の第四の実施例の駆動電圧波形、動作電圧波形、および動作電流波形を示す。また、図 14 (B) は 1 フレーム期間における図 14 (A) の波形のタイミングチャートを示す。

図 14 (A) の横軸は時間である。SD1、SA1、P1、W1、D1、AT1 は各信号線に入力する電圧を縦軸に表している。a、b は各ノードで発生する電圧を縦軸に表している。ILED は E L 素子 121 に流れる電流を縦軸に表している。いずれも図面上方向が + 方向である。SD1、SA1、P1、W1 の信号はそれぞれ 2 値のロジック電圧であり、AT1、D1 の信号はアナログ電圧である。SD1、SA1、W1 のにおいて、HH レベルはそれぞれ TFT117、TFT118、TFT113 が ON になる電圧、LL レベルは OFF になる電圧である。P1 のにおいて、H レベルは TFT116 を ON にするのに十分な電圧、L レベルは TFT116 を OFF にするのに十分な電圧を意味する。また、信号線 D1、AT1 およびノード a、b のアナログ電圧は L レベル電圧を基準電圧 0V として記述する。図 14 (A) の斜線部分は複数の値を取り得るか、あるいは動作に無関係であることを示している。なお、図 14 (A) の W1、P1、SD1、SA1、AT1、D1 の記号の数字 "1" は、1 列目、1 行目の画素 112 に供給する信号を意味する数字であるので、ほかの画素の場合には対応する列と行に数字は変更になる。

20

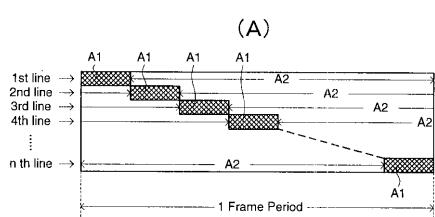

図 14 (B) のタイミングチャートは縦軸を表示領域 111 のライン番号を、横軸に 1 フレーム期間内の時間を表している。ここで、ライン番号は表示領域の上側から何行目の画素 12 であるかを表している。

30

1 フレーム期間は、自分の画素に表示信号を書き込む期間 A1 と、E L 素子を発光する期間 A2 に分かれている。1 フレーム期間内において、期間 A1 が 1 番ラインから順番に 2 番ライン、3 番ラインと割り当てられ、期間 A の最後で n 番ラインに割り当てられる。期間 A2 は現在の 1 フレーム期間内の期間 A1 が終了してから次の 1 フレーム期間の期間 A1 が開始されるまでの時間である。要するに、各ラインのタイミングがそれぞれ期間 A1 だけシフトしている訳である。

期間 A1 のにおいて、信号線 SD1 を HH レベルにし、信号線 D1 に表示信号であるアナログ電圧信号 Vdata を供給すると、TFT117 を通してキャパシタ 119 の一端にも電圧 Vdata が供給される。続いて P1 を H レベルにすると、TFT115 を通してノード b に H レベルの電圧が供給される。次に W1 を HH レベルにすると TFT113 が ON になり、ノード a は H レベルになる。その後、P1 を L レベルにすると TFT114 を通して電流が流れ、ノード a とノード b には TFT114 のドレイン - ソース電極間の ON / OFF がちょうど切り替わるときのゲート - ソース電極間の電圧であるスレッショルド電圧 Vth が残留し、キャパシタ 119 のもう一端に印加される。その後に、W1 を L レベルにするとノード a はノード b と切り離され、キャパシタ 119 は表示信号であるアナログ電圧 Vdata と、TFT114 のスレッショルド電圧 Vth の差電圧 "Vdata - Vth" を記憶する。最後に SD1 を LL レベルにして TFT117 を OFF にする。

40

なお、P1 が H レベルである時間、E L 素子 121 に電流が流れて点灯するが、P1 が H

50

レベルである時間は、1フレーム期間よりはるかに短く、これによる発光は無視できる。期間A2では、他のラインの画素に書き込みをしているので、W1、P1、SD1は変化しない。このとき、信号線D1の電圧は変化するが、TFT113およびTFT117がOFFであるのでキャパシタ17が記憶したVdata-Vthの電圧は保存されている。また、期間A2では、画素112は点灯動作をする。期間A2の始めに、P1にHレベルのパルスを供給する。すると、TFT15を通してキャパシタ120にHレベルの電圧が印加され、TFT116はONになる。P1がLレベルになった後も、キャパシタ18がHレベルの電圧を記憶しているので、TFT116はONの状態を保持し、EL素子121に配線E1から電流が流れて発光する(プリセット動作)。

また、P1にHレベルのパルスを供給するのと同時にSA1をHレベルにすると、TFT118がONになり、キャパシタ119には信号線AT1の電圧が供給される。そして、信号線AT1には、表示信号であるアナログ電圧のとり得る範囲の最低電圧から最高電圧へ一様に増加する三角波を入力する。期間A2において時間が経過すると、信号線AT1の電圧は三角波に従い徐々に上昇するので、画素112のノードaの電圧も上昇する。信号線AT1の電圧と、画素112に期間A1の時に書き込んだ電圧Vdataとが等しくなったとき、ノードaの電圧がちょうどTFT114のスレッショルド電圧Vthになつて、TFT114はOFFからONに変化し、キャパシタ120の電荷がTFT114を通して放電され、ノードbの電位はLレベルになる。するとTFT116はOFFになり、TFT116を流れる電流が0になってEL素子112は消灯する(リセット動作)。信号線AT1に三角波を入力するとき、信号線P1はLレベルに固定にする必要がある。なぜならば、TFT114のスレッショルド電圧VthはP1はTFT114のソース電極の電圧を基準としているからである。つまり、信号線P1のLレベルの電圧は、三角波に対して基準電圧となっている。

最後にSA1を再びLLレベルにすることで、期間A2は終了する。

以上のように期間A2においてプリセット動作は表示信号にかかるらず期間A2の始めに行われ、リセット動作のタイミングは、表示信号であるアナログ電圧Vdataに依存する。したがって、EL素子121の点灯と消灯時間の比率は、表示信号であるアナログ電圧Vdataによって0%から100%まで変化できる。

EL素子121が発光状態のときにEL素子121の発光輝度がほぼ一定になるよう、電源126から電流を供給することで、画素112の平均輝度はこのON/OFFの時間比率、すなわち表示信号であるアナログ電圧Vdataによって制御することができる。

したがって、表示信号であるアナログ電圧信号Vdataによって各画素の平均輝度を多段階に制御することができるので、本発明の第四の実施例によって階調のある画像を表示することができる。

さらに、信号線AT1～ATmに入力する三角波の傾斜角度に変化をつけるだけで、アナログ電圧信号Vdata-平均輝度の関係に対して容易に補正をすることもできる。なお、図示された三角波に代えて、階段状に電圧が増加する電圧波形のように時間経過に対して電圧が不連続に増加する波形を用いてもよい。さらに、1フレーム内にEL素子が発光している時間は必ず連続しており、動画像を表示しても擬似輪郭は発生しない。

さらに、1フレーム期間で各画素112に表示信号を書き込む回数は1回であるので、書き込み回数が少なくでき、かつ、各画素112に表示信号を書き込む時間を1フレーム全てに割り振る使うことができるので、書き込み時間を長くできるので、高解像度化が容易である。

したがって本発明の第四の実施例によって、補正が容易で、動画に対して擬似輪郭が発生せず、高解像度化が容易なELディスプレイを構成することができる。

本発明の第四の実施例の第一の変形例として、TFT116をpチャネル型の薄膜トランジスタで形成する構成をすることもできる。この場合、TFT116はゲート電位がHレベルのときにOFF、Lレベルの時にONになるので、プリセット動作によりOFFになり、リセット動作により反転してOFF状態になる。つまり、期間A2におけるEL素子

10

20

30

40

50

の点灯、消灯時間が反転する。結果として、画素 112 の平均輝度はこの ON / OFF の時間比率、すなわち表示信号であるアナログ電圧  $V_{data}$  によって制御することができる、本発明の第四の実施例と等価である。

また、本発明の第四の実施例は、本発明の第一の実施例の第二、第四の変形例と同様な構造をとることができる。

本発明の各実施例の画像表示装置は、n チャネル型、あるいは p チャネル型の薄膜トランジスタのみで画素回路を構成することができるので、両方のチャネル型が必要な画像表示装置に比べて製造コストを低減する効果がある。

本発明の各実施例の画像表示装置は、携帯電話、TV、PDA、ノートPC、モニタに適用することで、携帯電話、TV、PDA、ノートPC、モニタの擬似輪郭を防止し、特性を容易にし、高解像度化を容易にすることができます。

10

#### 【0007】

#### 【発明の効果】

本発明では、1 フレーム期間に各画素に書き込む回数を 1 回ないしは 2 回と少なくしたので高解像度化が容易である。

さらに、信号線に入力する三角波の傾斜角度に変化をつけるだけで、アナログ電圧信号  $V_{data}$  - 平均輝度の関係に対して容易に補正をすることもできる。さらに、1 フレーム内に EL 素子が発光している時間は必ず連続しており、動画像を表示しても擬似輪郭は発生しない。

#### 【図面の簡単な説明】

【図 1】本発明の第一の実施例の画素およびその周辺の回路を表した図である。

20

【図 2】本発明の第一および第二の実施例の構成を表した図である。

【図 3】本発明の第一の実施例の駆動電圧波形、動作電圧波形、動作電流波形、および、タイミングチャートを表した図である。

【図 4】本発明の第一の実施例の第二の変形例の画素の回路を表した図である。

【図 5】本発明の第一の実施例の第三の変形例の特徴を表した図である。

【図 6】本発明の第二の実施例の画素およびその周辺の回路を表した図である。

【図 7】本発明の第二の実施例の駆動電圧波形、動作電圧波形、動作電流波形、および、タイミングチャートを表した図である。

【図 8】本発明の第一の実施例の第五の変形例の特徴を表した図である。

30

【図 9】本発明の第三の実施例の画素およびその周辺の回路を表した図である。

【図 10】本発明の第三の実施例の構成を表した図である。

【図 11】本発明の第三の実施例の駆動電圧波形、動作電圧波形、動作電流波形、および、タイミングチャートを表した図である。

【図 12】本発明の第四の実施例の画素およびその周辺の回路を表した図である。

【図 13】本発明の第四の実施例の構成を表した図である。

【図 14】本発明の第四の実施例の駆動電圧波形、動作電圧波形、動作電流波形、および、タイミングチャートを表した図である。

【図 15】EL 素子を使った従来の画素の構成を表した図である。

#### 【符号の説明】

1 ... ガラス基板、2 ... 走査回路、3 ... 信号回路、11 ... 表示領域、12 ... 画素、13 ~ 16 ... TFT、17 ~ 18 ... キャパシタ、19 ... 電極、21 ... EL 素子、24 ... 電極、25 ... スイッチ、26 ... 電源、28 ... 接地電極、31 ... スイッチ、32 ... 電源、33 ~ 36 ... TFT、37 ~ 38 ... キャパシタ、39 ... 電極、41 ... TFT、42 ... 配線、43 ... 基準電圧源、44 ... 接地電極、51 ... ガラス基板、52 ... 走査回路、53 ... 信号回路、61 ... 表示領域、62 ... 画素、71 ~ 77 ... TFT、78 ~ 79 ... キャパシタ、81 ... EL 素子、82 ... 基準電流源、83 ... TFT (保護ダイオード回路)、84 ... 抵抗器、86 ~ 87 ... 電源、88 ... 接地電極、89 ... 共通電極、101 ... ガラス基板、102 ... 走査回路、103 ... 信号回路、104 ... 三角波発生回路、111 ... 表示領域、112 ... 画素、113 ~ 118 ... TFT、119 ~ 120 ... キャパシタ、121 ... EL 素子、122 ... 電極、12

40

10

20

30

40

50

9 ... 共通電極、 151 ... 画素、 152 ~ 154 ... TFT、 155 ... キャパシタ、 156 ... EL 素子。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【 四 9 】

☒ 9

8

JLED

【図10】

10

【 四 1 1 】

図11

【図12】

【図13】

【図14】

【図15】

**(B)**

---

フロントページの続き

(51)Int.Cl.

F I

G 09 G 3/20 6 4 1 R

H 05 B 33/14 A

(56)参考文献 国際公開第02/027700(WO,A1)

特表2004-510208(JP,A)

特表平05-503175(JP,A)

特開2002-082651(JP,A)

特開2003-043999(JP,A)

特開2003-288055(JP,A)

特開2003-241711(JP,A)

特許第3854161(JP,B2)

特許第3892732(JP,B2)

特許第3899886(JP,B2)

(58)調査した分野(Int.Cl., DB名)

G09G 3/00-3/38