(12) INTERNATIONAL APPLICATION PUBLISHED UNDER THE PATENT COOPERATION TREATY (PCT)

(19) World Intellectual Property Organization

(10) International Publication Number WO 2012/162316 A1

(51) International Patent Classification: **G11C 16/34** (2006.01) G11C 16/10 (2006.01)

(21) International Application Number:

(22) International Filing Date:

22 May 2012 (22.05.2012)

(25) Filing Language:

English

(26) Publication Language:

English

(30) Priority Data:

13/113,786

23 May 2011 (23.05.2011)

US

- (71) Applicant (for all designated States except SANDISK TECHNOLOGIES, INC. [US/US]; Two Legacy Town Center, 6900 North Dallas Parkway, Plano, TX 75024 (US).

- (72) Inventors; and

- (75) Inventors/Applicants (for US only): HEMINK, Gerrit, Jan [NL/JP]; 601 Mccarthy Boulevard, Milpitas, CA 95035 (US). LEE, Shin-chung [JP/JP]; 601 Mccarthy Boulevard, Milpitas, CA 95035 (US). KHANDELWAL, Anubhav [US/US]; 601 Mccarthy Boulevard, Milpitas, CA 95035 (US). CHIN, Henry [US/US]; 601 Mccarthy Boulevard, Milpitas, CA 95035 (US). LIANG, Guirong [CN/US]; 601 Mccarthy Boulevard, Milpitas, CA 95035 (US). LEE, Dana [US/US]; 601 Mccarthy Boulevard, Milpitas, CA 95035 (US).

- Agent: MAGEN, Burt; Vierra Magen Marcus & DeNiro, LLP, 575 Market Street, Suite 2500, San Francisco, CA 94105 (US).

- PCT/US2012/038992 (81) Designated States (unless otherwise indicated, for every kind of national protection available): AE, AG, AL, AM, AO, AT, AU, AZ, BA, BB, BG, BH, BR, BW, BY, BZ, CA, CH, CL, CN, CO, CR, CU, CZ, DE, DK, DM, DO, DZ, EC, EE, EG, ES, FI, GB, GD, GE, GH, GM, GT, HN, HR, HU, ID, IL, IN, IS, JP, KE, KG, KM, KN, KP, KR, KZ, LA, LC, LK, LR, LS, LT, LU, LY, MA, MD, ME, MG, MK, MN, MW, MX, MY, MZ, NA, NG, NI, NO, NZ, OM, PE, PG, PH, PL, PT, QA, RO, RS, RU, RW, SC, SD, SE, SG, SK, SL, SM, ST, SV, SY, TH, TJ, TM, TN, TR, TT, TZ, UA, UG, US, UZ, VC, VN, ZA, ZM, ZW.

- (84) Designated States (unless otherwise indicated, for every kind of regional protection available): ARIPO (BW, GH, GM, KE, LR, LS, MW, MZ, NA, RW, SD, SL, SZ, TZ, UG, ZM, ZW), Eurasian (AM, AZ, BY, KG, KZ, RU, TJ, TM), European (AL, AT, BE, BG, CH, CY, CZ, DE, DK, EE, ES, FI, FR, GB, GR, HR, HU, IE, IS, IT, LT, LU, LV, MC, MK, MT, NL, NO, PL, PT, RO, RS, SE, SI, SK, SM, TR), OAPI (BF, BJ, CF, CG, CI, CM, GA, GN, GQ, GW, ML, MR, NE, SN, TD, TG).

## Published:

- with international search report (Art. 21(3))

- with amended claims (Art. 19(1))

(54) Title: RAMPING PASS VOLTAGE TO ENHANCE CHANNEL BOOST IN MEMORY DEVICE, WITH TEMPERATURE COMPENSATION

(57) Abstract: In a non-volatile storage system, one or more substrate channel regions for an unselected NAND string are boosted during programming to inhibit program disturb. A voltage applied to one or more unselected word lines associated with at least a first channel region is increased during a program pulse time period in which a program pulse is applied to a selected word line. The increase can be gradual, in the form of a ramp, or step-wise. The boosting level of the first channel region can be maintained. The increase in the voltage applied to the one or more unselected word lines can vary with temperature as well. Before the program pulse time period, the voltage applied to the one or more unselected word lines can be ramped up at a faster rate for a second, adjacent channel region than for the first channel region, to help isolate the channel regions.

-1-

RAMPING PASS VOLTAGE TO ENHANCE CHANNEL BOOST IN MEMORY DEVICE, WITH TEMPERATURE COMPENSATION

## **BACKGROUND**

[0001] The present technology relates to non-volatile memory.

**[0002]** Semiconductor memory has become increasingly popular for use in various electronic devices. For example, non-volatile semiconductor memory is used in cellular telephones, digital cameras, personal digital assistants, mobile computing devices, non-mobile computing devices and other devices. Electrically Erasable Programmable Read Only Memory (EEPROM) and flash memory are among the most popular non-volatile semiconductor memories. With flash memory, also a type of EEPROM, the contents of the whole memory array, or of a portion of the memory, can be erased in one step, in contrast to the traditional, full-featured EEPROM.

[0003] Both the traditional EEPROM and the flash memory utilize a floating gate that is positioned above and insulated from a channel region in a semiconductor substrate. The floating gate is positioned between the source and drain regions. A control gate is provided over and insulated from the floating gate. The threshold voltage (Vth) of the transistor thus formed is controlled by the amount of charge that is retained on the floating gate. That is, the minimum amount of voltage that must be applied to the control gate before the transistor is turned on to permit conduction between its source and drain is controlled by the level of charge on the floating gate.

[0004] Some EEPROM and flash memory devices have a storage element or cell with a floating gate that is used to store two ranges of charges and, therefore, the storage element can be programmed/erased between two states, e.g., an erased state and a programmed state. Such a flash memory device is

-2-

sometimes referred to as a binary flash memory device because each storage element can store one bit of data.

**[0005]** A multi-state (also called multi-level) flash memory device is implemented by identifying multiple distinct allowed/valid programmed threshold voltage ranges. Each distinct threshold voltage range corresponds to a predetermined value for the set of data bits encoded in the memory device. For example, each storage element can store two bits of data when the storage element can be placed in one of four discrete charge bands corresponding to four distinct threshold voltage ranges.

[0006]Typically, a program voltage Vpgm applied to the control gate during a program operation is applied as a series of pulses that increase in magnitude over time. The program voltage can be applied to a selected word line. In one possible approach, the magnitude of the pulses is increased with each successive pulse by a predetermined step size or increment, e.g., 0.2-0.4 V. Vpgm can be applied to the control gates of flash memory elements. In the periods between the program pulses, verify operations are carried out. That is, the programming level of each element of a group of storage elements being programmed in parallel is read between successive program pulses to determine whether it is equal to or greater than a verify level to which the element is being programmed. For arrays of multi-state flash memory elements, a verification step may be performed for each state of an element to determine whether the element has reached its data-associated verify level. For example, a multi-state memory element capable of storing data in four states may need to perform verify operations for three compare points.

[0007] Moreover, when programming an EEPROM or flash memory device, such as a NAND flash memory device in a NAND string, typically Vpgm is applied to the control gate and the bit line of a NAND string which is selected for programming is grounded, causing electrons from the channel of a storage element to be injected into the floating gate. When electrons accumulate in the floating gate, the floating gate becomes negatively charged and the threshold

voltage of the storage element is raised so that it is considered to be in a programmed state.

[0008] However, for a NAND string which is not selected for programming, the associated storage elements are subject to program disturb when Vpgm is applied.

## BRIEF DESCRIPTION OF THE DRAWINGS

[0001] In the drawings, like-numbered elements correspond to one another.

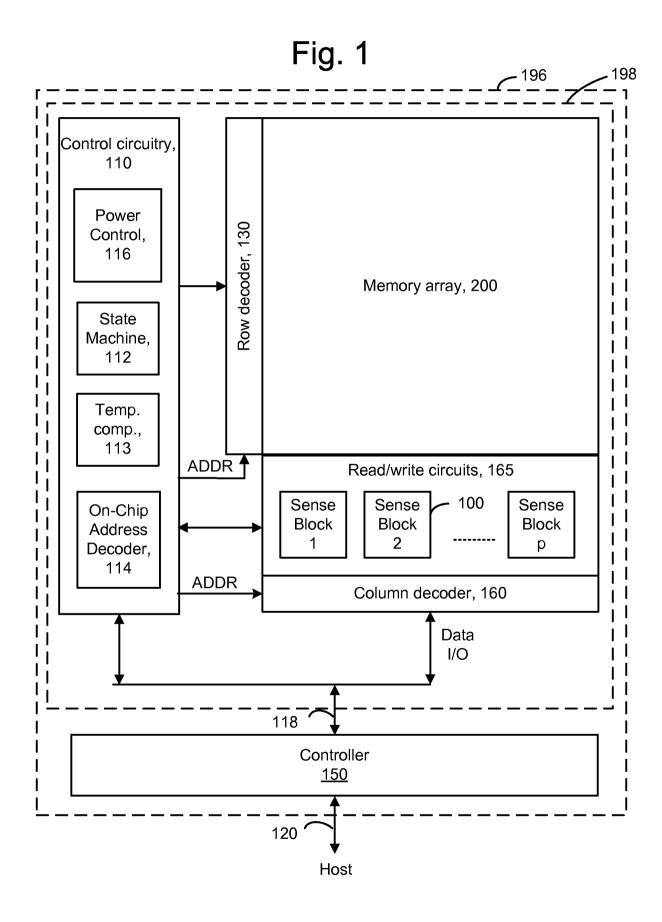

[0002] FIG. 1 is a block diagram of a non-volatile memory system using single row/column decoders and read/write circuits.

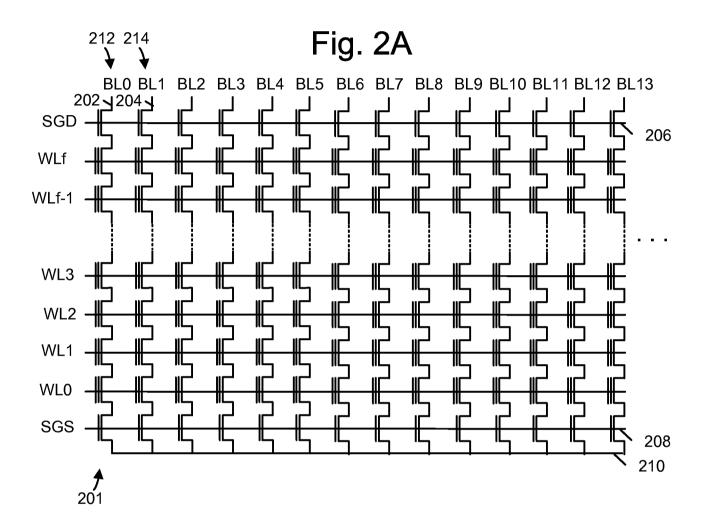

[0003] FIG. 2A depicts an example block in a memory array, such as the memory array 200 of FIG. 1.

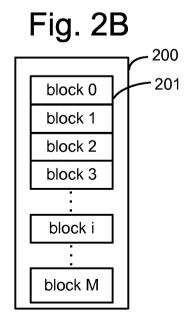

[0004] FIG. 2B depicts a memory array 200 comprising multiple blocks, such as the block 201 of FIG. 2A.

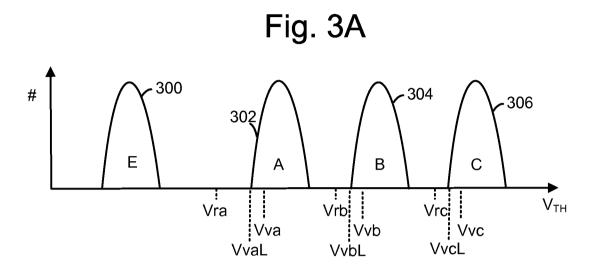

[0005] FIG. 3A depicts an example set of threshold voltage distributions.

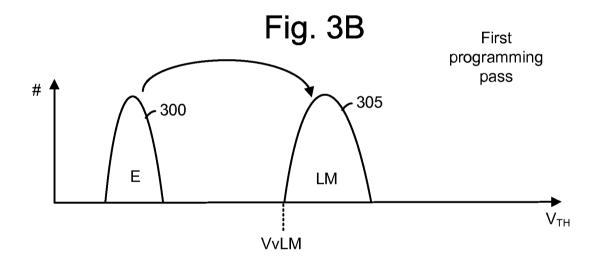

[0006] FIG. 3B illustrates a first pass of a two-pass programming technique.

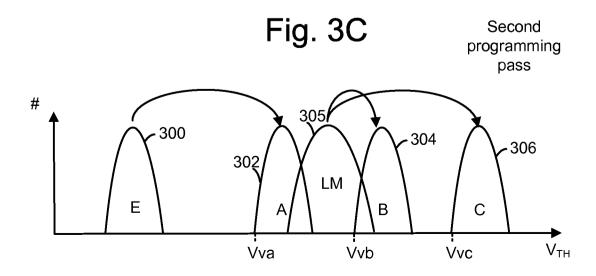

[0007] FIG. 3C illustrates a second pass of the two-pass programming technique of FIG. 3B.

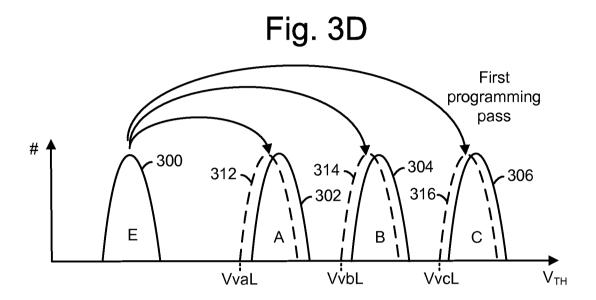

[0008] FIG. 3D illustrates a first pass of another two-pass programming technique.

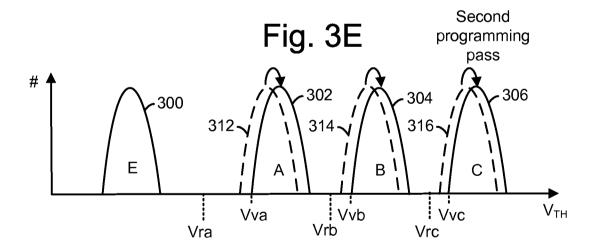

[0009] FIG. 3E illustrates a second pass of the two-pass programming technique of FIG. 3D.

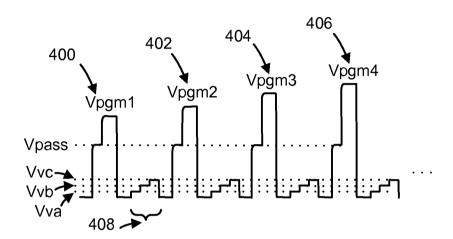

[0010] FIG. 4A depicts a series of program and verify pulses which are applied to a selected word line during a programming operation.

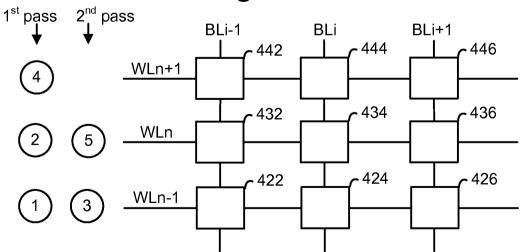

[0011] FIG. 4B depicts a multi-pass program operation for a set of storage elements.

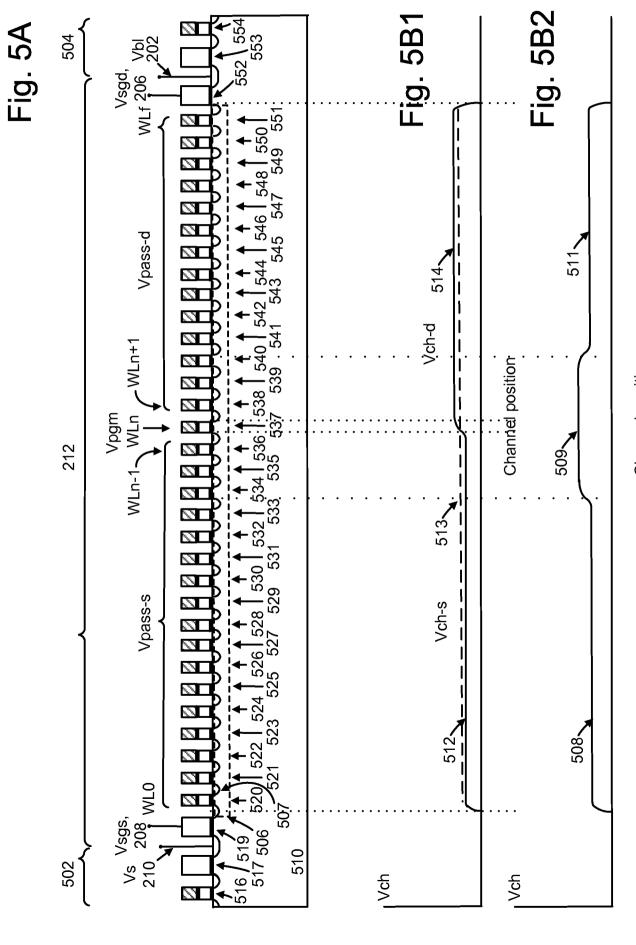

[0012] FIG. 5A depicts a cross-sectional view of the unselected NAND string 212 of FIG. 2A showing a first channel boosting technique.

[0013] FIG. 5B1 is a graph showing channel boosting levels in the substrate of the unselected NAND string of FIG. 5A.

[0014] FIG. 5B2 is a graph showing channel boosting levels in the substrate of the unselected NAND string of FIG. 5A, in another embodiment.

[0015] FIG. 5C depicts a voltage applied to a selected word line during a program portion of a program-verify iteration.

[0016] FIG. 5D depicts a fixed voltage applied to unselected word lines during a program portion of a program-verify iteration, consistent with the channel boosting technique of FIG. 5A.

[0017] FIG. 5E depicts a channel boosting level in the substrate of the NAND string for the channel boosting technique of FIG. 5A, when the unselected word line voltage of FIG. 5D is used.

[0018] FIG. 5F depicts a voltage applied to a bit line 202 of the unselected NAND string of FIG. 5A during a program portion of a program-verify iteration.

**[0019]** FIG. 5G depicts a voltage applied to a line 206 in communication with a drain-side select gate of the unselected NAND string of FIG. 5A during a program portion of a program-verify iteration.

[0020] FIG. 5H depicts a voltage applied to a source line 210 of the unselected NAND string of FIG. 5A during a program portion of a program-verify iteration.

[0021] FIG. 5I depicts a voltage applied to a line 208 in communication with a source-side select gate of the unselected NAND string of FIG. 5A during a program portion of a program-verify iteration.

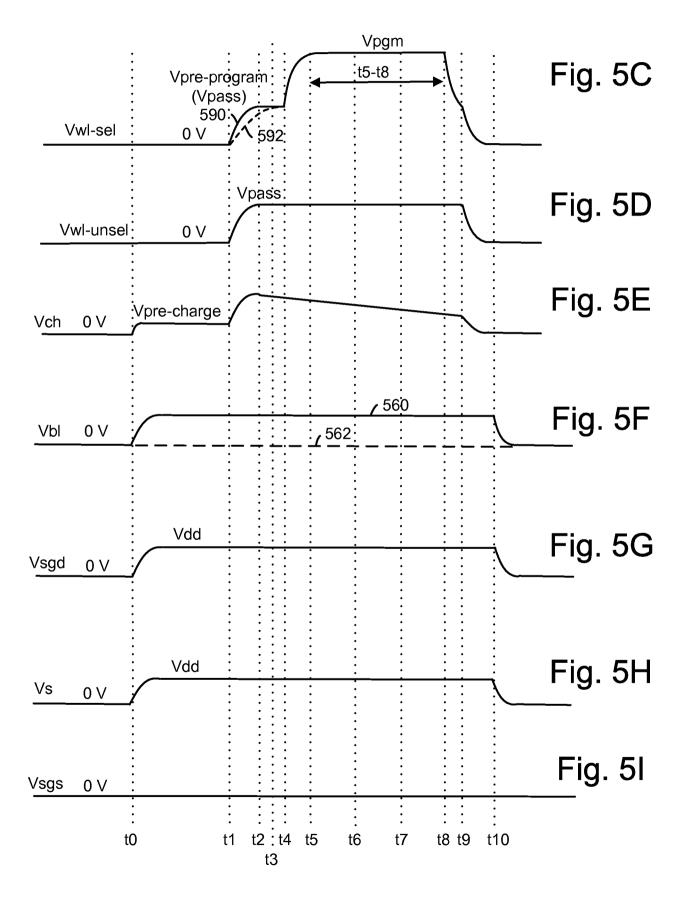

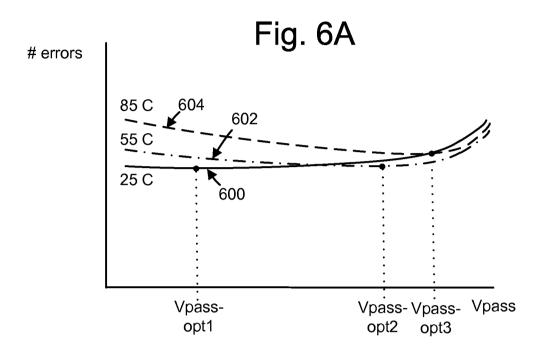

**[0022]** FIG. 5J depicts a voltage applied to an unselected word line during a program portion of a program-verify iteration, where the voltage is increased in a linear or non-linear ramp, such as for the first channel boosting technique of FIG. 5A.

[0023] FIG. 5K depicts a channel boosting level in the substrate of the NAND string of FIG. 5A, e.g., based on the unselected word line voltages of FIG. 5J.

[0024] FIG. 5L depicts a step-wise increasing voltage applied to an unselected word line during a program portion of a program-verify iteration, as

an alternative to the ramped voltage of FIG. 5J.

[0025] FIG. 5M depicts a channel boosting level in the substrate of the NAND string of FIG. 5A, e.g., based on the unselected word line voltage of FIG. 5L.

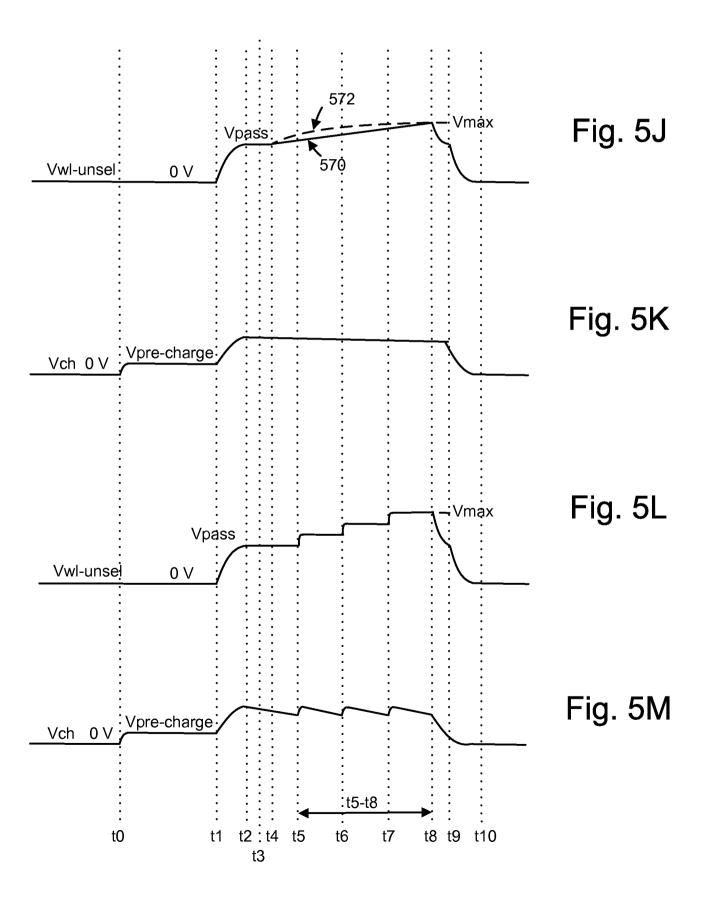

**[0026]** FIG. 6A depicts a graph showing bit errors as a function of pass voltage for unselected word lines for a typical boosting technique, for different temperatures.

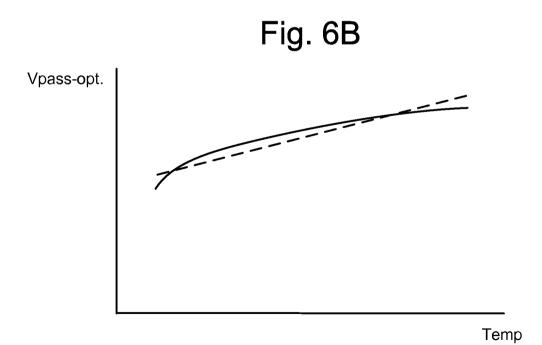

[0027] FIG. 6B depicts an optimum pass voltage for unselected word lines for a typical channel boosting technique, as a function of temperature, consistent with FIG. 6A.

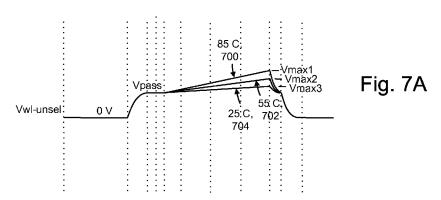

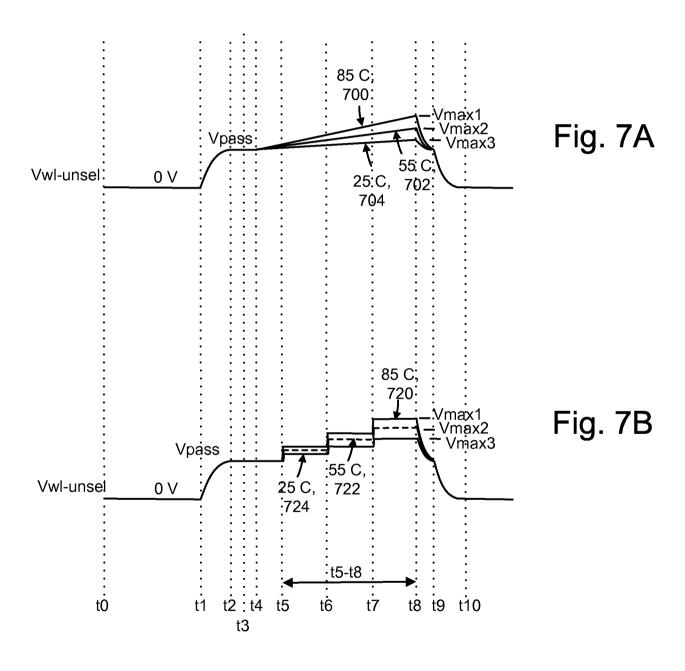

**[0028]** FIG. 7A depicts a voltage applied to an unselected word line during a program portion of a program-verify iteration, where the voltage is increased like a ramp, as a function of temperature, such as for the first channel boosting technique of FIG. 5A.

**[0029]** FIG. 7B depicts a step-wise increasing voltage applied to an unselected word line during a program portion of a program-verify iteration, as a function of temperature, as an alternative to the ramped voltage of FIG. 7A.

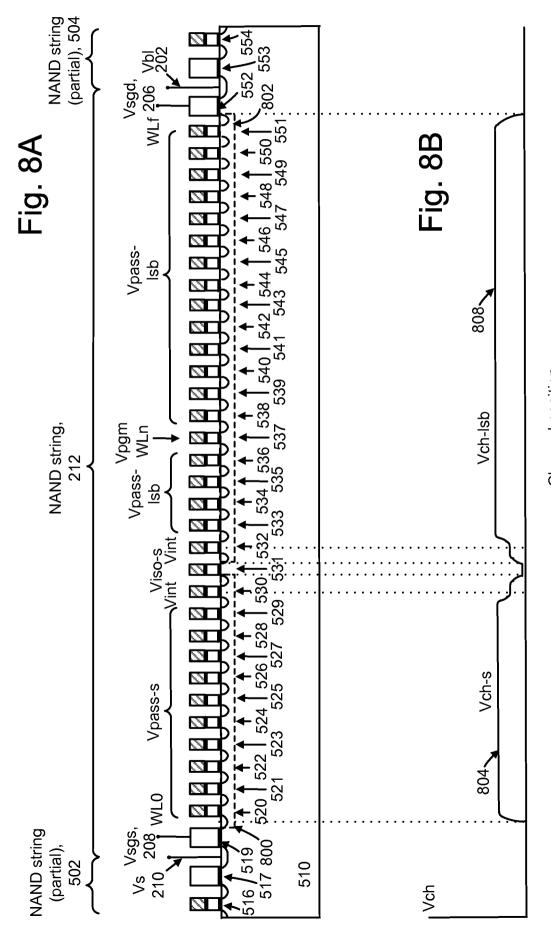

[0030] FIG. 8A depicts a cross-sectional view of the unselected NAND string 212 of FIG. 2A showing a second channel boosting technique.

[0031] FIG. 8B is a graph showing channel boosting levels in the substrate of the unselected NAND string of FIG. 8A.

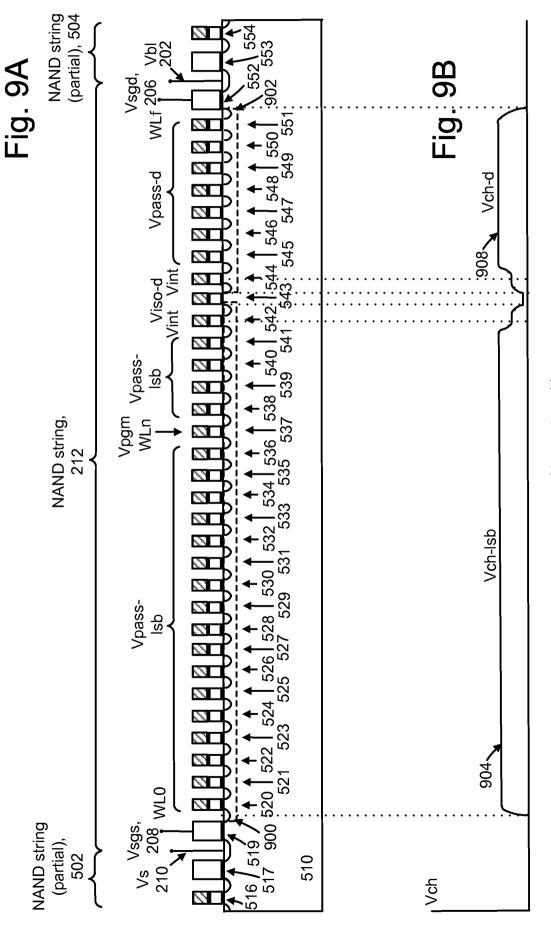

[0032] FIG. 9A depicts a cross-sectional view of the unselected NAND string 212 of FIG. 2A showing a third channel boosting technique.

[0033] FIG. 9B is a graph showing channel boosting levels in the substrate of the unselected NAND string of FIG. 9A.

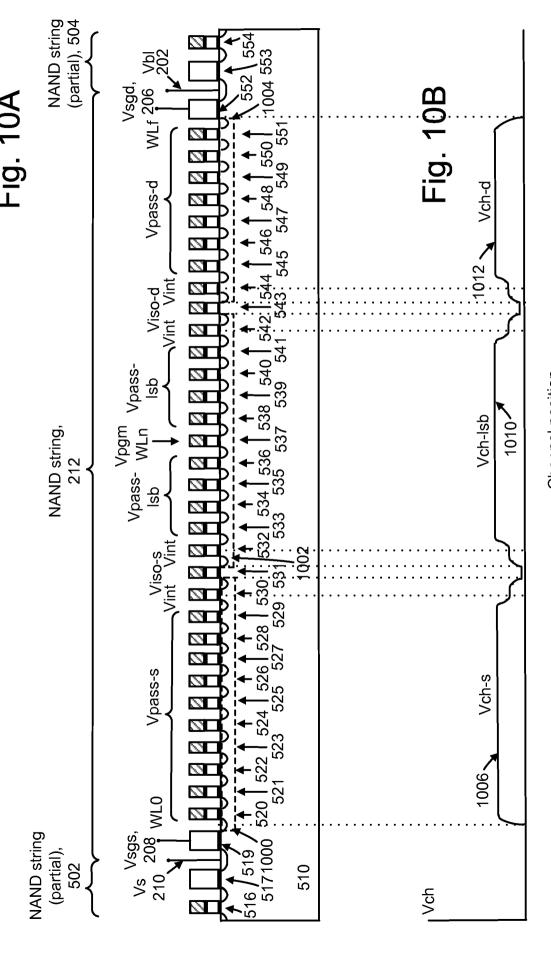

[0034] FIG. 10A depicts a cross-sectional view of the unselected NAND string 212 of FIG. 2A showing a fourth channel boosting technique.

[0035] FIG. 10B is a graph showing channel boosting levels in the substrate of the unselected NAND string of FIG. 10A.

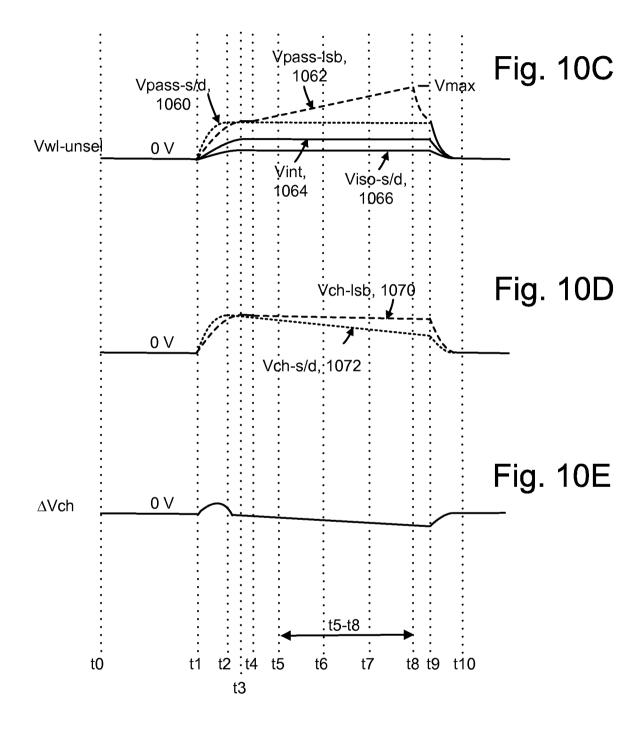

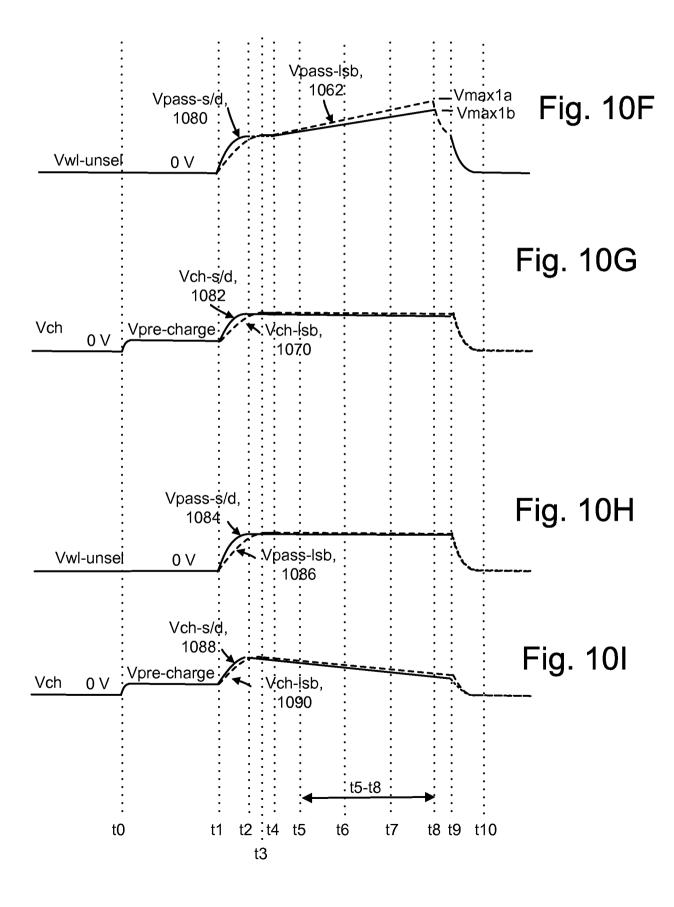

[0036] FIG. 10C depicts voltages applied to unselected word lines during a

program portion of a program-verify iteration, for the channel boosting techniques of FIGs. 8A, 9A or 10A.

[0037] FIG. 10D depicts channel boosting levels in the substrate of the NAND string of FIGs. 8A, 9A or 10A e.g., based on the unselected word line voltages of FIG. 10C.

[0038] FIG. 10E depicts a difference in the channel boosting levels of FIG. 10D.

**[0039]** FIG. 10F depicts alternative voltages applied to unselected word lines during a program portion of a program-verify iteration, for the channel boosting techniques of FIGs. 8A, 9A or 10A.

[0040] FIG. 10G depicts channel boosting levels in the substrate of the NAND string of FIGs. 8A, 9A or 10A e.g., based on the unselected word line voltages of FIG. 10F.

[0041] FIG. 10H depicts alternative voltages applied to unselected word lines during a program portion of a program-verify iteration, for the channel boosting techniques of FIGs. 8A, 9A or 10A.

[0042] FIG. 10I depicts channel boosting levels in the substrate of the NAND string of FIGs. 8A, 9A or 10A e.g., based on the unselected word line voltages of FIG. 10H.

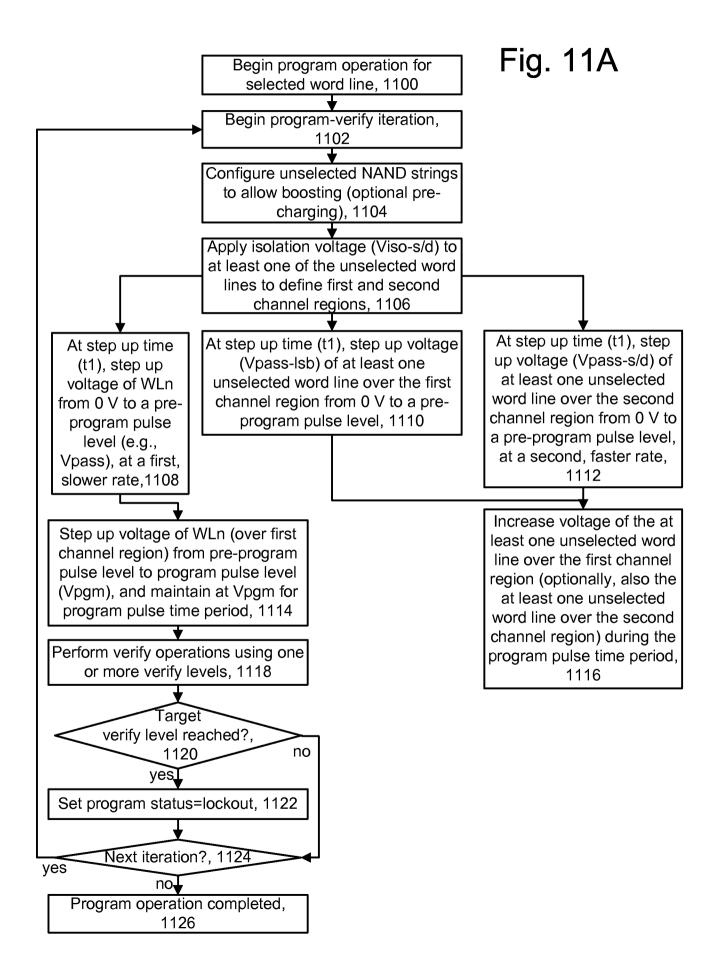

[0043] FIG. 11A depicts a programming method, e.g., based on the boosting technique of FIG. 8A or 9A.

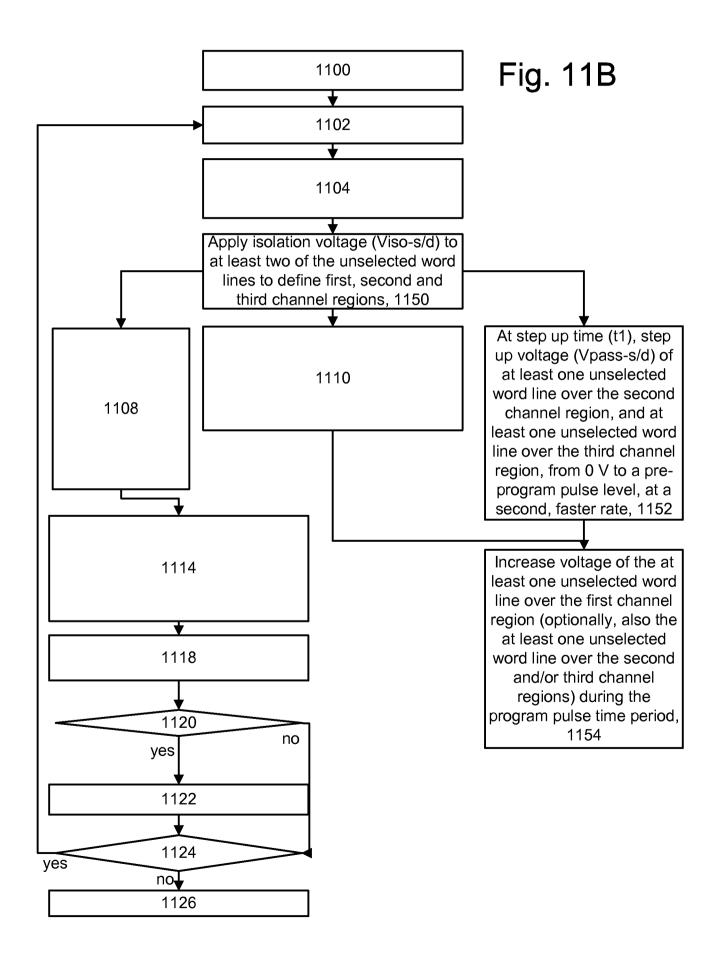

[0044] FIG. 11B depicts a programming method, e.g., based on the boosting technique of FIG. 10A.

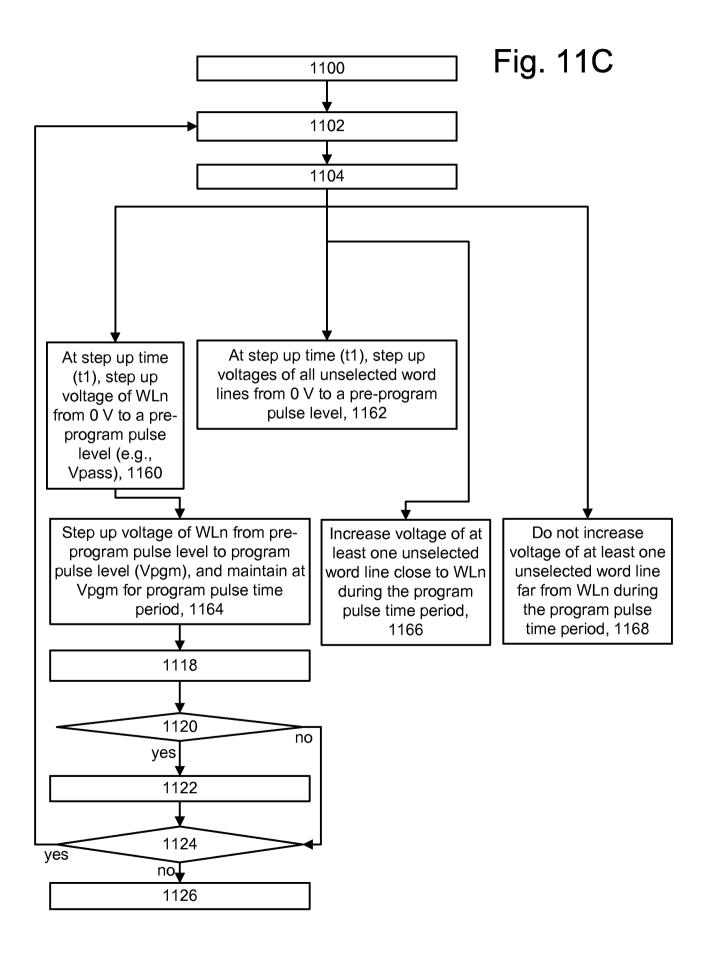

[0045] FIG. 11C depicts an additional programming method, e.g., based on the boosting technique of FIG. 5A.

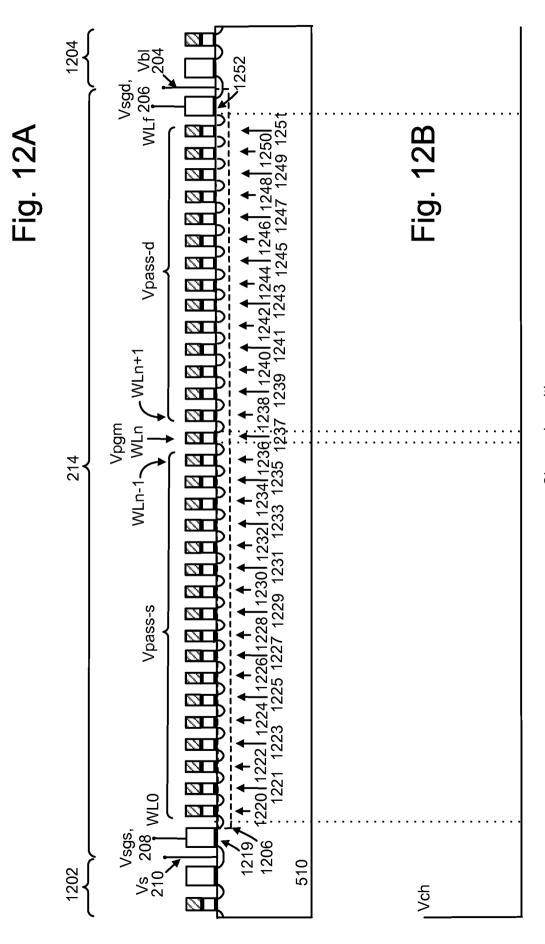

[0046] FIG. 12A depicts a cross-sectional view of the selected NAND string 214 of FIG. 2A.

[0047] FIG. 12B is a graph showing no channel boosting in the substrate of the selected NAND string of FIG. 12A.

-7-

## **DETAILED DESCRIPTION**

[0048] A method and non-volatile storage system are provided in which programming is optimized to reduce program disturb.

During a programming operation, unselected storage elements which [0049] have previously completed programming to a target data state are inhibited or locked out from further programming by boosting associated substrate channel regions. Channel boosting is used to reduce the occurrence of program disturb of inhibited storage elements in which their threshold voltages are raised to a next higher data state, other data states, or to a level at which the storage element cannot be accurately read, for example, in between two adjacent data The occurrence of Vpass disturb is also reduced. Program disturb generally refers to disturbs which occur on inhibited storage elements that are associated with other storage elements that are still being programmed, i.e. storage elements that are controlled by the same word line and are subjected to a program voltage. Vpass disturb generally refers to disturbs which are caused specifically by pass voltages. A channel boosting level can deteriorate over time, more specifically, the channel boosting level can deteriorate during the application of a program voltage or program pulse due to leakage currents, later referred to as channel leakage, and thus result in worsening program disturb. Moreover, the ambient temperature of the memory device can affect the amount of program disturb as the channel leakage can be temperature dependent.

[0050] It has been determined that channel boosting can be improved by providing a controlled increase of a voltage which is applied to one or more unselected word lines during a program pulse time period in which a program pulse is applied to a selected word line. The increase can be gradual, in the form of a ramp, or step-wise, in the form of a staircase, for instance. This controlled increase helps maintain the boosting level of the first channel region by offsetting the effects of channel leakage. Moreover, the rate of increase in the voltage can vary with temperature to further optimize the channel boosting

-8-

level. Channel boosting levels can be improved at high temperatures without increasing Vpass disturb at low temperatures.

[0051] In an additional aspect, before the program pulse time period in which a program pulse is applied, the voltage applied to the one or more unselected word lines can be ramped up at different rates for different unselected word lines to help isolate different channel regions and maintain the channel boosting level in at least one of the channel regions.

[0052] FIG. 1 is a block diagram of a non-volatile memory system using single row/column decoders and read/write circuits. The diagram illustrates a memory device 196 having read/write circuits for reading and programming a page of storage elements in parallel, according to one embodiment. Memory device 196 may include one or more memory die 198. Memory die 198 includes a two-dimensional array of storage elements 200, control circuitry 110, and read/write circuits 165. In some embodiments, the array of storage elements can be three dimensional. The memory array 200 is addressable by word lines via a row decoder 130 and by bit lines via a column decoder 160. The read/write circuits 165 include multiple sense blocks 100 and allow a page of storage elements to be read or programmed in parallel. Typically a controller 150 is included in the same memory device 196 (e.g., a removable storage card) as the one or more memory die 198. Commands and Data are transferred between the host and controller 150 via lines 120 and between the controller and the one or more memory die 198 via lines 118.

[0053] The control circuitry 110 cooperates with the read/write circuits 165 to perform memory operations on the memory array 200. The control circuitry 110 includes a state machine 112, an on-chip address decoder 114, and a power control module 116. The state machine 112 provides chip-level control of memory operations. The on-chip address decoder 114 provides an address interface between that used by the host or a memory controller to the hardware address used by the decoders 130 and 160. The power control module 116 controls the power and voltages supplied to the word lines and bit lines during

-9-

memory operations. During programming, the power supply module can supply different constant and varying voltages to the word lines and select gates. For example, voltages for a selected word line (Vwl-sel) can include Vpre-program, Vpass and Vpgm. Voltages for the select gates can include Vsgd and Vsgs. Voltages for an unselected word line (Vwl-unsel) can include Vpass, Vpass-s/d, Vpass-lsb, Vint and Viso-s/d. The voltages applied to the word lines can be independent and have their own step-up rate and/or ramp rate. Different step-up rates or ramp rates can be achieved using different RC time constants. With a lower RC time constant, the step up or ramp is faster, and with a higher RC time constant, the step up or ramp is slower.

A temperature compensation block 113 can provide a temperature-[0054] dependent reference signal for use by the control circuitry, such as in setting voltages of unselected word lines as described further below. techniques are known for providing a temperature-dependent reference signal for a memory device. In one possible approach, a band gap circuit is used. For example, U.S. Patent No. 6,801,454, titled "Voltage Generation Circuitry Having Temperature Compensation," incorporated herein by reference, describes a voltage generation circuit which outputs read voltages to a nonvolatile memory based on a temperature coefficient. The circuit uses a band gap current which includes a temperature-independent portion and a temperaturedependent portion which increases as temperature increases. U.S. Patent No. 6,560,152, titled "Non-Volatile Memory With Temperature-Compensated Data Read," incorporated herein by reference, uses a bias generator circuit which biases a voltage which is applied to a source or drain of a data storage element. U.S. Pat. No. 5,172,338, titled "Multi-State EEPROM Read and Write Circuits and Techniques", incorporated herein by reference, describes a temperaturecompensation technique which uses reference storage cells that are formed in the same manner, and on the same integrated circuit chip, as data storage cells. The reference storage cells provide reference levels against which measured currents or voltages of the selected cells are compared. Temperature

compensation is provided since the reference levels are affected by temperature in the same manner as the values read from the data storage cells. Any of these techniques, as well as any other known techniques, can be used to provide a temperature-dependent reference signals.

[0055] In some implementations, some of the components of FIG. 1 can be combined. In various designs, one or more of the components (alone or in combination), other than storage element array 200, can be thought of as a managing or control circuit. For example, one or more managing or control circuits may include any one of, or a combination of, control circuitry 110, state machine 112, decoders 114/160, power control 116, sense blocks 100, read/write circuits 165, controller 150, etc.

[0056] In another embodiment, a non-volatile memory system uses dual row/column decoders and read/write circuits. Access to the memory array 200 by the various peripheral circuits is implemented in a symmetric fashion, on opposite sides of the array, so that the densities of access lines and circuitry on each side are reduced by half. Thus, the row decoder is split into two row decoders and the column decoder into two column decoders. Similarly, the read/write circuits are split into read/write circuits connecting to bit lines from the bottom and read/write circuits connecting to bit lines from the top of the array 200. In this way, the density of the read/write modules is essentially reduced by one half.

[0057] FIG. 2A depicts an example block in a memory array, such as the memory array 200 of FIG. 1. See also FIG. 2B. The block 201 includes example bit lines BL0 (202), BL1 (204), ... and f+1 word lines WL0 through WLf. SGS represents a common control line 208 for a source-side select gate, SGD represents a common control line 206 for a drain-side select gate, and line 210 represents a common source line for the block 201. Each bit line is in communication with a set of storage elements in a respective NAND string, such as NAND strings 212 and 214 associated with BL0 and BL1, respectively. In examples further below, the NAND string 212 is considered to be unselected

for programming, and the NAND string 214 is considered to be selected for programming, as an example. Other NAND strings in the block can similarly be selected or unselected. All bit line programming can be used in which adjacent NAND strings in a block are programmed concurrently. That is, for a selected word line, adjacent storage elements in different NAND strings are programmed concurrently.

FIG. 2B depicts a memory array 200 comprising multiple blocks, [0058] such as the block 201 of FIG. 2A. As one example, a NAND flash EEPROM is described that is partitioned into M=1,024 blocks. The data stored in each block can be simultaneously erased. In one embodiment, the block is the minimum unit of storage elements that are simultaneously erased. Storage elements can be erased by raising the p-well to an erase voltage (e.g., 14-22 V) and grounding the word lines of a selected block while floating the source and bit lines. Erasing can be performed on the entire memory array, separate blocks, or another unit of the storage elements which is a portion of the memory device. During erasing, electrons are transferred from the floating gates of the storage elements to the p-well region so that the Vth of the storage elements becomes negative. A strong electric field is applied to the tunnel oxide layers of selected storage elements and the data of the selected storage elements are erased as electrons of the floating gates are emitted to the substrate side, typically by Fowler-Nordheim tunneling mechanism. As electrons are transferred from the floating gate to the p-well region, the Vth of a selected storage element is lowered.

[0059] FIG. 3A depicts an example set of threshold voltage distributions for a four-state memory device in which each storage element stores two bits of data. A first threshold voltage (Vth) distribution 300 is provided for erased (Estate) storage elements. Three Vth distributions 302, 304 and 306 represent programmed states A, B and C, respectively. In one embodiment, the threshold voltages in the E-state and the threshold voltages in the A, B and C distributions are positive.

**[0060]** Three read reference voltages, Vra, Vrb and Vrc, are also provided for reading data from storage elements. By testing whether the threshold voltage of a given storage element is above or below Vra, Vrb and Vrc, the system can determine the state, e.g., programming condition, the storage element is in.

**[0061]** Further, three verify reference voltages, Vva, Vvb and Vvc, are provided. When programming storage elements to the A-state, B-state or C-state, the system will test whether those storage elements have a threshold voltage greater than or equal to Vva, Vvb or Vvc, respectively.

[0062] In one embodiment, known as full sequence programming, storage elements can be programmed from the E-state directly to any of the programmed states A, B or C. For example, a population of storage elements to be programmed may first be erased so that all storage elements in the population are in the E-state. A series of program pulses such as depicted in FIG. 4A will then be used to program storage elements directly into states A, B or C. While some storage elements are being programmed from the E-state to the A-state, other storage elements are being programmed from the E-state to the B-state and/or from the E-state to the C-state.

[0063] Another option is to use low and high verify levels for one or more data states. For example, VvaL and Vva are lower and higher verify levels, respectively, for the A-state, VvbL and Vvb are lower and higher verify levels, respectively, for the B-state, and VvcL and Vvc are lower and higher verify levels, respectively, for the C-state. In some case, VvcL is not used since reduced programming precision may be acceptable for the highest state. During programming, when the Vth of a storage element which is being programmed to the A-state as a target state exceeds VvaL, the programming speed of the storage element is slowed down, in a slow programming mode, such as by raising the associated bit line voltage to a level, e.g., 0.5-1.0 V, which is between a nominal program or non-inhibit level, e.g., 0 V and a full inhibit level, e.g., 2-4 V. This provides greater accuracy by avoiding large step increases in

threshold voltage. When the Vth reaches Vva, the storage element is locked out from further programming. Similarly, when the Vth of a storage element which is being programmed to the B-state as a target state exceeds VvbL, the programming speed of the storage element is slowed down, and when the Vth reaches Vvb, the storage element is locked out from further programming. Optionally, when the Vth of a storage element which is being programmed to the C-state as a target state exceeds VvcL, the programming speed of the storage element is slowed down, and when the Vth reaches Vvc, the storage element is locked out from further programming. This programming technique has been referred to as a quick pass write or dual verify technique. Note that, in one approach, dual verify levels are not used for the highest state since some overshoot is typically acceptable for that state. Instead, the dual verify levels can be used for the programmed states, above the erased state, and below the highest state.

[0064] FIG. 3B illustrates a first pass of a two-pass programming technique. In this example, a multi-state storage element that stores data for two different pages: a lower page and an upper page. Four states are depicted by repeating the threshold voltage distributions 300, 302, 304 and 306 from FIG. 3A. These states, and the bits they represent, are: E-state (11), A-state (01), B-state (00) and C-state (10). For E-state, both pages store a "1." For A-state, the lower page stores a "1" and the upper page stores a "0." For B-state, both pages store "0." For C-state, the lower page stores "0" and the upper page stores "1." Note that although specific bit patterns have been assigned to each of the states, different bit patterns may also be assigned.

[0065] In the first programming pass, the lower page is programmed for a selected word line WLn. If the lower page is to remain data 1, then the storage element state remains at state E (distribution 300). If the data is to be programmed to 0, then the threshold voltage of the storage elements on WLn are raised such that the storage element is programmed to an intermediate (LM or lower middle) state (distribution 305).

[0066] In one embodiment, after a storage element is programmed from the E-state to the LM-state, as indicated by step "1" in FIG. 4B, its neighbor storage element on an adjacent word line WLn+1 in the NAND string will then be programmed with respect to its lower page in a respective first programming pass of the adjacent word line, as indicated by step "2" in FIG. 4B.

[0067] FIG. 3C illustrates a second pass of the two-pass programming technique of FIG. 3B. The A-state storage elements are programmed from the E-state distribution 300 to the A-state distribution 302, the B-state storage elements are programmed from the LM-state distribution 305 to the B-state distribution 304, and the C-state storage elements are programmed from the LM-state distribution 305 to the C-state distribution 306. The second pass of the two-pass programming technique for WLn is indicated by step "3" in FIG. 4B. The second pass of the two-pass programming technique for WLn+1 is indicated by step "5" in FIG. 4B.

[0068] FIG. 3D illustrates a first pass of another two-pass programming technique. In this example, referred to as foggy-fine programming, the A-state, B-state and C-state storage elements are programmed from the E-state to distributions 312, 314 and 316, respectively, using lower verify levels VvaL, VvbL and VvcL, respectively. This is the foggy programming pass. A relatively large program voltage step size may be used, for instance, to quickly program the storage elements to the respective lower verify levels.

**[0069]** FIG. 3E illustrates a second pass of the two-pass programming technique of FIG. 3D. The A-state, B-state and C-state storage elements are programmed from the respective lower distributions to respective final distributions 302, 304 and 306, respectively, using the nominal, higher verify levels Vva, Vvb and Vvc, respectively. This is the fine programming pass. A relatively small program voltage step size may be used, for instance, to slowly program the storage elements to the respective final verify levels while avoiding a large overshoot.

[0070] Although the programming examples depict four data states and two

pages of data, the concepts taught can be applied to other implementations with more or fewer than four states and more or fewer than two pages. For example, memory devices with eight or sixteen states per storage element are currently planned or in production.

[0071] Moreover, in the example programming techniques discussed, the Vth of a storage element is raised gradually as it is programmed to a target data state. However, programming techniques can be used in which the Vth of a storage element is lowered gradually as it is programmed to a target data state. Programming techniques which measure storage element current can be used as well. The concepts herein can be adapted to the different programming techniques.

FIG. 4A depicts a series of program and verify pulses which are [0072] applied to a selected word line during a programming operation. programming operation may include multiple program-verify iterations, where each iteration applies a program voltage followed by verify voltages, to a selected word line. In one possible approach, the program voltages are stepped up in successive iterations. Moreover, each program voltage may include a first portion which has a pass voltage (Vpass) level, e.g., 6-10 V, followed by a second, highest amplitude portion at a program level, e.g., 12-25 V. For example, a first, second, third and fourth program pulses 400, 402, 404 and 406 have program pulse levels of Vpgm1, Vpgm2, a Vpgm3 and Vpgm4, respectively, and so forth. One or more verify voltages, such as example verify voltages Vva, Vvb and Vvc (408), may be provided after each program pulse. In some cases, one or more initial program pulses are not followed by verify pulses because it is not expected that any storage elements have reached the lowest program state (e.g., A-state). Subsequently, program iterations may use verify pulses for the A-state, followed by program iterations which use verify pulses for the A- and B-states, followed by program iterations which use verify pulses for the B- and C-states, for instance.

[0073] FIG. 4B depicts a multi-pass program operation for a set of storage

elements. The components depicted may be a subset of a much larger set of storage elements, word lines and bit lines. In one possible program operation, storage elements on WLn-1, e.g., storage elements 402, 424 and 426, are programmed in a first programming pass. This step is represented by the circled "1." Next ("2"), storage elements on WLn, e.g., storage elements 432, 434 and 436, are programmed in a first programming pass. In this example, when a word line is selected for programming, verify operations occur after each program pulse. During the verify operations on WLn, one or more verify voltages are applied to WLn and pass voltages are applied to the remaining word lines including WLn-1 and WLn+1. The pass voltages are used to turn on (make conductive) the unselected storage elements so that a sensing operation can occur for the selected word line. Note that these pass voltages are often referred to as read voltages, or Vread, as these voltages are only applied during read or verify operations. Next ("3"), storage elements on WLn-1 are programmed in a second programming pass. Next ("4"), storage elements on WLn+1, e.g., storage elements 442, 444 and 446, are programmed in a first programming pass. Next ("5"), the storage elements on WLn are programmed in a second programming pass to their respective target states.

[0074] FIG. 5A depicts a cross-sectional view of an unselected NAND string showing a first channel boosting technique, in which a single boosted channel region is provided in the unselected NAND string 212 of FIG. 2A. Portions 502 and 504 of other NAND strings which are arranged end-to-end with the NAND string 212 are also depicted. The view is simplified and not to scale. The NAND string 212 includes a source-side select gate 519 connected to SGS control line 208, a drain-side select gate 552 connected to SGD control line 206, thirty-two non-volatile storage elements 520-551 (in communication with word lines WL0 to WLf, respectively), all of which are formed, at least partly, on a substrate 510, which can include an insulating layer. A source-side select gate 517 and a storage element 516 are part of the NAND string portion 502, while a drain-side select gate 553 and a storage element 554 are part of the

NAND string portion 504.

[0075] The source supply line 210 of FIG. 2A with a potential of Vs is provided between the select gates 517 and 519, while the bit line 202 of FIG. 2A with a voltage of Vbl is provided between the select gates 552 and 553.

**[0076]** A NAND string is typically formed in a p-well region of the substrate 510. The p-well region in turn may be within an n-well region of a p-type substrate. Each storage element includes a stacked gate structure that includes a control gate above a floating gate. The floating gates can be formed on the surface of the p-well on top of an oxide or other dielectric film. The control gate is above the floating gate, with an inter-polysilicon dielectric layer separating the control gate and floating gate. The control gates of the memory cells form the word lines. N+ doped regions (e.g., example source/drain region 507) in the substrate are shared between neighboring cells, whereby the cells are connected to one another in series to form a NAND string. These n+ doped regions form the source and drain of each of the cells. In one embodiment, n+ doped regions are not used and the channel areas in between adjacent memory cells are made conducting by fringing field effects that create electron rich regions that carry out the same function as the n+ doped regions.

[0077] Other types of non-volatile memory cells can also be used, such as memory cells in which the floating gate is replaced by a thin trapping layer such as Silicon Nitride in a so-called MONOS structure.

[0078] During programming, a programming voltage Vpgm is provided on a selected word line WLn, e.g., a word line associated with one or more storage elements to be programmed, such as storage element 537. Further, recall that the control gate of a storage element may be provided as a portion of the word line. For example, WL0 to WLf can extend via the control gates of storage elements 520-551, respectively. The word line voltages are therefore applied to all of the NAND strings, including selected and unselected NAND strings.

[0079] For the unselected NAND string, channel boosting techniques attempt to reduce the incidence of program disturb by boosting a channel area

506 of a substrate below an unselected NAND string during the program portion of a program-verify iteration. To achieve this, the source-side select gate 519 and the drain-side select gate 552 are rendered non-conductive, and voltages are applied to the unselected word lines. These voltages capacitively couple to the channel 506, thereby boosting the channel potential. For example, a pass voltage Vpass-s is applied to word lines in communication with storage elements 520-536 on the source side of WLn, and a pass voltage Vpass-d is applied to word lines in communication with storage elements 538-551 on the drain side of the selected word line. The source side of WLn is the side toward the source line 210, and the drain side of WLn is the side toward the drain line 206. Vpass-s and Vpass-d can be the same, in one approach. However in some cases, it can be more advantageous to use Vpass-s>Vpass-d to compensate for a reduction in channel boosting due to a source-to-drain programming order in which channel boosting is less for storage elements that are already in a programmed state.

[0800] An unselected storage element or NAND string may be referred to as an inhibited or locked out storage element or NAND string, respectively, as it is inhibited or locked out from programming in a given program-verify iteration of a programming operation. The channel region 506 represents a conductive path in the substrate, extending along the NAND string, from doped region to doped region. Boosting can be achieved in different ways. For example, in a precharge operation, which occurs before a pass voltage is applied to an unselected word line, a voltage supplied on the bit line 202 can be passed to the channel 506 via the drain-side select gate transistor 552. In one possible scenario, with an appropriate bit line voltage, the drain-side select gate transistor 552 provides a voltage of Vsgd - Vth to the channel, where Vsgd is the select gate voltage and Vth is the threshold voltage of the drain-side select gate transistor. In this case, Vsgd is set to a lower level in which the drain side select gate acts as a source-follower. During the pre-charge operation, the drain-side select gate transistor becomes non-conductive or at least less conductive, so that the bit line

Vth is maintained in the channel. Subsequently, additional channel boosting can be achieved by applying pass voltages to the unselected word lines and maintaining the drain-side select gate transistor non-conductive. As mentioned, the pass voltages couple to the channel, raising its potential. In other embodiments, during the pre-charge operation, the drain side select gate voltage is raised to a higher level which allows the drain side select gate to act as a pass gate and transfer the bit line voltage Vbl to the channel area 506. At the end of the pre-charge operation, the select gate voltage is lowered to the lower level to render the drain side select gate non-conductive. The advantage of such an embodiment is that the channel 506 can be pre-charged to a higher level and thus result in higher channel boosting when subsequently the pass voltages are applied.

[0081] In this example boosting technique, a single channel is formed along the entire NAND string. In various other channel boosting techniques, multiple channel regions which are isolated from one another are associated with each unselected NAND string, based on isolation voltages which are applied to the word lines. Examples of such channel boosting techniques are discussed further below.

[0082] FIG. 5B1 is a graph showing channel boosting levels in the substrate of the unselected NAND string of FIG. 5A, in one embodiment. The y-axis depicts a channel boosting level Vch and the x-axis depicts a distance in the substrate 510 along, and directly under, the NAND string 212. The x-axes of FIGs. 5A, 5B1 and 5B2 are aligned. A disadvantage of this boosting technique is that the boosting level is uneven - it is lower on the source side of the selected word line (Vch-s, waveform 512) than on the drain side of the selected word line (Vch-d, waveform 514). Generally, the amount of boosting of a channel region is proportional to a level of the voltages, and to a rate of increase of the voltages, on the word lines which are directly over the channel region, less a Vth of the storage elements.

[0083] Vch-d can exceed Vch-s when programming of storage elements along selected NAND strings progresses from word line to word line, starting from the lower-numbered (source side) word lines, e.g., WL0, WL1, ... and progressing to the higher-numbered (drain side) word line, e.g., ...WLf-1, WLf. In this case, when the higher-numbered word lines are used for programming, the storage elements in communication with the lower-numbered word lines already have been programmed, at least in part. Thus, for a given NAND string, all or some of storage elements which are below (on the source side of) the selected word line will have electrons programmed into and stored in their respective floating gates, and all or some of the other storage elements which are above (on the drain side of) the selected word line will be erased or partially programmed, depending on the programming mode. With the boosting technique of FIG. 5A, areas of the channel which are associated with the erased or only partly programmed storage elements experience relatively higher boosting, and areas of the channel which are associated with the fully programmed storage elements experience relatively lower boosting. During the boosting, the difference in boosted channel level Vch-d and Vch-s will reduce as electrons will flow from the highly boosted area 514 to the lowly boosted area 512. As a result, the boosted channel level will reduce as more and more storage elements in the NAND string are programmed. An equalized boosting level may be reached as indicated by the dashed line 513. This reduction in channel boosting level can be reduced or compensated by applying higher pass voltages to storage elements that are already in a programmed state, or more specifically, applying a higher pass voltage (e.g., Vpass-s>Vpass-d) to word lines on the source side of the selected word line than to word lines on the drain side of the selected word line.

[0084] See FIGs 12A and 12B for corresponding figures for a selected NAND string which experiences essentially no channel boosting.

[0085] FIG. 5B2 is a graph showing channel boosting levels in the substrate of the unselected NAND string of FIG. 5A, in another embodiment. Here, a

number of chosen unselected word lines which are close to WLn receive an increasing voltage during a program pulse time period to increase boosting of a portion 509 of the channel region 506 which is directly under the chosen unselected word lines and directly under WLn. The chosen unselected word lines could be associated with storage elements 534-536 and 538-540, for instance. Unselected word lines which are not close to WLn do not receive an increasing voltage during the program pulse time period so that boosting is not increased in portions 508 and 511 of the channel region 506 which are directly under the unselected word lines which are not close to WLn. The unselected word lines which are not close to WLn could be associated with storage elements 520-533 and 541-551, for instance. The portions 508 and 511 are depicted at an equalized level. Thus, an increasing voltage is applied to a chosen number of unselected word lines which are within a specified number of word lines from the selected word line, on either side of the selected word line. Optionally, an increasing voltage is not applied to other unselected word lines which are not within the specified number of word lines from the selected word line, on either side of the selected word line. See also the discussion in connection with FIG. 5J.

[0086] FIG. 5C depicts a voltage applied to a selected word line during a program portion of a program-verify iteration. The horizontal direction denotes time, while the vertical direction denotes amplitude. The waveforms of FIGs 5C-5I are time aligned. The time increments are not necessarily equally spaced. Waveform 590 depicts a nominal step up, discussed here, and waveform 592 depicts a case with a slow step up, as discussed further in connection with FIGs. 10C-10I.

[0087] Vwl-sel (a selected word line voltage) is at 0 V (or another low voltage) from t0-t1. At a step up time t1, Vwl-sel is stepped up from 0 V to a pre-program pulse level, Vpre-program, which can be the same as one or more pass voltages which are applied to one or more unselected word lines. This level, denoted by Vpass, can reach a substantially steady state level by t2, and

remain at that level from t2-t4. Or, Vwl-sel can continue to increase at a given rate until t4 is reached. t4 is a next step up time in which Vwl-sel is increased to a program pulse level Vpgm and is maintained at least at that level during a program pulse time period of t5-t8. t4 to t5 may be a transition or step up period. Note that the step-up or ramp at t1 can be at a different rate than the step-up or ramp at t4. Alternatively, Vpre-program can differ from Vpass. For example, Vpre-program could be 0 V (or another low voltage) in which case Vwl-sel is stepped up directly from 0 V to Vpgm.

[0088] FIG. 5D depicts a fixed voltage applied to unselected word lines during a program portion of a program-verify iteration, e.g., consistent with the channel boosting technique of FIG. 5A. Vwl-unsel (an unselected word line voltage) steps up at t1, along with Vwl-sel, in one approach, and remains fixed at Vpass during the program pulse time period. Generally, different types of unselected word line voltages (e.g., Vpass, Vpass-s/d and Vpass-lsb) can be independent and can have their own step up or ramp rate starting at t1 and starting at t4 or t5 or even later. We can distinguish two step up or ramp rates: a first one from 0 V to Vpass starting at t1, and a second one starting at t4, t5 or later.

[0089] FIG. 5E depicts a channel boosting level in the substrate of the NAND string, e.g., for the channel boosting technique of FIG. 5A, when the unselected word line voltage of FIG. 5D is used. Optionally, Vbl is increase (FIG. 5F) at t0, causing a pre-charge voltage, Vpre-charge, in the channel. When Vwl-unsel and Vwl-sel are stepped up to Vpass at t1, there is a corresponding increase in Vch. However, it has been observed that the channel boosting level is typically not maintained at a fixed level, but dissipates, due to the occurrence of leakage currents, during the program pulse time period, when a fixed pass voltage is used. There are various possible sources of channel leakage, e.g., leakage to poorly boosted channel regions, temperature-dependent leakage due to the reverse biased channel area, and leakage currents caused by GIDL (Gate Induced Drain Leakage) especially close to storage elements that

have a relatively low biased word line voltage and are in a high programmed state. Leakage can occur generally with any channel boosting scheme, regardless of whether there is one continuous channel region, such as in FIG. 5A, or multiple channel regions defined by isolation voltages, such as in FIGs. 8A, 9A and 10A. As a result, the likelihood of program disturb is increased. Boosting techniques which address this problem are described in detail further below.

[0090]FIG. 5F depicts a voltage applied to a bit line 202 of the unselected NAND string of FIG. 5A during a program portion of a program-verify iteration. Waveform 560 depicts an elevated voltage Vbl such as Vdd, e.g., 2-3 V, which is applied to the unselected NAND string at t0 to render the drain-side select gate non-conductive. Some pre-charge (Vpre-charge) of the channel occurs due to Vbl reaching the channel before the drain-side select gate is rendered nonconductive. The select gate is rendered non-conductive when its select gate voltage does not exceed the sum of Vbl and the Vth of the select gate. A precharge and a boosting level can be maintained in the substrate channel region below the unselected NAND string when the select gates are non-conductive. In contrast, waveform 562 depicts a Vbl which is applied to the bit line 204 of the selected NAND string to render the drain-side select gate conductive, so that boosting is not maintained in the substrate channel region below the selected NAND string. See also FIG. 12B. On the contrary, grounding the bit line and channel allows programming to occur in a selected storage element of the selected NAND string. In some programming schemes, Vbl is set above zero but below Vdd to partially inhibit, or slow down, the rate of programming.

[0091] FIG. 5G depicts a voltage applied to a line 206 in communication with a drain-side select gate of the unselected NAND string of FIG. 5A during a program portion of a program-verify iteration. As mentioned, at t0, Vsgd is set to a high level such as Vdd, to render the drain-side select gate conductive for a selected NAND string for which Vbl=0 V, or to render the drain-side select gate non-conductive for an unselected NAND string for which Vbl=Vdd. Vsgd can

rise before, at the same time, or after Vbl. In other embodiments, during the pre-charge operation from t0 to t1, the drain side select gate voltage is raised to a voltage higher than Vsgd or Vdd to be able to transfer the bit line voltage Vbl to the channel area 506. At the end of the pre-charge operation, the select gate voltage is lowered to Vsgd or Vdd to render the drain-side select gate non-conductive. The advantage of such an embodiment is that the channel 506 can be pre-charged to a higher level and thus result in higher channel boosting when subsequently the pass voltages are applied.

[0092] FIG. 5H depicts a voltage applied to a source line 210 of the unselected NAND string of FIG. 5A during a program portion of a program-verify iteration. Vs is set to a high level such as Vdd. The source line is common to all of the NAND strings, whether selected or unselected, in a block, in one configuration. In other embodiments, a voltage lower than Vdd, such as 1-2 V, can be applied.

[0093] FIG. 5I depicts a voltage applied to a line 208 in communication with a source-side select gate of the unselected NAND string of FIG. 5A during a program portion of a program-verify iteration. Vsgs is set to 0 V to render the source-side select gates non-conductive for the selected and unselected NAND strings, due to Vs being set high. Note that in general, even without applying a high Vs voltage, the source-side select gate can be non-conductive, however, by applying the bias voltage >0V the isolation characteristics of the source-side select gate are further improved.

[0094] FIG. 5J depicts a voltage applied to an unselected word line during a program portion of a program-verify iteration, where the voltage is increased in a linear or non-linear ramp, such as for the first channel boosting technique of FIG. 5A. Specifically, to counteract channel boosting leakage, discussed, e.g., in connection with FIG. 5E, Vwl-unsel is gradually increased in a controlled manner during all, or a portion of, the program pulse time period, when program disturb is most likely to occur. The increase is indicated by the sloped solid line from t4-t8, which reaches a maximum level of Vmax. The power control

module 116 of the control circuitry 100 may be configured for this purpose, as discussed further in connection with FIG. 1. This gradual increase serves to reduce or compensate the drop in the channel boosting level by counteracting or compensating the channel leakage current. In some cases, some reduction of the channel boosting level may still occur, but at a reduced rate. The gradual increase in Vwl-unsel can be linear (e.g., waveform 570), at a fixed rate of increase, or non-linear (e.g., waveform 572), at a varying rate of increase, over time. Further, the increase can be essentially continuous, e.g., ramp-like, based on the lowest increment of voltage which the power control module 116 can provide, or step-wise, such as depicted in FIG. 5L. Vwl-unsel can increase during a majority, e.g., over half, of the program pulse time period of t5-t8. Vwl-unsel thus increases within the program pulse time period. In the approach shown, Vwl-unsel begins increasing at t4, at the same time Vwl-sel is stepped up from Vpre-program and begins to approach Vpgm. Generally, the risk of program disturb is greatest when Vwl-sel has reached a high level such as Vpgm, so the time period in which Vwl-unsel increases should correspond to the time period in which Vwl-sel is high or is transitioning or close to the final high level.

[0095] In the approach shown, the increase is ramp like, increasing gradually or substantially continuously during the program pulse time period, at a fixed rate or slope. The increase in Vwl-unsel can be the same (e.g., same slope and duration of increase) for different program-verify iterations in which different levels of Vpgm are used. In another approach, the increase in Vwl-unsel is a function of Vpgm, so that a higher rate of increase and/or a longer duration of increase is used when Vpgm is higher. Thus, in the earlier program-verify iterations of a program operation, no increase, or a lower increase in Vwl-unsel is used, and in later program-verify iterations of the program operation, an increase, or higher increase, in Vwl-unsel is used. This approach accounts for the fact that program disturb is greatest when Vpgm is greatest, so that the countermeasure of increasing Vwl-unsel can be tailored to the level of

Vpgm. In yet another approach, Vwl-unsel at the beginning of the programming pulse (t4) can be dependent on Vpgm as well. This approach accounts for the fact that program disturb is greatest when Vpgm is greatest, so that the countermeasure of also using a higher Vwl-unsel at the beginning of the programming pulse can be tailored to the level of Vpgm. That is, an initial level (e.g., Vpass) of Vwl-unsel, at the beginning of the programming pulse (e.g., at t4), can be higher when the program pulse voltage is higher.

[0096]Moreover, all unselected word lines, or only particular unselected word lines, can receive an increasing voltage. Thus, some unselected word lines can receive an increasing voltage while others receive a fixed voltage. For example, in FIG. 5A and 5B2, where there is one continuous channel region 506 along the entire NAND string, chosen unselected word lines which are close to the selected word line could receive the gradually an increasing Vsl-unsel such as waveforms 570 or 572. This would increase the boosting level in the portion 509 of the channel region which is directly under the chosen unselected word lines and directly under the selected word line, where it is most needed to prevent disturbs. For instance, close word lines such as WLn-3 to WLn-1 and WLn+1 to WLn+3 could receive the waveform of FIG. 5J, which increases during the program pulse time period, while other unselected word lines, further from the selected word line, receive the waveform of FIG. 5D, which does not increase during the program pulse time period. The close word lines could alternatively receive another waveform which increases during the program pulse time period, such as shown in FIGs. 5L, 7A, 7B, 10C and 10F. A specified number N1 of word lines on the source side of WLn and a specified number of word line N2 on the drain side of WLn, can receive a waveform which increase during the program pulse time period. N1 and N2 are integer numbers greater or equal than one, and can be the same or different.

[0097] It is also possible for different unselected word lines to receive voltages which increase at different rates. For example, unselected word lines which are closer to the selected word line, such as WLn-1 and WLn+1, can

receive a higher increase and/or start at a higher level than unselected word lines which are farther from the selected word line. Vpass(n-1) is a voltage applied to WLn-1, and Vpass(n+1) is a voltage applied to WLn+1. Vpass(n-1/n+1) represents both voltages. This mode of biasing, which applies to any of the boosting techniques herein, reduces the voltage difference between the selected WL (WLn) and the adjacent neighbor word lines (WLn-1 and WLn+1) to reduce the possibility of breakdown or leakage between those word lines. Also, a higher bias voltage on the neighboring word lines assists in programming the memory cells on the selected word line by providing extra "parasitic" coupling. As a result, the programming voltage on the selected word line can be reduced compared to the case where the neighboring unselected word lines do not use a higher voltage than the non-neighboring unselected word lines. Further, the unselected word lines (WLn-2, WLn-3, ...) on the source side of the selected word line may received a higher voltage than the unselected word lines (WLn+2, WLn+3, ...) on the drain side of the selected word line, since cells on the source side are already programmed and are less susceptible to program disturb, or more accurately, Vpass disturb. Thus, a higher Vpass on those word lines is possible without increasing the likelihood of program disturb (e.g., Vpass disturb).

[0098] Increasing the voltages of the unselected word lines during the program pulse time period is advantageous because it compensates or reduces the effect of channel leakage while avoiding disadvantages of other approaches. For example, reducing the program pulse time period (the program pulse width) would reduce the effect of channel leakage, resulting in a reduction of the boosted channel level, and the total amount of channel leakage, since the leakage occurs over a shorter period of time, but at the expense of increasing the final Vpgm which is needed to complete programming and possibly even increasing the programming time as more programming loops maybe needed. Moreover, reductions in the program pulse time period are limited by the word line RC delay.

[0099] FIG. 5K depicts a channel boosting level in the substrate of the NAND string of FIG. 5A, e.g., based on the unselected word line voltages of FIG. 5J. The channel boosting level is approximately constant, as an example, due to the increasing Vwl-unsel that compensates for the channel leakage. As mentioned, generally, the amount of boost of a channel region is proportional to a level of the voltages, and to a rate of increase of the voltages, on the word lines which are directly over the channel region, less a Vth of the storage elements. By maintaining an approximately constant channel boosting level during the program pulse time period, program disturb can be reduced compared to the case where channel boosting level decreases during the program pulse time period, as in FIG. 5E. Some channel boosting level decrease could still occur, but it will be less than the case where Vwl-unsel is constant.

**[00100]** FIG. 5L depicts a step-wise increasing voltage applied to an unselected word line during a program portion of a program-verify iteration, as an alternative to the ramped voltage of FIG. 5J. The amplitude change (step height or rise) and/or duration of each step can be configured. In one approach, the step heights in the staircase are approximately equal and/or the step durations are approximately equal. A maximum level of Vmax is reached. If unequal step heights are used, larger steps could be followed by smaller steps, for example, or vice-versa. If unequal step durations are used, longer steps could be followed by shorter steps, for example, or vice-versa. The step height may be greater than the lowest increment of voltage which the power control module 116 can provide. A waveform which combines discrete steps with a ramp could also be used. Other variations are possible. Temperature-based variations to Vwl-unsel can also be used, as discussed further below. Or, Vwl-unsel can be temperature-independent.

[00101] FIG. 5M depicts a channel boosting level in the substrate of the NAND string of FIG. 5A, e.g., based on the unselected word line voltage of FIG. 5L. The channel boosting level generally decreases when Vwl-unsel is constant,

e.g., during the run of a step, and increases during the rise of a step, so that a repeated pattern of decreasing and increasing is expected. The program pulse time period t5-t8 is depicted for reference.

**[00102]** Another consideration in reducing program disturb is that temperature changes in a memory device can affect the channel boosting level. For example, FIG. 6A depicts a graph showing bit errors as a function of pass voltage for unselected word lines for a typical boosting technique, for different temperatures.

[00103] Program disturb related bit errors are typically highest for storage elements in the erased state. The y-axis depicts a number of bit errors and the x-axis depicts a pass voltage. Curves 600, 602 and 604 provide data for temperatures of 25 °C, 55 °C and 85 °C, respectively. Each curve has a different point (a minimum, marked by a dot) at which the number of errors is minimal. This is the optimum pass voltage, e.g., Vpass-opt1, Vpass-opt2 or Vpass-opt3 for curve 600, 602 or 604, respectively. At higher temperatures, a higher Vpass can result in fewer errors due to better channel boosting, up to a certain point, which is the optimum Vpass. Above the optimum Vpass, errors are increased due to Vpass disturb. The optimum Vpass is lower for lower temperatures.

[00104] FIG. 6B depicts an optimum pass voltage for unselected word lines for a typical channel boosting technique, as a function of temperature, consistent with FIG. 6A. The optimum Vpass can be approximated as a linear function of temperature (dashed line). As a result, the change in the optimum Vpass as a function of temperature can be described by a constant temperature coefficient. By adjusting the pass voltages of unselected word lines during programming as a function of temperature, the performance of the memory device can be improved. In particular, a higher pass voltage can be used when the temperature is higher. Similarly, in a boosting technique which increases the pass voltage during the program pulse time period, a higher rate of increase and/or a longer duration of increase, can be used when the temperature is higher.

[00105] FIG. 7A depicts a voltage applied to an unselected word line during a program portion of a program-verify iteration, where the voltage is increased like a ramp, as a function of temperature, such as for the first channel boosting technique of FIG. 5A. As an extension of the discussion in connection with FIG. 5J, waveforms 700, 702 and 704 can be used for a relatively high temperature such as 85 °C, an intermediate temperature such as 55 °C, and a relatively low temperature such as 25 °C, respectively. Maximum levels of Vmax1, Vmax2 and Vmax3 are reached. In one possible approach, a given waveform is used for a range of temperatures. For example, waveform 700 can be used for temperatures of 70 °C or higher, waveform 702 can be used for temperatures from 40-70 °C and waveform 704 can be used for temperatures below 40 °C. By tailoring the rate of increase to temperature, program disturb can be optimally reduced even in different temperature environments of the memory device. Moreover, since Vpass is lower when the temperature is lower, Vpass disturb at lower temperatures is reduced.

[00106] The ramp rate can be set by a coefficient which describes the rate of change of Vwl-unsel per unit of time as a function of temperature.

[00107] FIG. 7B depicts a step-wise increasing voltage applied to an unselected word line during a program portion of a program-verify iteration, as a function of temperature, as an alternative to the ramped voltage of FIG. 7A. As an extension of the discussion in connection with FIG. 5L, waveforms 720, 722 and 724 can be used for 85 °C, 55 °C and 25 °C, respectively. Maximum levels of Vmax1, Vmax2 and Vmax3 are reached. In one possible approach, a given waveform is used for a range of temperatures. For example, waveform 720 can be used for temperatures of 70 °C or higher, waveform 722 can be used for temperatures from 40-70 °C and waveform 724 can be used for temperatures below 40 °C. The step height and/or duration can be a function of temperature. In this example, the height of each step is a function of temperature (larger step height for higher temperatures) while the step durations (t8-7, t7-t6 and t6-t5) are independent of temperature.

[00108] FIG. 8A depicts a cross-sectional view of the unselected NAND string 212 of FIG. 2A showing a second channel boosting technique. A first channel region 802 and a second channel region 800 are defined in the substrate 510 due to the application of an isolation voltage Viso-s on the source side of WLn, and the application of non-isolation voltages on other unselected word lines. This approach allows independent boosting levels to be achieved in the different channel regions. In one approach, the isolation voltage is applied to a word line which is relatively close to WLn, to provide separate channel boosting regions for programmed storage elements on the source side of WLn, and for unprogrammed or only partly programmed storage elements on the drain side of WLn. However, the isolation word line can be separated from WLn by a few word lines, for instance, so that the isolation voltage does not adversely affect the channel boosting level under WLn.

[00109] An isolation voltage can be a relatively small voltage such as 0-3 V which is sufficiently low to essentially isolate channel regions in the substrate on either side of the word line (an isolation word line) which receives the isolation voltage. In comparison, a nominal Vwl-unsel might be 6-10 V, for instance. Further, a set of multiple adjacent word lines can receive an isolation voltage to more strongly isolate the channel regions in the substrate on either side of the set of word lines which receives the isolation voltage. Additionally, to provide a gradual transition to the isolation region, one or more word lines which are adjacent to an isolation word line can receive a voltage (Vint) which is intermediate to Viso and the nominal Vwl-unsel.

[00110] In this example, Viso-s is applied to a word line which communicates with storage element 531, and Vint is applied to the unselected word lines which are adjacent to the word line which receives Viso-s. Specifically, Vint is applied to word lines which communicate with storage elements 530 and 532. On the source side of the isolation word line, Vpass-s is applied to word lines which communicate with storage elements 520 to 529. Further on the drain side of the isolation word line, Vpass-lsb is applied to word

lines which communicate with storage elements 533 to 536 and 538 to 551. Vpass-lsb is a local self-boosting voltage of, e.g., 6-10 V. WLn extends directly over the first channel region 802. The boosting of the channel region 800 is set by the voltages of the word lines which are directly above the channel region 800, resulting in the channel boosting profile 804 of FIG. 8B. A boosting level of Vch-s is achieved under the word lines which receive Vpass-s, while a lower boosting level is achieved under the word line (and storage element 530) which receives Vint. Similarly, a boosting level of Vch-lsb 808 is achieved under the word lines which receive Vpass-lsb, while a lower boosting level is achieved under the word line (and storage element 532) which receives Vint. An even lower boosting level that depends on the bias voltages Vint, Viso-s and the state of the storage elements may be achieved under the word line (and storage element 531) which receives Viso-s.

[00111] Since Vpass-lsb is applied to only a small number of word lines, in one approach, it may be higher than Vpass-d, as the storage elements will be exposed to Vpass-lsb for a shorter time than to Vpass-d. Vpass-s, relative to Vpass-lsb or Vpass-d, can be quite high because the associated storage elements are already programmed and therefore less susceptible to program disturb. Vpass-lsb maybe higher than Vpass-d as it is applied to fewer WLs and thus each WL is exposed a shorter total time to Vpass-lsb and thus Vpass disturb will be less of a concern. Further, a high Vpass may cause Vpass disturb on, for example, WLn+2 and 3, while it may be safe to apply a high Vpass to WLn-2 and n-3. In some embodiments, Vpass-lsb on the source side of WLn can be higher than Vpass-lsb on the drain side of WLn for this reason.

[00112] FIG. 8B is a graph showing channel boosting levels in the substrate of the unselected NAND string of FIG. 8A. The x-axes of FIGs. 8A and 8B are aligned. As mentioned, waveform 804 represents a boosting level on the source side of the isolation word line, while waveform 808 represents a boosting level on the drain side of the isolation word line.

[00113] FIG. 9A depicts a cross-sectional view of the unselected NAND

string 212 of FIG. 2A showing a third channel boosting technique. This boosting technique essentially is a reverse of the technique of FIG. 8A, and uses an isolation voltage on the drain side of WLn instead of on the source side. Although, this boosting technique is less advantageous than others because it isolated the poorly boosted channel region area at the drain side.

[00114] Specifically, a first channel region 900 and a second channel region 902 are defined in the substrate 510 due to the application of an isolation voltage Viso-d on the drain side of WLn, and the application of non-isolation voltages on other unselected word lines. This approach allows independent boosting levels to be achieved in the different channel regions.

Viso-d is applied to a word line which communicates with storage element 543, and Vint is applied to the unselected word lines which are adjacent to the word line which receives Viso-d. Specifically, Vint is applied to word lines which communicate with storage elements 542 and 544. On the source side of the isolation word line, Vpass-lsb is applied to word lines which communicate with storage elements 520 to 536 and 538 to 541. Further on the drain side of the isolation word line, Vpass-d is applied to word lines which communicate with storage elements 545 to 551. WLn extends directly over the first channel region 900. The boosting of the channel region 900 is set by the voltages of the word lines which are directly above the channel region 900, resulting in the channel boosting profile 904 of FIG. 9B. A boosting level of Vch-lsb is achieved under the word lines which receive Vpass-lsb, while a lower boosting level is achieved under the word line (and storage element 542) which receives Vint. Similarly, a boosting level of Vch-d 908 is achieved under the word lines which receive Vpass-d, while a lower boosting level is achieved under the word line (and storage element 544) which receives Vint. An even lower boosting level may be achieved under the word line (and storage element 543) which receives Viso-d. Vpass-d can be the same as, or less than Vpass-lsb, for instance, when a source-to-drain word line programming order is used.

[00116] FIG. 9B is a graph showing channel boosting levels in the substrate

of the unselected NAND string of FIG. 9A. The x-axes of FIGs. 9A and 9B are aligned. As mentioned, waveform 904 represents a boosting level on the source side of the isolation word line, while waveform 908 represents a boosting level on the drain side of the isolation word line.

[00117] FIG. 10A depicts a cross-sectional view of the unselected NAND string 212 of FIG. 2A showing a fourth channel boosting technique. This boosting technique combines the techniques of FIGs. 8A and 9A. It uses isolation voltages on both the source and drain sides of WLn. Specifically, a first channel region 1002, a second channel region 1004, and a third channel region 1000 are defined in the substrate 510 due to the application of an isolation voltage Viso-s on the source side of WLn, an isolation voltage Viso-d on the drain side of WLn, and non-isolation voltages on other unselected word lines.

[00118] This approach allows independent boosting levels to be achieved in the different channel regions. In one approach, the isolation voltages are applied to word lines which are relatively close to WLn, on either side of WLn, to provide separate channel boosting regions for programmed storage elements on the source side of WLn, unprogrammed or only partly programmed storage elements on the drain side of WLn and a small channel region which extends directly under WLn.

**[00119]** Viso-s is applied to a word line which communicates with storage element 531, and Vint is applied to the unselected word lines which are adjacent to the word line which receives Viso-s. Specifically, Vint is applied to word lines which communicate with storage elements 530 and 532.

**[00120]** Viso-d is applied to a word line which communicates with storage element 543, and Vint is applied to the unselected word lines which are adjacent to the word line which receives Viso-d. Specifically, Vint is applied to word lines which communicate with storage elements 542 and 544.

[00121] On the source side of the word line which receives Viso-s, Vpass-s is applied to word lines which communicate with storage elements 520 to 529.

Between the word line which receives Viso-s and WLn, Vpass-lsb is applied to word lines which communicate with storage elements 520 to 529. Between WLn and the word line which receives Viso-s, Vpass-lsb is applied to word lines which communicate with storage elements 538 to 541. Between the word line which receives Viso-d and SGD, Vpass-d is applied to word lines which communicate with storage elements 545 to 551.

[00122] FIG. 10B is a graph showing channel boosting levels in the substrate of the unselected NAND string of FIG. 10A. The x-axes of FIGs. 10A and 10B are aligned. Boosting levels of Vch-lsb, Vch-d and Vch-s are achieved in the first, second and third channel boosting regions (waveforms 1010, 1012 and 1006, respectively),

[00123] FIG. 10C depicts voltages applied to unselected word lines during a program portion of a program-verify iteration, e.g., for the channel boosting techniques of FIGs. 5A, 8A, 9A or 10A. The waveforms of FIGs. 5F-5I may be used with the waveforms of FIGs. 10C and 10D. The time scale in FIGs. 5F-5I corresponds with that in FIGs. 10C and 10D. Waveform 1066 depicts Viso-s or Viso-d (e.g., Viso-s/d), and waveform 1064 depicts Vint. Waveform 1060 depicts Vpass-s or Vpass-d (e.g., Vpass-s/d), and waveform 1062 depicts Vpass-lsb. For waveform 1062, a maximum level of Vmax is reached. For simplicity, Vpass-s, Vpass-d and Vpass-lsb are depicted as being stepped up to the same level at t1, although they can be stepped up to different levels, as discussed.

[00124] In this example, the unselected word lines which contribute to boosting of the channel which WLn extends directly over, have their voltages increase during the program pulse time period, and the unselected word lines which extend directly over another channel do not have their voltages increased during the program pulse time period. Alternatively, the unselected word lines which are close to WLn, e.g., within a few word lines on either side of WLn, can have their voltages increased during the program pulse time period. These approaches address the increased chance of program disturb for storage

elements which are in communication with WLn by maintaining the associated channel boosting level (waveform 1070, FIG. 10D). In this approach, it is acceptable to allow the channel boosting level to decrease for one or more other channel boosting regions (waveform 1072, FIG. 10D), e.g., under word lines which are further away from WLn, since the risk of Vpass disturb is less. Limiting the unselected word lines for which Vpass increases also can reduce a risk of Vpass disturb for the associated storage elements.