(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5972881号

(P5972881)

(45) 発行日 平成28年8月17日(2016.8.17)

(24) 登録日 平成28年7月22日(2016.7.22)

|               |              |

|---------------|--------------|

| (51) Int.Cl.  | F 1          |

| HO 1 L 29/74  | (2006.01)    |

| HO 1 L 29/861 | (2006.01)    |

| HO 1 L 29/868 | (2006.01)    |

| HO 1 L 21/322 | (2006.01)    |

|               |              |

|               | HO 1 L 29/74 |

|               | HO 1 L 29/91 |

請求項の数 15 (全 14 頁) 最終頁に続く

|               |                               |

|---------------|-------------------------------|

| (21) 出願番号     | 特願2013-530733 (P2013-530733)  |

| (86) (22) 出願日 | 平成23年9月29日 (2011.9.29)        |

| (65) 公表番号     | 特表2013-543260 (P2013-543260A) |

| (43) 公表日      | 平成25年11月28日 (2013.11.28)      |

| (86) 國際出願番号   | PCT/EP2011/066979             |

| (87) 國際公開番号   | W02012/041958                 |

| (87) 國際公開日    | 平成24年4月5日 (2012.4.5)          |

| 審査請求日         | 平成26年8月1日 (2014.8.1)          |

| (31) 優先権主張番号  | 10181546.2                    |

| (32) 優先日      | 平成22年9月29日 (2010.9.29)        |

| (33) 優先権主張国   | 歐州特許庁 (EP)                    |

|           |                                                                                   |

|-----------|-----------------------------------------------------------------------------------|

| (73) 特許権者 | 505063441<br>アーベーベー・テヒノロギー・アーゲー<br>スイス国、シーエイチ-8050 チュ<br>リッヒ、アフォルテルンシュトラーセ 4<br>4 |

| (74) 代理人  | 100108855<br>弁理士 蔵田 昌俊                                                            |

| (74) 代理人  | 100109830<br>弁理士 福原 淑弘                                                            |

| (74) 代理人  | 100088683<br>弁理士 中村 誠                                                             |

| (74) 代理人  | 100103034<br>弁理士 野河 信久                                                            |

| (74) 代理人  | 100095441<br>弁理士 白根 俊郎                                                            |

最終頁に続く

(54) 【発明の名称】逆導通パワー半導体デバイス

## (57) 【特許請求の範囲】

## 【請求項 1】

第1の主面(11)および前記第1の主面(11)に平行に配置された第2の主面(15)を有するウェハ(10)を伴う逆導通パワー半導体デバイス(1)であって、前記デバイスは、複数のダイオードセル(96)および複数のIGCTセル(91)を具備すること、ここにおいて、各IGCTセル(91)は、前記第1および第2の主面(11, 15)の間に以下の順で複数の層を具備する：

- カソード電極(2)、

- 第1導電型の第1のカソード層(4)、

- 第2導電型のベース層(6)、

- 前記第1導電型のドリフト層(3)、

- 前記第1導電型のバッファ層(8)、

- 前記第2導電型の第1のアノード層(5)、

- 第1のアノード電極(25)、

10

ここにおいて、各IGCTセル(91)は、前記第1のカソード層(4)の横に配置され、そして、それとは前記ベース層(6)によって分離されているゲート電極をさらに具備し、

ここにおいて、各ダイオードセル(96)は、前記第1の主面(11)上の第2のアノード電極(28)、前記ドリフト層(3)によって前記ベース層(6)から分離された前記第2導電型の第2のアノード層(55)、および、前記第2の主面(15)上で前記第

20

1 のアノード層 ( 5 ) と交互に配置された前記第 1 導電型の第 2 のカソード層 ( 4 5 ) を具備し、および、

ここにおいて、前記デバイスは、少なくとも一つの混合部 ( 9 9 ) を具備しており、その中では前記ダイオードセル ( 9 6 ) の前記第 2 のアノード層 ( 5 5 ) は前記 I G C T セル ( 9 1 ) の前記第 1 のカソード層 ( 4 ) と交互する、

ことを特徴とする逆導通パワー半導体デバイス ( 1 )。

**【請求項 2】**

請求項 1 のデバイス ( 1 ) において、前記混合部 ( 9 9 ) 内で、各ダイードセル ( 9 6 ) は、一つの第 2 のアノード層 ( 5 5 ) が二つの第 1 のカソード層 ( 4 ) および / またはゲート電極 ( 7 ) の間に配置されるように、配置されることを特徴とする。 10

**【請求項 3】**

請求項 1 のデバイス ( 1 ) において、I G C T セル ( cells ) 9 1 に対するダイオードセル ( cells ) 9 6 の比は 1 : 1 ないし 1 : 5 であり、ここにおいて、前記ダイオードセルの数は前記第 2 のアノード層 ( 5 5 ) の数として定義され、そして、前記 I G C T セルの数は前記第 1 のカソード層 ( 4 ) の数として定義されることを特徴する。 15

**【請求項 4】**

請求項 1 または 2 のいずれかのデバイス ( 1 ) において、前記デバイス ( 1 ) は、第 2 のアノード層 ( 5 5 ) を間に持つことなく、互いに隣接して直接的に配置された複数の第 1 のカソード層 ( 4 ) およびゲート電極 ( 7 ) からなる、少なくとも一つのパイロット I G C T 部 ( 9 ) を具備することを特徴とする。 20

**【請求項 5】**

請求項 4 のデバイス ( 1 ) において、前記少なくとも一つのパイロット I G C T 部 ( 9 ) は、前記ウェハの面積 ( total wafer area ) の 1 0 ないし 5 0 % の全面積 ( total area ) を有することを特徴する。 25

**【請求項 6】**

請求項 1 または 2 のいずれかのデバイス ( 1 ) において、前記第 2 のアノード層 ( 5 5 ) は、前記混合部 ( 9 9 ) 内の前記ウェハ上に均一に分散されていることを特徴する。 30

**【請求項 7】**

請求項 1 ないし 6 のいずれかのデバイス ( 1 ) において、前記 I G C T セル ( cells ) 9 1 の前記第 1 の主面側の部分に対する前記ダイオードセル ( cells ) 9 6 の少なくとも一つまたはすべて、または、前記 I G C T セル ( cells ) 9 1 の二つの隣り合う第 1 の主面側の部分は、前記第 1 の主面 ( 1 1 ) に平行な面内において 5 0 から 5 0 0  $\mu$ m までの最大ラテラルエクステンション ( lateral extension ) を互いに有することを特徴する。 35

**【請求項 8】**

請求項 1 ないし 7 のいずれかのデバイス ( 1 ) において、前記ベース層 ( 6 ) および前記第 2 のアノード層 ( 5 5 ) のドーピング濃度および深さの少なくとも一つは異なっており、特に前記第 2 のアノード層 ( 5 5 ) のドーピング濃度および深さの少なくとも一つは、前記ベース層 ( 6 ) のそれよりも低いことを特徴する。 40

**【請求項 9】**

請求項 1 ないし 8 のいずれかのデバイス ( 1 ) において、前記第 1 の主面 ( 1 1 ) に平行な面内における前記第 2 のカソード層 ( 4 5 ) の全面積 ( total area ) は前記ウェハの面積 ( total wafer area ) の 1 0 ないし 3 0 % であることを特徴する。 45

**【請求項 10】**

請求項 1 ないし 9 のいずれかのデバイス ( 1 ) において、前記第 2 のカソード層 ( layers ) ( 4 5 ) は、多くても I G C T セル ( 9 1 ) に直接的に隣接する第 1 のカソード層 ( 4 ) の正射影領域に制限される領域内において、前記第 2 のアノード層 ( 5 5 ) に正射影に配置されることを特徴とする。 50

**【請求項 11】**

請求項 1 0 のデバイス ( 1 ) において、前記第 2 のカソード層 ( layers ) ( 4 5 ) は、第 2 のアノード層 ( 5 5 ) に正射影な領域内に配置され、前記領域は多くても前記 I G C

Tセル(91)に直接的に隣接する前記第1のカソード層(4)のその半分部の正射影領域に制限され、前記領域は前記第2のカソード層(45)に向かって配置されることを特徴とする。

【請求項12】

請求項1ないし11のいずれかのデバイス(1)において、前記第2のカソード層(45)は、前記第2導電型のアノード短絡領域(regions)(51)と交互する、前記第1導電型の分散されたカソード領域(451)を具備することを特徴とする。

【請求項13】

請求項1ないし12のいずれかのデバイス(1)において、ライフタイムキリング(lifetime killing)層は、前記ダイオードセル(96)内に配置されるか、または、ウェハ全体(the whole wafer)(10)上の少なくとも一つの面内の連続した層として配置されることを特徴とする。 10

【請求項14】

請求項1ないし13のいずれかのデバイス(1)において、前記ウェハ(10)は円の形状を有し、そして、前記第1のカソード層(4)および前記第2のアノード層(55)は円の中心に対して放射状にストライプ状に配置されることを特徴とする。

【請求項15】

請求項14のデバイス(1)において、前記デバイス(1)は少なくとも一つのパイロットIGCT部(9)を具備し、それは複数の第1のカソード層(4)、ベース層(6)およびゲート電極(7)からなり、それらは第2のアノード層(4)を間に持つことなく、互いに隣接して直接的に配置され、そして、前記円の少なくとも一つのセグメントはパイロットIGCT部(9)であることを特徴とする。 20

【発明の詳細な説明】

【技術分野】

【0001】

本発明はパワー半導体デバイスの分野に関する。それは請求項1による逆導通パワー半導体デバイスに関する。

【背景技術】

【0002】

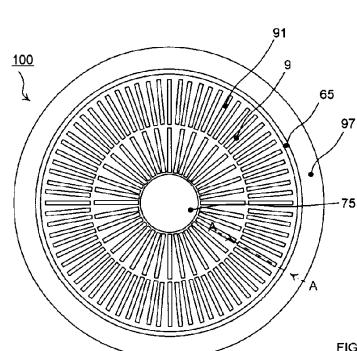

図1には、従来技術の逆導電半導体デバイス(RC-IGCT)100が示されており、それは、IGCTセル(cells)がある集積化ゲート転流型サイリスタ(IGCT)部分9および単一ビルトインフリーホイーリングダイード97をウェハ10内に具備する。 30

【0003】

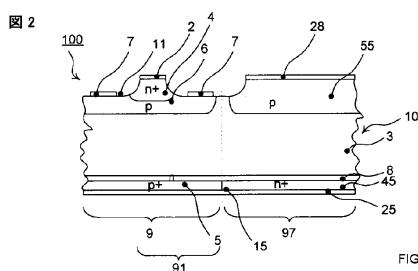

このような逆導電半導体デバイス100は、集積化IGCTのカソード面(cathode side)である第1の主面(main side)11と、複数のIGCTセル91のコレクタ面(collector side)であり、そして、エミッタ面(emitter side)11の反対側にある第2の主面15との間に、異なる導電型の複数の層があるウェハ10を具備する。前記デバイスは複数のIGCTセル91を具備しており、その各々は第1の主面11から第2の主面15までに以下の層がある：カソードメタライザーション層の形でのカソード電極2、第1の(n+)ドープされたカソード層4、(p)ドープされたベース層6、(n-)ドープされたドリフト層3、(n)ドープされたバッファー層8、(p+)ドープされた第1のアノード層5およびアノードメタライザーション層の形でのアノード電極25。 40

【0004】

複数のIGCTセル91は、ゲート電極7を備えており、それによってそれらは制御される。それはゲートメタライザーション層として第1の主面11上に配置される。ゲート電極7はカソード電極2および第1のカソード層4の横に(lateral)配置されるが、カソード電極2および第1のカソード層4からは分離されており、そして、pドープされたベース層6にコンタクトする。層(layers)に対して“横(lateral)”とは、第1の主面11に平行な面の観点から二つの層が互いに横に配置されることを意味する。

【0005】

図1に示されるように、複数の逆導電半導体デバイス100に対して単一フリーホイーリングダイード97が同じウェハ10上に集積化される。この単一フリーホイーリングダイード97はIGCT部分9の横に配置され、そして、第1の主面11上には第2の(p)ドープされたアノード層55、および、第2のアノード層55の領域への正射影内には(in orthogonal projection)第2の主面上15上の第2の(n+)ドープされたカソード層45を具備する。

#### 【0006】

代表的には、円形のウェハ10上には複数のIGCTセル91が複数のストライプとして放射状に配置される。複数のストライプは、一般には互いに平行に配置された二つの長辺を有することによって、一方向に他方向よりも長い伸長(extension)を有する、複数の層として理解されるべきである。放射状に配置された複数のIGCTセル91間には複数のゲート電極7が配置されている。ダイオードは、常に、円形のウェハの中心部内または前記ウェハの円周上のいずれかに單一ダイードとして配置される。もし単一ダイオード97が前記中心部内に配置されるなら、IGCT部分9は前記円周上に配置され、單一ダイオード97およびIGCT部分9は、複数のゲート電極7が電気的にコンタクトするゲートコンタクト75によって分離されることになる。前記ウェハの円周に配置されている單一ダイオード97に対しては、IGCT部分9は前記中央部内に配置され、そして、ゲートコンタクト75によって單一ダイオード97からは分離されるか、または、IGCT部分9はダイオード97に隣接して配置され、そして、ゲートコンタクト75は前記中央部内に配置される。

10

20

#### 【0007】

いずれの場合でも、單一ダイオード97はIGCT部分9から完全に分離され、お互いの間には相互作用(interaction)はない。それは、もしデバイスの動作期間中に熱が引き起こされると、もし前記デバイスがダイオードモードで動くならは單一ダイオード97内、または、もし前記デバイスがIGCTモードで動くなら單一ダイオード97内のどちらで、熱は発生されることを意味する。これは過熱問題につながるかもしれない。加えて、單一ダイオード97およびIGCT部分9は厳密にダイオードまたはIGCTモードに専念されているので、これは大きなデバイスをもたらす。

#### 【0008】

EP 0 676 812 AはMOS制御サイリスタ(MCT)を記載している。そのようなデバイスは、GCTよりもはるかに低いスイッチング周波数で作動させることができ、そしてまたスイッチドパワーははるかに低い。そのようなMCTは絶縁されたゲートおよび一つの共通の連続したp層を有し、それはダイオードセル(cells)に対してのアノード層の他にMCTセル内のベース層としても機能する。(パイロットMCTセルを形成する)複数のサイリスタセルは別のそのような複数のサイリスタセルから分離され、それらは各セットを囲む。ダイオードセル(cells)は、キャリアがダイオードセル(cell)を通過する(flow through)ことができないほど非常に広い。もし一組のサイリスタセル(cells)が欠陥によって動作不可能なら、これらのセルは始動されないので、デバイスはまだ動作することができる。

30

40

#### 【0009】

しかしながら、MCTは電圧パルス(MOSチャネル制御)でターンオフされ、するとGCTに対してのように電流パルスではない。また、電流はターンオフの間にGCT内のゲートから引き抜かれるのに対して、MCTは、MOS通路を提供することによって電流が主カソード内を通じて減少するとともに、ターンオフせざるを得ない。それ故、MCTに対してはダイオード領域を提供することは容易であり、というのはその導入はゲート制御によって影響を受けないからである。最終的に、かようなMCTデバイスは異なる技術的な要件に直面し、そして、GCTデバイスとは異なる用途に使用されることになる。

#### 【発明の概要】

#### 【0010】

本発明の目的は、熱的および電気的特性に関して改善された特性を有し、そして、小型

50

化された逆導通パワー半導体デバイスを提供することにある。

【0011】

問題は、請求項1の特徴を有する逆導通パワー半導体デバイスによって解決される。発明の逆導通パワー半導体デバイスは、第1の正面および前記第1の正面に平行に配置された第2の正面を有するウェハを具備する。前記デバイスは、複数のダイオードセルおよび複数のIGCTセル(integrated gate commutated thyristor cells)を具備し、ここにおいて、各IGCTセルは、前記第1の正面と前記第2の正面との間に以下の順で複数の層を具備する。

【0012】

- カソード電極、

- 第1導電型の第1のカソード層、

- 第2導電型のベース層、

- 前記第1導電型のドリフト層、

- 前記第1導電型のバッファ層、

- 前記第2導電型の第1のアノード層、および

- 第1のアノード電極。

10

【0013】

各IGCTセルはさらにゲート電極を具備し、それは前記第1のカソード層の横に配置され、そして、前記ベース層によってそれから分離されている。そのようなGCTセルは専門家にはよく知られている。それらは構造においてGCTセル(cells)と似ており、それらはそれからさらに発展しているが、ゲート制御およびオン・オフ切り替え(switching on and off)においてそれらとは異なっている。IGCTセルの位置決め(positioning)については、第1のカソード層4(およびゲート電極7およびベース層6)の位置決め、つまり、IGCTセルの第1の正面側の層(layers)の位置決めであると理解されるべきである。

20

【0014】

各ダイオードセルは、前記ドリフト層によって前記ベース層から分離された、前記第2導電型の第2のアノード層にコンタクトする、前記第1の正面の第2のアノード電極、および、前記第1のアノード層と交互に配置された、前記第2の正面の前記第1導電型の第2のカソード層を具備する。本特許出願においてダイオードセルの位置決めについては、前記第2のカソード層の位置決め、つまり、前記ダイオードセルの前記第1の正面側の層(layers)の位置決めであると理解されるべきである。

30

【0015】

前記デバイスは、少なくとも一つの混合部(mixed part)を具備しており、その中でダイオードセル(cells)(つまり、前記ダイオードセル(cells)の前記第2のアノード層(layers))は、IGCTセル(cells)(つまり、前記IGCTセル(cells)の前記第1のカソード層(layers)(およびゲート電極7およびベース層6))と交互している。

【0016】

前記IGCTセルおよび前記ダイオードセルの交互配置に起因して、前記ダイオードセルの前記第2のアノード層と前記IGCTセルの前記第1のアノード層との間に、バイポーラ接合トランジスタ(BJT)が形成される。IGCTターンオフモードにおいて、安全動作領域(SOA)特性はこの集積化されたBJTによって改善される。そのうえ、ターンオフ期間のゲート電力はBJTに起因して低減され、それはある一定の量のターンオフ電流をBJTのカソード端子、つまり、前記アノード電極を通じて運ぶ。

40

【0017】

前記IGCTの前記第1のアノード層は、前記ダイオードセルの前記第2のカソード層によってショートされる。これらのショートによって、前記デバイスは、スナップ逆回復(snappy reverse recovery)を被っている従来技術のデバイスよりもソフトな特性を示す。

【0018】

50

発明の逆導通パワー半導体デバイスはより良い熱耐性を有し、というのは分散されたダイオードおよびIGCTセルに起因して熱はより広い領域上に分散されるからである。IGCTモードで働いているデバイスの場合、典型的には、分散されたセル(cells)に起因して、熱は容易にダイオードセル(cells)中にも広がり、そして、したがって、前記デバイス内の温度は、單一ダイオードが一つの連続した領域に集中されて熱がはるかに小さい効率でダイオード領域中に広がる従来技術のデバイスよりも低い。

【0019】

IGCTモードの動作における(典型的にはシリコンで作られる)ウェハ領域の一部または全部の利用およびダイオードモードの動作におけるウェハ領域の十分な利用を可能とするためのダイオードおよびIGCT構造の少なくとも一部または全部の集積化に起因して、電流処理能力もまた従来技術のデバイスよりも良くなる。上記の効果は、前記IGCTおよびダイオードセルの近接(close proximity)、つまり、IGCTのための導通の期間中の荷電プラズマ(charge plasma)が隣接したダイオードセル(cells)を横方向にまたは貫いて広がるのを可能とするであろうIGCTおよびダイオードセルの交互配列に起因して、達する。ダイオードセル(cells)のサイズに依存して、ホール(holes)はダイオードセル(cells)に入り(ホールは前記第2のカソード層中に流れる)、そして、それどころか、それらを通り抜けるかも知れない。

【0020】

本発明によるさらなる利点は従属クレームから明らかであろう。

【0021】

本発明の主題は、添付された図面を参照して以下の本文にてより詳細に説明される。

【図面の簡単な説明】

【0022】

【図1】図1は、従来技術によるRC-IGCTについての平面図を示す。

【図2】図2は、従来技術によるRC-IGCTの切断(cut through)を示す。

【図3】図3は、発明のRC-IGCTの切断を示す。

【図4】図4は、別の発明のRC-IGCTの切断を示す。

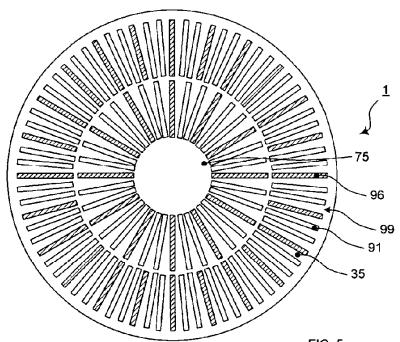

【図5】図5は、発明のRC-IGCTについての平面図を示す。

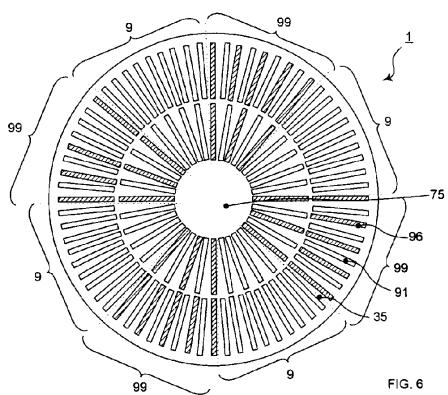

【図6】図6は、他の発明のRC-IGCTについての平面図を示す。

【発明を実施するための形態】

【0023】

複数の図に用いられた複数の参照記号およびそれらの意味は参照記号のリストに要約されている。一般に、同様または同様に機能する部分には同じ参照記号が与えられている。説明される実施形態は例として示され、本発明を制限するものではない。

【0024】

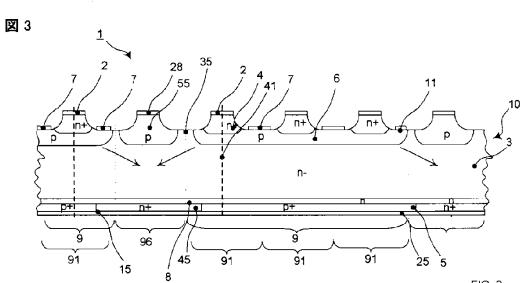

図3は、第1の主面11および第1の主面11に平行に配置された第2の主面15を有するウェハ10を伴う逆導通パワー半導体デバイス1の形態での発明の半導体デバイスを示す。前記デバイスは、複数のダイオードセル96および複数のIGCTセル91を具備し、ここにおいて、各IGCTセル91は、第1の主面11と第2の主面15との間に以下の順で複数の層を具備している。

【0025】

- カソード電極2、

- n+ドープト第1のカソード層4、

- pドープトベース層6、

- (n-)ドープトドリフト層3、

- nドープトバッファ層8、

- p+ドープト第1の別のアノード層5、および

- 第1のアノード電極25。

【0026】

各IGCTセル91はさらにゲート電極7を具備し、それは第1のカソード層4の横に

10

20

30

40

50

配置され、そして、ベース層 6 によってそれから分離されている。例示的な実施形態において、バッファ層 8 は最大で  $10^{16} \text{ c m}^{-3}$  の最大ドーピング濃度を有する。IGCTセルの第1の正面側の複数の層（つまり、第1のカソード層4、ゲート電極7を伴うベース層6）は、前記IGCTセルの第2の正面側の複数の層（つまり、第1のアノード層5）に位置合わせされ（aligned）ても構わない。非位置合わせ（non-alignment）の場合、第1の正面側の層に最も近くに配置された第1のアノード層5は同じセルに属するべきである。したがって、非位置合わせの場合、前記デバイスは、一つよりも多くの第2の並んだ層（sided layer）が一つのセルに割り当てられる、または、一つの第2の並んだ層（sided layer）が二つのセルに割り当てられるように設計されても構わない。各ダイオードセル96は、第2のアノード電極28、ドリフト層3によってベース層6から分離された、第1の正面11上のpドープト第2のアノード層55、および、第1のアノード層5と交互に配置された、第2の正面15上の（n+）ドープト第2のカソード層45を具備する。第2のアノード層55は、第2のアノード電極28にコンタクトする。IGCTセルの第1のアノード電極25は、ダイオードセル96に対してのカソード電極として機能する。ダイオードセルの第1の正面側の複数の層（つまり、第2のアノード層55）は、前記ダイオードセルの第2の正面側の複数の層（つまり、第2のカソード層45）に位置合わせされても構わない。

#### 【0027】

非位置合わせ（non-alignment）の場合、第1の正面側の層に最も近くに配置される第2のカソード層45は同じセルに属するべきである。したがって、非位置合わせの場合、前記デバイスは、一つよりも多くの第2の並んだ層（sided layer）が一つのセルに割り当てられる、または、一つの第2の並んだ層（sided layer）が二つのセルに割り当てられるように設計されても構わない。

#### 【0028】

ダイオードセル96は、ダイオードとIGCTセル96, 91との間に配置され且つ第1の正面11にまで延びるドリフト層3の部分によって形成された、分離領域35によって、IGCTセル91から分離されている。分離領域35はまた逆バイアス条件下での改善されたフィールド広がりのための標準エッジ終端技術を採用することができる。

#### 【0029】

ライフタイムキリング（lifetime killing）層は少なくともダイオードセル96内に配置されても構わない。これは、作成の期間中にマスクを用いること、または、ダイオードセル96上に横方向に制限されたイオンビームを適用することによって、ダイオードセル96へのライフタイムキリング層を制限することにより行うことができる。別の例示的な実施形態では、ライフタイムキリング層は、前記正面（sides）に平行に配置されている一つの面内において、ウェハの全領域上に一つの連続した層として形成されても構わない。ライフタイムキリング層が、ダイオードセルに制限されているか、または、連続層として作られているかとは独立的に、前記デバイスはライフタイムキリング層の作成のために典型的にはフォトンまたはヘリウムイオンで照射され、その後、アニールステップが続く。

#### 【0030】

“深さ”は、前記面（side）から層が延び、前記層が配置される最大距離を意味し、例えば、Pベース層6に対しては、それは、第1の正面11からの最大距離であり、そして、前記第1の正面11への正射影である。第1の正面11は、ゲート電極7がウェハ10から突出する面内に配置される。

#### 【0031】

前記デバイスは、少なくとも一つの混合部（mixed part）99を具備しており、その中ではダイオードセル（cells）96はIGCTセル（cells）91と交互している。例示的な実施形態では、ダイオードセル96は、一つのダイオードが二つの隣り合うIGCTセル91内に配置されるように、配置される。それは、各ダイオードセル96が、一つの第2のアノード層55が、二つの隣り合うIGCTセル91間に、つまり、これらのIGCTセル91に属している第1のカソード層（4）間および/またはそれらのゲート電極7

10

20

30

40

50

間に配置されるように、配置されることを意味する。

【0032】

別の例示的な実施形態では、IGCTセル9\_1に対するダイオードセル9\_6の比が1:1から1:5までの間で変わるように、複数のIGCTセルが直接的に互いに隣り合って配置されていても構わない。ダイオードセルの数は第2のアノード層の数として定義され、そして、IGCTセルに対しては第1のカソード層の数として定義される。また、混合部に対してはダイオードセルは第2のアノード層および第1のカソード層の配置としてのIGCTの配置として解釈されるべきである。

【0033】

この特許出願では、ダイオードセル9\_6の位置決め(positioning)に関しては第2のカソード層5\_5の位置決め、つまり、ダイオードセルの第1の正面側の層(layers)の位置決めとして理解されるべきである。IGCTセルの位置決めに関しては第1のカソード層4(およびゲート電極7およびベース層6)の位置決め、つまり、IGCTセルの第1の正面側の層(layers)の位置決めとして理解されるべきである。

10

【0034】

すべての実施形態において、第2の正面1\_5上の層(layers)、つまり、第1のアノード層5および第2のカソード層4\_5は、ダイオードセル9\_6に対しては第2のカソード層4\_5が第2のアノード層5\_5に対して正射影/反対側に配置されるように、第1の正面上の層(layers)に位置合わせされても構わない。IGCTセル9\_1に対しては第1のカソード層およびゲート電極7は第1のアノード層5に対して正射影/反対側に配置される。代替的には、前記第1の正面側の層と前記第2の正面側の層との間に位置合わせがない。

20

【0035】

この実施形態では、少なくともダイオードセル9\_1があるのと同数のIGCTセルがある。その比は、例えば、良いIGCT特性を達成するためには、少なくとも1:3とすることができる。そのような比が伴っていても、ダイオードモード内で良い特性を保証するために十分なダイオードセル9\_6がまだある。別の例示的な実施形態では、第1の正面上の前記構造は第2の正面の前記構造と位置合わせされている。それは、ダイオードセル内では第2のアノード層が第2カソード層に対して正射影/反対側に配置されることを意味する。IGCTセル内では、第1のカソード層およびゲート電極は第1のアノード層に対して正射影/反対側に配置される。

30

【0036】

ダイオードセル9\_6は、IGCTモードでのデバイスの動作の期間中にダイオードセル9\_6内にプラズマが形成されるような小さいサイズを有していても構わない。この効果は、ダイオードセル(cells)9\_6の少なくとも一つまたはすべてが第1の正面1\_1に平行な面内において50から500μmまでの最大ラテラルエクステンション(lateral extension)を有することによって達成され得る。前記効果を達成するために、IGCTセル(cells)9\_1の少なくとも一つまたはすべてまた第1の正面1\_1に平行な面内において50から500μmまでの最大ラテラルエクステンションを有する。別の例示的な実施形態では、IGCTおよびダイオードセルの少なくとも一つまたはすべては第1の正面1\_1に平行な面内において50から500μmまでの最大ラテラルエクステンションを有する。セルのラテラルエクステンションは、二つの隣り合うセル間の距離、つまり、直接的に隣り合うIGCTセルの第1の正面側の層(layers)の一つと第2のアノード層5\_5との間、または、二つの直接的に隣り合うIGCTセルの第1の正面側の層(layers)間の距離として理解することができる。

40

【0037】

別の例示的な実施形態では、第2のカソード層(layers)4\_5は、第2のアノード層5\_5に対して正射影に領域内に配置され、それは最大で直接的に隣接したIGCTセルの第1のカソード層4の正射影領域に限定される。

【0038】

第1のカソード層4は、一つの第1の半分部(half part)を具備しており、それは第

50

2の半分部よりも第2のカソード層45に近くに配置される。第2のカソード層45が配置される前記領域は、さらに、ダイオードセル領域およびIGCTセル91に直接的に隣接する第1のカソード層4の前記第1の半分部の正射影領域によって、制限され得る。それは、第2のカソード層(layers)45は第2のアノード層55に正射影な領域内に配置され、それは多くてもIGCTセル91に直接的に隣接する第1のカソード層4のその半分部の正射影領域に制限され、それは前記第2のカソード層45に向かって配置されること、を意味する。

【0039】

ベース層(複数)6および第2のアノード層55(複数)のドーピング濃度および深さは同じまたは互いに独立に選ぶことができる。例えば、第2のアノード層(複数)55のドーピング濃度および/または深さは、ベース層(複数)6のそれよりも小さく選択することができる。その場合、第2のアノード層55内には低い注入効率があり、そして、したがって、深い第2のアノード層55を伴うデバイスよりも小さいライフタイム制御が必要とされる。

【0040】

第1の主面11に平行な面内における第2のカソード層45の全面積(total area)は代表的には全ウェハ面積(total wafer area)の10ないし30%に選ぶことができる。

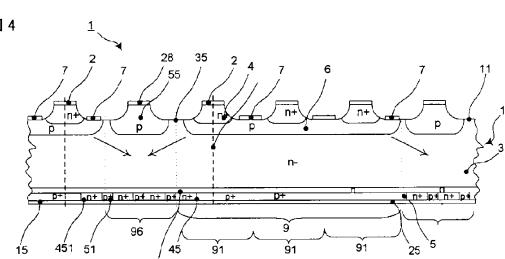

【0041】

図4に示されるように、第2のカソード層45は、第2導電型のアノード短絡領域(regions)51と交互する分散されたカソード領域451から形成されていても構わない。アノード短絡領域(regions)51は、前記第1の主面11上の前記デバイスの構造に対して、つまり、第2のカソード層45の他に第1のカソード層5に対して位置合わせされる必要なく、そして、アノード短絡領域(regions)51は、第2のアノード層55または第1のカソード層4に対してそれぞれ正射影に配置される必要はない。

【0042】

IGCT-ダイオードモード間の高速な切り替えを可能するために、ダイオードセル96(つまり、第2のアノード層55)は混合部99内のウェハ上に均一に分散されている構わない。

【0043】

ウェハ10上にパイロットIGCT部9を持つことも有利であり得り、それはIGCTセル(cells)91のみ(代表的には6以上、代表的には少なくとも10)からなり、それらは互いに直接的に隣接して配置され、そして、パイロットIGCT部9内ではダイオードセルを持たない。そのようなパイロットIGCT部9は、第1のカソード層4の第1の主面11および(共通で、連続したベース層6と一緒に)複数のゲート電極7上に成り、それらは第2のアノード層4を間に持つことなく、互いに隣接して直接的に配置されている。

【0044】

そのようなパイロットIGCT部は、単一IGCT部9とすることもでき、または、複数つまり2以上のそのようなパイロットIGCT部はデバイス内に配置されても構わない。IGCT部9の全面積(total area)は全ウェハ面積(total wafer area)の10ないし50%とすることができる。このようなIGCT部9があることで、デバイスのターンオフ特性を改善することができる。

【0045】

さらに別の実施形態では、ウェハ10は円の形状を有し、そして、第1のカソード層4および第2のアノード層55は円の中心に対して放射状にストライプ状に配置される。ダイオードセル96は、図5に示されるように円の中心の周りに規則正しく配置されても構わない。別の代替的では、セグメントと交互する円のセグメント内に配置された複数のIGCT部9があり、その中ではIGCTセル(cells)95はダイオードセル(cells)96と交互し、したがって、ダイオードセル(cells)96を伴うIGCTセル(cells)91が混合された領域99を形成する。それは、複数の第1のカソード層4、ベース層6およ

10

20

30

40

50

びゲート電極 7 が、第 2 のアノード層 4 を間に持つことなく、互いに隣接して直接的に配置されていることを意味する。

【 0 0 4 6 】

別の実施形態では、導電型は取り換えられ、つまり、第 1 導電型の全ての層は p 型（例えば、ドリフト層 3 ）および第 2 導電型の全ての層は n 型（例えば、ベース層 6 ）である。

【 0 0 4 7 】

用語“具備すること（comprising）”は他の要素またはステップを除外はせず、そして、不定冠詞“a”または“an”は複数を除外しないことに留意すべきである。また、異なる実施形態に関連して説明された要素を組み合わせてもよい。特許請求の範囲中の参照符号は、特許請求の範囲を限定するものとして解釈されるべきではないことにも留意すべきである。

【 0 0 4 8 】

これらの例は本発明の範囲を限定するものではない。上述の設計および配置は、単に、ベース層（s）およびウェル（ゾーン（zones））に対しての任意の種類の可能な設計および配置の例である。

【 0 0 4 9 】

本発明は、その精神または主要な特徴から逸脱することなく、他の特定の形態で実施できることは、当業者には理解されるであろう。開示された実施形態は、したがって、すべての点において例示的であると考慮され、そして、制限されない。本発明の範囲は、前述の説明よりむしろ添付の特許請求の範囲によって示され、その意味および範囲および均等物内に入る全ての変更はその中に含まれると意図されている。

以下に、本願出願当初の特許請求の範囲に記載された発明を付記する。

【 C 1 】

第 1 の正面（11）および前記第 1 の正面（11）に平行に配置された第 2 の正面（15）を有するウェハ（10）を伴う逆導通パワー半導体デバイス（1）であって、前記デバイスは、複数のダイオードセル（96）および複数の I G C T セル（91）を具備すること、ここにおいて、各 I G C T セル（91）は、前記第 1 および第 2 の正面（11, 15）の間に以下の順で複数の層を具備する：

- カソード電極（2）、

- 第 1 導電型の第 1 のカソード層（4）、

- 第 2 導電型のベース層（6）、

- 前記第 1 導電型のドリフト層（3）、

- 前記第 1 導電型のバッファ層（8）、

- 前記第 2 導電型の第 1 のアノード層（5）、

- 第 1 のアノード電極（25）。

ここにおいて、各 I G C T セル（91）は、前記第 1 のカソード層（4）の横に配置され、そして、それとは前記ベース層（6）によって分離されているゲート電極をさらに具備し、

ここにおいて、各ダイオードセル（96）は、前記第 1 の正面（11）上の第 2 のアノード電極（28）、前記ドリフト層（3）によって前記ベース層（6）から分離された前記第 2 導電型の第 2 のアノード層（55）、および、前記第 2 の正面（15）上で前記第 1 のアノード層（5）と交互に配置された前記第 1 導電型の第 2 のカソード層（45）を具備し、および、

ここにおいて、前記デバイスは、少なくとも一つの混合部（99）を具備しており、その中では前記ダイオードセル（96）の前記第 2 のアノード層（55）は前記 I G C T セル（91）の前記第 1 のカソード層（4）と交互する。

【 C 2 】

【 C 1 】のデバイス（1）において、前記混合部（99）内で、各ダイオードセル（96）は、一つの第 2 のアノード層（55）が二つの第 1 のカソード層（4）および／または

10

20

30

40

50

ゲート電極(7)の間に配置されるように、配置されることを特徴とする。

[C 3]

[C 1]のデバイス(1)において、G C Tセル(cells)96に対するダイオードセル(cells)96の比は1.1ないし1.5であり、ここにおいて、前記ダイオードセルの数は前記第2のアノード層(55)の数として定義され、そして、前記I G C Tセルに対しては前記第1のカソード層(4)の数として定義されることを特徴する。

[C 4]

[C 1]または[C 2]のいずれかのデバイス(1)において、前記デバイス(1)は、第2のアノード層(4)を間に持つことなく、互いに隣接して直接的に配置された複数の第1のカソード層(4)およびゲート電極(7)からなる、少なくとも一つのパイロットI G C T部(9)を具備することを特徴とする。

10

[C 5]

[C 3]のデバイス(1)において、前記少なくとも一つのI G C T部(9)は、前記ウェハ面積(total wafer area)の10ないし50%の全面積(total area)を有することを特徴する。

[C 6]

[C 1]または[C 2]のいずれかのデバイス(1)において、前記第2のアノード層(55)は、前記混合部(99)内の前記ウェハ上に均一に分散されていることを特徴する。

20

[C 7]

[C 1]ないし[C 6]のいずれかのデバイス(1)において、前記I G C Tセル(cells)91の前記第1の正面側の部分に対する前記ダイオードセル(cells)96の少なくとも一つまたはすべて、または、前記I G C Tセル(cells)91の二つの隣り合う第1の正面側の部分は、前記第1の正面(11)に平行な面内において50から500μmまでの最大ラテラルエクステンション(lateral extension)を互いに有することを特徴する。

[C 8]

[C 1]ないし[C 7]のいずれかのデバイス(1)において、前記ベース層(6)および前記第2のアノード層(55)のドーピング濃度および深さの少なくとも一つは異なっており、特に前記第2のアノード層(55)のドーピング濃度および深さの少なくとも一つは、前記ベース層(6)のそれよりも低いことを特徴する。

30

[C 9]

[C 1]ないし[C 8]のいずれかのデバイス(1)において、前記第1の正面(11)に平行な面内における前記第2のカソード層(45)の全面積(total area)は前記ウェハ面積(total wafer area)の10ないし30%であることを特徴する。

[C 10]

[C 1]ないし[C 9]のいずれかのデバイス(1)において、前記第2のカソード層(layers)(45)は、多くてもI G C Tセル(91)に直接的に隣接する第1のカソード層(4)の正射影領域に制限される領域内において、前記第2のアノード層(55)に正射影に配置されることを特徴とする。

40

[C 11]

[C 10]のデバイス(1)において、前記第2のカソード層(layers)(45)は、第2のアノード層(55)に正射影な領域内に配置され、前記領域は多くても前記I G C Tセル(91)に直接的に隣接する前記第1のカソード層(4)のその半分部の正射影領域に制限され、前記領域は前記第2のカソード層(45)に向かって配置されることを特徴とする。

[C 12]

[C 1]ないし[C 11]のいずれかのデバイス(1)において、前記第2のカソード層(45)は、前記第2導電型のアノード短絡領域(regions)(51)と交互する、前記第1導電型の分散されたカソード領域(451)を具備することを特徴とする。

50

## [ C 1 3 ]

[ C 1 ] ないし [ C 1 2 ] のいずれかのデバイス ( 1 ) において、ライフタイムキリング ( lifetime killing )層は、前記ダイオードセル ( 9 6 ) 内に配置されるか、または、ウェハ全体 ( the whole wafer ) ( 1 0 ) 上の少なくとも一つの面内の連続した層として配置されることを特徴とする。

## [ C 1 4 ]

[ C 1 ] ないし [ C 1 3 ] のいずれかのデバイス ( 1 ) において、前記ウェハ ( 1 0 ) は円の形状を有し、そして、前記第1のカソード層 ( 4 ) および前記第2のアノード層 ( 5 5 ) は円の中心に対して放射状にストライプ状に配置されることを特徴とする。

## [ C 1 5 ]

[ C 1 4 ] のデバイス ( 1 ) において、前記デバイス ( 1 ) は少なくとも一つのパイロットIGCT部 ( 9 ) を具備し、それは複数の第1のカソード層 ( 4 ) 、ベース層 ( 6 ) およびゲート電極 ( 7 ) からなり、それらは第2のアノード層 ( 4 ) を間に持つことなく、互いに隣接して直接的に配置され、そして、前記円の少なくとも一つのセグメントはパイロットIGCT部 ( 9 ) であることを特徴とする。

10

## 【符号の説明】

## 【 0 0 5 0 】

1 ... 逆導通パワー半導体デバイス、 1 0 ... ウェハ、 1 1 ... 第1の主面、 1 5 ... 第2の主面、 1 0 0 ... 従来技術の逆導通パワー半導体デバイス、 2 ... カソード電極、 2 5 ... 第1のアノード電極、 2 8 ... 第2のアノード電極、 3 ... ドリフト層、 3 5 ... 分離領域、 4 ... 第1のカソード層、 4 1 ... 半分部、 4 5 ... 第2のカソード層、 4 5 1 ... 分散されたカソード領域、 5 ... 第1のアノード層、 5 1 ... アノード短絡領域、 5 5 ... 第2のアノード層、 6 ... ベース層、 7 ... ゲート電極、 7 5 ... ゲートコンタクト、 8 ... バッファ層、 9 ... パイロットIGCT部、 9 1 ... IGCTセル、 9 6 ... ダイオードセル、 9 7 ... 単一ダイオード、 9 9 ... 混合されたIGCT / ダイオード部。

20

## 【図1】

FIG. 1 従来技術

## 【図2】

FIG. 2 従来技術

## 【図3】

FIG. 3

## 【図4】

FIG. 4

【図5】

図5

FIG. 5

【図6】

図6

FIG. 6

---

フロントページの続き

(51)Int.Cl.

F I

H 0 1 L 21/322

K

(74)代理人 100075672

弁理士 峰 隆司

(74)代理人 100140176

弁理士 砂川 克

(72)発明者 ラヒモ、ムナフ

スイス国、5619 ウエツビル、バッハベーク 10

(72)発明者 アーノルド、マルティン

スイス国、5400 バーデン、ツルヒヤーシュトラーセ 4

(72)発明者 スティアスニー、トーマス

スイス国、8820 ベーデンスビル、ブックシュトラーセ 30

審査官 棚田 一也

(56)参考文献 国際公開第00/16406 (WO, A1)

特開2004-259810 (JP, A)

(58)調査した分野(Int.Cl., DB名)

H 0 1 L 29/68-74

H 0 1 L 21/33-331

H 0 1 L 29/861

H 0 1 L 29/868