(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4288849号

(P4288849)

(45) 発行日 平成21年7月1日(2009.7.1)

(24) 登録日 平成21年4月10日(2009.4.10)

|                       |                |

|-----------------------|----------------|

| (51) Int.Cl.          | F 1            |

| G09F 9/00 (2006.01)   | G09F 9/00 348C |

| G02F 1/133 (2006.01)  | G02F 1/133 550 |

| G02F 1/1345 (2006.01) | G02F 1/1345    |

| G09F 9/30 (2006.01)   | G09F 9/30 338  |

| G09G 3/20 (2006.01)   | G09G 3/20 621M |

請求項の数 11 (全 9 頁) 最終頁に続く

|           |                               |

|-----------|-------------------------------|

| (21) 出願番号 | 特願2000-371043 (P2000-371043)  |

| (22) 出願日  | 平成12年12月6日 (2000.12.6)        |

| (65) 公開番号 | 特開2002-175021 (P2002-175021A) |

| (43) 公開日  | 平成14年6月21日 (2002.6.21)        |

| 審査請求日     | 平成19年6月29日 (2007.6.29)        |

前置審査

|           |                                        |

|-----------|----------------------------------------|

| (73) 特許権者 | 000002185<br>ソニー株式会社<br>東京都港区港南1丁目7番1号 |

| (74) 代理人  | 100086298<br>弁理士 船橋 國則                 |

| (72) 発明者  | 仲島 義晴<br>東京都品川区北品川6丁目7番35号 ソニー株式会社内    |

| (72) 発明者  | 前川 敏一<br>東京都品川区北品川6丁目7番35号 ソニー株式会社内    |

| 審査官       | 中村 直行                                  |

最終頁に続く

(54) 【発明の名称】アクティブマトリクス型表示装置およびこれを用いた携帯端末

## (57) 【特許請求の範囲】

## 【請求項 1】

電気光学素子を有する画素がマトリクス状に配置されてなる表示エリア部と、複数の基準電圧を発生する基準電圧発生回路と、前記複数の基準電圧の中からデジタルデータに対応した基準電圧を選択する基準電圧選択型D A変換回路を有し、このD A変換回路で選択された基準電圧を画像信号として選択画素行の各画素に対して供給する水平駆動回路とを備え、

前記水平駆動回路は、前記表示エリア部に対してその上下に一対配置されており、前記基準電圧発生回路は、前記表示エリア部および前記水平駆動回路と共に同一基板上に作成されるとともに、前記表示エリア部の各画素を行単位で選択する垂直駆動回路と前記画素アレイ部を挟んで反対側の辺における前記一対の水平駆動回路から等距離の位置に1つ配置され、前記複数の基準電圧を前記一対の水平駆動回路に対してバッファ回路を介在させることなく直接供給する

アクティブマトリクス型表示装置。

## 【請求項 2】

前記基準電圧発生回路は、前記表示エリア部および前記水平駆動回路と共に同一プロセスを用いて作成されている

請求項1記載のアクティブマトリクス型表示装置。

## 【請求項 3】

前記表示エリア部の各画素において、前記電気光学素子を駆動する能動素子が薄膜トランジスタ

ンジスタからなり、

前記水平駆動回路および前記基準電圧発生回路が薄膜トランジスタを用いて構成される請求項1記載のアクティブマトリクス型表示装置。

【請求項4】

前記基準電圧発生回路は、前記基板上において前記水平駆動回路が配置されていない辺のいずれかに配置される

請求項1記載のアクティブマトリクス型表示装置。

【請求項5】

前記電気光学素子が液晶セルである

請求項1記載のアクティブマトリクス型表示装置。

10

【請求項6】

前記電気光学素子がエレクトロルミネッセンス素子である

請求項1記載のアクティブマトリクス型表示装置。

【請求項7】

電気光学素子を有する画素がマトリクス状に配置されてなる表示エリア部と、複数の基準電圧を発生する基準電圧発生回路と、

前記複数の基準電圧の中からデジタルデータに対応した基準電圧を選択する基準電圧選択型DA変換回路を有し、このDA変換回路で選択された基準電圧を画像信号として選択画素行の各画素に対して供給する水平駆動回路とを備え、

前記水平駆動回路は、前記表示エリア部に対してその上下に一対配置されており、

20

前記基準電圧発生回路は、前記表示エリア部および前記水平駆動回路と共に同一基板上に作成されるとともに、前記表示エリア部の各画素を行単位で選択する垂直駆動回路と前記画素アレイ部を挟んで反対側の辺における前記一対の水平駆動回路から等距離の位置に1つ配置され、前記複数の基準電圧を前記一対の水平駆動回路に対してバッファ回路を介在させることなく直接供給する

アクティブマトリクス型表示装置を表示部として用いた携帯端末。

【請求項8】

前記表示エリア部の各画素において、前記電気光学素子を駆動する能動素子が薄膜トランジスタからなり、

前記水平駆動回路および前記基準電圧発生回路が薄膜トランジスタを用いて構成される請求項7記載の携帯端末。

30

【請求項9】

前記基準電圧発生回路は、前記基板上において前記水平駆動回路が配置されていない辺のいずれかに配置される

請求項7記載の携帯端末。

【請求項10】

前記アクティブマトリクス型表示装置は、前記電気光学素子として液晶セルを用いた液晶表示装置である

ことを特徴とする請求項7記載の携帯端末。

【請求項11】

前記アクティブマトリクス型表示装置は、前記電気光学素子としてエレクトロルミネッセンス素子を用いたエレクトロルミネッセンス表示装置である

ことを特徴とする請求項7記載の携帯端末。

40

【発明の詳細な説明】

【0001】

【発明の属する技術分野】

本発明は、アクティブマトリクス型表示装置およびこれを用いた携帯端末に関し、特に基準電圧選択型のDA(デジタル-アナログ)変換回路を含む駆動系を搭載したアクティブマトリクス型表示装置およびこの表示装置を表示部として用いた携帯端末に関する。

【0002】

50

**【従来の技術】**

近年、携帯電話機やPDA(Personal Digital Assistants)などの携帯端末の普及がめざましい。これら携帯端末の急速な普及の要因の一つとして、その出力表示部として搭載されている液晶表示装置が挙げられる。その理由は、液晶表示装置が原理的に駆動するための電力を要しない特性を持ち、低消費電力の表示デバイスであるためである。

**【0003】**

この液晶表示装置などでは、デジタルインターフェース駆動回路を表示エリア部と同一基板上に一体的に形成する傾向にある。この駆動回路一体型液晶表示装置では、スイッチング素子としてポリシリコンTFT(Thin Film Transistor; 薄膜トランジスタ)を用いた画素がマトリクス状に多数配置されてなる表示エリア部に対して、その周辺部(額縁)に水平駆動系や垂直駆動系が配され、これら駆動系がTFTを用いて表示エリア部と共に同一基板上に一体的に形成された構成となっている。

10

**【0004】**

ところで、デジタルインターフェース駆動回路では、入力されるデジタルデータをアナログ信号に変換するためのDA変換回路が用いられる。このDA変換回路としては、例えば、複数の基準電圧の中からデジタル画像データに対応した基準電圧を選択してこれをアナログ画像信号として出力する基準電圧選択型のDA変換回路が知られている。この基準電圧選択型DA変換回路では、複数の基準電圧を発生する基準電圧発生回路が必要となる。この基準電圧発生回路は、従来、表示エリア部が形成される基板とは別基板である単結晶シリコン基板上に形成されていた。

20

**【0005】****【発明が解決しようとする課題】**

上述したように、液晶表示装置に代表される表示装置において、複数の基準電圧を発生する基準電圧発生回路を、表示エリア部が形成される基板とは別の基板上に形成したのではなく、セットを構成する部品点数が増えるとともに、それぞれ別々のプロセスで作成しなければならないため、セットの小型化、低コスト化の妨げになるという問題があった。

**【0006】**

本発明は、上記課題に鑑みてなされたものであり、その目的とするところは、セットの小型化、低コスト化が可能なアクティブマトリクス型表示装置およびこれを表示部として用いた携帯端末を提供することにある。

30

**【0007】****【課題を解決するための手段】**

上記目的を達成するために、本発明では、電気光学素子を有する画素がマトリクス状に配置されてなる表示エリア部と、複数の基準電圧を発生する基準電圧発生回路と、これら複数の基準電圧の中からデジタルデータに対応した基準電圧を選択する基準電圧選択型DA変換回路を有し、このDA変換回路で選択された基準電圧を画像信号として選択画素行の各画素に対して供給する水平駆動回路とを備えたアクティブマトリクス型表示装置において、水平駆動回路は、表示エリア部に対してその上下に一対配置されており、基準電圧発生回路は、表示エリア部および水平駆動回路と共に同一基板上に作成されるとともに、前記表示エリア部の各画素を行単位で選択する垂直駆動回路と前記画素アレイ部を挟んで反対側の辺における一対の水平駆動回路から等距離の位置に1つ配置され、複数の基準電圧を一対の水平駆動回路に対してバッファ回路を介在させることなく直接供給する構成を探っている。そして、このアクティブマトリクス型表示装置は、携帯端末の表示部として用いられる。

40

**【0008】**

上記構成のアクティブマトリクス型表示装置あるいはこれを用いた携帯端末において、基準電圧発生回路を表示エリア部および水平駆動回路と共に同一基板上に作成することでき、セットを構成する部品点数を少なく抑えることができる。したがって、セットの低コスト化、さらには薄型化、コンパクト化が可能になる。また、基準電圧発生回路が一対の水平駆動回路から等距離の位置に設けられることで、一対の水平駆動回路との間の配線長を

50

等しくできるため、複数の基準電圧を一对の水平駆動回路に対してバッファ回路を介在させることなく直接供給できる。これにより、基準電圧発生回路が別基板に配置された場合に必要となるバッファ回路を省略できる。

#### 【0009】

##### 【発明の実施の形態】

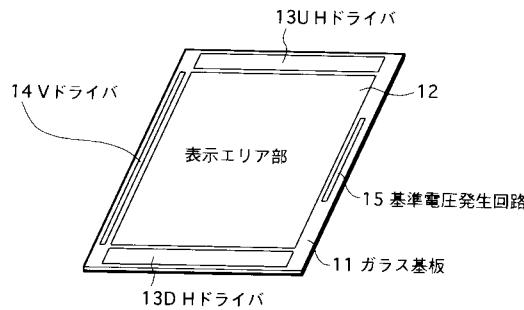

以下、本発明の実施の形態について図面を参照して詳細に説明する。図1は、本発明に係る表示装置の構成例を示す概略構成図である。ここでは、例えば、各画素の電気光学素子として液晶セルを用いたアクティブマトリクス型液晶表示装置に適用した場合を例に採って説明するものとする。

#### 【0010】

図1において、透明絶縁基板、例えばガラス基板11上には、液晶セルを含む画素がマトリクス状に多数配置されてなる表示エリア部12、上下一対のHドライバ(水平駆動回路)13U, 13DおよびVドライバ(垂直駆動回路)14とともに、複数の基準電圧を発生する基準電圧発生回路15が集積されている。ガラス基板11は、能動素子(例えば、トランジスタ)を含む多数の画素回路がマトリクス状に配置形成される第1の基板と、この第1の基板と所定の間隙をもって対向して配置される第2の基板とによって構成される。そして、これら第1, 第2の基板間に液晶が封入される。

#### 【0011】

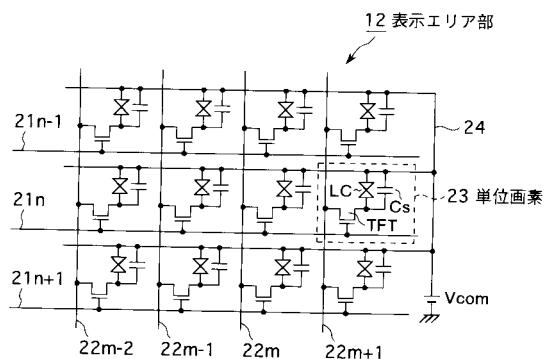

図2に、表示エリア部12の具体的な構成の一例を示す。ここでは、図面の簡略化のために、3行( $n - 1$ 行～ $n + 1$ 行)4列( $m - 2$ 列～ $m + 1$ 列)の画素配列の場合を例に採って示している。図2において、表示エリア部12には、垂直走査ライン…, 21n-1, 21n, 21n+1, …と、データライン…, 22m-2, 22m-1, 22m, 22m+1, …とがマトリクス状に配線され、それらの交点部分に単位画素23が配置されている。

#### 【0012】

単位画素23は、画素トランジスタである薄膜トランジスタTFT、液晶セルLCおよび保持容量Csを有する構成となっている。ここで、液晶セルLCは、薄膜トランジスタTFTで形成される画素電極(一方の電極)とこれに対向して形成される対向電極(他方の電極)との間で発生する容量を意味する。

#### 【0013】

薄膜トランジスタTFTは、ゲート電極が垂直走査ライン…, 21n-1, 21n, 21n+1, …に接続され、ソース電極がデータライン…, 22m-2, 22m-1, 22m, 22m+1, …に接続されている。液晶セルLCは、画素電極が薄膜トランジスタTFTのドレイン電極に接続され、対向電極が共通ライン24に接続されている。保持容量Csは、薄膜トランジスタTFTのドレイン電極と共通ライン24との間に接続されている。共通ライン24には、所定の直流電圧がコモン電圧Vcomとして与えられる。

#### 【0014】

垂直走査ライン…, 21n-1, 21n, 21n+1, …の各一端は、図1に示すVドライバ14の対応する行の各出力端にそれぞれ接続される。Vドライバ14は、例えばシフトレジスタによって構成され、垂直転送クロックVCK(図示せず)に同期して順次垂直選択パルスを発生して垂直走査ライン…, 21n-1, 21n, 21n+1, …に与えることによって垂直走査を行う。

#### 【0015】

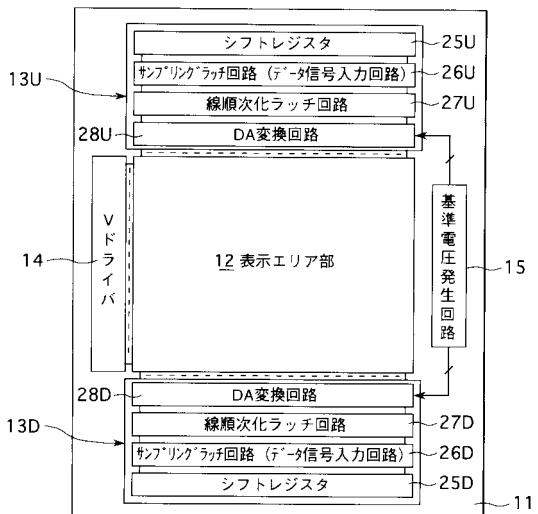

一方、表示エリア部12において、例えば、奇数番目のデータライン…, 22m-1, 22m+1, …の各一端が図1に示すHドライバ13Uの対応する列の各出力端に、偶数番目のデータライン…, 22m-2, 22m, …の各他端が図1に示すHドライバ13Dの対応する列の各出力端にそれぞれ接続される。Hドライバ13U, 13Dの具体的な構成の一例を図3に示す。

#### 【0016】

図3に示すように、Hドライバ13Uは、シフトレジスタ25U、サンプリングラッチ回

10

20

30

40

50

路（データ信号入力回路）26U、線順次化ラッチ回路27UおよびDA変換回路28Uを有する構成となっている。シフトレジスタ25Uは、水平転送クロックHCK（図示せず）に同期して各転送段から順次シフトパルスを出力することによって水平走査を行う。サンプリングラッチ回路26Uは、シフトレジスタ25Uから与えられるシフトパルスに応答して、入力される所定ビットのデジタル画像データを点順次にてサンプリングしてラッチする。

【0017】

線順次化ラッチ回路27Uは、サンプリングラッチ回路26Uで点順次にてラッチされたデジタル画像データを1ライン単位で再度ラッチすることによって線順次化し、この1ライン分のデジタル画像データを一斉に出力する。DA変換回路28Uは例えば基準電圧選択型の回路構成をとり、線順次化ラッチ回路27Uから出力される1ライン分のデジタル画像データをアナログ画像信号に変換して先述した画素エリア部12のデータライン…, 22m-2, 22m-1, 22m, 22m+1, …に与える。

10

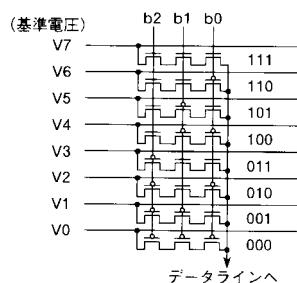

【0018】

図4に、基準電圧選択型DA変換回路28Uの単位回路の構成例を示す。ここでは、入力されるデジタルデータが例えれば3ビット(b2, b1, b0)の場合を例に採って示しており、この3ビットのデータに対して8(=2<sup>3</sup>)個の基準電圧V0～V7が用意されることになる。この単位回路が、画素エリア部12のデータライン…, 22m-2, 22m-1, 22m, 22m+1, …ごとに1個ずつ配置されることになる。

20

【0019】

下側のHドライバ13Dについても、上側のHドライバ13Uと全く同様に、シフトレジスタ25D、サンプリングラッチ回路26D、線順次化ラッチ回路27Dおよび基準電圧選択型のDA変換回路28Dを有する構成となっている。なお、本例に係るアクティブマトリクス型液晶表示装置では、表示エリア部12の上下にHドライバ13U, 13Dを配する構成を探ったが、これに限定されるものではなく、上下のいずれか一方のみに配する構成を探ることも可能である。

【0020】

図1および図3から明らかなように、基準電圧発生回路15についても、Hドライバ13U, 13DおよびVドライバ14と同様に、表示エリア部12と共に同一のガラス基板11上に集積される。ここで、例えれば表示エリア部12の上下にHドライバ13U, 13Dを配する構成を探る液晶表示装置の場合には、Hドライバ13U, 13Dが搭載されていない辺の額縁エリア（表示エリア部12の周辺エリア）に基準電圧発生回路15を搭載するのが好ましい。

30

【0021】

何故ならば、Hドライバ13U, 13Dは、上述した如くVドライバ14に比べて構成要素が多く、その回路面積が非常に大きくなる場合が多いことから、Hドライバ13U, 13Dが搭載されていない辺の額縁エリアに搭載することで、有効画面率（ガラス基板11に対する有効エリア部12の面積率）を低下させることなく、基準電圧発生回路15を表示エリア部12と同一のガラス基板11上に集積することができるからである。

【0022】

40

なお、本例に係るアクティブマトリクス型液晶表示装置においては、Hドライバ13U, 13Dが搭載されていない辺の額縁エリアの一方側にはVドライバ14が集積されていることから、その反対側の辺の額縁エリアに基準電圧発生回路15を集積する構成を探っている。

【0023】

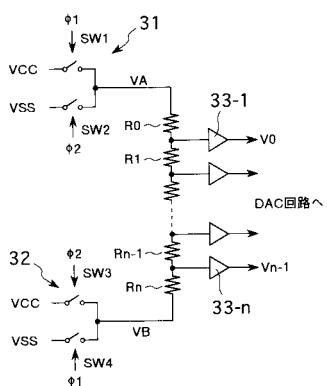

基準電圧発生回路の一般的な構成例を図5に示す。本構成例に係る基準電圧発生回路は、正電源電圧VCCと負電源電圧VSSとを一定の周期で互いに逆相でスイッチングする2つのスイッチ回路31, 32と、これらスイッチ回路31, 32の各出力端間に直列に接続されたn+1個の抵抗R0～Rnとからなり、これら抵抗R0～Rnによって電圧VCC-VSSを分圧することにより、各抵抗の共通接続点からn個の基準電圧V0～Vn-

50

1を導出し、バッファ回路33-1～33-nを介して出力する構成となっている。

【0024】

上記構成の基準電圧発生回路において、バッファ回路33-1～33-nは、インピーダンス変換の機能を持ち、従来のように、本基準電圧発生回路を別基板に形成し、ガラス基板11上のD A変換回路まで基準電圧を伝送する形態を採った場合に、基準電圧発生回路からD A変換回路までの配線長が長くなることによって配線インピーダンスが大きくなつたとしても、上下のHドライバ（図1のHドライバ13U, 13Dに相当）間で書き込み特性にばらつきが生じないようにする作用を為している。

【0025】

一方、本実施形態に係るアクティブマトリクス型液晶表示装置では、基準電圧発生回路15をHドライバ13U, 13Dと共に同一のガラス基板11上に集積した構成を採っていることで、基準電圧発生回路15とHドライバ13U, 13Dとの間の配線長を極めて短く設定できる。特に、図3から明らかなように、基準電圧発生回路15の集積に際して、基準電圧発生回路15を表示エリア部12の垂直方向のほぼ中間位置、即ち上下のHドライバ13U, 13Dからほぼ等距離の位置に配置することで、Hドライバ13U, 13Dとの間の配線長をほぼ等しく設定できる。

【0026】

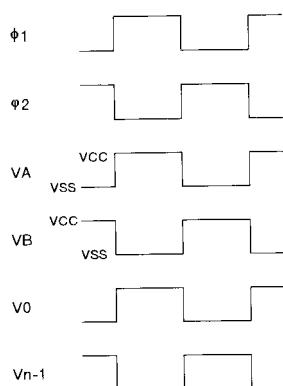

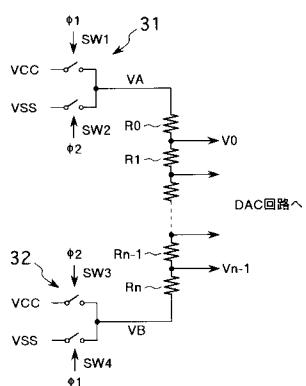

これにより、基準電圧発生回路15を構成するに当たって、図6の回路図に示すように、図5に示す一般的な回路例で用いられていたバッファ回路33-1～33-nが不要になる。すなわち、図6に示す構成例から明らかなように、抵抗R0～Rnの共通接続点から導出されるn個の基準電圧V0～Vn-1を上下のHドライバ13U, 13Dに対して直接供給できるようになる。その結果、バッファ回路33-1～33-nを省略できる分だけ基準電圧発生回路15の回路構成を簡略化できることになる。

【0027】

なお、図6中、図5と同等部分には同一符号を付して示している。また、図6において、スイッチ回路31, 32を構成するスイッチSW1～SW4は、例えばトランジスタによって構成される。図7に、制御パルス1, 2、上限、下限電圧VA, 電圧VBおよび基準電圧V0, Vn-1の波形を示す。

【0028】

スイッチ回路31, 32において、スイッチSW1とSW4が制御パルス1によってスイッチングされ、スイッチSW2とSW3が制御パルス1と逆相の制御パルス2によってスイッチングされる。このように、正電源電圧VCCと負電源電圧VSSとを一定の周期、例えば1H（Hは水平走査期間）周期で互いに逆相でスイッチングするのは、液晶の劣化防止を目的として、液晶を交流駆動するためである。

【0029】

また、基準電圧発生回路15の集積に際しては、表示エリア部12の各画素トランジスタとして薄膜トランジスタTFTを用いていることから、基準電圧発生回路15のスイッチ回路31, 32を構成するトランジスタとしても薄膜トランジスタを用い、少なくともこれらトランジスタ回路を表示エリア部12と共に同一ガラス基板11上に作成することにより、その製造が容易になるとともに、低コストにて実現できる。

【0030】

薄膜トランジスタについては、近年の性能向上や消費電力の低下に伴って集積化が容易になっているのが現状である。したがって、基準電圧発生回路15、特に少なくともトランジスタ回路を表示エリア部12の画素トランジスタと同じ薄膜トランジスタを用いて同一のガラス基板11上に同一プロセスにて一体的に形成することにより、製造プロセスの簡略化に伴う低コスト化、さらには集積化に伴う薄型化、コンパクト化を図ることができる。

【0031】

なお、上記実施形態では、アクティブマトリクス型液晶表示装置に適用した場合を例に採って説明したが、これに限定されるものではなく、エレクトロルミネッセンス（EL）素

10

20

30

40

50

子を各画素の電気光学素子として用いた E L 表示装置などの他のアクティブマトリクス型表示装置にも同様に適用可能である。

【 0 0 3 2 】

また、上記実施形態に係るアクティブマトリクス型液晶表示装置に代表されるアクティブマトリクス型表示装置は、パーソナルコンピュータ、ワードプロセッサ等の O A 機器やテレビジョン受像機などのディスプレイとして用いられる外、特に装置本体の小型化、コンパクト化が進められている携帯電話機や P D A などの携帯端末の表示部として用いて好適なものである。

【 0 0 3 3 】

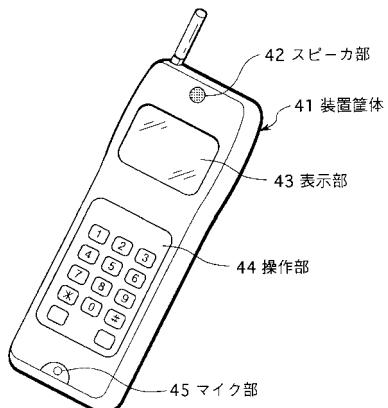

図 8 は、本発明が適用される携帯端末、例えば携帯電話機の構成の概略を示す外観図である。 10

【 0 0 3 4 】

本例に係る携帯電話機は、装置筐体 4 1 の前面側に、スピーカ部 4 2 、表示部 4 3 、操作部 4 4 およびマイク部 4 5 が上部側から順に配置された構成となっている。かかる構成の携帯電話機において、表示部 4 3 には例えば液晶表示装置が用いられ、この液晶表示装置として、先述した実施形態に係るアクティブマトリクス型液晶表示装置が用いられる。

【 0 0 3 5 】

このように、携帯電話機などの携帯端末において、先述した実施形態に係るアクティブマトリクス型液晶表示装置を表示部 4 3 として用いることにより、当該液晶表示装置に搭載される基準電圧発生回路の回路構成が簡単で、表示装置の低コスト化、さらには薄型化、コンパクト化を図ることができるため、端末本体の低コスト化、さらには薄型化、コンパクト化が可能となる。 20

【 0 0 3 6 】

【発明の効果】

以上説明したように、本発明によれば、アクティブマトリクス型表示装置あるいはこれを表示部として用いた携帯端末において、基準電圧発生回路を表示エリア部および水平駆動回路と共に同一基板上に作成するようにしたことにより、セットを構成する部品点数を少なく抑えることができるため、セットの低コスト化、さらには薄型化、コンパクト化が可能になる。また、基準電圧発生回路を表示エリア部を挟んで垂直駆動回路と反対側の辺における一対の水平駆動回路から等距離の位置に配置したことで、基準電圧発生回路を別基板に配置した場合に必要となるバッファ回路を省略できるため、その分だけ基準電圧発生回路の回路構成を簡略化できる。 30

【図面の簡単な説明】

【図 1】本発明の一実施形態に係るアクティブマトリクス型表示装置の構成例を示す概略構成図である。

【図 2】液晶表示装置の表示エリア部の構成例を示す回路図である。

【図 3】H ドライバの具体的な構成の一例を示すブロック図である。

【図 4】基準電圧選択型 D A 変換回路の構成の一例を示す回路図である。

【図 5】基準電圧発生回路の一般的な構成例を示す回路図である。

【図 6】本実施形態に係る基準電圧発生回路の具体的な構成例を示す回路図である。 40

【図 7】本実施形態に係る基準電圧発生回路の動作説明のためのタイミングチャートである。

【図 8】本発明に係る携帯端末である携帯電話機の構成の概略を示す外観図である。

【符号の説明】

1 1 ... ガラス基板、 1 2 ... 表示エリア部、 1 3 U , 1 3 D ... H ドライバ ( 水平駆動回路 ) 、 1 4 ... V ドライバ ( 垂直駆動回路 ) 、 1 5 ... 基準電圧発生回路、 2 3 ... 単位画素、 2 8 U , 2 8 D ... 基準電圧選択型 D A 変換回路、 3 1 , 3 2 ... スイッチ回路、 3 1 - 1 ~ 3 1 - n ... バッファ回路

【図1】

【図2】

【図3】

【図4】

【図5】

【図7】

【図6】

【図8】

---

フロントページの続き

| (51)Int.Cl.    |               | F I              |                |              |                |

|----------------|---------------|------------------|----------------|--------------|----------------|

| <b>G 0 9 G</b> | <b>3/30</b>   | <b>(2006.01)</b> | <b>G 0 9 G</b> | <b>3/20</b>  | <b>6 8 0 G</b> |

| <b>G 0 9 G</b> | <b>3/36</b>   | <b>(2006.01)</b> | <b>G 0 9 G</b> | <b>3/20</b>  | <b>6 8 0 S</b> |

| <b>H 0 1 L</b> | <b>21/822</b> | <b>(2006.01)</b> | <b>G 0 9 G</b> | <b>3/30</b>  | <b>Z</b>       |

| <b>H 0 1 L</b> | <b>27/04</b>  | <b>(2006.01)</b> | <b>G 0 9 G</b> | <b>3/36</b>  |                |

| <b>H 0 1 L</b> | <b>29/786</b> | <b>(2006.01)</b> | <b>H 0 1 L</b> | <b>27/04</b> | <b>B</b>       |

|                |               |                  | <b>H 0 1 L</b> | <b>29/78</b> | <b>6 1 2 B</b> |

(56)参考文献 特開平06-095078 (JP, A)

特開平08-201763 (JP, A)

特開平11-338435 (JP, A)

特開2000-305527 (JP, A)

特開平08-304760 (JP, A)

特開平06-208337 (JP, A)

特開平10-239655 (JP, A)

特開平09-171376 (JP, A)

## (58)調査した分野(Int.Cl., DB名)

G09G 3/00 - 3/38

G09F 9/00

G02F 1/133- 1/1345

H01L 21/822

H01L 27/04

H01L 29/786