(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6584812号

(P6584812)

(45) 発行日 令和1年10月2日(2019.10.2)

(24) 登録日 令和1年9月13日(2019.9.13)

(51) Int.Cl.

F 1

|             |             |                  |      |      |   |

|-------------|-------------|------------------|------|------|---|

| <b>H04B</b> | <b>1/18</b> | <b>(2006.01)</b> | H04B | 1/18 | D |

| <b>H04B</b> | <b>1/40</b> | <b>(2015.01)</b> | H04B | 1/18 | J |

| <b>H03H</b> | <b>9/72</b> | <b>(2006.01)</b> | H04B | 1/40 |   |

| <b>H03H</b> | <b>7/46</b> | <b>(2006.01)</b> | HO3H | 9/72 |   |

|             |             |                  | HO3H | 7/46 | A |

請求項の数 12 外国語出願 (全 24 頁)

(21) 出願番号 特願2015-80857 (P2015-80857)

(22) 出願日 平成27年4月10日 (2015.4.10)

(65) 公開番号 特開2015-204628 (P2015-204628A)

(43) 公開日 平成27年11月16日 (2015.11.16)

審査請求日 平成30年4月5日 (2018.4.5)

(31) 優先権主張番号 61/978,810

(32) 優先日 平成26年4月11日 (2014.4.11)

(33) 優先権主張国・地域又は機関

米国(US)

(73) 特許権者 503031330

スカイワークス ソリューションズ、イン

コーポレイテッド

S K Y W O R K S S O L U T I O N S,

I N C.

アメリカ合衆国、01801 マサチュー

セツツ州、ウォーバーン、シリバン・ロード

、20

(74) 代理人 110001195

特許業務法人深見特許事務所

(72) 発明者 イブラヒム・エンジン・ペーリバノグル

アメリカ合衆国、92627 カリフォル

ニア州、コスター・メサ、カレッジ・アベニ

ュ、2160、ユニット・シイ

最終頁に続く

(54) 【発明の名称】キャリアアグリゲーション回路、高周波モジュール、および無線装置

## (57) 【特許請求の範囲】

## 【請求項 1】

キャリアアグリゲーション回路であって、

入力ノードと、共通ノードと、出力ノードと、

第1の周波数帯での動作を可能にするように構成された第1のフィルタと、

第2の周波数帯での動作を可能にするように構成された第2のフィルタと、

前記入力ノードと前記出力ノードとの間に実装された第1の増幅経路とを備え、前記第1の増幅経路は、前記第1のフィルタと、そのベースを通して信号を受け、かつ、そのコレクタを通して出力を生成するように構成されたバイポーラ接合トランジスタとして実装された第1の電流変換器段と、前記共通ノードと、共有バイポーラ接合トランジスタとして実装された共通加算器段とを含み、前記第1の増幅経路にはスイッチがなく、

前記入力ノードと前記出力ノードとの間に実装された第2の増幅経路を備え、前記第2の増幅経路は、前記第2のフィルタと、そのベースを通して信号を受け、かつそのコレクタを通して出力を生成するように構成されたバイポーラ接合トランジスタとして実装された第2の電流変換器段と、前記共通ノードと、前記共通加算器段とを含み、前記第2の増幅経路にはスイッチがなく、前記共有バイポーラ接合トランジスタは、そのエミッタを通して、前記第1の電流変換器段および前記第2の電流変換器段の前記バイポーラ接合トランジスタから出力された信号を受け、そのコレクタを通して出力を生成し、前記第1の電流変換器段、前記第2の電流変換器段および前記共通加算器段は、低雑音増幅器の一部であり、

10

前記入力ノードと前記出力ノードとの間に実装された第2の増幅経路を備え、前記第2の増幅経路は、前記第2のフィルタと、そのベースを通して信号を受け、かつそのコレクタを通して出力を生成するように構成されたバイポーラ接合トランジスタとして実装された第2の電流変換器段と、前記共通ノードと、前記共通加算器段とを含み、前記第2の増幅経路にはスイッチがなく、前記共有バイポーラ接合トランジスタは、そのエミッタを通して、前記第1の電流変換器段および前記第2の電流変換器段の前記バイポーラ接合トランジスタから出力された信号を受け、そのコレクタを通して出力を生成し、前記第1の電流変換器段、前記第2の電流変換器段および前記共通加算器段は、低雑音増幅器の一部であり、

20

前記第1の電流変換器段および前記第2の電流変換器段の前記バイポーラ接合トランジスタに結合されたバイアス回路をさらに備え、前記バイアス回路は、それぞれのバイアスノードとそれぞれの前記ベースとの間に、切替可能なバイアス供給経路を含み、前記切替可能なバイアス供給経路は、オンまたはオフされることによってそれぞれの前記バイポーラ接合トランジスタをアクティブ化または非アクティブ化することができるよう構成され、前記バイアス回路はさらに、それぞれの前記バイポーラ接合トランジスタが非アクティブ化されたときに分路を与えるように構成された切替可能な分路を含む、キャリアアグリゲーション回路。

**【請求項2】**

前記第1の増幅経路および前記第2の増幅経路にスイッチがないことにより、前記キャリアアグリゲーション回路は雑音指数が減じられた状態で動作することができる、請求項1に記載のキャリアアグリゲーション回路。 10

**【請求項3】**

前記第1の電流変換器段および前記第2の電流変換器段各々の前記バイポーラ接合トランジスタは、インダクタンスを通して接地に結合されたエミッタを含む、請求項1に記載のキャリアアグリゲーション回路。

**【請求項4】**

前記共有バイポーラ接合トランジスタは、そのベースを通してカスコードバイアス電圧を受けるように構成される、請求項1に記載のキャリアアグリゲーション回路。

**【請求項5】**

前記第1の増幅経路および前記第2の増幅経路は各々、アクティブ状態または非アクティブ状態になることにより、前記第1の増幅経路および前記第2の増幅経路に沿う個別のスイッチなしで、前記キャリアアグリゲーション回路をキャリアアグリゲーションモードまたは非キャリアアグリゲーションモードで動作させることができる、請求項1に記載のキャリアアグリゲーション回路。 20

**【請求項6】**

前記第1の増幅経路および前記第2の増幅経路各々のアクティブ状態または非アクティブ状態は、それぞれの電流変換器段をアクティブ化または非アクティブ化することによって得られる、請求項5に記載のキャリアアグリゲーション回路。

**【請求項7】**

高周波モジュールであって、

複数の構成要素を支持するように構成された実装基板と、

前記実装基板上に実装されたキャリアアグリゲーション回路とを備え、前記キャリアアグリゲーション回路は、入力ノードと、共通ノードと、出力ノードとを含み、

前記キャリアアグリゲーション回路は、さらに、第1の周波数帯での動作を可能にするように構成された第1のフィルタと、第2の周波数帯での動作を可能にするように構成された第2のフィルタとを含み、前記キャリアアグリゲーション回路はさらに前記入力ノードと前記出力ノードとの間に実装された第1の増幅経路を含み、前記第1の増幅経路は、前記第1のフィルタと、そのベースを通して信号を受け、かつ、そのコレクタを通して出力を生成するように構成されたバイポーラ接合トランジスタとして実装された第1の電流変換器段と、前記共通ノードと、共有バイポーラ接合トランジスタとして実装された共通加算器段とを含み、前記第1の増幅経路にはスイッチがなく、前記キャリアアグリゲーション回路はさらに前記入力ノードと前記出力ノードとの間に実装された第2の増幅経路を含み、前記第2の増幅経路は、前記第2のフィルタと、そのベースを通して信号を受け、かつそのコレクタを通して出力を生成するように構成されたバイポーラ接合トランジスタとして実装された第2の電流変換器段と、前記共通ノードと、前記共通加算器段とを含み、前記第2の増幅経路にはスイッチがなく、前記共有バイポーラ接合トランジスタは、そのエミッタを通して、前記第1の電流変換器段および前記第2の電流変換器段の前記バイポーラ接合トランジスタから出力された信号を受け、そのコレクタを通して出力を生成し、前記第1の電流変換器段、前記第2の電流変換器段および前記共通加算器段は、低雑音 40

10

20

30

40

50

増幅器の一部であり、

前記キャリアアグリゲーション回路は、前記第1の電流変換器段および前記第2の電流変換器段の前記バイポーラ接合トランジスタに結合されたバイアス回路をさらに含み、前記バイアス回路は、それぞれのバイアスノードとそれぞれの前記ベースとの間に、切替可能なバイアス供給経路を含み、前記切替可能なバイアス供給経路は、オンまたはオフされることによってそれぞれの前記バイポーラ接合トランジスタをアクティブ化または非アクティブ化することができるよう構成され、前記バイアス回路はさらに、それぞれの前記バイポーラ接合トランジスタが非アクティブ化されたときに分路を与えるように構成された切替可能な分路を含む、高周波モジュール。

**【請求項8】**

10

前記第1のフィルタおよび前記第2のフィルタは各々表面弾性波フィルタを含む、請求項7に記載の高周波モジュール。

**【請求項9】**

前記高周波モジュールはダイバーシティ受信モジュールである、請求項8に記載の高周波モジュール。

**【請求項10】**

無線装置であって、

高周波信号を処理するように構成された受信機と、

前記受信機と通信するモジュールとを備え、前記モジュールは、前記高周波信号をルーティングするように構成されたキャリアアグリゲーション回路を含み、前記キャリアアグリゲーション回路は、入力ノードと、共通ノードと、出力ノードとを含み、前記キャリアアグリゲーション回路は、さらに、第1の周波数帯での動作を可能にするように構成された第1のフィルタと第2の周波数帯での動作を可能にするように構成された第2のフィルタとを含み、前記キャリアアグリゲーション回路はさらに、前記入力ノードと前記出力ノードとの間に実装された第1の増幅経路を含み、前記第1の増幅経路は、前記第1のフィルタと、そのベースを通して信号を受け、かつ、そのコレクタを通して出力を生成するように構成されたバイポーラ接合トランジスタとして実装された第1の電流変換器段と、前記共通ノードと、共有バイポーラ接合トランジスタとして実装された共通加算器段とを含み、前記第1の増幅経路にはスイッチがなく、前記キャリアアグリゲーション回路はさらに、前記入力ノードと前記出力ノードとの間に実装された第2の増幅経路を含み、前記第2の増幅経路は、前記第2のフィルタと、そのベースを通して信号を受け、かつそのコレクタを通して出力を生成するように構成されたバイポーラ接合トランジスタとして実装された第2の電流変換器段と、前記共通ノードと、前記共通加算器段とを含み、前記第2の増幅経路にはスイッチがなく、前記共有バイポーラ接合トランジスタは、そのエミッタを通して、前記第1の電流変換器段および前記第2の電流変換器段の前記バイポーラ接合トランジスタから出力された信号を受け、そのコレクタを通して出力を生成し、前記第1の電流変換器段、前記第2の電流変換器段および前記共通加算器段は、低雑音増幅器の一部であり、

20

前記キャリアアグリゲーション回路は、前記第1の電流変換器段および前記第2の電流変換器段の前記バイポーラ接合トランジスタに結合されたバイアス回路をさらに含み、前記バイアス回路は、それぞれのバイアスノードとそれぞれの前記ベースとの間に、切替可能なバイアス供給経路を含み、前記切替可能なバイアス供給経路は、オンまたはオフされることによってそれぞれの前記バイポーラ接合トランジスタをアクティブ化または非アクティブ化することができるよう構成され、前記バイアス回路はさらに、それぞれの前記バイポーラ接合トランジスタが非アクティブ化されたときに分路を与えるように構成された切替可能な分路を含み、

30

前記無線装置はさらに、前記モジュールと通信するアンテナを備え、前記アンテナは高周波信号を受信するように構成される、無線装置。

**【請求項11】**

前記アンテナはダイバーシティアンテナを含み、前記モジュールはダイバーシティ受信

40

50

モジュールを含む、請求項1\_0に記載の無線装置。

**【請求項 1 2】**

前記高周波信号を前記ダイバーシティアンテナから前記受信機にルーティングするよう構成されたアンテナスイッチモジュールをさらに備え、前記ダイバーシティ受信モジュールは前記ダイバーシティアンテナと前記アンテナスイッチモジュールとの間に実装される、請求項1\_1に記載の無線装置。

**【発明の詳細な説明】**

**【技術分野】**

**【0 0 0 1】**

関連出願の相互参照

10

本願は、2014年4月11に出願され「CIRCUITS AND METHODS RELATED TO SWITCHLESS CARRIER AGGREGATION IN RADIO-FREQUENCY RECEIVERS（高周波受信機におけるスイッチレスキャリアアグリゲーションに関する回路および方法）」と題された米国仮出願第61/978,810号に基づく優先権を主張し、その開示全体を本明細書に引用により特に援用する。

**【0 0 0 2】**

背景

分野

本開示は高周波（R F）受信機におけるキャリアアグリゲーションに関する。

**【背景技術】**

20

**【0 0 0 3】**

関連技術の説明

いくつかのR F用途において、セルラーキャリアアグリゲーション（CA）には、共通の経路を通して処理されている2つ以上のR F信号が関与し得る。たとえば、キャリアアグリゲーションには、それぞれの周波数範囲が十分に離れている複数の周波数帯に対して1つの経路を使用することが関与し得る。このような構成では、2つ以上の周波数帯を同時に機能させることができる。

**【発明の概要】**

**【課題を解決するための手段】**

**【0 0 0 4】**

30

概要

いくつかの実装例において、本開示は、第1の周波数帯での動作を可能にするように構成された第1のフィルタと第2の周波数帯での動作を可能にするように構成された第2のフィルタとを含むキャリアアグリゲーション（CA）回路に関する。CA回路はさらに、第1のフィルタと出力ノードとの間に実装された第1の信号経路を含む。第1の信号経路は、第1の高周波（R F）信号を増幅するように構成された複数の増幅段を含む。第1の信号経路には実質的にスイッチがない。CA回路はさらに、第2のフィルタと上記出力ノードとの間に実装された第2の信号経路を含む。第2の信号経路は、第2のR F信号を増幅するように構成された複数の増幅段を含む。第2の信号経路には実質的にスイッチがない。

40

**【0 0 0 5】**

ある実施形態において、第1の信号経路および第2の信号経路は、低雑音増幅器（LNA）の一部であってもよい。第1の信号経路および第2の信号経路に実質的にスイッチがないことにより、CA回路は雑音指数が減じられた状態で動作することができる。

**【0 0 0 6】**

ある実施形態において、第1の信号経路および第2の信号経路各々の複数の増幅段は、第1段と第2段とを含み得る。第1段はそれぞれのR F信号を電流に変換するように構成し得る。第2段は電流を加算するように構成し得る。

**【0 0 0 7】**

ある実施形態において、第1の信号経路および第2の信号経路各々の第1段は、そのベ

50

ースを通してそれぞれの R F 信号を受けそのコレクタを通して出力を生成するように構成された第 1 のバイポーラ接合トランジスタ ( B J T ) を含み得る。 C A 回路はさらに、第 1 の B J T に結合されたバイアス回路を含み得る。バイアス回路は、バイアスノードと上記ベースとの間に、切替可能なバイアス供給経路を含み得る。この切替可能なバイアス供給経路は、オンまたはオフされることによってそれぞれの第 1 の B J T をアクティブ化または非アクティブ化することができるよう構成される。バイアス回路はさらに、それぞれの第 1 の B J T が非アクティブ化されたときに分路を与えるように構成された切替可能な分路を含み得る。

#### 【 0 0 0 8 】

ある実施形態において、第 1 の信号経路および第 2 の信号経路各々の第 1 の B J T は、インダクタンスを通して接地に結合されたエミッタを含み得る。第 1 の信号経路および第 2 の信号経路の第 1 の B J T のエミッタは、別々のインダクタンスを通してまたは共通のインダクタンスを通して接地に結合し得る。 10

#### 【 0 0 0 9 】

ある実施形態において、第 1 の信号経路および第 2 の信号経路の第 2 段は、そのエミッタを通して第 1 の B J T から R F 信号を受けそのコレクタを通して出力を生成するように構成された共有第 2 B J T によって与えられてもよい。共有第 2 B J T は、そのベースを通してカスコードバイアス電圧 V c a s を受けるように構成し得る。カスコードバイアス電圧 V c a s は、共有第 2 B J T の入力の数に応じて調整可能であってもよい。 20

#### 【 0 0 1 0 】

ある実施形態において、第 1 の信号経路および第 2 の信号経路各々の第 2 段は、そのエミッタを通してそれぞれの第 1 の B J T から R F 信号を受けそのコレクタを通して出力を生成するように構成された個別第 2 B J T を含み得る。各個別第 2 B J T は、そのベースを通してそれぞれのカスコードバイアス電圧 V c a s を受けるように構成し得る。 20

#### 【 0 0 1 1 】

ある実施形態において、第 1 のフィルタおよび第 2 のフィルタは、ダイプレクサの一部であってもよい。ダイプレクサは、アンテナから R F 信号を受信するように構成された入力ポートを含み得る。 30

#### 【 0 0 1 2 】

ある実施形態において、第 1 の信号経路および第 2 の信号経路は各々、アクティブ状態または非アクティブ状態になることにより、第 1 の信号経路および第 2 の信号経路に沿う個別のスイッチなしで、 C A 回路を C A モードまたは非 C A モードで動作させることができるものであってもよい。第 1 の信号経路および第 2 の信号経路各々のアクティブ状態または非アクティブ状態は、それぞれの第 1 段をアクティブ化または非アクティブ化することによって得ることができる。 30

#### 【 0 0 1 3 】

ある実装例に従うと、本開示は、複数の構成要素を支持するように構成された実装基板と、実装基板上に実装されたキャリアアグリゲーション ( C A ) 回路とを含む高周波 ( R F ) モジュールに関する。 C A 回路は、第 1 の周波数帯での動作を可能にするように構成された第 1 のフィルタと第 2 の周波数帯での動作を可能にするように構成された第 2 のフィルタとを含む。 C A 回路はさらに、第 1 のフィルタと出力ノードとの間に実装された第 1 の信号経路を含み、第 1 の信号経路は、第 1 の高周波 ( R F ) 信号を増幅するように構成された複数の増幅段を含み、第 1 の信号経路には実質的にスイッチがない。 C A 回路はさらに、第 2 のフィルタと上記出力ノードとの間に実装された第 2 の信号経路を含み、第 2 の信号経路は、第 2 の R F 信号を増幅するように構成された複数の増幅段を含み、第 2 の信号経路には実質的にスイッチがない。 40

#### 【 0 0 1 4 】

ある実施形態において、第 1 のフィルタおよび第 2 のフィルタは各々、表面弾性波 ( S A W ) フィルタを含み得る。第 1 の S A W フィルタおよび第 2 の S A W フィルタは、ダイプレクサとして実装し得る。第 1 の信号経路および第 2 の信号経路各々の複数の増幅段は 50

、低雑音増幅器（LNA）の一部であってもよい。

**【0015】**

ある実施形態において、RFモジュールはフロントエンドモジュールであってもよい。ある実施形態において、RFモジュールはダイバーシティ受信（DRx）モジュールであってもよい。

**【0016】**

いくつかの教示において、本開示は、高周波（RF）モジュールを製造する方法に関する。この方法は、複数の構成要素を支持するように構成された実装基板を与えるまたは形成することと、キャリアアグリゲーション（CA）回路を実装基板上に実装することとを含む。CA回路は、第1の周波数帯での動作を可能にするように構成された第1のフィルタと、第2の周波数帯での動作を可能にするように構成された第2のフィルタとを含む。CA回路はさらに、第1のフィルタと出力ノードとの間に実装された第1の信号経路を含み、第1の信号経路は、第1の高周波（RF）信号を増幅するように構成された複数の増幅段を含み、第1の信号経路には実質的にスイッチがない。CA回路はさらに、第2のフィルタと上記出力ノードとの間に実装された第2の信号経路を含み、第2の信号経路は、第2のRF信号を増幅するように構成された複数の増幅段を含み、第2の信号経路には実質的にスイッチがない。10

**【0017】**

いくつかの実装例に従うと、本開示は、高周波（RF）装置に関し、この装置は、RF信号を処理するように構成された受信機と、受信機と通信するRFモジュールとを含む。RFモジュールは、第1の周波数帯での動作を可能にするように構成された第1のフィルタと、第2の周波数帯での動作を可能にするように構成された第2のフィルタとを有するキャリアアグリゲーション（CA）回路を含む。CA回路はさらに、第1のフィルタと出力ノードとの間に実装された第1の信号経路を含み、第1の信号経路は、第1の高周波（RF）信号を増幅するように構成された複数の増幅段を含み、第1の信号経路には実質的にスイッチがない。CA回路はさらに、第2のフィルタと上記出力ノードとの間に実装された第2の信号経路を含み、第2の信号経路は、第2のRF信号を増幅するように構成された複数の増幅段を含み、第2の信号経路には実質的にスイッチがない。RF装置はさらに、RFモジュールと通信するアンテナを含み、アンテナはRF信号を受信するように構成されている。20

**【0018】**

ある実施形態において、RF装置は無線装置であってもよい。このような無線装置はたとえば携帯電話であってもよい。ある実施形態において、アンテナはダイバーシティアンテナを含み得る。また、RFモジュールはダイバーシティ受信（DRx）モジュールを含み得る。ある実施形態において、無線装置はさらに、RF信号をダイバーシティアンテナから受信機にルーティングするように構成されたアンテナスイッチモジュール（ASM）を含み得る。DRxモジュールは、ダイバーシティアンテナとASMの間に実装し得る。30

**【0019】**

本開示を要約するために、この明細書では本発明のある局面、利点、および新規な特徴について説明してきた。本発明のいずれか特定の実施形態に従いすべてのこのような利点を実現し得る訳では必ずしもないことが理解されるはずである。したがって、本明細書で教示されている1つの利点または一群の利点を、本明細書で教示または示唆されているであろうその他の利点は必ずしも得られないが、得るまたは最適化するように、本発明を実施または実行することができる。40

**【図面の簡単な説明】**

**【0020】**

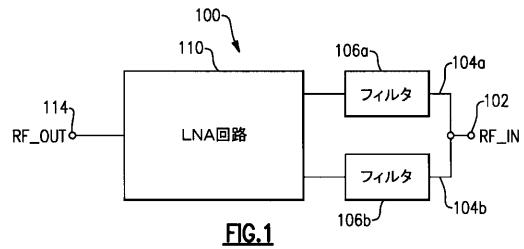

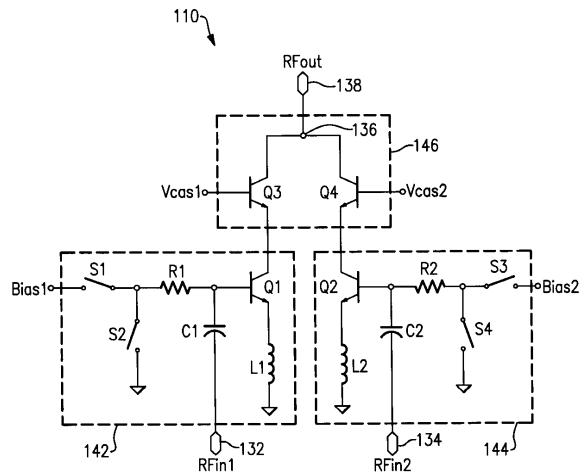

【図1】2つの入力を受信し出力を生成するように構成された低雑音増幅器（LNA）回路を含むキャリアアグリゲーション（CA）構成を示す。

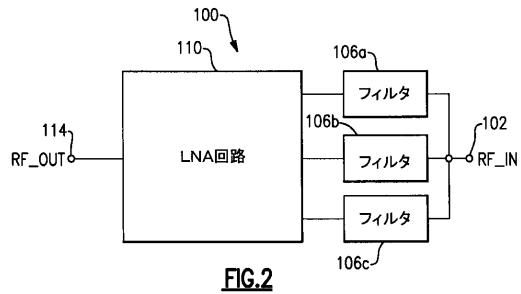

【図2】3つ以上の周波数帯の集約においても実装し得る本開示の1つ以上の特徴を示す。50

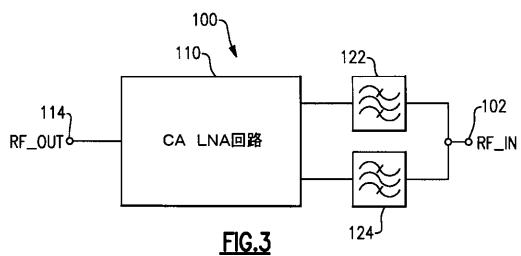

【図3】信号経路に沿うスイッチなしでCA機能を提供するように本明細書に記載の1つ以上の特徴を有するLNA回路を実装し得る例を示す。

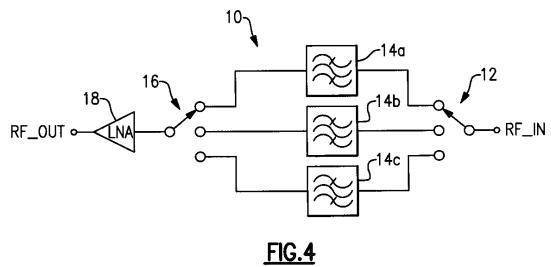

【図4】共通アンテナおよび共通LNAを利用して3つの周波数帯で動作するように構成されたマルチバンド受信機アーキテクチャの例を示す。

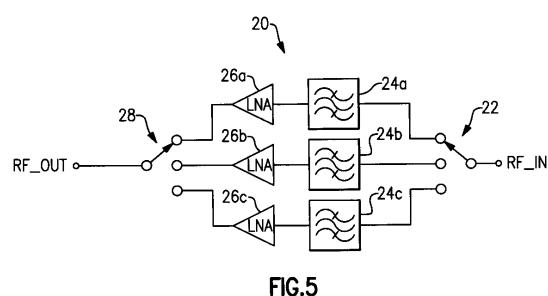

【図5】共通アンテナおよび3つの個別LNAを利用して3つの周波数帯で動作するように構成された、別の例としてのマルチバンド受信機アーキテクチャを示す。

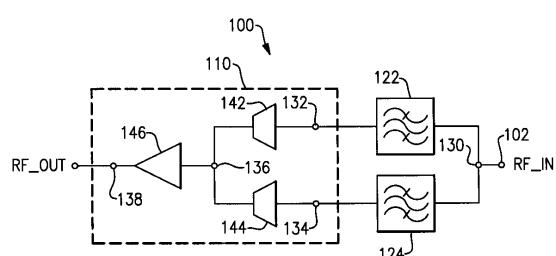

【図6】バンドパスフィルタとLNAとの間のスイッチを省くことができそれでもなおCAアーキテクチャがCAモードまたは非CAモードで動作できるように構成されたLNA回路を含むキャリアアグリゲーション(CA)アーキテクチャを示す。

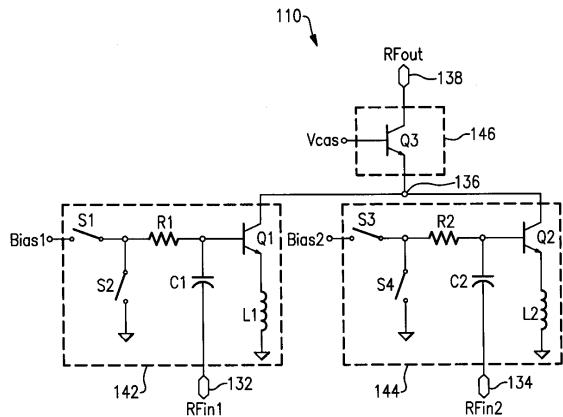

【図7】図6のLNA回路のより具体的な例として実装し得るLNA回路を示す。 10

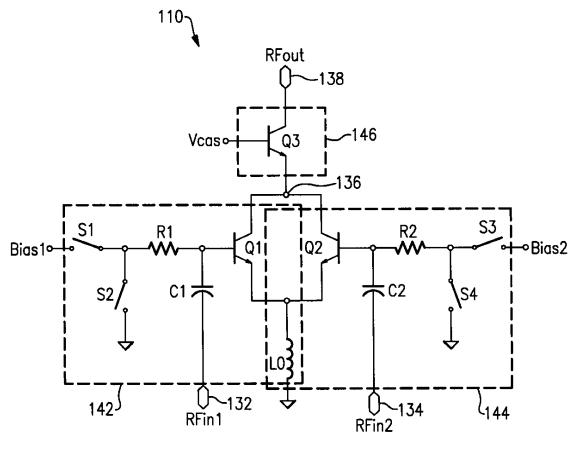

【図8】図6のLNA回路の別のより具体的な例として実装し得るLNA回路を示す。

【図9】図6のLNA回路の他のより具体的な例として実装し得るLNA回路を示す。

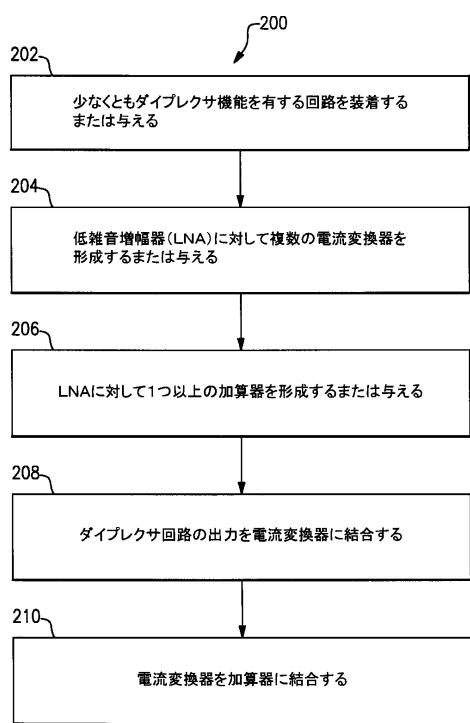

【図10】本明細書に記載の1つ以上の特徴を有する装置を製造するために実装し得るプロセスを示す。

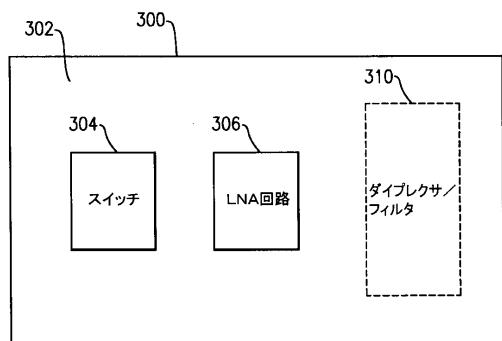

【図11】ある実施形態において本明細書に記載の1つ以上の特徴をRF用途に合わせて構成されたモジュールにおいて実装し得ることを示す。

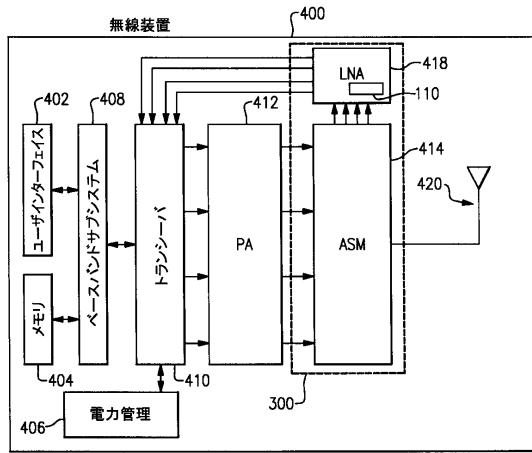

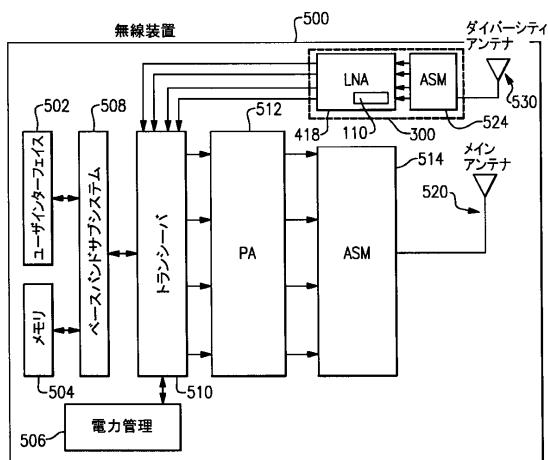

【図12】本明細書に記載の1つ以上の有利な特徴を有する無線装置の例を示す。

【図13】本明細書に記載の1つ以上の有利な特徴を有する無線装置の別の例を示す。

【図14】本開示の1つ以上の特徴をダイバーシティ受信モジュールにおいて実装し得ることを示す。 20

【図15】図14のダイバーシティ受信モジュールを有する無線装置の例を示す。

#### 【発明を実施するための形態】

##### 【0021】

###### いくつかの実施形態の詳細な説明

本明細書では、見出しが設けられていても、それは便宜上設けられているだけでありクレームされている発明の範囲または意味には必ずしも影響しない。

##### 【0022】

セルラーキャリアアグリゲーション(CA)は、共通経路を通して2つ以上の高周波(RF)信号が処理されるようにすることができる。たとえば、キャリアアグリゲーションには、それぞれの周波数範囲が十分に離れている複数の周波数帯に対して1つの経路を使用することが関与し得る。このような構成では、2つ以上の周波数帯を同時に機能させることができある。 30

##### 【0023】

受信機との関連では、キャリアアグリゲーションは、複数の周波数帯のRF信号が同時に処理されることによって、たとえば高データレート能力を提供することができる。このようなキャリアアグリゲーションシステムでは、各RF信号について低雑音指数(NF)を保つことが望ましい。集約されている2つの周波数帯の周波数が近い場合、2つの周波数帯の十分な分離を保つことも望ましい。

##### 【0024】

図1は、2つの入力を受信し出力を生成するように構成された低雑音増幅器(LNA)回路110を含むキャリアアグリゲーション(CA)構成100を示す。この2つの入力は、第1のRF信号および第2のRF信号を含み得る。第1のRF信号は、共通入力ノード102(RF\_IN)から、第1のフィルタ106aを含む第1の経路104aを通してLNA回路110に与えることができる。同様に、第2のRF信号は、共通入力ノード102(RF\_IN)から、第2のフィルタ106bを含む第2の経路104bを通してLNA回路110に与えることができる。本明細書に記載のように、LNA回路110は、共通出力ノード114での出力が、第1および第2のRF信号に関連する2つの分離された周波数帯を含む増幅されたRF信号となるように、構成し得る。また、本明細書に記載のように、LNA回路110は、低損失、低雑音指数、および2つの信号経路104a、104b間の高度な分離といった望ましい性能の特徴を生出すように構成し得る。 40

## 【0025】

図1の例を含む、本明細書におけるさまざまな例について、2つの周波数帯の集約との関連で説明する。しかしながら、本開示の1つ以上の特徴は3つ以上の周波数帯の集約において実装し得ることが理解されるであろう。たとえば、図2は、3つのRF信号が、共通入力ノード102(RF\_IN)で分離され、それぞれのフィルタ106a、106b、106cを通して処理され、LNA回路110によって処理されることにより、共通出力ノード114(RF\_OUT)において増幅RF信号を与える、CA構成100を示す。本明細書に記載の1つ以上の特徴を利用して他の数の周波数帯を集約することも可能であることが理解されるであろう。

## 【0026】

図1および図2のアグリゲーション構成100は、多数のRF用途において実装し得る。図3は、本明細書に記載の1つ以上の特徴を有するLNA回路110を、信号経路に沿うスイッチなしでまたはスイッチの数を少なくしてCA機能を提供するように実装し得る、より具体的な例を示す。LNA回路110は、たとえば2つの入力を受け出力を生成するように構成し得る。2つの入力は第1のRF信号および第2のRF信号を含み得る。第1のRF信号は、共通入力ノード102(RF\_IN)から、第1のバンドパスフィルタ122を含む第1の経路を通してLNA回路110に与えることができる。同様に、第2のRF信号は、共通入力ノード102(RF\_IN)から、第2のバンドパスフィルタ124を含む第2の経路を通してLNA回路110に与えることができる。本明細書に記載のように、LNA回路110は、共通出力ノード114における出力が、第1および第2のRF信号に関連する2つの分離された周波数帯を含む増幅RF信号となるように、構成し得る。また、本明細書に記載のように、LNA回路110は、低損失、低雑音指数、および2つの入力信号経路間の高度な分離といった望ましい性能の特徴を生出すように構成し得る。

10

## 【0027】

ある実施形態において、LNA回路110は、十分に広い帯域幅に対して機能することにより第1および第2の周波数帯を効果的に増幅するように構成し得る。ある実施形態において、バンドパスフィルタ122、124は、たとえば表面弹性波(SAW)フィルタを含む多数のやり方で実装し得る。本明細書ではSAWフィルタとの関連でさまざまな例を説明しているが、その他の種類のフィルタも利用できることが理解されるであろう。

20

## 【0028】

本明細書に記載のように、図3のアグリゲーション構成100は、他の受信機構成よりも有利な多数の特徴を提供することができる。たとえば、図4に示すマルチバンド受信機アーキテクチャ10は、共通アンテナ(図示せず)と共にLNA18を利用して3つの周波数帯で動作するように構成されている。共通アンテナからのRF信号は入力信号RF\_INとして受信されている。第1のスイッチ12および第2のスイッチ16によってこのような入力信号を3つの経路のうちの1つを通してルーティングすることができる。たとえば、第1および第2のスイッチ12、16が、示されている状態であれば、入力信号は第1のバンドパスフィルタ14aにルーティングされて第1の周波数帯に対応するフィルタリングされた第1の信号を与える。第2の周波数帯での動作が望まれる場合は、入力信号が第2のバンドパスフィルタ14bにルーティングされて第2の周波数帯に対応するフィルタリングされた第2の信号を与えるように、第1および第2のスイッチ12、16を設定すればよい。同様に、第3の周波数帯での動作が望まれる場合、入力信号が第3のバンドパスフィルタ14cにルーティングされて第3の周波数帯に対応するフィルタリングされた第3の信号を与えるように、第1および第2のスイッチ12、16を設定すればよい。

30

## 【0029】

図4の例では、CAモードでの動作は一般的には不可能である。なぜなら、2つの経路を同時にオンにすると、結果として2つのフィルタ出力が短絡するからである。さらに、アーキテクチャ10内のスイッチは、性能および/または設計上の課題をもたらし得る。

40

50

たとえば第2のスイッチ16は、たとえば雑音指数性能の劣化をもたらし得る。別の例では、スイッチおよびLNAは、所望の性能を得るために互いに異なるプロセスのものである必要がある場合がある（たとえばスイッチはシリコン・オン・インシュレータ（SOI）、LNAはバイポーラ接合トランジスタ（BJT））。また、このように異なるプロセスを使用すると、結果として装置のサイズおよび／またはコストが大幅に増大する可能性がある。

#### 【0030】

図5は、共通アンテナ（図示せず）と3つの個別LNA26a、26b、26cを利用して3つの周波数帯で動作するように構成された、別の例としてのマルチバンド受信機アーキテクチャ20を示す。共通アンテナからのRF信号は入力信号RF\_INとして受信されることが示されている。第1のスイッチ22および第2のスイッチ28によってこのような入力信号を3つの経路のうちの1つを通してルーティングすることができる。たとえば、第1および第2のスイッチ22、28が、示されている状態であれば、入力信号は第1のバンドパスフィルタ24aにルーティングされて第1の周波数帯に対応するフィルタリングされた第1の信号を与える。このようなフィルタリングされた信号は第1のLNA26aに与えられることが示されている。第2の周波数帯での動作が望まれる場合、入力信号が第2のバンドパスフィルタ24bにルーティングされて第2の周波数帯に対応するフィルタリングされた第2の信号を与えるように、第1および第2のスイッチ22、28を設定すればよい。このようなフィルタリングされた信号は第2のLNA26bに与えられることが示されている。同様に、第3の周波数帯での動作が望まれる場合、入力信号が第3のバンドパスフィルタ24cにルーティングされて第3の周波数帯に対応するフィルタリングされた第3の信号を与えるように、第1および第2のスイッチ22、28を設定すればよい。このようなフィルタリングされた信号は第3のLNA26cに与えられることが示されている。

#### 【0031】

図5の例では、図4の例に関連する雑音指数劣化の問題をLNAが大部分解決することができた後に、第2のスイッチ28が実装されている。第2のスイッチに関連する雑音は增幅されないからである。しかしながら、図5のアーキテクチャ20は一般的に、複数の信号経路の各フィルタに対して個別のLNAを必要とする。このような複数のLNAは一般的に、受信機アーキテクチャに関連する、サイズ、コスト、および複雑度の増大を生じさせる。さらに、CAモードでの動作は一般的には不可能である。なぜなら、2つの経路を同時にオンにすると、結果としてLNA出力が短絡するからである。

#### 【0032】

図6は、バンドパスフィルタとLNAとの間のスイッチを省くことができそれでもなおCAアーキテクチャ100がCAモードまたは非CAモードで動作できるように構成されたLNA回路110を含むキャリアアグリゲーション（CA）アーキテクチャ100を示す。LNA回路110は、複数の入力（たとえば2つの入力）を受け出力を生成するように構成し得る。この2つの入力は、共通ノード130で分離された第1のRF信号と第2のRF信号とを含み得る。第1のRF信号は、共通入力ノード102（RF\_IN）から、第1のバンドパスフィルタ122を含む第1の経路を通してLNA回路110に与えることができる。同様に、第2のRF信号は、共通入力ノード102（RF\_IN）から、第2のバンドパスフィルタ124を含む第2の経路を通してLNA回路110に与えることができる。

#### 【0033】

LNA回路110は、共通出力ノード138での出力（RF\_OUT）が、第1および第2のRF信号に関連する分離された2つの周波数帯を含む増幅されたRF信号となるように構成し得る。本明細書に記載のように、LNA回路110は、低損失、低雑音指数、および2つの入力信号経路間の高度な分離といった望ましい性能の特徴を生出すように構成し得る。

#### 【0034】

10

20

30

40

50

ある実施形態において、LNA回路110は複数の増幅経路を含み得る。各増幅経路は、電流変換器部分と加算器部分に分割される。図6の例において、LNA回路110は2つの増幅経路を含むことが示されている。第1の増幅経路は、第1の入力ノード132と、第1の電流変換器142と、共通ノード136と、加算器146と、出力ノード138とを含み得る。同様に、第2の増幅経路は、第2の入力ノード134と、第2の電流変換器144と、共通ノード136と、加算器146と、出力ノード138とを含み得る。LNA回路110のより具体的な例を本明細書において図7～図9を参照しながら説明する。

#### 【0035】

ある実施形態において、上記のように構成されたLNA回路は、たとえば所与の経路のフィルタと増幅回路との間にスイッチがないので雑音指数が減じられているということから利益を得ることができる。加えて、このようにスイッチがないので、CAアーキテクチャに関連するサイズおよび／またはコストを減じることができる。本明細書に記載のように、このようなLNA回路を、集約されている入力間の分離が十分な状態で、CAモードで動作させることができる。さらに、このようなLNA回路は、さまざまな数の入力に合わせて容易に拡大／縮小できる。

#### 【0036】

図7は、図6を参照しながら説明したLNA回路のより具体的な例として実装し得るLNA回路110を示す。図7の例は入力が2つのバージョンであるが、3つ以上の入力を実装できることが理解されるであろう。

#### 【0037】

図7において、第1の電流変換器142は、第1のRF信号(RFin1)を第1の入力ノード132で受け第1のRF信号を処理し処理された第1のRF信号を共通ノード136に出力するように構成されていることが、示されている。同様に、第2の電流変換器144は、第2のRF信号(RFin2)を第2の入力ノード134で受け第2のRF信号を処理し処理された第2のRF信号を共通ノード136に出力するように構成されていることが、示されている。処理された第1および第2のRF信号を共通ノード136で合成し共通加算器146でさらに処理することにより、出力ノード138で出力RF信号(Rfout)を与えることができる。

#### 【0038】

図7において、第1の電流変換器142と共に加算器146の組合せは、第1のカスコード増幅器として実装し得る。同様に、第2の電流変換器144と共に加算器146の組合せは、第2のカスコード増幅器として実装し得る。したがって、第1および第2の電流変換器各々(142または144)は、それぞれのRF信号に対してトランスクンダクタンス増幅機能を提供することができ、共通加算器146は、合成されたRF信号に対して電流バッファ機能を提供することができる。

#### 【0039】

図7において、第1の電流変換器142は共通エミッタ構成のバイポーラ接合トランジスタ(BJT)Q1を含むことが示されている。第1のRF信号(RFin1)は、第1の入力ノード132からDCブロック容量C1を通してQ1のベースに与えることができる。Q1からの出力は、共通ノード136に結合されたコレクタを通して与えることができる。Q1のエミッタはインダクタンスL1を通して接地に結合されることが示されている。Q1に対するバイアス信号(Bias1)は、バイアススイッチS1およびベース抵抗R1を通してQ1のベースに与えることができる。Q1がアクティブ状態のときはバイアススイッチS1を閉じ分路スイッチS2を開くことができる。Q1が非アクティブ状態のときはバイアススイッチS1を開き分路スイッチS2を閉じることができる。バイアススイッチS1および分路スイッチS2は第1のRF信号(RFin1)の経路に直接沿っていないので、これらは第1のRF信号に対する雑音をほとんどまたは全くもたらさない。

#### 【0040】

10

20

30

40

50

図 7において、第 2 の電流変換器 144 は共通エミッタ構成の BJT Q2 を含むことが示されている。第 2 の RF 信号 (RFin2) は、第 2 の入力ノード 134 から DC ブロック容量 C2 を通して Q2 のベースに与えることができる。Q2 からの出力は、共通ノード 136 に結合されたコレクタを通して与えることができる。Q2 のエミッタはインダクタンス L2 を通して接地に結合されることが示されている。Q2 に対するバイアス信号 (Bias2) は、バイアススイッチ S3 およびベース抵抗 R2 を通して Q2 のベースに与えることができる。Q2 がアクティブ状態のときはバイアススイッチ S3 を閉じ分路スイッチ S4 を開くことができる。Q2 が非アクティブ状態のときはバイアススイッチ S3 を開き分路スイッチ S4 を閉じることができる。バイアススイッチ S3 および分路スイッチ S4 は第 2 の RF 信号 (RFin2) の経路に直接沿っていないので、これらは第 2 の RF 信号に対する雑音をほとんどまたは全くもたらさない。10

#### 【0041】

図 7において、共通加算器 146 は共通ベース構成の BJT Q3 を含むことが示されている。共通ノード 136 からの合成 RF 信号は Q3 のエミッタに与えられ Q3 からの出力はそのコレクタを通して与えられることが示されている。コレクタは出力ノード 138 に結合されて出力 RF 信号 (RFout) を与えることが示されている。Q3 のベースには、アクティブ入力の数に応じて調整できるバイアス電圧 Vcas が与えられることが示されている。

#### 【0042】

図 8 は、図 6 を参照しながら説明した LNA 回路の別のより具体的な例として実装し得る LNA 回路 110 を示す。図 8 の例は入力が 2 つのバージョンであるが、3 つ以上の入力を実装できることができ理解されるであろう。図 8 の例は図 7 の例に似ているが、図 8 では第 1 および第 2 の電流変換器の BJT のエミッタが共通インダクタンスを共有している。20

#### 【0043】

より具体的には、図 8において、第 1 の電流変換器 142 は、第 1 の RF 信号 (RFin1) を第 1 の入力ノード 132 で受け第 1 の RF 信号を処理し処理された第 1 の RF 信号を共通ノード 136 に出力するように構成されていることが、示されている。同様に、第 2 の電流変換器 144 は、第 2 の RF 信号 (RFin2) を第 2 の入力ノード 134 で受け第 2 の RF 信号を処理し処理された第 2 の RF 信号を共通ノード 136 に出力するように構成されていることが、示されている。処理された第 1 および第 2 の RF 信号を共通ノード 136 で合成し共通加算器 146 でさらに処理することにより、出力ノード 138 で出力 RF 信号 (RFout) を与えることができる。30

#### 【0044】

図 8において、第 1 の電流変換器 142 と共通加算器 146 の組合せは、第 1 のカスコード増幅器として実装し得る。同様に、第 2 の電流変換器 144 と共通加算器 146 の組合せは、第 2 のカスコード増幅器として実装し得る。したがって、第 1 および第 2 の電流変換器各々 (142 または 144) は、それぞれの RF 信号に対してトランスクンダクタンス増幅機能を提供することができ、共通加算器 146 は、合成された RF 信号に対して電流バッファ機能を提供することができる。

#### 【0045】

図 8において、第 1 の電流変換器 142 は共通エミッタ構成の BJT Q1 を含むことが示されている。第 1 の RF 信号 (RFin1) は、第 1 の入力ノード 132 から DC ブロック容量 C1 を通して Q1 のベースに与えることができる。Q1 からの出力は、共通ノード 136 に結合されたコレクタを通して与えることができる。Q1 のエミッタはインダクタンス L0 を通して接地に結合されることが示されている。Q1 に対するバイアス信号 (Bias1) は、バイアススイッチ S1 およびベース抵抗 R1 を通して Q1 のベースに与えることができる。Q1 がアクティブ状態のときはバイアススイッチ S1 を閉じ分路スイッチ S2 を開くことができる。Q1 が非アクティブ状態のときはバイアススイッチ S1 を開き分路スイッチ S2 を閉じることができる。バイアススイッチ S1 および分路スイッチ S2 は第 1 の RF 信号 (RFin1) の経路に直接沿っていないので、これらは第 1 の4050

R F 信号に対する雑音をほとんどまたは全くもたらさない。

#### 【 0 0 4 6 】

図 8において、第 2 の電流変換器 1 4 4 は共通エミッタ構成の B J T Q 2 を含むことが示されている。第 2 の R F 信号 ( R F i n 2 ) は、第 2 の入力ノード 1 3 4 から D C ブロック容量 C 2 を通して Q 2 のベースに与えることができる。Q 2 からの出力は、共通ノード 1 3 6 に結合されたコレクタを通して与えることができる。Q 2 のエミッタはインダクタンス L 0 を通して接地に結合されている。Q 2 に対するバイアス信号 ( B i a s 2 ) は、バイアススイッチ S 3 およびベース抵抗 R 2 を通して Q 2 のベースに与えることができる。Q 2 がアクティブ状態のときはバイアススイッチ S 3 を閉じ分路スイッチ S 4 を開くことができる。Q 2 が非アクティブ状態のときはバイアススイッチ S 3 を開き分路スイッチ S 4 を閉じることができる。バイアススイッチ S 3 および分路スイッチ S 4 は第 2 の R F 信号 ( R F i n 2 ) の経路に直接沿っていないので、これらは第 2 の R F 信号に対する雑音をほとんどまたは全くもたらさない。10

#### 【 0 0 4 7 】

図 8において、共通加算器 1 4 6 は共通ベース構成の B J T Q 3 を含むことが示されている。共通ノード 1 3 6 からの合成 R F 信号は Q 3 のエミッタに与えられ Q 3 からの出力はそのコレクタを通して与えられることが示されている。コレクタは出力ノード 1 3 8 に結合されて出力 R F 信号 ( R F o u t ) を与えることが示されている。Q 3 のベースには、アクティブ入力の数に応じて調整できるバイアス電圧 V c a s が与えられることが示されている。20

#### 【 0 0 4 8 】

図 9 は、図 6 を参照しながら説明した L N A 回路の、もう 1 つのより具体的な例として実装し得る、L N A 回路 1 1 0 を示す。図 9 の例は入力が 2 つのバージョンであるが、3 つ以上の入力を実装できることができることが理解されるであろう。図 9 の例は図 7 の例に似ているが、図 9 では第 1 および第 2 の電流変換器各々が個別の加算器に結合されている。

#### 【 0 0 4 9 】

図 9において、第 1 の電流変換器 1 4 2 は、第 1 の R F 信号 ( R F i n 1 ) を第 1 の入力ノード 1 3 2 で受け第 1 の R F 信号を処理し処理された第 1 の R F 信号を加算器回路 1 4 6 によってさらに処理するために出力するように構成されていることが、示されている。同様に、第 2 の電流変換器 1 4 4 は、第 2 の R F 信号 ( R F i n 2 ) を第 2 の入力ノード 1 3 4 で受け第 2 の R F 信号を処理し処理された第 2 の R F 信号を加算器回路 1 4 6 によってさらに処理するために出力するように構成されていることが、示されている。処理された第 1 および第 2 の R F 信号を加算器回路 1 4 6 によってさらに処理することにより、出力ノード 1 3 8 で出力 R F 信号 ( R F o u t ) を与えることができる。30

#### 【 0 0 5 0 】

図 9において、第 1 の電流変換器 1 4 2 と加算器回路 1 4 6 の一部との組合せは、第 1 のカスコード増幅器として実装し得る。同様に、第 2 の電流変換器 1 4 4 と加算器回路 1 4 6 の一部との組合せは、第 2 のカスコード増幅器として実装し得る。したがって、第 1 および第 2 の電流変換器各々 ( 1 4 2 または 1 4 4 ) は、それぞれの R F 信号に対してトランスクンダクタンス増幅機能を提供することができ、加算器回路 1 4 6 のそれぞれの一部は、それぞれの R F 信号に対して電流バッファ機能を提供することができる。40

#### 【 0 0 5 1 】

図 9において、第 1 の電流変換器 1 4 2 は共通エミッタ構成の B J T Q 1 を含むことが示されている。第 1 の R F 信号 ( R F i n 1 ) は、第 1 の入力ノード 1 3 2 から D C ブロック容量 C 1 を通して Q 1 のベースに与えることができる。Q 1 からの出力は、加算器回路 1 4 6 の対応する部分に結合されたコレクタを通して与えることができる。Q 1 のエミッタはインダクタンス L 1 を通して接地に結合されている。Q 1 に対するバイアス信号 ( B i a s 1 ) は、バイアススイッチ S 1 およびベース抵抗 R 1 を通して Q 1 のベースに与えることができる。Q 1 がアクティブ状態のときはバイアススイッチ S 1 を閉じ分路スイッチ S 2 を開くことができる。Q 1 が非アクティブ状態のときはバイア50

スイッチ S 1 を開き分路スイッチ S 2 を閉じることができる。バイアススイッチ S 1 および分路スイッチ S 2 は第 1 の RF 信号 ( R F i n 1 ) の経路に直接沿っていないので、これらは第 1 の RF 信号に対する雑音をほとんどまたは全くもたらさない。

#### 【 0 0 5 2 】

図 9において、第 2 の電流変換器 1 4 4 は共通エミッタ構成の B J T Q 2 を含むことが示されている。第 2 の RF 信号 ( R F i n 2 ) は、第 2 の入力ノード 1 3 4 から DC ブロック容量 C 2 を通して Q 2 のベースに与えることができる。Q 2 からの出力は、加算器回路 1 4 6 の対応する部分に結合されたコレクタを通して与えることができる。Q 2 のエミッタはインダクタンス L 2 を通して接地に結合されている。Q 2 に対するバイアス信号 ( B i a s 2 ) は、バイアススイッチ S 3 およびベース抵抗 R 2 を通して Q 2 のベースに与えることができる。Q 2 がアクティブ状態のときはバイアススイッチ S 3 を閉じ分路スイッチ S 4 を聞くことができる。Q 2 が非アクティブ状態のときはバイアススイッチ S 3 を開き分路スイッチ S 4 を閉じることができる。バイアススイッチ S 3 および分路スイッチ S 4 は第 2 の RF 信号 ( R F i n 2 ) の経路に直接沿っていないので、これらは第 2 の RF 信号に対する雑音をほとんどまたは全くもたらさない。10

#### 【 0 0 5 3 】

図 9において、加算器回路 1 4 6 は第 1 の電流変換器 1 4 2 の B J T Q 1 に対して共通ベース構成である B J T Q 3 を含むことが示されている。Q 1 のコレクタからの出力は Q 3 のエミッタに与えられることが示されており、Q 3 からの出力はそのコレクタを通して与えられることが示されている。( Q 3 の ) コレクタは共通ノード 1 3 6 に結合されることが示されており、共通ノード 1 3 6 では、Q 3 からの処理後の信号を他方のカスコード増幅経路からの処理後の信号と合成することができる。Q 3 のベースには第 1 のバイアス電圧 V c a s 1 が与えられることが示されている。20

#### 【 0 0 5 4 】

加算器回路 1 4 6 は第 2 の電流変換器 1 4 4 の B J T Q 2 に対して共通ベース構成である B J T Q 4 をさらに含むことが示されている。Q 2 のコレクタからの出力は Q 4 のエミッタに与えられることが示されており、Q 4 からの出力はそのコレクタを通して与えられることが示されている。( Q 4 の ) コレクタは共通ノード 1 3 6 に結合されることが示されており、共通ノード 1 3 6 では、Q 4 からの処理後の信号を他方のカスコード増幅経路からの処理後の信号と合成することができる。共通ノード 1 3 6 は出力ノード 1 3 8 に結合されて出力 RF 信号 ( R F o u t ) を与えることが示されている。Q 4 のベースには第 2 のバイアス電圧 V c a s 2 が与えられることが示されている。30

#### 【 0 0 5 5 】

さまざまなレベルの他の変形を実装することもできる。たとえば、本開示の 1 つ以上の特徴を、LNA および / またはその他の増幅の応用を必要とするアーキテクチャにおいて実装することができる。別の例ではさまざまな実施例がカスコード構成との関連で説明されていが、その他の種類の増幅構成 ( プッシュプル構成等 ) を利用できることができることが理解されるであろう。さらに他の例ではさまざまな実施例が BJT との関連で説明されているが、その他の種類のトランジスタ ( 電界効果トランジスタ ( FET ) 等 ) を利用できることができ理解されるであろう。40

#### 【 0 0 5 6 】

表 1 は、一例としてのセルラー帯域 B 3 0 ( RX に対して 2 . 3 5 0 ~ 2 . 3 6 0 G H z ) および B 3 8 ( RX に対して 2 . 5 7 0 ~ 2 . 6 2 0 G H z ) をサポートするように構成された図 7 の LNA 回路のシミュレーションから得られたさまざまな性能パラメータを一覧表示している。このシミュレーションは、B 3 0 帯域に対しては周波数約 2 . 3 5 5 G H z 、B 3 8 帯域に対しては周波数約 2 . 6 G H z で実施された。

#### 【 0 0 5 7 】

## 【表1】

| モード       | 利得 (dB) | NF (dB) | S11 (dB) | S22 (dB) | 電流 (mA) |

|-----------|---------|---------|----------|----------|---------|

| B30 (非CA) | 16.8    | 2.44    | -12      | -15.2    | 3.7     |

| B38 (非CA) | 16.5    | 2.13    | -11.7    | -23      | 3.7     |

| B30 (CA)  | 16.1    | 3.02    | -15      | -17.2    | 6.3     |

| B38 (CA)  | 14.2    | 2.9     | -10.5    | -50      | 6.3     |

表1

## 【0058】

表1において、利得は、対応するRF帯経路によって与えられた総合的な利得であり、NFは、LNA回路の出力で測定された雑音指数であり（ダイプレクサ損失およびすべての整合要素からの雑音を含む）、S11は入力電圧反射係数を表わし、S22は出力電圧反射係数を表わし、電流は、対応するRF帯経路に関連する全電流である。CAモードではB30およびB38帯域の性能の劣化は相対的にほとんどないことがわかる。

## 【0059】

図10は、本明細書に記載の1つ以上の特徴を有する装置を製造するために実装し得るプロセス200を示す。ロック202で、少なくともダイプレクサ機能を有する回路を基板上に装着するまたは与えることができる。さまざまな例においてキャリアアグリゲーション(CA)はダイプレクサとの関連で説明しているが、CAを3つ以上の帯域とともに実装する（たとえばマルチプレクサを利用）ことも可能であることが理解されるであろう。ある実施形態において、ダイプレクサを装置として実装してもよく、このような装置を基板上に装着してもよい。

## 【0060】

ロック204で、低雑音増幅器(LNA)に対して複数の電流変換器を形成するまたは与えることができる。ロック206で、LNAに対して1つ以上の加算器を形成するまたは与えることができる。ロック208で、ダイプレクサ回路の出力を電流変換器に結合することができる。ロック210で、電流変換器を1つ以上の加算器に結合することができる。

## 【0061】

ある実施形態において、図10で説明した、本明細書に記載の1つ以上の特徴を有する装置は、RF用途に合わせて構成されたモジュールであってもよい。図11は、積層基板等の実装基板302を有するRFモジュール300（たとえばフロントエンドモジュール）のブロック図を示す。このようなモジュールは1つ以上のLNA回路を含み得る。ある実施形態において、このようなLNA回路は半導体チップ306上に実装してもよい。このようなチップ上に実装されたLNA回路は、本明細書に記載のCA動作を容易にするように構成し得る。このようなLNA回路は、本明細書に記載の改善されたキャリアアグリゲーション(CA)機能に関連する1つ以上の有利な特徴を提供することも可能である。

## 【0062】

モジュール300はさらに、1つ以上の半導体チップ304上に実装された複数のスイッチを含み得る。ある実施形態において、このようなスイッチはダイプレクサとLNA回路との間のRF信号経路に沿って実装されていないので、たとえば改善された雑音指数性能をもたらす。

## 【0063】

モジュール300はさらに、RF信号を処理するように構成された、1つ以上のダイプレクサおよび/または複数のフィルタ（まとめて310で示す）を含み得る。このようなダイプレクサ/フィルタは、表面実装装置(SMD)として実装してもよく、集積回路(IGC)の一部として実装してもよく、その組合せであってもよい。このようなダイプレクサ/フィルタは、たとえばSAWフィルタを含み得るまたはSAWフィルタに基づき得るものであり、高Q装置として構成し得る。

10

20

30

40

50

## 【0064】

ある実装例において、本明細書に記載の1つ以上の特徴を有するアーキテクチャ、装置、および／または回路は、無線装置等のRF装置に含まれていてもよい。このようなアーキテクチャ、装置、および／または回路は、無線装置に直接実装されてもよく、本明細書に記載の1つ以上のモジュラー形態で実装されてもよく、または、その組合せで実装されてもよい。ある実施形態において、このような無線装置は、たとえば、携帯電話、スマートフォン、電話機能付または電話機能なしのハンドヘルド無線装置、無線タブレット、無線ルータ、無線アクセスポイント、無線基地局等を含み得る。本開示の1つ以上の特徴は、無線装置との関連で説明されているが、基地局等のその他のRFシステムで実装することも可能であることが理解されるであろう。

10

## 【0065】

図12は、本明細書に記載の1つ以上の有利な特徴を有する一例としての無線装置400を概略的に示す。ある実施形態において、このような有利な特徴は、本明細書に記載のフロントエンド(FE)モジュール300において実装することができる。ある実施形態において、このようなFEMは、点線の枠によって示されるものよりも多いまたは少ない構成要素を含み得る。

## 【0066】

PAモジュール412の中の電力増幅器(PA)は、増幅および送信すべきRF信号を生成するようにかつ受信した信号を処理するように構成され動作することができるトランシーバ410から、それぞれのRF信号を受信することができる。トランシーバ410は、ユーザに適したデータおよび／または音声信号とトランシーバ410に適したRF信号との間の変換を提供するように構成されたベースバンドサブシステム408と対話することが示されている。また、トランシーバ410は、無線装置400の動作のための電力を管理するように構成された電力管理要素406に接続されていることが示されている。このような電力管理は、ベースバンドサブシステム408および無線装置400の他の構成要素の動作を制御することもできる。

20

## 【0067】

ベースバンドサブシステム408は、ユーザインターフェイス402に接続されることにより、ユーザに与えられユーザから受ける音声および／またはデータのさまざまな入力および出力を容易にすることが示されている。また、ベースバンドサブシステム408は、無線装置の動作を容易にするためにデータおよび／または命令を格納するように、および／またはユーザのための情報の記憶装置を提供するように構成されたメモリ404に接続されてもよい。

30

## 【0068】

一例としての無線装置400において、フロントエンドモジュール300は、本明細書に記載の1つ以上の機能を提供するように構成されたキャリアアグリゲーション対応の1つ以上の信号経路を含み得る。このような信号経路は、それぞれのダイブレクサを通してアンテナスイッチモジュール(ASM)414と通信することができる。ある実施形態において、アンテナ420を通して受信した信号のうちの少なくともいくつかを、本明細書に記載のやり方でASM414から1つ以上の低雑音増幅器(LNA)418にルーティングすることができる。LNA418からの増幅された信号はトランシーバ410にルーティングされることが示されている。ある実施形態において、LNA418のうちの少なくともいくつかは、本明細書に記載の1つ以上の特徴を有するLNA回路110を含み得る。

40

## 【0069】

図13は、本明細書に記載の1つ以上の有利な特徴を有する一例としての無線装置500を概略的に示す。ある実施形態において、このような有利な特徴は、本明細書に記載のフロントエンド(FE)モジュール300において実装することができる。ある実施形態において、このようなFEMは、点線の枠によって示されるものよりも多いまたは少ない構成要素を含み得る。

50

**【 0 0 7 0 】**

P A モジュール 5 1 2 の中の P A は、増幅および送信すべき R F 信号を生成するようになかつ受信した信号を処理するように構成され動作することができるトランシーバ 5 1 0 から、それぞれの R F 信号を受信することができる。トランシーバ 5 1 0 は、ユーザに適したデータおよび／または音声信号とトランシーバ 5 1 0 に適した R F 信号との間の変換を提供するように構成されたベースバンドサブシステム 5 0 8 と対話することが示されている。また、トランシーバ 5 1 0 は、無線装置 5 0 0 の動作のための電力を管理するように構成された電力管理要素 5 0 6 に接続されていることが示されている。このような電力管理は、ベースバンドサブシステム 5 0 8 および無線装置 5 0 0 の他の構成要素の動作を制御することもできる。

10

**【 0 0 7 1 】**

ベースバンドサブシステム 5 0 8 は、ユーザインターフェイス 5 0 2 に接続されることにより、ユーザに与えられユーザから受ける音声および／またはデータのさまざまな入力および出力を容易にすることが示されている。また、ベースバンドサブシステム 5 0 8 は、無線装置の動作を容易にするためにデータおよび／または命令を格納するように、および／またはユーザのための情報の記憶装置を提供するように構成されたメモリ 5 0 4 に接続されてもよい。

**【 0 0 7 2 】**

一例としての無線装置 5 0 0 において、フロントエンドモジュール 3 0 0 は、本明細書に記載の 1 つ以上の機能を提供するように構成されたキャリアアグリゲーション対応の 1 つ以上の信号経路を含み得る。このような信号経路は、それぞれのダイブレクサを通してアンテナスイッチモジュール（ A S M ） 5 2 4 と通信することができる。ある実施形態において、ダイバーシティアンテナ 5 3 0 を通して受信した信号のうちの少なくともいくつかを、本明細書に記載のやり方で A S M 5 2 4 から 1 つ以上の低雑音増幅器（ L N A ） 4 1 8 にルーティングすることができる。L N A 4 1 8 からの増幅された信号はトランシーバ 5 1 0 にルーティングされることが示されている。

20

**【 0 0 7 3 】**

いくつかのその他の無線装置構成は、本明細書に記載の 1 つ以上の特徴を利用することができます。たとえば、無線装置はマルチバンド装置である必要はない。別の例において、無線装置は、ダイバーシティアンテナ等の他のアンテナ、および、W i - F i 、B l u e t o o t h（登録商標）、および G P S 等の他の接続特徴を含み得る。

30

**【 0 0 7 4 】****ダイバーシティ受信（ D R x ）の実装に関する例**

無線装置において 1 つ以上のメインアンテナと 1 つ以上のダイバーシティアンテナを使用することにより、信号受信の品質を改善することができる。たとえば、ダイバーシティアンテナは、無線装置の近傍において R F 信号をさらにサンプリングすること可能にする。加えて、無線装置のトランシーバを、メインアンテナおよびダイバーシティアンテナが受信した信号を処理するように構成することにより、メインアンテナのみを使用する構成と比較して、より高エネルギーのおよび／または忠実度が改善された受信信号を取得することができる。

40

**【 0 0 7 5 】**

メインアンテナおよびダイバーシティアンテナが受信した信号間の相関性を減じるためおよび／またはアンテナの分離を高めるためには、無線装置内におけるメインアンテナとダイバーシティアンテナの間の物理的な距離を比較的大きくしてこれらを分離すればよい。たとえば、ダイバーシティアンテナを無線装置の上部近くに配置しメインアンテナを無線装置の下部近くに配置してもよく、または、その逆にしてもよい。

**【 0 0 7 6 】**

無線装置は、信号の送信または受信を、メインアンテナを用いて対応する信号をアンテナスイッチモジュールを通してトランシーバからまたはトランシーバにルーティングすることによって、行なうことができる。設計の規格に合うようにするまたはそれを超えるよ

50

うにするためには、トランシーバ、アンテナスイッチモジュール、および／またはメインアンテナを、無線装置内で物理的に互いに近くなるようにすればよい。無線装置をこのように構成することにより、比較的小さい信号損失、低い雑音、および／または高度な分離が得られる。

#### 【0077】

上記例において、メインアンテナがアンテナスイッチモジュールに物理的に近いということは、結果として、ダイバーシティアンテナがアンテナスイッチモジュールから相対的に遠いということになり得る。このような構成において、ダイバーシティアンテナとアンテナスイッチモジュールとの間の信号経路が比較的長いことにより、結果として、ダイバーシティアンテナを通して受信した信号に関連する多大な損失および／または損失の追加が生じ得る。したがって、本明細書に記載の1つ以上の特徴の実装を含む、ダイバーシティアンテナを通して受信した信号の処理を、ダイバーシティアンテナの近傍で行なうこと 10 は、有利となり得る。

#### 【0078】

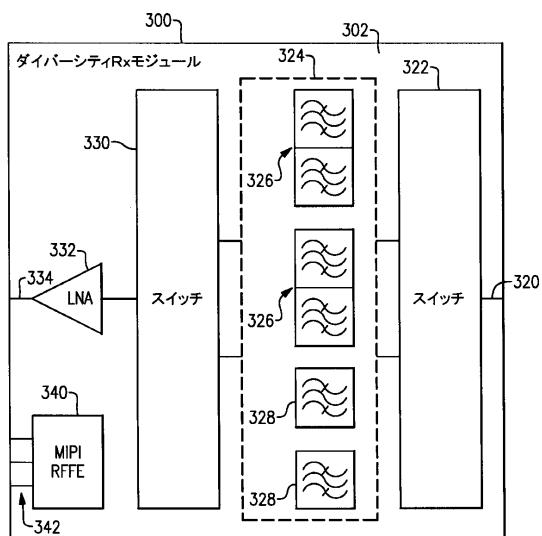

図14は、ある実施形態において本開示の1つ以上の特徴をダイバーシティ受信(DR ×)モジュール300において実装できることを示す。このようなモジュールは、複数の構成要素を支持するように、かつこのような構成要素に関連する電気的接続を与えるまたは容易にするように構成された、実装基板302(たとえば積層基板)を含み得る。

#### 【0079】

図14の例において、DR ×モジュール300は、入力320においてダイバーシティアンテナ(図14には示されていない)からのRF信号を受信しこのようなRF信号を低雑音増幅器(LNA)332にルーティングするように構成し得る。RF信号のこのようなルーティングにはキャリアアグリゲーション(CA)および／または非CA構成が関与し得ることが理解されるであろう。また、1つのLNA(たとえばプロードバンドLNA)が示されているが、DR ×モジュール300内には2つ以上のLNAがあつてもよいことが理解されるであろう。LNAの種類および動作モード(たとえばCAまたは非CA)に応じて、LNA332の出力334は、1つ以上の周波数帯に関連する1つ以上の周波数成分を含み得る。 20

#### 【0080】

ある実施形態において、入力320とLNA332との間のRF信号の上記ルーティングのうちの一部またはすべてを、入力320とダイプレクサおよび／またはフィルタのアセンブリ(まとめて324で示す)との間の1つ以上のスイッチのアセンブリ322によって、および、ダイプレクサ／フィルタアセンブリ324とLNA332との間の1つ以上のスイッチのアセンブリ330によって、容易に実現することができる。ある実施形態において、スイッチアセンブリ322、330を、たとえば1つ以上のシリコン・オン・インシュレータ(SOI)チップの上に実装することができる。ある実施形態において、入力320とLNA332との間のRF信号の上記ルーティングのうちの一部またはすべてを、スイッチアセンブリ322、330に関連するスイッチのうちのいくつかまたはすべてがなくても実現することができる。 30

#### 【0081】

図14の例において、ダイプレクサ／フィルタアセンブリ324は、一例としての2つのダイプレクサ326および2つの個別フィルタ328を含むものとして示されている。DR ×モジュール300は、より多いまたは少ない数のダイプレクサおよびより多いまたは少ない数の個別フィルタを有し得ることが理解されるであろう。このようなダイプレクサ／フィルタは、たとえば、表面実装装置(SMD)として実装してもよく、集積回路(IC)の一部として実装してもよく、その組合せであつてもよい。このようなダイプレクサ／フィルタは、たとえばSAWフィルタを含み得るまたはSAWフィルタに基づき得るものであり、高Q装置として構成し得る。 40

#### 【0082】

ある実施形態において、DR ×モジュール300は、スイッチアセンブリ322、33

10

20

30

40

50

0およびLNA332のうちのいくつかまたはすべてに関連する制御機能を提供するようによび／または容易にするように構成された、MIPIMIFFEインターフェイス340等の制御要素を含み得る。このような制御インターフェイスは1つ以上のI/O信号342に対して動作するように構成し得る。

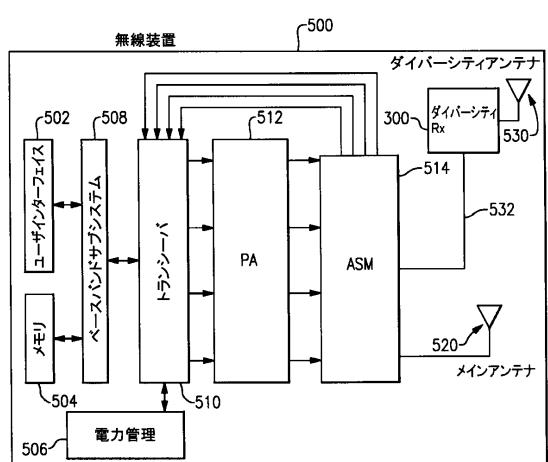

#### 【0083】

図15は、ある実施形態において、本明細書に記載の1つ以上の特徴を有するDRxモジュール300（たとえば図14のDRxモジュール300）を、無線装置500等のRF装置に含めることができることを示す。このような無線装置において、ユーザインターフェイス502、メモリ504、電力管理506、ベースバンドサブシステム508、トランシーバ510、電力増幅器（PA）512、アンテナスイッチモジュール（ASM）514、およびアンテナ520等の構成要素は、図12および図13の例と概ね同様であつてもよい。10

#### 【0084】

ある実施形態において、DRxモジュール300は、1つ以上のダイバーシティアンテナとASM514との間に実装し得る。このような構成によって、ダイバーシティアンテナ530を通して受信したRF信号を、ダイバーシティアンテナ530からのRF信号に対して雑音の損失がほとんどまたは全くない状態で、および／または雑音の追加がほとんどまたは全くない状態で、処理する（ある実施形態ではLNAによる増幅を含む）ことができる。次に、DRxモジュール300からの、このような処理された信号を、比較的損失が大きい可能性がある1つ以上の信号経路532を通してASMにルーティングすることができる。20

#### 【0085】

図15の例において、DRxモジュール300からのRF信号を、1つ以上の受信（Rx）経路を通しASM514を通してトランシーバ510にルーティングすることができる。このようなRx経路のうちのいくつかまたはすべてはそれぞれのLNAを含み得る。ある実施形態において、DRxモジュール300からのRF信号は、このようなLNAを用いてさらに増幅しても増幅しなくてもよい。

#### 【0086】

本開示の1つ以上の特徴は、本明細書に記載のさまざまなセルラー周波数帯とともに実装することができる。このような帯域の例を表2に示す。この帯域のうちの少なくともいくつかはサブ帯域に分割できることが理解されるであろう。また、本開示の1つ以上の特徴を表2の例のような呼称がない周波数帯とともに実装し得ることも理解されるであろう。30

#### 【0087】

【表2】

| 帯域  | モード | Tx 周波数範囲 (MHz)    | Rx 周波数範囲 (MHz)    |

|-----|-----|-------------------|-------------------|

| B1  | FDD | 1,920 - 1,980     | 2,110 - 2,170     |

| B2  | FDD | 1,850 - 1,910     | 1,930 - 1,990     |

| B3  | FDD | 1,710 - 1,785     | 1,805 - 1,880     |

| B4  | FDD | 1,710 - 1,755     | 2,110 - 2,155     |

| B5  | FDD | 824 - 849         | 869 - 894         |

| B6  | FDD | 830 - 840         | 875 - 885         |

| B7  | FDD | 2,500 - 2,570     | 2,620 - 2,690     |

| B8  | FDD | 880 - 915         | 925 - 960         |

| B9  | FDD | 1,749.9 - 1,784.9 | 1,844.9 - 1,879.9 |

| B10 | FDD | 1,710 - 1,770     | 2,110 - 2,170     |

| B11 | FDD | 1,427.9 - 1,447.9 | 1,475.9 - 1,495.9 |

| B12 | FDD | 699 - 716         | 729 - 746         |

| B13 | FDD | 777 - 787         | 746 - 756         |

| B14 | FDD | 788 - 798         | 758 - 768         |

| B15 | FDD | 1,900 - 1,920     | 2,600 - 2,620     |

| B16 | FDD | 2,010 - 2,025     | 2,585 - 2,600     |

| B17 | FDD | 704 - 716         | 734 - 746         |

| B18 | FDD | 815 - 830         | 860 - 875         |

| B19 | FDD | 830 - 845         | 875 - 890         |

| B20 | FDD | 832 - 862         | 791 - 821         |

| B21 | FDD | 1,447.9 - 1,462.9 | 1,495.9 - 1,510.9 |

| B22 | FDD | 3,410 - 3,490     | 3,510 - 3,590     |

| B23 | FDD | 2,000 - 2,020     | 2,180 - 2,200     |

| B24 | FDD | 1,626.5 - 1,660.5 | 1,525 - 1,559     |

| B25 | FDD | 1,850 - 1,915     | 1,930 - 1,995     |

| B26 | FDD | 814 - 849         | 859 - 894         |

| B27 | FDD | 807 - 824         | 852 - 869         |

| B28 | FDD | 703 - 748         | 758 - 803         |

| B29 | FDD | N/A               | 716 - 728         |

| B30 | FDD | 2,305 - 2,315     | 2,350 - 2,360     |

| B31 | FDD | 452.5 - 457.5     | 462.5 - 467.5     |

| B33 | TDD | 1,900 - 1,920     | 1,900 - 1,920     |

| B34 | TDD | 2,010 - 2,025     | 2,010 - 2,025     |

| B35 | TDD | 1,850 - 1,910     | 1,850 - 1,910     |

| B36 | TDD | 1,930 - 1,990     | 1,930 - 1,990     |

| B37 | TDD | 1,910 - 1,930     | 1,910 - 1,930     |

| B38 | TDD | 2,570 - 2,620     | 2,570 - 2,620     |

| B39 | TDD | 1,880 - 1,920     | 1,880 - 1,920     |

| B40 | TDD | 2,300 - 2,400     | 2,300 - 2,400     |

| B41 | TDD | 2,496 - 2,690     | 2,496 - 2,690     |

| B42 | TDD | 3,400 - 3,600     | 3,400 - 3,600     |

| B43 | TDD | 3,600 - 3,800     | 3,600 - 3,800     |

| B44 | TDD | 703 - 803         | 703 - 803         |

表2

## 【0088】

説明上「マルチプレクサ」、「多重化」等が「ダイプレクサ」、「二重化」等を含み得ることが理解されるであろう。

## 【0089】

本明細書および請求項を通して、文脈上明らかに別段の要求がない限り、「含む／備え

10

20

30

40

50

る」等の単語は、排他的または網羅的な意味ではなく、包括的な意味、すなわち「含むがそれに限定されない」という意味で解釈されるべきものである。本明細書において一般的に使用されている「結合される」という単語は、直接接続し得るまたは1つ以上の中間素子を介して接続し得る2つ以上の素子に関連する。加えて、「本明細書において」、「上記」、「下記」という単語および同様の意味を有する単語は、本願で使用される場合、この出願全体に関連しこの出願のある特定の部分に関連しているのではない。文脈上認められる場合、上記詳細な説明の中の、単数形または複数形の単語はそれぞれ、複数形または単数形を含み得る。2つ以上の項目を列挙した場合の「または」という単語は、この単語の解釈、すなわち、列挙された項目のうちのいずれか、列挙された項目すべて、および、列挙された項目の任意の組合せ、という解釈をすべてカバーする。

10

#### 【0090】

本発明の実施形態の上記詳細な説明は、網羅的であることまたは本発明を上記開示された形態そのものに限定することを意図していない。本発明の具体的な実施形態および本発明の例は例示を目的として記載されているが、均等であるさまざまな修正が本発明の範囲の中で可能であることを当業者は理解するであろう。たとえば、プロセスまたはブロックは所与の順序で示されているが、代替の実施形態は、他の順序のステップを有するルーチンを実行し得る、または、他の順序のブロックを有するシステムを採用し得る。また、いくつかのプロセスまたはブロックを、削除、移動、追加、細分、結合、および／または修正してもよい。これらプロセスまたはブロックは各々、さまざまな他の方法で実装してもよい。また、プロセスまたはブロックは連続して実行されるものとして示されている場合があるが、これらプロセスもしくはブロックは、その代わりに並列に実行されてもよく、または、異なる時間に実行されてもよい。

20

#### 【0091】

本明細書において与えられている本発明の教示は、上記システムに限らずその他のシステムに応用できる。上記さまざまな実施形態の要素および機能を組合せてさらに他の実施形態を提供することができる。

#### 【0092】

発明のいくつかの実施形態について説明してきたが、これら実施形態は、専ら例示のために示しているのであって、本開示の範囲を限定する意図がある訳ではない。実際、本明細書に記載の新規な方法およびシステムは、他のさまざまな形態で実施し得る。さらに、本明細書に記載の方法およびシステムの形態における、さまざまな省略、代用、および変更は、本開示の精神から逸脱することなく行ない得る。以下の請求項およびそれらの均等物は、本開示の範囲および精神に含まれる形態または修正をカバーすることを意図している。

30

【図1】

【図3】

【図2】

【図4】

【図5】

【図6】

【図7】

【図8】

FIG.8

【図9】

FIG.9

【図10】

FIG.10

【図11】

FIG.11

【図12】

FIG.12

【図13】

FIG.13

【図14】

FIG.14

【図15】

FIG.15

---

フロントページの続き

審査官 高野 洋

(56)参考文献 米国特許出願公開第2004/0232993(US,A1)

特表2003-529265(JP,A)

米国特許出願公開第2005/0231290(US,A1)

特開2010-233023(JP,A)

米国特許出願公開第2013/0315348(US,A1)

(58)調査した分野(Int.Cl., DB名)

H04B 1/18

H03F 1/00 - 3/45

3/50 - 3/52

3/62 - 3/64

3/68 - 3/72

H03H 3/08 - 3/10

9/145

9/25

9/42 - 9/44

9/64

9/68

9/72

9/76

H04B 1/18 - 1/24

1/38 - 1/58

7/02 - 7/12

H04L 1/02 - 1/06