(19)日本国特許庁(JP)

## (12)特許公報(B2)

(11)特許番号

特許第7246552号

(P7246552)

(45)発行日 令和5年3月27日(2023.3.27)

(24)登録日 令和5年3月16日(2023.3.16)

(51)国際特許分類

|         |                 |         |        |         |

|---------|-----------------|---------|--------|---------|

| G 0 9 F | 9/30 (2006.01)  | G 0 9 F | 9/30   | 3 3 8   |

| G 0 9 G | 3/20 (2006.01)  | G 0 9 F | 9/30   | 3 6 5   |

| G 0 9 G | 3/3233(2016.01) | G 0 9 G | 3/20   | 6 2 4 B |

| H 1 0 K | 59/12 (2023.01) | G 0 9 G | 3/20   | 6 1 1 H |

| H 0 5 B | 33/02 (2006.01) | G 0 9 G | 3/3233 |         |

F I

請求項の数 4 (全35頁) 最終頁に続く

(21)出願番号 特願2022-92286(P2022-92286)

(22)出願日 令和4年6月7日(2022.6.7)

(62)分割の表示 特願2021-145443(P2021-145443)

)の分割

原出願日 平成24年7月12日(2012.7.12)

(65)公開番号 特開2022-126699(P2022-126699)

A)

(43)公開日 令和4年8月30日(2022.8.30)

審査請求日 令和4年6月16日(2022.6.16)

(31)優先権主張番号 特願2011-161103(P2011-161103)

(32)優先日 平成23年7月22日(2011.7.22)

(33)優先権主張国・地域又は機関

日本国(JP)

(31)優先権主張番号 特願2011-259828(P2011-259828)

(32)優先日 平成23年11月29日(2011.11.29)

最終頁に続く

(73)特許権者 000153878

株式会社半導体エネルギー研究所

神奈川県厚木市長谷398番地

(72)発明者 井上 聖子

神奈川県厚木市長谷398番地 株式会

社半導体エネルギー研究所内

三宅 博之

神奈川県厚木市長谷398番地 株式会

社半導体エネルギー研究所内

審査官 小野 博之

最終頁に続く

(54)【発明の名称】 発光装置

## (57)【特許請求の範囲】

## 【請求項1】

半導体膜と、第1の導電膜と、第2の導電膜と、第3の導電膜と、第4の導電膜と、発光素子の画素電極と、を有し、

前記半導体膜は、第1のトランジスタのチャネル形成領域、第2のトランジスタのチャネル形成領域、不純物領域、及び、容量素子の一方の電極としての機能を有する第1の領域を有し、

前記不純物領域は、前記第1のトランジスタのソース又はドレインの一方としての機能を有し、かつ、前記第2のトランジスタのソース又はドレインの一方としての機能を有し、

前記第1の導電膜は、前記第1のトランジスタのゲートとしての機能を有し、かつ、前記半導体膜の上方に位置し、

前記第2の導電膜は、前記第2のトランジスタのゲートとしての機能を有し、かつ、前記半導体膜の上方に位置し、

前記容量素子の他方の電極としての機能を有する前記第4の導電膜は、前記第1の領域の上方に位置し、

前記第1のトランジスタのソース又はドレインの一方及び前記第2のトランジスタのソース又はドレインの一方は、前記容量素子の一方の電極と電気的に接続され、

前記第3の導電膜は、前記第2のトランジスタのソース又はドレインの他方、及び前記画素電極と電気的に接続され、

平面視において、前記第1の導電膜、前記第2の導電膜、及び前記第4の導電膜は、互

いに重なりを有さず、

前記半導体膜は、前記第1のトランジスタのチャネル形成領域において折れ曲がった形状を有し、

前記第1のトランジスタは、前記発光素子への電流の供給を制御する機能を有する発光装置。

【請求項2】

半導体膜と、第1の導電膜と、第2の導電膜と、第3の導電膜と、第4の導電膜と、発光素子の画素電極と、を有し、

前記半導体膜は、第1のトランジスタのチャネル形成領域、第2のトランジスタのチャネル形成領域、不純物領域、及び、容量素子の一方の電極としての機能を有する第1の領域を有し、

前記不純物領域は、前記第1のトランジスタのソース又はドレインの一方としての機能を有し、かつ、前記第2のトランジスタのソース又はドレインの一方としての機能を有し、

前記第1の導電膜は、前記第1のトランジスタのゲートとしての機能を有し、かつ、前記半導体膜の上方に位置し、

前記第2の導電膜は、前記第2のトランジスタのゲートとしての機能を有し、かつ、前記半導体膜の上方に位置し、

前記容量素子の他方の電極としての機能を有する前記第4の導電膜は、前記第1の領域の上方に位置し、

前記第1のトランジスタのソース又はドレインの一方及び前記第2のトランジスタのソース又はドレインの一方は、前記容量素子の一方の電極と電気的に接続され、

前記第1のトランジスタのソース又はドレインの他方は、電位を供給する機能を有する配線と電気的に接続され、

前記第3の導電膜は、前記第2のトランジスタのソース又はドレインの他方、及び前記画素電極と電気的に接続され、

平面視において、前記第1の導電膜、前記第2の導電膜、及び前記第4の導電膜は、互いに重なりを有さず、

前記半導体膜は、前記第1のトランジスタのチャネル形成領域において折れ曲がった形状を有し、

前記第1のトランジスタは、前記発光素子への電流の供給を制御する機能を有する発光装置。

【請求項3】

半導体膜と、第1の導電膜と、第2の導電膜と、第3の導電膜と、第4の導電膜と、発光素子の画素電極と、を有し、

前記半導体膜は、第1のトランジスタのチャネル形成領域、第2のトランジスタのチャネル形成領域、不純物領域、及び、容量素子の一方の電極としての機能を有する第1の領域を有し、

前記不純物領域は、前記第1のトランジスタのソース又はドレインの一方としての機能を有し、かつ、前記第2のトランジスタのソース又はドレインの一方としての機能を有し、

前記第1の導電膜は、前記第1のトランジスタのゲートとしての機能を有し、かつ、前記半導体膜の上方に位置し、

前記第2の導電膜は、前記第2のトランジスタのゲートとしての機能を有し、かつ、前記半導体膜の上方に位置し、

前記容量素子の他方の電極としての機能を有する前記第4の導電膜は、前記第1の領域の上方に位置し、

前記第1のトランジスタのソース又はドレインの一方及び前記第2のトランジスタのソース又はドレインの一方は、前記容量素子の一方の電極と電気的に接続され、

前記第3の導電膜は、前記第2のトランジスタのソース又はドレインの他方、及び前記画素電極と電気的に接続され、

平面視において、前記第1の導電膜、前記第3の導電膜、及び前記第4の導電膜は、互

10

20

30

40

50

いに重なりを有さず、

前記半導体膜は、前記第1のトランジスタのチャネル形成領域において折れ曲がった形状を有し、

前記第1のトランジスタは、前記発光素子への電流の供給を制御する機能を有する発光装置。

【請求項4】

半導体膜と、第1の導電膜と、第2の導電膜と、第3の導電膜と、第4の導電膜と、発光素子の画素電極と、を有し、

前記半導体膜は、第1のトランジスタのチャネル形成領域、第2のトランジスタのチャネル形成領域、不純物領域、及び、容量素子の一方の電極としての機能を有する第1の領域を有し、

10

前記不純物領域は、前記第1のトランジスタのソース又はドレインの一方としての機能を有し、かつ、前記第2のトランジスタのソース又はドレインの一方としての機能を有し、

前記第1の導電膜は、前記第1のトランジスタのゲートとしての機能を有し、かつ、前記半導体膜の上方に位置し、

前記第2の導電膜は、前記第2のトランジスタのゲートとしての機能を有し、かつ、前記半導体膜の上方に位置し、

前記容量素子の他方の電極としての機能を有する前記第4の導電膜は、前記第1の領域の上方に位置し、

前記第1のトランジスタのソース又はドレインの一方及び前記第2のトランジスタのソース又はドレインの一方は、前記容量素子の一方の電極と電気的に接続され、

20

前記第1のトランジスタのソース又はドレインの他方は、電位を供給する機能を有する配線と電気的に接続され、

前記第3の導電膜は、前記第2のトランジスタのソース又はドレインの他方、及び前記画素電極と電気的に接続され、

平面視において、前記第1の導電膜、前記第3の導電膜、及び前記第4の導電膜は、互いに重なりを有さず、

前記半導体膜は、前記第1のトランジスタのチャネル形成領域において折れ曲がった形状を有し、

前記第1のトランジスタは、前記発光素子への電流の供給を制御する機能を有する発光装置。

30

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、トランジスタが各画素に設けられた発光装置に関する。

【背景技術】

【0002】

発光素子を用いた表示装置は視認性が高く、薄型化に最適であると共に、視野角にも制限が無いため、C R T (c a t h o d e r a y t u b e) や液晶表示装置に替わる表示装置として注目されている。発光素子を用いたアクティブマトリクス型の表示装置は、具体的に提案されている構成がメーカーによって異なるが、通常、少なくとも発光素子と、画素へのビデオ信号の入力を制御するトランジスタ(スイッチング用トランジスタ)と、当該発光素子に供給する電流値を制御するトランジスタ(駆動用トランジスタ)とが、各画素に設けられている。

40

【0003】

画素に設ける上記トランジスタをすべて同じ極性とすることで、トランジスタの作製工程において、半導体膜に一導電性を付与する不純物元素の添加などの工程を、一部省略することができる。下記の特許文献1には、nチャネル型トランジスタのみで画素が構成されている発光素子型ディスプレイについて、記載されている。

【先行技術文献】

50

**【特許文献】****【0004】**

【文献】特開2003-195810号公報

**【発明の概要】****【発明が解決しようとする課題】****【0005】**

ところで、発光装置では、駆動用トランジスタのドレイン電流が発光素子に供給されるため、画素間において駆動用トランジスタの閾値電圧にばらつきが生じると、発光素子の輝度にもそのばらつきが反映されてしまう。従って、閾値電圧のばらつきを見越して駆動用トランジスタの電流値を補正することができる画素構成の提案は、発光装置の画質向上を図る上で、重要な課題である。

10

**【0006】**

また、一般的に、発光素子の陽極として用いる導電膜は、発光素子の陰極として用いる導電膜よりも、大気中においてその表面が酸化されにくい。なおかつ、発光素子の陽極として用いる導電膜は、通常、スパッタリング法を用いて形成されるため、発光材料を含むEL層上に陽極を形成すると、スパッタダメージによりEL層が損傷を受けやすい。よって、陽極、EL層、陰極の順に積層された構造を有する発光素子は、作製プロセスも簡易であり、高い発光効率が得られやすい。しかし、上記構造の発光素子にnチャネル型の駆動用トランジスタを組み合わせる場合、駆動用トランジスタのソースが発光素子の陽極に接続される。よって、発光材料の劣化に伴って、発光素子の陽極と陰極間の電圧が増加すると、駆動用トランジスタにおいてソースの電位が上昇し、ゲートとソース間の電圧（ゲート電圧）が小さくなる。そのため、駆動用トランジスタのドレイン電流、すなわち、発光素子に供給される電流が小さくなり、発光素子の輝度が低下する。

20

**【0007】**

上述したような技術的背景のもと、本発明は、駆動用トランジスタの閾値電圧のばらつきによる画素間の輝度のばらつきが抑えられる、発光装置の提供を課題の一つとする。或いは、本発明は、EL層の劣化により、発光素子の輝度が低下するのを抑制できる発光装置の提供を、課題の一つとする。

**【課題を解決するための手段】****【0008】**

30

本発明の発光装置の一態様は、トランジスタと、第1の配線と、第2の配線と、第1のスイッチと、第2のスイッチと、第3のスイッチと、第4のスイッチと、容量素子と、発光素子とを、少なくとも有する。第1のスイッチは、第1の配線と容量素子の一対の電極のうちの一方との間の導通または非導通を選択する機能を有する。容量素子の一対の電極のうちの他方は、トランジスタのソース及びドレインの一方に接続される。第2のスイッチは、第2の配線と、トランジスタのゲートとの間の導通または非導通を選択する機能を有する。第3のスイッチは、容量素子の一対の電極のうちの一方と、トランジスタのゲートとの間の導通または非導通を選択する機能を有する。第4のスイッチは、トランジスタのソース及びドレインの一方と、発光素子の陽極との間の導通または非導通を選択する機能を有する。

40

**【0009】**

或いは、本発明の発光装置の一態様は、トランジスタと、第1の配線と、第2の配線と、第3の配線と、第1のスイッチと、第2のスイッチと、第3のスイッチと、第4のスイッチと、容量素子と、発光素子とを、少なくとも有する。第1のスイッチは、第1の配線と容量素子の一対の電極のうちの一方との間の導通または非導通を選択する機能を有する。容量素子の一対の電極のうちの他方は、トランジスタのソース及びドレインの一方及び発光素子の陽極に接続される。第2のスイッチは、第2の配線と、トランジスタのゲートとの間の導通または非導通を選択する機能を有する。第3のスイッチは、容量素子の一対の電極のうちの一方と、トランジスタのゲートとの間の導通または非導通を選択する機能を有する。第4のスイッチは、トランジスタのソース及びドレインの一方と、第3の配線と

50

の間の導通または非導通を選択する機能を有する。

【0010】

なお、上記スイッチは、電流または電位の供給を制御する機能を有する素子であり、例えば、電気的スイッチまたは機械的なスイッチなどを用いることができる。具体的には、トランジスタ、ダイオードなどで構成すればよい。また、スイッチはトランジスタを組み合わせた論理回路でもよい。

【0011】

本発明の一態様に係る発光装置では、上記構成により、駆動用トランジスタの閾値電圧よりも高く、なおかつ、駆動用トランジスタのソースとドレイン間の電圧に上記閾値電圧を加算することで得られる電圧よりも低い電圧を、駆動用トランジスタのゲートとソース間に印加することができる。上記電圧を印加した状態で、駆動用トランジスタのソースをフローティング（浮遊状態）とすることで、駆動用トランジスタのゲートとソースの間に閾値電圧を取得することができる。そして、ソースをフローティング（浮遊状態）としたまま、ゲートに画像信号の電圧を与えると、駆動用トランジスタのゲートとソース間に、画像信号の電圧に閾値電圧を加算した電圧が与えられる。発光素子は、駆動用トランジスタのゲート電圧に見合った値の電流が供給され、階調の表示を行う。

10

【発明の効果】

【0012】

本発明の一態様に係る発光装置では、画像信号の電圧に、トランジスタの閾値電圧を加算することで得られる電位を、トランジスタのゲート電極に与えることができる。よって、閾値電圧の補正と、陽極の電位の補正とを行うことで、発光装置の画質の向上を実現できる。

20

【図面の簡単な説明】

【0013】

【図1】画素の回路図。

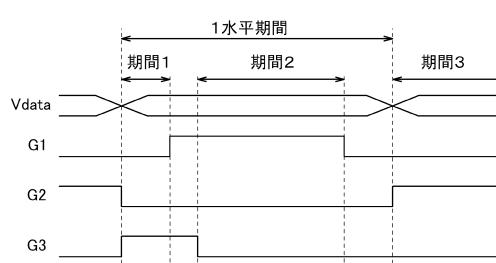

【図2】画素の動作を示すタイミングチャート。

【図3】画素の動作を示す図。

【図4】画素の動作を示すタイミングチャート。

【図5】画素の動作を示す図。

30

【図6】画素の上面図。

【図7】画素の断面図。

【図8】画素の上面図。

【図9】画素の断面図。

【図10】画素の断面図。

【図11】画素の断面図。

【図12】パネルの斜視図。

【図13】電子機器の図。

【図14】酸化物半導体の構造を説明する図。

【図15】酸化物半導体の構造を説明する図。

【図16】酸化物半導体の構造を説明する図。

40

【図17】シミュレーションの結果を示す図。

【図18】シミュレーションの結果を示す図。

【発明を実施するための形態】

【0014】

以下では、本発明の実施の形態について図面を用いて詳細に説明する。ただし、本発明は以下の説明に限定されず、本発明の趣旨及びその範囲から逸脱することなくその形態及び詳細を様々に変更し得ることは、当業者であれば容易に理解される。したがって、本発明は、以下に示す実施の形態の記載内容に限定して解釈されるものではない。

【0015】

なお、本明細書において発光装置とは、発光素子が各画素に形成されたパネルと、該パネ

50

ルにコントローラを含むIC等を実装した状態にあるモジュールとを、その範疇に含む。

【0016】

(実施の形態1)

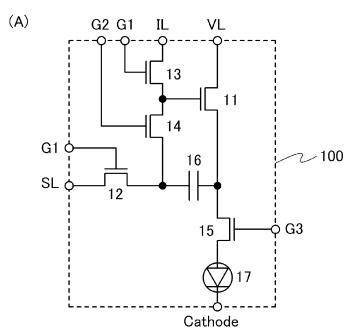

図1(A)に、本発明の一態様に係る発光装置が有する、画素100の構成を一例として示す。

【0017】

画素100は、トランジスタ11乃至トランジスタ15と、容量素子16と、発光素子17とを有する。なお、図1(A)では、トランジスタ11乃至トランジスタ15がnチャネル型である場合を例示している。

【0018】

トランジスタ12は、配線SLと、容量素子16の一対の電極のうちの一方との間の導通または非導通を選択する機能を有する。容量素子16の一対の電極のうちの他方は、トランジスタ11のソース及びドレインの一方に接続される。トランジスタ13は、配線ILと、トランジスタ11のゲートとの間の導通または非導通を選択する機能を有する。トランジスタ14は、容量素子16の一対の電極のうちの一方と、トランジスタ11のゲートとの間の導通または非導通を選択する機能を有する。トランジスタ15は、トランジスタ11のソース及びドレインの一方と、発光素子17の陽極との間の導通または非導通を選択する機能を有する。

【0019】

さらに、図1(A)では、トランジスタ11のソース及びドレインの他方は配線VLに接続されている。

【0020】

また、トランジスタ12における導通または非導通の選択は、トランジスタ12のゲートに接続された配線G1の電位により定まる。トランジスタ13における導通または非導通の選択は、トランジスタ13のゲートに接続された配線G1の電位により定まる。トランジスタ14における導通または非導通の選択は、トランジスタ14のゲートに接続された配線G2の電位により定まる。トランジスタ15における導通または非導通の選択は、トランジスタ15のゲートに接続された配線G3の電位により定まる。

【0021】

なお、本明細書において接続とは電気的な接続を意味しており、電流、電圧又は電位が、供給可能、或いは伝送可能な状態に相当する。従って、接続している状態とは、直接接続している状態を必ずしも指すわけではなく、電流、電圧又は電位が、供給可能、或いは伝送可能であるように、配線、導電膜、抵抗、ダイオード、トランジスタなどの素子を介して間接的に接続している状態も、その範疇に含む。

【0022】

また、回路図上は独立している構成要素どうしが接続されている場合であっても、実際には、例えば配線の一部が電極として機能する場合など、一の導電膜が、複数の構成要素の機能を併せ持っている場合もある。本明細書において接続とは、このような、一の導電膜が、複数の構成要素の機能を併せ持っている場合も、その範疇に含める。

【0023】

発光素子17は、陽極と、陰極と、陽極と陰極の間に設けられたEL層とを有する。EL層は、単層または複数の層で構成されていて、これらの層の中に、発光性の物質を含む発光層を少なくとも含んでいる。EL層は、陰極を基準としたときの、陰極と陽極間の電位差が、発光素子17の閾値電圧Vth以上になったときに供給される電流により、エレクトロルミネッセンスが得られる。エレクトロルミネッセンスには、一重項励起状態から基底状態に戻る際の発光(蛍光)と三重項励起状態から基底状態に戻る際の発光(リン光)とが含まれる。

【0024】

なお、トランジスタが有するソースとドレインは、トランジスタの極性及びソースとドレインに与えられる電位の高低によって、その呼び方が入れ替わる。一般的に、nチャネル

10

20

30

40

50

型トランジスタでは、ソースとドレインのうち、低い電位が与えられる方がソースと呼ばれ、高い電位が与えられる方がドレインと呼ばれる。また、pチャネル型トランジスタでは、ソースとドレインのうち、低い電位が与えられる方がドレインと呼ばれ、高い電位が与えられる方がソースと呼ばれる。本明細書では、便宜上、ソースとドレインとが固定されているものと仮定して、トランジスタの接続関係を説明する場合があるが、実際には上記電位の関係に従ってソースとドレインの呼び方が入れ替わる。

【0025】

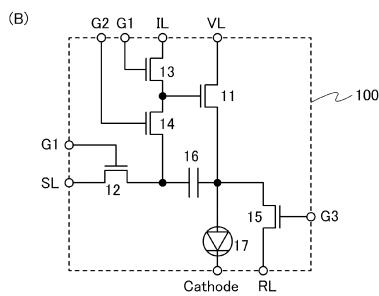

次いで、図1(B)に、本発明の一態様に係る発光装置が有する、画素100の別の一例を示す。

【0026】

画素100は、トランジスタ11乃至トランジスタ15と、容量素子16と、発光素子17とを有する。なお、図1(B)では、トランジスタ11乃至トランジスタ15がnチャネル型である場合を例示している。

10

【0027】

トランジスタ12は、配線SLと、容量素子16の一対の電極のうちの一方との間の導通または非導通を選択する機能を有する。容量素子16の一対の電極のうちの他方は、トランジスタ11のソース及びドレインの一方及び発光素子17の陽極に接続される。トランジスタ13は、配線ILと、トランジスタ11のゲートとの間の導通または非導通を選択する機能を有する。トランジスタ14は、容量素子16の一対の電極のうちの一方と、トランジスタ11のゲートとの間の導通または非導通を選択する機能を有する。トランジスタ15は、トランジスタ11のソース及びドレインの一方及び発光素子17の陽極と、配線RLとの間の導通または非導通を選択する機能を有する。また、トランジスタ11のソース及びドレインの他方は配線VLに接続されている。

20

【0028】

また、トランジスタ12における導通または非導通の選択は、トランジスタ12のゲートに接続された配線G1の電位により定まる。トランジスタ13における導通または非導通の選択は、トランジスタ13のゲートに接続された配線G1の電位により定まる。トランジスタ14における導通または非導通の選択は、トランジスタ14のゲートに接続された配線G2の電位により定まる。トランジスタ15における導通または非導通の選択は、トランジスタ15のゲートに接続された配線G3の電位により定まる。

30

【0029】

なお、図1(A)及び図1(B)において、トランジスタ11乃至トランジスタ15は、ゲートを半導体膜の片側において少なくとも有していれば良いが、半導体膜を間に挟んで存在する一対のゲートを有していても良い。一対のゲートの一方をフロントゲート、他方をバックゲートとすると、バックゲートはフローティングの状態であっても良いし、電位が他から与えられている状態であっても良い。後者の場合、フロントゲート及びバックゲートに同じ高さの電位が与えられていても良いし、バックゲートにのみ接地電位などの固定の電位が与えられていても良い。バックゲートに与える電位の高さを制御することで、トランジスタの閾値電圧を制御することができる。また、バックゲートを設けることで、チャネル形成領域が増え、ドレイン電流の増加を実現することができる。また、バックゲートを設けることで、半導体膜に空乏層ができやすくなるため、S値の改善を図ることができる。

40

【0030】

また、図1(A)及び図1(B)では、トランジスタ11乃至トランジスタ15が全てnチャネル型である場合を例示している。トランジスタ11乃至トランジスタ15が全て同じ極性である場合、トランジスタの作製工程において、半導体膜に一導電性を付与する不純物元素の添加などの工程を、一部省略することができる。ただし、本発明の一態様に係る発光装置では、必ずしもトランジスタ11乃至トランジスタ15が全てnチャネル型である必要はない。発光素子17の陽極がトランジスタ15のソース及びドレインの一方に接続されている場合、少なくともトランジスタ11はnチャネル型であることが望ましく

50

、発光素子 17 の陰極がトランジスタ 15 のソース及びドレインの一方に接続されている場合、少なくともトランジスタ 11 は p チャネル型であることが望ましい。

【 0 0 3 1 】

また、電流を流すときにトランジスタ 11 を飽和領域で動作させる場合、チャネル長またはチャネル幅を、トランジスタ 12 乃至トランジスタ 15 よりも長くすることが望ましい。チャネル長またはチャネル幅を長くすることにより、飽和領域での特性がフラットになり、キンク効果を低減することができる。或いは、チャネル長またはチャネル幅を長くすることにより、トランジスタ 11 は、飽和領域においても、多くの電流を流すことができる。

【 0 0 3 2 】

また、図 1 (A) 及び図 1 (B) では、トランジスタ 11 乃至トランジスタ 15 が、単数のゲートを有することで、単数のチャネル形成領域を有するシングルゲート構造である場合を例示しているが、本発明はこの構成に限定されない。トランジスタ 11 乃至トランジスタ 15 のいずれかまたは全てが、電気的に接続された複数のゲートを有することで、複数のチャネル形成領域を有する、マルチゲート構造であっても良い。

10

【 0 0 3 3 】

次いで、図 1 (A) に示す画素 100 の動作について説明する。

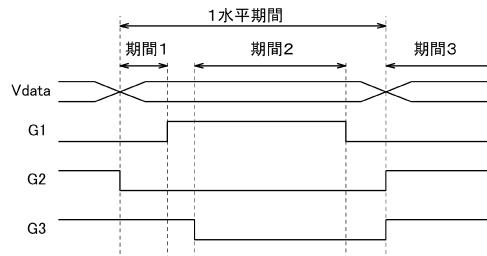

【 0 0 3 4 】

図 2 に、図 1 (A) に示す画素 100 に接続される、配線 G1 乃至配線 G3 の電位と、配線 S\_L に供給される電位 V\_d a t a とを、タイミングチャートで例示する。ただし、図 2 に示すタイミングチャートは、トランジスタ 11 乃至トランジスタ 15 が n チャネル型である場合を例示している。図 2 に示すように、図 1 (A) に示す画素 100 の動作は、主に期間 1 における第 1 の動作、期間 2 における第 2 の動作、期間 3 における第 3 の動作に分けることができる。

20

【 0 0 3 5 】

まず、期間 1 において行われる第 1 の動作について説明する。期間 1 では、配線 G1 にローレベルの電位が与えられ、配線 G2 にローレベルの電位が与えられ、配線 G3 にハイレベルの電位が与えられる。よって、トランジスタ 15 が導通状態となり、トランジスタ 12 乃至トランジスタ 14 が非導通状態となる。

【 0 0 3 6 】

30

また、配線 V\_L には電位 V\_a n o が与えられ、発光素子 17 の陰極には電位 V\_c a t が与えられる。電位 V\_a n o は、発光素子 17 の閾値電圧 V\_t h e を電位 V\_c a t に加算した電位よりも高いものとする。なお、以下、発光素子 17 の閾値電圧 V\_t h e は 0 であるものと仮定する。

【 0 0 3 7 】

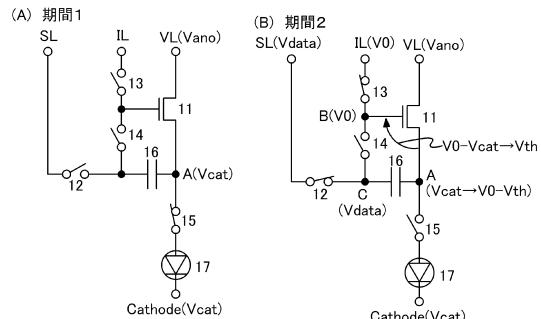

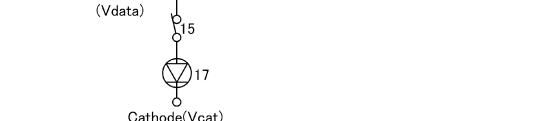

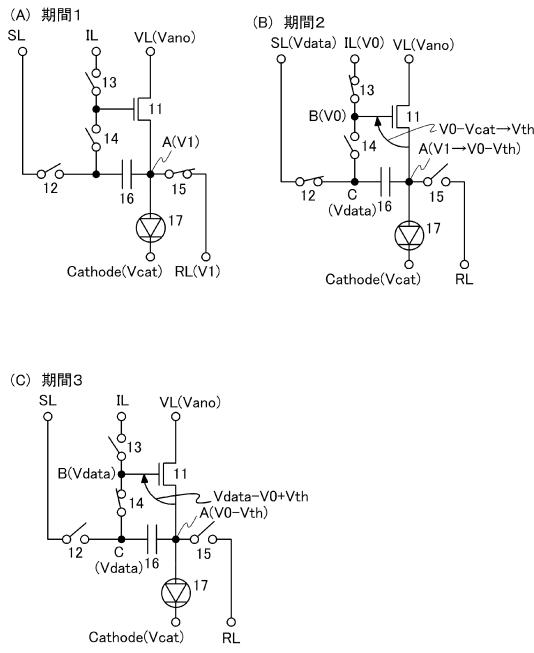

図 3 (A) に、期間 1 における画素 100 の動作を示す。なお、図 3 (A) では、トランジスタ 12 乃至トランジスタ 15 をスイッチとして表記している。期間 1 では、上記動作により、トランジスタ 11 のソース及びドレインの一方 (ノード A として図示する) が、電位 V\_c a t に発光素子 17 の閾値電圧 V\_t h e を加算した電位となる。図 3 (A) では、閾値電圧 V\_t h e が 0 であるものと仮定しているので、ノード A の電位は電位 V\_c a t となる。

40

【 0 0 3 8 】

次いで、期間 2 において行われる第 2 の動作について説明する。期間 2 では、配線 G1 にハイレベルの電位が与えられ、配線 G2 にローレベルの電位が与えられ、配線 G3 にローレベルの電位が与えられる。よって、トランジスタ 12 及びトランジスタ 13 が導通状態となり、トランジスタ 14 及びトランジスタ 15 が非導通状態となる。

【 0 0 3 9 】

なお、期間 1 から期間 2 に移行する際、配線 G1 に与える電位がローレベルからハイレベルに切り替えられてから、配線 G3 に与える電位をハイレベルからローレベルに切り替えることが望ましい。上記構成により、配線 G1 に与える電位の切り替えによって、ノード

50

Aにおける電位が変動するのを防ぐことができる。

【0040】

また、配線V<sub>L</sub>には電位V<sub>ano</sub>が与えられ、発光素子17の陰極には電位V<sub>cat</sub>が与えられる。そして、配線I<sub>L</sub>には電位V<sub>0</sub>が与えられ、配線S<sub>L</sub>には画像信号の電位V<sub>data</sub>が与えられる。なお、電位V<sub>0</sub>は、電位V<sub>cat</sub>にトランジスタ11の閾値電圧V<sub>th</sub>及び発光素子17の閾値電圧V<sub>the</sub>を加算した電位よりも高く、電位V<sub>ano</sub>にトランジスタ11の閾値電圧V<sub>th</sub>を加算した電位よりも低いことが望ましい。

【0041】

図3(B)に、期間2における画素100の動作を示す。なお、図3(B)では、トランジスタ12乃至トランジスタ15をスイッチとして表記している。期間2では、上記動作により、トランジスタ11のゲート(ノードBとして図示する)に電位V<sub>0</sub>が与えられるため、トランジスタ11が導通状態になる。よって、トランジスタ11を介して容量素子16の電荷が放出され、電位V<sub>cat</sub>だったノードAの電位が上昇を始める。そして、最終的には、ノードAの電位が電位V<sub>0</sub>-V<sub>th</sub>となると、すなわちトランジスタ11のゲート電圧が閾値電圧V<sub>th</sub>まで小さくなると、トランジスタ11が非導通状態となる。また、容量素子16の一方の電極(ノードCとして図示する)には、電位V<sub>data</sub>が与えられる。

10

【0042】

次いで、期間3において行われる第3の動作について説明する。期間3では、配線G<sub>1</sub>にローレベルの電位が与えられ、配線G<sub>2</sub>にハイレベルの電位が与えられ、配線G<sub>3</sub>にハイレベルの電位が与えられる。よって、トランジスタ14及びトランジスタ15が導通状態となり、トランジスタ12及びトランジスタ13が非導通状態となる。

20

【0043】

なお、期間2から期間3に移行する際、配線G<sub>1</sub>に与える電位がハイレベルからローレベルに切り替えられてから、配線G<sub>2</sub>及び配線G<sub>3</sub>に与える電位をローレベルからハイレベルに切り替えることが望ましい。上記構成により、配線G<sub>1</sub>に与える電位の切り替えによって、ノードAにおける電位が変動するのを防ぐことができる。

【0044】

また、配線V<sub>L</sub>には電位V<sub>ano</sub>が与えられ、発光素子17の陰極には電位V<sub>cat</sub>が与えられる。

30

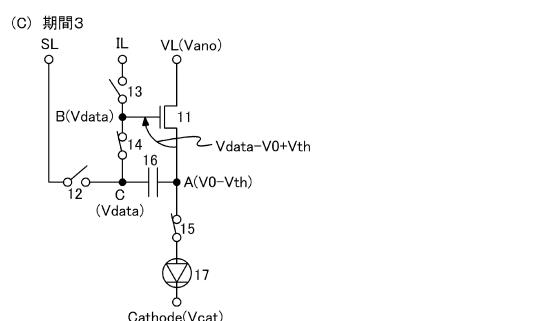

【0045】

図3(C)に、期間3における画素100の動作を示す。なお、図3(C)では、トランジスタ12乃至トランジスタ15をスイッチとして表記している。期間3では、上記動作により、ノードBに電位V<sub>data</sub>が与えられるため、トランジスタ11のゲート電圧がV<sub>data</sub>-V<sub>0</sub>+V<sub>th</sub>となる。よって、トランジスタ11のゲート電圧を、閾値電圧V<sub>th</sub>が加味された値に設定することができる。上記構成により、トランジスタ11の閾値電圧V<sub>th</sub>のばらつきが、発光素子17に供給する電流値に影響を及ぼすのを防ぐことができる。または、トランジスタ11が劣化して、閾値電圧V<sub>th</sub>が変化しても、上記変化が発光素子17に供給する電流値に影響を及ぼすのを防ぐことができる。よって、表示ムラを低減でき、高い画質の表示を行うことができる。

40

【0046】

次いで、図1(B)に示す画素100の動作について説明する。

【0047】

図4に、図1(B)に示す画素100に接続される、配線G<sub>1</sub>乃至配線G<sub>3</sub>の電位と、配線S<sub>L</sub>に供給される電位V<sub>data</sub>とを、タイミングチャートで例示する。ただし、図4に示すタイミングチャートは、トランジスタ11乃至トランジスタ15がnチャネル型である場合を例示している。図4に示すように、図1(B)に示す画素100の動作は、主に期間1における第1の動作、期間2における第2の動作、期間3における第3の動作に分けることができる。

【0048】

50

まず、期間1において行われる第1の動作について説明する。期間1では、配線G1にローレベルの電位が与えられ、配線G2にローレベルの電位が与えられ、配線G3にハイレベルの電位が与えられる。よって、トランジスタ15が導通状態となり、トランジスタ12乃至トランジスタ14が非導通状態となる。

【0049】

また、配線VLには電位Vanoが与えられ、発光素子17の陰極には電位Vcatが与えられる。電位Vanoは、上述したように、発光素子17の閾値電圧Vthを電位Vcatに加算した電位よりも高いものとする。さらに、配線RLには、電位V1が与えられる。電位V1は、電位Vcatに発光素子17の閾値電圧Vthを加算した電位よりも低いことが望ましい。電位V1を上記値に設定することで、期間1において発光素子17に電流が流れるのを防ぐことができる。

10

【0050】

図5(A)に、期間1における画素100の動作を示す。なお、図5(A)では、トランジスタ12乃至トランジスタ15をスイッチとして表記している。期間1では、上記動作により、トランジスタ11のソース及びドレインの一方(ノードAとして図示する)に、電位V1が与えられる。

【0051】

次いで、期間2において行われる第2の動作について説明する。期間2では、配線G1にハイレベルの電位が与えられ、配線G2にローレベルの電位が与えられ、配線G3にローレベルの電位が与えられる。よって、トランジスタ12及びトランジスタ13が導通状態となり、トランジスタ14及びトランジスタ15が非導通状態となる。

20

【0052】

なお、期間1から期間2に移行する際、配線G1に与える電位がローレベルからハイレベルに切り替えられてから、配線G3に与える電位をハイレベルからローレベルに切り替えることが望ましい。上記構成により、配線G1に与える電位の切り替えによって、ノードAにおける電位が変動するのを防ぐことができる。

30

【0053】

また、配線VLには電位Vanoが与えられ、発光素子17の陰極には電位Vcatが与えられる。そして、配線ILには電位V0が与えられ、配線SLには画像信号の電位Vdataが与えられる。なお、電位V0は、上述したように、電位Vcatにトランジスタ11の閾値電圧Vth及び発光素子17の閾値電圧Vthを加算した電位よりも高く、電位Vanoにトランジスタ11の閾値電圧Vthを加算した電位よりも低いことが望ましい。ただし、図1(A)に示す画素100の場合とは異なり、図1(B)に示す画素100の場合は、発光素子17の陽極と、トランジスタ11のソース及びドレインの一方とが接続されている。よって、期間2において発光素子17に供給される電流値を小さく抑えるために、図1(B)に示す画素100の場合は、図1(A)に示す画素100の場合よりも、電位V0を低い値に設定することが望ましい。

【0054】

図5(B)に、期間2における画素100の動作を示す。なお、図5(B)では、トランジスタ12乃至トランジスタ15をスイッチとして表記している。期間2では、上記動作により、トランジスタ11のゲート(ノードBとして図示する)に電位V0が与えられるため、トランジスタ11が導通状態になる。よって、トランジスタ11を介して容量素子16の電荷が放出され、電位V1だったノードAの電位が上昇を始める。そして、最終的には、ノードAの電位が電位V0-Vthになると、すなわちトランジスタ11のゲート電圧が閾値電圧Vthまで小さくなると、トランジスタ11が非導通状態となる。また、容量素子16の一方の電極(ノードCとして図示する)には、電位Vdataが与えられる。

40

【0055】

次いで、期間3において行われる第3の動作について説明する。期間3では、配線G1にローレベルの電位が与えられ、配線G2にハイレベルの電位が与えられ、配線G3にロー

50

レベルの電位が与えられる。よって、トランジスタ 14 が導通状態となり、トランジスタ 12、トランジスタ 13、及びトランジスタ 15 が非導通状態となる。

【 0 0 5 6 】

なお、期間 2 から期間 3 に移行する際、配線 G1 に与える電位がハイレベルからローレベルに切り替えられてから、配線 G2 に与える電位をローレベルからハイレベルに切り替えることが望ましい。上記構成により、配線 G1 に与える電位の切り替えによって、ノード A における電位が変動するのを防ぐことができる。

【 0 0 5 7 】

また、配線 V<sub>L</sub> には電位 V<sub>an0</sub> が与えられ、発光素子 17 の陰極には電位 V<sub>cat</sub> が与えられる。

10

【 0 0 5 8 】

図 5 (C) に、期間 3 における画素 100 の動作を示す。なお、図 5 (C) では、トランジスタ 12 乃至トランジスタ 15 をスイッチとして表記している。期間 3 では、上記動作により、ノード B に電位 V<sub>data</sub> が与えられるため、トランジスタ 11 のゲート電圧が V<sub>data</sub> - V<sub>0</sub> + V<sub>th</sub> となる。よって、トランジスタ 11 のゲート電圧を、閾値電圧 V<sub>th</sub> が加味された値に設定することができる。上記構成により、トランジスタ 11 の閾値電圧 V<sub>th</sub> のばらつきが、発光素子 17 に供給する電流値に影響を及ぼすのを防ぐことができる。または、トランジスタ 11 が劣化して、閾値電圧 V<sub>th</sub> が変化しても、上記変化が発光素子 17 に供給する電流値に影響を及ぼすのを防ぐことができる。よって、表示ムラを低減でき、高い画質の表示を行うことができる。

20

【 0 0 5 9 】

なお、特許文献 1 に記載された発光素子型ディスプレイでは、有機 EL 素子に電流を供給するためのトランジスタ (Tr12) のゲートとドレインを電気的に接続し、閾値電圧の取得を行っている。よって、トランジスタ (Tr12) がノーマリオンの場合、トランジスタ (Tr12) のソースがゲートよりも高くなることはない。そのため、トランジスタ (Tr12) がノーマリオンの場合、閾値電圧を取得することが困難である。

【 0 0 6 0 】

一方、図 1 (A) 及び図 1 (B) に示した画素を有する本発明の一態様に係る発光装置では、トランジスタ 11 のソース及びドレインの他方と、トランジスタ 11 のゲートとが電気的に分離しているので、それぞれの電位を個別に制御することができる。よって、第 2 の動作において、トランジスタ 11 のソース及びドレインの他方の電位を、トランジスタ 11 のゲートの電位に、閾値電圧 V<sub>th</sub> を加算した電位よりも高い値に設定することができる。そのため、トランジスタ 11 がノーマリオンである場合に、すなわち閾値電圧 V<sub>th</sub> がマイナスの値を有している場合に、トランジスタ 11 において、ソースの電位がゲートの電位 V<sub>0</sub> よりも高くなるまで、容量素子 16 に電荷を蓄積することができる。よって、本発明の一態様に係る発光装置では、トランジスタ 11 がノーマリオンであっても、上記第 2 の動作において閾値電圧を取得することができ、第 3 の動作において、閾値電圧 V<sub>th</sub> を加味した値になるよう、トランジスタ 11 のゲート電圧を設定することができる。

30

【 0 0 6 1 】

したがって、本発明の一態様に係る発光装置では、例えばトランジスタ 11 の半導体膜に酸化物半導体を用いた場合などに、トランジスタ 11 がノーマリオンとなっても、表示ムラを低減でき、高い画質の表示を行うことができる。

40

【 0 0 6 2 】

( 実施の形態 2 )

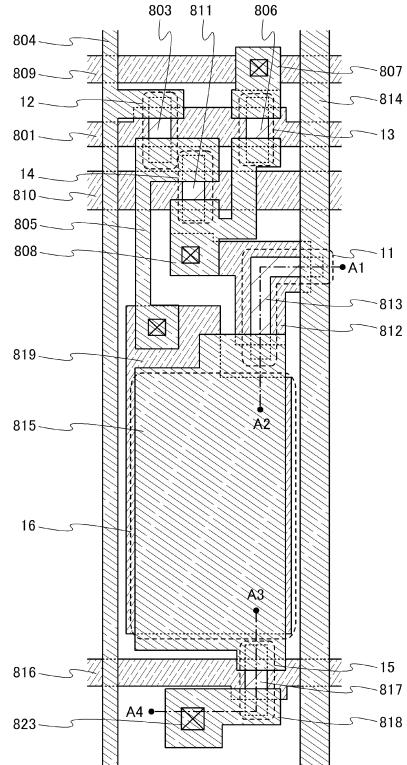

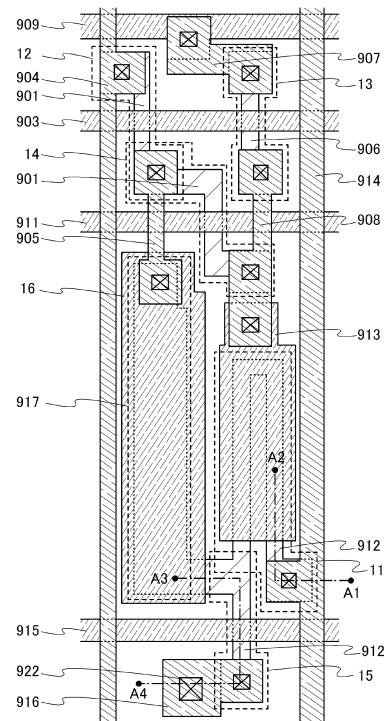

図 6 に、図 1 (A) に示した画素の上面図を、一例として示す。なお、図 6 では、画素のレイアウトを明確に示すために、各種の絶縁膜を省略して、画素の上面図を示す。また、図 6 では、画素が有するトランジスタと容量素子のレイアウトを明確に示すために、陽極と、EL 層と、陰極とを省略して、画素の上面図を示す。

【 0 0 6 3 】

また、図 7 に、図 6 に示す上面図の、破線 A1 - A2 及び破線 A3 - A4 における断面図

50

を示す。

【 0 0 6 4 】

トランジスタ 1 2 は、絶縁表面を有する基板 8 0 0 上に、ゲートとして機能する導電膜 8 0 1 と、導電膜 8 0 1 上のゲート絶縁膜 8 0 2 と、導電膜 8 0 1 と重なる位置においてゲート絶縁膜 8 0 2 上に位置する半導体膜 8 0 3 と、ソースまたはドレインとして機能し、半導体膜 8 0 3 上に位置する導電膜 8 0 4 及び導電膜 8 0 5 とを有する。導電膜 8 0 1 は配線 G 1 としても機能する。導電膜 8 0 4 は、配線 S L としても機能する。

【 0 0 6 5 】

トランジスタ 1 3 は、絶縁表面を有する基板 8 0 0 上に、ゲートとして機能する導電膜 8 0 1 と、導電膜 8 0 1 上のゲート絶縁膜 8 0 2 と、導電膜 8 0 1 と重なる位置においてゲート絶縁膜 8 0 2 上に位置する半導体膜 8 0 6 と、ソースまたはドレインとして機能し、半導体膜 8 0 6 上に位置する導電膜 8 0 7 及び導電膜 8 0 8 とを有する。導電膜 8 0 7 は、コンタクトホールを介して、配線 I L として機能する導電膜 8 0 9 に接続されている。

10

【 0 0 6 6 】

トランジスタ 1 4 は、絶縁表面を有する基板 8 0 0 上に、ゲートとして機能する導電膜 8 1 0 と、導電膜 8 1 0 上のゲート絶縁膜 8 0 2 と、導電膜 8 1 0 と重なる位置においてゲート絶縁膜 8 0 2 上に位置する半導体膜 8 1 1 と、ソースまたはドレインとして機能し、半導体膜 8 1 1 上に位置する導電膜 8 0 5 及び導電膜 8 0 8 とを有する。導電膜 8 1 0 は、配線 G 2 としても機能する。

【 0 0 6 7 】

トランジスタ 1 1 は、絶縁表面を有する基板 8 0 0 上に、ゲートとして機能する導電膜 8 1 2 と、導電膜 8 1 2 上のゲート絶縁膜 8 0 2 と、導電膜 8 1 2 と重なる位置においてゲート絶縁膜 8 0 2 上に位置する半導体膜 8 1 3 と、ソースまたはドレインとして機能し、半導体膜 8 1 3 上に位置する導電膜 8 1 4 及び導電膜 8 1 5 とを有する。導電膜 8 1 2 は、導電膜 8 0 8 に接続されている。導電膜 8 1 4 は配線 V L としても機能する。

20

【 0 0 6 8 】

トランジスタ 1 5 は、絶縁表面を有する基板 8 0 0 上に、ゲートとして機能する導電膜 8 1 6 と、導電膜 8 1 6 上のゲート絶縁膜 8 0 2 と、導電膜 8 1 6 と重なる位置においてゲート絶縁膜 8 0 2 上に位置する半導体膜 8 1 7 と、ソースまたはドレインとして機能し、半導体膜 8 1 7 上に位置する導電膜 8 1 5 及び導電膜 8 1 8 とを有する。導電膜 8 1 6 は配線 G 3 としても機能する。

30

【 0 0 6 9 】

容量素子 1 6 は、絶縁表面を有する基板 8 0 0 上に、導電膜 8 1 9 と、導電膜 8 1 9 上のゲート絶縁膜 8 0 2 と、導電膜 8 1 9 と重なる位置においてゲート絶縁膜 8 0 2 上に位置する導電膜 8 1 5 とを有する。導電膜 8 1 9 は、導電膜 8 0 5 と接続されている。

【 0 0 7 0 】

また、導電膜 8 0 4 、導電膜 8 0 5 、導電膜 8 0 7 、導電膜 8 0 8 、導電膜 8 1 4 、導電膜 8 1 5 、導電膜 8 1 8 上には、絶縁膜 8 2 0 が形成されている。そして、絶縁膜 8 2 1 上には、陽極として機能する導電膜 8 2 2 が設けられている。導電膜 8 2 2 は、絶縁膜 8 2 0 及び絶縁膜 8 2 1 に形成されたコンタクトホール 8 2 3 を介して、導電膜 8 1 8 に接続されている。

40

【 0 0 7 1 】

また、導電膜 8 2 2 の一部が露出するような開口部を有した絶縁膜 8 2 4 が、絶縁膜 8 2 1 上に設けられている。導電膜 8 2 2 の一部及び絶縁膜 8 2 4 上には、E L 層 8 2 5 と、陰極として機能する導電膜 8 2 6 とが、順に積層するように設けられている。導電膜 8 2 2 と、E L 層 8 2 5 と、導電膜 8 2 6 とが重なっている領域が、発光素子 1 7 に相当する。

【 0 0 7 2 】

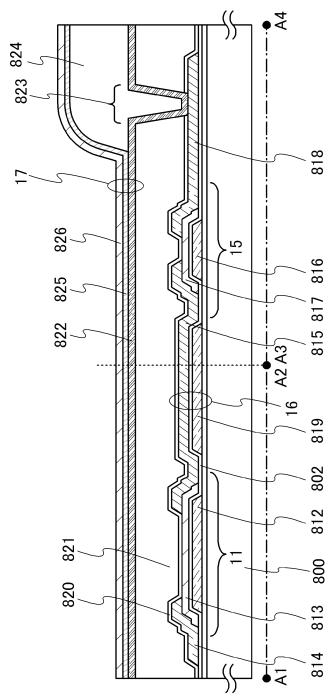

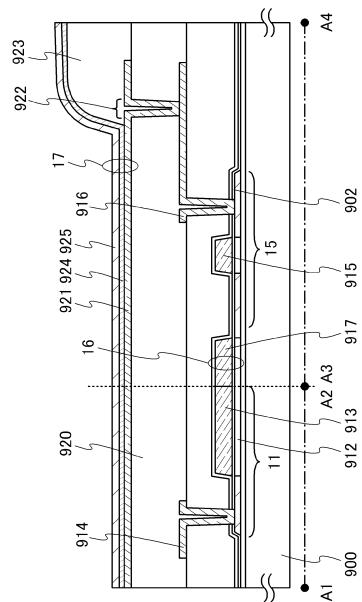

次いで、図 8 に、図 1 ( A ) に示した画素の上面図を、別の一例として示す。なお、図 8 では、画素のレイアウトを明確に示すために、各種の絶縁膜を省略して、画素の上面図を

50

示す。また、図8では、画素が有するトランジスタと容量素子のレイアウトを明確に示すために、陽極と、EL層と、陰極とを省略して、画素の上面図を示す。

【0073】

また、図9に、図8に示す上面図の、破線A1-A2及び破線A3-A4における断面図を示す。

【0074】

トランジスタ12は、絶縁表面を有する基板900上に、半導体膜901と、半導体膜901上のゲート絶縁膜902と、半導体膜901と重なる位置においてゲート絶縁膜902上に位置し、ゲートとして機能する導電膜903と、半導体膜901が有するソースまたはドレインに接続された導電膜904及び導電膜905とを有する。導電膜903は配線G1としても機能する。導電膜904は、配線SLとしても機能する。

10

【0075】

トランジスタ13は、絶縁表面を有する基板900上に、半導体膜906と、半導体膜906上のゲート絶縁膜902と、半導体膜906と重なる位置においてゲート絶縁膜902上に位置し、ゲートとして機能する導電膜903と、半導体膜906が有するソースまたはドレインに接続された導電膜907及び導電膜908とを有する。導電膜907は、コンタクトホールを介して、配線ILとして機能する導電膜909に接続されている。

【0076】

トランジスタ14は、絶縁表面を有する基板900上に、半導体膜901と、半導体膜901上のゲート絶縁膜902と、半導体膜901と重なる位置においてゲート絶縁膜902上に位置し、ゲートとして機能する導電膜911と、半導体膜901が有するソースまたはドレインに接続された導電膜905及び導電膜908とを有する。導電膜911は、配線G2としても機能する。なお、図8では、トランジスタ12とトランジスタ14とが一の半導体膜901を共有しているが、トランジスタ12とトランジスタ14とが互いに独立した半導体膜を有していても良い。

20

【0077】

トランジスタ11は、絶縁表面を有する基板900上に、半導体膜912と、半導体膜912上のゲート絶縁膜902と、半導体膜912と重なる位置においてゲート絶縁膜902上に位置し、ゲートとして機能する導電膜913と、半導体膜912が有するソースまたはドレインに接続された導電膜914とを有する。導電膜913は、導電膜908に接続されている。導電膜914は配線VLとしても機能する。

30

【0078】

トランジスタ15は、絶縁表面を有する基板900上に、半導体膜912と、半導体膜912上のゲート絶縁膜902と、半導体膜912と重なる位置においてゲート絶縁膜902上に位置し、ゲートとして機能する導電膜915と、半導体膜912が有するソースまたはドレインに接続された導電膜916とを有する。導電膜915は配線G3としても機能する。

【0079】

容量素子16は、絶縁表面を有する基板900上に、半導体膜912と、半導体膜912上のゲート絶縁膜902と、半導体膜912と重なる位置においてゲート絶縁膜902上に位置する導電膜917とを有する。導電膜917は、導電膜905と接続されている。

40

【0080】

そして、導電膜904、導電膜905、導電膜907、導電膜908、導電膜914、導電膜916上には、絶縁膜920が形成されている。絶縁膜920上には、陽極として機能する導電膜921が設けられている。導電膜921は、絶縁膜920に形成されたコンタクトホール922を介して、導電膜916に接続されている。

【0081】

また、導電膜921の一部が露出するような開口部を有した絶縁膜923が、絶縁膜920上に設けられている。導電膜921の一部及び絶縁膜923上には、EL層924と、陰極として機能する導電膜925とが、順に積層するように設けられている。導電膜92

50

1と、EL層924と、導電膜925とが重なっている領域が、発光素子17に相当する。

【0082】

なお、本発明の一態様では、トランジスタ11乃至トランジスタ15は、非晶質、微結晶、多結晶又は単結晶である、シリコン又はゲルマニウムなどの半導体が半導体膜に用いられても良いし、酸化物半導体などのワイドギャップ半導体が半導体膜に用いられても良い。

【0083】

トランジスタ11乃至トランジスタ15の半導体膜に、非晶質、微結晶、多結晶又は単結晶である、シリコン又はゲルマニウムなどの半導体が用いられる場合、一導電性を付与する不純物元素を上記半導体膜に添加して、ソースまたはドレインとして機能する不純物領域を形成する。例えば、リンまたはヒ素を上記半導体膜に添加することで、n型の導電性を有する不純物領域を形成することができる。また、例えば、ボロンを上記半導体膜に添加することで、p型の導電性を有する不純物領域を形成することができる。

10

【0084】

トランジスタ11乃至トランジスタ15の半導体膜に、酸化物半導体が用いられる場合、ドーパントを上記半導体膜に添加して、ソースまたはドレインとして機能する不純物領域を形成しても良い。ドーパントの添加は、イオン注入法を用いることができる。ドーパントは、例えばヘリウム、アルゴン、キセノンなどの希ガスや、窒素、リン、ヒ素、アンチモンなどの15族元素などを用いることができる。例えば、窒素をドーパントとして用いた場合、不純物領域中の窒素原子の濃度は、 $5 \times 10^{19} / \text{cm}^3$ 以上 $1 \times 10^{22} / \text{cm}^3$ 以下であることが望ましい。

20

【0085】

なお、シリコン半導体としては、プラズマCVD法などの気相成長法若しくはスパッタリング法で作製された非晶質シリコン、非晶質シリコンをレーザーアニールなどの処理により結晶化させた多結晶シリコン、単結晶シリコンウエハーに水素イオン等を注入して表層部を剥離した単結晶シリコンなどを用いることができる。

【0086】

また、酸化物半導体として、酸化インジウム、酸化スズ、酸化亜鉛、二元系金属の酸化物であるIn-Zn系酸化物、Sn-Zn系酸化物、Al-Zn系酸化物、Zn-Mg系酸化物、Sn-Mg系酸化物、In-Mg系酸化物、In-Ga系酸化物、三元系金属の酸化物であるIn-Ga-Zn系酸化物（IGZOとも表記する）、In-Al-Zn系酸化物、In-Sn-Zn系酸化物、Sn-Ga-Zn系酸化物、Al-Ga-Zn系酸化物、Sn-Al-Zn系酸化物、In-Hf-Zn系酸化物、In-La-Zn系酸化物、In-Ce-Zn系酸化物、In-Pr-Zn系酸化物、In-Nd-Zn系酸化物、In-Sm-Zn系酸化物、In-Eu-Zn系酸化物、In-Gd-Zn系酸化物、In-Tb-Zn系酸化物、In-Dy-Zn系酸化物、In-Ho-Zn系酸化物、In-Er-Zn系酸化物、In-Tm-Zn系酸化物、In-Yb-Zn系酸化物、In-Lu-Zn系酸化物、四元系金属の酸化物であるIn-Sn-Ga-Zn系酸化物、In-Hf-Ga-Zn系酸化物、In-Al-Ga-Zn系酸化物、In-Sn-Al-Zn系酸化物、In-Sn-Hf-Zn系酸化物、In-Hf-Al-Zn系酸化物を用いることができる。

30

【0087】

なお、例えば、In-Ga-Zn系酸化物とは、InとGaとZnを有する酸化物という意味であり、InとGaとZnの比率は問わない。また、InとGaとZn以外の金属元素が入っていてもよい。

【0088】

また、酸化物半導体として、 $\text{InMO}_3 (\text{ZnO})_m$  ( $m > 0$ 、且つ、 $m$ は整数でない) で表記される材料を用いてもよい。なお、Mは、Ga、Fe、Mn及びCoから選ばれた一の金属元素または複数の金属元素を示す。また、酸化物半導体として、 $\text{In}_2\text{SnO}_5$

40

50

$(ZnO)_n$  ( $n > 0$ 、且つ、 $n$  は整数) で表記される材料を用いてもよい。

【0089】

例えば、 $In:Ga:Zn = 1:1:1$  ( $= 1/3:1/3:1/3$ ) あるいは  $In:Ga:Zn = 2:2:1$  ( $= 2/5:2/5:1/5$ ) の原子比の  $In-Ga-Zn$  系酸化物やその組成の近傍の酸化物を用いることができる。あるいは、 $In:Sn:Zn = 1:1:1$  ( $= 1/3:1/3:1/3$ )、 $In:Sn:Zn = 2:1:3$  ( $= 1/3:1/6:1/2$ ) あるいは  $In:Sn:Zn = 2:1:5$  ( $= 1/4:1/8:5/8$ ) の原子比の  $In-Sn-Zn$  系酸化物やその組成の近傍の酸化物を用いるとよい。

【0090】

また、該酸化物半導体を用いたトランジスタの電気的特性のばらつきを減らすためのスタビライザーとして、スズ (Sn)、ハフニウム (Hf)、アルミニウム (Al)、ジルコニウム (Zr)、チタン (Ti) を有することが好ましい。他のスタビライザーとして、ランタノイドである、ランタン (La)、セリウム (Ce)、プラセオジム (Pr)、ネオジム (Nd)、サマリウム (Sm)、ユウロピウム (Eu)、ガドリニウム (Gd)、テルビウム (Tb)、ジスプロシウム (Dy)、ホルミウム (Ho)、エルビウム (Er)、ツリウム (Tm)、イッテルビウム (Yb)、ルテチウム (Lu) のいずれか一種あるいは複数種を有してもよい。

10

【0091】

なお、電子供与体 (ドナー) となる水分または水素などの不純物が低減され、なおかつ酸素欠損が低減されることにより高純度化された酸化物半導体 (purified OS) は、i型 (真性半導体) 又はi型に限りなく近い。そのため、上記酸化物半導体を用いたトランジスタは、オフ電流が著しく低いという特性を有する。また、酸化物半導体のバンドギャップは、2 eV以上、好ましくは2.5 eV以上、より好ましくは3 eV以上である。水分または水素などの不純物濃度が十分に低減され、なおかつ酸素欠損が低減されることにより高純度化された酸化物半導体膜を用いることにより、トランジスタのオフ電流を下げることができる。

20

【0092】

具体的に、高純度化された酸化物半導体を半導体膜に用いたトランジスタのオフ電流が低いことは、いろいろな実験により証明できる。例えば、チャネル幅が  $1 \times 10^6 \mu m$  でチャネル長が  $10 \mu m$  の素子であっても、ソース電極とドレイン電極間の電圧 (ドレイン電圧) が 1 V から 10 V の範囲において、オフ電流が、半導体パラメータアナライザの測定限界以下、すなわち  $1 \times 10^{-13} A$  以下という特性を得ることができる。この場合、オフ電流をトランジスタのチャネル幅で除した数値に相当するオフ電流は、 $100 zA / \mu m$  以下であることが分かる。また、容量素子とトランジスタとを接続して、容量素子に流入または容量素子から流出する電荷を当該トランジスタで制御する回路を用いて、オフ電流の測定を行った。当該測定では、上記トランジスタに高純度化された酸化物半導体膜をチャネル形成領域に用い、容量素子の単位時間あたりの電荷量の推移から当該トランジスタのオフ電流を測定した。その結果、トランジスタのソース電極とドレイン電極間の電圧が 3 V の場合に、数十  $yA / \mu m$  という、さらに低いオフ電流が得られることが分かった。従って、高純度化された酸化物半導体膜をチャネル形成領域に用いたトランジスタは、オフ電流が、結晶性を有するシリコンを用いたトランジスタに比べて著しく低い。

30

【0093】

なお、特に断りがない限り、本明細書でオフ電流とは、nチャネル型トランジスタにおいては、ドレインをソースとゲートよりも高い電位とした状態において、ソースの電位を基準としたときのゲートの電位が 0 以下であるときに、ソースとドレインの間に流れる電流のことを意味する。或いは、本明細書でオフ電流とは、pチャネル型トランジスタにおいては、ドレインをソースとゲートよりも低い電位とした状態において、ソースの電位を基準としたときのゲートの電位が 0 以上であるときに、ソースとドレインの間に流れる電流のことを意味する。

40

【0094】

50

なお、例えば、酸化物半導体膜は、In (インジウム)、Ga (ガリウム)、及びZn (亜鉛)を含むターゲットを用いたスパッタ法により形成することができる。In - Ga - Zn系酸化物半導体膜をスパッタリング法で成膜する場合、好ましくは、原子数比がIn : Ga : Zn = 1 : 1 : 1、4 : 2 : 3、3 : 1 : 2、1 : 1 : 2、2 : 1 : 3、または3 : 1 : 4で示されるIn - Ga - Zn系酸化物のターゲットを用いる。前述の原子数比を有するIn - Ga - Zn系酸化物のターゲットを用いて酸化物半導体膜を成膜することで、多結晶またはCACが形成されやすくなる。また、In、Ga、及びZnを含むターゲットの充填率は90%以上100%以下、好ましくは95%以上100%未満である。充填率の高いターゲットを用いることにより、成膜した酸化物半導体膜は緻密な膜となる。

10

#### 【0095】

なお、酸化物半導体としてIn - Zn系酸化物の材料を用いる場合、用いるターゲット中の金属元素の原子数比は、In : Zn = 50 : 1 ~ 1 : 2 (モル数比に換算するとIn<sub>2</sub>O<sub>3</sub> : ZnO = 25 : 1 ~ 1 : 4)、好ましくはIn : Zn = 20 : 1 ~ 1 : 1 (モル数比に換算するとIn<sub>2</sub>O<sub>3</sub> : ZnO = 10 : 1 ~ 1 : 2)、さらに好ましくはIn : Zn = 15 : 1 ~ 1.5 : 1 (モル数比に換算するとIn<sub>2</sub>O<sub>3</sub> : ZnO = 15 : 2 ~ 3 : 4)とする。例えば、In - Zn系酸化物である酸化物半導体膜の形成に用いるターゲットは、原子数比がIn : Zn : O = X : Y : Zのとき、Z > 1.5X + Yとする。Znの比率を上記範囲に収めることで、移動度の向上を実現することができる。

20

#### 【0096】

そして、具体的に酸化物半導体膜は、減圧状態に保持された処理室内に基板を保持し、処理室内の残留水分を除去しつつ水素及び水分が除去されたスパッタガスを導入し、上記ターゲットを用いて形成すればよい。成膜時に、基板温度を100以上600以下、好ましくは200以上400以下としても良い。基板を加熱しながら成膜することにより、成膜した酸化物半導体膜に含まれる不純物濃度を低減することができる。また、スパッタリングによる損傷が軽減される。処理室内の残留水分を除去するためには、吸着型の真空ポンプを用いることが好ましい。例えば、クライオポンプ、イオンポンプ、チタンサブリメーションポンプを用いることが好ましい。また、排気手段としては、ターボポンプにコールドトラップを加えたものであってもよい。クライオポンプを用いて成膜室を排気すると、例えば、水素原子、水(H<sub>2</sub>O)など水素原子を含む化合物(より好ましくは炭素原子を含む化合物も)等が排気されるため、当該処理室で成膜した酸化物半導体膜に含まれる不純物の濃度を低減できる。

30

#### 【0097】

なお、スパッタ等で成膜された酸化物半導体膜中には、不純物としての水分または水素(水酸基を含む)が多量に含まれていることがある。水分または水素はドナー準位を形成しやすいため、酸化物半導体にとって不純物である。そこで、本発明の一態様では、酸化物半導体膜中の水分または水素などの不純物を低減(脱水化または脱水素化)するために、酸化物半導体膜に対して、減圧雰囲気下、窒素や希ガスなどの不活性ガス雰囲気下、酸素ガス雰囲気下、または超乾燥エア(CRDS(キャビティリングダウンレーザー分光法)方式の露点計を用いて測定した場合の水分量が20ppm(露点換算で-55)以下、好ましくは1ppm以下、好ましくは10ppb以下の空気)雰囲気下で、加熱処理を施す。

40

#### 【0098】

酸化物半導体膜に加熱処理を施すことで、酸化物半導体膜中の水分または水素を脱離させることができる。具体的には、250以上750以下、好ましくは400以上基板の歪み点未満の温度で加熱処理を行えば良い。例えば、500、3分間以上6分間以下程度で行えば良い。加熱処理にRTA法を用いれば、短時間に脱水化または脱水素化が行えるため、ガラス基板の歪点を超える温度でも処理することができる。

#### 【0099】

なお、上記加熱処理により、酸化物半導体膜から酸素が脱離し、酸化物半導体膜内に酸素

50

欠損が形成される場合がある。よって、本発明の一態様では、酸化物半導体膜と接するゲート絶縁膜などの絶縁膜として、酸素を含む絶縁膜を用いる。そして、酸素を含む絶縁膜を形成した後、加熱処理を施すことで、上記絶縁膜から酸化物半導体膜に酸素が供与されるようにする。上記構成により、ドナーとなる酸素欠損を低減し、酸化物半導体膜に含まれる酸化物半導体の、化学量論的組成比を満たすことができる。酸化物半導体膜には、化学量論的組成比を超える量の酸素が含まれていることが好ましい。その結果、酸化物半導体膜をi型に近づけることができ、酸素欠損によるトランジスタの電気的特性のばらつきを軽減し、電気的特性の向上を実現することができる。

#### 【0100】

なお、酸素を酸化物半導体膜に供与するための加熱処理は、窒素、超乾燥空気、または希ガス（アルゴン、ヘリウムなど）の雰囲気下において、好ましくは200以上400以下、例えば250以上350以下で行う。上記ガスは、水の含有量が20ppm以下、好ましくは1ppm以下、より好ましくは10ppb以下であることが望ましい。

10

#### 【0101】

また、酸化物半導体は、アモルファス（非晶質）であってもよいし、結晶性を有していてもよい。後者の場合、単結晶でもよいし、多結晶でもよいし、一部分が結晶性を有する構成でもよいし、アモルファス中に結晶性を有する部分を含む構造でもよいし、非アモルファスでもよい。一部分が結晶性を有する構成の一例として、c軸配向し、かつab面、表面または界面に垂直な方向から見て三角形状または六角形状の原子配列を有し、c軸に垂直な方向から見て金属原子が層状または金属原子と酸素原子とが層状に配列しており、ab面においてはa軸またはb軸の向きが異なる（c軸を中心に回転した）結晶を含む酸化物半導体（CAAC-OS: C Axis Aligned Crystalline Oxide Semiconductorともいう。）を用いてもよい。

20

#### 【0102】

CAAC-OSとは、広義に、非単結晶であって、そのab面に垂直な方向から見て、三角形、六角形、正三角形または正六角形の原子配列を有し、かつc軸方向に垂直な方向から見て、金属原子が層状、または金属原子と酸素原子が層状に配列した相を含む酸化物をいう。

#### 【0103】

CAAC-OSは単結晶ではないが、非晶質のみから形成されているものでもない。また、CAACは結晶化した部分（結晶部分）を含むが、1つの結晶部分と他の結晶部分の境界を明確に判別できないこともある。

30

#### 【0104】

CAAC-OSを構成する酸素の一部は窒素で置換されてもよい。また、CAAC-OSを構成する個々の結晶部分のc軸は一定の方向（例えば、CAAC-OSが形成される基板面、CAAC-OSの表面などに垂直な方向）に揃っていてもよい。または、CAAC-OSを構成する個々の結晶部分のab面の法線は一定の方向（例えば、CAAC-OSが形成される基板面、CAAC-OSの表面などに垂直な方向）を向いていてもよい。

#### 【0105】

CAAC-OSは、その組成などに応じて、導体であったり、半導体であったり、絶縁体であったりする。また、その組成などに応じて、可視光に対して透光性を有していたり、有していないかったりする。

40

#### 【0106】

このようなCAAC-OSの例として、膜状に形成され、膜表面または膜が形成される基板面に垂直な方向から観察すると三角形または六角形の原子配列が認められ、かつその膜断面を観察すると金属原子または金属原子及び酸素原子（または窒素原子）の層状配列が認められる酸化物を挙げることもできる。

#### 【0107】

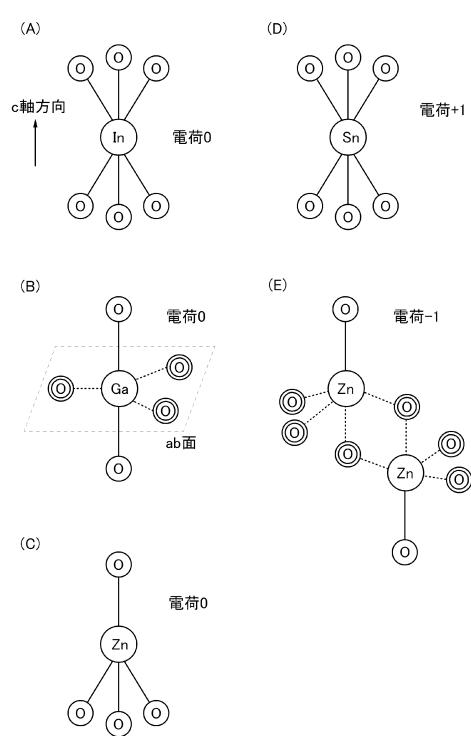

CAAC-OSに含まれる結晶構造の一例について図14乃至図16を用いて詳細に説明する。なお、特に断りがない限り、図14乃至図16は上方向をc軸方向とし、c軸方向

50

と直交する面を a b 面とする。なお、単に上半分、下半分という場合、a b 面を境にした場合の上半分、下半分をいう。また、図 14 において丸で囲まれた O は 4 配位の O を示し、二重丸で囲まれた O は 3 配位の O を示す。

#### 【 0 1 0 8 】

図 14 ( A ) に、1 個の 6 配位の I n と、I n に近接の 6 個の 4 配位の酸素原子 ( 以下 4 配位の O ) と、を有する構造を示す。ここでは、金属原子が 1 個に対して、近接の酸素原子のみ示した構造を小グループと呼ぶ。図 14 ( A ) の構造は、八面体構造をとるが、簡単のため平面構造で示している。なお、図 14 ( A ) の上半分および下半分にはそれぞれ 3 個ずつ 4 配位の O がある。図 14 ( A ) に示す小グループは電荷が 0 である。

#### 【 0 1 0 9 】

図 14 ( B ) に、1 個の 5 配位の G a と、G a に近接の 3 個の 3 配位の酸素原子 ( 以下 3 配位の O ) と、G a に近接の 2 個の 4 配位の O と、を有する構造を示す。3 配位の O は、いずれも a b 面に存在する。図 14 ( B ) の上半分および下半分にはそれぞれ 1 個ずつ 4 配位の O がある。また、I n も 5 配位をとるため、図 14 ( B ) に示す構造をとりうる。図 14 ( B ) に示す小グループは電荷が 0 である。

#### 【 0 1 1 0 】

図 14 ( C ) に、1 個の 4 配位の Z n と、Z n に近接の 4 個の 4 配位の O と、を有する構造を示す。図 14 ( C ) の上半分には 1 個の 4 配位の O があり、下半分には 3 個の 4 配位の O がある。または、図 14 ( C ) の上半分に 3 個の 4 配位の O があり、下半分に 1 個の 4 配位の O があつてもよい。図 14 ( C ) に示す小グループは電荷が 0 である。

#### 【 0 1 1 1 】

図 14 ( D ) に、1 個の 6 配位の S n と、S n に近接の 6 個の 4 配位の O と、を有する構造を示す。図 14 ( D ) の上半分には 3 個の 4 配位の O があり、下半分には 3 個の 4 配位の O がある。図 14 ( D ) に示す小グループは電荷が + 1 となる。

#### 【 0 1 1 2 】

図 14 ( E ) に、2 個の Z n を含む小グループを示す。図 14 ( E ) の上半分には 1 個の 4 配位の O があり、下半分には 1 個の 4 配位の O がある。図 14 ( E ) に示す小グループは電荷が - 1 となる。

#### 【 0 1 1 3 】

ここでは、複数の小グループの集合体を中グループと呼び、複数の中グループの集合体を大グループ ( ユニットセルともいう。 ) と呼ぶ。

#### 【 0 1 1 4 】

ここで、これらの小グループ同士が結合する規則について説明する。図 14 ( A ) に示す 6 配位の I n の上半分の 3 個の O は、下方向にそれぞれ 3 個の近接 I n を有し、下半分の 3 個の O は、上方向にそれぞれ 3 個の近接 I n を有する。図 14 ( B ) に示す 5 配位の G a の上半分の 1 個の O は下方向に 1 個の近接 G a を有し、下半分の 1 個の O は上方向に 1 個の近接 G a を有する。図 14 ( C ) に示す 4 配位の Z n の上半分の 1 個の O は、下方向に 1 個の近接 Z n を有し、下半分の 3 個の O は、上方向にそれぞれ 3 個の近接 Z n を有する。この様に、金属原子の上方向の 4 配位の O の数と、その O の下方向にある近接金属原子の数は等しく、同様に金属原子の下方向の 4 配位の O の数と、その O の上方向にある近接金属原子の数は等しい。O は 4 配位なので、下方向にある近接金属原子の数と、上方向にある近接金属原子の数の和は 4 になる。従って、金属原子の上方向にある 4 配位の O の数と、別の金属原子の下方向にある 4 配位の O の数との和が 4 個のとき、金属原子を有する二種の小グループ同士は結合することができる。例えば、6 配位の金属原子 ( I n または S n ) が下半分の 4 配位の O を介して結合する場合、4 配位の O が 3 個であるため、5 配位の金属原子 ( G a または I n ) 、4 配位の金属原子 ( Z n ) のいずれかと結合することになる。

#### 【 0 1 1 5 】

これらの配位数を有する金属原子は、c 軸方向において、4 配位の O を介して結合する。また、このほかにも、層構造の合計の電荷が 0 となるように複数の小グループが結合して

10

20

30

40

50

中グループを構成する。

【0116】

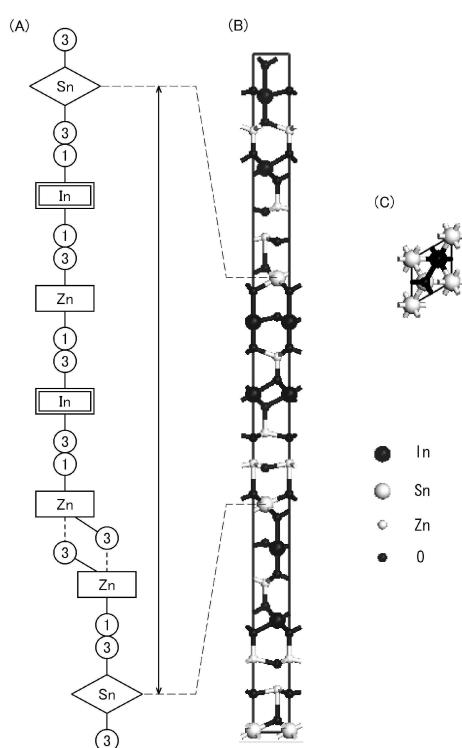

図15(A)に、In-Sn-Zn系酸化物の層構造を構成する中グループのモデル図を示す。図15(B)に、3つの中グループで構成される大グループを示す。なお、図15(C)は、図15(B)の層構造をc軸方向から観察した場合の原子配列を示す。

【0117】

図15(A)においては、簡単のため、3配位のOは省略し、4配位のOは個数のみ示し、例えば、Snの上半分および下半分にはそれぞれ3個ずつ4配位のOがあることを丸枠の3として示している。同様に、図15(A)において、Inの上半分および下半分にはそれぞれ1個ずつ4配位のOがあり、丸枠の1として示している。また、同様に、図15(A)において、下半分には1個の4配位のOがあり、上半分には3個の4配位のOがあるZnと、上半分には1個の4配位のOがあり、下半分には3個の4配位のOがあるZnとを示している。

【0118】

図15(A)において、In-Sn-Zn系酸化物の層構造を構成する中グループは、上から順に4配位のOが3個ずつ上半分および下半分にあるSnが、4配位のOが1個ずつ上半分および下半分にあるInと結合し、そのInが、上半分に3個の4配位のOがあるZnと結合し、そのZnの下半分の1個の4配位のOを介して4配位のOが3個ずつ上半分および下半分にあるInと結合し、そのInが、上半分に1個の4配位のOがあるZn2個からなる小グループと結合し、この小グループの下半分の1個の4配位のOを介して4配位のOが3個ずつ上半分および下半分にあるSnと結合している構成である。この中グループが複数結合して大グループを構成する。

【0119】

ここで、3配位のOおよび4配位のOの場合、結合1本当たりの電荷はそれぞれ-0.667、-0.5と考えることができる。例えば、In(6配位または5配位)、Zn(4配位)、Sn(5配位または6配位)の電荷は、それぞれ+3、+2、+4である。従って、Snを含む小グループは電荷が+1となる。そのため、Snを含む層構造を形成するためには、電荷+1を打ち消す電荷-1が必要となる。電荷-1をとる構造として、図14(E)に示すように、2個のZnを含む小グループが挙げられる。例えば、Snを含む小グループが1個に対し、2個のZnを含む小グループが1個あれば、電荷が打ち消されるため、層構造の合計の電荷を0とすることができます。

【0120】

具体的には、図15(B)に示した大グループが繰り返されることで、In-Sn-Zn系酸化物の結晶( $In_2SnZn_3O_8$ )を得ることができる。なお、得られるIn-Sn-Zn系酸化物の層構造は、 $In_2SnZn_2O_7$ ( $ZnO$ )<sub>m</sub>(mは0または自然数。)とする組成式で表すことができる。

【0121】

また、このほかにも、四元系金属の酸化物であるIn-Sn-Ga-Zn系酸化物や、三元系金属の酸化物であるIn-Ga-Zn系酸化物(IGZOとも表記する。)、In-Al-Zn系酸化物、Sn-Ga-Zn系酸化物、Al-Ga-Zn系酸化物、Sn-Al-Zn系酸化物や、In-Hf-Zn系酸化物、In-La-Zn系酸化物、In-Ce-Zn系酸化物、In-Pr-Zn系酸化物、In-Nd-Zn系酸化物、In-Sm-Zn系酸化物、In-Eu-Zn系酸化物、In-Gd-Zn系酸化物、In-Tb-Zn系酸化物、In-Dy-Zn系酸化物、In-Ho-Zn系酸化物、In-Er-Zn系酸化物、In-Tm-Zn系酸化物、In-Yb-Zn系酸化物、In-Lu-Zn系酸化物や、二元系金属の酸化物であるIn-Zn系酸化物、Sn-Zn系酸化物、Al-Zn系酸化物、Zn-Mg系酸化物、Sn-Mg系酸化物、In-Mg系酸化物や、In-Ga系酸化物の材料などを用いた場合も同様である。

【0122】

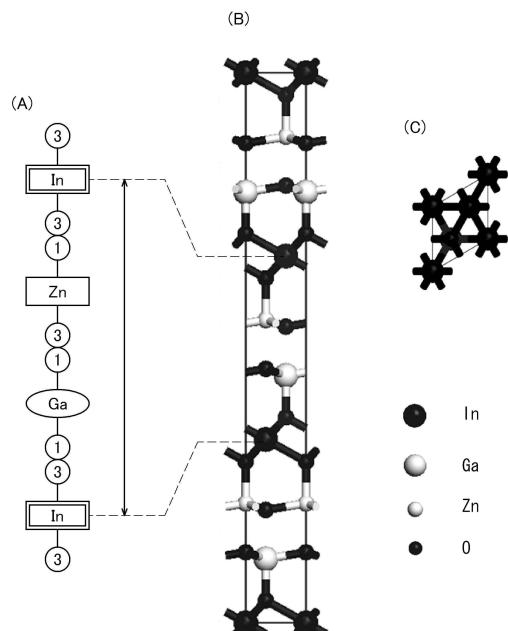

例えば、図16(A)に、In-Ga-Zn系酸化物の層構造を構成する中グループのモ

10

20

30

40

50

デル図を示す。

【0123】

図16(A)において、In-Ga-Zn系酸化物の層構造を構成する中グループは、上から順に4配位のOが3個ずつ上半分および下半分にあるInが、4配位のOが1個上半分にあるZnと結合し、そのZnの下半分の3個の4配位のOを介して、4配位のOが1個ずつ上半分および下半分にあるGaと結合し、そのGaの下半分の1個の4配位のOを介して、4配位のOが3個ずつ上半分および下半分にあるInと結合している構成である。この中グループが複数結合して大グループを構成する。

【0124】

図16(B)に3つの中グループで構成される大グループを示す。なお、図16(C)は、図16(B)の層構造をc軸方向から観察した場合の原子配列を示している。

10

【0125】

ここで、In(6配位または5配位)、Zn(4配位)、Ga(5配位)の電荷は、それぞれ+3、+2、+3であるため、In、ZnおよびGaのいずれかを含む小グループは、電荷が0となる。そのため、これらの小グループの組み合わせであれば中グループの合計の電荷は常に0となる。

【0126】

また、In-Ga-Zn系酸化物の層構造を構成する中グループは、図16(A)に示した中グループに限定されず、In、Ga、Znの配列が異なる中グループを組み合わせた大グループも取りうる。

20

【0127】

具体的には、図16(B)に示した大グループが繰り返されることで、In-Ga-Zn系酸化物の結晶を得ることができる。なお、得られるIn-Ga-Zn系酸化物の層構造は、 $In_n Ga O_3 (ZnO)_n$ (nは自然数。)とする組成式で表すことができる。

【0128】

本実施の形態は、他の実施の形態と組み合わせて実施することが可能である。

【0129】

(実施の形態3)

本発明の一態様に係る発光装置では、白色などの単色の光を発する発光素子と、カラーフィルタを組み合わせることで、フルカラー画像の表示を行う、カラーフィルタ方式を採用することができる。或いは、互いに異なる色相の光を発する複数の発光素子を用いて、フルカラー画像の表示を行う方式を採用することもできる。この方式は、発光素子が有する一対の電極間に設けられるEL層を、対応する色ごとに塗り分けるため、塗り分け方式と呼ばれる。

30

【0130】

塗り分け方式の場合、EL層の塗り分けは、通常、メタルマスクなどのマスクを用いて、蒸着法で行われる。そのため、画素のサイズは蒸着法によるEL層の塗り分け精度に依存する。一方、カラーフィルタ方式の場合、塗り分け方式とは異なり、EL層の塗り分けを行う必要がない。よって、塗り分け方式の場合よりも、画素サイズの縮小化が容易であり、高精細の画素部を実現することができる。

40

【0131】

また、発光装置には、トランジスタが形成された基板、所謂素子基板側から発光素子の光を取り出すボトムエミッション構造と、素子基板とは反対の側から発光素子の光を取り出すトップエミッション構造とがある。トップエミッション構造の場合、発光素子から発せられる光を、配線、トランジスタ、保持容量などの各種素子によって遮られることがないため、ボトムエミッション構造に比べて、画素からの光の取り出し効率を高めることができる。よって、トップエミッション構造は、発光素子に供給する電流値を低く抑えても、高い輝度を得ることができるため、発光素子の長寿命化に有利である。

【0132】

また、本発明の一態様に係る発光装置では、EL層から発せられる光を発光素子内で共振

50

させる、マイクロキャビティ（微小光共振器）構造を有していても良い。マイクロキャビティ構造により、特定の波長の光について、発光素子からの取り出し効率を高めることができるので、画素部の輝度と色純度を向上させることができる。

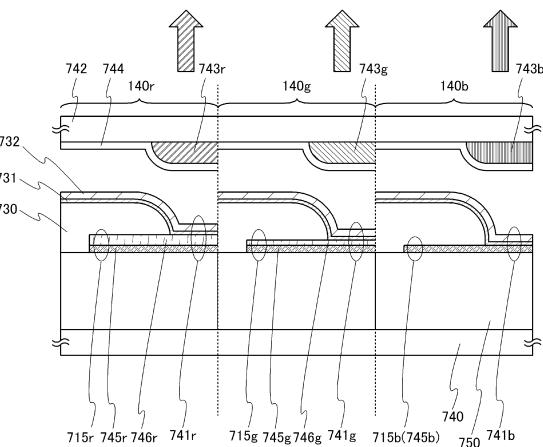

#### 【0133】

図10に、画素の断面図を、一例として示す。なお、図10では、赤に対応する画素の断面の一部、青に対応する画素の断面の一部と、緑に対応する画素の断面の一部とを示している。

#### 【0134】

具体的に、図10では、赤に対応した画素140rと、緑に対応した画素140gと、青に対応した画素140bとが示されている。画素140r、画素140g、画素140bは、それぞれ陽極715r、陽極715g、陽極715bを有する。上記陽極715r、陽極715g、陽極715bは、画素140r、画素140g、画素140bのそれぞれにおいて、基板740に形成された絶縁膜750の上に設けられている。

10

#### 【0135】

そして、陽極715r、陽極715g、及び陽極715b上には絶縁膜を有する隔壁730が設けられている。隔壁730は開口部を有し、上記開口部において、陽極715r、陽極715g、及び陽極715bが、それぞれ一部露出している。また、上記露出している領域を覆うように、隔壁730上に、EL層731と、可視光に対して透光性を有する陰極732とが、順に積層されている。

20

#### 【0136】

陽極715rと、EL層731と、陰極732とが重なる部分が、赤に対応した発光素子741rに相当する。陽極715gと、EL層731と、陰極732とが重なる部分が、緑に対応した発光素子741gに相当する。陽極715bと、EL層731と、陰極732とが重なる部分が、青に対応した発光素子741bに相当する。

#### 【0137】

また、基板742は、発光素子741r、発光素子741g、及び発光素子741bを間に挟むように、基板740と対峙している。基板742上には、画素140rに対応した着色層743r、画素140gに対応した着色層743g、画素140bに対応した着色層743bが設けられている。着色層743rは、赤に対応した波長領域の光の透過率が、他の波長領域の光の透過率より高い層であり、着色層743gは、緑に対応した波長領域の光の透過率が、他の波長領域の光の透過率より高い層であり、着色層743bは、青に対応した波長領域の光の透過率が、他の波長領域の光の透過率より高い層である。

30

#### 【0138】

さらに、基板742上には、着色層743r、着色層743g、着色層743bを覆うように、オーバーコート744が設けられている。オーバーコート744は、着色層743r、着色層743g、着色層743bを保護するための、可視光に対して透光性を有する層であり、平坦性の高い樹脂材料を用いるのが好ましい。着色層743r、着色層743g、及び着色層743bと、オーバーコート744とを合わせてカラーフィルタと見なしても良いし、着色層743r、着色層743g、及び着色層743bのそれぞれをカラーフィルタと見なしても良い。

40

#### 【0139】

そして、図10では、陽極715rに、可視光の反射率が高い導電膜745rと、可視光の透過率が上記導電膜745rよりも高い導電膜746rとを、順に積層して用いる。また、陽極715gに、可視光の反射率が高い導電膜745gと、可視光の透過率が上記導電膜745gよりも高い導電膜746gとを、順に積層して用いる。導電膜746gの膜厚は、導電膜746rの膜厚よりも小さいものとする。また、陽極715bに、可視光の反射率が高い導電膜745bを用いる。

#### 【0140】

よって、図10に示す発光装置では、発光素子741rにおいて、EL層731から発せられた光の光路長は、導電膜745rと陰極732の距離により調節することができる。

50

また、発光素子 741g において、EL 層 731 から発せられた光の光路長は、導電膜 745g と陰極 732 の距離により調節することができる。また、発光素子 741b において、EL 層 731 から発せられた光の光路長は、導電膜 745b と陰極 732 の距離により調節することができる。

【0141】

本発明の一態様では、発光素子 741r と、発光素子 741g と、発光素子 741b にそれぞれ対応する光の波長に合わせて、上記光路長を調整することで、EL 層 731 から発せられた光を上記各発光素子内において共振させる、マイクロキャビティ構造としても良い。

【0142】

上記マイクロキャビティ構造を、本発明の一態様に係る発光装置に採用することで、発光素子 741r から発せられる光において、赤に対応した波長を有する光の強度が、共振により高まる。よって、着色層 743r を通して得られる赤の光の色純度及び輝度が高まる。また、発光素子 741g から発せられる光において、緑に対応した波長を有する光の強度が、共振により高まる。よって、着色層 743g を通して得られる緑の光の色純度及び輝度が高まる。また、発光素子 741b から発せられる光において、青に対応した波長を有する光の強度が、共振により高まる。よって、着色層 743b を通して得られる青の光の色純度及び輝度が高まる。

【0143】

なお、図 10 では、赤、緑、青の 3 色に対応する画素を用いる構成について示したが、本発明の一態様では、当該構成に限定されない。本発明の一態様で用いる色の組み合わせは、例えば、赤、緑、青、黄の 4 色、または、シアン、マゼンタ、イエローの 3 色を用いていても良い。或いは、上記色の組み合わせは、淡色の赤、緑、及び青、並びに濃色の赤、緑、及び青の 6 色を用いていても良い。或いは、上記色の組み合わせは、赤、緑、青、シアン、マゼンタ、イエローの 6 色を用いていても良い。

【0144】

なお、例えば、赤、緑、及び青の画素を用いて表現できる色は、色度図上のそれぞれの発光色に対応する 3 点が描く三角形の内側に示される色に限られる。従って、赤、緑、青、黄の画素を用いた場合のように、色度図上の該三角形の外側に発光色が存在する発光素子を別途加えることで、当該発光装置において表現できる色域を拡大し、色再現性を豊かにことができる。

【0145】

また、図 10 では、発光素子 741r、発光素子 741g、発光素子 741b のうち、光の波長  $\lambda$  が最も短い発光素子 741b において、可視光の反射率が高い導電膜 745b を陽極として用い、他の発光素子 741r、発光素子 741g においては、膜厚が互いに異なる導電膜 746r 及び導電膜 746g を用いることにより、光路長を調整している。本発明の一態様では、波長  $\lambda$  が最も短い発光素子 741b においても、可視光の反射率が高い導電膜 745b 上に、導電膜 746r 及び導電膜 746g のような、可視光の透過率の高い導電膜を設けていても良い。ただし、図 10 に示すように、波長  $\lambda$  が最も短い発光素子 741b において、可視光の反射率が高い導電膜 745b で陽極を構成する場合、全ての発光素子において、陽極に可視光の透過率が高い導電膜を用いる場合よりも、陽極の作製工程が簡素化されるため、好ましい。

【0146】

なお、可視光の反射率が高い導電膜 745b は、可視光の透過率が高い導電膜 746r 及び導電膜 746g に比べて、仕事関数が小さい場合が多い。よって、光の波長  $\lambda$  が最も短い発光素子 741b では、発光素子 741r、発光素子 741g に比べて、陽極 715b から EL 層 731 への正孔注入が行われにくいため、発光効率が低い傾向にある。そこで、本発明の一態様では、光の波長  $\lambda$  が最も短い発光素子 741b において、EL 層 731 のうち、可視光の反射率が高い導電膜 745b と接する層において、正孔輸送性の高い物質に、当該正孔輸送性の高い物質に対してアクセプター性（電子受容性）を示す物質を含

10

20

30

40

50

有させた複合材料を用いることが好ましい。上記複合材料を、陽極 715b に接して形成することにより、陽極 715b から E L 層 731 への正孔注入が行われやすくなり、発光素子 741b の発光効率を高めることができる。

【0147】

アクセプター性を示す物質としては、7, 7, 8, 8 - テトラシアノ - 2, 3, 5, 6 - テトラフルオロキノジメタン（略称：F<sub>4</sub>-TCNQ）、クロラニル等を挙げることができる。また、遷移金属酸化物を挙げることができる。また、元素周期表における第4族乃至第8族に属する金属の酸化物を挙げることができる。具体的には、酸化バナジウム、酸化ニオブ、酸化タンタル、酸化クロム、酸化モリブデン、酸化タンゲステン、酸化マンガン、酸化レニウムはアクセプター性が高いため好ましい。中でも特に、酸化モリブデンは大気中でも安定であり、吸湿性が低く、扱いやすいため好ましい。

10

【0148】

複合材料に用いる正孔輸送性の高い物質としては、芳香族アミン化合物、カルバゾール誘導体、芳香族炭化水素、高分子化合物（オリゴマー、デンドリマー、ポリマー等）など、種々の化合物を用いることができる。なお、複合材料に用いる有機化合物としては、正孔輸送性の高い有機化合物であることが好ましい。具体的には、10<sup>-6</sup> cm<sup>2</sup> / Vs 以上の正孔移動度を有する物質であることが好ましい。但し、電子よりも正孔の輸送性の高い物質であれば、これら以外のものを用いてもよい。

【0149】

また、可視光の反射率が高い導電膜 745r、導電膜 745g、導電膜 745b としては、例えば、アルミニウム、銀、または、これらの金属材料を含む合金等を、単層で、或いは積層することで、形成することができる。また、導電膜 745r、導電膜 745g、導電膜 745b を、可視光の反射率の高い導電膜と、膜厚の薄い導電膜（好ましくは 20 nm 以下、更に好ましくは 10 nm 以下）とを積層させて、形成してもよい。例えば、可視光の反射率の高い導電膜上に、薄いチタン膜やモリブデン膜を積層して、導電膜 745b を形成することにより、可視光の反射率の高い導電膜（アルミニウム、アルミニウムを含む合金、または銀など）の表面に酸化膜が形成されるのを防ぐことができる。

20

【0150】

また、可視光の透過率が高い導電膜 746r 及び導電膜 746g には、例えば、酸化インジウム、酸化スズ、酸化亜鉛、インジウム錫酸化物、インジウム亜鉛酸化物などを用いることができる。

30

【0151】

また、陰極 732 は、例えば、光を透過する程度の薄い導電膜（好ましくは 20 nm 以下、更に好ましくは 10 nm 以下）と、導電性の金属酸化物で構成された導電膜とを積層することで、形成することができる。光を透過する程度の薄い導電膜は、銀、マグネシウム、またはこれらの金属材料を含む合金等を、単層で、或いは積層して形成することができる。導電性の金属酸化物としては、酸化インジウム、酸化スズ、酸化亜鉛、インジウム錫酸化物、インジウム亜鉛酸化物、またはこれらの金属酸化物材料に酸化シリコンを含ませたものを用いることができる。

【0152】

40

本実施の形態は、他の実施の形態と適宜組み合わせて実施することが可能である。

【0153】

（実施の形態 4）

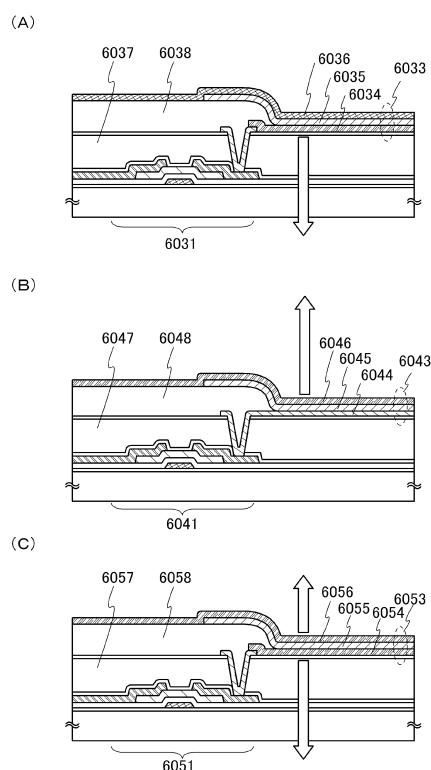

本実施の形態では、ボトムエミッション構造、トップエミッション構造、デュアルエミッション構造について説明する。デュアルエミッション構造とは、発光素子の光を、素子基板側からと、素子基板とは反対の側からと、取り出す構造を意味する。

【0154】

図 11 (A) に、発光素子 6033 から発せられる光を陽極 6034 側から取り出す場合の、画素の断面図を示す。トランジスタ 6031 は絶縁膜 6037 で覆われており、絶縁膜 6037 上には開口部を有する隔壁 6038 が形成されている。隔壁 6038 の開口部

50

において陽極 6034 が一部露出しており、該開口部において陽極 6034、EL層 6035、陰極 6036 が順に積層されている。

【0155】

陽極 6034 は、光を透過しやすい材料または膜厚で形成し、陰極 6036 は、光を透過しにくい材料または膜厚で形成する。上記構成により、陽極 6034 側から白抜きの矢印で示すように光を取り出す、ボトムエミッション構造を得ることができる。

【0156】

図 11 (B) に、発光素子 6043 から発せられる光を陰極 6046 側から取り出す場合の、画素の断面図を示す。トランジスタ 6041 は絶縁膜 6047 で覆われており、絶縁膜 6047 上には開口部を有する隔壁 6048 が形成されている。隔壁 6048 の開口部において陽極 6044 が一部露出しており、該開口部において陽極 6044、EL層 6045、陰極 6046 が順に積層されている。

10

【0157】

陽極 6044 は、光を透過しにくい材料または膜厚で形成し、陰極 6046 は、光を透過しやすい材料または膜厚で形成する。上記構成により、陰極 6046 側から白抜きの矢印で示すように光を取り出す、トップエミッション構造を得ることができる。

【0158】

図 11 (C) に、光素子 6053 から発せられる光を陽極 6054 側及び陰極 6056 側から取り出す場合の、画素の断面図を示す。トランジスタ 6051 は絶縁膜 6057 で覆われており、絶縁膜 6057 上には開口部を有する隔壁 6058 が形成されている。隔壁 6058 の開口部において陽極 6054 が一部露出しており、該開口部において陽極 6054、EL層 6055、陰極 6056 が順に積層されている。

20

【0159】

陽極 6054 及び陰極 6056 は、光を透過しやすい材料または膜厚で形成する。上記構成により、陽極 6054 及び陰極 6056 側から白抜きの矢印で示すように光を取り出す、デュアルエミッション構造を得ることができる。

【0160】

なお、陽極または陰極となる電極には、金属、合金、電気伝導性化合物、およびこれらの混合物などを用いることができる。具体的には、酸化インジウム - 酸化スズ (ITO : I n d i u m T i n O x i d e)、珪素若しくは酸化珪素を含有した酸化インジウム - 酸化スズ、酸化インジウム - 酸化亜鉛 (I n d i u m Z i n c O x i d e)、酸化タンゲステン及び酸化亜鉛を含有した酸化インジウム、金 (Au)、白金 (Pt)、ニッケル (Ni)、タンゲステン (W)、クロム (Cr)、モリブデン (Mo)、鉄 (Fe)、コバルト (Co)、銅 (Cu)、パラジウム (Pd)、チタン (Ti) の他、元素周期表の第 1 族または第 2 族に属する元素、すなわちリチウム (Li) やセシウム (Cs) 等のアルカリ金属、およびカルシウム (Ca)、ストロンチウム (Sr) 等のアルカリ土類金属、マグネシウム (Mg)、およびこれらを含む合金 (MgAg, AlLi)、ユウロピウム (Eu)、イッテルビウム (Yb) 等の希土類金属およびこれらを含む合金、その他、グラフェン等を用いることができる。そして、上記材料を適宜選択し、その膜厚を最適な値に設定することで、ボトムエミッション構造、トップエミッション構造、またはデュアルエミッション構造を作り分けることが可能となる。

30

【0161】

本実施の形態は、他の実施の形態と適宜組み合わせて実施することができる。

【0162】

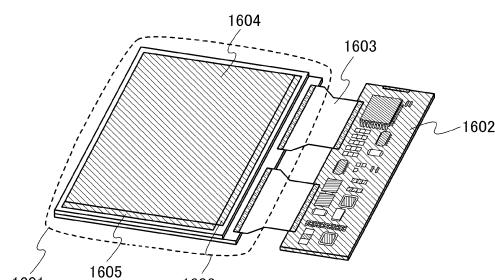

(実施の形態 5)

図 12 は、本発明の一態様に係る発光装置の斜視図の一例である。

【0163】

図 12 に示す発光装置は、パネル 1601 と、回路基板 1602 と、接続部 1603 とを有している。パネル 1601 は、画素が複数設けられた画素部 1604 と、複数の画素を行ごとに選択する走査線駆動回路 1605 と、選択された行内の画素への画像信号の入力

40

50

を制御する信号線駆動回路 1606 とを有する。具体的に、走査線駆動回路 1605 では、配線 G1 乃至配線 G3 に入力する信号を生成する。

【0164】

回路基板 1602 から、接続部 1603 を介して、各種信号と、電源の電位とが、パネル 1601 に入力される。接続部 1603 には、FPC (Flexible Printed Circuit) などを用いることができる。また、接続部 1603 に COF テープを用いる場合、回路基板 1602 内の一部の回路、或いはパネル 1601 が有する走査線駆動回路 1605 や信号線駆動回路 1606 の一部などを別途用意したチップに形成しておき、COF (Chip On Film) 法を用いて当該チップを COF テープに接続しておいても良い。

10

【0165】

本実施の形態は、他の実施の形態と組み合わせて実施することが可能である。

【0166】

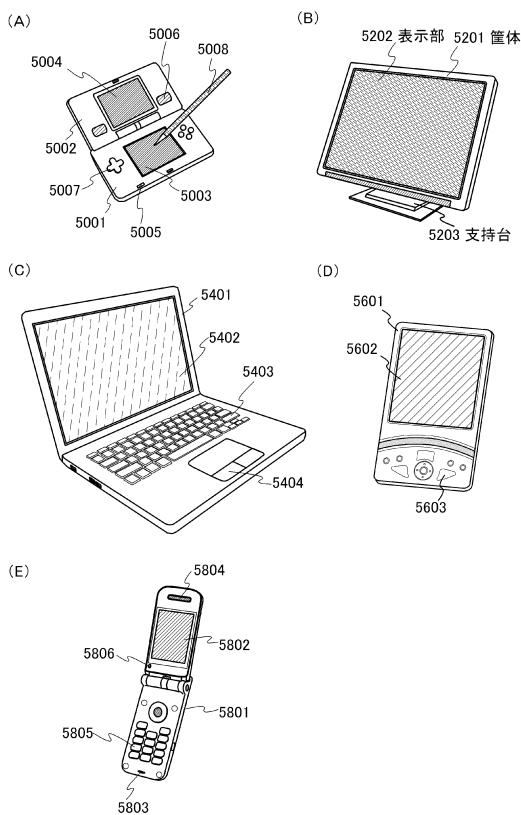

(実施の形態 6)

本発明の一態様に係る発光装置は、表示機器、パーソナルコンピュータ、記録媒体を備えた画像再生装置（代表的には DVD : Digital Versatile Disc 等の記録媒体を再生し、その画像を表示しうるディスプレイを有する装置）に用いることができる。その他に、本発明の一態様に係る発光装置を用いることができる電子機器として、携帯電話、携帯型を含むゲーム機、携帯情報端末、電子書籍、ビデオカメラ、デジタルスチルカメラ、ゴーグル型ディスプレイ（ヘッドマウントディスプレイ）、ナビゲーションシステム、音響再生装置（カーオーディオ、デジタルオーディオプレイヤー等）、複写機、ファクシミリ、プリンター、プリンター複合機、現金自動預け入れ払い機（ATM）、自動販売機などが挙げられる。これら電子機器の具体例を図 13 に示す。

20

【0167】

図 13 (A) は携帯型ゲーム機であり、筐体 5001、筐体 5002、表示部 5003、表示部 5004、マイクロホン 5005、スピーカー 5006、操作キー 5007、スタイルス 5008 等を有する。本発明の一態様に係る発光装置は、表示部 5003、表示部 5004 に用いることができる。表示部 5003 または表示部 5004 に本発明の一態様に係る発光装置を用いることで、高画質の携帯型ゲーム機を提供することができる。なお、図 13 (A) に示した携帯型ゲーム機は、2 つの表示部 5003 と表示部 5004 とを有しているが、携帯型ゲーム機が有する表示部の数は、これに限定されない。

30

【0168】

図 13 (B) は表示機器であり、筐体 5201、表示部 5202、支持台 5203 等を有する。本発明の一態様に係る発光装置は、表示部 5202 に用いることができる。表示部 5202 に本発明の一態様に係る発光装置を用いることで、高画質の表示機器を提供することができる。なお、表示機器には、パーソナルコンピュータ用、TV 放送受信用、広告表示用などの全ての情報表示用表示機器が含まれる。

30

【0169】

図 13 (C) はノート型パーソナルコンピュータであり、筐体 5401、表示部 5402、キーボード 5403、ポインティングデバイス 5404 等を有する。本発明の一態様に係る発光装置は、表示部 5402 に用いることができる。表示部 5402 に本発明の一態様に係る発光装置を用いることで、高画質のノート型パーソナルコンピュータを提供することができる。

40

【0170】

図 13 (D) は携帯情報端末であり、筐体 5601、表示部 5602、操作キー 5603 等を有する。図 13 (D) に示す携帯情報端末は、モジュムが筐体 5601 に内蔵されても良い。本発明の一態様に係る発光装置は、表示部 5602 に用いることができる。表示部 5602 に本発明の一態様に係る発光装置を用いることで、高画質の携帯情報端末を提供することができる。

【0171】

50

図13(E)は携帯電話であり、筐体5801、表示部5802、音声入力部5803、音声出力部5804、操作キー5805、受光部5806等を有する。受光部5806において受信した光を電気信号に変換することで、外部の画像を取り込むことができる。本発明の一態様に係る発光装置は、表示部5802に用いることができる。表示部5802に本発明の一態様に係る発光装置を用いることで、高画質の携帯電話を提供することができる。

【0172】

本実施の形態は、他の実施の形態と適宜組み合わせて実施することができる。

【0173】

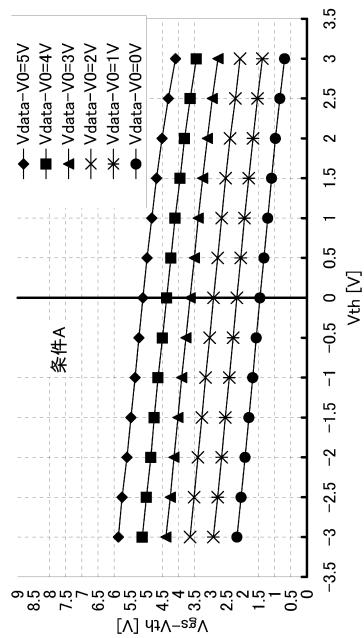

(実施の形態7)

10

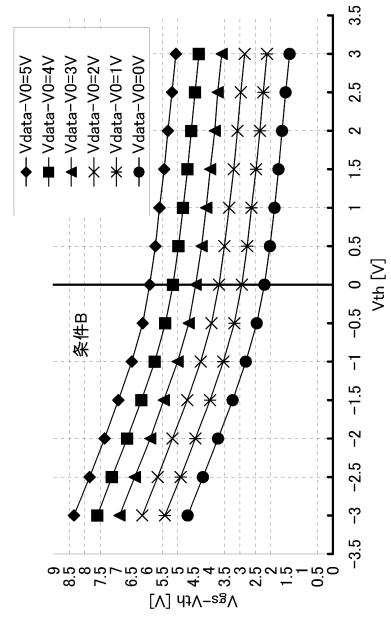

本実施の形態では、実施の形態1において説明した図1(A)に示す画素100の動作の、期間3における、トランジスタ11のゲート電圧 $V_{gs}$ の値を、シミュレーションにより求めた。

【0174】

シミュレーションは、配線ILにおける電位 $V_0$ の値が互いに異なる、条件Aまたは条件Bを用いて行った。具体的に、条件Aと条件Bにおける各配線の電位の値を、下記の表1に示す。電位GVDDは、配線G1、配線G2、及び配線G3にそれぞれ与えられるハイレベルの電位に相当する。また、電位GVSSは、配線G1、配線G2、及び配線G3にそれぞれ与えられるローレベルの電位に相当する。なお、表1では、電位 $V_{cat}$ を0Vとし、電位 $V_{data}$ 、電位 $V_{ano}$ 、電位 $V_0$ 、電位GVDD、電位GVSSの値を、電位 $V_{cat}$ との電位差で示している。

20

【0175】

【表1】

30

|            | 条件A     | 条件B     |

|------------|---------|---------|

| $V_{th}$   | -3V~3V  | -3V~3V  |

| $V_{data}$ | 10V~15V | 14V~19V |

| $V_0$      | 10V     | 14V     |

| $V_{ano}$  | 14V     | 14V     |

| $V_{cat}$  | 0V      | 0V      |

| GVDD/GVSS  | 20V/0V  | 25V/0V  |

【0176】

また、シミュレーションにおける各トランジスタのチャネル長Lとチャネル幅Wの比は、トランジスタ11では $L/W = 9\mu m/3\mu m$ 、トランジスタ12乃至トランジスタ15では $L/W = 3\mu m/3\mu m$ とした。そして、図1(A)に示した画素100が有する全てのトランジスタにおいて、ソースまたはドレインとして機能する導電膜と半導体膜とが接している領域を領域Aとすると、上記領域Aと、ゲート電極が形成されている領域とが重なる領域における、チャネル長方向の長さ( $L_{ov}$ )を、1.5μmとした。

40

【0177】

期間3では、トランジスタ11のゲート電圧 $V_{gs}$ は、図3(C)にて示したように、電圧 $V_{data} - V_0 + V_{th}$ となる。よって、図1(A)に示した画素100において、 $V_{gs} - V_{th} = V_{data} - V_0$ となるため、 $V_{gs} - V_{th}$ は、理想的には、閾値電圧 $V_{th}$ の値に関わらず一定の値を有する。

【0178】

図17に、条件Aを用いた場合における、シミュレーションにより得られた $V_{gs} - V_{th}$ の値を示す。図17では、横軸が閾値電圧 $V_{th}$ (V)、縦軸が $V_{gs} - V_{th}$ (V)の値を示す。図17では、閾値電圧 $V_{th}$ の値を変化させても、 $V_{gs} - V_{th}$ の値がほぼ均一であり、そのばらつきは25%~30%程度に抑えられていることが分かる。

50

## 【0179】

図18に、条件Bを用いた場合における、シミュレーションにより得られた $V_{gs} - V_{th}$ の値を示す。図18では、横軸が閾値電圧 $V_{th}$ (V)、縦軸が $V_{gs} - V_{th}$ (V)の値を示す。図18では、閾値電圧 $V_{th}$ の値が正の値を有する場合だと、 $V_{gs} - V_{th}$ の値が均一である。しかし、閾値電圧 $V_{th}$ の値が負の値を有する場合、閾値電圧 $V_{th}$ の値が負の方向に大きくなるほど、 $V_{gs} - V_{th}$ の値が大きくなっている、 $V_{gs} - V_{th}$ の値が閾値電圧 $V_{th}$ の値に依存していることが分かる。

## 【0180】

上記シミュレーションの結果から、本発明の一態様に係る発光装置では、トランジスタ11がノーマリオンであっても、すなわち閾値電圧 $V_{th}$ がマイナスの値を有していても、トランジスタ11の閾値電圧 $V_{th}$ を加味した値になるよう、トランジスタ11のゲート電圧 $V_{gs}$ を設定することができる事が証明された。

10

## 【0181】

本実施の形態は、他の実施の形態と組み合わせて実施することが可能である。

## 【符号の説明】

## 【0182】

|         |         |    |

|---------|---------|----|

| 1 1     | トランジスタ  | 20 |

| 1 2     | トランジスタ  |    |

| 1 3     | トランジスタ  |    |

| 1 4     | トランジスタ  |    |

| 1 5     | トランジスタ  |    |

| 1 6     | 容量素子    |    |

| 1 7     | 発光素子    |    |

| 1 0 0   | 画素      |    |

| 1 4 0 b | 画素      |    |

| 1 4 0 g | 画素      |    |

| 1 4 0 r | 画素      |    |

| 7 1 5 b | 陽極      |    |

| 7 1 5 g | 陽極      |    |

| 7 1 5 r | 陽極      |    |

| 7 3 0   | 隔壁      | 30 |

| 7 3 1   | EL層     |    |

| 7 3 2   | 陰極      |    |

| 7 4 0   | 基板      |    |

| 7 4 1 b | 発光素子    |    |

| 7 4 1 g | 発光素子    |    |

| 7 4 1 r | 発光素子    |    |

| 7 4 2   | 基板      |    |

| 7 4 3 b | 着色層     |    |

| 7 4 3 g | 着色層     | 40 |

| 7 4 3 r | 着色層     |    |

| 7 4 4   | オーバーコート |    |

| 7 4 5 b | 導電膜     |    |

| 7 4 5 g | 導電膜     |    |

| 7 4 5 r | 導電膜     |    |

| 7 4 6 g | 導電膜     |    |

| 7 4 6 r | 導電膜     |    |

| 7 5 0   | 絶縁膜     |    |

| 8 0 0   | 基板      |    |

| 8 0 1   | 導電膜     | 50 |

|         |          |    |

|---------|----------|----|

| 8 0 2   | ゲート絶縁膜   |    |

| 8 0 3   | 半導体膜     |    |

| 8 0 4   | 導電膜      |    |

| 8 0 5   | 導電膜      |    |

| 8 0 6   | 半導体膜     |    |

| 8 0 7   | 導電膜      |    |

| 8 0 8   | 導電膜      |    |

| 8 0 9   | 導電膜      |    |

| 8 1 0   | 導電膜      |    |

| 8 1 1   | 半導体膜     | 10 |

| 8 1 2   | 導電膜      |    |

| 8 1 3   | 半導体膜     |    |

| 8 1 4   | 導電膜      |    |

| 8 1 5   | 導電膜      |    |

| 8 1 6   | 導電膜      |    |

| 8 1 7   | 半導体膜     |    |

| 8 1 8   | 導電膜      |    |

| 8 1 9   | 導電膜      |    |

| 8 2 0   | 絶縁膜      |    |

| 8 2 1   | 絶縁膜      | 20 |

| 8 2 2   | 導電膜      |    |

| 8 2 3   | コンタクトホール |    |

| 8 2 4   | 絶縁膜      |    |

| 8 2 5   | EL層      |    |

| 8 2 6   | 導電膜      |    |

| 9 0 0   | 基板       |    |

| 9 0 1   | 半導体膜     |    |

| 9 0 2   | ゲート絶縁膜   |    |

| 9 0 3   | 導電膜      |    |

| 9 0 4   | 導電膜      | 30 |

| 9 0 5   | 導電膜      |    |

| 9 0 6   | 半導体膜     |    |

| 9 0 7   | 導電膜      |    |

| 9 0 8   | 導電膜      |    |

| 9 0 9   | 導電膜      |    |

| 9 1 1   | 導電膜      |    |

| 9 1 2   | 半導体膜     |    |

| 9 1 3   | 導電膜      |    |

| 9 1 4   | 導電膜      |    |

| 9 1 5   | 導電膜      | 40 |

| 9 1 6   | 導電膜      |    |

| 9 1 7   | 導電膜      |    |

| 9 2 0   | 絶縁膜      |    |

| 9 2 1   | 導電膜      |    |

| 9 2 2   | コンタクトホール |    |

| 9 2 3   | 絶縁膜      |    |

| 9 2 4   | EL層      |    |

| 9 2 5   | 導電膜      |    |

| 1 6 0 1 | パネル      |    |

| 1 6 0 2 | 回路基板     | 50 |

|         |             |    |

|---------|-------------|----|

| 1 6 0 3 | 接続部         |    |

| 1 6 0 4 | 画素部         |    |

| 1 6 0 5 | 走査線駆動回路     |    |

| 1 6 0 6 | 信号線駆動回路     |    |

| 5 0 0 1 | 筐体          |    |

| 5 0 0 2 | 筐体          |    |

| 5 0 0 3 | 表示部         |    |

| 5 0 0 4 | 表示部         |    |

| 5 0 0 5 | マイクロホン      | 10 |

| 5 0 0 6 | スピーカー       |    |

| 5 0 0 7 | 操作キー        |    |

| 5 0 0 8 | スタイルス       |    |

| 5 2 0 1 | 筐体          |    |

| 5 2 0 2 | 表示部         |    |

| 5 2 0 3 | 支持台         |    |

| 5 4 0 1 | 筐体          |    |

| 5 4 0 2 | 表示部         |    |

| 5 4 0 3 | キー ボード      |    |

| 5 4 0 4 | ポインティングデバイス |    |

| 5 6 0 1 | 筐体          | 20 |

| 5 6 0 2 | 表示部         |    |

| 5 6 0 3 | 操作キー        |    |

| 5 8 0 1 | 筐体          |    |

| 5 8 0 2 | 表示部         |    |

| 5 8 0 3 | 音声入力部       |    |

| 5 8 0 4 | 音声出力部       |    |

| 5 8 0 5 | 操作キー        |    |

| 5 8 0 6 | 受光部         |    |

| 6 0 3 1 | トランジスタ      |    |

| 6 0 3 3 | 発光素子        | 30 |

| 6 0 3 4 | 陽極          |    |

| 6 0 3 5 | E L 層       |    |

| 6 0 3 6 | 陰極          |    |

| 6 0 3 7 | 絶縁膜         |    |

| 6 0 3 8 | 隔壁          |    |

| 6 0 4 1 | トランジスタ      |    |

| 6 0 4 3 | 発光素子        |    |

| 6 0 4 4 | 陽極          |    |

| 6 0 4 5 | E L 層       |    |

| 6 0 4 6 | 陰極          | 40 |

| 6 0 4 7 | 絶縁膜         |    |

| 6 0 4 8 | 隔壁          |    |

| 6 0 5 1 | トランジスタ      |    |

| 6 0 5 3 | 光素子         |    |

| 6 0 5 4 | 陽極          |    |

| 6 0 5 5 | E L 層       |    |

| 6 0 5 6 | 陰極          |    |

| 6 0 5 7 | 絶縁膜         |    |

| 6 0 5 8 | 隔壁          |    |

【図面】

【図 1】

【図 2】

10

20

【図 3】

【図 4】

30

40

50

【図5】

【図6】

【図7】

【図8】

10

20

30

40

50

【図9】

【図10】

10

【図11】

【図12】

30

40

50

【図 1 3】

【図 1 4】

10

20

30

40

【図 1 5】

【図 1 6】

50

【図17】

【図18】

10

20

30

40

50

## フロントページの続き

## (51)国際特許分類

H 1 0 K 50/00 (2023.01)

F I

H 1 0 K 59/12

H 0 5 B 33/02

H 0 5 B 33/14

A

## (33)優先権主張国・地域又は機関

日本国(JP)

## (56)参考文献

特開2003-317961 (JP, A)

特開2010-049056 (JP, A)

特開2011-043830 (JP, A)

特開2007-005766 (JP, A)

特開2003-295793 (JP, A)

特開2004-047410 (JP, A)

米国特許出願公開第2005/0243035 (US, A1)

中国実用新案第201904343 (CN, U)

## (58)調査した分野 (Int.Cl., DB名)

G 0 9 F 9 / 0 0 - 4 6

G 0 9 G 1 / 0 0 - 5 / 4 2

H 0 5 B 3 3 / 0 0 - 3 3 / 2 8

4 4 / 0 0

4 5 / 6 0

H 1 0 K 5 0 / 0 0 - 9 9 / 0 0