US 20090174464A1

### (19) United States

# (12) Patent Application Publication Kapoor et al.

(54) APPARATUS AND METHOD FOR IMPROVED LEAKAGE CURRENT OF SILICON ON INSULATOR TRANSISTORS USING A FORWARD BIASED DIODE

(76) Inventors: Ashok Kumar Kapoor, Palo Alto, CA (US); Robert Strain, San Jose, CA (US)

Correspondence Address:

GLENN PATENT GROUP 3475 EDISON WAY, SUITE L MENLO PARK, CA 94025 (US)

(21) Appl. No.: 12/348,797

(22) Filed: Jan. 5, 2009

### Related U.S. Application Data

(63) Continuation-in-part of application No. 11/737,559, filed on Apr. 19, 2007, which is a continuation of application No. 11/029,542, filed on Jan. 4, 2005, now Pat. No. 7,224,205. (10) **Pub. No.: US 2009/0174464 A1**(43) **Pub. Date:**Jul. 9, 2009

(60) Provisional application No. 60/585,582, filed on Jul. 7, 2004, provisional application No. 60/601,979, filed on Aug. 17, 2004.

### **Publication Classification**

(51) Int. Cl. H03K 3/01 (2006.01) H01L 27/12 (2006.01) H01L 21/8238 (2006.01) H01L 21/336 (2006.01)

(52) **U.S. Cl.** ........ **327/534**; 257/350; 438/154; 438/155; 257/E27.112; 257/E21.632; 257/E21.409

### (57) ABSTRACT

Use of a forward biased diode to reduce leakage current of transistors implemented on silicon on insulator (SOI) is a particular challenge due to the difficulty of achieving effective contact with the region beneath the gate of the transistor. An improved implementation in SOI gate fingers that reach under the source through tunnels that are contacted with a region outside the transistor. A further embodiment uses drain extension implants to provide good channel connection.

FIGURE 1 (PRIOR ART)

FIGURE 2 (PRIOR ART)

FIGURE 3b

### APPARATUS AND METHOD FOR IMPROVED LEAKAGE CURRENT OF SILICON ON INSULATOR TRANSISTORS USING A FORWARD BIASED DIODE

## CROSS REFERENCE TO RELATED APPLICATIONS

[0001] This application is a continuation-in-part of U.S. patent application Ser. No. 11/737,559, filed Jan. 4, 2005, which is a continuation of U.S. Pat. No. 7,224,205, which claims priority from U.S. provisional application Ser. Nos. 60/585,582, filed Jul. 7, 2004, and 60/601,979, filed Aug. 17, 2004, and claims priority from U.S. provisional patent application Ser. No. 61/006,307, filed Jan. 4, 2008, each of which is incorporated herein in its entirety by this reference thereto.

### BACKGROUND OF THE INVENTION

[0002] The invention relates to MOS transistors implemented on SOI. More particularly, the invention relates to the improvement of drive-strength and leakage of deep submicron MOS transistors on SOI.

### DESCRIPTION OF THE PRIOR ART

[0003] The use of metal oxide semiconductor (MOS) transistors implemented on silicon-on-insulator (SOI) is well known in the art. The SOI technology, while having various complexities, provides certain advantages over bulk MOS transistors. While transistors implemented on SOI tend to have a lower current leakage than bulk MOS transistors there is still a need in the art to reduce such currents further, especially in the deep submicron, i.e., under 100, nanometers technologies.

[0004] The prior art suggests various approaches to connecting a device between the gate and the substrate of the MOS, transistor primarily to control threshold voltages. One such approach is described in detail in a U.S. Pat. No. 7,224, 205 (the '205 patent), entitled Apparatus and Method for Improving Drive-Strength and Leakage of Deep Submicron MOS Transistors, assigned to common assignee, and which is incorporated herein in its entirety by this reference thereto. The connection of a forward biased diode between the gate and the well of a MOS transistor is shown in the '205 patent. Such approach enables the change of threshold voltage of the MOS transistor as a function of the input voltage, and thereby provides the benefits described therein in more detail.

[0005] Implementing such a solution for MOS transistors that are implemented on SOI requires certain considerations due to the limitations of SOI and, more specifically, due to partially depleted SOI, because there is a problem in making an effective contact with the region beneath the gate. While Pelloie in U.S. Pat. No. 6,787,850 suggests a dynamic threshold voltage MOS transistor that is fitted with a current limiter, Pelloie does overcome the stated limitation.

[0006] It would be therefore advantageous to provide an approach that improved drive strength and leakage of deep submicron MOS transistors that are implemented in SOI.

### BRIEF DESCRIPTION OF THE DRAWINGS

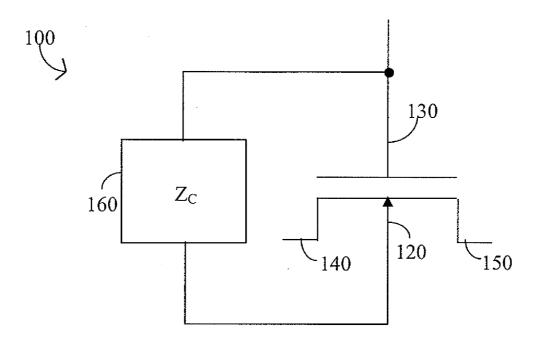

[0007] FIG. 1 is a schematic diagram showing a control circuit  $Z_c$  connected between the gate and substrate terminals of a NMOS transistor (prior art);

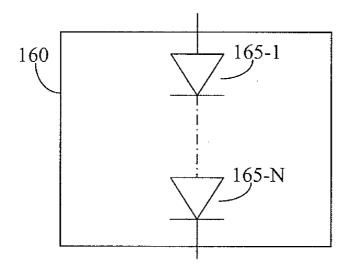

[0008] FIG. 2 is a schematic diagram showing the control circuit  $Z_c$  (prior art);

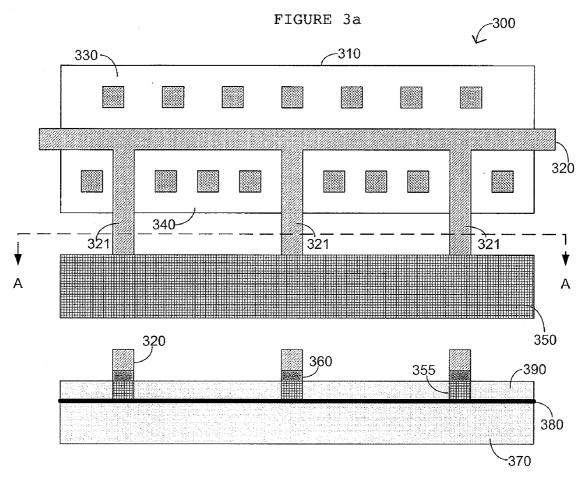

[0009] FIG. 3a is a plan view and FIG. 3b is a section view of a MOS transistor comprising a well contact area, and cross section thereof, in accordance with an embodiment of the invention; and

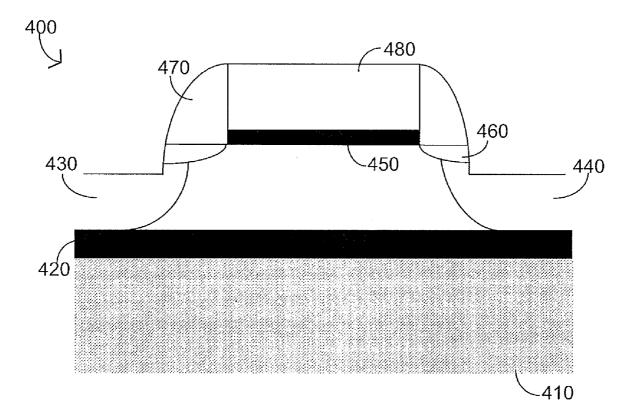

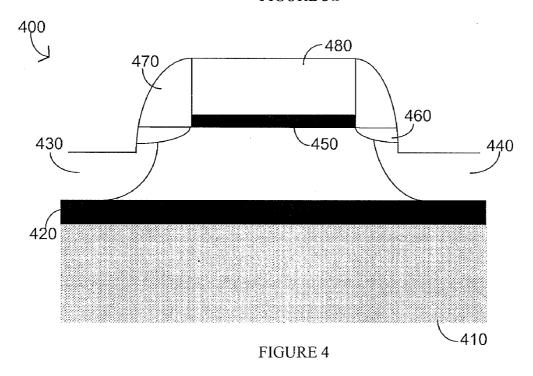

[0010] FIG. 4 is a cross section view of a MOS transistor formed over a SOI wafer in accordance with an embodiment of the invention.

### DETAILED DESCRIPTION OF THE INVENTION

[0011] The use of a forward biased diode to reduce leakage current in metal-oxide semiconductor (MOS) transistors implemented on silicon on insulator (SOI) is a particular challenge because it is difficult to achieve effective contact with the region beneath the gate of the transistor. This is particularly true for a MOS transistor that is fabricated on partially depleted SOI. An improved implementation in SOI that includes the use of gate fingers that reach under the source through tunnels that are contacted with a region outside the transistor is disclosed. A further embodiment uses drain extension implants to provide a good channel connection.

[0012] FIG. 1 shows a prior art circuit 100 that is discussed in detail in U.S. Pat. No. 7,224,205, assigned to common assignee, and which is incorporated herein in its entirety by this reference thereto. In an N-type metal-oxide semiconductor (NMOS) transistor comprising a substrate 120, a gate 130, a drain 140, and a source 150, a control circuit  $Z_c$  160 connected between the gate 130 and this substrate 120. This control circuit  $Z_c$  implements a dynamic voltage control by using, for example, various types of diodes to control substrate voltage. By providing for threshold voltages in the ON and OFF states of the controlled NMOS transistor, an improvement in drive current in the ON state and leakage current in the OFF state is achieved. Furthermore, an extremely area efficient implementation of dynamic threshold voltage control is provided as described in further detail below:

[0013] FIG. 2 shows details of control circuit 160 that is comprised of one or more diodes 165 connected in series. The threshold voltage is dynamically adjusted by varying the diode layout geometry. No significant variations in the manufacturing process are required. The diodes are fabricated using a variety of techniques. One such technique uses diffused diodes. These diodes are conventional diodes that are fabricated by diffusing n-type and p-type layers in a completely isolated structure. The voltage across the diodes is controlled by adjusting the doping profiles in silicon and programming the area, thereby controlling the voltage drop across the diode. In one embodiment, a capacitor (not shown) is connected in parallel with the diodes 165. Such embodiment is disclosed in U.S. patent application Ser. No. 11/533, 332, entitled Apparatus and Method for Improving Drive-Strength and Leakage of Deep Submicron MOS Transistors, assigned to common assignee, and incorporated herein in its entirety by this reference thereto.

[0014] While the solutions discussed above are applicable to both bulk MOS and SOI MOS, application of the invention SOI requires specific consideration due to its unique structure. A cross section of an SOI wafer is shown in FIG. 3, in which the bare wafer is formed of two or three layers, including a thin active silicon layer 390 and a thick foundation 370. The thick foundation 370 may be made of materials such as silicon, sapphire, or glass. An insulating layer 380 is provided between the foundation 370 and the active silicon layer 370,

if the foundation layer 370 is a non-insulating material, such as silicon. The manufacturing process for such wafers is outside the scope of this disclosure and therefore not discussed herein. A person skilled in the art will note, however, that the thin silicon layer 380 provides for a limited depth of source and drain junctions of a MOS transistor that is diffused into this area. Due to the limited thickness of the silicon layer 390, the resistivity of the semiconductor region under the gate is increased. As a result, when applying the control circuit 160, where the contact to silicon under the gate is made from the edges along the length of the transistor, a large series resistance is encountered. The effectiveness of this method is reduced when used with a large series resistance which results from larger than minimum sized transistors. The major challenge for applying an adaptive threshold voltage to the MOS transistor is contacting to the region beneath the gate with minimal parasitic resistance. Pelloie resolved this problem by abutting a device to one side of the transistor. However, this is not an effective solution for transistors of large width W because of voltage variations from the contact region across the transistor.

[0015] Therefore, a different approach is taught herein with respect to FIG. 3. A MOS transistor 310 is formed in an SOI wafer having a drain region 330 which is N+ for a NMOS transistor, a source region 340 which is N+ for a NMOS transistor, and a gate 320, typically made of poly silicon and placed over the area 310 that comprises the transistor. The MOS transistor further comprises one or more gate fingers 321 that extend from the gate 320. The gate fingers 321 protect the silicon film from the source/drain implants. This approach creates tunnels of the P-silicon 355, surrounded by the N+ source region, that can be contacted with a P+ silicon, thereby creating a well contact region 350 that is located outside of the transistor 310. The region created by the P+substrate 350 is the well contact that may be used to contact the control circuit 160, or specifically a diode 165, for example a poly diode, to make the required connection to the well. This approach ensures an effective connection of the diode 165 to the well of the NMOS transistor to make effective use of its capability to improve drive strength or leakage current when the NMOS transistor is implemented on an SOI wafer. In one embodiment of the invention, the poly gate over the connecting fingers 321 acts as a feed-forward capacitor. Further, a poly diode 165 may be created in the single crystal silicon, contiguous with the well contact region 350. It should be noted that the dimensions of the device depicted in FIG. 3 are provided for illustration only and should not be considered as design rules. Rather, the principle of creating the gate fingers for the purpose of creating an effective well contact for a MOS transistor fabricated in SOI is shown. A person skilled in the art would appreciate that the implementation is equally applicable for PMOS transistors with the appropriate adjustments to account for the different polarity.

[0016] As noted above, the region 390 of an SOI wafer is relatively thin, resulting in a relatively shallow active substrate for the MOS transistor implemented on such wafers. One problem with this is that the SOI side thin films may have a rather small conductance, which may prove ineffective in changing the leakage characteristics of the MOS transistor 310. This problem can be alleviated by targeting a thicker substrate film. If this film is so thick that it becomes impossible to bottom out the source and drain regions on the underlying insulator reliably, then that problem can be solved by

thinning the source and drain silicon by processes, such as etching, after spacer formation, but the N+ and P+ implants. [0017] Reference is now made to a cross-section of an MOS transistor implemented on an SOI wafer, as shown in FIG. 4. The SOI wafer consists of a foundation layer 410 and an SiO<sub>2</sub> insulating layer 420. The active silicon over the insulating layer 420 is used for the creation of the MOS transistor. Areas 430 and 440 form the source and drain of the MOS transistor. Layer 450 is an SiO<sub>2</sub> layer that insulates the channel 490 of the MOS transistor from the gate electrode 480, which is made of polysilicon and placed over insulating layer 450. Areas 470 are spacers made, for example, from Si<sub>3</sub>N<sub>4</sub>, and area 460 is used for the lightly doped drain (LDD) structure. Therefore, a gate electrode 480 is formed over insulator 450. SiN<sub>4</sub> is deposited in the regions 470 to create spacers. After a nitride etch, the silicon over the regions where the source and drain areas 430 and 440 are to be placed is further etched. This step is performed when the gate 480 is covered by a thin oxide. The etch is performed until such level where it is possible to bottom out the source and drain regions 430 and 440, as shown in FIG. 4, i.e. that the source and drain implants can reach through the active silicon layer all the way to the insulating layer 420. Once done, an implant takes place to form the desired source, drain, and gate areas, that is N+ or P+ as the case may be.

[0018] Accordingly, although the invention has been described in detail with reference to a particular preferred embodiment, persons possessing ordinary skill in the art to which this invention pertains will appreciate that various modifications and enhancements may be made without departing from the spirit and scope of the claims that follow.

- 1. A semiconductor apparatus, comprising:

- a well area having a first doping type of a metal-oxidesilicon (MOS) transistor formed on a silicon-on-insulator (SOI) wafer;

- a polysilicon gate of said MOS transistor positioned over said well area for separating a source region and a drain region, both of a second doping type, of said MOS transistor:

- a gate oxide separating all portions of said well area from overlying polysilicon regions;

- a doped region of said first doping type for enabling contact to said well area:

- at least one finger of thin film silicon extending from said well area of said MOS transistor to abut with said doped region, said at least one finger being protected from a source of said second doping type and a drain doping of said second doping type, such that an extension of said at least one finger beyond said well area retains a doping character of said first doping type and form a connectivity tunnel through said source of said second doping type or said drain of said second doping type to said doped region of said first doping type.

- 2. The apparatus of claim 1, further comprising:

- a forward biased diode connected between said gate and said well area through said doped region.

- 3. The apparatus of claim 2, wherein said forward biased diode comprises a junction diode.

- **4**. The apparatus of claim **2**, wherein said forward biased diode is formed from polycrystalline silicon.

- 5. The apparatus of claim 2, wherein said forward biased diode is formed as a single crystal silicon from said doped region.

- 6. The apparatus of claim 1, further comprising:

- a feed forward capacitor connected between said gate and said well area through said doped region.

- 7. The apparatus of claim 1, wherein said well contacting doped region comprises a P+ region for an N-type MOS transistor.

- **8**. The apparatus of claim **1**, wherein said well contacting doped region comprises an N+ region for a P-type MOS transistor.

- **9.** A method of manufacturing a semiconductor device, comprising the steps of:

- forming a well area having a first doping type for a metaloxide-silicon (MOS) transistor on a silicon-on-insulator (SOI) wafer:

- forming a polysilicon gate of said MOS transistor over said well area to separate a source region and a drain region, both of a second doping type, of the MOS device;

- forming a gate oxide to separate all portions of said well area from overlying polysilicon regions;

- forming a doped region of said first doping type to enable contact to said well area;

- forming at least one finger of thin film silicon that extends from said well area of said MOS transistor to abut with said doped region; and

- protecting said at least one finger from source/drain doping of a second doping type;

- wherein said at least one finger that extends from said well area retains a doping character of said first doping to form a connectivity tunnel through an oppositely doped source region or oppositely doped drain region to said doped region.

- 10. The method of claim 9, further comprising the step of: forming a forward biased diode connected between said gate and said well area through said doped region.

- 11. The method of claim 10, wherein said forward biased diode comprises a junction diode.

- 12. The method of claim 10, further comprising the step of: forming said forward biased diode from polycrystalline silicon.

- 13. The method of claim 10, further comprising the step of: forming said forward biased diode as a single crystal silicon from said doped region.

- 14. The method of claim 9, further comprising the step of: forming a feed forward capacitor connected between said gate and said well area through said doped region.

- **15**. The method of claim **9**, further comprising the step of: forming said doped region by creating a P+ region for an N-type MOS transistor.

- 16. The method of claim 9, further comprising the step of: forming said doped region by creating a N+ region for a P-type MOS transistor.

- 17. A method of manufacturing a semiconductor device, comprising the step of:

- forming a polysilicon gate over a thin layer of insulator created over an active area of a silicon-on-insulator (SOI) wafer;

depositing nitride for a spacer;

performing a nitride etch;

performing a silicon etch to a level that bottoms out a drain and a source region of a MOS transistor formed over said SOI; and

implanting a drain, source and gate of said MOS transistor; wherein said MOS transistor is formed on said SOI having a thick active layer over an insulator of said SOI.

- 18. The method of claim 17, further comprising the step of: forming a forward biased diode connected between said gate and said well area through said doped region.

- 19. The method of claim 18, wherein said forward biased diode comprises a junction diode.

- 20. The method of claim 18, further comprising the step of: forming said forward biased diode from polycrystalline silicon.

- 21. The method of claim 18, further comprising the step of: forming said forward biased diode as a single crystal silicon from said doped region.

\* \* \* \* \*