(19) 日本国特許庁(JP)

## (12) 公表特許公報(A)

(11) 特許出願公表番号

特表2004-503089

(P2004-503089A)

(43) 公表日 平成16年1月29日(2004.1.29)

(51) Int.Cl.<sup>7</sup>

H01L 21/768

F 1

H01L 21/90

テーマコード(参考)

A

5 F 0 3 3

審査請求 有 予備審査請求 有 (全 35 頁)

(21) 出願番号 特願2002-507438 (P2002-507438)

(86) (22) 出願日 平成13年7月2日 (2001.7.2)

(85) 翻訳文提出日 平成14年12月27日 (2002.12.27)

(86) 國際出願番号 PCT/US2001/021161

(87) 國際公開番号 WO2002/003457

(87) 國際公開日 平成14年1月10日 (2002.1.10)

(31) 優先権主張番号 09/608,540

(32) 優先日 平成12年6月30日 (2000.6.30)

(33) 優先権主張國 米国(US)

(81) 指定國 EP(AT, BE, CH, CY, DE, DK, ES, FI, FR, GB, GR, IE, IT, LU, MC, NL, PT, SE, TR), JP, KR

(71) 出願人 501209070

インフィネオン テクノロジーズ アクチ

エンゲゼルシャフト

ドイツ連邦共和国 81669 ミュンヘ

ナン ザンクト マルティン シュトラーセ

53

(71) 出願人 500460058

インターナショナル ビジネス マシーン

ズ コーポレイション

アメリカ合衆国, 10504 ニュー ヨ

ーク州, アーモンク, ニュー オーチャー

ド ロード

(74) 代理人 100080034

弁理士 原 謙三

最終頁に続く

(54) 【発明の名称】銅のメタライゼーションに関するピアファーストのデュアルダマシン法

## (57) 【要約】

配線パターンが、銅が充填されたパターンから成るピア及びトレンチを備えた、シリコンウェハの表面上に形成される。ピア及びトレンチを充填するプロセスは、エッチストップとしてのシリコンニトリドフィルムの使用と、反射防止コーティングによりピアを充填することを具備している。

**【特許請求の範囲】****【請求項 1】**

半導体ウェハ上に形成するための方法であって、

半導体ウェハの中に及び／またはその上において、

誘電性接触領域を備え、半導体ウェハの上面に重ねあわせている絶縁層を貫通する複数のビアおよびいくつかのトレンチにて、銅を使用する配線パターンを有しているデバイスを備えており、

上記デバイス上に第1の絶縁層を形成するステップ；

第1の絶縁層の上面からビアを形成することで、上記ビアがデバイスの接触領域と導通するステップ；

導体によりビアを充填するステップ；

第1の絶縁層上に第2の絶縁層を形成するステップ；

第1の絶縁層の導体が充填されたビアと導通している第2の絶縁層を貫通して、ビアを形成するステップ；

第2の絶縁層を貫通して、銅によりビアを充填するステップ；

第2の絶縁層の上面上に、第3の絶縁層を形成するステップ；

第3の絶縁層の上面上に、上記第3の絶縁層に比べて異なるエッチング特性を有する第4の絶縁層を形成するステップ；

第3の絶縁層により、第2の絶縁層を貫通して銅が充填されたビアから分離されるが、第2の絶縁層を貫通しているビアの位置と合わせるようにビアを形成するため、第4の絶縁層のパターンを形成し、エッチングするステップ；

第4の絶縁層の上面上に、反射防止層を形成することで、反射防止材料によりビアを充填するステップ；

反射防止層および材料のパターンを形成して、第4の絶縁層にてトレンチの範囲を規定するステップ；

反射防止層および第4の絶縁層の部分を取り除いて、第4の絶縁層を貫通しているビアの上位部分と通じている第4の絶縁層にて、トレンチを形成し、上記第4の絶縁層を貫通するビアおよび、第2と第4の絶縁層のビア間にある第3の絶縁層部分において、反射防止材料を取り除くステップ；

第4の絶縁層および取り除かれた第3の絶縁層の部分において、トレンチおよびビアを銅により充填するステップを有することを特徴とする方法。

**【請求項 2】**

上記第4の絶縁層のビアおよびトレンチは、銅によりはみ出るまで充填され、生成された構成を平坦化するために化学的機械研磨が用いられることを特徴とする請求項1に記載の方法のプロセス。

**【請求項 3】**

上記第1の絶縁層がBPSG、第2および第4の絶縁層がシリコンオキシド、第3の絶縁層がシリコンニトリドであることを特徴とする請求項1に記載の方法。

**【請求項 4】**

上記導体は、タンゲステンであることを特徴とする請求項1に記載の方法。

**【請求項 5】**

上記導体は、アルミニウムであることを特徴とする請求項1に記載の方法。

**【請求項 6】**

第1の絶縁層を貫通して、分離しているビア各々と導通しており、導体により各々充填されているトレンチを第1の絶縁層の上面にて形成するステップ；

第1の絶縁層のビアおよびトレンチを、はみ出るまで導体により充填し、化学的機械研磨を用いて双方を平坦化するステップ；

第2の絶縁層の分離しているビア各々と導通しており、銅により各々充填されているトレンチを第2の絶縁層の上面にて形成するステップ；

第2の絶縁層のビアおよびトレンチを、はみ出るまで銅により充填し、化学的機械研磨を

用いて双方を平坦化するステップを有することを特徴とする請求項 1 に記載の方法。

【請求項 7】

反射防止層および反射防止材料は、第 3 の絶縁層に比べて異なるエッチング率を有することを特徴とする請求項 7 に記載の方法。

【請求項 8】

上記反射防止層および反射防止材料は、ともに DUV30 であることを特徴とする請求項 12 に記載の方法。

【請求項 9】

上記シリコンニトリド層は、PECVD によって堆積されることを特徴とする請求項 7 に記載の方法。

10

【請求項 10】

半導体ウェハに重ねあわせている絶縁層内にあり、上記ウェハの上面に対して並列に伸びているトレンチに銅線を備えており、絶縁層を垂直に貫通するようにのびているビアを銅により充填している配線パターンを半導体ウェハ上に形成するための方法であって、

半導体ウェハの上面上に第 1 の絶縁層を形成するステップ；

第 1 の絶縁層の上層面にトレンチを形成し、上記トレンチと導通しており、トレンチの底から第 1 の絶縁層を貫通してデバイスの接触領域と導通しているビアを形成するステップ；

第 1 の絶縁層のビアおよびトレンチを、接触金属によってはみ出るまで充填し、半導体ウェハ上に第 1 の平面を残すように平坦化するステップ；

20

第 1 の絶縁層を充填したメタル上に、第 2 の絶縁層を形成するステップ；

第 2 の絶縁層にてビアおよびトレンチを形成し、ビア及びトレンチを銅によりはみ出るまで充填するステップ；

第 2 の絶縁層を充填した銅に第 2 の平面を形成するステップ；

上記平坦化した面上に、シリコンニトリド層を形成するステップ；

シリコンニトリド層に比べて異なるエッチング率を有する第 3 の絶縁層を、シリコンニトリド層上に堆積するステップ；

第 3 の絶縁層のパターンを形成することで、下層にある銅と合わせられたビア、エッチストップとして働くシリコンニトリドフィルムを形成するステップ；

結果としてビアもまた充填することとなる、第 3 の絶縁層の上面上に、反射防止材料層を形成するステップ；

反射防止層および反射防止材料を充填したビア上に、フォトレジスト層を堆積するステップ；

フォトレジストのパターンを形成し、ビアの反射防止層および反射防止材料の露出した部分ならびに第 3 の絶縁層部分をエッチングして、第 3 の絶縁層にトレンチを形成するステップ；

パターンをなしたフォトレジストを取り除き、ビアから反射防止材料を、そして第 2 と第 3 の絶縁層との間のシリコンニトリド部分を取り除き、その結果、第 2 の絶縁層のビアの 1 つとつながっている第 3 の絶縁層にて、各トレンチおよび該トレンチの下にあるビアとなるステップ；

40

第 3 の絶縁層のビアおよびトレンチ、ならびにシリコンニトリド層の開口を、銅によりはみ出るまで充填し、表面を平坦化して、ビアおよびトレンチを充填する第 2 の銅を、シリコンニトリド層の開口を通って第 2 の絶縁層にあるビアにて銅に接触している第 3 の絶縁層に残すステップを有することを特徴とする方法。

【請求項 11】

第 1 の絶縁層は BPSG であり、第 2 および第 3 の絶縁層は、シリコンオキシドからなることを特徴とする請求項 10 に記載のプロセス。

【請求項 12】

化学的機械研磨は、絶縁層の表面がメタルにより充填された後、上記絶縁層の表面を平坦化するために用いられることを特徴とする請求項 10 に記載のプロセス。

50

**【請求項 13】**

上記接触金属は、タンゲステンであることを特徴とする請求項10に記載の方法。

**【請求項 14】**

上記接触金属は、アルミニウムであることを特徴とする請求項10に記載の方法。

**【請求項 15】**

上記反射防止層および反射防止材料は、第3の絶縁層と比べて異なるエッティング率を有することを特徴とする請求項10に記載の方法。

**【請求項 16】**

反射防止層および反射防止材料は、ともにDUV30であることを特徴とする請求項15に記載の方法。

**【請求項 17】**

シリコンニトリド層は、PECVDによって成膜されていることを特徴とする請求項10に記載の方法。

**【発明の詳細な説明】****(発明の技術分野)**

本発明は、半導体シリコンウェハのラインの後工程 (the back-end-of-the-line processing) 部材としてディスクリート回路部品を配線するために、銅を用いる集積回路装置に関するものであり、特には、デュアルダマシン法にて、トレンチより先にビアがエッティングされる場合、ケミカルエッティングがなされている間、銅を保護することが必要なウェハ工程での改良に関するものである。

**【0001】****(本発明の背景)**

高速集積回路 (faster integrated circuits) に対する需要によって、技術者は、より小さいチップ上に、半導体の部品を形成し、記録密度を増加させるようとしている。この需要の結果、冶金学的配線 (interconnect metalurgy) は、アルミニウムベースの金属からより固有抵抗の小さい銅を用いるように移行した。銅は、より高い導電性を有し、低コストであるので、回路部品を配線するのに非常に好ましい。また、銅は、AlまたはAl-Cuよりもエレクトロマイグレーションを抑制するのにより適した電気抵抗を有しており、より信頼性が高い。

**【0002】**

銅は、大変好ましい電気的特性を有しているが、いくつかの一般的に用いられる処理ケミカル (processing chemicals) に接触すると、酸化し腐食する傾向がある。それ故、処理中に銅が曝された場合、つまり銅が覆われていない場合に上記したような周りの環境から影響を受けないようにした銅を用いたメタライゼーションを配線に用いるプロセスは重大である。ラインの後工程における配線材料AlおよびAl-Cuのメタライゼーションは、これらの材料の金属表面を覆っている保護酸化物のため、腐食は抑制される。

**【0003】**

シングル又はデュアルダマシン法が用いられた場合、銅は、ラインの後工程用金属として非常に発展性のある材料である。ダマシン法は、絶縁層に形成された一連のトレンチに用いる。トレンチが銅によりはみ出るまで充填された後、化学的機械研磨 (CMP) は、あふれ出た銅を取り除くために使われる。そしてトレンチは、ビアから区別されるようになる。トレンチは、伸ばされた溝であり、概してシリコンチップの上面と並列に伸ばされており、ラインの後工程と同じ階層に配線回路のパターンが形成される。一方、ビアは孔であり、概して上記面の法線となるようにのばされており、層間にて金属線を接合するようパターンが形成される。

**【0004】**

現在の技術では、「トレンチを先に」処理するように取りかかる方法が取られている。当初は、比較的厚いシリコンニトリドフィルムの多層を要求したので、「ビアを先に」処理するように取りかかる方法で妥協された。処理中に銅を保護するシリコンニトリドは、必

ず、多くの電極作用面の後に残る。しかしながら、これらのシリコンニトリド層は、上記したシリコンニトリドの堆積の絶縁特性が実質的に増加し、回路性能を低下させることになった。しかし仮に、シリコンニトリドフィルムが薄層に作られたならば、シリコンニトリドフィルムは、ビアをエッチングしている間に劣化したであろうし、また、ビアのエッチングは、トレンチの範囲を規定している酸化物にまでエッチングを施すことになったであろう。0.25 μmの設計基準 (ground rule) である場合には、ライン範囲の規定での些細な変化でさえ、信頼性に対する深刻な問題が生じる。

#### 【0005】

銅は、その周りの影響に非常に敏感であることが知られているので、概して硫黄を含有するフォトレジストと酸化を促すケミカルとは、処理中に銅の表面に接触することは許されない。本発明のシリコンニトリドは、銅の層を保護するものとしておよびエッチストップとしての両方で用いられる。

10

#### 【0006】

しかしながら、「トレンチを先に」処理するように取りかかる方法もまた限界がある。この限界とは、ウェハのフォトリソグラフィ処理と関連するものである。トレンチの構成が、異なるフォトレジストの厚さを招来する場合に困難が生じる。上記厚さの変化は、例えばDRAMにより要求されるものとして、幅広なトレンチ（広幅ライン）または、非常に緻密なトレンチ（密な空間、狭いライン）が知られており、ビアイメージのプリントの歪みを引き起こす。

20

#### 【0007】

本発明は、ビアとトレンチとの同時エッチングを行う間、シリコンニトリドがダメージを受けないことを保証する新規性のある方法を用いる一方で、銅を覆うシリコンニトリドの保護層を提供することを目的とする。

#### 【0008】

##### （本発明の概要）

本発明は、デュアルダマシン法を用いて、不動態層にビア（開口、孔）およびトレンチ（溝）を形成するための、好ましい「ビアを先に」処理するように取りかかる方法の使用に関する。

#### 【0009】

実施例において、接触冶金 (contact metallurgy) は、ガラス層 [ 例えれば、ボロンホスホシリケイトガラス (boron phosphosilicate glass) (BPSG) ] のパターンを形成するように成膜させて、上記ガラスは、平坦化される。シリコンオキシドのような異なる絶縁材料が、上記ガラス層上に成膜され、接触面にあわせた浅いビア開口を形成するようにパターンが形成される。ビアは、銅で充填され、ビアの表面は、化学的機械研磨により平坦化される。薄いシリコンニトリド層は、保護層 / エッチストップとしての役目を担うように平坦化された絶縁材料面上に成膜される。

30

#### 【0010】

$\text{SiO}_2$  層は、シリコンニトリド層上に成膜され、従来のフォトリソグラフ技術によってパターンを形成され、 $\text{SiO}_2$  層の中に最初に形成したビアに合わせてビア孔を形成する。

40

#### 【0011】

本発明における新しい使用は、ウェハ上に回転塗布された反射防止膜 (ARC) を有利に構成する。ARCのコーティングは、ビアを充填し、薄いARC層で残りの表面を覆う。所定位置にARC材料があれば、フォトレジストは、ウェハ上に回転塗布して、トレンチの構成を形成するようにパターンを形成する。ビアを含む $\text{SiO}_2$ 層は、トレンチを形成するため再度エッチングされる。トレンチのエッチングを行う間、 $\text{SiO}_2$ とは異なる割合でだが、ARC材料もまたエッチングされる。この異なるエッチング率の結果、トレンチオープンプロセス (trench open process) が終了した後、ARC材料のプラグは上記ビアの底に残ったままである。上記ARCプラグは、シリコンニトリド

50

が分解してしまうことから保護し、そしてひいては、エッティング液が銅と接触しないように下層の銅を保護する。

【0012】

このために、本発明の1つの特徴は、絶縁層のエッティングを行う際に銅を保護するためシリコンニトリドフィルムを使用することである。特には、上記シリコンニトリド層は、堆積の絶縁特性が最小限維持されるぐらいに薄い。

【0013】

本発明の他の特徴は、シリコンニトリド層を保護するために、反射防止膜（ARC）を用いることである。通常、半導体チップを製造する際、フォトレジスト材料は、シリコンと、絶縁体と、金属とからなる部品を解像するフォトリソグラフィ媒体を提供する以外にも、保護層として用いられる。

【0014】

本発明に関する特徴として、ARCのエッティングが挙げられる。このエッティングによって、ARCがピアから完全には除去されていないことが保証されるのである。ピアおよびトレンチのエッティングが完了した後、ARCは、フォトレジスト除去工程（strip process）の一環として除去される。

【0015】

第1処理工程（process aspect）では、本発明は、導電性の接触領域を備えるデバイスを半導体ウェハの中および／または上に有しており、半導体ウェハ上に、デバイスの配線パターンを形成する方法を示す。なお、この配線パターンには、半導体ウェハの上面を覆う絶縁層を貫通している複数のピアおよびいくつかのトレンチに銅が用いられる。本方法は、次のステップを有している。つまり、デバイス上に第1絶縁層を形成するステップと、第1絶縁層の上面からピアを形成することで、ピアがデバイスの接触領域と導通するステップと、導体によりピアを充填するステップと、第1絶縁層上に第2絶縁層を形成するステップと、第1絶縁層に位置する導体が充填されたピアと導通しているピアを第2絶縁層を貫通して形成するステップと、第2絶縁層を貫通するピアに銅を充填するステップと、第2絶縁層の上面に第3絶縁層を形成するステップと、第3絶縁層の上面に第3絶縁層とは異なるエッティング特性を有する第4絶縁層を形成するステップと、第3絶縁層により、第2絶縁層を貫通している銅が充填されたピアから分離されるが、第2絶縁層を貫通しているピアの位置と合わせるようピアを形成するために、上記第4絶縁層のパターンを形成し、エッティングするステップと、第4絶縁層の上面に反射防止膜を形成し、第4絶縁層を貫通しているピアを反射防止材料により充填するステップと、第4絶縁層にトレンチを固定するために、反射防止層と材料とのパターンを形成するステップと、第4絶縁層を貫いているピアの上部部分と導通している第4絶縁層において、トレンチを形成するために、反射防止層と第4絶縁層の一部とを除去し、第2・第4絶縁層のピア間に位置する第3絶縁層の一部と、第4絶縁層を貫通しているピアの反射防止材料を除去するステップと、トレンチおよび第4絶縁層と除去された第3絶縁層の部分のピアを銅により充填するステップとである。

【0016】

第2処理工程では、本発明は、半導体ウェハ上における配線パターンの形成方法示す。なお、この配線パターンは、半導体ウェハに積層した絶縁層にあり、ウェハの上面に対して並列に伸びるトレンチにて銅線を備えており、絶縁層を貫通して垂直に伸びるピアに、銅が充填されている。本方法は、次のステップを有している。つまり、半導体ウェハの上面に第1絶縁層を形成するステップと、第1絶縁層の上面にトレンチを形成し、ピアがデバイスの接触領域と導通するように、第1絶縁層を貫通しているトレンチの底から、トレンチと導通しているピアを形成するステップと、接触金属を備えた第1絶縁層のピアとトレンチとを覆い、半導体ウェハ上に第1平面を残すために平坦化するステップと、上記メタルにより充填された第1絶縁層上に、第2絶縁層を形成するステップと、第2絶縁層にピアとトレンチとを形成し、ピアとトレンチとに銅を充填するステップと、銅が充填された第2絶縁層上に第2平面を形成するステップと、平坦化された表面上にシリコンニトリド

10

20

30

40

50

層を形成するステップと、エッチストップとして作用しているシリコンニトリド層上に、シリコンニトリド層とは異なるエッチング速度を有する第3絶縁層を堆積するステップと、第3絶縁層を貫通して、下層に位置する銅に整合させたビアを形成するために、第3絶縁層のパターンを形成するステップと、第3絶縁層を貫通しているビアも結果として充填することとなる、反射防止材料層を第3絶縁層の上面に形成するステップと、反射防止材料が充填されているビアと反射防止層との上に、フォトレジスト層を堆積するステップと、フォトレジストのパターンを形成し、第3絶縁層にトレンチを形成するために、反射防止層の露光部分および第3絶縁層の部分とビアとに位置する反射防止材料をエッチングするステップと、ビアの1つと導通している第3絶縁層の下に位置する各トレンチとビアとが形成されるように、パターンを形成したフォトレジストと、ビアから反射防止材料と、第2・第3絶縁層間に位置するシリコンニトリド層の一部とを除去するステップと、第3絶縁層に位置するビアおよびトレンチと、シリコンニトリド層に位置する開口部とを銅により充填し、シリコンニトリド層に位置する開口部と、第2絶縁層に位置するビア中の接触銅とを貫通して広がる第3絶縁層に、銅が充填された第2ビアおよびトレンチを残すために、表面を平坦化するステップとである。10

## 【0017】

本発明は、発明の利点を正しく認識した上、添付図面に基づいて次の詳述および請求項によってさらに理解され得る。20

## 【0018】

## (図面の簡単な説明)

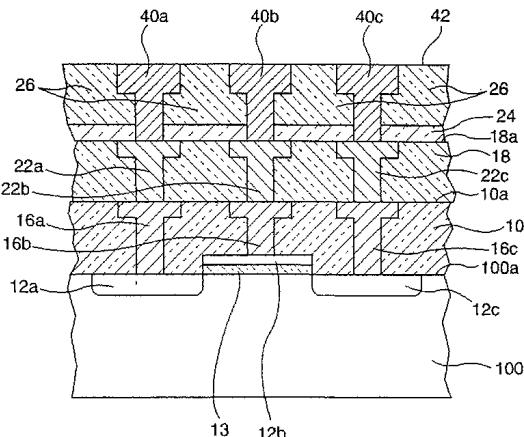

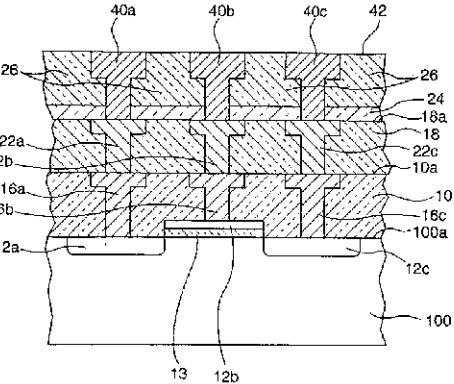

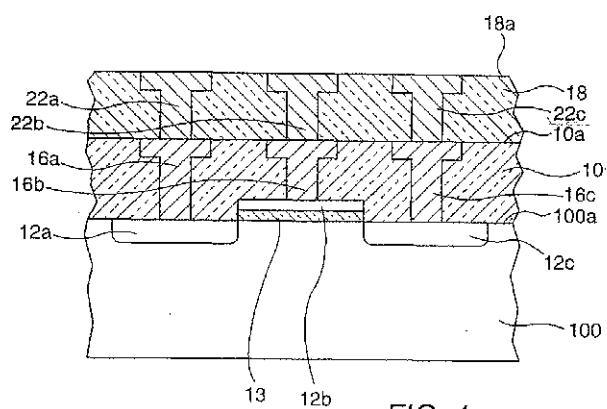

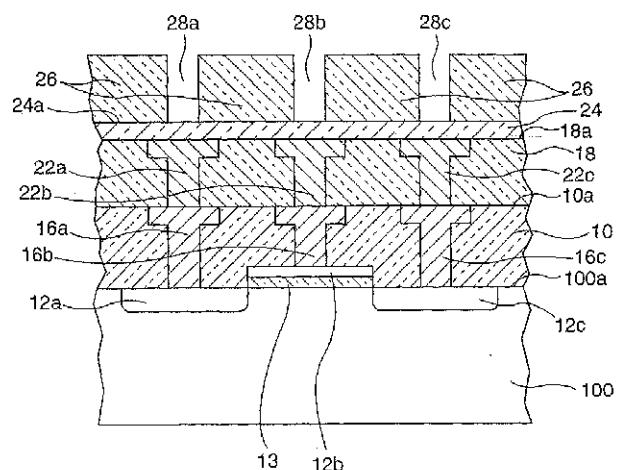

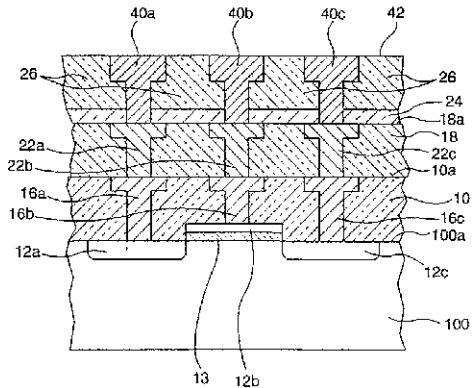

各図1～6は、半導体ウェハに形成された集積回路の導体の配線パターン部分として、金属が充填されているビアおよびトレンチを備えており、本発明の実施形態に基づくプロセスの連続した段階を示す。30

## 【0019】

なお、本図は縮尺どおりではない。

## 【0020】

## (詳細な説明)

本明細書において、ラインの後工程におけるデュアルダマシン法に対して要求されることは、ビアとトレンチとの両方が、異なるレベルの導電性の配線パターン間に位置するシリコン酸化物またはシリカガラス絶縁層にエッチングされることである。「ビアを先に」処理するように取りかかる方法に対しては、銅が堆積する前に、ビアとトレンチとの両方を配置する必要がある。工程を簡易化するために、一堆积工程中に両方を充填することが有効である。その後、メタルの第1層を保護するように配置されたシリコンニトリドフィルムは、第1層の銅線と第1ビアとの間の金属接触となる金属があるために、実質的には取り除かなければならない。30

## 【0021】

上述したように、通常の方法は、「トレンチを先に」処理するように取りかかる方法を用いることであった。銅の導電率を損なわないように、銅が処理中に保護されている限り、「ビアを先に」処理するように取りかかる方法の使用には多数の利点がある。

## 【0022】

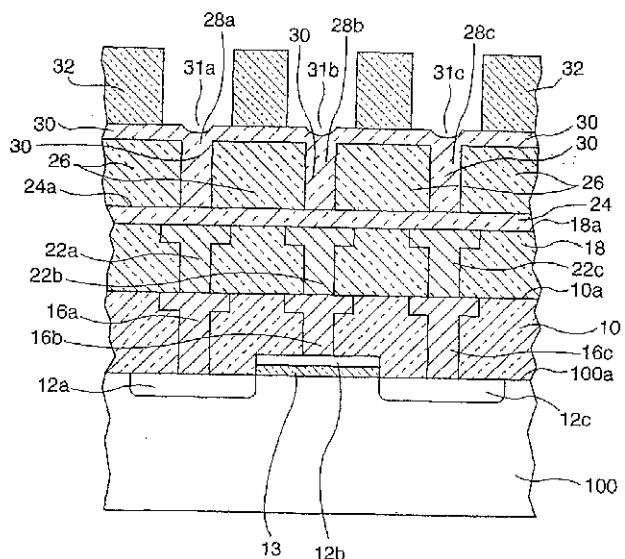

図1は、概してボロンホスホシリケイトガラス(BPSG)からなる絶縁(誘電)層10が形成されているシリコンウェハ100の一部を示している。ウェハ100は、その上面100aに、および、その上面100a上に形成された絶縁ゲート電界効果トランジスタと共に示されている。電界効果トランジスタ(デバイス)は、拡散領域12aおよび12c(ドレイン・ソース領域)と、ゲート領域12bとをそれぞれ含んでいる。なお、ゲート領域12bは、ウェハ100の上面100aに位置する誘電ゲート層13上にあり、領域12aと12cとの中央に位置している。一般的には、誘電層13およびゲート領域12bは、領域12aおよび12cが自己整合されてゲート領域12bを形成し得るマスクとして働く領域12bと共に、初めに形成される。従来のフォト処理工程(photo processing)では、拡散領域12aおよび12cならびにゲート領域12bを露4050

光するために、層 10 を貫通して、ビア（開口部）を形成するエッティングプロセスに続いて層 10 のパターンの形成が行われる。概して、トレンチは、層 10 の上面 10 a にエッティングされる。その際に、層 10 のビアおよびトレンチは、概してタングステン（W）である金属 16 a・16 b・16 c があふれ出るまで充填され、平面 10 a を得るために化学的機械研磨が行われる。概して  $\text{SiO}_2$  からなる絶縁層 18 は、平坦化された表面 10 a 上に堆積される。従来のフォトレジストおよび層 18 のエッティングによって、ビアおよびトレンチが提供される。このビアおよびトレンチは、タングステン 16 a・16 b・16 c と金属接触する金属を提供するために、銅 22 a・22 b・22 c を用いてそれぞれ充填される。第 1 ダマシン工程は、化学的機械研磨を用いて平坦化された層 18 の上面 18 a を備えることで完成される。

10

## 【0023】

図 2 は、概して PECVD により成膜された 50 nm のシリコンニトリドである絶縁層 24 が、エッティングバリア / キャップ層（etch barrier / cap layer）として機能する表面 18 a 上に堆積され、概して  $\text{SiO}_2$  からなる絶縁層 26 が、シリコンニトリド層 24 の上面 24 a 上に堆積された後のウェハ 100 を示している。次に、フォトレジスト（図示せず）を層 26 上に回転塗布させる。フォトレジストのパターンが形成された後、ビア 28 a・28 b・28 c を開口するために、層 26 をそれぞれイオンエッティングする。フォトレジストと層 26 の露出した部分とを除去するために用いられるエッティング前処理（post etch treatment）は、シリコンニトリドバリア層（silicon nitride barrier layer）24 でやめる。この工程によって、非反応性のイオンエッティング（RIE）被覆材を用いて先端部（sharp end point）を形成し、ビア 28 a・28 b・28 c が十分に開口され得るという高度な選択性を提供する。

20

## 【0024】

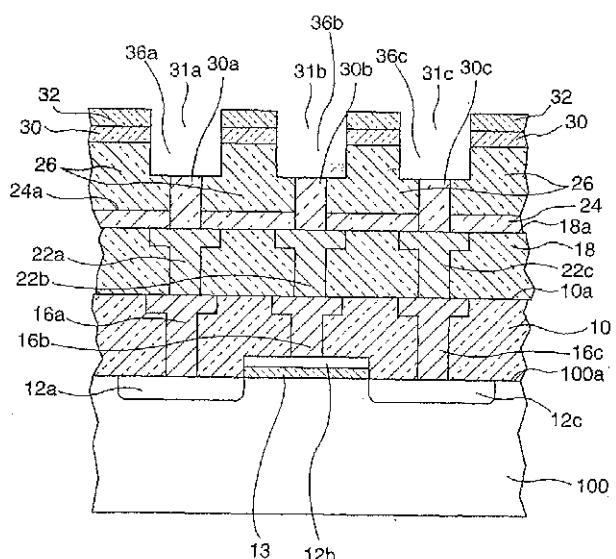

図 3 は、比較的薄い反射防止膜 30 が表面を覆い、層 26 のビア 28 a・28 b・28 c を充填するように、ウェハ 100 上に回転塗布された後のウェハ 100 を示している。空所が存在しないようにビア 28 a・28 b・28 c に確実に充填することが、重要である。実際としては、処理されたウェハの断面図は、トレンチ 28 a・28 b・28 c に、その高さの約 4 分の 3 まで ARC 材料を充填することを示している。

30

## 【0025】

例えば、グレード（grade）1100 A の ARC 材料を（最初に 95 で、続いて 180 で）ペークし、40 秒間、 $\text{C}_4\text{F}_8 + \text{O}_2$  を用いて  $\text{SiO}_2$  26 の表面に対し非選択的に RIE を行う。その際に、概して DUV 30 MCSIII / JSR 130 / 6250 であるフォトレジスト層 32 を、ウェハ 100 上に回転塗布して、層 30 の部分を曝す開口部 31 a・31 b・31 c が形成されるようにパターン化される。ビア 28 a よりも幅の広い開口部 31 a は、ビア 28 a と導通するように配置される。ビア 28 b よりも幅の広い開口部 31 b は、ビア 28 b と導通するように配置される。ビア 28 c よりも幅の広い開口部 31 c は、ビア 28 c と導通するように配置される。

30

## 【0026】

選択性の低い反応性イオンエッティングは、一般的には 40 秒間、 $\text{C}_4\text{F}_8$  と Ar と  $\text{O}_2$  との組み合わせを用いて、同様にエッティングされる層 26 の部分を曝している ARC 層 30 の露出した部分をエッティングし続ける。このことが、結果として、ビア 28 a・28 b・28 c と導通しているトレンチ 36 a・36 b・36 c の形成につながる。図 4 は、エッティング後、ビア 28 a・28 b・28 c の底に残っている各 ARC プラグ 30 a・30 b・30 c を示す。これは、ARC 材料が層 26 の  $\text{SiO}_2$  よりも低速度で除去されるためである。このことは、シリコンニトリド層 24 に接触しないように、 $\text{SiO}_2$  の周囲がエッティングされることを防ぐ。図 4 はまた、トレンチ 36 a・36 b・36 c とビア 28 a・28 b・28 c とを一体化するために、オキシド層 26 が、それぞれエッティングされたことを示している。

40

## 【0027】

50

ARC 材料 30 が、ビアにある場合、オキシド層 26 のエッティングは、SiO<sub>2</sub> と、まさに SiO<sub>2</sub> の代わりとなる ARC 材料との両方のエッティングが両立するようにエッティングプロセスを修整することによって、「フェンス」を形成することなく達成される。エッティング液が、材料の配置に依存して異なる速度で、ビアから材料を除去する場合、フェンスは形成される。例えば、ARC / オキシド境界面にて ARC 材料と比較すると、ビアの中央において ARC 材料のエッティング率が異なることが分かる。

【0028】

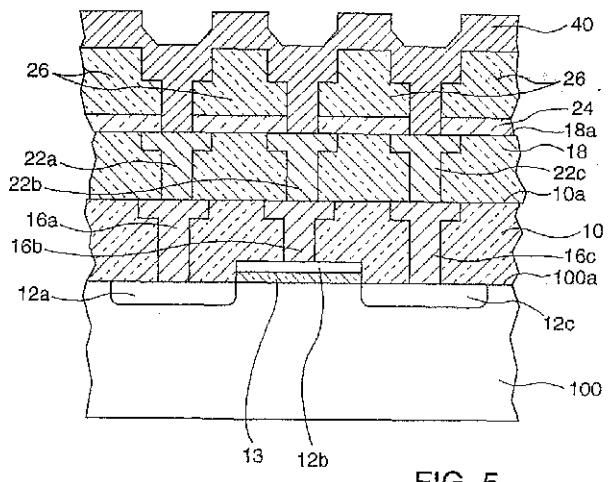

20 ~ 40 秒間のエッティング前処理によって、残りの ARC 材料 30a · 30b · 30c は、ビア 28a · 28b · 28b からそれぞれ除去される。その際に、シリコンニトリド層 24 は、約 35 秒間、CHF<sub>3</sub> + O<sub>2</sub> を用いて選択的にエッティングされる。たとえトレンチが導通しているビアよりも幅広いとしても、全てのトレンチは、ビアの一面以上に広がることはない。

【0029】

通常の洗浄段階が完了した後、図 4 に示す構成は、銅を用いて金属充填できるようになっている。

【0030】

図 5 は、ビア / トレンチ開口部 28a · 36a · 28b · 36b が、電気メッキされた銅 40 によりはみ出るまで充填された後のウェハ 100 を示している。

【0031】

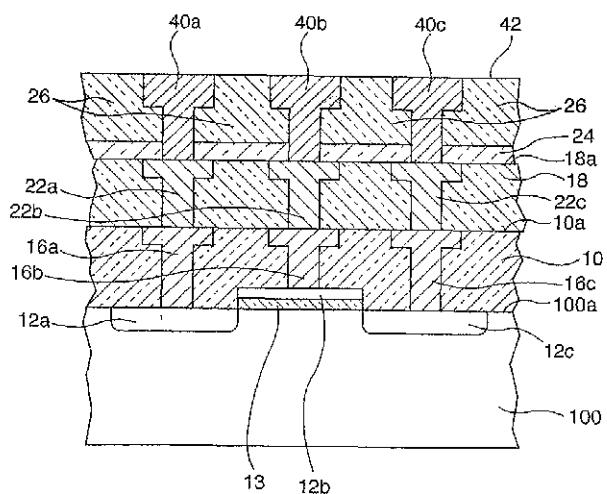

図 6 は、余分な銅を残す導体 40a · 40b · 40c を除去するために、生じた上面 42 が化学的機械研磨によって平坦化された後のウェハ 100 を示している。図 6 はまた、この階層でのメタライゼーションに関して、デュアルルダマシン方法を完了させた結果を示している。

【0032】

上記した具体的な実施例は、本発明の一般原則を例証しているにすぎず、本方法において当業者が理解できる基本原則から離れることなく、他の様々な実施例を考案することが望まれるということが分かる。例えば、絶縁層は、シリコンジオキシド以外のものでよく、半導体本体のデバイスと接觸している金属は、アルミニウムでもよい。さらに、処理例 (application) によっては、トレンチのいくつか、または、全てを、絶縁層を完全に貫通して拡大しているビアと共に使用する必要はない。その上、第 1 階層の導体からなるトレンチ部分を、金属 16a · 16b · 16c がタンゲステンであるビアと銅であるトレンチとを備えるように組み合わせて本発明の新規性のあるプロセスを始動してもよい。

【図面の簡単な説明】

【図 1】半導体ウェハに形成された集積回路の導体の配線パターン部分として、金属が充填されているビアおよびトレンチを備えており、本発明の実施形態に基づくプロセスの連続した段階を示す図である。

【図 2】半導体ウェハに形成された集積回路の導体の配線パターン部分として、金属が充填されているビアおよびトレンチを備えており、本発明の実施形態に基づくプロセスの連続した段階を示す図である。

【図 3】半導体ウェハに形成された集積回路の導体の配線パターン部分として、金属が充填されているビアおよびトレンチを備えており、本発明の実施形態に基づくプロセスの連続した段階を示す図である。

【図 4】半導体ウェハに形成された集積回路の導体の配線パターン部分として、金属が充填されているビアおよびトレンチを備えており、本発明の実施形態に基づくプロセスの連続した段階を示す図である。

【図 5】半導体ウェハに形成された集積回路の導体の配線パターン部分として、金属が充填されているビアおよびトレンチを備えており、本発明の実施形態に基づくプロセスの連続した段階を示す図である。

【図 6】半導体ウェハに形成された集積回路の導体の配線パターン部分として、金属が充

10

20

30

40

50

填されているピアおよびトレンチを備えており、本発明の実施形態に基づくプロセスの連続した段階を示す図である。

## 【国際公開パンフレット】

(12) INTERNATIONAL APPLICATION PUBLISHED UNDER THE PATENT COOPERATION TREATY (PCT)

(19) World Intellectual Property Organization

International Bureau(43) International Publication Date

10 January 2002 (10.01.2002)

PCT

(10) International Publication Number

WO 02/03457 A2

- (51) International Patent Classification<sup>7</sup>: H01L 21/768 Neuflusschuhner Strasse 46, 01145 Dresden (DE). HOLLOWAY, Karen, Lyone, 26 Horseshoe Drive, Poughkeepsie, NY 12603 (US).

- (21) International Application Number: PCT/US01/21161 (74) Agents: BRAIDEN, Stanton, C. et al.; Siemens Corporation - Intellectual Property Dept., 186 Wood Avenue South, Iselin, NJ 08830 (US).

- (22) International Filing Date: 2 July 2001 (02.07.2001) (84) Designated States (regional): European patent (AT, BE, CL, CX, DE, DK, ES, FI, FR, GB, GR, IE, IT, LU, MC, NL, PT, SI, TR).

- (25) Filing Language: English (81) Designated States (national): JP, KR.

- (26) Publication Language: English (85) Designated States (regional): European patent (AT, BE, CL, CX, DE, DK, ES, FI, FR, GB, GR, IE, IT, LU, MC, NL, PT, SI, TR).

- (30) Priority Data: 09/608,546 30 June 2000 (30.06.2000) US (71) Applicants: INFINEON TECHNOLOGIES NORTH AMERICA CORP. (US/US), 1730 North First Street, San Jose, CA 95112 (508) (US); INTERNATIONAL BUSINESS MACHINES CORPORATION (US/US), New Orchard Road, Armonk, NY 10504 (US).

- (72) Inventors: BRASE, Gabriela, 11 Chemin de la Poste, F 91630 Marolles en h (FR); SCHROEDER, Uwe, Paul.

(54) Title: VIA FIRST DIALE DAMASCENE PROCESS FOR COPPER METALLIZATION

WO 02/03457 A2

(57) Abstract: An interconnection pattern is formed over the surface of a silicon wafer in which both the vias and the trenches of the pattern are filled with copper. The process of filling the vias and trenches involves use of a silicon nitride film as an etch stop and the filling of the vias with an anti reflection coating.

WO 02/03457

PCT/US01/21161

VIA FIRST DUAL DAMASCENE PROCESS FOR COPPER METALLIZATIONField of the Invention

This invention relates to integrated circuit devices using copper for interconnecting discrete circuit components as part of the back-end-of-the-line processing of semiconductor silicon wafers, and particularly, to modifications in wafer processing needed to protect the copper during chemical etching when the via is etched before the trench in a dual Damascene process.

Background of the Invention

The demand for faster integrated circuits is driving the technologists to make the solid state components on a chip smaller and to increase the packing density. As a result of this demand, the interconnect metallurgy is shifting from aluminum-based metals to copper, which has a lower resistivity. The higher conductivity and lower cost of copper makes it very desirable for interconnecting the circuit components. Also, copper has a better resistance to electromigration failures than Al or Al-Cu and therefore, better reliability.

Although copper has very favorable electrical properties, it is prone to oxidation and corrosion when it comes in contact with some commonly-used processing chemicals. Therefore, it is critical that the processes used in conjunction with copper metallization be free from these environments when the copper is exposed, that is, not covered, during processing. Al and Al-Cu back-end-of-the-line metallizations are not prone to corrosion because of the protective oxide covering the metal surfaces in these materials.

Copper is a very viable material as the back-end-of-the-line metal when the single or dual Damascene processes are used. The Damascene process makes use of a series of trenches formed in an insulating layer. After the trenches are overfilled with copper, a chemical mechanical polishing process (CMP) is used to remove the overfill. Trenches are to be distinguished from vias. Trenches are extended grooves, typically extending parallel to the top surface of the silicon chip, that are patterned to interconnect circuits on the same level of the back-end-of-the-line process whereas vias are holes, typically extending normal to the surface, that are patterned to connect the metal lines from layer to layer.

WO 02/03457

PCT/US01/21161

Present technology uses a 'trench first' approach. Initially, the 'via first' approach was compromised because of the need for multiple layers of a relatively thick silicon nitride film. The silicon nitride, which protected the copper during processing had to, by necessity, remain behind in many of the active areas. These silicon nitride layers, however, resulted in a substantial increase in the dielectric properties of the stack and degraded the performance of the circuit. If the silicon nitride films were made thinner, they would degrade during the via etch. Also, the via etch could etch into the oxide that defines the trench. Even small changes in the line definition can cause serious reliability problems when 0.25μm ground rules are in place.

Since copper is known to be very sensitive to its environment, photoresists, which typically contain sulfur, and oxidizing chemicals should not be permitted to come in contact with the copper surfaces during processing. In this invention silicon nitride is used both as a protective layer for the copper and as an etch stop.

The 'trench first' approach however, also has its limitations. These limitations are associated with the photolithographic processing of the wafer. The difficulties occur when the trench configurations lead to differences in photoresist thicknesses. The thickness variations are seen in either broad trenches (wide lines) or very dense trenches (closely spaced narrow lines) as required, for example, by DRAMS and cause printing distortions of the via images.

The present invention seeks to provide a protective layer of silicon nitride over the copper while using a novel approach for assuring that the silicon nitride is not damaged during the simultaneous etching of the vias and trenches.

#### Summary of the Invention

This invention relates to the use of the preferred 'via first' approach for forming vias (openings, holes) and trenches (grooves) in a passivating layer by using the double Damascene process.

In an exemplary embodiment, a contact metallurgy is deposited into a patterned glass layer (e.g., boron phospho silicate glass (BPSG)) and the glass is planarized. A

WO 02/03457

PCT/US01/21161

different insulating material, such as silicon oxide, is then deposited onto the glass layer and patterned to form shallow via openings aligned with the contacts. The vias are filled with copper and the surface is planarized with a chem-mech polish. A thin silicon nitride layer is deposited onto the planarized insulator surface to act as a barrier layer/etch stop.

An  $\text{SiO}_2$  layer is deposited over the silicon nitride layer and patterned by a conventional photolithographic technique to form therein via holes aligned with the earlier vias.

In the present invention an unconventional use is advantageously made of an anti-reflective coating material (ARC) which is spun onto the wafer. The coating of ARC fills the vias and covers the rest of the surface with a thin ARC layer. With the ARC material in place, photoresist is spun onto the wafer and patterned to form the trench configuration. The  $\text{SiO}_2$  layer, which contains the vias, is etched again to form the trenches. During the trench etching the ARC material is also etched but at a rate different from the  $\text{SiO}_2$ . As a result of this differential etch rate, a plug of ARC material remains in the bottom of the vias after the trench open process has been completed. This ARC plug protects the silicon nitride from degrading which, in turn, protects the underlying copper because the etchant never comes into contact with the copper.

To this end, one feature of the invention is the use of a silicon nitride film to protect the copper during the etching of the insulating layers. In particular this silicon nitride layer should be thin so that the increase in the dielectric properties of the stack is kept to a minimum.

Another feature of the invention is on the use of an anti-reflective coating (ARC) to protect the silicon nitride layer. Normally, in the fabrication of semiconductive chips, photoresist materials are used as protective layers in addition to providing a photolithographic medium for component definition of the silicon, insulators and metals.

A related feature of the invention involves the etching of the ARC layer so as to insure that it is not entirely removed from the vias. After the etching of the vias and trenches has been completed, the ARC coating is removed as part of the photoresist strip process.

WO 02/03457

PCT/US01/21161

Viewed from a first process aspect, the present invention is directed to a method for forming over a semiconductive wafer, which contains therein and/or thereon devices having conductive contact regions, an interconnection pattern that uses copper in at least some vias and some trenches through insulating layers overlying a top surface of the semiconductor wafer. The method comprises the steps of: forming a first insulating layer over the device; forming vias from a top surface of the first insulating layer therethrough with the vias being in communication with the contact regions of the device; filling the vias with a conductor; forming a second insulating layer over the first insulating layer; forming vias through the second insulating layer which are in communication with the conductor filled vias in the first insulating layer; filling the vias through the second insulating layer with copper; forming a third insulating layer over a top surface of the second insulating layer; forming a fourth insulating layer over a top surface of the third insulating layer, the fourth insulating layer having a different etch characteristic than the third insulating layer; patterning and etching the fourth insulating layer to form vias therethrough which are separated from the copper-filled vias through the second insulating layer by the third insulating layer but are aligned with the vias through the second insulating layer; forming an anti-reflective layer over a top surface of the fourth insulating layer and filling the vias therethrough with anti-reflective material; patterning the anti-reflective layer and material to define trenches in the fourth insulating layer; removing the layer of anti-reflective layer and a portion of the fourth insulating layer to form trenches in the fourth insulating layer which are in communication with top portions of the vias through the fourth insulating layer, and removing the anti-reflective material in the vias through the fourth insulating layer and a portion of the third insulating layer between the vias of the second and fourth insulating layers; filling the trenches and vias in the fourth insulating layer and portions of the third insulating layer which were removed with copper.

Viewed from a second process aspect, the present invention is directed to a method for forming over a semiconductive wafer an interconnection pattern that is in insulating layers overlying the semiconductive wafer and that includes copper lines in trenches

WO 02/03457

PCT/US01/21161

extending parallel to a top surface of the wafer and copper fill in vias that extend vertically through insulating layers. The method comprises the steps of: forming over a top surface of the semiconductive wafer a first insulating layer; forming trenches in a top surface of the first insulating layer and forming vias, which are in communication with the trenches, from bottoms of the trenches through the first insulating layer such that same are in communication with the contact regions of the device; overfilling the vias and trenches of the first insulating layer with contact metal and planarizing to leave a first planar surface over the semiconductive wafer; forming over the metal-filled first insulating layer a second insulating layer; forming vias and trenches in the second insulating layer and overfilling the vias and trenches with copper; forming a second planar surface on the copper-filled second insulating layer; forming a silicon nitride layer over the planarized surface; depositing a third insulating layer over the silicon nitride layer, said third insulating layer having a different etch rate than the silicon nitride layer; patterning the third insulating layer to form vias therethrough which are aligned with the underlying copper, the silicon nitride film acting as an etch stop; forming an anti-reflecting material layer over a top surface of the third insulating layer which also fills the vias therethrough; depositing a layer of photoresist over the anti-reflective layer and the vias filled with the anti-reflective material; patterning the photoresist and etching exposed portions of the anti-reflective layer and anti-reflective material in the vias and portions of the third insulating layer to form trenches in the third insulating layer; removing the patterned photoresist, the anti-reflective material from the vias and a portion of the silicon nitride layer between the second and third insulating layers to result in each trench and the via there below in the third insulating layer being in communication with one of the vias in the second insulating layer; and overfilling the vias and trenches in the third insulating layer and the openings in the silicon nitride layer with copper and planarizing the surface to leave second copper-filled vias and trenches in the third insulating layer which extend through the openings in the silicon nitride layer and contact copper in the vias in the second insulating layer.

WO 02/03457

PCT/US01/21161

A better understanding of the invention together with a fuller appreciation of its advantages will be gained from the following detailed description and claims in conjunction with the accompanying drawings.

Brief Description of the Drawings

Each of the FIGS. 1-6 shows a portion of a semiconductive wafer at successive stages of processing in accordance with an exemplary embodiment of the invention to provide metal-filled vias and trenches as parts of the interconnection pattern of conductors of the integrated circuit formed in the semiconductive wafer.

The drawings are not necessarily to scale.

Detailed Description

In this specification the back-end-of-the-line processing for a dual Damascene process requires that both vias and trenches be etched into the silicon oxide or silica glass insulating layers between different levels of the conductive interconnection pattern. For the 'via first' approach it is necessary that both the vias and trenches are in place before the copper is deposited. It is advantageous to fill both during one deposition process to reduce process complexity. Silicon nitride film that is in place to protect the first level of metal must be removed subsequently so that there is a metal to metal contact between the first level copper lines and the first vias.

As has been discussed above, it has been the usual practice to use a 'trench first' approach. The use of the 'via first' approach offers a number of advantages as long as the copper remains protected during the processing so that its conductivity is not compromised.

FIG. 1 shows a portion of a silicon wafer 100 over which there has been formed an insulating (dielectric) layer 10, typically of boron phospho silicate glass (BPSG). Wafer 100 is shown with an insulated gate field effect transistor formed in and over a top surface 100a thereof. The field effect transistor (device) comprises diffused regions 12a and 12c, the drain and source regions, respectively, and a gate region 12b which is over a dielectric gate layer 13 that lies on the top surface 100a of wafer 100 and is centered between the regions 12a and 12c. Typically the dielectric layer 13 and gate region 12b are first formed with the

WO 02/03457

PCT/US01/21161

region 12b serving as a mask which allows for the regions 12a and 12c to be self aligned to the gate region 12b. Conventional photoprocessing is done to pattern layer 10 followed by etch processes to form vias (openings) through layer 10 to expose the diffusion regions 12a and 12c and the gate region 12b. Typically trenches are etched into a top surface 10a of layer 10. The vias and trenches in the layer 10 are then overfilled with metal 16a, 16b, and 16c, typically tungsten (W), and chem-mech polished to achieve a planar surface 10a. An insulating layer 18, typically of  $\text{SiO}_2$ , is deposited over the planarized surface 10a. Conventional photoresist and etching of the layer 18 provides vias and trenches which are overfilled with copper 22a, 22b, and 22c to provide metal to metal contact with the tungsten 16a, 16b, and 16c, respectively. The first Damascene process is completed with a top surface 18a of layer 18 being planarized with a chem-mech polish.

FIG. 2 shows the wafer 100 after an insulating layer 24, typically 50nm PECVD of silicon nitride, has been deposited onto surface 18a to act as an etch barrier/cap layer, and an insulating layer 26, typically  $\text{SiO}_2$ , has been deposited over a top surface 24a of the silicon nitride layer 24. Photoresist (not shown) is then spun onto the layer 26. After the photoresist is patterned, the layer 26 is reactively ion etched to open vias 28a, 28b, and 28c. A post etch treatment, which is used to remove the photoresist and exposed portions of layer 26, stops on the silicon nitride barrier layer 24. This process provides a high degree of selectivity which gives a sharp end point with no reactive ion etch (RIE) lag and allows the vias 28a, 28b, and 28c to be fully opened.

FIG. 3 shows the wafer 100 after a relatively thin anti-reflexive coating 30 has been spun onto the wafer 100 to cover the surfaces and to fill the vias 28a, 28b, and 28c in layer 26. It is important to insure that the vias 28a, 28b, and 28c are filled so that no voids are present. In practice, cross sections of a processed wafer show that the ARC material fills the trenches 28a, 28b, and 28c to about three fourths of its height.

For example, the ARC material, grade 1100A, is baked (first at 95 °C and then at 180 °C) and non-selectively RIE'd from the surface of the  $\text{SiO}_2$  26 with  $\text{C}_4\text{F}_8 + \text{O}_2$  for 40 seconds. A layer of photoresist 32, typically DUV30 MCSIII/JSR 130/6250, is then spun

WO 02/03457

PCT/US01/21161

onto the wafer 100 and patterned to result in openings 31a, 31b, and 31c which expose portions of layer 30. Opening 31a, which is wider than via 28a, is located over and in communication with via 28a. Opening 31b, which is wider than via 28b, is located over and in communication with via 28b. Opening 31c, which is wider than via 28c, is located over and in communication with via 28c.

A low selective reactive ion etch, with a typical duration of 40 seconds, uses a combination of C<sub>4</sub>F<sub>8</sub>, Ar, and O<sub>2</sub>, is used to etch the exposed portions of ARC layer 30 to expose portions of layer 26 which are then also etched. This results in the formation of trenches 36a, 36b, and 36c which are in communication with vias 28a, 28b, and 28c, respectively. FIG. 4 shows that ARC plugs 30a, 30b, and 30c remaining in the bottom of the vias 28a, 28b, and 28c, respectively, after this etch. This is because the ARC material is removed at a slower rate than the SiO<sub>2</sub> of layer 26. This prevents the SiO<sub>2</sub> etching ambient from touching the silicon nitride layer 24. FIG. 4 also shows that oxide layer 26 has been etched to integrate the trenches 36a, 36b, and 36c with the vias 28a, 28b, and 28c, respectively.

The etching of the oxide layer 26, when the ARC material 30 is in the vias, is achieved without the formation of 'fences' by tailoring the etch process to be compatible with the etching of both the SiO<sub>2</sub> and the ARC material instead of just the SiO<sub>2</sub>. Fences are formed when the etchant removes material from the via at different rates depending on the material location. For example, it is possible to find a different etch rate for the ARC material in the center of the via when compared with the ARC material at the ARC/oxide interface.

A post etch treatment for 20-40 seconds removes the remaining ARC material 30a, 30b, and 30c from the vias 28a, 28b, and 28c, respectively. The silicon nitride layer 24 is then selectively etched away using CHF<sub>3</sub> + O<sub>2</sub> for about 35 seconds. It is to be noted that all of the trenches, although wider than the vias in which they are in communication, do not have to extend over more than one side of a via.

WO 02/03457

PCT/US01/21161

After the normal cleaning steps have been completed the structure of FIG. 4 is ready for metal fill with copper.

FIG. 5 shows the wafer 100 after the via/trench openings 28a/36a, 28b/36b have been overfilled with electroplated copper 40.

FIG. 6 shows the wafer 100 after a resulting top surface 42 has been planarized using a chem-mech polish to remove the excess copper leaving conductors 40a, 40b, and 40c. FIG. 6 also illustrates the result of the completed dual Damascene process for this level of metallization.

It is to be understood that the specific embodiment described is merely illustrative of the general principles of the invention and various other embodiments may be devised without departing from the basic teaching by a worker in the art. For example, the insulating layers can be other than silicon dioxide and the metal contacting the device of the semiconductive body could be aluminum. Further, in some applications some or all of the trenches need not be used with the vias extending completely through an insulating layer. Furthermore, the novel process of the present invention can be implemented starting at the trench portions of the first level of conductors with the metal 16a, 16b, and 16c being tungsten in the vias and being cooper in the trenches.

What is claimed is:

1. A method for forming over a semiconductive wafer, which contains therein and/or thereon devices having conductive contact regions, an interconnection pattern that uses copper in at least some vias and some trenches through insulating layers overlying a top surface of the semiconductive wafer, the method comprising the steps of:

- forming a first insulating layer over the device;

- forming vias from a top surface of the first insulating layer therethrough with the vias being in communication with the contact regions of the device;

- filling the vias with a conductor;

- forming a second insulating layer over the first insulating layer;

- forming vias through the second insulating layer which are in communication with the conductor filled vias in the first insulating layer;

- filling the vias through the second insulating layer with copper;

- forming a third insulating layer over a top surface of the second insulating layer;

- forming a fourth insulating layer over a top surface of the third insulating layer, the fourth insulating layer having a different etch characteristic than the third insulating layer;

- patterned and etching the fourth insulating layer to form vias therethrough which are separated from the copper-filled vias through the second insulating layer by the third insulating layer but are aligned with the vias through the second insulating layer;

- forming an anti-reflective layer over a top surface of the fourth insulating layer and filling the vias therethrough with anti-reflective material;

- patterned the anti-reflective layer and material to define trenches in the fourth insulating layer;

- removing the layer of anti-reflective layer and a portion of the fourth insulating layer to form trenches in the fourth insulating layer which are in communication with top portions of the vias through the fourth insulating layer, and removing the anti-reflective

WO 02/03457

PCT/US01/21161

material in the vias through the fourth insulating layer and a portion of the third insulating layer between the vias of the second and fourth insulating layers;

filling the trenches and vias in the fourth insulating layer and portions of the third insulating layer which were removed with copper.

2. The process of claim 1 in which the vias and trenches of the fourth insulating layer are overfilled with copper and chemical mechanical polishing is used to planarize the resulting structure.

3. The method of claim 1 wherein the first insulating layer is BPSG, the second and fourth insulating layers are silicon oxide, and the third insulating layer is silicon nitride.

4. The method of claim 1 wherein the conductor is tungsten.

5. The method of claim 1 wherein the conductor is aluminum.

6. The method of claim 1 further comprising the steps of:

forming trenches in top surfaces of the first insulating layer which are each in communication with a separate via through the first insulating layer and which are each filled with the conductor;

over filling the vias and trenches of the first insulating layer with the conductor and planarizing same using chemical mechanical polishing;

forming trenches in a top surface of the second insulating layer which are each in communication with a separate via of the second insulating layer and which are each filled with copper; and

over filling the vias and trenches of the second insulating layer with copper and planarizing same using chemical mechanical polishing.

7. The method of claim 7 wherein the anti-reflective layer and the anti-reflective material have a different etch rate than the third insulating layer.

8. The method of claim 12 wherein the anti-reflective layer and the anti-reflective material are both DUV30.

9. The method of claim 7 in which the silicon nitride layer is deposited by PECVD.

WO 02/03457

PCT/US01/21161

10. A method for forming over a semiconductive wafer an interconnection pattern that is in insulating layers overlying the semiconductive wafer and that includes copper lines in trenches extending parallel to a top surface of the wafer and copper fill in vias that extend vertically through insulating layers, said method comprising the steps of:

forming over a top surface of the semiconductive wafer a first insulating layer;

forming trenches in a top surface of the first insulating layer and forming vias, which are in communication with the trenches, from bottoms of the trenches through the first insulating layer such that same are in communication with the contact regions of the device;

overfilling the vias and trenches of the first insulating layer with contact metal and planarizing to leave a first planar surface over the semiconductive wafer;

forming over the metal-filled first insulating layer a second insulating layer;

forming vias and trenches in the second insulating layer and overfilling the vias and trenches with copper;

forming a second planar surface on the copper-filled second insulating layer;

forming a silicon nitride layer over the planarized surface;

depositing a third insulating layer over the silicon nitride layer, said third insulating layer having a different etch rate than the silicon nitride layer;

patterned the third insulating layer to form vias therethrough which are aligned with the underlying copper, the silicon nitride film acting as an etch stop;

forming an anti-reflecting material layer over a top surface of the third insulating layer which also fills the vias therethrough;

depositing a layer of photoresist over the anti-reflective layer and the vias filled with the anti-reflective material;

patterned the photoresist and etching exposed portions of the anti-reflective layer and anti-reflective material in the vias and portions of the third insulating layer to form trenches in the third insulating layer;

removing the patterned photoresist, the anti-reflective material from the vias and a portion of the silicon nitride layer between the second and third insulating layers to

WO 02/03457

PCT/US01/21161

result in each trench and the via there below in the third insulating layer being in communication with one of the vias in the second insulating layer; and overfilling the vias and trenches in the third insulating layer and the openings in the silicon nitride layer with copper and planarizing the surface to leave second copper-filled vias and trenches in the third insulating layer which extend through the openings in the silicon nitride layer and contact copper in the vias in the second insulating layer.

11. The process of claim 10 in which the first insulating layer is BPSG, and the second and third insulating layers are of silicon oxide.

12. The process of claim 10 in which chemical mechanical polishing is used to planarize surfaces of the insulating layers after same are overfilled with metal.

13. The method of claim 10 wherein the contact metal is tungsten.

14. The method of claim 10 wherein the contact metal is aluminum.

15. The method of claim 10 wherein the anti-reflective layer and the anti-reflective material have a different etch rate than the third insulating layer.

16. The method of claim 15 wherein the anti-reflective layer and the anti-reflective material are both DUV30.

17. The method of claim 10 in which the silicon nitride layer is deposited by PECVD.

1/6

FIG. 1

2/6

FIG. 2

3/6

FIG. 3

WO 02/03457

PCT/US01/21161

4/6

FIG. 4

5/6

FIG. 5

6/6

FIG. 6

## 【国際公開パンフレット（コレクトバージョン）】

(12) INTERNATIONAL APPLICATION PUBLISHED UNDER THE PATENT COOPERATION TREATY (PCT)

(19) World Intellectual Property Organization

International Bureau(43) International Publication Date

10 January 2002 (10.01.2002)

PCT

(10) International Publication Number

WO 02/03457 A3

(51) International Patent Classification: 11011, 21/768 Neuhofheimer Strasse 46, 01465 Dresden (DE). HOLLOWAY, Karen, Lynne; 26 Horseshoe Drive, Poughkeepsie, NY 12603 (US).

(21) International Application Number: PCT/US01/21161

(22) International Filing Date: 2 July 2001 (02.07.2001)

(25) Filing Language: English

(26) Publication Language: English

(30) Priority Date: 09/606,540 30 June 2000 (30.06.2000) US

(71) Applicants: INFINEON TECHNOLOGIES NORTH AMERICA CORP. (US/US); 1730 North First Street, San Jose, CA 95112-4508 (US). INTERNATIONAL BUSINESS MACHINES CORPORATION (US/US); New Orchard Road, Armonk, NY 10504 (US).

(72) Inventors: BRASE, Gabriela; 11 Chemin de la Poste, F-91610 Marolles-en-Haut (FR). SCHROEDER, Uwe, Paul;

(74) Agents: BRADEN, Stanton, C. et al.; Siemens Corporation - Intellectual Property Dept., 186 Wood Avenue South, Iselin, NJ 08830 (US).

(83) Designated States (national): JP, KR.

(84) Designated States (regional): European patent (AT, BE, CH, CY, DE, DK, ES, FI, FR, GB, GR, IE, IT, LU, MC, NL, PT, SE, TR).

Published:

— with international search report

(85) Date of publication of the international search report: 6 June 2002

For two-letter codes and other abbreviations, refer to the "Guidance Notes on Codes and Abbreviations" appearing at the beginning of each regular issue of the PCT Gazette.

(54) Title: VIA FIRST DUAL DAMASCENE PROCESS FOR COPPER METALLIZATION

WO 02/03457 A3

(57) Abstract: An interconnection pattern is formed over the surface of a silicon wafer in which both the vias and the trenches of the pattern are filled with copper. The process of filling the vias and trenches involves use of a silicon nitride film (24) as an etch stop and the filling of the vias with an anti-reflection coating (130).

## 【国際調査報告】

| INTERNATIONAL SEARCH REPORT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                          | Int'l. Search Application No.<br>PCT/US 01/21161                              |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|

| A. CLASSIFICATION OF SUBJECT MATTER<br>IPC 7 H01L21/768                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                          |                                                                               |

| According to International Patent Classification (IPC) or to both national classification and IPC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                          |                                                                               |

| B. FIELDS SEARCHED<br>Minimum documentation searched (classification system followed by classification symbols)<br>IPC 7 H01L                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                          |                                                                               |

| Documentation searched other than minimum documentation to the extent that such documents are included in the fields searched                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                          |                                                                               |

| Electronic data base consulted during the international search (name of data base and, where practical, search terms used)<br>EPO-Internal, PAJ, WPI Data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                          |                                                                               |

| C. DOCUMENTS CONSIDERED TO BE RELEVANT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                          |                                                                               |

| Category                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Citation of document, with indication, where appropriate, of the relevant passages                                                                                       | Relevant to claim No                                                          |

| A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | WO 00 14793 A (APPLIED MATERIALS INC)<br>16 March 2000 (2000-03-16)<br>page 12 -page 14; figures 5-10                                                                    | 1,2,7,9,<br>10,12,<br>15,17                                                   |

| A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | PATENT ABSTRACTS OF JAPAN<br>vol. 2000, no. 08,<br>6 October 2000 (2000-10-06)<br>& JP 2000 150644 A (MITSUBISHI ELECTRIC<br>CORP), 30 May 2000 (2000-05-30)<br>abstract | 1,2,7,9,<br>10,12,<br>15,17                                                   |

| P,A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | -& US 6 251 774 B1 (MITSUBISHI DENKI<br>KABUSHIKI KAISHA)<br>26 June 2001 (2001-06-26)<br>figure 2; example 2                                                            | 1,2,7,9,<br>10,12,<br>15,17<br>-/-                                            |

| <input checked="" type="checkbox"/> Further documents are listed in the continuation of box C.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                          | <input checked="" type="checkbox"/> Patent family members are listed in annex |

| <p>* Special categories of cited documents:</p> <p>'A' document defining the general state of the art which is not considered to be of particular relevance</p> <p>'E' earlier document not published on or after the international filing date</p> <p>'L' document which may throw doubt on another claim or which may be used to establish the publication date of another citation or other special relevance as specified</p> <p>'C' document referring to an oral disclosure, use, exhibition or other means</p> <p>'P' document published prior to the international filing date but later than the priority date claimed</p> <p>*'T' later document published after the international filing date or priority date and not in conflict with the application but which nevertheless constitutes prior art under the principles of novelty and inventive step</p> <p>*'V' document of particular relevance, the invention of which cannot be considered to involve an inventive step when the document is taken alone</p> <p>*'W' document of particular relevance; the claimed invention cannot be considered to involve an inventive step when the document is combined with one or more other such documents, such combination being obvious to a person skilled in the art.</p> <p>*'S' document member of the same patent family</p> |                                                                                                                                                                          |                                                                               |

| Date of the actual completion of the international search<br>14 March 2002                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                          | Date of mailing of the international search report<br>21/03/2002              |

| Name and mailing address of the ISA<br>European Patent Office, P.O. 5010 Patentlinie 2<br>NL-2280 MV Einheit<br>Tel. (+31-70) 340 9000, Fax. (+31-70) 340 9010<br>Fax. (+31-70) 340 9010                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                          | Authorised officer<br>Szarowski, A                                            |

## INTERNATIONAL SEARCH REPORT

Int. Search Application No.

PCT/US 01/21161

| C(Continuation) DOCUMENTS CONSIDERED TO BE RELEVANT |                                                                                                                                                                                                                                                               |                                  |

|-----------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

| Category                                            | Citation of document, with indication where appropriate, of the relevant passages                                                                                                                                                                             | Relevant to claim No.            |

| A                                                   | PATENT ABSTRACTS OF JAPAN<br>vol. 2000, no. 05,<br>14 September 2000 (2000-09-14)<br>& JP 2000 049137 A (MOTOROLA INC),<br>18 February 2000 (2000-02-18)<br>abstract<br>-& US 6 127 258 A (MOTOROLA INC)<br>3 October 2000 (2000-10-03)<br>the whole document | 1-4,10,<br>11,13                 |

| P,A                                                 | EP 0 892 428 A (SHARP KK ;SHARP MICROELECT<br>TECH INC (US))<br>20 January 1999 (1999-01-20)<br>the whole document                                                                                                                                            | 1-4,10,<br>11,13                 |

| A                                                   | US 6 057 239 A (KAI JAMES K ET AL)<br>2 May 2000 (2000-05-02)                                                                                                                                                                                                 | 1,2,7,8,<br>10,12,<br>15,16      |

|                                                     | the whole document                                                                                                                                                                                                                                            | ---                              |

| A                                                   | WO 00 05763 A (APPLIED MATERIALS INC)<br>3 February 2000 (2000-02-03)                                                                                                                                                                                         | 1,2,5-7,<br>9,10,12,<br>14,15,17 |

|                                                     | page 8 -page 10; figures 4A-4G                                                                                                                                                                                                                                | ---                              |

| P,A                                                 | WO 01 01480 A (HUSSEIN MAKAREM A ;RECCHIA<br>CHARLES H (US); SIVAKUMAR SAM (US); INT)<br>4 January 2001 (2001-01-04)<br>the whole document                                                                                                                    | 1,2,6,7,<br>9,10,12,<br>15,17    |

|                                                     | ---                                                                                                                                                                                                                                                           | ---                              |

| INTERNATIONAL SEARCH REPORT            |                  |                                                                               |  | Int'l. Application No                                              |

|----------------------------------------|------------------|-------------------------------------------------------------------------------|--|--------------------------------------------------------------------|

| Information on patent family members   |                  |                                                                               |  | PCT/US 01/21161                                                    |

| Patent document cited in search report | Publication date | Patent family member(s)                                                       |  | Publication date                                                   |

| WO 0014793                             | A 16-03-2000     | US 2001008226 A1<br>WO 0014793 A2                                             |  | 19-07-2001<br>16-03-2000                                           |

| JP 2000150644                          | A 30-05-2000     | US 6251774 B1                                                                 |  | 26-06-2001                                                         |

| JP 2000049137                          | A 18-02-2000     | US 6127258 A<br>JP 3195203 B2                                                 |  | 03-10-2000<br>06-08-2001                                           |

| EP 0892428                             | A 20-01-1999     | US 5904565 A<br>EP 0892428 A2<br>JP 11087509 A<br>TW 382798 B<br>US 6023102 A |  | 18-05-1999<br>20-01-1999<br>30-03-1999<br>21-02-2000<br>08-02-2000 |

| US 6057239                             | A 02-05-2000     | US 2001046778 A1                                                              |  | 29-11-2001                                                         |

| WO 0005763                             | A 03-02-2000     | US 6245662 B1<br>EP 1101247 A1<br>WO 0005763 A1                               |  | 12-06-2001<br>23-05-2001<br>03-02-2000                             |

| WO 0101480                             | A 04-01-2001     | AU 5790800 A<br>WO 0101480 A1                                                 |  | 31-01-2001<br>04-01-2001                                           |

Form PCT/ISA/210 (patent family annex) - Rev 1999

## フロントページの続き

(74)代理人 100113701

弁理士 木島 隆一

(74)代理人 100116241

弁理士 金子 一郎

(72)発明者 ブラズ, ガブリエラ

フランス 91630 マロルザン アッシュ シュマン ドゥ ラ ポスト 11

(72)発明者 シュレーダー, ウヴェ, パウル

ドイツ連邦共和国 01465 ドレスデン ノイルスハイマー シュトラーセ 46

(72)発明者 ハロウェイ, ケレン, リン

アメリカ合衆国 ニューヨーク州 12603 ポーキプシー ホースシュー ドライブ 26

F ターム(参考) 5F033 HH08 HH11 HH19 JJ01 JJ08 JJ11 JJ19 KK01 KK08 KK11

KK19 MM02 PP27 QQ04 QQ09 QQ13 QQ25 QQ37 QQ47 QQ96

RR04 RR06 RR15 SS15 XX01