(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2005-233678

(P2005-233678A)

(43) 公開日 平成17年9月2日(2005.9.2)

(51) Int.C1.<sup>7</sup>

GO1S 13/26

GO1S 13/93

F1

GO1S 13/26

GO1S 13/93

テーマコード(参考)

5J070

Z

審査請求 未請求 請求項の数 8 O L (全 17 頁)

(21) 出願番号

特願2004-40149 (P2004-40149)

(22) 出願日

平成16年2月17日 (2004.2.17)

(71) 出願人 000237592

富士通テン株式会社

兵庫県神戸市兵庫区御所通1丁目2番28号

(71) 出願人 000005223

富士通株式会社

神奈川県川崎市中原区上小田中4丁目1番1号

(74) 代理人 100099759

弁理士 青木 篤

(74) 代理人 100092624

弁理士 鶴田 準一

(74) 代理人 100113826

弁理士 倉地 保幸

最終頁に続く

(54) 【発明の名称】 レーダ装置

## (57) 【要約】

【課題】 温度、電源変動が相関値に与える影響を補正することが可能なレーダ装置を得る。

【解決手段】 スペクトル拡散符号および逆拡散符号を発生する符号発生器1と、スペクトル拡散符号により変調された信号を送信する送信部2、3と、送信信号のターゲットからの反射波を受信する受信部4、5と、逆拡散符号を段階的に遅延する遅延部6と、段階的に遅延された逆拡散符号を用いて受信信号を逆拡散処理する逆拡散処理部7と、逆拡散処理されたデータから相関値を検出する相関値検出部8と、その相関値に基づいてターゲットの存在を検出するターゲット検出部9とを備え、さらに、送信部と受信部間の直接波の相関強度があらかじめ決められた値以上となるようにスペクトル拡散符号と逆拡散符号間の位相を調整する調整部11、12を設ける。

【選択図】

図6

**【特許請求の範囲】****【請求項 1】**

スペクトル拡散符号および逆拡散符号を発生する符号発生器と、前記スペクトル拡散符号により変調された信号を送信する送信部と、前記送信された信号のターゲットからの反射波を受信する受信部と、前記逆拡散符号を段階的に遅延する遅延部と、前記段階的に遅延された逆拡散符号を用いて前記受信部によって受信された信号を逆拡散処理する逆拡散処理部と、前記逆拡散処理されたデータから相関値を検出する相関値検出部と、前記検出された相関値からターゲットの存在を検出するターゲット検出部とを備えたレーダ装置において、前記送信部と前記受信部間の直接波の相関強度があらかじめ決められた値以上となるように前記スペクトル拡散符号と逆拡散符号間の位相を調整する調整部を設けたことを特徴とする、レーダ装置。10

**【請求項 2】**

請求項 1 に記載のレーダ装置において、前記調整部は、前記スペクトル拡散符号と逆拡散符号のいずれか一方を遅延制御する遅延制御部で構成されることを特徴とする、レーダ装置。

**【請求項 3】**

請求項 1 に記載のレーダ装置において、前記符号発生器はスペクトル拡散符号生成用および逆拡散符号生成用にそれぞれ P L L 回路内蔵 P / S 変換回路を含んで構成され、前記調整部は、これらの P L L 回路内蔵 P / S 変換回路のいずれか一方への入力を前記送信部と前記受信部間の直接波の相関強度があらかじめ決められた値以上となるように遅延する遅延制御部で構成されることを特徴とする、レーダ装置。20

**【請求項 4】**

請求項 3 記載のレーダ装置において、前記 P L L 回路内蔵 P / S 変換回路は受信用の S / P 変換回路を一体に有して構成され、さらに、前記それぞれの P / S 変換回路出力であるスペクトル拡散符号と逆拡散符号間との間のビット位相のずれを補正するために、前記スペクトル拡散符号生成用 P L L 回路内蔵 P / S 変換回路出力を逆拡散符号生成用 P L L 回路内蔵 P / S 変換回路の受信用 S / P 変換回路にループバックさせる手段を設けたことを特徴とする、レーダ装置。

**【請求項 5】**

スペクトル拡散符号および逆拡散符号を発生する符号発生器と、前記スペクトル拡散符号により変調された信号を送信する送信部と、前記送信された信号のターゲットからの反射波を受信する受信部と、前記逆拡散符号を段階的に遅延する遅延部と、前記段階的に遅延された逆拡散符号を用いて前記受信部によって受信された信号を逆拡散処理する逆拡散処理部と、前記逆拡散処理されたデータから相関値を検出する相関値検出部と、前記検出された相関値からターゲットの存在を検出するターゲット検出部とを備えたレーダ装置において、前記符号発生器によって生成されたスペクトル拡散符号および逆拡散符号間の相関値を検出し、該相関値があらかじめ決められた値となるように前記符号発生器の動作を調整することを特徴とする、レーダ装置。30

**【請求項 6】**

請求項 5 に記載のレーダ装置において、前記符号発生器はスペクトル拡散符号生成用および逆拡散符号生成用にそれぞれ P L L 回路内蔵 P / S 変換回路を含んで構成され、さらに、これらの P L L 回路内蔵 P / S 変換回路間でその出力符号の相関値が前記あらかじめ決められた値となるように、これらの P L L 回路内蔵 P / S 変換回路のいずれか一方への入力を遅延する遅延制御部を有することを特徴とする、レーダ装置。40

**【請求項 7】**

請求項 6 に記載のレーダ装置において、前記 P L L 回路内蔵 P / S 変換回路は受信用の S / P 変換回路を一体に有して構成され、さらに、前記それぞれの P / S 変換回路出力であるスペクトル拡散符号と逆拡散符号間との間のビット位相のずれを補正するために、前記スペクトル拡散符号生成用の P L L 回路内蔵 P / S 変換回路出力を逆拡散符号生成用の P L L 回路内蔵 P / S 変換回路の受信用 S / P 変換回路にループバックさせる手段を設け50

たことを特徴とする、レーダ装置。

【請求項 8】

請求項 5 乃至 7 の何れか 1 項に記載のレーダ装置において、前記スペクトル拡散符号および逆拡散符号間の相関値の検出は、ターゲットの検出処理に影響を与えない周期で繰り返し行われることを特徴とする、レーダ装置。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、スペクトル拡散方式を用いたレーダ装置に関する。

【背景技術】

【0002】

他の通信システムから受ける干渉の影響を小さくするために、情報をある符号列を用いて広帯域に拡散して通信を行うスペクトル拡散方式を採用した UWB (Ultra Wide Band) レーダ装置が開発されている。このレーダ装置が例えば車載用のレーダ装置である場合、自車前方に障害物 (ターゲット) が存在するか否か、そのターゲットまでの距離、ターゲットとの相対速度等を精度良く検出することが可能である。

【0003】

このレーダ装置において、ターゲットまでの距離を決定するためには、受信した反射波の逆拡散処理に使用する逆拡散符号を、送信符号に対して距離に応じて一定量づつ遅延している。したがって、この遅延量が、装置を構成する半導体デバイス等の温度および電源変動に基づく特性変化の影響を受けて変動すると、送信符号と逆拡散符号間で位相のずれを生じ、その結果これらの符号間の相関特性が変化する。このような相関特性の変化によって、ターゲットまでの距離検出に際して誤差を生じる場合がある。

【0004】

図 1 は、従来のスペクトル拡散方式を用いたレーダ装置の概略構成を示すブロック図である。図 1 において、1 はスペクトル拡散符号および逆拡散符号を発生するための符号発生器、2 は符号発生器 1 によって生成されたスペクトル拡散符号を用いて送信信号を変調しつつ送信処理するための拡散・送信処理部、3 は拡散処理された信号を送信するためのアンテナである。

【0005】

4 は受信アンテナであり、送信アンテナ 3 から送信された電波がターゲット 13 によって反射され戻ってきたもの、即ちターゲット 13 による反射波 14 を受信するためのものである。受信アンテナ 4 は、送信アンテナ 3 からの直接波 15 も受信する。5 は受信処理部であり、受信アンテナ 4 によって受信した信号の復調処理を行う。6 は、符号発生器 1 によって生成された逆拡散符号を段階的に遅延するステップディレイ、7 はステップディレイ 6 によって遅延された逆拡散符号を用いて受信信号を逆拡散処理しさらに A/D 変換する逆拡散処理部、8 は逆拡散処理された A/D 変換データから相関値を検出する相関値検出部、さらに 9 は検出された相関値から、ターゲットまでの距離、受信強度、ターゲットと自車との相対速度およびターゲットが何であるかを判定する等の種々の処理を行うターゲット検出部である。

【0006】

ターゲット検出部 9 の処理結果は、図示されていないがディスプレイ等に表示されて運転者に注意を喚起し、あるいは車両の ECU 等に導入されて種々の走行制御に利用される。

【0007】

図 1 の装置において、アンテナ 3、4 間で直接受信される直接波の受信タイミングは、符号発生器 1 による符号生成のタイミングに対して、機器の物理的構成あるいは配置等で決まるある一定の遅延を有している。したがって、符号発生器 1 によって生成される逆拡散符号を同じだけ遅延させる必要がある。図 1 の固定ディレイ 10 は、このための遅延 (初期ディレイ) を構成するものである。

10

20

30

40

50

## 【0008】

図2は、図1に示す装置の動作説明のためのタイムチャートであって、特に、ターゲットまでの距離をどのように検出するかを示している。図2(a)は符号発生器1において生成されるスペクトル拡散のための符号列を示し、図2(b)は、ステップディレイ6によって段階的に遅延された逆拡散符号列を示す。逆拡散符号列(b)には、受信符号と同期させるために、固定ディレイ10において一定の初期ディレイが与えられている。

## 【0009】

逆拡散符号列(b)は、送信符号(1)、(2)、(3)…(n)をステップディレイ6によって例えれば1クロック分づつ遅延することによって形成されている。図(c)は直接波の受信符号列を示し、図(d)はレーダ装置から1クロック分の距離にあるターゲットからの反射波における符号列を示し、さらに図(e)は2クロック分の距離にあるターゲットからの反射波の符号列を示す。

## 【0010】

図2に示すように、直接波の受信符号列(c)を逆拡散符号列(b)によって逆拡散処理する場合、符号1が強い相関を示し、その他の符号は受信符号と逆拡散符号間で位相がずれているため、強い相関を示さない。同様に、1クロック分の距離にあるターゲットからの反射波の符号列(d)は、符号2において逆拡散符号列と強い相関を示す。さらに2クロック分の距離にあるターゲットからの反射波の符号列(e)は、符号3において強い相関を示す。

## 【0011】

したがって、図2(g)に示すように、受信波(f)を逆拡散符号列(b)で逆拡散処理し、各符号について相関値を検出することにより、各距離に反射波を形成するターゲットがあるか否かが検出される。即ち0m、0m+1クロック分の距離、0m+2クロック分の距離等における相関特性において、強い相関を示した場合その距離にターゲットが存在していることが分かる。

## 【0012】

以上のように、スペクトル拡散を利用したUWBレーダ装置では、ステップディレイによって段階的に遅延された逆拡散符号と受信符号間で相関を取り、その相関特性からターゲットの存在およびターゲットまでの距離を決定している。したがって、逆拡散符号と受信符号間では正確にその位相が同期していなければならない。両者の位相関係が、何らかの原因によりあらかじめ設定されていたものと異なると、図2(g)に示すような相関値の検出において正しい相関強度を得ることがせず、その結果、正しいターゲットの距離検出が行えない。

## 【0013】

ところが、レーダ装置を構成する半導体デバイスは温度変化または電源変動によってその特性を変化させ易く、またデバイス間での変動は一様ではない。そのため、逆拡散処理部において、受信符号と逆拡散符号間に位相のずれを発生する。

## 【0014】

図3は、温度、電源変動による逆拡散符号と受信符号間の位相のずれ(ディレイ差)を示している。信号速度が遅い場合、このようなわずかな位相のずれはあまり問題とならないが、UWBレーダ装置のように高速の信号を用いる装置ではその影響は大きく、受信符号と逆拡散符号間の相関特性に大きな変化を生じる。

## 【0015】

レーダ装置の使用を開始する際の図3に示すようなディレイ差は、固定ディレイ10の値を調整することによって吸収することが可能であるが、使用中の温度、電源変動によって生じるこのようなディレイを固定ディレイ10によって吸収することはできない。

## 【0016】

本発明の参考文献としては、例えば以下の特許文献1乃至3を上げることができる。しかしながらこれらの特許文献は、本願の発明時点における一般的なスペクトル拡散レーダ装置の技術レベルを示すものであって、本発明の特徴を示唆し教示するものではない。

10

20

30

40

50

【 0 0 1 7 】

【特許文献1】特開2002-290273

【特許文献2】特開2000-310675

【特許文献3】特開平9-211111

【発明の開示】

【発明が解決しようとする課題】

【 0 0 1 8 】

本発明は、従来のレーダ装置の上記の欠点を解決するために為されたものであり、レーダ装置使用中の温度、電源変動による受信符号と逆拡散符号間の位相のずれを自動的に補正して、常に正確な相関特性を得ることが可能なレーダ装置を提供することを課題とする。

10

【課題を解決するための手段】

【 0 0 1 9 】

本発明の第1のレーダ装置は、上記の課題を解決するために、スペクトル拡散符号および逆拡散符号を発生する符号発生器と、前記スペクトル拡散符号により変調された信号を送信する送信部と、前記送信された信号のターゲットからの反射波を受信する受信部と、前記逆拡散符号を段階的に遅延する遅延部と、前記段階的に遅延された逆拡散符号を用いて前記受信部によって受信された信号を逆拡散処理する逆拡散処理部と、前記逆拡散処理されたデータから相関値を検出する相関値検出部と、前記検出された相関値からターゲットの存在を検出するターゲット検出部とを備えたレーダ装置において、前記送信部と前記受信部間での直接波の相関強度があらかじめ決められた値以上となるように、前記スペクトル拡散符号と逆拡散符号間の位相を調整する調整部を設けて構成される。

20

【 0 0 2 0 】

スペクトル拡散符号と逆拡散符号間で、温度、電源変動によりその位相が正常な関係からずれた場合、相関特性が変化する。その変化は相関特性の波形変化および相関強度の低下をもたらす。そこで、レーダ機器等の物理的構成および配置条件等で一義的にその距離が決まる直接波を利用し、その測定された相関強度が最大値（あるマージンを含んでいても良い）となるように、スペクトル拡散符号と逆拡散符号間の位相を調整することにより、両符号間の位相のずれを補正することができる。このようにして位相のずれを補正したスペクトル拡散符号と逆拡散符号を用いて相関特性を得ることにより、距離誤差要因を低減してより正確なターゲットの距離検出が行える。

30

【 0 0 2 1 】

前記調整部は、スペクトル拡散符号と逆拡散符号のいずれか一方を遅延制御する遅延制御部で構成される。また、符号発生器が、スペクトル拡散符号生成用および逆拡散符号生成用にそれぞれPLL回路内蔵P/S変換回路を含んで構成される場合、前記調整部は、これらのPLL回路内蔵P/S変換回路のいずれか一方への入力を前記送信部と前記受信部間の直接波の相関強度があらかじめ決められた値以上となるように遅延する遅延制御部で構成される。

【 0 0 2 2 】

本発明の第2のレーダ装置は、上記の課題を解決するために、スペクトル拡散符号および逆拡散符号を発生する符号発生器と、前記スペクトル拡散符号により変調された信号を送信する送信部と、前記送信された信号のターゲットからの反射波を受信する受信部と、前記逆拡散符号を段階的に遅延する遅延部と、前記段階的に遅延された逆拡散符号を用いて前記受信部によって受信された信号を逆拡散処理する逆拡散処理部と、前記逆拡散処理されたデータから相関値を検出する相関値検出部と、前記検出された相関値からターゲットの存在を検出するターゲット検出部とを備えたレーダ装置において、

前記符号発生器はスペクトル拡散符号生成用および逆拡散符号生成用にそれぞれPLL回路内蔵P/S変換回路を含んで構成され、さらに、これらのPLL回路内蔵P/S変換回路間でその出力符号の相関値があらかじめ決められた一定の値となるように、これらのPLL回路内蔵P/S変換回路のいずれか一方への入力を遅延する遅延制御部を設けて構成

40

50

される。

【0023】

無線送受信のための回路部分は、符号生成のための回路部分に比べてその動作クロックの周波数がかなり高く、その部分で発生する温度、電源変動が特性上問題にならない場合がある。そのような場合には、解析、制御が複雑となる直接波の検出結果を用いず、符号発生器で生成されるスペクトル拡散符号および逆拡散符号間で相関特性を取得し、その相関値があらかじめ決められた値、即ち両者が正常な位相差にある場合の相関値を取るように、符号発生器の動作を調整する。これによって、温度、電源変動によって送信用のスペクトル拡散符号と逆拡散符号間の位相にずれが生じても、これを適正に補正して、正しい相関特性を得ることができる。

10

【0024】

なお、符号発生器が、スペクトル拡散符号生成用および逆拡散符号生成用にそれぞれPLL回路内蔵P/S変換回路を含んで構成されている場合、これらのPLL回路内蔵P/S変換回路間でその出力符号の相関値が前記あらかじめ決められた値となるように、これらのPLL回路内蔵P/S変換回路のいずれか一方への入力を遅延することにより、スペクトル拡散符号と逆拡散符号間の位相のずれを補正することができる。

【0025】

また、PLL回路内蔵P/S変換回路として受信用のS/P変換回路を一体に構成したものを使用する場合、それぞれのP/S変換回路出力であるスペクトル拡散符号と逆拡散符号間との間のビット位相のずれを補正するために、スペクトル拡散符号生成用のPLL回路内蔵P/S変換回路出力を逆拡散符号生成用のPLL回路内蔵P/S変換回路の受信用S/P変換回路にループバックさせても良い。

20

【発明を実施するための最良の形態】

【0026】

(実施形態1)

以下に本発明の実施形態1にかかるUWBレーダ装置について説明する。

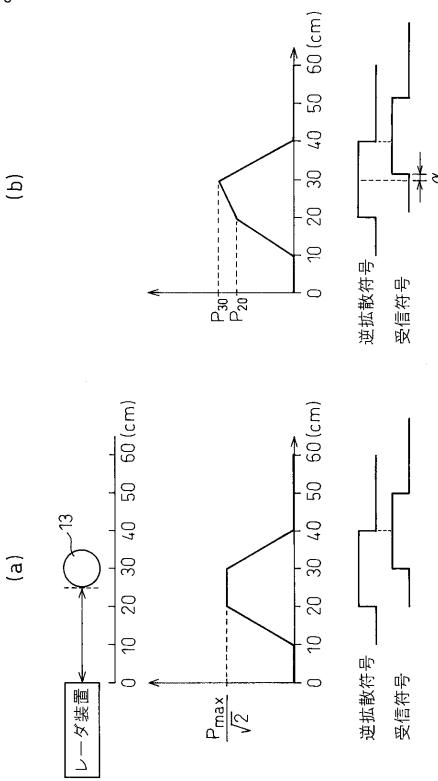

【0027】

まず、逆拡散符号と受信符号間に同期のずれがあった場合に、相関値がどのように変化するかについて説明する。図4はターゲットが基準検出距離にある場合、図5はターゲットが基準検出距離の中間にある場合の、同期ずれによる相関値の変化を示す。なお、図4および5に示す説明では、距離分解能を10cmとし、Gold符号では相関図が複雑となるためPN符号を用いている。

30

【0028】

図4(a)は、ターゲット13がレーダ装置から20cmの距離にあり、逆拡散符号および受信符号間で同期のずれがない場合の相関特性を示している。この場合は、図示するように、距離20cmのところにのみ自己相関のピークが現れる。一方、温度、電源変動により逆拡散符号と受信符号間に図(b)に示すような同期のずれが生じた場合、距離20cmのところのピーク値が減少し( $P_{max}$ から $P_d$ )、距離30cmのところに小さなピークが現れる。

40

【0029】

ある基準距離(図4の例では20cm)のピーク値が最大値よりも小さく、次の基準距離(30cm)に小さなピークを観測するということは、ターゲットが基準距離よりもわずかに次の基準距離側によって存在していることを示す。したがって、図(b)の相関特性に基づいてデータ解析を行うと、実際の距離よりもターゲットが遠くに見えてしまうことになる。この結果、検出距離に誤差が生じる。

【0030】

図5は、ターゲット13が基準距離20cmと30cmの中間にある場合の相関図を示す。この場合、逆拡散符号と受信符号は図(a)に示すように位相が半相ずれているため、距離20cmと距離30cmのところに $P_{max}/2$ をピーク値とする2個のピークが現れる。これによって、ターゲット13が、基準距離20cmと基準距離30cmの中間

50

である 25 cm の距離にあることが理解される。

【0031】

レーダ装置の使用中に温度、電源等が変動し、逆拡散符号と受信符号間に位相のずれが生じると、図(a)の波形が崩れ、図(b)に示すように距離 30 cm のピーク値が増加し、距離 20 cm のピーク値が減少する。この結果、ターゲット 13 が距離 25 cm よりも基準距離 30 cm 側に寄っているように理解され、検出距離に誤差を生じる。

【0032】

なお、図 4 および 5 は、送信符号が遅くなつた場合、もしくは逆拡散符号が速くなつた場合を示しているが、送信符号が早くなつた場合、もしくは逆拡散符号が遅くなつた場合は図 4 および 5 に示す例とは逆に、ターゲットが実際の距離よりも近くに検出される。

10

【0033】

以上のように、逆拡散符号と受信符号間に温度、電源変動により位相のずれが生じた場合、相関値の波形に崩れが生じる。したがって、相関値の波形が図 4 および図 5 において、(b) に示すものから (a) に示すものとなるように、逆拡散符号と受信符号間の位相を調整することができれば、両者の間の温度、電源変動による位相のずれを補償することができる。

【0034】

本発明はこのような観点からなされたもので、レーダ装置の物理的構成および配置条件等で一義的に距離が決まる直接波を利用し、直接波の相関強度が最大となるように、符号発生器で生成される送信符号と逆拡散符号間の位相差を調整することによって、温度、電源変動に影響されない正確な相関値を得るようにしたものである。

20

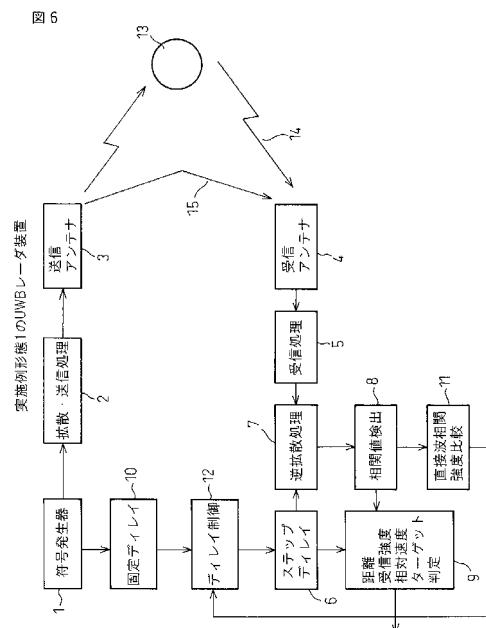

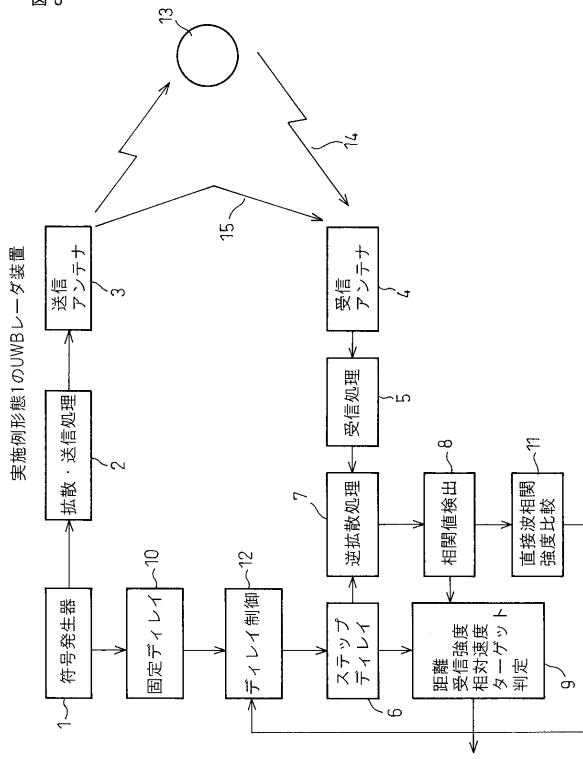

【0035】

図 6 に、このような考えに基づいて構成された本発明の実施形態 1 にかかる UWB レーダ装置を示す。なお、図 6 および以下に説明するその他の実施形態の図面において、図 1 に示すものと同じ符号は同一または類似の構成要素を示すので、その重複した説明は行わない。

【0036】

図 6 の装置は、図 1 の装置において、相関値検出部 8 の後段に、直接波相関強度の比較部 11 とこの比較部 11 における比較結果に基づいて逆拡散符号のディレイ制御を行うディレイ制御部 12 を設けたことを特徴とする。直接波相関強度比較部 11 は、あらかじめ測定によって決定されかつ機器に組み込まれた直接波の相関強度に関する基準データを保持しており、レーダ装置の運用中、相関値検出部 8 において検出された直接波の相関強度をこの基準データと比較し、その間に差があるとその差が 0 となるまで、あるいは一定の許容範囲内に収まるまで、ディレイ制御部 12 を制御して逆拡散符号を遅延させる。

30

【0037】

図 4 および 5 を用いて説明したように、直接波の相関強度が基準データ値に補正された場合、逆拡散符号と受信符号間で位相のずれが無くなっているか、あるいは許容範囲内に収まっているものと考えられる。したがって、この状態でレーダ測定を行うと、補正された相関特性が得られる。なお、直接波の相関強度における基準データは、このレーダ装置を出荷する場合に、ある程度のマージンをとって機器に組み込んでおく。

40

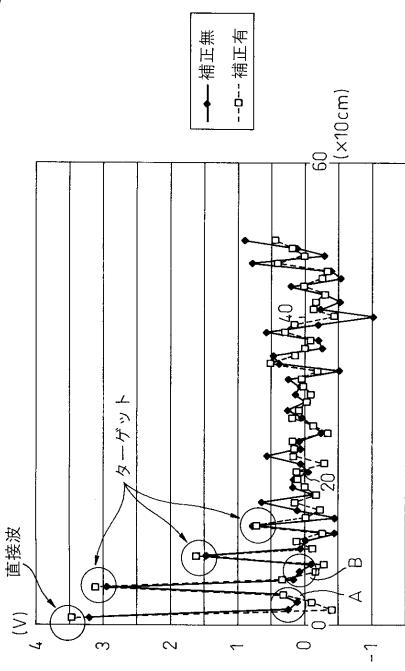

【0038】

図 7 は、補正前の相関特性と補正後の相関特性を示す図である。図において、実線は補正前の相関特性データを、一破鎖線は補正後の相関特性を示す。この図から、ターゲットの相関強度が全体として増加し、位相ずれが補正されていることが理解される。また、図に A および B で示す部分では補正後の相関値が大きく下がっており、一方、ターゲットの相関ピーク値は増加している。このことから、補正前の A および B 部分の相関値は、図 4 (b) に示した現象によって持ち上がっているものと考えられる。したがって、本実施形態によるディレイ補正を行うことによって正しい相関特性が得られ、この相関特性に基づいてデータ分析を行うことにより距離誤差要因が取り除かれて正確な距離検出を行うことができる。

50

## 【0039】

なお、図6に示す実施形態1では、固定ディレイ10の後段にディレイ制御部12を配置しているが、本実施形態はこの構成に限定されるものではない。例えば、ディレイ制御部12は、固定ディレイ10の前段に配置しても良く、さらには符号発生器1と拡散・送信処理部2の間に配置し、送信符号を遅延制御してもよい。また、逆拡散符号が受信符号に対して遅れている場合は、逆拡散符号の位相を進める制御を行う。ディレイ制御部12における制御の目的は、逆拡散符号と受信符号間の位相を正常な関係に戻すことである。

## 【0040】

## (実施形態2)

以下に本発明の実施形態2について説明する。

10

## 【0041】

数百MHz以上の高速信号を生成する場合は、低速で生成した信号列を、PLL回路等を用いて高速信号に変換することが一般的に行われている。実施形態2では、このようなPLL回路を用いた符号発生器を使用して送信符号と逆拡散符号を生成し、その符号生成の過程で実施形態1におけるディレイ制御を行うようにしたものである。

## 【0042】

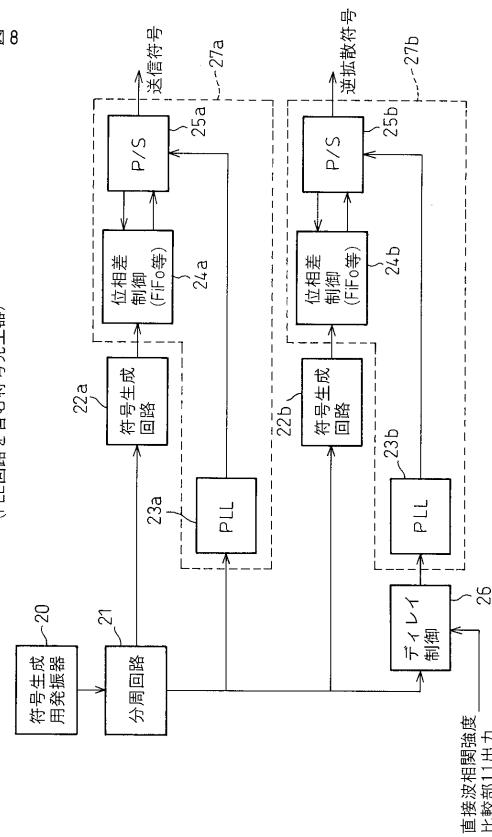

図8は、PLL回路を用いて形成した図6の符号生成器1を示す。図8において、20は符号生成用のクロック信号を発振する発振器、21は発振器20によって生成された信号をさらに高速とするための分周回路である。分周回路21の出力は、送信符号形成用の符号生成回路22a、逆拡散符号生成用の符号生成回路22b、送信符号生成用のPLL回路23aおよび逆拡散符号生成用のPLL回路23bに出力される。

20

## 【0043】

符号生成回路23aで生成された符号は、FiFo等の位相差制御回路24aを介してP/S(パラレル-シリアル)変換回路25aに出力され、ここでPLL回路23aにより高速信号に変換された後、送信符号として出力される。符号生成回路22bで生成された符号列も同様にして、FiFo等の位相差制御回路24bを介してP/S(パラレル-シリアル)変換回路25bに出力され、ここでPLL回路23bにより高速信号に変換された後、逆拡散符号として出力される。

## 【0044】

P/S変換回路24aからの出力符号列は、図6の拡散・送信処理部2に出力され、P/S変換回路24bからの出力符号列は図6の固定ディレイ10、ステップディレイ6を経て、逆拡散処理部7に導入される。

30

## 【0045】

なお、図8の回路において、分周回路21を用いない構成もあり、また図に点線で示す部分27aおよび27bの機能をサーデス(Serdes)回路によって構成することも可能である。

## 【0046】

本実施形態では、実施形態1のディレイ制御部12に代わって符号発生器内部にディレイ制御部26を設け、逆拡散符号生成用のPLL回路23bにディレイ制御を行うようにしている。このディレイ制御は、図6の直接波相関強度比較部11において検出された直接波の基準強度と検出強度の差が実質的に0となるまで、逆拡散符号の位相を遅らせあるいは早めるものである。したがってディレイ制御部26には、図6に示す直接波相関強度比較部11の出力が導入される。

40

## 【0047】

このように、実施形態1では符号発生器1の外部でディレイ制御を行う構成であるが、実施形態2では符号発生器内でディレイ制御を行う点に特徴がある。

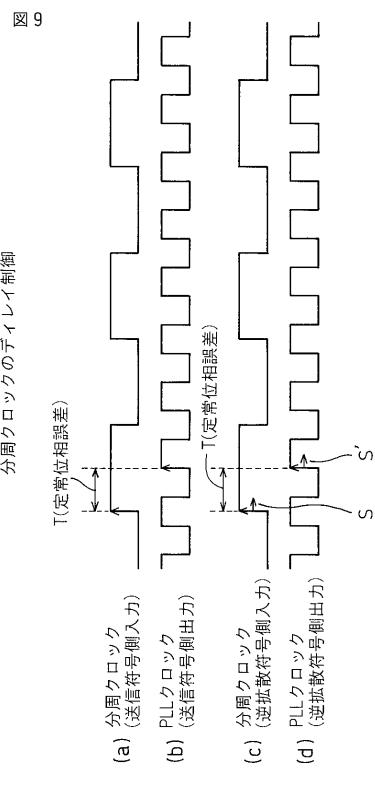

## 【0048】

図9は、分周回路21で生成される分周クロックと、PLL回路23aおよび23bの出力クロック(PLLクロック)のタイミングを示す図である。図(a)は送信符号側PLL回路23aへの入力信号(分周クロック)を、図(b)はPLL回路23aの出力ク

50

ロックを示す。さらに図(c)は逆拡散符号側PLL回路23bへの入力信号(分周クロック)を、図(d)はPLL回路23bの出力クロックを示す。

【0049】

図示するように、PLL回路23a、23bの出力は、外部から供給される低速クロック(分周クロック)に対して一定の位相関係、即ち定常位相誤差Tを有する。この場合、図(c)に示すように分周クロックに遅延Sをかけると、図(d)に示すようにその遅れに追従してPLLクロックも遅延S'を生じ、逆拡散符号を遅延させる。なお、図8では逆拡散符号生成用のPLL回路23bにディレイ制御を行っているが、送信符号生成用のPLL回路23aに位相を進める方向のディレイ制御を行っても、同じ効果が得られる。

【0050】

なお、PLL回路23aまたは23bの出力クロックに対してディレイ制御を行っても同じ効果が得られ、その場合はより細かいステップでディレイ制御が可能である。しかしながら、PLL回路の出力クロックにディレイ制御するためには、特性補償、回路の作り込み等が困難になり、装置の価格上昇の要因ともなる。

【0051】

したがって、図8に示す実施形態2では、ある程度あらいステップでしかディレイ制御が行えないが、分周回路21の出力クロックにディレイをかけることによって、実施形態1と同じ逆拡散符号または送信符号のディレイ制御を行うようにしている。これにより、簡単かつ安価な構成によりディレイ制御を行うことができる。

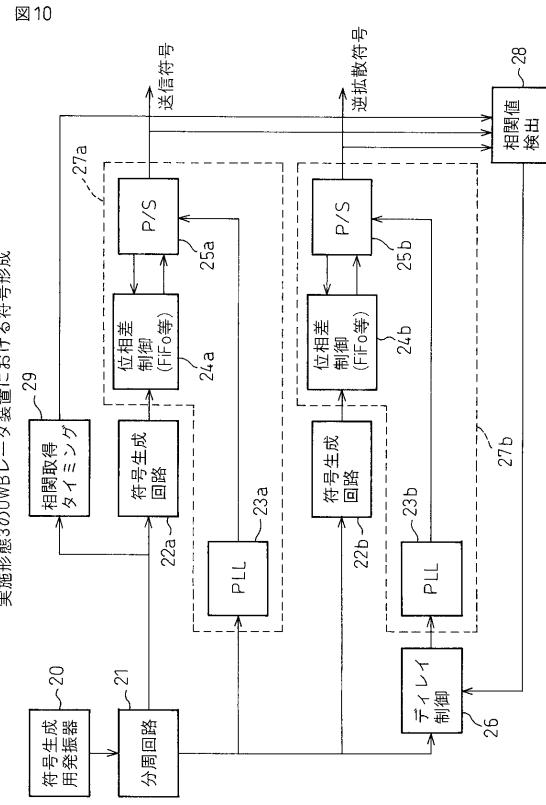

【0052】

(実施形態3)

図10は、本発明の実施形態3にかかるUWBレーダ装置の符号発生器の構成を示す回路図である。本実施形態では、図6に示すUWBレーダ装置において、拡散・送信処理部2、送信アンテナ3、受信アンテナ4および受信処理部5を含む無線送受信処理のための機構の温度、電源変動が特性上問題にならない場合を想定して構成されている。無線送受信処理部分を構成する部品は、その動作速度が通常数十ギガ程度であり、一方符号生成部分の動作速度は数ギガ程度である。したがって、無線送信処理部分の温度、電源変動の影響は、符号生成部分の十分の1程度と小さく、装置の価格面を重視する場合、無視することができる。

【0053】

したがって、図6の回路において、拡散・送信処理部2、送信アンテナ3、受信アンテナ4および受信処理部5の温度、電源変動を考慮しなくても良い場合は、符号発生器1、固定ディレイ10、ディレイ制御部12、ステップディレイ6および逆拡散処理部7を含む部分で、位相調整を行えばよい。そのため、解析、制御が複雑である直接波の検出結果から送信符号、逆拡散符号間の位相を合わせる必要がなくなる。

【0054】

本実施形態では、符号発生器1で生成された送信符号と逆拡散符号間の相関を取り、その相関値から送信符号と逆拡散符号間の位相のずれを補正する構成をとっている。

【0055】

したがって本実施形態では、図8に示した構成の符号発生器に対して、図10に示すように、送信符号と逆拡散符号間の相関値を検出する相関値検出部28と、相関値を取得するタイミングを決定する相関値取得タイミング設定部29を新たに設け、検出した相関値があらかじめ決定された値、即ち送信符号と逆拡散符号間に温度、電源変動によって生じた位相のずれがない場合の相関値となるように、ディレイ制御部26のディレイ制御を行う。これによって、相関値における温度、電源変動の影響の、ほとんどの部分を除去することが可能となる。相関値取得のタイミングは、機器の設計に基づいて適宜に決定される。

【0056】

なお、図10に示した構成では、図8に示した符号発生器を利用しているが、本実施形態ではこの構成に限定されるものではない。即ち、図6に示す実施形態1のUWBレーダ

10

20

30

40

50

装置において、符号発生器1の出力部分において送信符号と逆拡散符号間の相関特性を取得する手段を設け、その結果に基づいてディレイ制御部12を制御することによって、本実施形態の目的を達成することができることは勿論である。

#### 【0057】

##### (実施形態4)

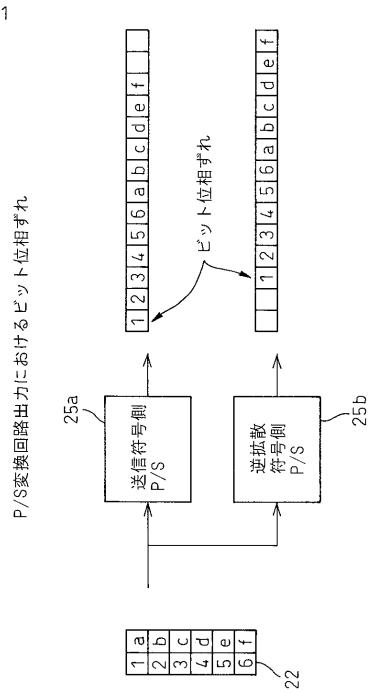

図8および10に示した、PLL機能を利用した符号発生器では、ある動作速度までは、送信符号側、逆拡散符号側のP/S変換回路におけるビット位相を制御することが可能である。しかしながら、デバイスの動作速度がさらに増加すると、デバイスの能力に依存してP/S変換回路のビット位相を制御することが困難となる。また、図8および10において点線で示した部分27aおよび27bを、例えばSerdes回路等の汎用部品で構成する場合は、各P/S変換回路のビット位相を制御することができない。本実施形態では、このような回路構成上生じる送信符号と逆拡散符号間の位相のずれを解消させることを目的としている。

#### 【0058】

図11は、送信符号生成側のP/S変換回路25aと、逆拡散符号生成側のP/S変換回路25b間のビット位相ずれを説明するための図である。符号生成回路22より生成された符号はP/S変換回路25a、25bにおいて高速で並直列変換されて出力されるが、このとき出力された符号のビット位相は、電源投入、リセット毎に変化し、そのためP/S変換回路25aおよび25b間で一定の位相関係に固定することができない。

#### 【0059】

汎用部品としてのPLL内蔵P/S変換回路は、一般に直並列(S/P)変換回路と一体化して構成され、またSerdes回路も送受信処理機能を一体で有している。

#### 【0060】

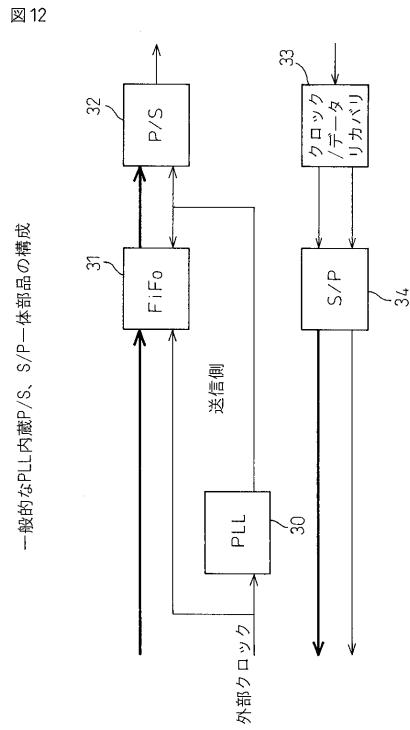

図12に、一般的なPLL内蔵P/S、S/P一体部品の構成を示す。図において、30はPLL回路、31はエンコーダ、32はP/S変換回路であり、送信側の機能を構成する。33はクロック/データリカバリ、34はS/P変換回路であって受信側の機能を構成する。なお、クロック/データリカバリ33を搭載しない回路もある。S/P変換回路34は、図11に示すP/S変換回路25a、25bと同様に、直並列変換時のビット位相を制御できないものが多い。

#### 【0061】

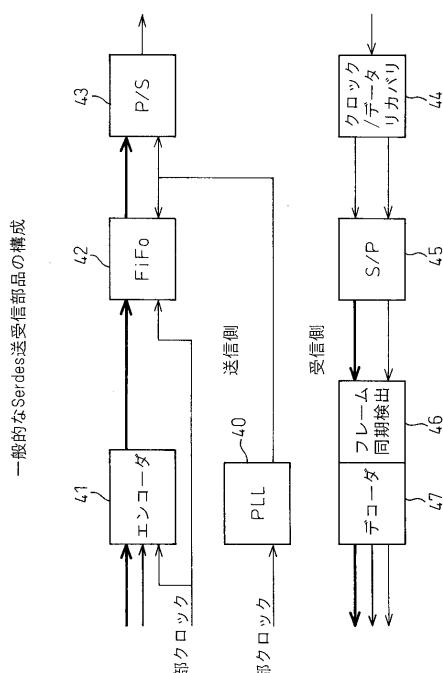

図13に、一般的なSerdes送受信部品の構成を示す。図において、40はPLL回路、41はエンコーダ、42はエンコーダ、43はP/S変換回路であり、これらは送信側の機能を構成する。さらに44はクロック/データリカバリ、45はS/P変換回路、46はフレーム同期検出回路、47はデコードであって、これらは受信側の機能を構成する。この回路で、S/P変換回路45も、図11に示すP/S変換回路25a、25bと同様に、直並列変換時のビット位相を制御できないものが多い。

#### 【0062】

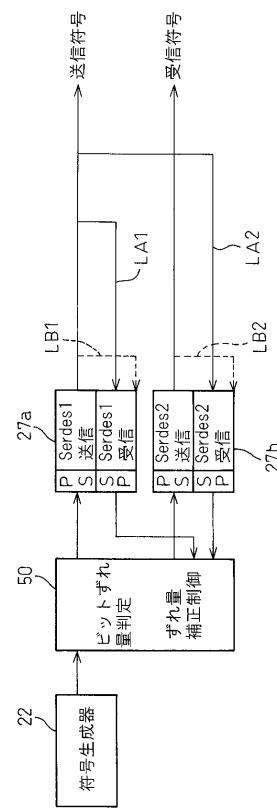

本実施形態では、PLL内蔵P/S変換回路部品が有する上記のような送受信機能を利用して、送信符号と逆拡散符号間に生じるビット位相のずれを検出し、その補正を行うようとしたものである。以下に、本実施形態の構成を、PLL内蔵P/S変換回路をSerdes回路で構成した場合を例にして説明する。

#### 【0063】

図14は、Serdes回路を使用した場合の送信符号、逆拡散符号間のビット位相制御を示す図である。本実施形態では、送信符号生成用のSerdes1(27a)を基準側とし、基準側に対するSerdes1の受信側のビット位相のずれを検出するためのループバックLA1、基準側に対するSerdes2(27b)の受信側のビットずれを検出するループバックLA2を設ける。

#### 【0064】

さらに、各個別のSerdesにおける送受信部間のビット位相のずれを検出するループバックLB1およびLB2を設け、これらのループバックで検出されたビット位相ずれ

10

20

30

40

50

から、Serdes1およびSerdes2間の送信出力におけるビット位相ずれを検出する。図14の50は、それぞれのループバックに基づいてSerdes1およびSerdes2間の送信出力におけるビット位相ずれを検出し、検出結果に基づいてSerdes1またはSerdes2の入力側のビット位相調整を行うための、ビット位相補正回路である。

#### 【0065】

以下、図14および15を参照して、ビット位相調整回路50におけるビットズレ量判定および補正制御について具体的に説明する。図14において、符号27aで示すSerdes1は送信符号生成用のPLL内蔵P/S変換回路回路であり、送信用P/S変換回路と受信用S/P変換回路を含んでいる。符号27bで示すSerdes2は、逆拡散符号生成用のPLL内蔵P/S変換回路であり、送信用P/S変換回路と受信用S/P変換回路を含んでいる。

10

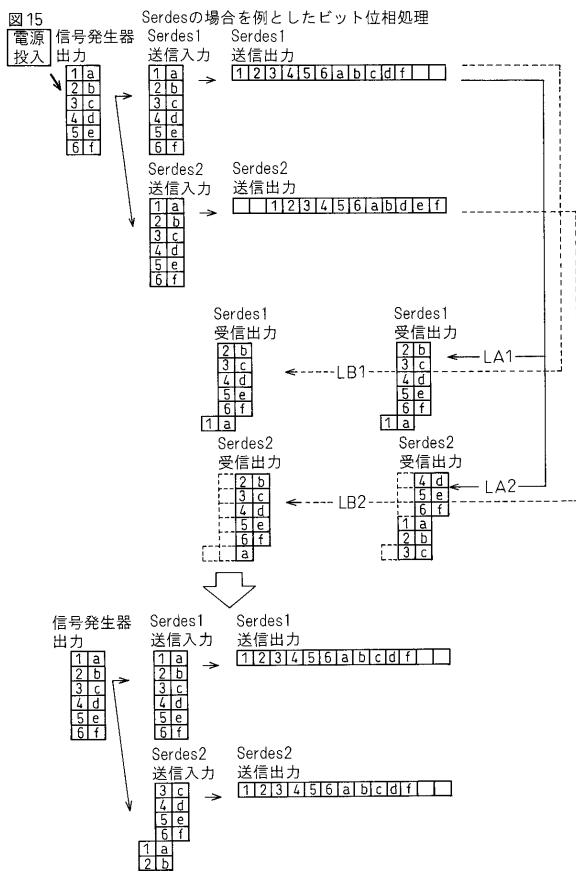

#### 【0066】

図15に、Serdes1とSerdes2間のビット位相差を2ビットとした場合の、各ループにおける受信出力が示されている。ここで、ループバックLA1とLA2におけるSerdes1受信出力とSerdes2受信出力を、図14のビット位相補正回路50において比較すると、Serdes2受信出力はSerdes1受信出力に比べて4ビット分遅れていることが分かる。次に、ループバックLB1とLB2におけるSerdes1受信出力とSerdes2受信出力を回路50において比較すると、Serdes2受信出力がSerdes1受信出力に比べて6ビット遅れていることが分かる。

20

#### 【0067】

Serdes1とSerdes2の送信側のビット位相差は、ループバックLA2とLB2におけるSerdes2の受信出力間のビット位相差であるので、6ビット - 4ビット = 2ビットが、Serdes2の送信出力遅れであることが理解される。

#### 【0068】

以上のようにして、補正回路50においてSerdes1とSerdes2のビット位相ずれの数値が決定されると、その分のビットだけ、Serdes2への符号の供給を早める。これによって、Serdes1とSerdes2間のビット位相を一致させることが可能となる。

30

#### 【0069】

図14に示すビット位相制御回路は、図8または図10に示す回路中に組み込まれて使用される。

#### 【0070】

上記実施形態3および4に示す位相ずれ補正の制御は、UWBレーダ装置としてのターゲット検出処理とは別に行う必要がある。また、実施形態4に示す補正は、電源投入時あるいはリセット時に1回行えば、通常、装置の運用中再度行う必要がない。しかしながら、実際にはスパークノイズ等の外的ノイズまたは電源の急変などによる異常によって、運用中に予期しない位相ずれが生じる。このような事態に対処するために、実施形態3または4に示した制御を周期的に行っても良い。この場合、ターゲットの検出処理を可能な限り劣化させないような周期を選択することが好ましい。また、UWBレーダ装置がターゲットを捕捉していない状況を利用して行うことも可能である。

40

#### 【0071】

実施形態3、4に示した制御のこのような繰り返しの実行により、車両の走行期間中、UWBレーダ装置の動作の安定性を確保することが可能となる。

#### 【図面の簡単な説明】

#### 【0072】

【図1】一般的なUWBレーダ装置の概略構成を示すブロック図。

【図2】図1の装置の動作説明に供するタイムチャート。

【図3】受信符号と逆拡散符号間の温度、電源変動による影響を説明するための図。

【図4】受信符号と逆拡散符号間の位相のずれが、自己相関特性に及ぼす影響を説明する

50

ための図。

【図5】受信符号と逆拡散符号間の位相のズレが、自己相関特性に及ぼす影響を説明するための図。

【図6】本発明の実施形態1にかかるUWBレーダ装置の概略構成を示すブロック図。

【図7】図6に示す装置を用いて取得した相関特性を示す図。

【図8】本発明の実施形態2にかかるUWBレーダ装置の要部の構成を示すブロック図。

【図9】分周クロックとPLLクロックの関係を示す図。

【図10】本発明の実施形態3にかかるUWBレーダ装置の要部の構成を示すブロック図。

。

【図11】本発明の実施形態4の動作説明に供する図。 10

【図12】一般的なPLL内蔵P/S変換回路の構成を示す図。

【図13】一般的なSerdess回路の構成を示す図。

【図14】本発明の実施形態4にかかるUWBレーダ装置の要部構成を示すブロック図。

【図15】図14に示す回路部分の動作説明に供する図。

【符号の説明】

【0073】

1 ... 符号発生器

2 ... 拡散・送信処理部

3 ... 送信アンテナ

4 ... 受信アンテナ

5 ... 受信処理部

6 ... ステップディレイ

7 ... 逆拡散処理部

8 ... 相関値検出部

9 ... ターゲット検出部

10 ... 固定ディレイ

11 ... 直接波相関強度比較部

12 ... ディレイ制御部

13 ... ターゲット

14 ... 反射波

15 ... 直接波

26 ... ディレイ制御部

28 ... 相関値検出部

29 ... 相関値取得タイミング設定部

10

20

30

【 四 5 】

ターナーが塞半立間間にめる場所の相対性

〔 図 7 〕

補正前および補正後の相美特性

【 四 6 】

図 6

〔 四 8 〕

四

実施形態2のUWBレーダ装置における符号形成

(P) 回路を含む符号発生器

【図 9】

【図 11】

【図 10】

【図 12】

【図13】

図13

【図14】

図14

【図15】

---

フロントページの続き

(74)代理人 100082898

弁理士 西山 雅也

(72)発明者 廣森 正樹

神奈川県横浜市港北区新横浜3丁目9番18号 新横浜T E C Hビル 富士通ネットワークテクノ

ロジーズ株式会社内

F ターム(参考) 5J070 AB07 AC02 AC07 AD02 AE01 AF03 AH04 AK06 AK28 AK35

BF00