## (12)发明专利

(10)授权公告号 CN 105981145 B

(45)授权公告日 2019.06.04

(21)申请号 201480066832.1

(74)专利代理机构 上海专利商标事务所有限公司 31100

(22)申请日 2014.11.20

代理人 袁逸

(65)同一申请的已公布的文献号

申请公布号 CN 105981145 A

(51)Int.Cl.

H01L 21/336(2006.01)

(43)申请公布日 2016.09.28

H01L 21/74(2006.01)

(30)优先权数据

H01L 29/78(2006.01)

14/100,760 2013.12.09 US

H01L 29/10(2006.01)

(85)PCT国际申请进入国家阶段日

H01L 29/205(2006.01)

2016.06.07

(56)对比文件

(86)PCT国际申请的申请数据

CN 102983165 A, 2013.03.20,

PCT/US2014/066676 2014.11.20

US 2009/0242873A1 A1, 2009.10.01,

(87)PCT国际申请的公布数据

CN 102983165 A, 2013.03.20,

W02015/088737 EN 2015.06.18

EP 1102327 A2, 2001.05.23,

(73)专利权人 高通股份有限公司

CN 102376715 A, 2012.03.14,

地址 美国加利福尼亚州

审查员 倪敬涵

(72)发明人 B·杨 X·李 P·齐达姆巴兰姆

权利要求书3页 说明书11页 附图10页

(54)发明名称

具有扩散势垒区的晶体管

(57)摘要

一种装置包括基板。该装置还包括形成在该基板的第一区域的表面上的扩散势垒区。该扩散势垒区是使用具有第一带隙能量的第一材料形成的。该装置进一步包括形成在该扩散势垒区的表面上的沟道区。该沟道区是使用具有低于该第一带隙能量的第二带隙能量的第二材料形成的。该装置进一步包括耦合到该基板的第一区域的背栅触点。

1. 一种装置，包括：

基板；

形成在所述基板的第一区域的表面上的扩散势垒区，其中所述扩散势垒区是使用具有第一带隙能量的第一材料形成的；

形成在所述扩散势垒区的表面上的沟道区，其中所述沟道区使用具有低于所述第一带隙能量的第二带隙能量的第二材料形成；以及

耦合到所述基板的所述第一区域的背栅触点，所述背栅触点延伸到所述基板的所述第一区域中。

2. 如权利要求1所述的装置，其特征在于，所述第一区域具有比所述沟道区更高的掺杂浓度。

3. 如权利要求1所述的装置，其特征在于，所述第一材料包括III-V族复合物或II-VI族复合物。

4. 如权利要求1所述的装置，其特征在于，所述第一材料包括砷化铝或砷化铟铝。

5. 如权利要求1所述的装置，其特征在于，所述第二材料包括砷化镓或砷化铟镓。

6. 如权利要求1所述的装置，其特征在于，所述沟道区和所述第一区域是基于超锐逆掺杂分布来掺杂的。

7. 如权利要求1所述的装置，其特征在于，进一步包括：

形成在所述沟道区的表面上的介电层；

形成在所述介电层的表面上的金属栅极；

形成在所述扩散势垒区的所述表面上的源极区；

形成在所述扩散势垒区的所述表面上的漏极区；

毗邻于所述源极区的第一浅沟槽隔离区；以及

毗邻于所述漏极区的第二浅沟槽隔离区。

8. 如权利要求1所述的装置，其特征在于，所述扩散势垒区介于所述沟道区和所述第一区域之间。

9. 如权利要求1所述的装置，其特征在于，所述装置是平面金属氧化物半导体场效应晶体管(MOSFET)。

10. 如权利要求1所述的装置，其特征在于，所述装置是鳍式场效应晶体管(FinFET)。

11. 一种方法，包括：

在基板的重掺杂区的表面上形成扩散势垒区，其中所述扩散势垒区是使用具有第一带隙能量的第一材料形成的；

在所述扩散势垒区的表面上形成沟道区，其中所述沟道区使用具有低于所述第一带隙能量的第二带隙能量的第二材料形成；

蚀刻所述沟道区的特定区域以形成源极区和漏极区；以及

形成背栅触点，所述背栅触点延伸到所述基板的所述重掺杂区中。

12. 如权利要求11所述的方法，进一步包括形成耦合到所述重掺杂区的背栅触点。

13. 如权利要求11所述的方法，其特征在于，所述扩散势垒区陷住来自所述重掺杂区的掺杂物。

14. 如权利要求13所述的方法，其特征在于，所述扩散势垒区在所述扩散势垒区的较低

界面处陷住所述掺杂物,以及其中所述第一材料是砷化镓或者砷化铟镓,并且所述第二材料是砷化铝或砷化铟铝。

15. 如权利要求13所述的方法,其特征在于,所述扩散势垒区在所述扩散势垒区的较高界面处陷住所述掺杂物,以及其中所述第一材料是硅,并且所述第二材料是砷化铝或砷化铟铝。

16. 如权利要求11所述的方法,其特征在于,所述重掺杂区具有比所述沟道区更高的掺杂浓度。

17. 如权利要求11所述的方法,其特征在于,所述第一材料包括III-V族复合物或II-VI族复合物。

18. 如权利要求11所述的方法,其特征在于,所述第一材料包括砷化铝或砷化铟铝。

19. 如权利要求11所述的方法,其特征在于,所述第二材料包括砷化镓或砷化铟镓。

20. 如权利要求11所述的方法,其特征在于,所述重掺杂区和所述沟道区是根据超锐逆掺杂分布形成的。

21. 如权利要求11所述的方法,其特征在于,进一步包括:

在所述沟道区的表面上形成介电层;

在所述介电层的表面上形成金属栅极;以及

在所述基板的第一表面上形成第一浅沟槽隔离区,以及在所述基板的第二表面上形成第二浅沟槽隔离区,其中所述第一浅沟槽隔离区和所述第二浅沟槽隔离区经由蚀刻工艺形成,并且其中所述第一浅沟槽隔离区毗邻于所述源极区并且所述第二浅沟槽隔离区毗邻于所述漏极区。

22. 如权利要求21所述的方法,其特征在于,所述金属栅极在形成所述源极区之前形成。

23. 如权利要求21所述的方法,其特征在于,所述金属栅极在所述源极区和所述漏极区的形成之后形成。

24. 一种装备,包括:

用于阻止掺杂物扩散的装置,其中所述用于阻止掺杂物扩散的装置形成在基板的重掺杂区的表面上,并且其中所述用于阻止掺杂物扩散的装置使用具有第一带隙能量的第一材料形成;

用于提供导电沟道的装置,其中所述用于提供导电沟道的装置形成在所述用于阻止掺杂物扩散的装置的表面上,并且其中所述用于提供导电沟道的装置使用具有低于所述第一带隙能量的第二带隙能量的第二材料形成;以及

用于控制阈值电压的装置,其中所述用于控制阈值电压的装置延伸到所述基板的所述重掺杂区中。

25. 如权利要求24所述的装备,其特征在于,所述第一区域具有比所述用于提供导电沟道的装置更高的掺杂浓度。

26. 如权利要求24所述的装备,其特征在于,所述第一材料包括III-V族复合物或II-VI族复合物。

27. 如权利要求24所述的装备,其特征在于,所述第一材料包括砷化铝或砷化铟铝。

28. 如权利要求24所述的装备,其特征在于,所述第二材料包括砷化镓或砷化铟镓。

29. 如权利要求24所述的装备，其特征在于，所述装备是根据超锐逆掺杂分布形成的。

30. 一种存储指令的计算机可读存储设备，所述指令能由计算机执行以执行操作，所述操作包括：

发起在基板的重掺杂区的表面上形成扩散势垒区，其中所述扩散势垒区是使用具有第一带隙能量的第一材料形成的；

发起在所述扩散势垒区的表面上形成沟道区，其中所述沟道区使用具有低于所述第一带隙能量的第二带隙能量的第二材料形成；

发起蚀刻所述沟道区的特定区域以形成源极区和漏极区；以及

发起形成背栅触点，所述背栅触点延伸到所述基板的所述重掺杂区中。

## 具有扩散势垒区的晶体管

[0001] 相关申请的交叉引用

[0002] 本申请要求共同拥有的于2013年12月9日提交的美国非临时专利申请No.14/100,760的优先权，该非临时专利申请的内容通过援引全部明确纳入于此。

[0003] 领域

[0004] 本公开一般涉及晶体管。

[0005] 相关技术描述

[0006] 技术进步已产生越来越小且越来越强大的计算设备。例如，当前存在各种各样的便携式个人计算设备，包括较小、轻量且易于由用户携带的无线计算设备，诸如便携式无线电话、个人数字助理 (PDA) 以及寻呼设备。更具体地，便携式无线电话 (诸如蜂窝电话和网际协议 (IP) 电话) 可通过无线网络传达语音和数据分组。此外，许多此类无线电话包括被纳入于其中的其他类型的设备。例如，无线电话还可包括数码相机、数码摄像机、数字记录器以及音频文件播放器。同样，此类无线电话可处理可执行指令，包括可被用于访问因特网的软件应用，诸如web浏览器应用。如此，这些无线电话可包括显著的计算能力。

[0007] 移动设备 (例如，智能电话、平板计算机、膝上型计算机等) 可以使用晶体管 (诸如金属氧化物半导体场效应晶体管 (MOSFET)) 实现。MOSFET的阈值电压可以由MOSFET的掺杂部分根据超锐逆掺杂分布来控制。为了实现超锐逆掺杂分布，可以使用不同的掺杂浓度来掺杂沟道区 (例如，直接在MOSFET的栅极下方的区域) 和沟道下方的区域 (“重掺杂区”)。沟道区的高度可以变动以控制器件阈值电压。例如，与重掺杂区的掺杂浓度相比，沟道区可以不掺杂或者可以具有较低掺杂浓度。然而，采用超锐逆掺杂分布的常规硅MOSFET可能不具有掺杂扩散势垒区来降低从重掺杂区到沟道区的掺杂物扩散。由此，沟道区的宽度因掺杂物扩散而降低，导致可能不能获得目标器件阈值电压。

[0008] 概述

[0009] 公开了降低基于超锐逆掺杂分布 (例如，沟道区和在沟道区下方的区域使用不同掺杂浓度来掺杂) 掺杂的MOSFET的掺杂物扩散的系统和方法。当MOSFET使用超锐逆掺杂分布制造时，所描述的技术可以使用扩散势垒区来降低从重掺杂区到沟道区的掺杂物扩散。扩散势垒区可以使用III-V族复合物 (例如，使用周期表中III组和V组中的元素形成的复合材料) 或II-VI族复合物 (例如，使用周期表中II组和VI组元素形成的复合材料) 形成。例如，扩散势垒区可以使用砷化铝 (AlAs) 形成。作为另一示例，扩散势垒区可以使用砷化铟铝 (InAlAs) 形成。由此，与不具有扩散势垒区的基于超锐逆掺杂分布来掺杂的硅MOSFET相比，掺杂物扩散可以被降低。

[0010] 在特定实施例中，一种装置包括基板以及形成在该基板的第一区域的表面上的扩散势垒区。该扩散势垒区是使用具有第一带隙能量的第一材料形成的。该装置还包括形成在该扩散势垒区的表面上的沟道区。该沟道区是使用具有低于该第一带隙能量的第二带隙能量的第二材料形成的。该装置进一步包括耦合到该基板的第一区域的背栅触点。

[0011] 在特定实施例中，一种方法包括在基板的重掺杂区的表面上形成扩散势垒区。该扩散势垒区是使用具有第一带隙能量的第一材料形成的。该方法还包括在该扩散势垒区的

表面上形成沟道区。该沟道区是使用具有低于该第一带隙能量的第二带隙能量的第二材料形成的。该方法进一步包括蚀刻沟道区的特定区域以形成源极区和漏极区。

[0012] 由至少一个所公开的实施例提供的一个特定优点在于制造具有降低的掺杂物扩散的采用超锐逆掺杂分布的MOSFET的能力。本公开的其他方面、优点和特征将在阅读了整个申请后变得明了，整个申请包括下述章节：附图简述、详细描述以及权利要求书。

[0013] 附图简述

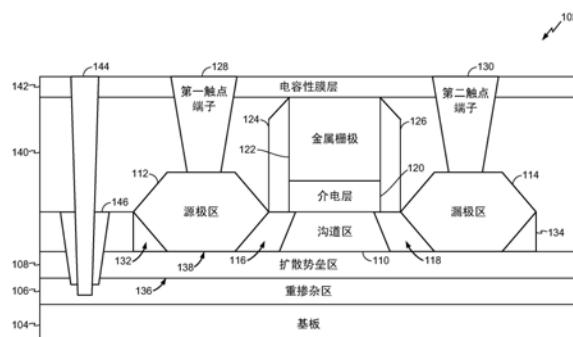

[0014] 图1是解说具有扩散势垒区的平面金属氧化物半导体场效应晶体管(MOSFET)的特定实施例的示图；

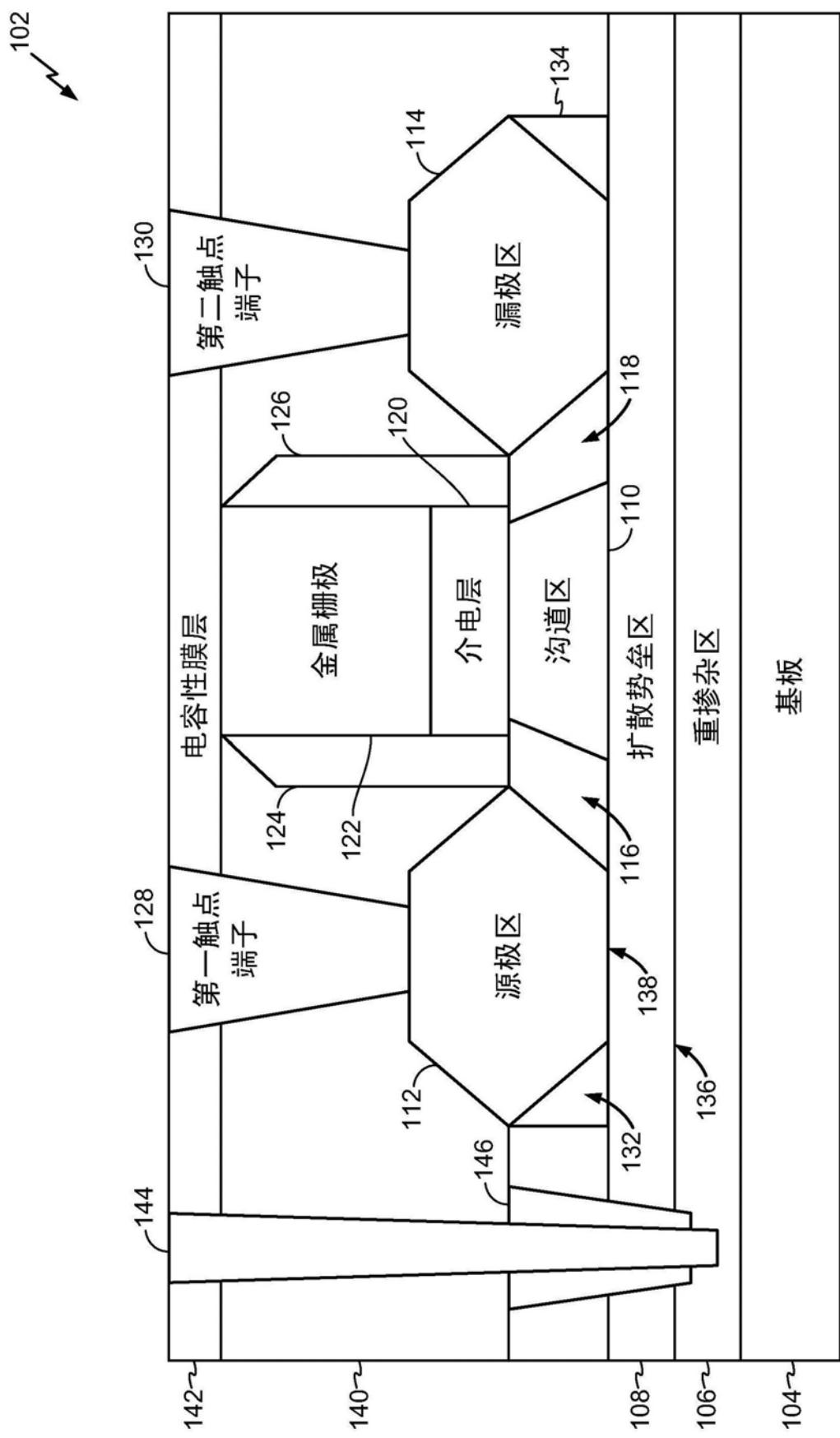

[0015] 图2是解说平面配置的具有扩散势垒区的平面MOSFET的另一特定实施例的示图；

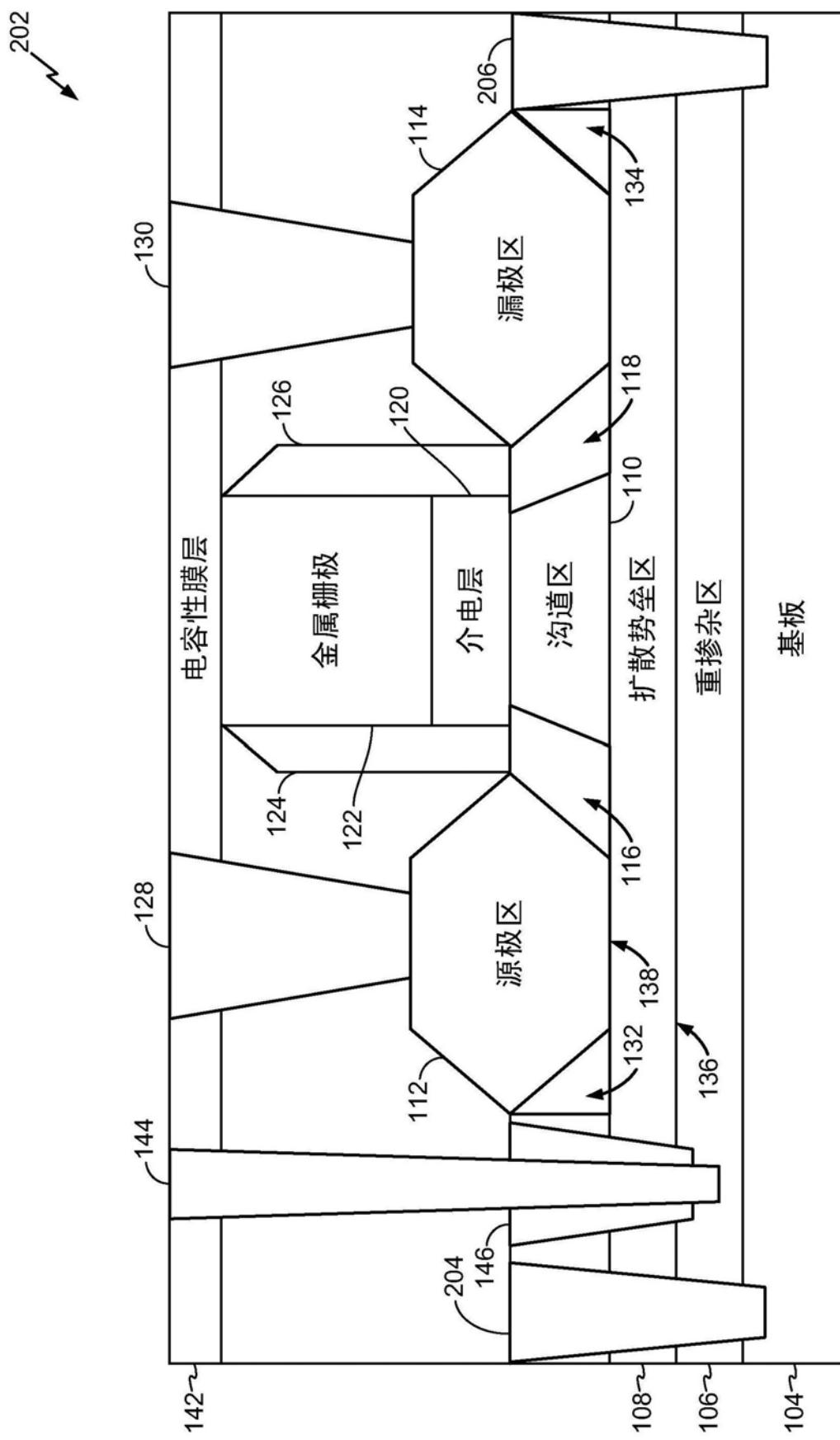

[0016] 图3是解说制造具有扩散势垒区的平面MOSFET的后栅极工艺的一部分的特定实施例的示图；

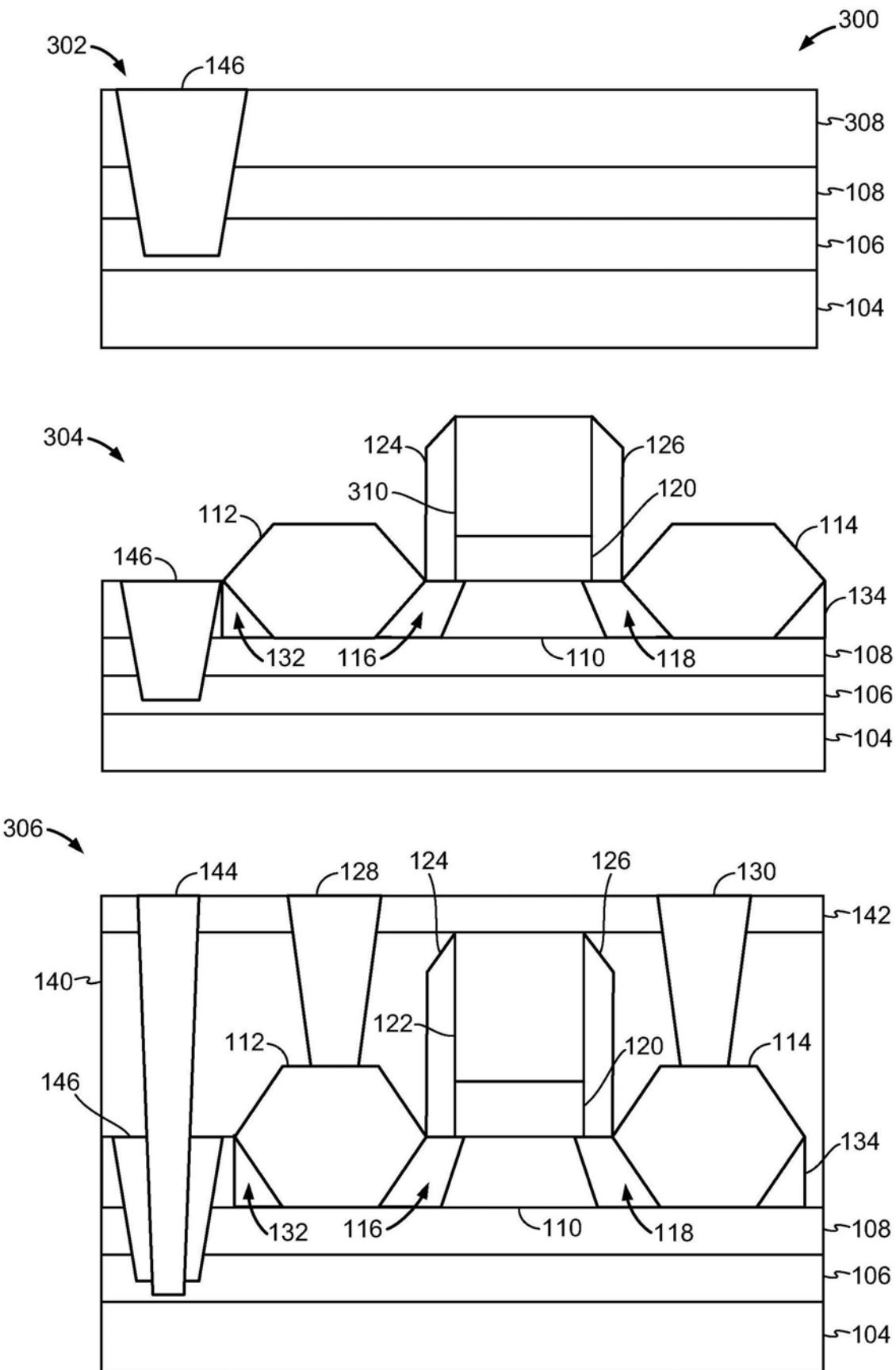

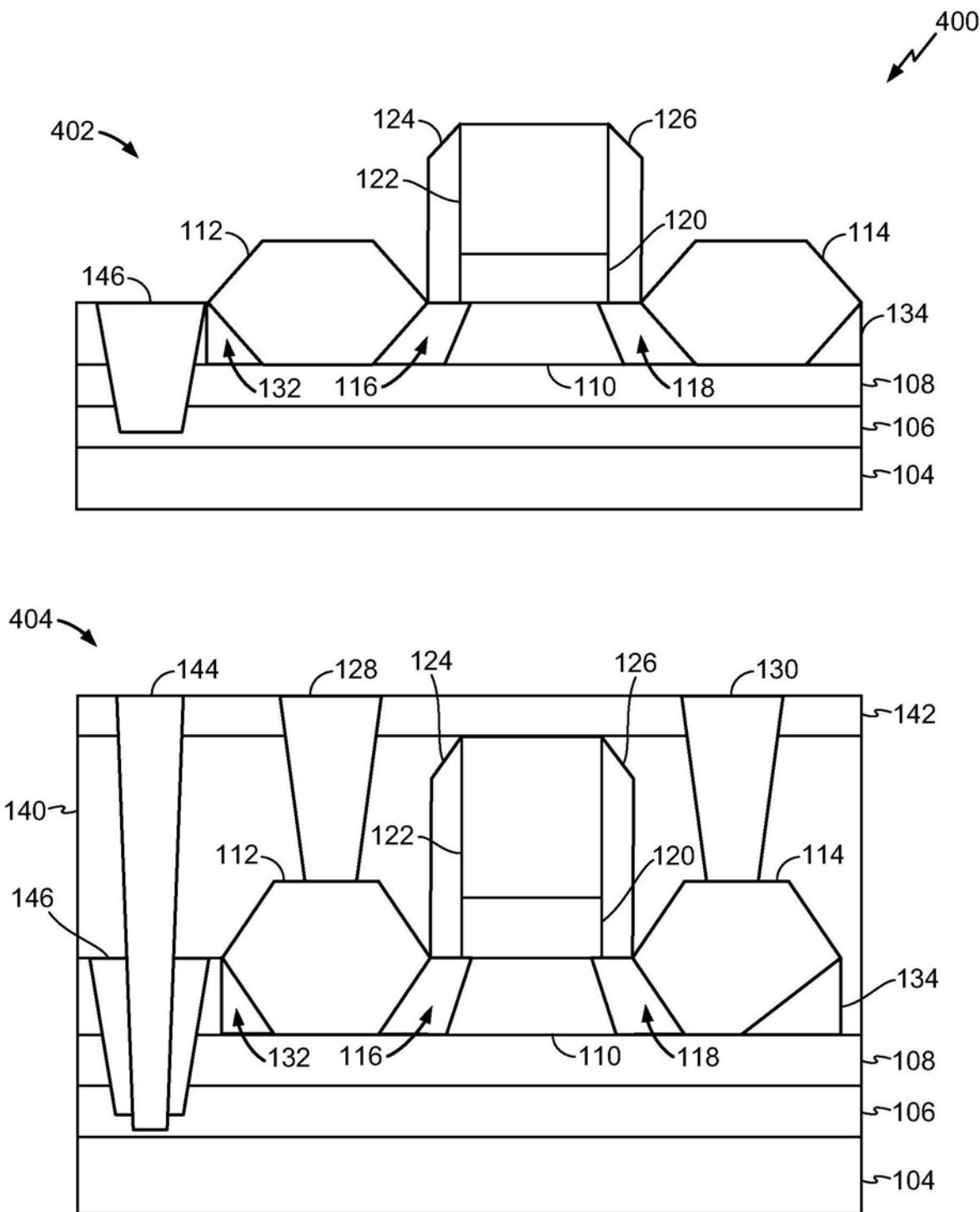

[0017] 图4是解说制造具有扩散势垒区的平面MOSFET的先栅极工艺的一部分的特定实施例的示图；

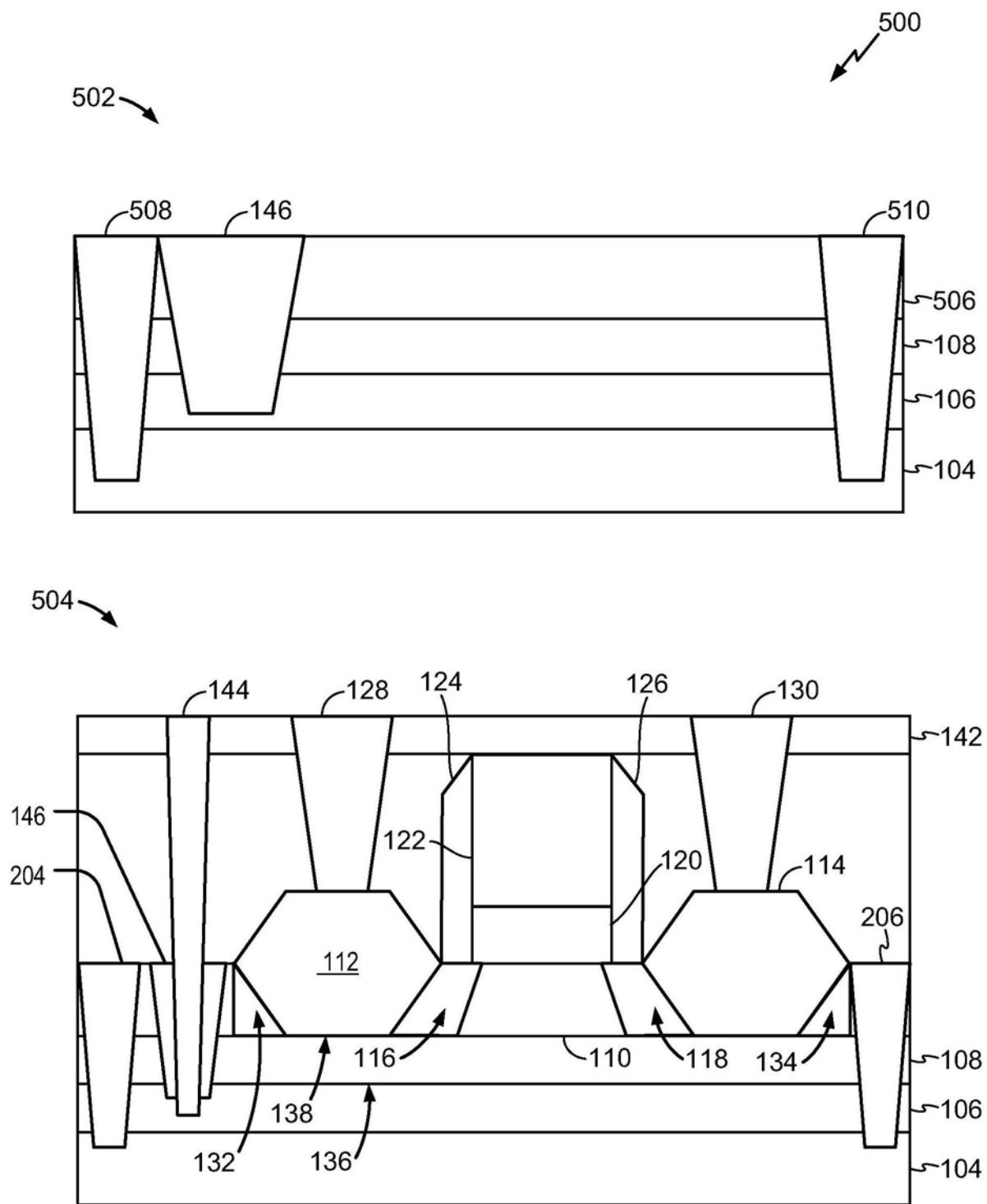

[0018] 图5是解说制造具有扩散势垒区的平面MOSFET的浅沟槽隔离阻挡件的工艺的一部分的特定实施例的示图；

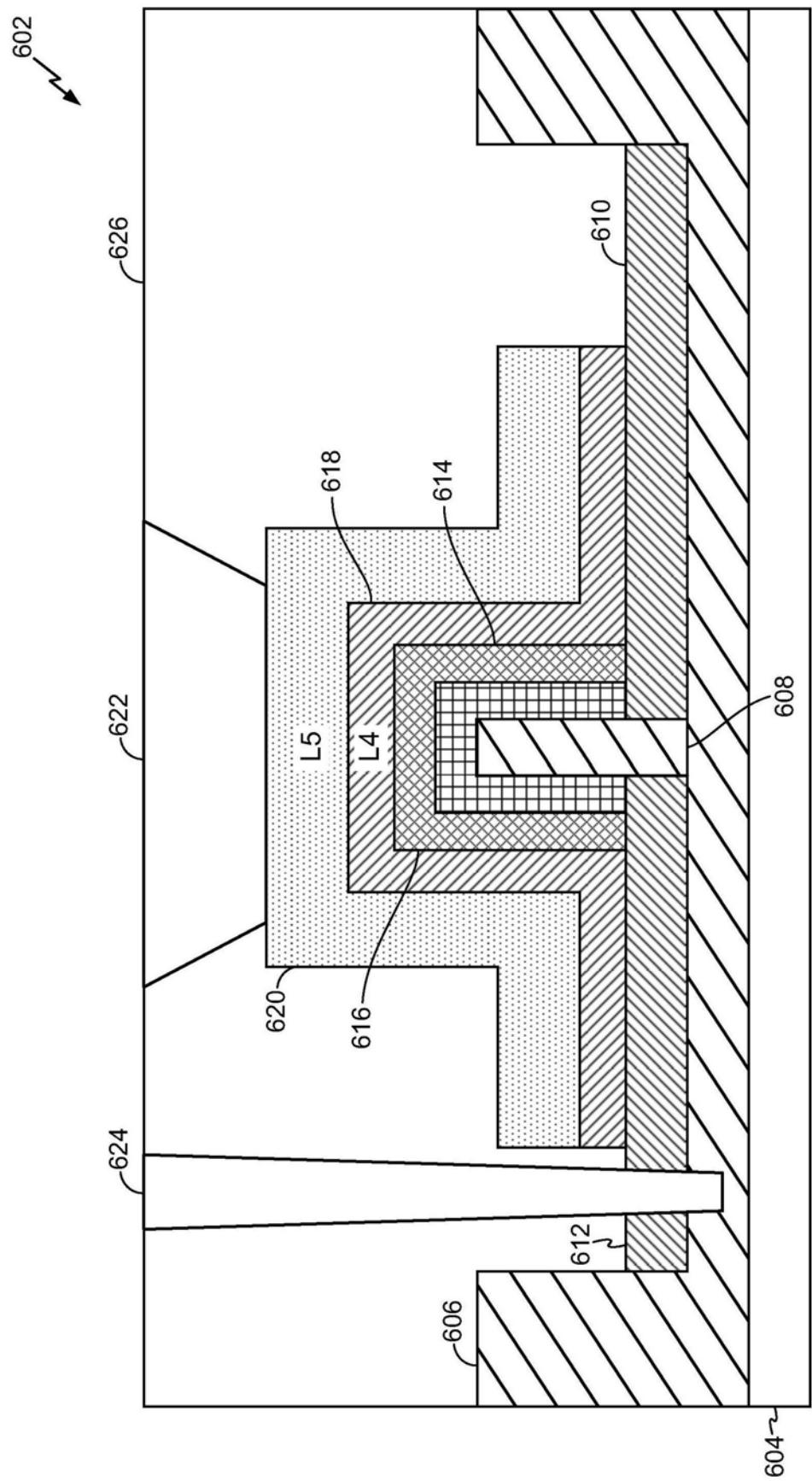

[0019] 图6是解说具有扩散势垒区的鳍式场效应晶体管(FinFET)的特定实施例的示图；

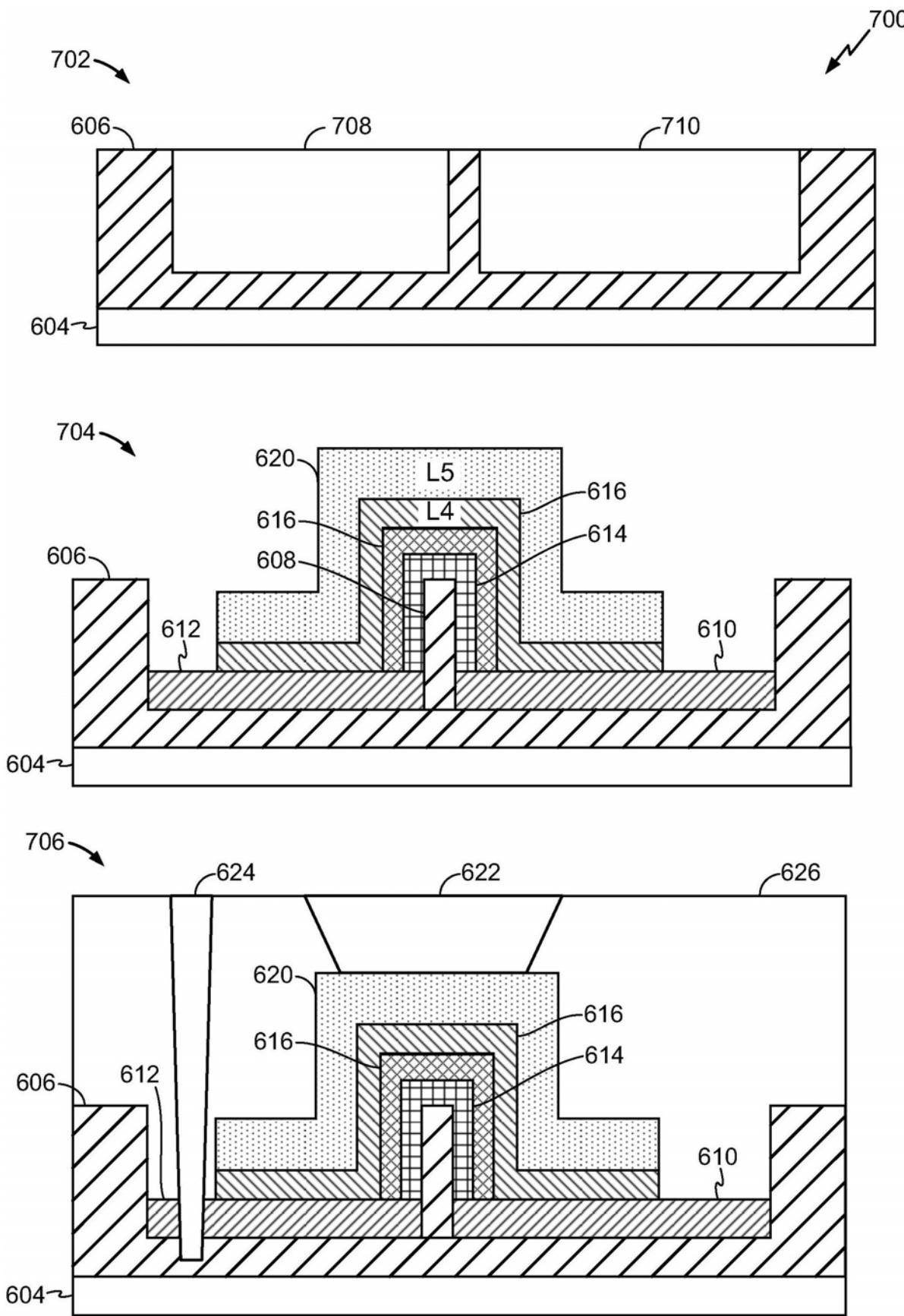

[0020] 图7是解说制造具有扩散势垒区的FinFET的工艺的一部分的特定实施例的示图；

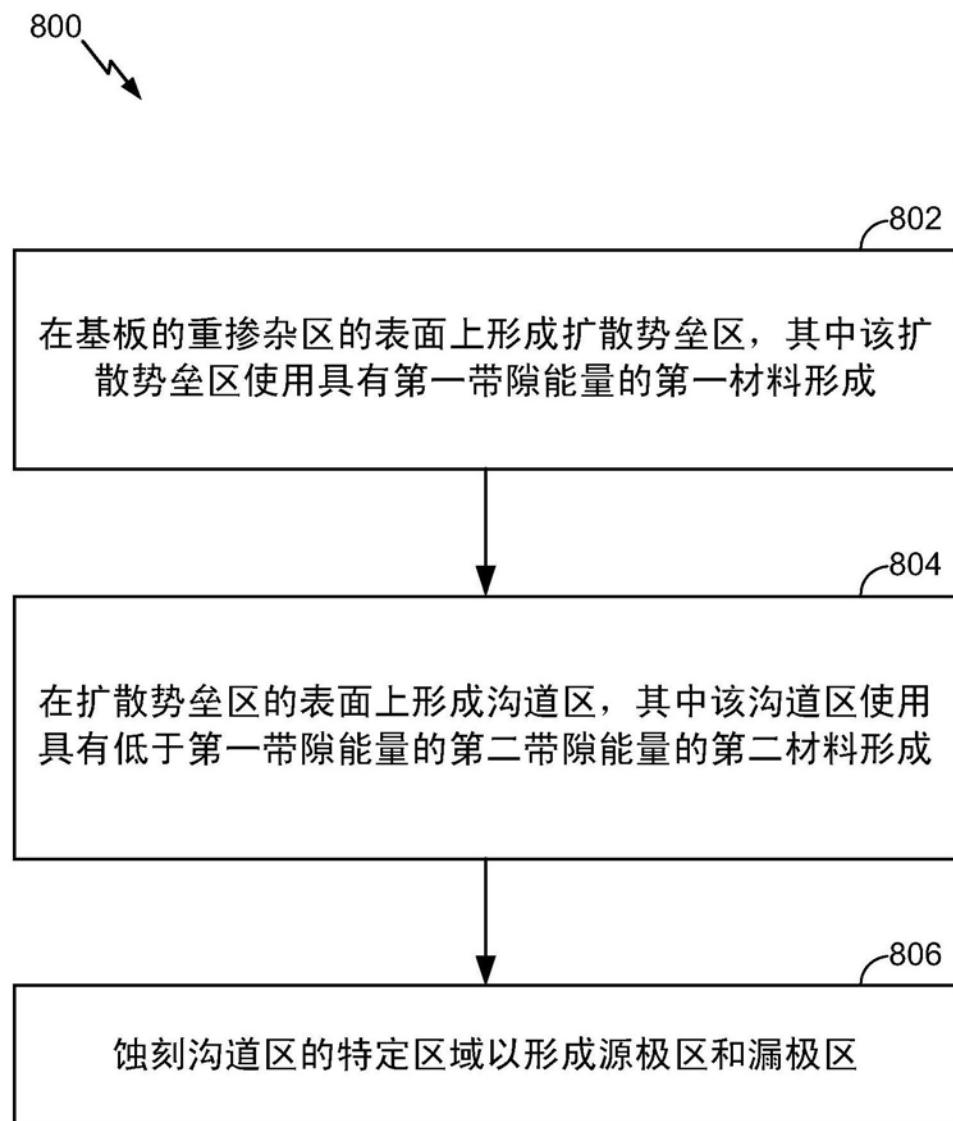

[0021] 图8是解说制造具有扩散势垒区的晶体管的方法的特定实施例的流程图；

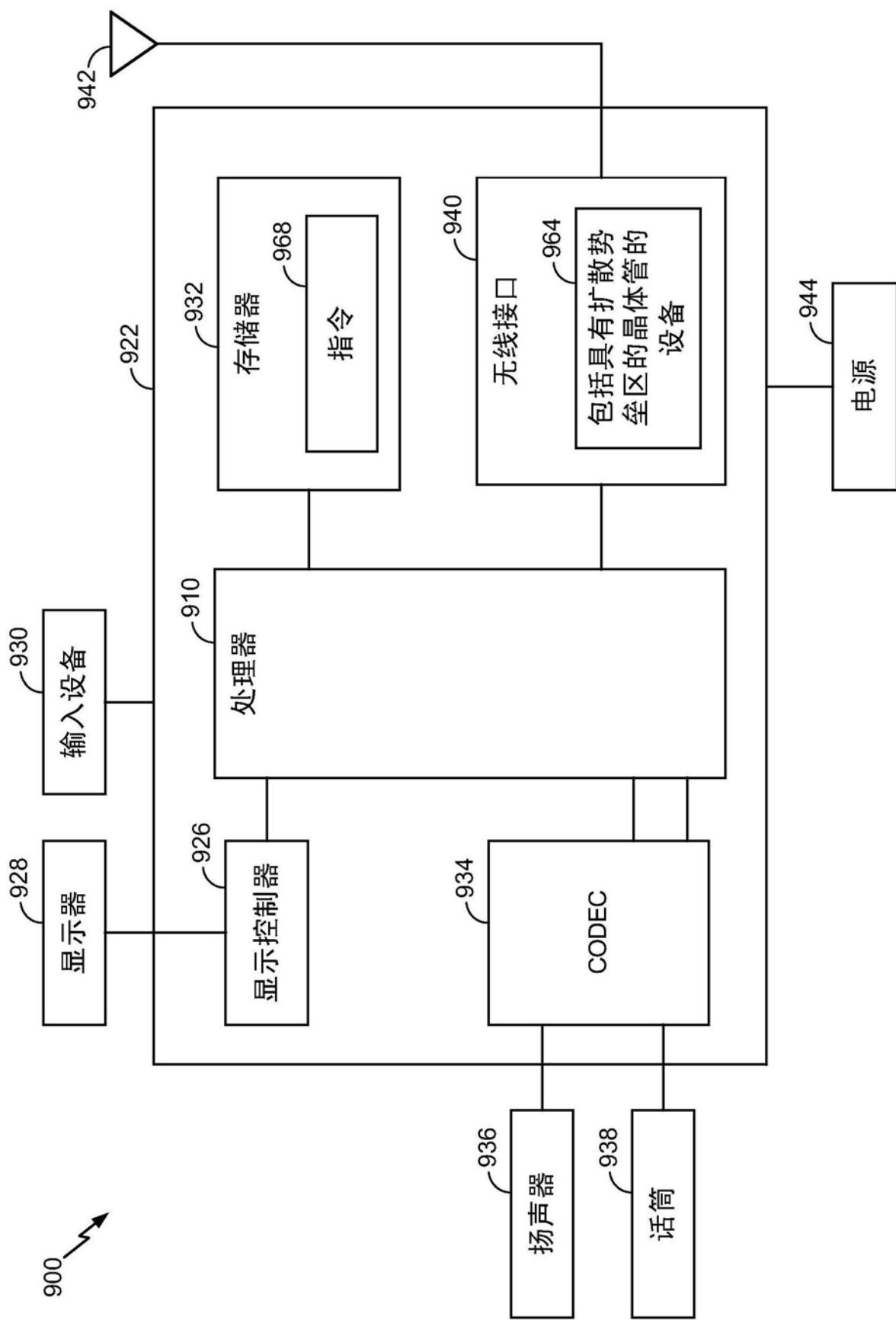

[0022] 图9是包括具有扩散势垒区的晶体管的通信设备的特定实施例的示图；以及

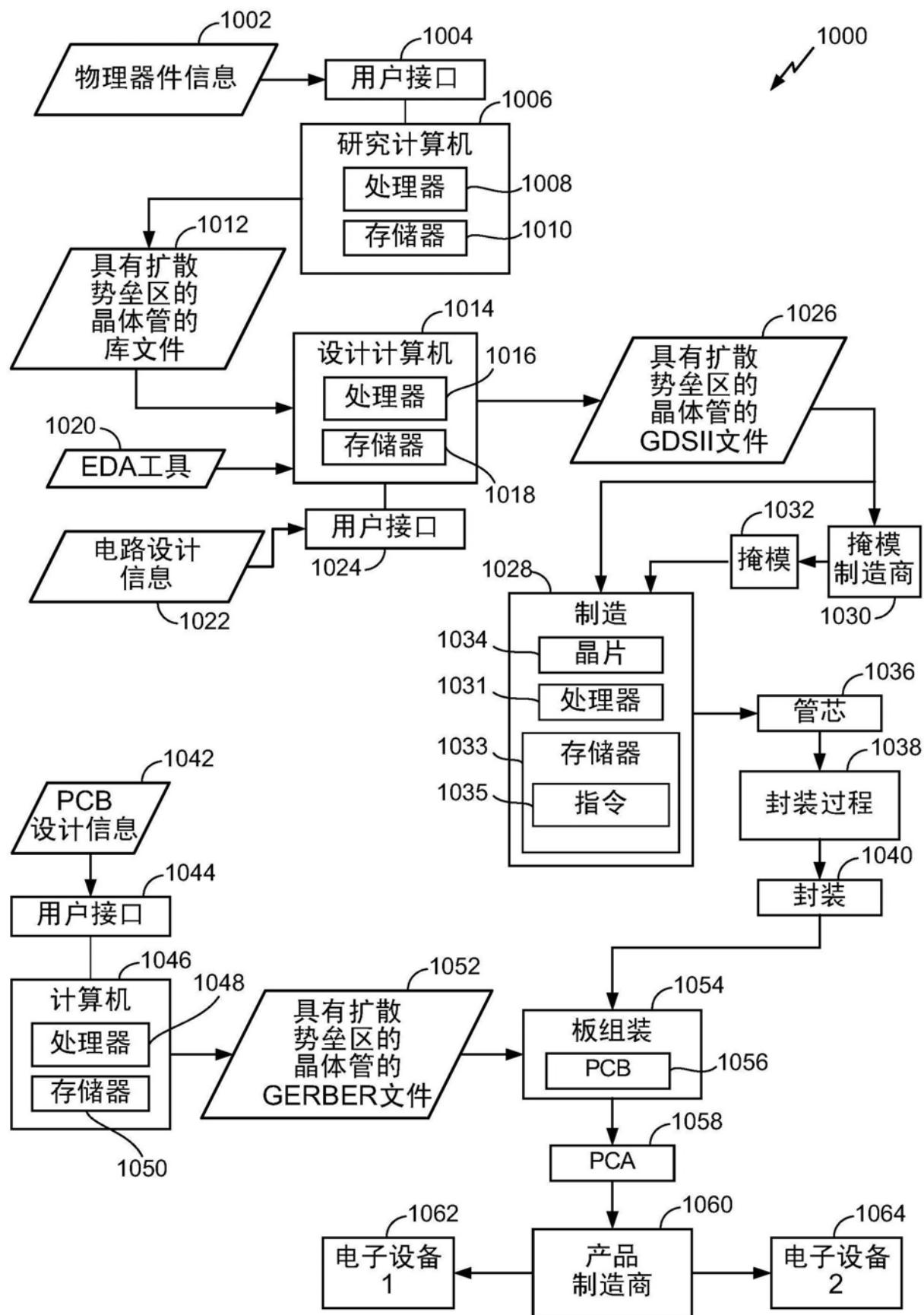

[0023] 图10是解说用以制造包括具有扩散势垒区的晶体管的电子设备的工艺的特定实施例的示图。

[0024] 详细描述

[0025] 图1解说了具有扩散势垒区108的平面金属氧化物半导体场效应晶体管(MOSFET)102的特定实施例。MOSFET 102可包括基板104、重掺杂区106和扩散势垒区108。重掺杂区106可以形成在基板104的区域中。重掺杂区106可以使用N型掺杂物或P型掺杂物来掺杂。重掺杂区106可具有第一掺杂浓度。基板104和重掺杂区106可以使用硅、III-V族复合物或II-VI族复合物来形成。作为一个示例，基板104和重掺杂区106可以使用砷化镓(GaAs)来形成。作为另一示例，基板104和重掺杂区106可以使用砷化铟镓(InGaAs)来形成。

[0026] 层间介电(ILD)层140可以在扩散势垒区108的表面上形成。MOSFET 102的多个组件可以位于ILD层140内。例如，沟道区110可以形成在扩散势垒区108的表面上。沟道区110可以使用III-V族复合物或II-VI族复合物形成。例如，沟道区110可以使用GaAs来形成。作为另一示例，沟道区110可以使用InGaAs来形成。沟道区110可以具有基于用以形成沟道区110的材料的带隙能量。例如，当使用GaAs形成沟道区110时，沟道区110可以具有1.424电子伏特(eV)的带隙能量。沟道区110可以是非掺杂的，或者具有低于第一掺杂浓度的第二掺杂浓度。可以根据特定超锐逆掺杂分布来形成沟道区110和重掺杂区106(例如，沟道区110和重掺杂区106根据不同掺杂浓度来掺杂)。

[0027] 源极应变区112和漏极应变区114还可以位于ILD层140内。源极应变区112和漏极应变区114可以形成在经蚀刻工艺后的扩散势垒区108的表面上。MOSFET 102可以进一步包括第一轻掺杂漏极(LDD)区116和第二LDD区118。第一LDD区116可以毗邻于源极应变区112，

并且第二LDD区118可以毗邻于漏极应变区114。

[0028] 介电层120可以形成在沟道区110的表面上。介电层120可以覆盖第一LDD区116的区域、第二LDD区118的区域、以及沟道区110的表面。金属栅极122可以形成在介电层120的表面上。金属栅极122可以毗邻于第一分隔件124且毗邻于第二分隔件126。第一有源或鳍式阻挡件132可以毗邻于源极区112。第二有源或鳍式阻挡件134可以毗邻于漏极区114。电容性膜层142可以形成在ILD层140的表面上，从而电容性膜层142毗邻于金属栅极122。第一触点128可以形成在源极应变区112的表面上。第一触点128可以延伸自源极应变区112并且通过电容性膜层142。第二触点130可以形成在漏极应变区114的表面上。第二触点130可以延伸自漏极应变区114并且通过电容性膜层142。

[0029] 扩散势垒区108可以形成在重掺杂区106的表面上。扩散势垒区108可以使用III-V族复合物形成。作为一个示例，扩散势垒区108可以使用AlAs形成。作为另一示例，扩散势垒区108可以使用InAlAs形成。其他示例性III-V族复合物可包括磷化铟(InP)、锑化铝(A1Sb)、锑化镓铝(A1GaSb)、碲化镉铝(CdAlTe)、碲化锌镉(ZnCdTe)等。作为另一示例，扩散势垒区108可以使用II-VI族复合物形成。扩散势垒区108可以具有基于用以形成扩散势垒区108的材料的带隙能量。例如，在使用AlAs形成扩散势垒区108时。第一带隙能量可以是2.16eV。

[0030] 扩散势垒区108可以在较低界面136和/或在较高界面138处陷住来自重掺杂区106的掺杂物。较低界面136可以是扩散势垒区108毗邻于重掺杂区106的表面。较高界面138可以是扩散势垒区108毗邻于MOSFET 102的沟道区110的另一表面。当使用硅形成重掺杂区106时(例如，当基板104是硅基板时)，扩散势垒区108可以在较高界面138处陷住来自重掺杂区106的掺杂物。当使用GaAs或InGaAs形成重掺杂区106时，扩散势垒区108可以在较低界面136处陷住掺杂物。由此，与基于超锐逆掺杂分布制造但没有扩散势垒区的MOSFET相比，从重掺杂区106扩散到沟道区110中的掺杂物量可以被降低。

[0031] MOSFET 102还可包括耦合到重掺杂区106的背栅触点144。背栅触点144可以毗邻于第一浅沟槽隔离(STI)146。第一STI 146可以将背栅触点144与扩散势垒区108隔离。背栅触点144可以延伸自重掺杂区106且通过ILD层140和电容性膜层142。当电压经由背栅触点144施加到重掺杂区106时，重掺杂区106可以用作MOSFET 102的背栅极(例如，第二栅极)。MOSFET 102的阈值电压可以通过独立地偏置金属栅极122和重掺杂区106来控制。因为背栅极提供了对阈值电压的附加程度的控制，所以与经由单个栅极控制阈值电压相比，使用重掺杂区106作为背栅极可以实现对阈值电压的增强控制。由此，MOSFET 102可以提供增强阈值电压控制和降低的掺杂物扩散。

[0032] 在操作期间，阈值电压可以被施加到金属栅极122(例如，经由栅极触点)以导通MOSFET 102。电流从源极应变区122流到漏极应变区114。当MOSFET 102将被截止时，阈值电压关断，并且电流不从源极应变区112流到漏极应变区114。

[0033] 图2是解说具有扩散势垒区的平面MOSFET 202的另一特定实施例的示图。MOSFET 202可以基本上类似于图1的MOSFET 102。MOSFET 202可包括MOSFET 102的所有组件。进一步，MOSFET 202可包括第二STI 204和第三STI 206。第二STI 204可毗邻于第一STI 146。第二STI 204可以延伸自基板104并且通过重掺杂区106和扩散势垒区108。第三STI 206可以毗邻于第二有源或鳍式阻挡件134。第三STI 206可以延伸自基板104并且通过重掺杂区106

和扩散势垒区108。除了使用第一有源或鳍式阻挡件132和第二有源或鳍式阻挡件134来降低MOSFET 202的寄生泄漏之外,第二STI 204和第三STI 206可进一步降低MOSFET 202的寄生泄漏。

[0034] 图3是解说用以制造具有扩散势垒区的平面MOSFET(例如,图1的MOSFET 102)的后栅极工艺300(例如,MOSFET的栅极是在形成MOSFET的源极区和漏极区之后制造的)的一部分的特定实施例的示图。在第一处理阶段302,重掺杂区106可以经由掺杂工艺形成在基板104的区域中。N型掺杂物或P型掺杂物可以被注入到基板106的区域以形成重掺杂区106。N型掺杂物或P型掺杂物可以根据第一掺杂浓度来注入。例如,第一掺杂浓度可以约为 $1\times10^{20}1/\text{cm}^2$ 。

[0035] 扩散势垒区108可以经由外延生长形成在重掺杂区106的表面上。例如,III-V族膜(例如,A1As膜、InAlAs膜等)可以通过使用低温(例如,小于300摄氏度)外延生长工艺生长在重掺杂区106的表面上以形成扩散势垒区108。使用低温外延生长工艺与常规硅晶体管(其中高温(例如,大于500摄氏度)可以被用来在重掺杂区106的表面上形成沟道区)相比可降低来自重掺杂区106的掺杂物扩散。温度越高,越大量的掺杂物可从重掺杂区106扩散。膜层308可以经由外延生长(例如,低温外延生长工艺)形成在扩散势垒区108的表面上。膜层308可以由III-V族复合物(例如,GaAs、InGaAs等)或II-VI族复合物制成。膜层308可以是非掺杂的,或者可以具有低于第一掺杂浓度的第二掺杂浓度。此外,膜层308可以具有比扩散势垒区108低的带隙能量(例如,价电带到传导带之间的能隙),从而扩散势垒区108可以用作重掺杂区106的掺杂物扩散势垒区。在III-V族和II-VI族材料系统中,扩散势垒区108的较高能带隙可以帮助形成有效背栅。

[0036] 第一STI 146可以经由蚀刻工艺形成。例如,膜层308、扩散势垒区108和重掺杂区106的区域可以被蚀刻以形成沟槽。第一STI 146可以经由氧化膜沉积工艺和CMP工艺形成在沟槽中。

[0037] 在第二处理阶段304,(与二氧化硅相比)具有高介电常数(“高k”)的介电膜可以沉积在膜层308的表面上,并且被图案化以形成介电层120。多晶硅膜可以沉积在介电层120的表面上,并且被图案化以形成多晶硅栅极310。LDD注入物可以经由晕状注入工艺来注入到膜层308的区域。分隔件膜(例如,SiN膜)可以毗邻于多晶硅栅极310和介电层120来沉积。分隔件膜可以被蚀刻以形成第一分隔件124和第二分隔件126。

[0038] 同样,在第二处理阶段304,离子注入物可以被注入到膜层308的LDD注入区的区域。在将离子注入区退火之后,离子注入区可以被蚀刻,并且可以经由外延生长工艺在经蚀刻的区域上形成应力源以形成源极应变区112和漏极应变区114。也可以在源极区112和漏极区114上形成自对准多晶硅化物(未示出)。离子注入区之间的膜层308的区域可以成为沟道区110。源极应变区112和沟道区308之间的离子注入区的第一区域可以成为第一LDD区116。漏极应变区114和沟道区308之间的离子注入区的第二区可以成为第二LDD区118。膜层308的第一边缘区可以由源极应变区112定义以形成第一有源边缘132。膜层308的第二边缘区可以由漏极应变区114定义以形成有源边缘134。

[0039] 在第三处理阶段306,ILD膜可以沉积在扩散势垒区108、有源边缘132、134、源极应变区112、漏极应变区114、分隔件124、126和多晶硅栅极310的表面上以形成ILD层140。化学机械平坦化(CMP)工艺可以被应用到ILD层140以暴露多晶硅栅极310的表面。多晶硅栅极

310可以经由蚀刻工艺来移除以形成分隔件124、126之间的沟槽。金属膜可以沉积到沟槽中以形成金属栅极122。CMP工艺可以被应用于金属栅极122的表面,从而该表面可以与ILD层140的表面齐平。电容性膜可以沉积在ILD层140的表面和金属栅极122的表面上以形成电容性膜层142。背栅触点114可以经由蚀刻工艺和金属膜沉积工艺以及CMP形成。由此,图1的MOSFET 102可以使用后栅极工艺300形成。

[0040] 图4解说了用以制造具有扩散势垒区的平面MOSFET(例如,图1的MOSFET 102)的先栅极工艺400(例如,MOSFET的栅极是在形成MOSFET的源极区和漏极区之前制造的)的一部分的特定实施例。在第一处理阶段402,介电膜(例如,高k介电膜)可以沉积在膜层(例如,图3的膜层308)的表面上以形成介电层120。金属膜可以沉积在介电层120的表面上,并且被图案化以形成金属栅极122。同样,第一STI 146还可以经由蚀刻工艺和氧化沉积以及CMP工艺形成。在第二处理阶段404,在形成金属栅极122之后,MOSFET 102的其他组件(例如,源极应变区112、漏极应变区114、沟道区110、分隔件124、126、有源边缘132、134、LDD区116、118、触点128、130、ILD层140、背栅触点144和电容性膜层142)可以如参照图3所描述的那样形成。由此,图1的MOSFET 102可以使用先栅极工艺400形成。

[0041] 图5解说了用以制造具有扩散势垒区的平面MOSFET(例如,图2的MOSFET 202)的工艺500的一部分的特定实施例。在第一过程阶段502,膜层506可以沉积在扩散势垒区108的表面上。膜层506可以类似于图3的膜层308。基板104、重掺杂区106、扩散势垒区108、和膜层506的区域可以被蚀刻以形成第一沟槽508和第二沟槽510。氧化膜可以沉积到沟槽508和510中,并且CMP以形成STI 204、206。在第二处理阶段504,当使用后栅极制造工艺时,MOSFET 202的其他组件(例如,金属栅极112、源极应变区112、漏极应变区114、沟道区110、分隔件124、126、有源边缘132、134、LDD区116、118、触点128、130、背栅触点144和电容性膜层142)可以如参照图3所描述的那样形成。当使用先栅极制造工艺时,其他组件可以如参照图4描述的那样形成。由此,图2的MOSFET 202可以使用工艺500形成。

[0042] 图6解说了具有扩散势垒区的鳍式场效应晶体管(FinFET)602的特定实施例。FinFET 602可以起到与图1的MOSFET 102和/或图2的MOSFET 202类似的功能,因为FinFET 602可以具有扩散势垒区614以降低从重掺杂区606到沟道区616的掺杂物扩散。FinFET 602可包括基板604和重掺杂区606。FinFET 602还可包括毗邻于STI 610和612的鳍608。鳍608可以形成为重掺杂区606的一部分。FinFET 602可进一步包括毗邻于鳍608的扩散势垒区614和毗邻于扩散势垒区614的沟道区616。扩散势垒区614可以基本上类似于图1的扩散势垒区108。沟道区616可以基本上类似于图1的沟道区110。扩散势垒区614可以降低从鳍608到沟道区616的掺杂物扩散。

[0043] FinFET 602的介电层618可以毗邻于沟道区616。介电层618可以使用具有高介电常数(“高k”)的材料形成。FinFET 602的金属栅极620可以毗邻于介电层618。FinFET 602可以进一步包括与金属栅极620接触的金属栅极触点622。FinFET 602可进一步包括延伸自重掺杂区606的背栅触点624。当电压经由背栅触点624施加到重掺杂区606时,重掺杂区606可以用作FinFET 602的第二栅极(例如,背栅)。FinFET 602可进一步包括与金属栅极触点622接触的氧化层626、源极区(未示出)和漏极区(未示出)。

[0044] 图7解说了用以制造具有扩散势垒区的FinFET(例如,图6的FinFET 602)的工艺700的一部分的特定实施例。在第一处理阶段702,重掺杂区606可以经由掺杂工艺形成在基

板604的区域中。基板604和重掺杂区606可以使用硅、III-V族复合物或II-VI族复合物来形成。作为一个示例，基板604和重掺杂区606可以使用砷化镓(GaAs)来形成。作为另一示例，基板604和重掺杂区606可以使用砷化铟镓(InGaAs)来形成。N型掺杂物或P型掺杂物可以被注入到基板604的区域以形成重掺杂区606。N型掺杂物或P型掺杂物可以根据第一掺杂浓度来注入。重掺杂区606的区域可以被蚀刻以形成沟槽。氧化膜可以沉积到沟槽中以形成STI区708和710。STI区708和710以及重掺杂区606的表面可以经由化学机械平坦化(CMP)工艺而被平坦化。

[0045] 在第二处理阶段704，STI区708和710可以被蚀刻以形成STI 610和612以及鳍608。扩散势垒区614可以经由外延生长而形成在鳍608的表面上。扩散势垒区614可以使用和图1的扩散势垒区108相同的材料形成。沟道区616可以经由外延生长而形成在扩散势垒区614的表面上。沟道区616可以使用和图1的沟道区110相同的材料形成。在形成沟道区616之后，介电层618可以经由沉积形成在沟道区616的表面上。金属栅极620可以形成在介电层618的表面上。

[0046] 在第三处理阶段706，介电膜可以沉积在金属栅极620、介电层618、重掺杂区606和STI 610与612的表面上以形成氧化层626。介电层626的顶面可以经由CMP工艺来平坦化。介电层626的区域可以被蚀刻以形成第一沟槽。金属膜可以沉积到第一沟槽中以形成金属栅极触点622。氧化层626、STI 612和重掺杂区606的区域可以被蚀刻以形成第二沟槽。金属膜可以沉积到第二沟槽中以形成背栅触点624。源极区(未示出)和漏极区(未示出)还可以在第三处理阶段706形成。关于图6，源极区和漏极区可以垂直于图6所解说的器件的平面。源极区和漏极区可以形成在鳍602处。源极区和漏极区可以被蚀刻，并且可以从FinFET 602形成应力源。由此，图6的FinFET 602可以使用工艺700形成。

[0047] 图8是解说制造具有扩散势垒区的晶体管(例如，图1的MOSFET 102、图2的MOSFET 202或图6的FinFET 602)的方法800的特定实施例。在802，方法800包括在基板的重掺杂区的表面上形成扩散势垒区，其中扩散势垒区是使用具有第一带隙能量的第一材料形成的。例如，参见图3，扩散势垒区108可以经由外延生长形成在重掺杂区106的表面上。在804，方法800还包括在扩散势垒区的表面上形成沟道区，其中沟道区使用具有低于第一带隙能量的第二带隙能量的第二材料形成。例如，参见图3，离子注入区之间的膜层308的区域可以成为沟道区110。在806，方法800进一步包括蚀刻沟道区的特定区域以形成源极区和漏极区。例如，参见图3，在将离子注入区退火之后，离子注入区可以被蚀刻，并且可以经由外延生长工艺在经蚀刻的区域上形成应力源以形成源极应变区112和漏极应变区114。在特定实施例中，方法800进一步包括形成耦合到重掺杂区的背栅触点。例如，参见图3，背栅触点144可以经由蚀刻工艺形成。

[0048] 在另一特定实施例中，方法800进一步包括在沟道区的表面上形成介电层。例如，参见图3，ILD膜可以沉积在扩散势垒区108、有源边缘132、134、源极应变区112、漏极应变区114、分隔件124、126和多晶硅栅极310的表面上以形成ILD层140。方法800进一步包括在介电层的表面上形成金属栅极。例如，参见图4，介电膜(例如，高k介电膜)可以沉积在膜层(例如，图3的膜层308)的表面上以形成介电层120。金属膜可以沉积在介电层120的表面上，并且被图案化以形成金属栅极122。方法800进一步包括在基板的第一表面上形成第一浅沟槽隔离(STI)区，以及在基板的第二表面上形成第二STI区，其中该第一STI区和第二STI区经

由蚀刻工艺形成，并且其中第一STI区毗邻于源极区并且第二STI区毗邻于漏极区。例如，参见图5，基板104、重掺杂区106、扩散势垒区108、和膜层506的区域可以被蚀刻以形成第一沟槽508和第二沟槽510。氧化膜可以沉积到沟槽508和510中以形成STI 204、206。由此，方法800可以使得能够制造具有扩散势垒区的基于超锐逆分布来掺杂的晶体管。相比于没有扩散势垒区的晶体管，扩散势垒区可以降低从晶体管的重掺杂区到晶体管的沟道区的掺杂物扩散。

[0049] 图9是包括具有扩散势垒区(例如，图1的扩散势垒区108)的晶体管(例如，图1的MOSFET 102、图2的MOSFET 202、图6的FinFET 602)的通信设备900的特定实施例的示图。设备900包括耦合至存储器932的处理器910(例如，数字信号处理器(DSP)、中央处理单元(CPU)等)。存储器932包括指令968(例如，可执行指令)，诸如可由处理器910读取的计算机可读指令。指令968可包括可由计算机(诸如处理器910)执行的一个或多个指令。

[0050] 图9还示出了耦合至处理器910和显示器928的显示控制器926。编码器/解码器(CODEC)934也可耦合至处理器910。扬声器936和话筒938可耦合至CODEC 934。

[0051] 图9还指示无线接口940可被耦合至处理器910和天线942。无线接口940可包括无线控制器、无线收发机，诸如接收机电路、发射机电路或其组合。在特定实施例中，无线接口940包括设备964，设备964包括具有扩散势垒区的晶体管(例如，图1的MOSFET 102、图2的MOSFET 202和图6的FinFET 602)。在替换实施例中，设备964可以位于设备900的一个或多个组件中，而非无线接口940中。设备964可包括模拟电路、数字电路、混合信号电路、射频(RF)电路、时钟信号生成电路、存储器设备(例如，动态随机存取存储器(DRAM)设备)、另一类型的设备或其任何组合。

[0052] 在特定实施例中，将处理器910、显示控制器926、存储器932、CODEC 934、以及无线接口940包括在系统级封装或片上系统设备922中。在一特定实施例中，输入设备930和电源944被耦合至片上系统设备922。此外，在一特定实施例中，如图9中所解说的，显示器928、输入设备930、扬声器936、话筒938、无线天线942和电源944在片上系统设备922的外部。然而，显示器928、输入设备930、扬声器936、话筒938、天线942和电源944中的每一者可被耦合到片上系统设备922的组件，诸如接口或控制器。

[0053] 所公开的实施例中的一个或多个实施例可在一种系统或装置(诸如设备900)中实现，该系统或装置可包括通信设备、固定位置的数据单元、移动位置的数据单元、移动电话、蜂窝电话、卫星电话、计算机、平板设备、便携式计算机、或台式计算机。另外，设备900可包括机顶盒、娱乐单元、导航设备、个人数字助理(PDA)、监视器、计算机监视器、电视机、调谐器、无线电、卫星无线电、音乐播放器、数字音乐播放器、便携式音乐播放器、视频播放器、数字视频播放器、数字视频盘(DVD)播放器、便携式数字视频播放器、存储或检索数据或计算机指令的任何其他设备、或其组合。作为另一解说性、非限制性示例，该系统或装置可包括远程单元(诸如移动电话、手持式个人通信系统(PCS)单元)、便携式数据单元(诸如个人数据助理、启用全球定位系统(GPS)的设备、导航设备)、固定位置的数据单元(诸如仪表读数装备)、或者存储或检索数据或计算机指令的任何其他设备、或其任何组合。

[0054] 上文公开的设备和功能性可被设计和配置在存储在计算机可读介质上的计算机文件(例如，RTL、GDSII、GERBER等)中。一些或全部此类文件可被提供给制造处理人员以基于此类文件来制造设备。结果产生的产品包括半导体晶片，其随后被切割为半导体管芯并

被封装成一个或多个半导体芯片。这些芯片随后被用在以上描述的设备中。图10描绘了电子器件制造过程1000的特定解说性实施例。

[0055] 物理器件信息1002在制造过程1000处(诸如在研究计算机1006处)被接收。物理器件信息1002可包括表示半导体器件(诸如包括具有扩散势垒区的晶体管(例如,图1的MOSFET 102、图2的MOSFET 202、和图6的FinFET 602)的半导体器件)的至少一个物理属性的设计信息。例如,物理器件信息1002可包括经由耦合至研究计算机1006的用户接口1004输入的物理参数、材料特性、以及结构信息。研究计算机1006包括耦合至计算机可读介质(诸如存储器1010)的处理器1008,诸如一个或多个处理核。存储器1010可存储计算机可读指令,其可被执行以使处理器1008将物理器件信息1002转换成遵循文件格式并生成库文件1012。

[0056] 在一特定实施例中,库文件1012包括至少一个包括经转换的设计信息的数据文件。例如,库文件1012可包括半导体器件库(该半导体器件库包括包含具有扩散势垒区的晶体管(例如,图1的MOSFET 102、图2的MOSFET 202和图6的FinFET 602)的器件),并且可以被提供以用于与电子设计自动化(EDA)工具1020联用。

[0057] 库文件1012可在设计计算机1014处与EDA工具1020协同使用,设计计算机1014包括耦合至存储器1018的处理器1016,诸如一个或多个处理核。EDA工具1020可作为处理器可执行指令存储在存储器1018处,以使得设计计算机1014的用户能够设计包括具有扩散势垒区的晶体管(例如,图1的MOSFET 102、图2的MOSFET 202、图6的FinFET 602)的电路。例如,设计计算机1014的用户可经由耦合至设计计算机1014的用户接口1024来输入电路设计信息1022。电路设计信息1022可包括表示半导体器件(诸如包括具有扩散势垒区的晶体管(例如,图1的MOSFET 102、图2的MOSFET 202、和图6的FinFET 602)的半导体器件)的至少一个物理属性的设计信息。为了解说,电路设计属性可包括特定电路的标识以及与电路设计中其他元件的关系、定位信息、特征尺寸信息、互连信息、或表示半导体器件的物理性质的其他信息。

[0058] 设计计算机1014可被配置成转换设计信息(包括电路设计信息1022)以遵循某一文件格式。为了解说,该文件格式可包括以阶层式格式表示关于电路布局的平面几何形状、文本标记、及其他信息的数据库二进制文件格式,诸如图形数据系统(GDSII)文件格式(例如,GDSII格式)。设计计算机1014可以配置成生成包括经转换的设计信息的数据文件(诸如,包括描述具有扩散势垒区的晶体管(例如,图1的MOSFET 102、图2的MOSFET 202、图6的FinFET 602)的信息的GDSII文件1026)以及其他电路或信息。为了解说,该数据文件可包括对应于片上系统(SOC)的信息,该SOC包括具有扩散势垒区的晶体管(例如,图1的MOSFET 102、图2的MOSFET 202、图6的FinFET 602)且还可以包括该SOC内的附加电子电路和组件。

[0059] GDSII文件1026可以在制造过程1028被接收以根据GDSII文件1026中的经转换的信息来制造包括具有扩散势垒区的晶体管(例如,图1的MOSFET 102、图2的MOSFET 202和图6的FinFET 602)的晶片。例如,设备制造过程可包括将GDSII文件1026提供给掩模制造商1030以创建一个或多个掩模,诸如用于与光刻处理联用的掩模,其被解说为代表性掩模1032。掩模1032可在制造过程期间使用以生成一个或多个晶片1034,诸如绝缘体上覆硅(SOI)晶片、硅上覆硅(SOS)晶片或块体硅晶片。

[0060] 在特定实施例中,制造过程1028可由处理器1031和存储器1033来发起或控制。存

储器1033(例如,非瞬态计算机可读介质)可包括可由处理器1031执行的指令1035。例如,该计算机可执行指令可以被执行以使得处理器1031发起或控制具有扩散势垒区的晶体管(例如,图1的MOSFET 102、图2的MOSFET 202和图6的FinFET 602)的形成。为了解说,这些指令可由处理器1031执行以发起或控制形成电容器、其组件或者附连到其的组件(例如,(诸)金属层、(诸)绝缘体层、通孔等)的一个或多个工具或过程的操作。

[0061] 制造过程1028可由全自动化或部分自动化的制造系统来执行。例如,制造过程1028可以是自动化的,并且制造过程1028的步骤可以根据调度来执行。制造系统可包括制造装备(例如,处理工具)以执行一个或多个操作来形成器件,诸如具有扩散势垒区的晶体管(例如,图1的MOSFET 102、图2的MOSFET 202、图6的FinFET 602)。例如,制造装备可配置成形成第一金属层、第一绝缘体层、第二金属层、第二绝缘体层、连接到第二金属层的通孔、钝化层等。

[0062] 制造系统(例如,执行制造过程1028的自动化系统)可具有分布式架构(例如,分层结构)。例如,该制造系统可包括根据该分布式架构分布的一个或多个处理器(诸如处理器1031)、一个或多个存储器(诸如存储器1033)、和/或控制器。该分布式架构可包括控制或发起一个或多个低级系统的操作的高级处理器。例如,控制或执行制造过程1028的制造系统的高级部分可包括一个或多个处理器(诸如处理器1031),并且低级系统可各自包括一个或多个相应控制器或可受其控制。特定低级系统的特定控制器可从高级系统接收一个或多个指令(例如,命令)、可向下级模块或处理工具发布子命令、以及可向高级系统传达状态信息。一个或多个低级系统中的每个低级系统可与一件或多件相应制造装备(例如,处理工具)相关联。在一特定实施例中,该制造系统可包括分布的多个处理器。例如,该制造系统的低级系统组件的控制器可包括处理器,诸如处理器831。

[0063] 替换地,处理器1031可以是该制造系统的高级系统、子系统、或组件的一部分。在另一实施例中,处理器1031包括制造系统的各级和组件处的分布式处理。

[0064] 由此,处理器1031可包括或执行使得处理器1031发起或控制形成器件(诸如具有扩散势垒区的晶体管(例如,图1的MOSFET 102、图2的MOSFET 202和图6的FinFET 602))的处理器可执行指令。例如,(诸)金属层可以由一个或多个沉积工具或者一个或多个镀敷平台、镀敷机、或配置成形成器件中的金属板的任何其他镀敷装备来形成。作为另一示例,(诸)绝缘体层和(诸)钝化层可通过一个或多个沉积工具或者“自底向上”制造工具(诸如化学气相沉积工具或旋涂式制造工具)来形成。作为又一个实例,可以由一个或多个蚀刻器(诸如湿法蚀刻器、干法蚀刻器、或等离子体蚀刻器)或一个或多个溶解工具来在(诸)绝缘体层和(诸)钝化层中形成开口。

[0065] 存储在存储器1033中的可执行指令可以使得处理器1031能够通过执行如由图8的方法800描述的操作来发起和控制器件的形成,诸如具有扩散势垒区的晶体管(例如,图1的MOSFET 102、图2的MOSFET 202、图6的FinFET 602)。

[0066] 管芯1036可被提供给封装过程1038,其中管芯1036被纳入到代表性封装1040中。例如,封装1040可包括单个管芯1036或多个管芯,诸如系统级封装(SiP)安排。封装1040可被配置成遵循一个或多个标准或规范,诸如电子设备工程联合委员会(JEDEC)标准。

[0067] 关于封装1040的信息可诸如经由存储在计算机1046处的组件库被分发给各产品设计者。计算机1046可包括耦合至存储器1050的处理器1048,诸如一个或多个处理核。印刷

电路板 (PCB) 工具可作为处理器可执行指令被存储在存储器1050处以处理经由用户接口1044从计算机1046的用户接收的PCB设计信息1042。PCB设计信息1042可包括经封装半导体器件在电路板上的物理定位信息,该经封装半导体器件对应于包括具有扩散势垒区的晶体管(例如,图1的MOSFET 102、图2的MOSFET 202和图6的FinFET 602)的封装1040。

[0068] 计算机1046可被配置成转换PCB设计信息1042以生成数据文件,诸如具有包括经封装半导体器件在电路板上的物理定位信息、以及电连接(诸如迹线和通孔)的布局的数据的GERBER文件1052,其中经封装半导体器件对应于封装1040,封装1040包括具有扩散势垒区的晶体管(例如,图1的MOSFET 102、图2的MOSFET 202、图6的FinFET 602)。在其他实施例中,由经转换的PCB设计信息生成的数据文件可具有GERBER格式以外的其他格式。

[0069] GERBER文件1052可在板组装过程1054处被接收并且被用于创建根据GERBER文件1052内存储的设计信息来制造的PCB,诸如代表性PCB 1056。例如,GERBER文件1052可被上传到一个或多个机器以执行PCB生产过程的各个步骤。PCB 1056可填充有电子组件(包括封装1040)以形成代表性印刷电路组装件(PCA) 1058。

[0070] PCA 1058可在产品制造过程1060处被接收,并被集成到一个或多个电子设备中,诸如第一代表性电子设备1062和第二代表性电子设备1064。作为解说而非限定性示例,第一代表性电子设备1062、第二代表性电子设备1064、或者这两者可选自下组:机顶盒、音乐播放器、视频播放器、娱乐单元、导航设备、通信设备、个人数字助理(PDA)、固定位置的数据单元、以及计算机,其中集成了具有扩散势垒区的晶体管(例如,图1的MOSFET 102、图2的MOSFET 202、图6的FinFET 602)。作为另一解说性而非限定性示例,电子设备1062和1064中的一者或者可以是远程单元(诸如移动电话)、手持式个人通信系统(PCS)单元、便携式数据单元(诸如个人数据助理)、启用全球定位系统(GPS)的设备、导航设备、位置固定的数据单元(诸如仪表读数装备)、或者存储或检索数据或计算机指令的任何其他设备、或其任何组合。尽管图10解说了根据本公开的教导的远程单元,但本公开并不限于所解说的这些示例性单元。本公开的实施例可合适地用在包括具有存储器和片上电路系统的有源集成电路系统的任何设备中。

[0071] 包括具有扩散势垒区的晶体管(例如,图1的MOSFET 102、图2的MOSFET 202、图6的FinFET 602)的器件可被制造、处理、并纳入到电子设备中,如解说性过程1000中所描述的。关于图1-9所公开的实施例的一个或多个方面可被包括在各个处理阶段,诸如被包括在库文件1012、GDSII文件1026、以及GERBER文件1052内,以及被存储在研究计算机1006的存储器1010、设计计算机1014的存储器1018、与制造过程1028相关联的计算机的存储器1033、计算机1046的存储器1050、在各个阶段(诸如在板组装过程1054处)使用的一个或多个其他计算机或处理器(未示出)的存储器处,并且还被纳入到一个或多个其他物理实施例中,诸如掩模1032、管芯1036、封装1040、PCA 1058、其他产品(诸如原型电路或设备(未示出))、或其任何组合。尽管描绘了从物理器件设计到最终产品的各个代表性生产阶段,然而在其他实施例中可使用较少的阶段或可包括附加阶段。类似地,过程1000可由单个实体或由执行过程1000的各个阶段的一个或多个实体来执行。

[0072] 结合所描述的实施例,一种装备可包括用于阻止掺杂物扩散的装置,其中该用于阻止掺杂物扩散的装置形成在基板的重掺杂区的表面上,并且其中该用于阻止掺杂物扩散的装置使用具有第一带隙能量的第一材料形成。例如,该用于阻止掺杂物扩散的装置可包

括图1的扩散势垒区108、图6的扩散势垒区614、配置成阻止掺杂物扩散的一个或多个其他器件，或者其任何组合。

[0073] 该装备还可以包括用于提供导电沟道的装置，其中该用于提供导电沟道的装置形成在用于阻止掺杂物扩散的装置的表面上，并且其中该用于提供导电沟道的装置使用具有比第一带隙能量低的第二带隙能量的第二材料形成。例如，用于提供导电沟道的装置可包括图1的沟道区110、图6的沟道区616、配置成提供导电沟道的一个或多个其他器件，或者其组合。

[0074] 该装备可进一步包括用于提供背栅触点的装置，其中用于提供背栅触点的装置耦合到基板的第一区域。例如，该用于提供背栅触点的装置可包括图1的背栅触点144、图6的背栅触点624、配置成提供背栅触点的一个或多个其他器件，或者其组合。

[0075] 尽管图1-10中的一者或者可能解说了根据本公开的教导的系统、装置、和/或方法，但本公开不限于这些所解说了的系统、装置、和/或方法。本公开的各实施例可在包括集成电路系统的任何设备中被合适地采用。本公开的各实施例还可在自立器件(例如，自立晶体管)中采用。

[0076] 技术人员将进一步领会，结合本文所公开的实施例来描述的各种解说性逻辑框、配置、模块、电路、和算法步骤可实现为电子硬件、由处理器执行的计算机软件、或这两者的组合。各种解说性组件、框、配置、模块、电路、和步骤已经在上文以其功能性的形式作了一般化描述。此类功能性是被实现为硬件还是处理器可执行指令取决于具体应用和加诸于整体系统的设计约束。技术人员可针对每种特定应用以不同方式来实现所描述的功能性，但此类实现决策不应被解读为致使脱离本发明的范围。

[0077] 结合本文所公开的实施例描述的方法或算法的各个步骤可直接用硬件、由处理器执行的软件模块或这两者的组合来实现。软件模块可驻留在随机存取存储器(RAM)、闪存、只读存储器(ROM)、可编程只读存储器(PROM)、可擦式可编程只读存储器(EPROM)、电可擦式可编程只读存储器(EEPROM)、寄存器、硬盘、可移动盘、压缩盘只读存储器(CD-ROM)、或本领域中所知的任何其他形式的非瞬态存储介质中。示例性的存储介质耦合至处理器以使该处理器能从/向该存储介质读写信息。在替换方案中，存储介质可以被整合到处理器。处理器和存储介质可驻留在专用集成电路(ASIC)中。ASIC可驻留在计算设备或用户终端中。在替换方案中，处理器和存储介质可作为分立组件驻留在计算设备或用户终端中。

[0078] 提供前面对所公开的实施例的描述是为了使本领域技术人员皆能制作或使用所公开的实施例。对这些实施例的各种修改对于本领域技术人员而言将是显而易见的，并且本文中定义的原理可被应用于其他实施例而不会脱离本公开的范围。因此，本公开并非旨在被限定于本文中示出的实施例，而是应被授予与如由所附权利要求定义的原理和新颖性特征一致的最广的可能范围。

图1

图2

图3

图4

图5

图6

图7

图8

图9

图10