(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2004-236311

(P2004-236311A)

(43) 公開日 平成16年8月19日(2004.8.19)

(51) Int.CI.<sup>7</sup>

H03K 19/0175

H01L 21/822

H01L 27/04

H04L 25/02

F 1

H03K 19/00

H04L 25/02

H01L 27/04

I O 1 K

F

V

テーマコード(参考)

5 F 0 3 8

5 J 0 5 6

5 K 0 2 9

審査請求 未請求 請求項の数 10 O L (全 12 頁)

(21) 出願番号 特願2004-12760 (P2004-12760)

(22) 出願日 平成16年1月21日 (2004.1.21)

(31) 優先権主張番号 10/354400

(32) 優先日 平成15年1月30日 (2003.1.30)

(33) 優先権主張国 米国(US)

(71) 出願人 399117121

アジレント・テクノロジーズ・インク

A G I L E N T T E C H N O L O G I E

S, I N C.

アメリカ合衆国カリフォルニア州パロアル

ト ページ・ミル・ロード 395

395 Page Mill Road

Palo Alto, California

U. S. A.

(74) 代理人 100099623

弁理士 奥山 尚一

(74) 代理人 100096769

弁理士 有原 幸一

(74) 代理人 100107319

弁理士 松島 鉄男

最終頁に続く

(54) 【発明の名称】集積回路デバイス間で伝送される出力信号の電圧ピーピングを制御するマルチデバイスシステム及び方法

## (57) 【要約】

【課題】I C デバイス間で伝送される出力信号の電圧ピ

ーキングを制御するためのマルチデバイスシステム及び

方法を提供する。

【解決手段】集積回路(I C)デバイス102の出力回路106と集積回路デバイス104の入力回路108との間で伝送される出力信号の電圧ピーピングを制御するマルチデバイスシステム及び方法は、I Cデバイスの製造後に調整することのできる様々な電気素子を利用して入力回路および出力回路のインピーダンスを変える。これらの調整可能電気素子には入力回路内の1つ以上のパストランジスタ126が含まれ、このトランジスタのオン抵抗はパストランジスタに供給される制御信号を調整することで変化させることができる。調整可能電気素子にはまた、下記のうちの1つ以上のものが含まれ得る。すなわち、調整可能電流源116、調整可能抵抗器114、130、132、調整可能抵抗器として動作する抵抗値調整可能トランジスタ132である。

【選択図】図1

**【特許請求の範囲】****【請求項 1】**

出力回路から入力回路へ伝送される出力信号の電圧ピーキングを制御する方法であって、

前記入力回路を配設するステップであって、該入力回路は、入力ノードと低電圧端子との間に直列接続されたパストランジスタを有し、前記入力ノードは、前記出力回路から前記出力信号を受信するように接続されている、ステップと、

前記入力回路の前記パストランジスタに印加される制御信号を調整して該パストランジスタのオン抵抗を変えるステップであって、前記パストランジスタの前記オン抵抗は、前記電圧ピーキングが、前記パストランジスタの前記オン抵抗の変化により少なくとも部分的に制御され得るように、前記出力信号の前記電圧ピーキングと所定の関係を有している、ステップと、

を含む方法。

**【請求項 2】**

前記入力回路を配設するステップが前記入力ノードに直列接続された調整可能抵抗器を更に有する前記入力回路を配設するステップを含み、前記入力回路の前記調整可能抵抗器の前記抵抗値を変化させるステップを更に含む、請求項 1 に記載の方法。

**【請求項 3】**

前記入力回路を配設するステップが前記入力ノードに直列接続された抵抗値調整可能トランジスタを更に有する前記入力回路を配設するステップを含み、前記入力回路の前記抵抗値調整可能トランジスタに印加される制御信号を調整して前記抵抗値調整可能トランジスタのオン抵抗を変えるステップを更に含む、請求項 1 又は 2 に記載の方法。

**【請求項 4】**

高電圧端子と低電圧端子との間に直列接続された駆動トランジスタを有する前記出力回路を配設するステップであって、該出力回路は、前記駆動トランジスタと出力ノードとの間に直列接続された調整可能抵抗器をも有し、前記出力ノードは、前記入力回路の前記入力ノードに電気的に接続されて、前記出力信号を前記入力回路へ伝送している、ステップと、

前記出力回路の前記調整可能抵抗器の抵抗値を変えるステップと、

を更に含む、請求項 1 乃至 3 のいずれか 1 項に記載の方法。

**【請求項 5】**

前記出力回路を配設するステップであって、該出力回路は、高電圧端子と低電圧端子との間に直列接続された駆動トランジスタ及び調整可能電流源を有し、前記出力回路は、前記駆動トランジスタに接続された出力ノードをも有し、前記出力ノードは、前記入力回路の前記入力ノードに電気的に接続されて前記出力信号を前記入力回路へ伝送している、ステップと、

前記出力回路の調整可能電流源へ供給される制御信号電圧を調整して、前記調整可能電流源によって引き込まれる電流を変えるステップと、

を更に含む、請求項 1 乃至 4 のいずれか 1 項に記載の方法。

**【請求項 6】**

出力信号を伝送するよう構成された出力回路を有する第 1 の集積回路デバイスと、

前記出力回路に電気的に接続された入力回路を有する第 2 の集積回路デバイスであって、前記入力回路が、

前記出力回路に接続されて前記出力信号を受信する入力ノードと、

前記入力ノードに接続されたパストランジスタであって、制御信号を受信して前記パストランジスタを選択的に作動させる制御電極を有する前記パストランジスタと、

前記パストランジスタの前記制御電極に直列接続された調整可能信号源であって、前記制御信号を調整して前記パストランジスタのオン抵抗を変え、それにより、前記出力信号の電圧ピーキングを制御する前記調整可能信号源と、

を有する前記第 2 の集積回路デバイスと、

10

20

30

40

50

を備えているマルチデバイスシステム。

**【請求項 7】**

前記出力回路が、駆動トランジスタと調整可能電流源と調整可能信号源とを有し、前記駆動トランジスタおよび前記調整可能電流源は、高電圧端子と低電圧端子との間に直列接続され、前記駆動トランジスタは、出力ノードにも接続されて前記出力信号を前記入力回路へ伝送し、前記調整可能信号源は、前記調整可能電流源に供給される第2の信号を調整して該調整可能電流源によって引き込まれる電流を調整するように構成されている、請求項6に記載のマルチデバイスシステム。

**【請求項 8】**

前記出力回路が、前記駆動トランジスタと前記出力ノードとの間に直列接続された調整可能抵抗器を更に備えている、請求項7に記載のマルチデバイスシステム。 10

**【請求項 9】**

前記入力回路が、前記入力ノードに直列接続された調整可能抵抗器を更に備えている、請求項6乃至8のいずれか1項に記載のマルチデバイスシステム。

**【請求項 10】**

前記入力回路が、前記入力ノードに直列接続された抵抗値調整可能トランジスタを更に備え、該抵抗値調整可能トランジスタは、第2の制御信号を前記抵抗値調整可能トランジスタへ供給する第2の調整可能信号源にも接続され、該第2の調整可能信号源は、前記第2の制御信号が、前記抵抗値調整可能トランジスタのオン抵抗を変えるように調整され得るよう構成されている、請求項6乃至9のいずれか1項に記載のマルチデバイスシステム。 20

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

本発明は一般に集積回路に関し、より詳しくは集積回路デバイスのインターフェースに関する。 25

**【背景技術】**

**【0002】**

システムの集積回路デバイス( I C )は、一般に入力回路と出力回路を用いてインターフェースがとられる。一つの I C デバイスの出力回路は別の I C デバイスの入力回路を駆動するのに用いられ、通常それは静電容量により左右される。 I C デバイス間の接続は、ボンディングワイヤ及び / 又は通常は誘導的である短絡( / 4 )伝送線路で構成することができる。この種のインターフェースには、下式が適用される。 30

**【0003】**

**【数1】**

$$R_D \cong \frac{1}{2\pi B W C_L}, R_D \ll \sqrt{\frac{L}{C_L}}, R_L \gg \sqrt{\frac{L}{C_L}} \quad \text{および} \quad f_{res} \cong \frac{1}{2\pi\sqrt{LC_L}}$$

40

**【0004】**

ここで、  $R_D$  は出力回路の抵抗であり、  $BW$  は帯域幅であり、  $C_L$  は入力回路の負荷容量であり、  $R_L$  は入力回路の負荷抵抗であり、  $L$  はデバイス間結線のインダクタンスであり、  $f_{res}$  は L C 共振周波数である。

**【0005】**

多くの広帯域用途にあっては、最大の帯域幅を有する平坦なすなわち非常に低い電圧ピーキング( peaking )周波数応答が望まれる。しかしながら、インターフェースがとられた I C デバイスは、  $f_{res}$  において L C 共振をもつことになる。たとえシステム帯域幅を出

50

力回路により決定し、 $f_{res}$ よりも小さくしたとしても、システム全体の伝達関数はインターフェースの誘導性共振が原因でかなりのピーキングを蒙る。ピーキング量はQ値により決定され、それは下式で表わされる。

## 【0006】

## 【数2】

$$Q \sim \frac{1}{(1/Q_L + 1/Q_C)} \quad \text{ここで、} Q_L = \frac{\omega L}{R_D} \quad \text{および} \quad Q_C = R_L \cdot \omega C_L$$

10

## 【0007】

ピーキングを制御する高速デバイス間結線の既存の方法は、 $R_D$ および $R_L$ を、 $R_L$ 、 $R_D$ 、 $Z_L$ の如く選択することが含まれる。ここで、伝送線路の終端に基づき、 $Z_L = (L/C_L)$ となる。しかしながら、これらの方法の使用は、 $R_D$ を増大させた場合に達成可能な帯域幅を減らし、或いは $R_L$ を $Z_L$ まで低減させた場合に信号振幅を低減する。更にまた、 $R_D$ 、 $R_L$ 、 $C_L$ は集積回路技術のプロセス変動の影響を受ける。かくして、 $R_D$ 、 $R_L$ を選択して予測可能な結果をもってピーキングを制御することは、プロセス変動により、困難な作業となる。

## 【発明の開示】

## 【発明が解決しようとする課題】

20

## 【0008】

これらの懸念に鑑み、必要とされるのは、達成可能な帯域幅及び/又は振幅を著しく低減することなく、その一方でプロセス変動を考慮に入れてインターフェースをとったICデバイス間で伝送される出力信号の電圧ピーキングを制御するマルチデバイスシステム及び方法である。

## 【課題を解決するための手段】

## 【0009】

集積回路(IC)デバイスの入力回路と出力回路との間で伝送される出力信号の電圧ピーキングを制御するマルチデバイスシステム及び方法は、ICデバイス製造後に調整することのできる様々な電気素子を利用して入力回路と出力回路のインピーダンスを変えるものである。これらの調整可能電気素子には入力回路内の1つ以上のパストランジスタが含まれ、このトランジスタのオン抵抗はパストランジスタに供給される制御信号を調整することで変化させることができる。調整可能電気素子にはまた、下記のうちの1つ以上の中のが含まれ得る。すなわち、調整可能電流源と、調整可能抵抗器と、調整可能抵抗器として動作する抵抗値調整可能トランジスタである。

30

## 【0010】

本発明の一実施形態によるマルチデバイスシステムには、出力回路を含む第1のICデバイスと入力回路を含む第2のICデバイスとが含まれる。出力回路は、出力信号を入力回路へ伝送するために、入力回路へ電気的に接続してある。入力回路は、入力ノードとパストランジスタと調整可能電圧源とを含む。入力ノードは、出力信号を受信するために第1のICデバイスの出力回路に接続してある。パストランジスタは、入力ノードに接続してある。パストランジスタは制御電極を有し、この制御電極は、制御信号を受信するために、調整可能電圧源に直列に接続してある。調整可能電圧源は、パストランジスタのオン抵抗を変える制御信号を調整するような構成としてある。パストランジスタのオン抵抗の変化は入力回路のインピーダンスに影響を及ぼし、そのことが翻って出力回路から入力回路へ伝送される出力信号の電圧ピーキングに影響を与える。

40

## 【0011】

本発明の一実施形態による、ICデバイス間で伝送される出力信号の電圧ピーキング制御方法は、入力ノードと低電圧端子との間に直列接続したパストランジスタを含む入力回路を設けるステップと、入力回路のパストランジスタに印加される制御信号を調整してパ

50

ストランジスタのオン抵抗を変化させ、それにより、出力回路から入力回路の入力ノードへ伝送される出力信号の電圧ピーキングに影響を与えるステップと、を含む。

#### 【0012】

本発明の他の態様及び効果は、本発明原理の例示として図示した添付図面と併せ以下の詳細な説明から明らかとなろう。

#### 【発明を実施するための最良の形態】

#### 【0013】

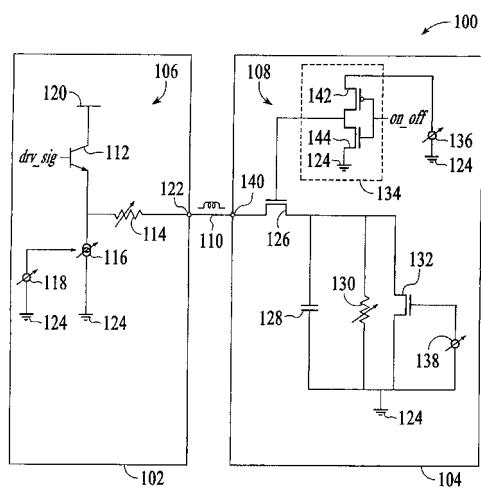

図1を参照すると、本発明の一実施形態による、集積回路（IC）デバイス102とICデバイス104とを有するマルチデバイスシステム100が図示してある。ICデバイス102, 104は、半導体チップとすることができる。ICデバイス102は出力回路106を含み、その一方でICデバイス104は入力回路108を含み、この入力回路は出力回路から伝送される出力信号により駆動される。ICデバイス102, 104は電気結線110によりインターフェースがとられており、この結線がICデバイス102の出力回路106とICデバイス104の入力回路108を接続している。電気結線110は、ボンディングワイヤ及び／又は短絡（／4）伝送線路とすることができます。図1に示した如く、電気結線110は誘導的であり、それが誘導性共振に起因するかなりのピーキングを招く。出力回路106と入力回路108は、ICデバイスのインターフェースによる電圧ピーキングが制御できるよう、それぞれのインピーダンスがICデバイス102, 104の製造後に調整し得るように設計してある。

10

20

30

40

#### 【0014】

ICデバイス102の出力回路106は、駆動トランジスタ112と随意選択的な調整可能抵抗器114と調整可能電流源116と調整可能電圧源118を含む。駆動トランジスタ112は、エミッターフォロワとして構成したバイポーラトランジスタである。かくして、駆動トランジスタ112のコレクタは高電圧端子（例えば、供給電圧端子）に接続され、トランジスタのエミッタは随意選択的な調整可能抵抗器114を介して出力ノード122に接続される。駆動トランジスタ112のエミッタはまた、調整可能電流源116に接続してある。他の実施形態では、駆動トランジスタ112は電界効果トランジスタ（FET）や相補型金属酸化膜半導体（CMOS）などの他種のトランジスタとすることもできる。出力ノード122は、電気結線110に接続してある。駆動トランジスタ112のベースは、駆動信号drv\_sigを受信する構成としてあり、この信号が駆動トランジスタ112を通って流れる電流を制御（増大或いは減少）する。かくして、駆動信号は出力回路106から入力回路108へ伝送される出力信号を決定して入力回路を駆動する。

#### 【0015】

調整可能電流源116は、駆動トランジスタ112のエミッタと低電圧端子124、例えばグラウンドとの間に直列接続してある。調整可能電流源116は、調整可能電圧源118からの制御電圧により制御される。調整可能電流源116が引き込む電流は、制御電圧に依存する。かくして、調整可能電流源116が引き込む電流は調整可能電圧源118からの制御電圧を変化させることで調整することができる。従って、固定された電流源とは対照的に、調整可能電流源116が引き込む電流をICデバイス102の製作後に調整し、下記の如く伝送出力信号の電圧ピーキングを制御することができる。一例として、調整可能電流源116はバイポーラトランジスタとすることもでき、調整可能電圧源118はオン・デバイスのディジタル／アナログ（D/A）変換器とすることもできる。本例では、バイポーラトランジスタが引き込む電流はディジタル信号をD/A変換器に選択的に伝送することで制御され、これによりバイポーラ電流源トランジスタに対するアナログ制御電圧を調整することができる。別の例では、調整可能電圧源118は調整可能抵抗器付き分圧器とし、分圧器が供給する電圧が調整可能となるようにすることもできる。

#### 【0016】

出力回路106の随意選択的な調整可能抵抗器114は、駆動トランジスタ112のエミッタと出力ノード122との間に接続してあり、その抵抗値を製造後に調整することの

50

できる抵抗器としてある。一例として、調整可能抵抗器 114 はレーザによりトリミングして抵抗器の抵抗値を変えることのできる抵抗器でよい。別の例では、調整可能抵抗器 114 は選択的に短絡させることのできる抵抗器群とし、幾つかの抵抗器だけを動作させて被接続抵抗器の総抵抗値を変えることができるようになることができる。

#### 【0017】

出力回路 106 の構成により、出力回路のインピーダンスは IC デバイス 102 の製作後に調整できるようになっている。出力回路 106 のインピーダンスは調整可能電流源 116 が引き込む電流を変化させることで調整され、調整可能電流源 116 は調整可能電圧源 118 が調整可能電流源 116 に供給する制御電圧によって制御される。出力回路 106 のインピーダンスは、調整可能抵抗器 114 の抵抗を変えることでも調整することができる。出力回路 106 のインピーダンスが IC デバイス 102 から IC デバイス 104 へ伝送される出力信号の電圧ピーキングに影響を及ぼすので、電圧ピーキングは調整可能電流源 116 及び / 又は調整可能抵抗器 114 を用いて出力回路のインピーダンスを選択的に調整することで少なくとも一部制御することができる。10

#### 【0018】

IC デバイス 104 の入力回路 108 は、パストランジスタ 126 と負荷キャパシタ 128 と隨意選択的な調整可能抵抗器 130 と隨意選択的な抵抗値調整可能トランジスタ 132 とスイッチング装置 134 と調整可能電圧源 136, 138 を含む。パストランジスタ 126 は入力ノード 140 に接続してあり、そのノードは電気結線 110 に接続してある。かくして、入力回路 108 の入力ノード 140 は電気結線 110 を介して出力回路 106 の出力ノード 122 に接続される。本実施形態では、パストランジスタ 126 は FET である。しかしながら、パストランジスタは他種のトランジスタとすることもできる。パストランジスタ 126 は、トランジスタのゲートに供給される制御信号により選択的に作動されて IC デバイス 102 の出力回路 106 から伝送される出力信号をサンプリングするサンプリングトランジスタとすることができる。パストランジスタ 126 のゲートに供給する制御信号の電圧を IC デバイス 104 製造後に調整し、これによりパストランジスタのオン抵抗を変えることができる。パストランジスタ 126 のゲートへの制御信号はスイッチング装置 134 を介して調整可能電圧源 136 により供給され、この装置はサンプリング用クロック信号でよいオンオフ信号 on/off に基づいて制御信号を選択的に伝送する構成としてある。本実施形態では、スイッチング装置 134 は相補型の P チャンネル金属酸化膜半導体 (PMOS) トランジスタ 142 及び N チャンネル金属酸化膜半導体 (NMOS) トランジスタ 144 を含む。PMOS トランジスタ 142 と NMOS トランジスタ 144 は、調整可能電圧源 136 と低電圧端子 124 との間に直列接続してある。PMOS トランジスタ 142 と NMOS トランジスタ 144 のゲートはオンオフ信号を受信するよう接続してあり、この信号が選択的に PMOS トランジスタを作動させ、NMOS トランジスタを作動停止させて、パストランジスタ 126 のゲートへ制御信号を伝送する。PMOS トランジスタの選択的な作動が調整可能電圧源 136 をパストランジスタ 126 のゲートへ接続するので、調整可能電圧源 136 が供給する電圧がパストランジスタのゲートの制御信号電圧を制御する。調整可能電圧源 136 は、オン・デバイスのディジタル / アナログ (D/A) 変換器或いは調整可能抵抗器付き分圧器とすることができる。203040

#### 【0019】

入力回路 108 の負荷キャパシタ 128 は、パストランジスタ 126 と低電圧端子 124 との間に接続してある。負荷キャパシタ 128 は、寄生回路容量及び / 又は故意に付加した容量を表わすことができる。隨意選択的な調整可能抵抗器 130 は、負荷キャパシタ 128 に並列接続してある。出力回路 106 の調整可能抵抗器 114 と同様、調整可能抵抗器 130 の抵抗値は IC デバイス 104 の製作後に調整することができる。調整可能抵抗器 130 は、レーザによるトリミングが可能な抵抗器などの製造後に抵抗値を調整することができるどんな種類の抵抗器であってもよい。隨意選択的な抵抗値調整可能トランジスタ 132 もまた、負荷キャパシタ 128 に並列接続される。本実施形態では、抵抗値調50

整可能トランジスタ 132 は FET である。しかしながら、抵抗値調整可能トランジスタは他種のトランジスタとすることもできる。抵抗値調整可能トランジスタ 132 は、調整可能抵抗器として機能する線形領域で動作する。抵抗値調整可能トランジスタ 132 のゲートは調整可能電圧源 138 に接続してあり、この電圧源はオン・デバイスの D/A 変換器或いは調整可能抵抗器付き分圧器とすることができる。調整可能電圧源 138 は I C デバイス 104 の製造後に調整することのできる電圧を抵抗値調整可能トランジスタ 132 のゲートへ供給し、トランジスタのオン抵抗を調整する。抵抗値調整可能トランジスタを調整可能抵抗器として動作させるため、ドレイン・ソース間電圧 ( $V_{ds}$ ) はゲート・ソース間電圧と閾値電圧との差分 ( $V_{gs} - V_{th}$ ) 未満としなければならない。代替構成では、調整可能抵抗器 130 及び / 又は抵抗値調整可能トランジスタ 132 は入力ノード 140 と低電圧端子 124 との間に並列に直接接続することができる。10

#### 【0020】

入力回路 108 の構成により、I C デバイス 104 の製造後に入力回路のインピーダンスを調整することができる。例えば、入力回路 108 のインピーダンスは調整可能電圧源 136 の電圧を調整してパストランジスタ 126 に供給される制御信号の電圧を調整することで先ず調整することができる。入力回路 108 のインピーダンスは次に、調整可能電圧源 138 から抵抗値調整可能トランジスタ 132 に供給される電圧を調整することで調整することができる。入力回路 108 のインピーダンスは次に、調整可能抵抗器 130 の抵抗値を変えることにより更に調整することができる。パストランジスタ 126 に供給される制御電圧、抵抗値調整可能トランジスタ 132 に供給される電圧、および調整可能抵抗器 130 の抵抗値に対し他の手順の調整を施して、入力回路 108 のインピーダンスを調整することができる。入力回路のインピーダンスが I C デバイス 102 から I C デバイス 104 へ伝送される出力信号の電圧ピークリングに影響を及ぼすため、パストランジスタ 126 と調整可能抵抗器 130 及び / 又は抵抗値調整可能トランジスタ 132 を用いて入力回路 108 のインピーダンスを選択的に調整することで電圧ピークリングを少なくとも一部制御することができる。20

#### 【0021】

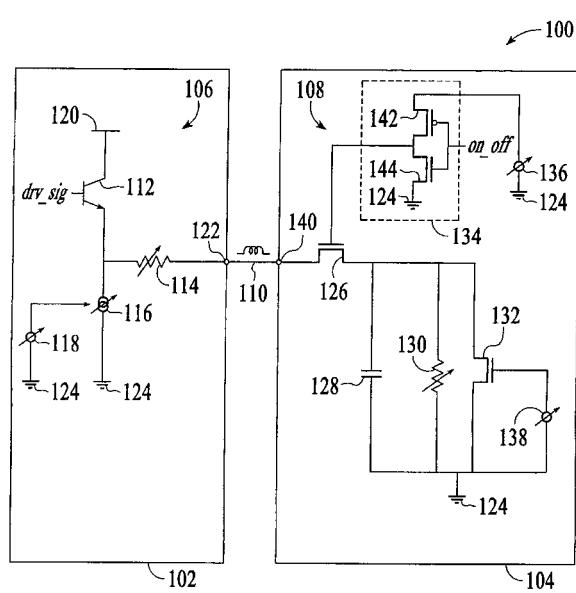

ここで図 2 を参照すると、本発明の別の実施形態による、I C デバイス 202 と I C デバイス 204 とを有するマルチデバイスシステム 200 が図示してある。図 2 のマルチデバイスシステム 200 は、図 1 のマルチデバイスシステム 100 の差動版である。かくして、本実施形態では、I C デバイス 202 は I C デバイス 204 の入力回路 208 に差動信号を伝送して入力回路を駆動するよう設計された出力回路 206 を含む。図 1 のマルチデバイスシステム 100 と同様、入力回路 208 と出力回路 206 は、I C デバイス 202, 204 の製造後に入力回路及び / 又は出力回路のインピーダンスを調整して差動信号の電圧ピークリングを制御できるよう構成してある。30

#### 【0022】

I C デバイス 202 の出力回路 206 は、駆動トランジスタ 210 と随意選択的な調整可能抵抗器 212 と調整可能電流源 214 と調整可能電圧源 216 とを含む。これらの構成要素は、図 1 のマルチデバイスシステム 100 の出力回路 106 と同一構成において、高電圧端子 218 と低電圧端子 220 (例えば、グラウンド) と出力ノード 222 とに接続してある。出力回路 206 には更に、駆動トランジスタ 224 と随意選択的な調整可能抵抗器 226 と調整可能電流源 228 と調整可能電圧源 230 とが含まれ、それらは同様に高電圧端子 218 と低電圧端子 220 と出力ノード 232 とに接続してある。他の実施形態では、調整可能電圧源 216, 230 は調整可能電流源 214, 228 の双方に制御電圧を供給する単一の調整可能電圧源により置き換えることもできる。40

#### 【0023】

駆動トランジスタ 210, 224 は駆動信号  $d_r v\_sig$ , バー  $d_r v\_sig$  を受信し、この駆動信号が出力ノード 222, 232 を介して I C デバイス 204 の入力回路 208 へ駆動トランジスタを交互に通って流れる電流を制御 (増大し減少させる) する。出力ノード 222, 232 は電気結線 234, 236 に接続してあり、それらの結線が I50

ICデバイス202の出力回路206とICデバイス204の入力回路208を接続している。電気結線234, 236は、ポンディングワイヤ及び/又は短絡( /4)伝送線路とすることができます。

#### 【0024】

図1のマルチデバイスシステム100の出力回路106と同様、出力回路206の構成により出力回路206のインピーダンスはICデバイス202の製造後に調整できるようになる。かくして、出力回路206から入力回路208へ伝送される差動信号の電圧ピーキングは、調整可能電流源214, 228及び/又は隨意選択的な調整可能抵抗器212, 226を用いて出力回路206のインピーダンスを調整することにより少なくとも部分的に制御することができる。

10

#### 【0025】

ICデバイス204の入力回路208には、パストランジスタ238と負荷キャパシタ240とスイッチング装置242と調整可能電圧源244とが含まれる。これらの構成要素は、図1のマルチデバイスシステム100の入力回路108と同じ構成において入力ノード246と低電圧端子220との間に直列に接続してある。入力ノード246は、電気結線234に接続してある。かくして、入力ノード246は出力回路206の出力ノード222に電気的に接続され、出力回路が伝送する差動信号の一方を受信する。入力回路208は更に、パストランジスタ248と負荷キャパシタ250とスイッチング装置252と調整可能電圧源254とを含み、それらは同様に入力ノード256と低電圧端子220との間に直列に接続してある。入力ノード256は、電気結線236へ接続してある。かくして、入力ノード256は出力回路206の出力ノード232に電気的に接続され、出力回路により伝送される差動信号の他方を受信する。スイッチング装置242, 252は、サンプリング用クロック信号でよいオンオフ信号on/offを受信する構成としてある。オンオフ信号はスイッチング装置を選択的に作動或いは作動停止させ、サンプリングトランジスタでよいパストランジスタ238, 248へ調整可能電圧源244, 254により供給される電圧に基づいた制御信号を伝送する。例示実施形態では、各スイッチング装置は相補型のPMOSトランジスタ258とNMOSトランジスタ260を含み、それらは個々の調整可能電圧源244や254と低電圧端子220とに直列接続してある。PMOSトランジスタ258とNMOSトランジスタ260のゲートはオンオフ信号を受信するよう構成してあり、このオンオフ信号が選択的にPMOSトランジスタ258を作動させるとともにNMOSトランジスタ260を作動停止させ、それにより、制御信号の一つが個々のパストランジスタ238, 248のゲートへ伝送される。制御信号がパストランジスタ238, 248を選択的に作動させ、例えば出力回路206からの差動信号をサンプリングする。

20

30

40

#### 【0026】

入力回路208は更に、隨意選択的な調整可能抵抗器262と隨意選択的な抵抗値調整可能トランジスタ264とを含み、それらはパストランジスタ238, 248間に並列に接続してある。抵抗値調整可能トランジスタ264は、調整可能電圧源266へも接続してある。調整可能電圧源266は、抵抗値調整可能トランジスタ264へ制御電圧を供給する。抵抗値調整可能トランジスタ264は線形領域で動作して調整可能抵抗器として機能し、その抵抗値は調整可能電圧源からの制御電圧を調整することで変化させることができる。調整可能抵抗器262は、ICデバイス204の製造後に抵抗値を調整することができる抵抗器である。代替構成では、調整可能抵抗器262及び/又は抵抗値調整可能トランジスタ264を入力ノード246と256との間に並列に直接接続することもできる。

#### 【0027】

図1のマルチデバイスシステム100の入力回路108と同様、入力回路208の構成によってICデバイス204の製作後に入力回路208のインピーダンスが調整できるようにしてある。かくして、ICデバイス202の出力回路から伝送される差動信号の電圧ピーキングは、パストランジスタ238, 248と隨意選択的な抵抗器262及び/又は

50

随意選択的な抵抗値調整可能なトランジスタ 264 を用いて入力回路 208 のインピーダンスを調整することで少なくとも一部制御することができる。

【0028】

マルチデバイスシステム 100, 200 の出力回路 106, 206 の調整可能電流源 116, 214, 228 が調整可能電圧により制御されるものとして説明したが、これらの調整可能電流源は代わって調整可能電流により制御することもできる。同様に、パストランジスタ 126, 238, 248 と抵抗値調整可能なトランジスタ 132, 264 は、調整可能電圧ではなく調整可能電流によって制御することもできる。

【0029】

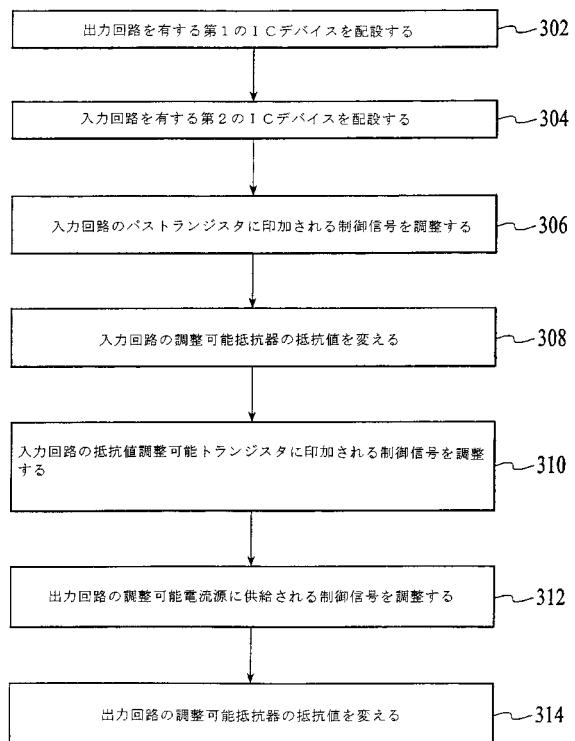

本発明の一実施形態に従い IC デバイス間で伝送される出力信号の電圧ピーキング制御方法を、図 3 のフロー線図を参照して説明する。ブロック 302 において、出力回路を有する第 1 の IC デバイスが設けられる。一例として、出力回路は図 1 のマルチデバイスシステム 100 の出力回路や図 2 のマルチデバイスシステム 200 の出力回路 206 とすることができる。ブロック 304 において、入力回路を有する第 2 の IC デバイスが設けられる。一例として、入力回路は図 1 のマルチデバイスシステム 100 の入力回路 108 や図 2 のマルチデバイスシステム 200 の入力回路 208 とすることができる。ブロック 306 において、入力回路のパストランジスタに印加される制御信号を調整し、パストランジスタのオン抵抗を変える。随意選択的なブロック 308 において、パストランジスタと低電圧端子との間に直列接続した入力回路の調整可能抵抗器の抵抗値を変える。随意選択的なブロック 310 において、パストランジスタと低電圧端子との間に直列接続した入力回路の抵抗値調整可能なトランジスタに印加する制御信号を調整し、トランジスタのオン抵抗を調整する。随意選択的なブロック 312 において、高電圧端子と低電圧端子の間に駆動トランジスタと直列に接続した出力回路の調整可能電流源に供給される制御信号を調整し、調整可能電流源が引き込む電流を調整する。随意選択的なブロック 314 において、駆動トランジスタと出力ノードとの間に直列に接続した出力回路の調整可能抵抗器の抵抗値を変える。ブロック 306 乃至 314 の実行により、入力回路及び / 又は出力回路のインピーダンスを調整し、そのことで出力回路から入力回路へ伝送される出力信号の電圧ピーキングに影響を与える。かくして、出力信号の電圧ピーキングは、ブロック 306 ~ 314 の 1 つ以上を実行することで制御することができる。

【0030】

本発明の特定の実施形態を説明し図示してきたが、本発明はかく説明し図示した部品の特定の形態や配置に限定すべきではない。本発明範囲は、本願明細書に添付した特許請求の範囲とそれらの等価物により規定される。

【図面の簡単な説明】

【0031】

【図 1】本発明の一実施形態によるマルチデバイスシステムを示す図である。

【図 2】本発明の別の実施形態によるマルチデバイスシステムを示す図である。

【図 3】本発明の一実施形態による電圧ピーキング制御方法のフロー図である。

【符号の説明】

【0032】

100 : マルチデバイスシステム

102, 104 : 集積回路デバイス

106 : 出力回路

108 : 入力回路

110 : 電気結線

112 : 駆動トランジスタ

114, 130 : 調整可能抵抗器

116 : 調整可能電流源

118, 136, 138 : 調整可能電圧源

120 : 高電圧端子

10

20

30

30

40

50

- 1 2 2 : 出力ノード

1 2 4 : 低電圧端子

1 2 6 : パストランジスタ

1 2 8 : 負荷キャパシタ

1 3 2 : 抵抗値調整可能トランジスタ

1 3 4 : スイッチング装置

1 4 0 : 入力ノード

1 4 2 : P M O Sトランジスタ

1 4 4 : N M O Sトランジスタ

【図 1】

【図 2】

【図3】

---

フロントページの続き

(72)発明者 ベルント・ヴァッパーマン

アメリカ合衆国カリフォルニア州94044, パシフィカ, タルボット アヴェニュー 460

F ターム(参考) 5F038 AV07 AV10 EZ20

5J056 AA01 AA04 BB12 BB23 BB24 CC01 CC23 DD00 DD02 DD13

DD23 DD29 DD51 DD59

5K029 AA03 CC01 DD04 JJ08