(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5247397号

(P5247397)

(45) 発行日 平成25年7月24日(2013.7.24)

(24) 登録日 平成25年4月19日(2013.4.19)

(51) Int.Cl.

H04N 5/335 (2011.01)

H01L 27/146 (2006.01)

F 1

H04N 5/335

H01L 27/14

A

請求項の数 15 (全 46 頁)

(21) 出願番号 特願2008-311439 (P2008-311439)

(22) 出願日 平成20年12月5日 (2008.12.5)

(65) 公開番号 特開2010-136205 (P2010-136205A)

(43) 公開日 平成22年6月17日 (2010.6.17)

審査請求日 平成23年11月24日 (2011.11.24)

(73) 特許権者 000001007

キヤノン株式会社

東京都大田区下丸子3丁目30番2号

(74) 代理人 100090273

弁理士 國分 孝悦

(72) 発明者 新井 公崇

東京都大田区下丸子3丁目30番2号 キ

ャノン株式会社内

審査官 木方 庸輔

最終頁に続く

(54) 【発明の名称】撮像装置及び撮像方法

## (57) 【特許請求の範囲】

## 【請求項 1】

水平方向及び垂直方向に並べて配置され、受光した光を光電変換して電荷を蓄積する複数の画素を具備する撮像手段と、

前記撮像手段による被写体に対する予備撮像により得られた画像における該被写体の輝度分布から、該被写体に対する本撮像の際の前記画素の各々の露光量を設定するピクセル露光量設定手段と、

を有することを特徴とする撮像装置。

## 【請求項 2】

前記予備撮像により得られた画像の輝度分布を表示部に表示させるように制御する表示制御手段を更に有する請求項 1 に記載の撮像装置。

## 【請求項 3】

前記露光量を設定するためのユーザーからの入力を受け付ける入力手段を更に有することを特徴とする請求項 2 に記載の撮像装置。

## 【請求項 4】

前記表示部に表示される輝度分布は被写体の輝度値の分布であることを特徴とする請求項 2 又は 3 に記載の撮像装置。

## 【請求項 5】

前記表示部に表示される輝度分布は被写体の輝度値のヒストグラムであることを特徴とする請求項 2 又は 3 に記載の撮像装置。

**【請求項 6】**

前記ユーザーからの入力は、前記複数の画素中で露光量を切り替えるための境界輝度であることを特徴とする請求項 3 に記載の撮像装置。

**【請求項 7】**

前記予備撮像は、前記複数の画素について同一の露光時間で行うことを特徴とする請求項 1 乃至 6 のいずれか 1 項に記載の撮像装置。

**【請求項 8】**

前記ピクセル露光量設定手段は、

前記撮像手段による撮像の結果、得られた画像から当該画像における前記画素の露光量マップを生成する露光量マップ生成手段と、

前記露光量マップに対応する画素駆動信号を生成するタイミングジェネレータ手段と、

を有することを特徴とする請求項 1 乃至 7 のいずれか 1 項に記載の撮像装置。

**【請求項 9】**

前記露光量マップ生成手段は、前記画素の各々に少なくとも 2 種類の露光時間のうち一つを設定することを特徴とする請求項 8 に記載の撮像装置。

**【請求項 10】**

前記タイミングジェネレータ手段は、

前記露光量マップに基づいて、

前記水平方向に並ぶ全ての画素に対して、電荷をリセットさせるリセットパルスを生成し、

前記水平方向に並ぶ全ての画素に対して、電荷を転送させる行転送パルスを生成し、

前記水平方向に並ぶ画素に対して、電荷を転送させる列転送パルスを個別に生成することを特徴とする請求項 8 又は 9 に記載の撮像装置。

**【請求項 11】**

前記タイミングジェネレータ手段は、

前記露光量マップに基づいて、

前記水平方向に並ぶ全ての画素に対して、電荷をリセットさせるリセットパルスを生成し、

前記水平方向に並ぶ画素に対して、電荷をリセットさせるリセットパルスを個別に生成し、

前記水平方向に並ぶ全ての画素に対して、電荷を転送させる行転送パルスを生成し、

前記水平方向に並ぶ画素に対して、電荷を転送させる列転送パルスを個別に生成することを特徴とする請求項 8 又は 9 に記載の撮像装置。

**【請求項 12】**

前記タイミングジェネレータ手段は、

前記露光量マップに基づいて、

前記水平方向に並ぶ全ての画素に対して、電荷をリセットさせるリセットパルスを生成し、

前記水平方向に並ぶ画素に対して、電荷をリセットさせるリセットパルスを生成し、

前記水平方向に並ぶ全ての画素に対して、電荷を転送させる行転送パルスを生成することを特徴とする請求項 8 又は 9 に記載の撮像装置。

**【請求項 13】**

前記タイミングジェネレータ手段は、

前記露光量マップに基づいて、

リセットパルスを生成し、

各露光時間に対応した第 1 の行転送パルスを生成し、

各露光時間に対応した列転送パルスを生成し、

第 2 の行転送パルスを生成することを特徴とする請求項 8 又は 9 に記載の撮像装置。

**【請求項 14】**

水平方向及び垂直方向に並べて配置され、受光した光を光電変換して電荷を蓄積する複

10

20

30

40

50

数の画素を具備する撮像手段を有する撮像装置を用いた撮像方法であって、

前記撮像手段による被写体に対する予備撮像により得られた画像における該被写体の輝度分布から、該被写体に対する本撮像の際の前記画素の各々の露光量を設定するピクセル露光量設定ステップと、

前記露光量に基づいて前記撮像手段を用いた前記本撮像を行う撮像ステップと、

を有することを特徴とする撮像方法。

#### 【請求項 15】

水平方向及び垂直方向に並べて配置され、受光した光を光電変換して電荷を蓄積する複数の画素を具備する撮像手段を有する撮像装置の制御をコンピュータに行わせるプログラムであって、

10

前記コンピュータに、

前記撮像手段による被写体に対する予備撮像により得られた画像における該被写体の輝度分布から、該被写体に対する本撮像の際の前記画素の各々の露光量を設定するピクセル露光量設定ステップと、

前記露光量に基づいて前記撮像手段を用いた前記本撮像を行う撮像ステップと、

を実行させることを特徴とするプログラム。

#### 【発明の詳細な説明】

##### 【技術分野】

##### 【0001】

本発明は、ダイナミックレンジの拡大を図った撮像装置及び撮像方法等に関する。

20

##### 【背景技術】

##### 【0002】

一般に、デジタル一眼レフカメラ、コンパクトデジタルカメラ、及びデジタルビデオカメラ等の撮像装置において用いられる像素子のダイナミックレンジ( D R )は、自然界のダイナミックレンジに対して小さいことが知られている。このため、従来、像素子のダイナミックレンジを拡大する方法について検討されてきた。例えば、マルチショットによる多サンプリング、固定パターンを用いたワンショットサンプリング、及び被写体輝度に応じた露光時間制御がある。

##### 【0003】

マルチショットによる多サンプリングでは、同じ被写体に対して、露光時間を変更して複数の撮像を行いダイナミックレンジの大きな情報を得る。そして、撮影後に、露光時間の比から各画像の画素値にゲイン補正を行い、複数ショット画像の合成を行う。

30

##### 【0004】

固定パターンを用いたワンショットサンプリングは、動体の位置ずれを回避する等、異なる露光ショット間の時間差を無くすための方法である。この方法では、センサ上に複数種の感度センサを設け、一度の撮影で複数の露出情報を取得する。感度の設定の際には、各画素の開口率の大小及びフィルタの透過率によって感度を変えたピクセルを固定パターンで配置する。この方法によれば、高低感度の時間差による位置ずれを改善することができる。

##### 【0005】

被写体輝度に応じた露光時間制御では、例えば、特許文献 2 及び 3 のように、画素毎にアナログデジタル変換器( A D C )、及び変換後のデジタル値と外部からのデジタル値とを比較する比較器を用いて、一度も電荷を読み出ことなく画素の適正露光量を検出する。

40

##### 【0006】

【特許文献 1】特開 2006 - 253876 号公報

【特許文献 2】特表 2007 - 532025 号公報

【特許文献 3】米国特許第 7362365 号明細書

#### 【発明の開示】

#### 【発明が解決しようとする課題】

50

**【0007】**

しかしながら、マルチショットによる多サンプリングでは、非常に広いダイナミックレンジを得ることができるが、結果として合成された画像はショット間に時間差で位置ズレが起こるため、合成後に輪郭ボケ及び擬似輪郭等の画像障害が発生する。

**【0008】**

また、固定パターンを用いたワンショットサンプリングでは、高低感度が固定されるため、シーンの輝度レンジが低感度で撮像できるダイナミックレンジがより広い場合は、白トビが発生する等、ダイナミックレンジ拡大効果が十分とならない場合がある。また、別の方法として、特許文献1のように露光時間の長短によって高感度、低感度の設定を行う方法もある。この場合、シーンに応じて感度設定が可能である。しかしながら、センサ上に固定パターンで感度差を設定する方法であるため、低感度、高感度ともにサンプリング点が従来のRGBセンサに比べて少なくなるため、解像度が低下する。また、被写体輝度に関係なく固定パターンを用いているため、低感度に該当するピクセルではノイズが増加する。10

**【0009】**

また、被写体輝度に応じた露光時間制御では、毎回全画素に対して電荷量を比較しなくてはならないため、多画素化及び多ビット化が困難であるという問題点がある。更に、フォトダイオードで発生する電荷は常にフローティングディフュージョンに流され続けるため、フローティングディフュージョンで発生しているノイズを常に除外することができず、ノイズ耐性が非常に劣るという問題点もある。20

**【0010】**

このように、従来の技術では、撮像素子のダイナミックレンジを適切に拡大することが困難である。

**【0011】**

本発明は、撮像素子のダイナミックレンジを適切に拡大することができる撮像装置及び撮像方法等を提供することを目的とする。

**【課題を解決するための手段】****【0012】**

本願発明者は、前記課題を解決すべく鋭意検討を重ねた結果、以下に示す発明の諸態様に想到した。30

**【0013】**

本発明に係る撮像装置は、水平方向及び垂直方向に並べて配置され、受光した光を光電変換して電荷を蓄積する複数の画素を具備する撮像手段と、前記撮像手段による被写体に対する予備撮像により得られた画像における該被写体の輝度分布から、該被写体に対する本撮像の際の前記画素の各々の露光量を設定するピクセル露光量設定手段と、を有することを特徴とする。

**【0014】**

本発明に係る撮像方法は、水平方向及び垂直方向に並べて配置され、受光した光を光電変換して電荷を蓄積する複数の画素を具備する撮像手段を有する撮像装置を用いた撮像方法であって、前記撮像手段による被写体に対する予備撮像により得られた画像における該被写体の輝度分布から、該被写体に対する本撮像の際の前記画素の各々の露光量を設定するピクセル露光量設定ステップと、前記露光量に基づいて前記撮像手段を用いた前記本撮像を行う撮像ステップと、を有することを特徴とする。40

**【発明の効果】****【0016】**

本発明によれば、白トビ、黒ツブレのない広いダイナミックレンジの撮像を行うことができる。

**【発明を実施するための最良の形態】****【0017】**

以下、本発明の実施形態について添付の図面を参照して具体的に説明する。

## 【0018】

(第1の実施形態)

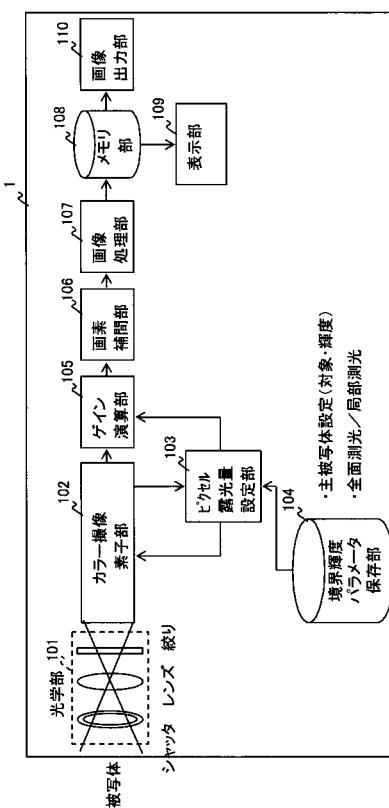

先ず、本発明の第1の実施形態について説明する。図1は、第1の実施形態に係る撮像装置の構成を示すブロック図である。

## 【0019】

第1の実施形態に係る撮像装置1には、光学部101、カラー撮像素子部102、ピクセル露光量設定部103、境界輝度パラメータ保存部104、ゲイン演算部105、画素補間部106、画像処理部107、及びメモリ部108が設けられている。更に、表示部109及び画像出力部110も設けられている。

## 【0020】

光学部101には、シャッタ、レンズ、絞り、及び光学ローパスフィルタ(LPF)等が設けられている。カラー撮像素子部102には、モザイク状に複数色配列されたカラーフィルタ及びCMOSセンサが設けられており、カラー撮像素子部102は、予備撮像及び本撮像を行う。ピクセル露光量設定部103は、カラー撮像素子部102の撮像結果から各ピクセルの露光量を設定する。境界輝度パラメータ保存部104は、複数の露光量間の境界輝度に関するパラメータを記憶している。ゲイン演算部105は、カラー撮像素子部102によって本撮像された画像、及びピクセル露光量設定部103によって設定された露光量に基づいて各画素についてのゲイン演算を行う。画素補間部106は、ゲイン演算部105によって処理が施されたモザイク状の画像に補間を施し、複数枚の独立プレーン画像を得る。画像処理部107は、色処理、ノイズ低減処理及び鮮鋭性向上処理等の処理を施す。メモリ部108は、画像処理部107によって処理された画像を記録する。表示部109は、撮影中、撮影後、及び画像処理後の画像等を表示する。表示部109としては、例えば液晶ディスプレイが用いられる。画像出力部110は、例えば出力インターフェースであり、画像出力部110に、ケーブル等を介してプリンタ、ディスプレイ及びメモリカード等の記録媒体等を接続することができ、画像出力部110を介して、メモリ部108に記録されている画像が外部の機器等に出力される。

## 【0021】

本実施形態では、ピクセル露光量設定部103は、境界輝度パラメータ保存部104に格納された予備撮像パラメータを用いて境界輝度の設定を行い、カラー撮像素子部102がこの境界輝度に基づく撮像を行う。

## 【0022】

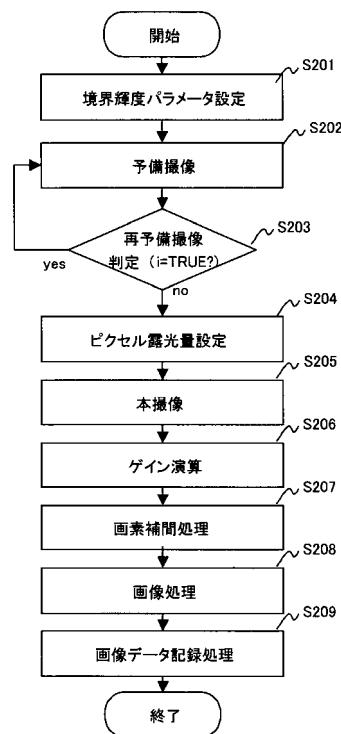

次に、撮像装置1の動作である広ダイナミックレンジ画像の撮像動作について図2を参照しながら説明する。図2は、撮像装置1の動作を示すフローチャートである。

## 【0023】

先ず、ステップS201において、初期化動作を行い、表示部109が境界輝度パラメータ設定ユーザインタフェース(UI)を表示し、ユーザ入力により、境界輝度パラメータ設定UIにパラメータを設定する。この結果、境界輝度パラメータが境界輝度パラメータ保存部104に保存される。なお、初期化動作では、例えば、予備撮像の終了を表す変数iへのFALSEの設定、及びメモリの確保等が行われる。輝度境界パラメータ設定UIの詳細については後述する。

## 【0024】

次いで、ステップS202において、カラー撮像素子部102が光学部101を介して予備撮影を行う。

## 【0025】

その後、ステップS203において、ピクセル露光量設定部103が所定の判定基準を満たしているか判定し、満たしていれば、変数iをTRUEに設定してステップS204へ移行し、そうでなければ、ステップS202へ移行する。この判断の詳細については後述する。

## 【0026】

ステップS204では、ピクセル露光量設定部103が、ステップS202で取得され

10

20

30

40

50

た予備撮像に基づいて、所定のピクセル露光量に基づき各画素の露光量を設定する。ピクセル露光量設定部 103 の詳細については後述する。

**【0027】**

続いて、ステップ S205において、カラー撮像素子部 102 が、ステップ S204で設定された各画素の露光量に基づき、本撮像処理を行う。

**【0028】**

次いで、ステップ S206において、ゲイン演算部 105 が、ステップ S204で設定された各画素の露光量に基づき、ステップ S205で取得された本撮像のデータにゲイン演算を行う。ゲイン演算の詳細については後述する。

**【0029】**

その後、ステップ S207において、画素補間部 106 が、ゲイン演算部 105 によるゲイン演算後のモザイク状の撮像画像に対する画素補間処理を行う。

**【0030】**

続いて、ステップ S208において、画像処理部 107 が、色処理、ノイズ低減処理、鮮鋭性向上処理等の画像処理を行う。

**【0031】**

次いで、ステップ S209において、メモリ部 108 が、ステップ S207 で処理された画像データを記録し、終了に関する動作を行う。

**【0032】**

なお、予備撮像の初期撮像条件におけるシャッタースピードは、本撮像に比べて十分短く設定されていることが望ましい。

**【0033】**

<境界輝度パラメータ設定 UI >

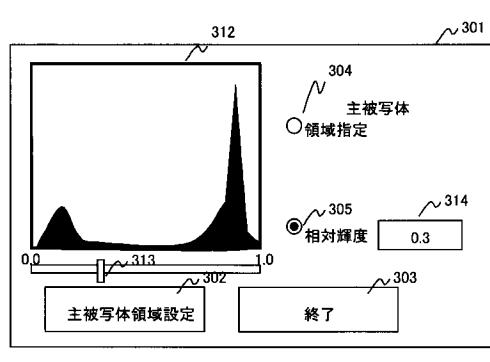

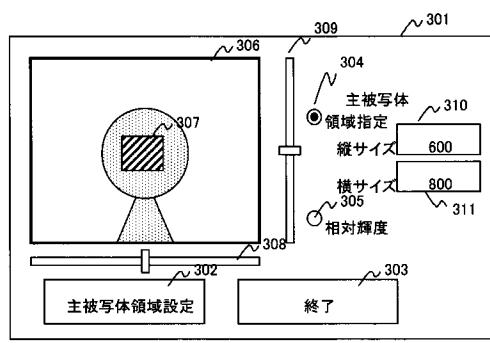

次に、境界輝度パラメータ設定 UI について図 3 を参照しながら説明する。図 3 は、ステップ S201において表示される境界輝度パラメータ設定 UI のダイアログウィンドウの例を示す図である。

**【0034】**

この境界輝度パラメータ設定 UI のダイアログウィンドウ 301 内には、図 3 (a) 及び (b) に示すように、境界輝度パラメータ設定ボタン 302、終了ボタン 303、主要被写体領域指定ラジオボタン 304、及び相対輝度指定ラジオボタン 305 が表示される。

**【0035】**

境界輝度パラメータ設定ボタン 302（主要被写体領域設定ボタン）が押下されると、設定した境界輝度パラメータを境界輝度パラメータ保存部 104 が記録する。終了ボタン 303 が押下されると、境界輝度パラメータが設定されている場合は、そのまま、RAM 等のメモリの解放等が行われ、表示部 109 における境界輝度パラメータ設定 UI のダイアログウィンドウの表示が終了する。一方、境界輝度パラメータが設定されていない場合は、予め与えられている測光ウィンドウ内の平均輝度を境界輝度パラメータ保存部 104 が境界輝度パラメータとして記録する。そして、RAM 等のメモリの解放等が行われ、表示部 109 における境界輝度パラメータ設定 UI のダイアログウィンドウの表示が終了する。

**【0036】**

主要被写体領域指定ラジオボタン 304 が選択されると、図 3 (a) に示すように、ウィンドウ 306 及び 307、スライドバー 308 及び 309、並びにテキストボックス 310 及び 311 が表示される。一方、相対輝度指定ラジオボタン 305 が選択されると、図 3 (b) に示すように、ウィンドウ 312、スライドバー 313 及びテキストボックス 314 が表示される。

**【0037】**

ウィンドウ 306 は、ファインダ画像表示ウィンドウとして機能し、ファインダ画像を表示する。ウィンドウ 307 は、主要被写体ウィンドウとして機能し、スライドバー 30

10

20

30

40

50

8 及び 309 の設定に基づいてウィンドウ 306 内での主要被写体の位置を表示する。スライドバー 308 及び 309 は、ウィンドウ位置設定スライドバーとして機能し、スライドバー 308 及び 309 がスライドされると、これに伴ってウィンドウ 307 の位置が変更される。テキストボックス 310 及び 311 は、主要被写体ウィンドウサイズ指定テキストボックスとして機能し、テキストボックス 310 及び 311 に数値が入力されると、これに伴ってウィンドウ 307 のサイズが変更される。

#### 【0038】

ウィンドウ 312 は、ヒストグラム表示ウィンドウとして機能し、ヒストグラムを表示する。スライドバー 313 は、主要被写体輝度設定スライドバーとして機能し、スライドバー 313 がスライドされると、この結果としてスライドされた相対輝度がテキストボックス 314 に反映される。逆に、テキストボックス 314 に数値が入力されると、この結果がスライドバー 313 に反映される。10

#### 【0039】

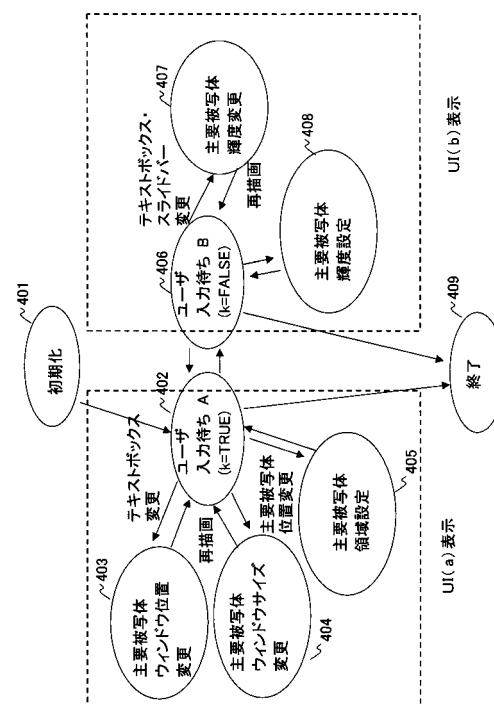

次に、境界輝度パラメータ設定 UI の境界輝度パラメータ設定動作について図 4 を参照しながら説明する。図 4 は、境界輝度パラメータ設定動作を示す状態遷移図である。

#### 【0040】

ステート 401 では、初期設定値を読み込み、図 3 (a) に示す境界輝度パラメータ設定 UI の表示等の初期化動作を行い、ステート 402 へ移行する。

#### 【0041】

ステート 402 では、図 3 (a) に示す境界輝度パラメータ設定 UI に対するユーザ操作判断待ち状態となる。また、境界輝度パラメータの指定パターンを示す変数 k が TRUE に設定される。ここで、スライドバー 308 又は 309 の位置が変更されると、ステート 403 へ移行し、ウィンドウ 307 の位置を変更すると共に、ウィンドウ 307 を再描画した後、ステート 402 へ移行する。また、テキストボックス 310 又は 311 に数値が入力されると、ステート 404 へ移行する。ステート 404 では、入力された数値に基づいてウィンドウ 307 のサイズを変更すると共に、ウィンドウ 307 を再描画した後、ステート 402 へ移行する。境界輝度パラメータ設定ボタン 302 が押下されると、ウィンドウ 307 の位置及びサイズ並びに境界輝度パラメータの指定パターンを示す変数 k をメモリ部 108 に格納する。終了ボタン 303 が押下されると、ステート 409 へ移行し、終了に関する動作を行う。20

#### 【0042】

ステート 402 で、相対輝度指定ラジオボタン 305 が選択されると、ステート 406 へ移行し、図 3 (b) に示す境界輝度パラメータ設定 UI に対するユーザ操作判断待ち状態となる。また、境界輝度パラメータの指定パターンを示す変数 k が FALSE に設定される。ここで、スライドバー 313 又はテキストボックス 314 が変更されると、ステート 407 へ移行する。ステート 407 では、変更後のスライドバー 313 の位置又はテキストボックス 314 に入力された情報に基づき主要被写体輝度を変更し、ステート 406 へ移行する。境界輝度パラメータ設定ボタン 302 が押下されると、主要被写体輝度及び境界輝度パラメータの指定パターンを示す変数 k をメモリ部 108 に格納する。終了ボタン 303 が押下されると、ステート 409 へ移行し、終了に関する動作を行う。30

#### 【0043】

境界輝度パラメータ設定 UI には、上述のような表示がなされ、これを介して上述のような動作が行われる。

#### 【0044】

<ピクセル露光量設定部 103 >

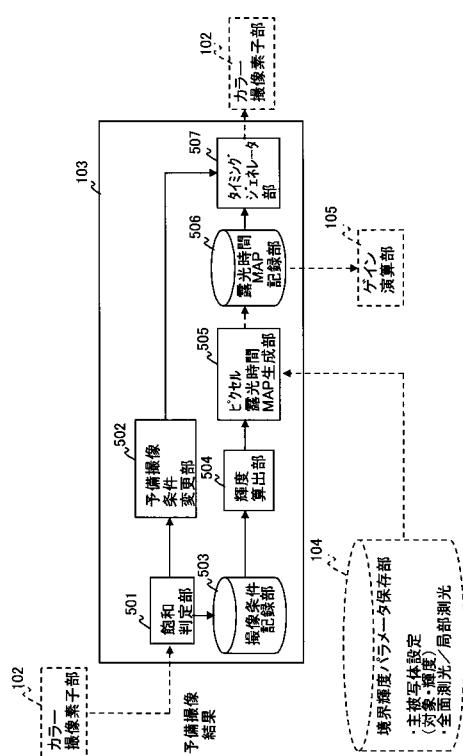

次に、ピクセル露光量設定部 103 について図 5 を参照しながら説明する。図 5 は、ピクセル露光量設定部 103 の一例を示すブロック図である。

#### 【0045】

ピクセル露光量設定部 103 には、飽和判定部 501、予備撮像条件変更部 502、撮像条件記録部 503、輝度算出部 504、露光時間 MAP 生成部 505、露光時間 MAP40

記録部 506、及びタイミングジェネレータ部 507 が設けられている。

#### 【0046】

飽和判定部 501 は、予備撮像結果に飽和画素が含まれているかを判定する。予備撮像条件変更部 502 は、飽和判定結果から予備撮像条件を変更する。撮像条件記録部 503 は、各画素について不飽和となる撮像条件を記録する。輝度算出部 504 は、撮像条件記録部 503 に記録されている撮像条件に基づき、各画素の輝度を算出する。露光時間 MAP 生成部 505 は、露光量マップ生成手段として、境界輝度パラメータ保存部 104 に保持された予備撮像パラメータ、及び輝度算出部 504 により算出された輝度情報を基づいて、ピクセル露光時間 MAP (露光量マップ) を生成する。露光時間 MAP 記録部 506 は、露光時間 MAP 生成部 505 により生成された MAP 情報を記録する。タイミングジェネレータ部 507 は、露光時間 MAP に基づき各画素の CMOS センサのトランジスタの駆動パルス (画素駆動信号) を生成する。なお、露光時間 MAP 記録部 506 に記録された情報は、後述のゲイン演算処理においても利用される。10

#### 【0047】

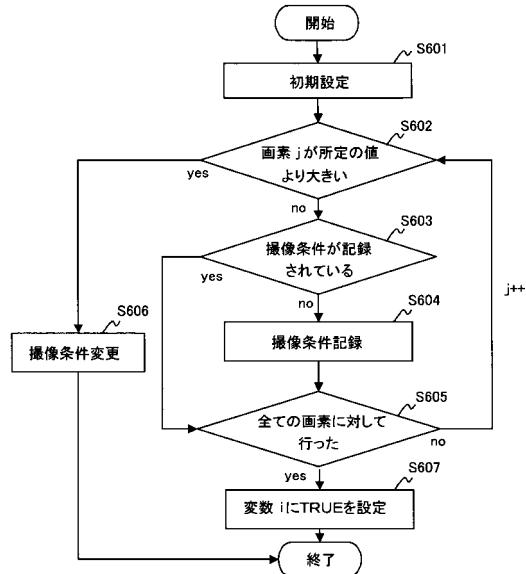

##### <再予備撮像判定動作>

次に、ステップ S203 の判断 (再予備撮像判定動作) について図 6 を参照しながら説明する。図 6 は、再予備撮像判定動作の詳細を示すフローチャートである。

#### 【0048】

先ず、ステップ S601において、ピクセル露光量設定部 103 が初期化動作を行う。例えば、画素番号を表す変数 j への 0 の設定、及びメモリの確保等が行われる。20

#### 【0049】

次いで、ステップ S602において、飽和判定部 501 が、画素 j と所定の値とを比較し、画素 j の方が小さければステップ S603 へ移行し、そうでなければステップ S606 へ移行する。ここで、所定の値とは、例えば、カラー撮像素子部 102 のカラー撮像素子のセンサ値が輝度に対して線形性を保持できる最大値が用いられる。なお、センサが取得しうる値であれば用いることができる。

#### 【0050】

ステップ S603 では、ピクセル露光量設定部 103 が、画素 j に対する撮像条件が撮像条件記録部 503 に記録されているかを判断し、記録されていなければステップ S604 へ移行し、記録されていればステップ S605 へ移行する。ここで、撮像条件とは、例えば絞り値、シャッタースピード、ISO 感度及び画素値である。30

#### 【0051】

ステップ S604 では、撮像条件記録部 503 が、図 7 に示すように、画素番号と関連付けされた撮像条件を記録する。

#### 【0052】

ステップ S605 では、ピクセル露光量設定部 103 が、全ての画素に対して処理が行われたか判断し、行われていればステップ S607 へ移行し、そうでなければ画素番号を表す変数 j に 1 を加えてステップ S602 へ移行する。

#### 【0053】

ステップ S606 では、予備撮像条件変更部 502 が、撮像条件のシャッタースピードを変更し、タイミングジェネレータ部 507 が全ての画素に同じ撮像条件に対するカラー撮像素子部 102 の画素駆動パルスを生成する。その後、終了に関する処理を行う。40

#### 【0054】

ステップ S607 では、予備撮像の終了を表す変数 i に TRUE を設定し、終了に関する処理を行う。

#### 【0055】

##### <ピクセル露光量設定動作>

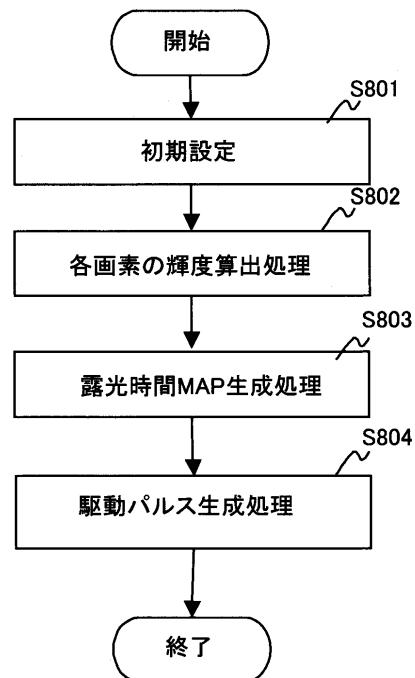

次に、ステップ S204 のピクセル露光量設定動作について図 8 を参照しながら説明する。図 8 は、ピクセル露光量設定動作の詳細を示すフローチャートである。

#### 【0056】

先ず、ステップ S 8 0 1において、ピクセル露光量設定部 1 0 3が初期化動作を行う。例えば、撮像条件記録部 5 0 3に格納されている絞り値、ISO感度及び各画素の輝度値の読み込み、並びにメモリの確保等が行われる。

## 【0057】

次いで、ステップ S 8 0 2において、輝度算出部 5 0 4が、図 7に示すような撮像条件を取得し、下記の式(数1～数6)を用いて輝度を算出する。ここで、画素番号を表す変数を  $j$ 、画素値を表す変数を  $P_j$ 、画素の輝度値を表す変数を  $PB_j$ 、絞り値を表す変数を  $F_j$ 、シャッタースピードを表す変数を  $T_j$ 、ISO感度を  $ISO_j$ 、被写体の適正輝度を表す変数を  $B_j$ とする。また、絞り値を表すAPEX値を  $AV_j$ 、シャッタースピードを表すAPEX値を  $TV_j$ 、ISO感度を表すAPEX値を  $SV_j$ 、被写体輝度を表すAPEX値を  $BV_j$ とする。

10

## 【0058】

即ち、輝度算出部 5 0 4は、先ず、撮像条件から画素番号  $j$ の各APEX値を数1～数3に基づいて算出する。

## 【0059】

## 【数1】

$$AV_j = 2 \log_2(F_j)$$

20

## 【0060】

## 【数2】

$$TV_j = -\log_2(T_j)$$

## 【0061】

## 【数3】

$$SV_j = \log_2(ISO_j / 3.125)$$

30

## 【0062】

次いで、輝度算出部 5 0 4は、数4から被写体輝度のAPEX値を算出する。

## 【0063】

## 【数4】

$$BV_j = AV_j + TV_j - SV_j$$

40

## 【0064】

その後、輝度算出部 5 0 4は、数5から被写体輝度を算出する。

## 【0065】

## 【数5】

$$B_j = 2^{BV_j} \times N \div K \quad (\text{但し、} N, K \text{は定数})$$

## 【0066】

続いて、輝度算出部 5 0 4は、数6から画素番号  $i$ の輝度を算出する。

50

【0067】

【数6】

$$PB_j = B_j \times (P_j \div \text{最大信号値}) \times (100 \div 18)$$

【0068】

ステップS802の後、ピクセル露光時間MAP生成部505が露光時間MAPを生成し、これを露光時間MAP記録部506が記録する。露光時間MAPの詳細については後述する。

10

【0069】

次いで、ステップS804において、ステップS803に生成された露光時間MAPに基づき、タイミングジェネレータ部507が画素の駆動パルスを生成し、終了に関する処理を行う。

【0070】

&lt;露光時間MAP生成処理&gt;

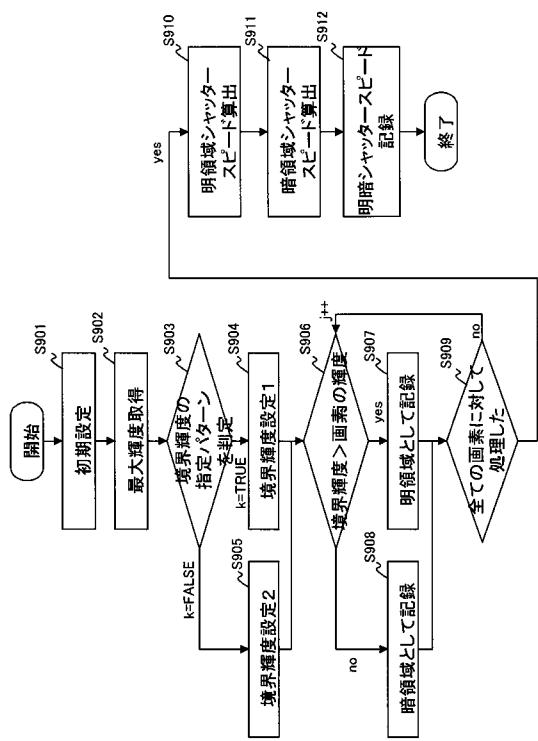

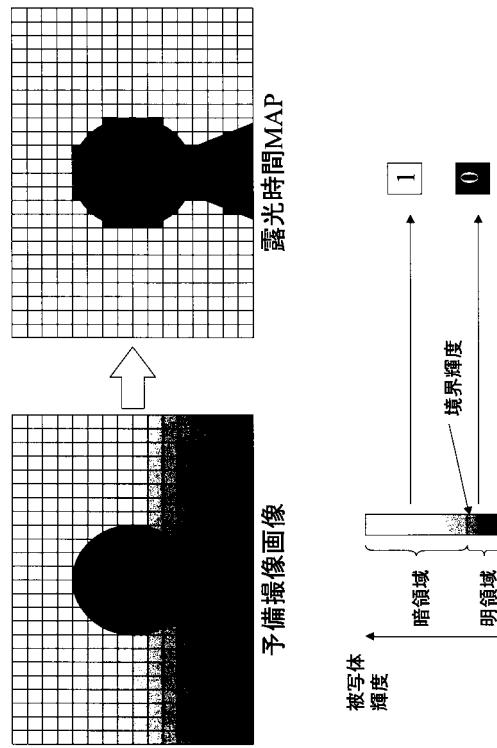

次に、ステップS803の露光時間MAP生成処理について図9を参照しながら説明する。図9は、露光時間MAP生成処理の詳細を示すフローチャートである。

【0071】

先ず、ステップS901において、ピクセル露光量設定部103が初期化動作を行う。例えば、境界輝度パラメータ保存部104に保存されている境界輝度パラメータ、撮像条件記録部503に格納されている絞り値、ISO感度及び各画素の輝度値の読み込み、並びにメモリの確保等が行われる。

20

【0072】

次いで、ステップS902において、ピクセル露光時間MAP生成部505が、全画素の輝度値を走査して最大輝度値MBを取得する。

【0073】

その後、ステップS903において、ピクセル露光時間MAP生成部505が、境界輝度パラメータの指定パターンを示す変数kがTRUEであるか判定し、TRUEであればステップS904へ移行し、そうでなければ905へ移行する。

30

【0074】

ステップS904では、ピクセル露光時間MAP生成部505が、境界輝度パラメータの指定領域位置の輝度情報、及びステップS903で取得した最大輝度値MBに基づいて、数7及び数8から境界輝度パラメータを算出すると共に、境界輝度を設定する。以後、境界輝度未満の輝度の領域を明領域、それ以上の輝度の領域を暗領域という。ここで、指定領域のサイズをm×nとし、各画素輝度PBk、平均輝度PBave、境界輝度SBとする。

【0075】

【数7】

$$PB_{ave} = \sum_1^{m \times n} \frac{PB_k}{m \times n}$$

40

【0076】

【数8】

$$SB = PB_{avr} \times (100 \div 18)$$

【0077】

ステップS905では、ピクセル露光時間MAP生成部505が、ステップS903で取得した最大輝度値MB、及び境界輝度パラメータに基づいて、数9から境界輝度を算出すると共に、境界輝度SBを設定する。

【0078】

【数9】

$$SB = \text{境界輝度パラメータ} \times MB$$

【0079】

ステップS904又はS905の後、ステップS906において、ピクセル露光時間MAP生成部505が、画素番号jの輝度値と設定された境界輝度とを比較する。そして、画素番号jの輝度値の方が小さければステップS907Sへ移行し、そうでなければステップS908へ移行する。

【0080】

ステップS907では、ピクセル露光時間MAP生成部505が、明領域を示す0を記録する。ステップS908では、ピクセル露光時間MAP生成部505が、暗領域示す1を記録する。なお、ピクセル露出時間MAPは、例えば図10に示すように記録される。

【0081】

ステップS907又はS908の後、ステップS909において、ピクセル露光時間MAP生成部505が、全ての画素に対して処理を行ったかを判定する。そして、行っているればステップS910へ移行し、そうでなければ画素番号を表すjに1を加えてステップS906へ移行する。

【0082】

ステップS910では、ピクセル露光時間MAP生成部505が、数10～数12に基づいて、明領域のシャッタースピードTV<sub>light</sub>を算出する。

【0083】

即ち、ピクセル露光時間MAP生成部505は、先ず、数10から主要被写体のBV<sub>light</sub>を求める。

【0084】

【数10】

$$BV_{light} = \log_2 (SB \times N \div K)$$

【0085】

次に、ピクセル露光時間MAP生成部505は、上記の数1及び数3からAV<sub>light</sub>及びSV<sub>light</sub>を求め、数11からTV<sub>light</sub>を求める。

【0086】

【数11】

$$TV_{light} = SV_{light} + BV_{light} - AV_{light}$$

【0087】

そして、ピクセル露光時間MAP生成部505は、数12から暗領域のシャッタースピードTV<sub>light</sub>を求める。

10

20

30

40

50

ード  $T_{light}$  を算出する。

【0088】

【数12】

$$T_{light} = 2^{-TV_{light}}$$

【0089】

ステップ S 9 1 0 の後、ステップ S 9 1 1において、ピクセル露光時間 M A P 生成部 5 0 5 が、数 1 3 ~ 数 1 5 を用いて、暗領域のシャッタースピード  $T_{dark}$  を算出する。 10

【0090】

即ち、ピクセル露光時間 M A P 生成部 5 0 5 は、先ず、数 1 3 から主要被写体の  $BV_{dark}$  を求める。

【0091】

【数13】

$$BV_{dark} = \log_2(MB \times N \div K)$$

【0092】

次に、ピクセル露光時間 M A P 生成部 5 0 5 は、上記の数 1 及び数 3 から  $AV_{dark}$  及び  $SV_{dark}$  を求め、数 1 4 から  $TV_{dark}$  を求める。 20

【0093】

【数14】

$$TV_{dark} = SV_{dark} + BV_{dark} - AV_{dark}$$

【0094】

そして、ピクセル露光時間 M A P 生成部 5 0 5 は、数 1 5 から暗領域のシャッタースピード  $T_{dark}$  を算出する。 30

【0095】

【数15】

$$T_{dark} = 2^{-TV_{dark}}$$

【0096】

ステップ S 9 1 1 の後、ステップ S 9 1 2において、露光時間 M A P 記録部 5 0 6 が、暗領域のシャッタースピードを表す  $T_{dark}$  及び明領域のシャッタースピードを表す  $T_{light}$  を格納する。その後、終了に関する処理を行う。 40

【0097】

< 駆動パルス生成処理 >

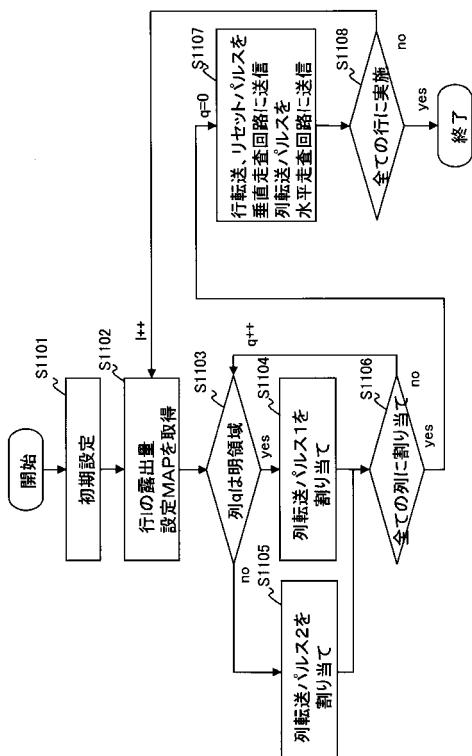

次に、ステップ S 8 0 4 の駆動パルス生成処理について図 1 1 を参照しながら説明する。図 1 1 は、第 1 の実施形態における駆動パルス生成処理の詳細を示すフローチャートである。

【0098】

先ず、ステップ S 1 1 0 1において、タイミングジェネレータ部 5 0 7 が初期化動作を行う。例えば、行を表す変数 l、列を表す変数 q を夫々 0 に設定する等の動作が行われる。

【0099】

次いで、ステップ S 1102において、タイミングジェネレータ部 507 が、第1行目の全ての露出量設定 MAP の値を読み込む。

#### 【0100】

その後、ステップ S 1103において、タイミングジェネレータ部 507 が、第 q 列目のシャッタースピードが明領域のシャッタースピードであるか判断し、そうであればステップ S 1104へ移行し、そうでなければステップ S 1105へ移行する。

#### 【0101】

ステップ S 1104では、タイミングジェネレータ部 507 が、第1行第 q 列目の画素に対し、明領域のシャッタースピードに対応する列転送トランジスタの駆動パルスを割り当てる。ステップ S 1105では、タイミングジェネレータ部 507 が、第1行第 q 列目の画素に対し、暗領域のシャッタースピードに対応する後述の列転送トランジスタの駆動パルスを割り当てる。10

#### 【0102】

ステップ S 1104又は S 1105の後、ステップ S 1106において、タイミングジェネレータ部 507 が、行中の全ての列について割り当てが行われたかを判定する。そして、行われていれば列を表す変数 q を 0 に設定してステップ S 1107へ移行し、そうでなければ列を表す変数 q に 1 を加えてステップ S 1103へ移行する。

#### 【0103】

ステップ S 1107では、タイミングジェネレータ部 507 が、第1行目の画素に対し、後述の行転送トランジスタ及びリセットトランジスタの駆動パルス（第1の行転送パルス、第2の行転送パルス及びリセットパルス）を生成する。また、タイミングジェネレータ部 507 は、これらを垂直走査回路に送信する。また、タイミングジェネレータ部 507 は、ステップ S 1104又はステップ S 1105で割り当てた列転送トランジスタの駆動パルス（列転送パルス）を生成し、これを水平走査回路に送信する。20

#### 【0104】

ステップ S 1108では、タイミングジェネレータ部 507 が、全ての行に対して駆動パルスの送信が行われているかを判定し、行われていれば終了に関する処理を行い、そうでなければ行を表す変数 1 に 1 を加えてステップ S 1102へ移行する。

#### 【0105】

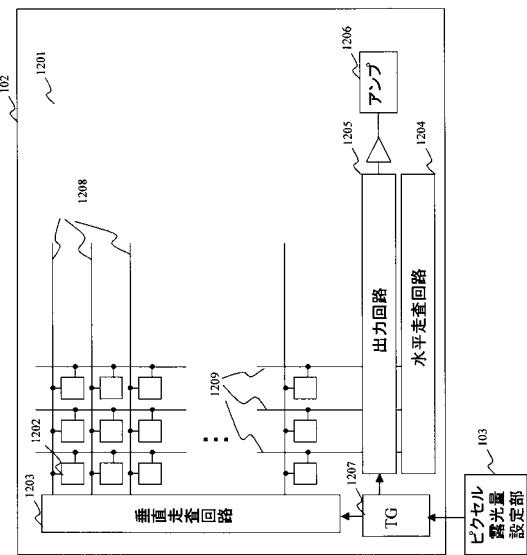

< カラー撮像素子部 102 >

次に、カラー撮像素子部 102 について図 12 を参照しながら説明する。図 12 は、カラー撮像素子部 102 を構成する各構成要素の配置の一例を示す模式図である。30

#### 【0106】

カラー撮像素子部 102 では、撮像面 1201 上に、水平方向及び垂直方向（二次元）に並んだ複数の画素 1202、垂直走査回路 1203、水平走査回路 1204、出力回路 1205、出力アンプ 1206、及びタイミングジェネレータ 1207 等が設けられている。そして、画素 1202 の水平行毎の並びと垂直走査回路 1203 とが行選択線 1208 で互いに結ばれ、画素 1002 の垂直列毎の並びと水平走査回路 1204 及び出力回路 1205 とが列信号線 1209 で結ばれている。このため、行又は列の所定単位毎（所定行毎又は所定列毎）の制御が行われる。40

#### 【0107】

カラー撮像素子部 102 の撮像動作の際には、ピクセル露光量設定部 103 の露光量設定に基づき、タイミングジェネレータ部 507 にて生成された駆動パルスをタイミングジェネレータ 1207 が垂直走査回路 1203 及び出力回路 1205 に出力する。各画素 1202 で、駆動パルスによるトランジスタの導通 / 非導通によって、リセット及び読み出しが制御される。読み出された電荷は電圧に変換され、水平走査回路 1204 から出力回路 1205 に、順次、転送され、出力アンプ 1206 に出力される。

#### 【0108】

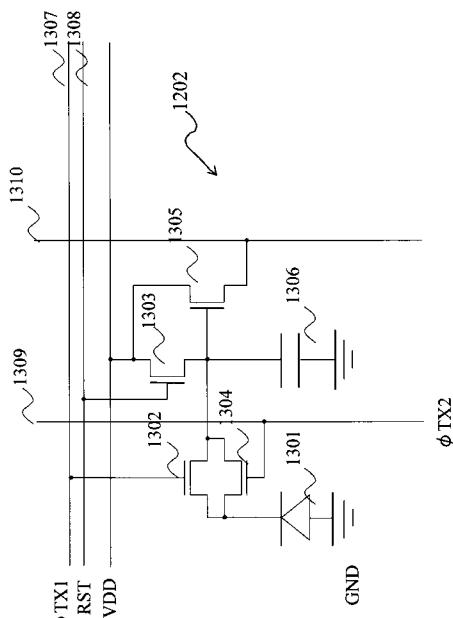

図 13 は、第 1 の実施形態における画素 1202 の構造の一例を示す回路図である。

#### 【0109】

50

30

40

50

画素 1202 には、受光素子である埋め込み型 PD (フォトダイオード) 1301、及びNチャンネルMOSトランジスタ 1302～1305が含まれている。トランジスタ 1302 及びトランジスタ 1304 のドレイン、並びにトランジスタ 1303 のソースの接続部は、FD (フローティングディフュージョン) 1306 で構成されている。行選択線 1307、行信号線 1308、列選択線 1309 及び列信号線 1310 は各トランジスタに対する信号を伝送し、図 13 中の VDD は電源、GND は接地を示す。なお、信号が H (High) であれば各ゲートが導通し、L (Low) ならば非導通になるように構成されている。

#### 【0110】

PD 1301 は光電変換部 (受光部) であり、被写体からの入射光量に応じた電荷を一時的に蓄積し、蓄積した信号電荷が転送ゲートとよばれる行転送トランジスタ 1302 又は列転送トランジスタ 1304 によって FD 1306 に完全転送されることで出力される。転送された信号電荷は、蓄積部として機能する FD 1306 に一時的に蓄積される。以下、行転送トランジスタ 1302 の電位を TX1、列転送トランジスタ 1304 の電位を TX2 と表す。

#### 【0111】

トランジスタ 1303 はリセットトランジスタとよばれ、トランジスタ 1303 が導通することによって FD 1306 が既定の電位 (RSB) にリセットされる。このリセット動作の際に、リセットノイズとよばれる、リセット動作を行う毎に FD 1306 の電位が RSB に対してばらつくノイズが発生することがある。

#### 【0112】

トランジスタ 1305 は、ソースフォロワ增幅回路を構成し、FD 1106 の電位 VF D に対する電流増幅を行うことで、出力インピーダンスを下げる。また、トランジスタ 1305 のドレインは列信号線 1310 に接続されており、低インピーダンス化されて、画素出力 VOUT として、列信号線 1310 へ導出される。

#### 【0113】

図 14A～図 14D は、図 13 に示す画素 1202 の駆動方法及びその特性を示す図である。図 14A は、転送ゲートであるトランジスタ 1302 及びトランジスタ 1304、並びにリセットトランジスタ 1303 の導通 / 非導通を制御する駆動方法を示すタイミングチャートである。なお、t11～t15 はタイミングを表す。

#### 【0114】

図 14A に示す例では、タイミング t11 で、リセットトランジスタ 1303 及び行転送トランジスタ 1302 のゲートが導通になる。この結果、PD 1301 の電荷が FD 1306 に完全転送されてリセットされ、FD 1306 もリセットトランジスタ 1303 のドレイン電位にリセットされる (第 1 のリセット、第 2 のリセット)。タイミング t11 から所定時間後のタイミング t12 で、行転送トランジスタ 1302 のゲートが非導通になる。この結果、PD 1301 への電荷の蓄積が開始される。また、リセットトランジスタ 1303 は導通のままであり、露光中に FD 1306 にて発生するノイズが列転送トランジスタ 1304 のゲート導通前に除去される。なお、これ以降の説明では、動作に変化のないトランジスタの状態に関する説明は省略する。タイミング t11 から所定時間後のタイミング t13 で、リセットトランジスタ 1303 が非導通、列転送トランジスタ 1304 のゲートが導通となり、被写体からの光が PD 1301 の電荷が FD 1306 に完全転送される (第 1 の転送、第 2 の転送)。タイミング t11 から所定時間後のタイミング t14 で、トランジスタ 1305 が導通する。この結果、FD 1306 の電位が低インピーダンス化されて、画素出力 VOUT として、出力回路 1205 に接続された信号線へ導出される。タイミング t11 から所定時間後のタイミング t15 で出力回路 1205 に接続された信号線への導出が終了する (第 3 の転送)。

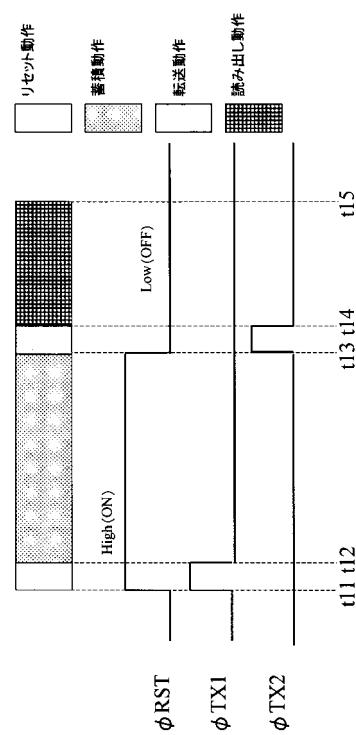

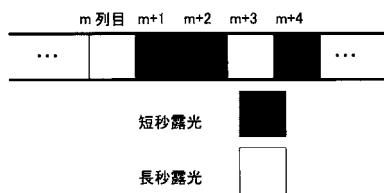

#### 【0115】

次に、ライン内の各画素に 2 種類の列転送パルスを送信して長短露光を制御する方法について、図 14B 及び図 14C を参照しながら説明する。なお、本実施形態における長短

10

20

30

40

50

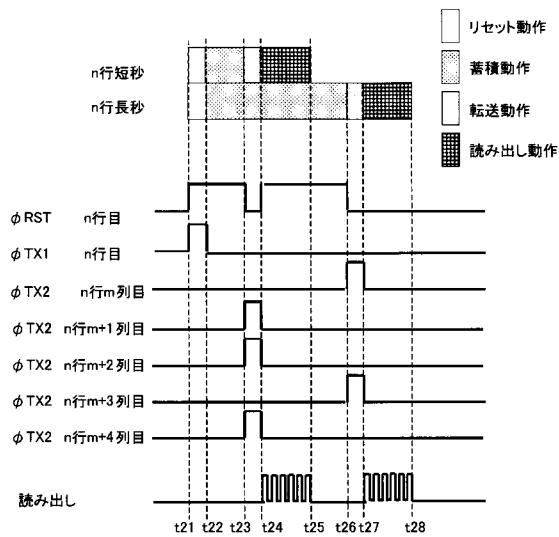

露光は、列転送トランジスタ毎に2種類のうちいずれかの導通タイミングを与えることにより制御を実現する。図14Bは、撮像画素第n行目の第m列～第m+4列までの露光量を示す模式図であり、白い部分が長秒露光、黒い部分が短秒露光を表す。また、図14Cは、行転送トランジスタ1302、列転送トランジスタ1304及びリセットトランジスタ1303の導通／非導通を制御する駆動方法を示すタイミングチャートである。なお、t21～t28はタイミングを表す。

#### 【0116】

図14Cに示す例では、タイミングt21で、全てのリセットトランジスタ1303、及び全ての行転送トランジスタ1302のゲートが導通になる。この結果、全てのPD1301の電荷がFD1106に完全転送されてリセットされ、全てのFD1306もリセットトランジスタ1303のドレイン電位にリセットされる。

10

#### 【0117】

タイミングt22で、全ての行転送トランジスタ1302のゲートが非導通になる。この結果、全てのPD1301への電荷の蓄積が開始される。

#### 【0118】

タイミングt23で、リセットトランジスタ1303が非導通となり、短秒露光が割り当てられている第m+1列目、第m+2列目及び第m+4列目の列転送トランジスタ1304のゲートが導通となり、被写体からの光から得られたPD1301の電荷がFD1306に完全転送される。

20

#### 【0119】

タイミングt24で、短秒露光が割り当てられている第m+1列目、第m+2列目及び第m+4列目の列転送トランジスタ1304のゲートが非導通となり、トランジスタ1305が導通する。この結果、FD1306の電位が低インピーダンス化されて、短秒画素出力VOUT<sub>s</sub>として、個別に、出力回路1205に接続された信号線へ導出される。また、出力回路1205に接続された信号線へ導出された後、リセットトランジスタ1303が導通、列転送トランジスタ1304が非導通となる。

#### 【0120】

タイミングt25で、短秒画素出力VOUT<sub>s</sub>の出力回路1205に接続された信号線への導出が終了する。

#### 【0121】

タイミングt26で、リセットトランジスタ1303が非導通となり、長秒露光が割り当てられている第m列目及び第m+3列目の列転送トランジスタ1304のゲートが導通となる。この結果、被写体からの光から得られたPD1301の電荷がFD1306に完全転送される。

30

#### 【0122】

タイミングt27で、長秒露光が割り当てられている第m列目及び第m+3列目の列転送トランジスタ1304のゲートが非導通となり、トランジスタ1305が導通する。この結果、FD1306の電位が低インピーダンス化されて、長秒画素出力VOUT<sub>L</sub>として、出力回路1205に接続された信号線へ導出される。

#### 【0123】

タイミングt28で、長秒画素出力VOUT<sub>L</sub>の出力回路1205に接続された信号線への導出が終了する。

40

#### 【0124】

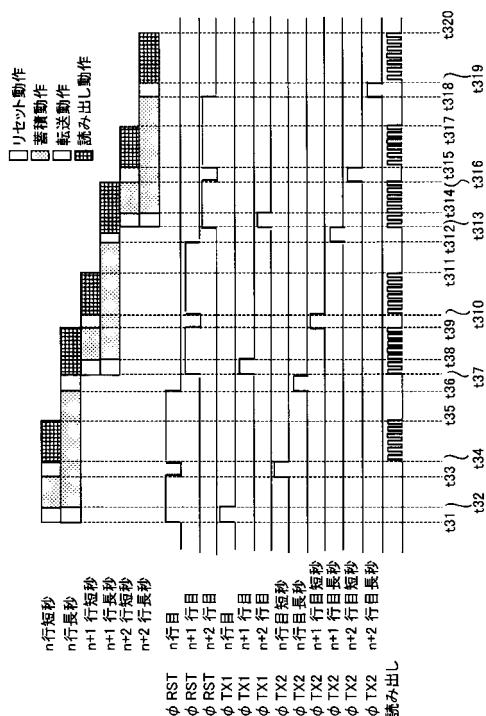

次に、各ラインの各画素に2種類の列転送パルスを送信して長短露光を制御する方法について、図14Dを参照しながら説明する。図14Dは、撮像画素第n行～第n+3行目までの行転送トランジスタ1302、列転送トランジスタ1304及びリセットトランジスタ1303の導通／非導通を制御する駆動方法を示すタイミングチャートである。なお、t31～t320はタイミングを表す。

#### 【0125】

図14Dに示す例では、タイミングt31で、第n行目全てのリセットトランジスタ1

50

303、及び第n行目全ての行転送トランジスタ1302のゲートが導通になる。この結果、第n行目全てのPD1301の電荷がFD1306に完全転送されてリセットされ、第n行目全てのFD1306もリセットトランジスタ1303のドレイン電位にリセットされる。

#### 【0126】

タイミングt32で、第n行目全ての行転送トランジスタ1302のゲートが非導通になる。この結果、第n行目全てのPD1301への電荷の蓄積が開始される。

#### 【0127】

タイミングt33で、第n行目全てのリセットトランジスタ1303が非導通となり、第n行目の短秒露光が割り当てられている列の列転送トランジスタ1304のゲートが導通となる。この結果、被写体からの光から得られたPD1301の電荷がFD1306に完全転送される。10

#### 【0128】

タイミングt34で、第n行目の短秒露光が割り当てられている列の列転送トランジスタ1304のゲートが非導通となり、n列目のトランジスタ1305が導通する。この結果、FD1306の電位が低インピーダンス化されて、第n列目の短秒画素出力VOUT<sub>n-s</sub>として、出力回路1205に接続された信号線へ導出される。また、出力回路1205に接続された信号線へ導出された後、第n行目全てのリセットトランジスタ1303が導通となる。

#### 【0129】

タイミングt35で、短秒画素出力VOUT<sub>n-s</sub>の出力回路1205に接続された信号線への導出が終了する。20

#### 【0130】

タイミングt36で、第n行目全てのリセットトランジスタ1303が非導通となり、第n行目の長秒露光が割り当てられている列の列転送トランジスタ1304のゲートが導通となる。この結果、被写体からの光から得られたPD1301の電荷がFD1306に完全転送される。

#### 【0131】

タイミングt37で、第n行目の長秒露光が割り当てられている列の列転送トランジスタ1304のゲートが非導通となり、第n列目のトランジスタ1305が導通する。この結果、FD1306の電位が低インピーダンス化されて、第n列目の長秒画素出力VOUT<sub>n-L</sub>として、出力回路1205に接続された信号線へ導出される。更に、第n+1行目全てのリセットトランジスタ1303及び第n+1行目全ての行転送トランジスタ1302のゲートが導通になる。この結果、第n+1行目全てのPD1301の電荷がFD1306に完全転送されてリセットされ、第n+1行目全てのFD1306も第n+1行目のリセットトランジスタ1303のドレイン電位にリセットされる。30

#### 【0132】

タイミングt38で、第n+1行目全ての行転送トランジスタ1302のゲートが非導通になる。この結果、第n+1行目全てのPD1301への電荷の蓄積が開始される。

#### 【0133】

タイミングt39で、第n+1行目のリセットトランジスタ1303が非導通となり、第n+1行目の短秒露光が割り当てられている列の列転送トランジスタ1304のゲートが導通となる。この結果、被写体からの光から得られたPD1301の電荷がFD1306に完全転送される。また、長秒画素出力VOUT<sub>n-L</sub>の出力回路1205に接続された信号線への導出が終了する。

#### 【0134】

タイミングt310で、第n+1行目の短秒露光が割り当てられている列の列転送トランジスタ1304のゲートが非導通となり、第n+1列目のトランジスタ1305が導通する。この結果、FD1306の電位が低インピーダンス化されて、第n+1列目の短秒画素出力VOUT<sub>n+1-s</sub>として、出力回路1205に接続された信号線へ導出される。50

た、出力回路 1205 に接続された信号線へ導出された後、リセットトランジスタ 1303 が導通となる。

**【0135】**

タイミング t311 で、短秒画素出力 VOUT<sub>n+1-s</sub> の出力回路 1205 に接続された信号線への導出が終了する。

**【0136】**

タイミング t312 で、第 n + 1 行目のリセットトランジスタ 1303 が非導通となり、第 n + 1 行目の長秒露光が割り当てられている列の列転送トランジスタ 1304 のゲートが導通となる。この結果、被写体からの光から得られた PD1301 の電荷が FD1306 に完全転送される。

10

**【0137】**

タイミング t313 で、第 n + 1 行目の長秒露光が割り当てられている列の列転送トランジスタ 1304 のゲートが非導通となり、第 n + 1 列目のトランジスタ 1105 が導通すると。この結果、FD1306 の電位が低インピーダンス化されて、第 n + 1 列目の長秒画素出力 VOUT<sub>n+1-s</sub> として、出力回路 1205 に接続された信号線へ導出される。また、出力回路 1205 に接続された信号線へ導出された後、リセットトランジスタ 1303 が導通となる。更に、第 n + 2 行目全てのリセットトランジスタ 1303 及び第 n + 2 行目全ての行転送トランジスタ 1302 のゲートが導通になる。この結果、第 n + 2 行目全ての PD1301 の電荷が FD1306 に完全転送されてリセットされ、第 n + 2 行目全ての FD1306 もリセットトランジスタ 1303 のドレイン電位にリセットされる。

20

**【0138】**

タイミング t314 で、第 n + 2 行目全ての行転送トランジスタ 1302 のゲートが非導通になる。この結果、第 n + 2 行目全ての PD1301 への電荷の蓄積が開始される。

**【0139】**

タイミング t315 で、第 n + 1 行目のリセットトランジスタ 1303 が非導通となり、第 n + 2 行目の短秒露光が割り当てられている列の列転送トランジスタ 1304 のゲートが導通となる。この結果、被写体からの光から得られた PD1301 の電荷が FD1106 に完全転送される。また、長秒画素出力 VOUT<sub>n+1-L</sub> の出力回路 1205 に接続された信号線への導出が終了する。

30

**【0140】**

タイミング t316 で、第 n + 2 行目の短秒露光が割り当てられている列の列転送トランジスタ 1304 のゲートが非導通となり、第 n + 2 列目のトランジスタ 1305 が導通する。この結果、FD1306 の電位が低インピーダンス化されて、第 n + 2 列目の短秒画素出力 VOUT<sub>n+2-s</sub> として、出力回路 1205 に接続された信号線へ導出される。また、出力回路 1205 に接続された信号線へ導出された後、リセットトランジスタ 1303 が導通となる。

**【0141】**

タイミング t317 で、短秒画素出力 VOUT<sub>n+2-s</sub> の出力回路 1205 に接続された信号線への導出が終了する。

40

**【0142】**

タイミング t318 で、第 n + 2 行目のリセットトランジスタ 1303 が非導通となり、第 n + 2 行目の長秒露光が割り当てられている列の列転送トランジスタ 1304 のゲートが導通となる。この結果、被写体からの光から得られた PD1301 の電荷が FD1306 に完全転送される。

**【0143】**

タイミング t319 で、第 n + 2 行目の長秒露光が割り当てられている列の列転送トランジスタ 1304 のゲートが非導通となり、第 n + 2 列目のトランジスタ 1305 が導通すると。この結果、FD1306 の電位が低インピーダンス化されて、第 n + 2 列目の長秒画素出力 VOUT<sub>n+2-L</sub> として、出力回路 1205 に接続された信号線へ導出される。

50

## 【0144】

タイミング  $t_{320}$  で、長秒画素出力  $VOUT_{n+2-L}$  の出力回路 1205 に接続された信号線への導出が終了する。

## 【0145】

<ゲイン演算>

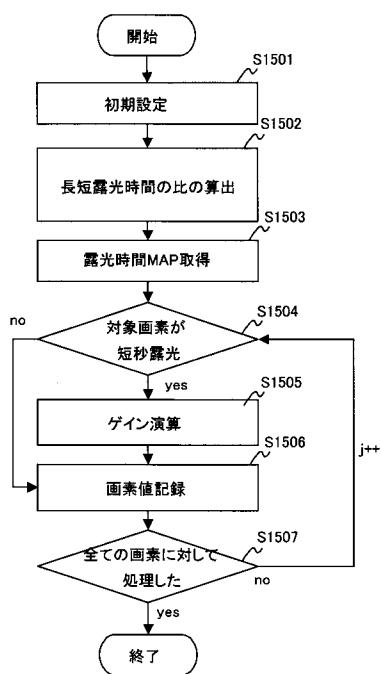

次に、ステップ S206 のゲイン演算について図 15 を参照しながら説明する。図 15 は、ゲイン演算の詳細を示すフローチャートである。

## 【0146】

先ず、ステップ S1501において、ゲイン演算部 105 が初期化動作を行う。例えば、画素番号を表す変数  $j$  への 0 の設定、本撮像結果及び長秒短秒の露光時間の取得、並びにメモリの確保等が行われる。

10

## 【0147】

次いで、ステップ S1502において、ゲイン演算部 105 が、ステップ S1501 で取得した長露光時間  $T_L$  と短露光時間  $T_s$  との比を数 16 から算出する。

## 【0148】

## 【数 16】

$$\alpha = T_L \div T_S$$

## 【0149】

20

その後、ステップ S1503において、ゲイン演算部 105 が、全画素の露光時間  $MAP$  を取得する。

## 【0150】

続いて、ステップ S1504において、ゲイン演算部 105 が、画素番号  $j$  の露光時間が短秒であるかを判定し、短秒であればステップ S1505 へ移行し、そうでなければステップ S1506 へ移行する。

## 【0151】

ステップ S1505 では、画素番号  $j$  の画素値  $P_j$  及び露光時間比に基づいて、数 17 からゲイン演算を行う。

## 【0152】

30

## 【数 17】

$$P_j = \alpha \times P_j$$

## 【0153】

次いで、ステップ S1506において、ゲイン演算部 105 が、画素値  $P_j$  を記録する。

## 【0154】

その後、ステップ S1507において、ゲイン演算部 105 が、全ての画素に対して処理を行ったかを判定し、行っていれば終了に関する処理を行い、そうでなければ画素番号を表す  $j$  に 1 を加えてステップ S1504 へ移行する。

40

## 【0155】

このような第 1 の実施形態では、列転送トランジスタ毎に 2 種類のうちのいずれかの導通タイミングを与えることにより、画素毎の露出時間の長短露出制御が可能である。この際、予備撮像時の被写体の輝度を用いて各画素の露光時間を割り当てることで、白トビ、黒ツブレのない広いダイナミックレンジを得ることができる。また、露光時間での露光量の制御のため、感度を自由に変えることができるため、様々なダイナミックレンジの被写体に対応することができる。更に、一度に広ダイナミックレンジの撮像が取得可能なため、動体撮影であっても、合成による位置ズレ等の問題は解決される。また、固定パターンでの広ダイナミックレンジ撮像と比較して、解像度の低下及び被写体輝度に適さない

50

短秒露光になった際のノイズ増加等の問題を回避することもできる。

#### 【0156】

(第2の実施形態)

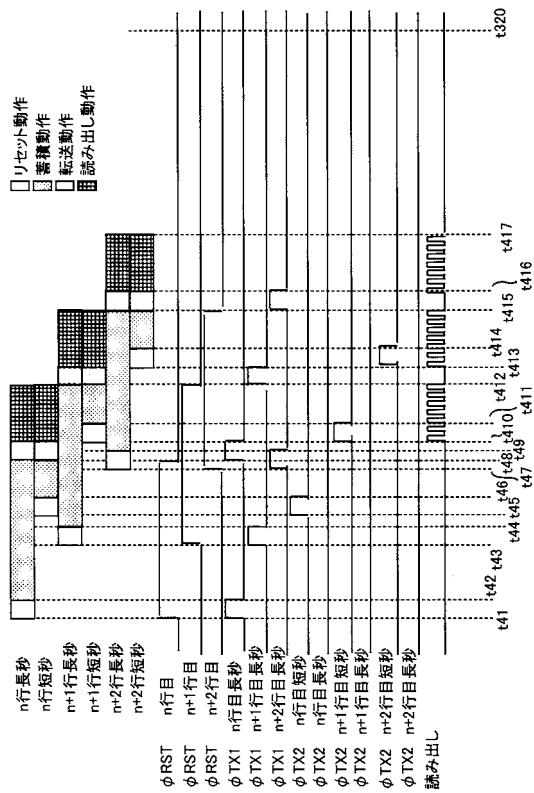

次に、本発明の第2の実施形態について説明する。第2実施形態は、各ラインの各画素に2種類の列転送パルスを送信して長短露光を制御する際に、画素読み出し速度の高速化を実現するためのものである。なお、本実施形態では、2種類のリセットタイミングのうちのいずれかを与えることにより長短露光の制御を実現する。一方は、行転送トランジスタ1302及びリセットトランジスタ1303の組み合わせである。他方は、列転送トランジスタ1304及びリセットトランジスタ1303の組み合わせである。図16は、第2の実施形態における画素1202の駆動方法及びその特性を示す図であり、転送ゲートであるトランジスタ1302及びトランジスタ1304、並びにリセットトランジスタ1303の導通／非導通を制御する駆動方法を示すタイミングチャートである。なお、 $t_4$  ~  $t_{418}$ はタイミングを表す。また、図16に記載のタイミング $t_{320}$ は、第1の実施形態との比較を表すために記載しており、本実施形態における動作のタイミングには関係しない。以降、第1の実施形態との相違点を中心にして説明する。

10

#### 【0157】

先ず、タイミング $t_{41}$ で、第n行目全てのリセットトランジスタ1303、及び第n行目全ての行転送トランジスタ1302のゲートが導通になる。この結果、第n行目全てのPD1301の電荷がFD1306に完全転送されてリセットされ、第n行目全てのFD1306もリセットトランジスタ1303のドレイン電位にリセットされる。

20

#### 【0158】

タイミング $t_{42}$ で、第n行目全ての行転送トランジスタ1302のゲートが非導通になる。この結果、第n行目全てのPD1301への電荷の蓄積が開始される。

#### 【0159】

タイミング $t_{43}$ で、第n+1行目全てのリセットトランジスタ1303、及び第n+1行目全ての行転送トランジスタ1302のゲートが導通になる。この結果、第n+1行目全てのPD1301の電荷がFD1306に完全転送されてリセットされ、第n+1行目全てのFD1306もリセットトランジスタ1303のドレイン電位にリセットされる。

30

#### 【0160】

タイミング $t_{44}$ で、第n+1行目全ての行転送トランジスタ1302のゲートが非導通になる。この結果、第n+1行目全てのPD1301への電荷の蓄積が開始される。

#### 【0161】

タイミング $t_{45}$ で、第n行目の短秒露光が割り当てられている列の列転送トランジスタ1304のゲートが導通となる。この結果、第n行目の短秒露光が割り当てられている列のPD1301の電荷がFD1306に完全転送されてリセットされ、第n行目の短秒露光が割り当てられている列のFD1306もリセットトランジスタ1303のドレイン電位にリセットされる。

#### 【0162】

タイミング $t_{46}$ で、第n行目の短秒露光が割り当てられている列の列転送トランジスタ1304が非導通になる。この結果、第n行目の短秒露光が割り当てられている列のPD1301への電荷の蓄積が開始される。

40

#### 【0163】

タイミング $t_{47}$ で、第n+2行目全てのリセットトランジスタ1303、及び第n+2行目全ての行転送トランジスタ1302のゲートが導通になる。この結果、第n+2行目全てのPD1301の電荷がFD1306に完全転送されてリセットされ、第n+2行目全てのFD1306もリセットトランジスタ1303のドレイン電位にリセットされる。

50

#### 【0164】

タイミング $t_{48}$ で、第n行目全てのリセットトランジスタ1303が非導通となり、

第 n 行目全ての行転送トランジスタ 1302 のゲートが導通となり、被写体からの光が P D 1301 の電荷が F D 1306 に完全転送される。

【0165】

タイミング t 4 9 で、第 n + 2 行目全ての行転送トランジスタ 1302 のゲートが非導通になる。この結果、第 n + 2 行目全ての P D 1301 への電荷の蓄積が開始される。

【0166】

タイミング t 4 1 0 で、第 n 行目全ての行転送トランジスタ 1302 のゲートが非導通となり、第 n 列目のトランジスタ 1305 が導通する。この結果、F D 1306 の電位が低インピーダンス化されて、第 n 列目の画素出力 V O U T<sub>n</sub> として、出力回路 1205 に接続された信号線へ導出される。また、第 n + 1 行目の短秒露光が割り当てられている列の列転送トランジスタ 1304 のゲートが導通となる。この結果、第 n + 1 行目の短秒露光が割り当てられている列の P D 1301 の電荷が F D 1306 に完全転送されてリセットされ、第 n + 1 行目の短秒露光が割り当てられている列の F D 1306 もリセットトランジスタ 1303 のドレイン電位にリセットされる。10

【0167】

タイミング t 4 1 1 で、第 n + 1 行目の短秒露光が割り当てられている列の列転送トランジスタ 1304 が非導通になる。この結果、第 n + 1 行目の短秒露光が割り当てられている列の P D 1301 への電荷の蓄積が開始される。

【0168】

タイミング t 4 1 2 で、第 n + 1 行目全てのリセットトランジスタ 1303 が非導通となり、第 n + 1 行目全ての行転送トランジスタ 1302 のゲートが導通となる。この結果、被写体からの光から得られた P D 1301 の電荷が F D 1306 に完全転送される。20

【0169】

タイミング t 4 1 3 で、第 n + 1 行目全ての行転送トランジスタ 1302 のゲートが非導通となり、第 n + 1 列目全てのトランジスタ 1305 が導通する。この結果、F D 1306 の電位が低インピーダンス化されて、第 n 列目の画素出力 V O U T<sub>n+1</sub> として、出力回路 1205 に接続された信号線へ導出される。また、第 n + 2 行目の短秒露光が割り当てられている列の列転送トランジスタ 1304 のゲートが導通となる。この結果、第 n + 2 行目の短秒露光が割り当てられている列の P D 1301 の電荷が F D 1306 に完全転送されてリセットされ、第 n + 1 行目の短秒露光が割り当てられている列の F D 1306 もリセットトランジスタ 1303 のドレイン電位にリセットされる。30

【0170】

タイミング t 4 1 4 で、第 n + 2 行目の短秒露光が割り当てられている列の列転送トランジスタ 1304 が非導通になる。この結果、第 n + 2 行目の短秒露光が割り当てられている列の P D 1301 への電荷の蓄積が開始される。

【0171】

タイミング t 4 1 5 で、第 n + 2 行目全てのリセットトランジスタ 1303 が非導通となり、第 n + 2 行目全ての行転送トランジスタ 1302 のゲートが導通となる。この結果、被写体からの光から得られた P D 1301 の電荷が F D 1306 に完全転送される。40

【0172】

タイミング t 4 1 6 で、第 n + 2 行目全ての行転送トランジスタ 1302 のゲートが非導通となり、第 n + 2 行目全てのトランジスタ 1305 が導通する。この結果、F D 1306 の電位が低インピーダンス化されて、画素出力 V O U T<sub>n+2</sub> として、出力回路 1205 に接続された信号線へ導出される。

【0173】

タイミング t 4 1 7 で、画素出力 V O U T<sub>n+2</sub> の出力回路 1205 に接続された信号線への導出が終了する。

【0174】

他の構成及び動作は第 1 の実施形態と同様である。

【0175】

このような第2の実施形態では、2種類のリセットタイミングうちのいずれかを与えることにより長短露光の制御を実現することが可能である。この際に、1行につき一度で読み出しできるため、1フレームあたりの読み出し時間を短縮することができる。また、列転送トランジスタの導通制御は1種類でよいため、トランジスタ制御処理にかかる負荷及びメモリを軽減することができる。また、短秒長秒にかかわらず、P D 1 3 0 1の電荷がF D 1 3 0 6に完全転送される前に、必ずF D 1 3 0 6がリセットトランジスタ1 3 0 3のドレイン電位にリセットされるため、露光中にF D 1 3 0 6で発生する可能性があるノイズを除去することができる。

#### 【0176】

(第3の実施形態)

10

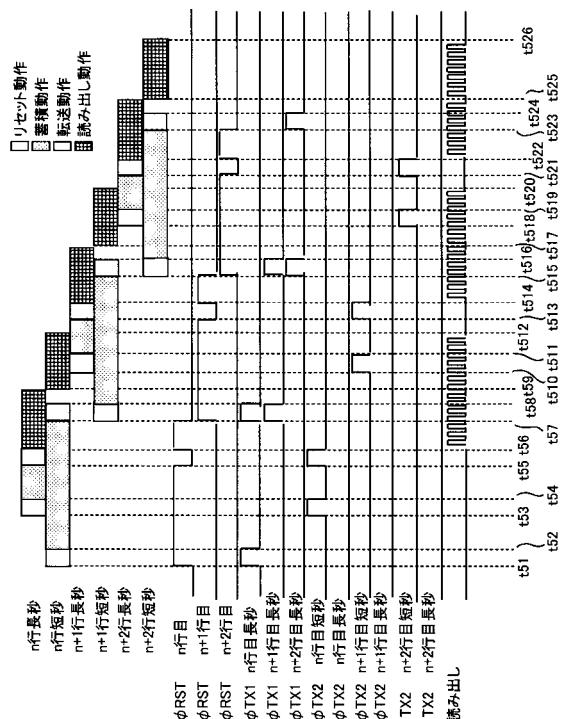

次に、本発明の第3実施形態について説明する。第3の実施形態は、各ラインの各画素に2種類の列転送パルスを送信して長短露光を制御する際に、ライン中の長短露光の時間的な重心を揃えることによって、長短露光間での時間差の軽減を実現するためのものである。なお、本実施形態では、2種類のリセット・読み出し動作のうちのいずれかを与えることにより重心を揃えた長短露光の制御を実現する。一方のリセット・読み出し動作は、行転送トランジスタ1 3 0 2及びリセットトランジスタ1 3 0 3によるリセット並びに行転送トランジスタ1 3 0 2の導通による読み出しの組み合わせである。他方のリセット・読み出し動作は、列転送トランジスタ1 3 0 4及びリセットトランジスタ1 3 0 3によるリセット並びに列転送トランジスタ1 3 0 4の導通による読み出しの組み合わせである。図17は、第3の実施形態における画素1 2 0 2の駆動方法及びその特性を示す図であり、転送ゲートであるトランジスタ1 3 0 2及びトランジスタ1 3 0 4、並びにリセットトランジスタ1 3 0 3の導通／非導通を制御する駆動方法を示すタイミングチャートである。なおt 5 1～t 5 2 6はタイミングを表す。以降、第1の実施形態との相違点を中心にして説明する。

20

#### 【0177】

先ず、タイミングt 5 1で、第n行目全てのリセットトランジスタ1 3 0 3、及び第n行目全ての行転送トランジスタ1 3 0 2のゲートが導通になる。この結果、第n行目全てのP D 1 3 0 1の電荷がF D 1 3 0 6に完全転送されてリセットされ、第n行目全てのF D 1 3 0 6もリセットトランジスタ1 3 0 3のドレイン電位にリセットされる。

#### 【0178】

30

タイミングt 5 2で、第n行目全ての行転送トランジスタ1 3 0 2のゲートが非導通になる。この結果、第n行目全てのP D 1 3 0 1への電荷の蓄積が開始される。

#### 【0179】

タイミングt 5 3で、第n行目の短秒露光が割り当てられている列の列転送トランジスタ1 3 0 4のゲートが導通となる。この結果、第n行目の短秒露光が割り当てられている列のP D 1 3 0 1の電荷がF D 1 3 0 6に完全転送されてリセットされ、第n行目の短秒露光が割り当てられている列のF D 1 3 0 6もリセットトランジスタ1 3 0 3のドレイン電位にリセットされる。

#### 【0180】

40

タイミングt 5 4で、第n行目の短秒露光が割り当てられている列の列転送トランジスタ1 3 0 4のゲートが非導通になる。この結果、第n行目の短秒露光が割り当てられている列のP D 1 3 0 1への電荷の蓄積が開始される。

#### 【0181】

タイミングt 5 5で、第n行目の短秒露光が割り当てられている列のリセットトランジスタが非導通となり、第n行目の短秒露光が割り当てられている列の列転送トランジスタ1 3 0 4が導通になる。この結果、被写体からの光から得られたP D 1 3 0 1の電荷がF D 1 3 0 6に完全転送される。

#### 【0182】

タイミングt 5 6で、第n行目の短秒露光が割り当てられている列の列転送トランジスタ1 3 0 4のゲートが非導通となり、第n列目のトランジスタ1 3 0 5が導通する。この

50

結果、 $F D 1 3 0 6$  の電位が低インピーダンス化されて、第  $n$  列目の短秒画素出力  $V O U T_{n-s}$  として、出力回路 1205 に接続された信号線へ導出される。また、出力回路 1205 に接続された信号線へ導出された後、第  $n$  行目全てのリセットトランジスタ 1303 が導通となる。

#### 【0183】

タイミング  $t_{57}$  で、第  $n$  行目の長秒露光が割り当てられている列のリセットトランジスタが非導通となり、第  $n$  行目の長秒露光が割り当てられている列の行転送トランジスタ 1304 が導通になる。この結果、被写体からの光が  $P D 1 3 0 1$  の電荷が  $F D 1 3 0 6$  に完全転送される。また、第  $n+1$  行目全てのリセットトランジスタ 1303、及び第  $n+1$  行目全ての行転送トランジスタ 1302 のゲートが導通になる。この結果、第  $n+1$  行目全ての  $P D 1 3 0 1$  の電荷が  $F D 1 3 0 6$  に完全転送されてリセットされ、第  $n+1$  行目全ての  $F D 1 3 0 6$  もリセットトランジスタ 1303 のドレイン電位にリセットされる。10

#### 【0184】

タイミング  $t_{58}$  で、第  $n$  行目の長秒露光が割り当てられている列の行転送トランジスタ 1304 のゲートが非導通となる。また、第  $n+1$  行目全ての行転送トランジスタ 1302 のゲートが非導通になる。この結果、第  $n+1$  行目全ての  $P D 1 3 0 1$  への電荷の蓄積が開始される。

#### 【0185】

タイミング  $t_{59}$  で、短秒画素出力  $V O U T_{n-s}$  の出力回路 1205 に接続された信号線への導出が終了する。また、第  $n$  列目のトランジスタ 1305 が導通する。この結果、 $F D 1 3 0 6$  の電位が低インピーダンス化されて、第  $n$  列目の長秒画素出力  $V O U T_{n-L}$  として、出力回路 1205 に接続された信号線へ導出される。20

#### 【0186】

タイミング  $t_{510}$  で、第  $n+1$  行目の短秒露光が割り当てられている列の行転送トランジスタ 1304 のゲートが導通となる。この結果、第  $n+1$  行目の短秒露光が割り当てられている列の  $P D 1 3 0 1$  の電荷が  $F D 1 3 0 6$  に完全転送されてリセットされ、第  $n+1$  行目の短秒露光が割り当てられている列の  $F D 1 3 0 6$  もリセットトランジスタ 1303 のドレイン電位にリセットされる。

#### 【0187】

タイミング  $t_{511}$  で、第  $n+1$  行目の短秒露光が割り当てられている列の行転送トランジスタ 1304 のゲートが非導通になる。この結果、第  $n+1$  行目の短秒露光が割り当てられている列の  $P D 1 3 0 1$  への電荷の蓄積が開始される。30

#### 【0188】

タイミング  $t_{512}$  で、長秒画素出力  $V O U T_{n-L}$  の出力回路 1205 に接続された信号線への導出が終了する。

#### 【0189】

タイミング  $t_{513}$  で、第  $n+1$  行目の短秒露光が割り当てられている列のリセットトランジスタが非導通となり、第  $n+1$  行目の短秒露光が割り当てられている列の行転送トランジスタ 1304 が導通になる。この結果、被写体からの光から得られた  $P D 1 3 0 1$  の電荷が  $F D 1 3 0 6$  に完全転送される。40

#### 【0190】

タイミング  $t_{514}$  で、第  $n+1$  行目の短秒露光が割り当てられている列の行転送トランジスタ 1304 のゲートが非導通となり、第  $n+1$  列目のトランジスタ 1305 が導通する。この結果、 $F D 1 3 0 6$  の電位が低インピーダンス化されて、第  $n$  列目の短秒画素出力  $V O U T_{n+1-s}$  として、出力回路 1205 に接続された信号線へ導出される。また、出力回路 1205 に接続された信号線へ導出された後、第  $n$  行目全てのリセットトランジスタ 1303 が導通となる。

#### 【0191】

タイミング  $t_{515}$  で、第  $n+1$  行目の長秒露光が割り当てられている列のリセットト50

ランジスタが非導通となり、第  $n + 1$  行目の長秒露光が割り当てられている列の列転送トランジスタ 1304 が導通になる。この結果、被写体からの光から得られた P D 1301 の電荷が F D 1306 に完全転送される。また、第  $n + 2$  行目全てのリセットトランジスタ 1303、及び第  $n + 2$  行目全ての行転送トランジスタ 1302 のゲートが導通になる。この結果、第  $n + 2$  行目全ての P D 1301 の電荷が F D 1306 に完全転送されてリセットされ、第  $n + 2$  行目全ての F D 1306 もリセットトランジスタ 1303 のドレイン電位にリセットされる。

#### 【0192】

タイミング t 516 で、第  $n + 1$  行目の長秒露光が割り当てられている列の列転送トランジスタ 1304 のゲートが非導通となる。また、第  $n + 2$  行目全ての行転送トランジスタ 1302 のゲートが非導通になる。この結果、第  $n + 2$  行目全ての P D 1301 への電荷の蓄積が開始される。10

#### 【0193】

タイミング t 517 で、短秒画素出力 V O U T <sub>$n+1-s$</sub>  の出力回路 1205 に接続された信号線への導出が終了する。また、第  $n + 1$  列目のトランジスタ 1305 が導通する。この結果、F D 1306 の電位が低インピーダンス化されて、第  $n + 1$  列目の長秒画素出力 V O U T <sub>$n+1-L$</sub>  として、出力回路 1205 に接続された信号線へ導出される。

#### 【0194】

タイミング t 518 で、第  $n + 2$  行目の短秒露光が割り当てられている列の列転送トランジスタ 1304 のゲートが導通となる。この結果、第  $n + 1$  行目の短秒露光が割り当てられている列の P D 1301 の電荷が F D 1306 に完全転送されてリセットされ、第  $n + 1$  行目の短秒露光が割り当てられている列の F D 1306 もリセットトランジスタ 1303 のドレイン電位にリセットされる。20

#### 【0195】

タイミング t 519 で、第  $n + 2$  行目の短秒露光が割り当てられている列の列転送トランジスタ 1304 のゲートが非導通になる。この結果、第  $n + 2$  行目の短秒露光が割り当てられている列の P D 1301 への電荷の蓄積が開始される。

#### 【0196】

タイミング t 520 で、長秒画素出力 V O U T <sub>$n+1-L$</sub>  の出力回路 1205 に接続された信号線への導出が終了する。30

#### 【0197】

タイミング t 521 で、第  $n + 2$  行目の短秒露光が割り当てられている列のリセットトランジスタが非導通となり、第  $n + 2$  行目の短秒露光が割り当てられている列の列転送トランジスタ 1304 が導通になる。この結果、被写体からの光から得られた P D 1301 の電荷が F D 1306 に完全転送される。

#### 【0198】

タイミング t 522 で、第  $n + 2$  行目の短秒露光が割り当てられている列の列転送トランジスタ 1304 のゲートが非導通となり、第  $n + 2$  列目のトランジスタ 1305 が導通する。この結果、F D 1306 の電位が低インピーダンス化されて、第  $n + 2$  列目の短秒画素出力 V O U T <sub>$n+2-s$</sub>  として、出力回路 1205 に接続された信号線へ導出される。また、出力回路 1205 に接続された信号線へ導出された後、第  $n + 2$  行目全てのリセットトランジスタ 1303 が導通となる。40

#### 【0199】

タイミング t 523 で、第  $n + 2$  行目の長秒露光が割り当てられている列のリセットトランジスタが非導通となり、第  $n + 2$  行目の長秒露光が割り当てられている列の列転送トランジスタ 1304 が導通になる。この結果、被写体からの光から得られた P D 1301 の電荷が F D 1306 に完全転送される。

#### 【0200】

タイミング t 524 で、第  $n + 2$  行目の長秒露光が割り当てられている列の列転送トランジスタ 1304 のゲートが非導通となる。50

## 【0201】

タイミング t<sub>525</sub>で、短秒画素出力 V<sub>O U T<sub>n+2-s</sub></sub>の出力回路 1205 に接続された信号線への導出が終了する。また、第 n + 2 列目のトランジスタ 1305 が導通する。この結果、F D 1306 の電位が低インピーダンス化されて、第 n + 2 列目の長秒画素出力 V<sub>O U T<sub>n+1-L</sub></sub>として、出力回路 1205 に接続された信号線へ導出される。

## 【0202】

タイミング t<sub>526</sub>で、長画素出力 V<sub>O U T<sub>n+2-L</sub></sub>の出力回路 1205 に接続された信号線への導出が終了する。

## 【0203】

他の構成及び動作は第 1 の実施形態と同様である。

10

## 【0204】

このような第 3 の実施形態では、電荷蓄積期間内にリセットトランジスタ及び列転送トランジスタを導通することで、画素毎の短秒露光の開始時間を制御することが可能である。また、列転送トランジスタを導通することで、画素毎の短秒露光の終了時間の制御が可能となる。更に、露光開始時間及び露光終了時間の双方を制御すれば、自由に露光時間を制御することが可能となる。例えば、長秒短秒の露光時間の重心を合わせた制御が可能である。つまり、所定のリセットと所定の転送との間の時間間隔を一致させた制御が可能である。これによって、同一ライン中の時間ズレを解消することができる。また、列転送トランジスタの導通制御は 1 種類でよいため、トランジスタ制御処理にかかる負荷及びメモリを軽減することができる。

20

## 【0205】

## (第 4 の実施形態)

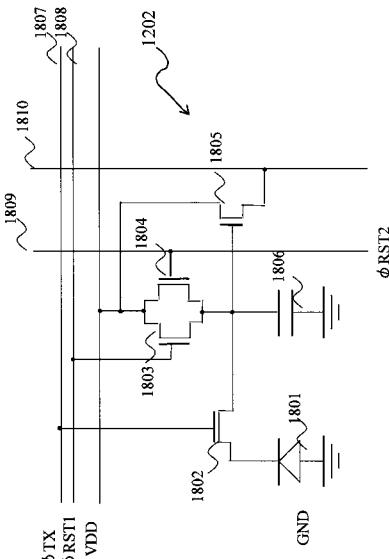

次に、本発明の第 4 の実施形態について説明する。第 4 の実施形態では、画素 1202 の構成及び駆動方法が第 1 の実施形態と相違している。図 18 は、第 4 の実施形態における画素 1202 の構造の一例を示す回路図である。

## 【0206】

画素 1202 には、受光素子である埋め込み型 P D ( フォトダイオード ) 1801、及び N チャンネル M O S トランジスタ 1802 ~ 1805 が含まれている。トランジスタ 1802 及びトランジスタ 1804 のドレイン、並びにトランジスタ 1803 及びトランジスタ 1804 のソースの接続部は F D ( フローティングディフュージョン ) 1806 で構成されている。行選択線 1807、行信号線 1808、列信号線 1809 及び列信号線 1810 は各トランジスタに対する信号を伝送し、図 18 中の V D D は電源、G N D は接地を示す。なお、信号が H ( H i g h ) であれば各ゲートが導通し、L ( L o w ) ならば非導通になるように構成されている。

30

## 【0207】

P D 1801 は光電変換部 ( 受光部 ) であり、被写体からの入射光量に応じた電荷を蓄積し、蓄積した信号電荷が転送ゲートとよばれる行転送トランジスタ 1802 によって F D 1806 に完全転送されることで出力される。転送された信号電荷は、蓄積部として機能する F D 1806 に一時的に蓄積される。なお、行転送トランジスタ 1802 の電位を T X で表す。

40

## 【0208】

トランジスタ 1803 は行リセットトランジスタとよばれ、トランジスタ 1803 が導通することによって F D 1806 が既定の電位 ( R S B 1 ) にリセットされる。トランジスタ 1804 は列リセットトランジスタとよばれ、トランジスタ 1804 が導通することによって F D 1806 が既定の電位 ( R S B 2 ) にリセットされる。これらのリセット動作の際に、リセットノイズとよばれる、リセット動作を行う毎に F D 1806 の電位が R S B に対してばらつくノイズが発生することがある。

## 【0209】

トランジスタ 1805 は、ソースフォロワ增幅回路を構成し、F D 1806 の電位 V F D に対する電流増幅を行うことで、出力インピーダンスを下げる。また、トランジスタ 1

50

805のドレインは列信号線1810に接続されており、低インピーダンス化されて、画素出力VOOUTとして、列信号線1810へ導出される。

#### 【0210】

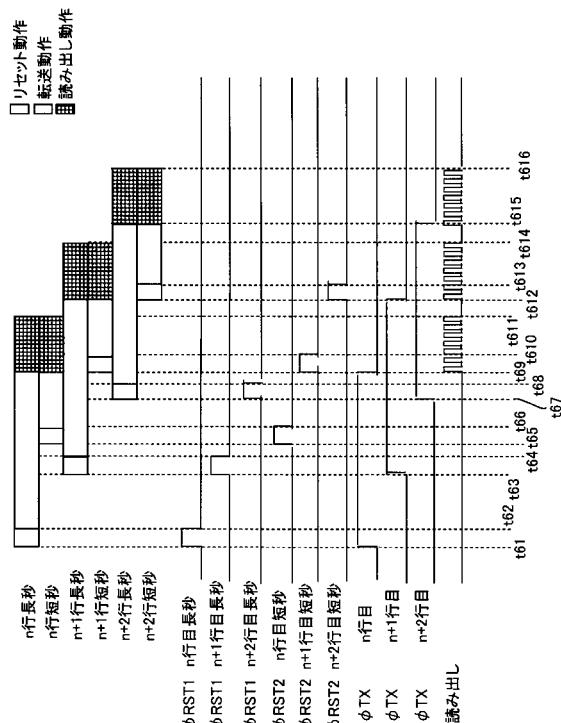

本実施形態では、第2の実施形態と同様に、2種類のリセットタイミングのうちのいずれかを与えることにより長短露光の制御を実現する。一方は、行転送トランジスタ1802及び行リセットトランジスタ1803の組み合わせである。他方は、行転送トランジスタ1802及び列リセットトランジスタ1804の組み合わせである。図19は、第4の実施形態における画素1202の駆動方法及びその特性を示す図である。この図19は、転送ゲートであるトランジスタ1802、行リセットトランジスタ1803、及び列リセットトランジスタ1804の導通／非導通を制御する駆動方法を示すタイミングチャートである。なお、 $t_{61} \sim t_{618}$ はタイミングを表す。

10

#### 【0211】

本実施形態では、タイミング $t_{61}$ で、第n行目全ての行リセットトランジスタ1803、及び第n行目全ての行転送トランジスタ1802のゲートが導通になる。この結果、第n行目全てのPD1801の電荷がFD1806に完全転送されてリセットされ、第n行目全てのFD1806もリセットトランジスタ1803のドレイン電位にリセットされる。

20

#### 【0212】

タイミング $t_{62}$ で、第n行目全ての行リセットトランジスタ1803のゲートが非導通になる。この結果、第n行目全てのPD1801の電荷がFD1806に転送され始める。

#### 【0213】

タイミング $t_{63}$ で、第 $n+1$ 行目全てのリセットトランジスタ1803、及び第 $n+1$ 行目全ての行転送トランジスタ1802のゲートが導通になる。この結果、第 $n+1$ 行目全てのPD1801の電荷がFD1806に完全転送されてリセットされ、第 $n+1$ 行目全てのFD1806もリセットトランジスタ1803のドレイン電位にリセットされる。

#### 【0214】

タイミング $t_{64}$ で、第 $n+1$ 行目全ての行リセットトランジスタ1803のゲートが非導通になる。この結果、第 $n+1$ 行目全てのPD1801の電荷がFD1806に転送され始める。

30

#### 【0215】

タイミング $t_{65}$ で、第n行目の短秒露光が割り当てられている列のリセットトランジスタ1804のゲートが導通となる。この結果、第n行目の短秒露光が割り当てられている列のFD1806の電荷がリセットトランジスタ1803のドレイン電位にリセットされる。

#### 【0216】

タイミング $t_{66}$ で、第n行目の短秒露光が割り当てられている列の列リセットトランジスタ1804が非導通になる。この結果、第n行目の短秒露光が割り当てられている列の電荷がFD1806に転送され始める。

40

#### 【0217】

タイミング $t_{67}$ で、第 $n+2$ 行目全てのリセットトランジスタ1803、及び第 $n+2$ 行目全ての行転送トランジスタ1802のゲートが導通になる。この結果、第 $n+2$ 行目全てのPD1801の電荷がFD1806に完全転送されてリセットされ、第 $n+2$ 行目全てのFD1806もリセットトランジスタ1803のドレイン電位にリセットされる。

#### 【0218】

タイミング $t_{68}$ で、第 $n+2$ 行目全ての行リセットトランジスタ1803のゲートが非導通になる。この結果、第 $n+2$ 行目全てのPD1801の電荷がFD1806に転送され始める。

50

## 【0219】

タイミング  $t_{6\ 9}$  で、第  $n$  行目全ての行転送トランジスタ  $1802$  のゲートが非導通となり、第  $n$  列目のトランジスタ  $1805$  が導通する。この結果、 $FD1806$  の電位が低インピーダンス化されて、第  $n$  列目の画素出力  $VOUT_n$  として、出力回路  $1205$  に接続された信号線へ導出される。また、第  $n+1$  行目の短秒露光が割り当てられている列のリセットトランジスタ  $1804$  のゲートが導通となる。この結果、第  $n+1$  行目の短秒露光が割り当てられている列の  $FD1806$  の電荷がリセットトランジスタ  $1803$  のドレイン電位にリセットされる。

## 【0220】

タイミング  $t_{6\ 10}$  で、第  $n+1$  行目の短秒露光が割り当てられている列のリセットトランジスタ  $1804$  が非導通になる。この結果、第  $n+1$  行目の短秒露光が割り当てられている列の電荷が  $FD1806$  に転送され始める。10

## 【0221】

タイミング  $t_{6\ 11}$  で、画素出力  $VOUT_n$  の出力回路  $1205$  に接続された信号線への導出が終了する。

## 【0222】

タイミング  $t_{6\ 12}$  で、第  $n+1$  行目全ての行転送トランジスタ  $1802$  のゲートが非導通となり、第  $n+1$  列目のトランジスタ  $1805$  が導通する。この結果、 $FD1806$  の電位が低インピーダンス化されて、第  $n$  列目の画素出力  $VOUT_{n+1}$  として、出力回路  $1205$  に接続された信号線へ導出される。また、第  $n+2$  行目の短秒露光が割り当てられている列のリセットトランジスタ  $1804$  のゲートが導通となる。この結果、第  $n+2$  行目の短秒露光が割り当てられている列の  $FD1806$  の電荷がリセットトランジスタ  $1803$  のドレイン電位にリセットされる。20

## 【0223】

タイミング  $t_{6\ 13}$  で、第  $n+2$  行目の短秒露光が割り当てられている列のリセットトランジスタ  $1804$  が非導通になる。この結果、第  $n+2$  行目の短秒露光が割り当てられている列の電荷が  $FD1806$  に転送され始める。

## 【0224】

タイミング  $t_{6\ 14}$  で、画素出力  $VOUT_{n+1}$  の出力回路  $1205$  に接続された信号線への導出が終了する。30

## 【0225】

タイミング  $t_{6\ 15}$  で、第  $n+2$  行目全ての行転送トランジスタ  $1802$  のゲートが非導通となり、第  $n+2$  列目のトランジスタ  $1805$  が導通する。この結果、 $FD1806$  の電位が低インピーダンス化されて、第  $n+2$  列目の画素出力  $VOUT_{n+2}$  として、出力回路  $1205$  に接続された信号線へ導出される。

## 【0226】

タイミング  $t_{6\ 16}$  で、画素出力  $VOUT_{n+2}$  の出力回路  $1205$  に接続された信号線への導出が終了する。

## 【0227】

他の構成及び動作は第 1 の実施形態と同様である。40

## 【0228】

このような第 4 の実施形態では、第 2 の実施形態と同様に、2 種類のリセットタイミングうちのいずれかを与えることにより長短露光の制御を実現することが可能である。また、この際に、1 行につき一度で画素出力  $VOUT$  を導出できるため、1 フレームあたりの読み出し時間を短縮することができる。

## 【0229】

(第 5 の実施形態)

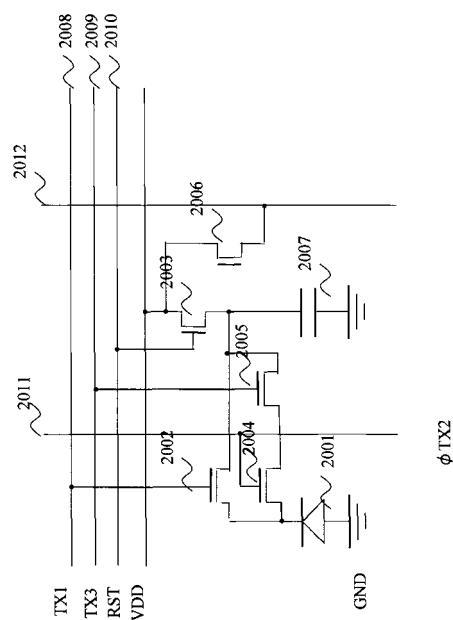

次に、本発明の第 5 の実施形態について説明する。第 5 の実施形態では、画素  $1202$  の構成及び駆動方法が第 1 の実施形態と相違している。図 20 は、第 5 の実施形態における画素  $1202$  の構造の一例を示す回路図である。50

## 【0230】

画素1202には、受光素子である埋め込み型PD（フォトダイオード）2001、及びNチャンネルMOSトランジスタ2002～2006が含まれている。トランジスタ2002及びトランジスタ2005のドレイン、並びにトランジスタ2003のソースの接続部はFD（フローティングディフェュージョン）2007で構成されている。行信号線2008、行信号線2009、行選択線2010、列信号線2011及び列信号線2012は各トランジスタに対する信号を示し、図20中のVDDは電源、GNDは接地を示す。なお、信号がH（High）であれば各ゲートが導通し、L（Low）ならば非導通になるように構成されている。

## 【0231】

PD2001は光電変換部（受光部）であり、被写体からの入射光量に応じた電荷を蓄積し、蓄積した信号電荷が転送ゲートとよばれる行転送トランジスタ2002によってFD2007に完全転送されるか、列転送トランジスタ2004及び行転送トランジスタ2005が同時に導通することによってFD2007に完全転送されることで出力される。転送された信号電荷は、蓄積部として機能するFD2007に一時的に蓄積される。なお、行転送トランジスタ2002の電位をTX1、列転送トランジスタ2004の電位をTX2、行転送トランジスタ2005の電位をTX3で表す。

## 【0232】

トランジスタ2003は行リセットトランジスタとよばれ、トランジスタ2003が導通することによってFD2007が既定の電位（RST1）にリセットされる。トランジスタ2006は、ソースフォロワ增幅回路を構成し、FD2007の電位VFDに対する電流増幅を行うことで、出力インピーダンスを下げる。また、トランジスタ2006のドレインは列信号線2012に接続されており、低インピーダンス化されて、画素出力VOUTとして、列信号線2012へ導出される。

## 【0233】

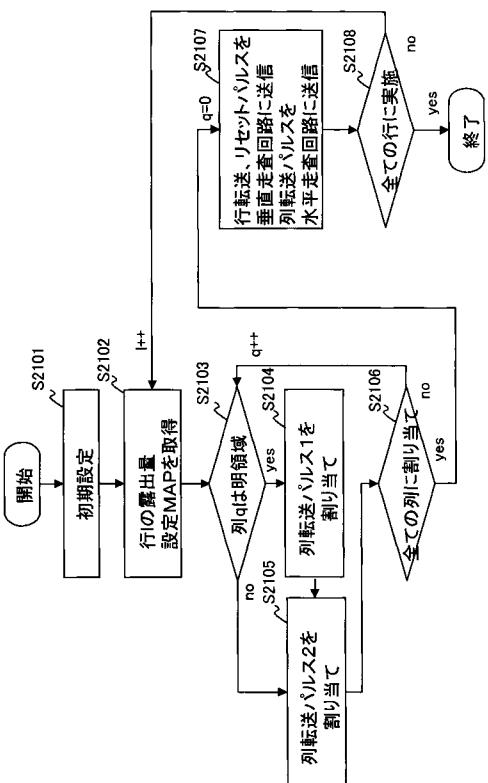

## &lt;駆動パルス生成処理&gt;

次に、本実施形態におけるステップS804の駆動パルス生成処理について図21を参考しながら説明する。図21は、第5の実施形態における駆動パルス生成処理の詳細を示すフローチャートである。

## 【0234】

先ず、ステップS2101において、タイミングジェネレータ部507が初期化動作を行う。例えば、行を表す変数1、列を表す変数qを夫々0に設定する等の動作が行われる。

## 【0235】

次いで、ステップS2102において、タイミングジェネレータ部507が、第1行目の全ての露出量設定MAPの値を読み込む。

## 【0236】

その後、ステップS2103において、タイミングジェネレータ部507が、第q列目のシャッタースピードが明領域のシャッタースピードであるか判断し、そうであればステップS2104へ移行し、そうでなければステップS2105へ移行する。

## 【0237】

ステップS2104では、タイミングジェネレータ部507が、第1行第q列目の画素に対し、明領域のシャッタースピードに対応する後述の列転送トランジスタ2004の駆動パルスTX2、行転送トランジスタ2005の駆動パルスTX3、及びリセットトランジスタ2003の駆動パルスRSTを割り当てる。ステップS2105では、タイミングジェネレータ部507が、第1行第q列目の画素に対し、行転送トランジスタ2002の駆動パルスTX1を割り当てる。

## 【0238】

ステップS2104又はS2105の後、ステップS2106において、タイミングジェネレータ部507が、行中の全ての列について割り当てが行われたかを判定する。そし

10

20

30

40

50

て、行われていれば列を表す変数 q を 0 に設定してステップ S 2 1 0 7 へ移行し、そうでなければ列を表す変数 q に 1 を加えてステップ S 2 1 0 3 へ移行する。

#### 【 0 2 3 9 】

ステップ S 2 1 0 7 では、タイミングジェネレータ部 5 0 7 が、ステップ S 2 1 0 4 又はステップ S 2 1 0 5 の結果に従って、第 1 行目の画素に対し、行転送トランジスタ 2 0 0 2 、行転送トランジスタ 2 0 0 5 、リセットトランジスタ 2 0 0 3 の駆動パルスを生成し、これらを垂直走査回路に送信する。また、タイミングジェネレータ部 5 0 7 は、列転送トランジスタ 2 0 0 4 の駆動パルスを生成し、これを水平走査回路に送信する。

#### 【 0 2 4 0 】

ステップ S 2 1 0 8 では、タイミングジェネレータ部 5 0 7 が、全ての行に対して駆動パルスの送信が行われているかを判定し、行われていれば終了に関する処理を行い、そうでなければ行を表す変数 1 に 1 を加えてステップ S 2 1 0 2 へ移行する。

#### 【 0 2 4 1 】

次に、ライン内の各画素に 2 種類の行転送パルスと、列転送パルスを送信して長短露光を制御する方法について、図 2 2 を参照しながら説明する。本実施形態でも、2 種類のリセットタイミングうちいずれかを与えることにより長短露光の制御を実現する。一方は、行転送トランジスタ 2 0 0 2 及びリセットトランジスタ 2 0 0 3 の組み合わせである。他方は、列転送トランジスタ 2 0 0 4 及び行転送トランジスタ 2 0 0 5 とリセットトランジスタ 2 0 0 3 の組み合わせである。図 2 2 は、第 5 の実施形態における画素 1 2 0 2 の駆動方法及びその特性を示す図である。この図 2 2 は、行転送トランジスタ 2 0 0 2 、列転送トランジスタ 2 0 0 4 、行転送トランジスタ 2 0 0 5 、及びリセットトランジスタ 2 0 0 3 の導通 / 非導通を制御する駆動方法を示すタイミングチャートである。なお、t 6 1 ~ t 6 1 8 はタイミングを表す。

#### 【 0 2 4 2 】

先ず、タイミング t 6 1 で、第 n 行目全てのリセットトランジスタ 2 0 0 3 、及び第 n 行目全ての行転送トランジスタ 2 0 0 2 のゲートが導通になる。この結果、第 n 行目全ての P D 2 0 0 1 の電荷が F D 2 0 0 7 に完全転送されてリセットされ、第 n 行目全ての F D 2 0 0 7 もリセットトランジスタ 2 0 0 3 のドレイン電位にリセットされる。

#### 【 0 2 4 3 】

タイミング t 6 2 で、第 n 行目全ての行転送トランジスタ 2 0 0 2 のゲートが非導通になる。この結果、第 n 行目全ての P D 2 0 0 1 への電荷の蓄積が開始される。

#### 【 0 2 4 4 】

タイミング t 6 3 で、第 n + 1 行目全てのリセットトランジスタ 2 0 0 3 、及び第 n + 1 行目全ての行転送トランジスタ 2 0 0 2 のゲートが導通になる。この結果、第 n + 1 行目全ての P D 2 0 0 1 の電荷が F D 2 0 0 7 に完全転送されてリセットされ、第 n + 1 行目全ての F D 2 0 0 7 もリセットトランジスタ 2 0 0 3 のドレイン電位にリセットされる。

。

#### 【 0 2 4 5 】

タイミング t 6 4 で、第 n + 1 行目全ての行転送トランジスタ 2 0 0 2 のゲートが非導通になる。この結果、第 n + 1 行目全ての P D 2 0 0 1 への電荷の蓄積が開始される。

#### 【 0 2 4 6 】

タイミング t 6 5 で、第 n + 2 行目全てのリセットトランジスタ 2 0 0 3 、及び第 n + 2 行目全ての行転送トランジスタ 2 0 0 2 のゲートが導通になる。この結果、第 n + 2 行目全ての P D 2 0 0 1 の電荷が F D 2 0 0 7 に完全転送されてリセットされ、第 n + 2 行目全ての F D 2 0 0 7 もリセットトランジスタ 2 0 0 3 のドレイン電位にリセットされる。

。

#### 【 0 2 4 7 】

タイミング t 6 6 で、第 n + 2 行目全ての行転送トランジスタ 2 0 0 2 のゲートが非導通になる。この結果、第 n + 2 行目全ての P D 2 0 0 1 への電荷の蓄積が開始される。

#### 【 0 2 4 8 】

10

20

30

40

50

タイミング  $t_{6\ 7}$  で、第  $n$  行目全てのリセットトランジスタ  $2\ 0\ 0\ 3$  及び行転送トランジスタ  $2\ 0\ 0\ 5$ 、並びに短秒露光が割り当てられている第  $m$  列目の列転送トランジスタ  $2\ 0\ 0\ 4$  のゲートが導通となる。この結果、被写体からの光である  $P\ D\ 2\ 0\ 0\ 1$  の電荷が  $F\ D\ 2\ 0\ 0\ 7$  に完全転送されリセットされる。

#### 【0249】

タイミング  $t_{6\ 8}$  で、第  $n$  行目全てのリセットトランジスタ  $2\ 0\ 0\ 3$  及び行転送トランジスタ  $2\ 0\ 0\ 5$ 、並びに短秒露光が割り当てられている第  $m$  列目の列転送トランジスタ  $2\ 0\ 0\ 4$  のゲートが非導通となる。この結果、 $P\ D\ 2\ 0\ 0\ 1$  への電荷の蓄積が再び開始される。

#### 【0250】

タイミング  $t_{6\ 9}$  で、第  $n + 1$  行目全てのリセットトランジスタ  $2\ 0\ 0\ 3$  及び行転送トランジスタ  $2\ 0\ 0\ 5$ 、並びに短秒露光が割り当てられている第  $m$  列目の列転送トランジスタ  $2\ 0\ 0\ 4$  のゲートが導通となる。この結果、被写体からの光である  $P\ D\ 2\ 0\ 0\ 1$  の電荷が  $F\ D\ 2\ 0\ 0\ 7$  に完全転送されリセットされる。

#### 【0251】

タイミング  $t_{6\ 1\ 0}$  で、第  $n + 1$  行目全てのリセットトランジスタ  $2\ 0\ 0\ 3$  及び行転送トランジスタ  $2\ 0\ 0\ 5$ 、並びに短秒露光が割り当てられている第  $m$  列目の列転送トランジスタ  $2\ 0\ 0\ 4$  のゲートが非導通となる。この結果、 $P\ D\ 2\ 0\ 0\ 1$  への電荷の蓄積が再び開始される。

#### 【0252】

タイミング  $t_{6\ 1\ 1}$  で、第  $n + 2$  行目全てのリセットトランジスタ  $2\ 0\ 0\ 3$  及び行転送トランジスタ  $2\ 0\ 0\ 5$ 、並びに短秒露光が割り当てられている第  $m$  列目の列転送トランジスタ  $2\ 0\ 0\ 4$  のゲートが導通となる。この結果、被写体からの光である  $P\ D\ 2\ 0\ 0\ 1$  の電荷が  $F\ D\ 2\ 0\ 0\ 7$  に完全転送されリセットされる。

#### 【0253】

タイミング  $t_{6\ 1\ 2}$  で、第  $n + 2$  行目全てのリセットトランジスタ  $2\ 0\ 0\ 3$  及び行転送トランジスタ  $2\ 0\ 0\ 5$ 、並びに短秒露光が割り当てられている第  $m$  列目の列転送トランジスタ  $2\ 0\ 0\ 4$  のゲートが非導通となる。この結果、 $P\ D\ 2\ 0\ 0\ 1$  への電荷の蓄積が再び開始される。

#### 【0254】

タイミング  $t_{6\ 1\ 3}$  で、第  $n$  行目全ての行転送トランジスタ  $2\ 0\ 0\ 2$  が導通となり、被写体からの光である  $P\ D\ 2\ 0\ 0\ 1$  の電荷が  $F\ D\ 2\ 0\ 0\ 7$  に完全転送される。

#### 【0255】

タイミング  $t_{6\ 1\ 4}$  で、第  $n$  行目全てのトランジスタ  $2\ 0\ 0\ 6$  が導通する。この結果、 $F\ D\ 2\ 0\ 0\ 7$  の電位が低インピーダンス化されて、画素出力  $V\ O\ U\ T\ n$  として、出力回路  $1\ 2\ 0\ 5$  に接続された信号線へ導出される。

#### 【0256】

タイミング  $t_{6\ 1\ 5}$  で、第  $n + 1$  行目全ての行転送トランジスタ  $2\ 0\ 0\ 2$  が導通となり、被写体からの光である  $P\ D\ 2\ 0\ 0\ 1$  の電荷が  $F\ D\ 2\ 0\ 0\ 7$  に完全転送される。

#### 【0257】

タイミング  $t_{6\ 1\ 6}$  で、第  $n + 1$  行目全てのトランジスタ  $2\ 0\ 0\ 6$  が導通する。この結果、 $F\ D\ 2\ 0\ 0\ 7$  の電位が低インピーダンス化されて、画素出力  $V\ O\ U\ T\ n + 1$  として、出力回路  $1\ 2\ 0\ 5$  に接続された信号線へ導出される。

#### 【0258】

タイミング  $t_{6\ 1\ 7}$  で、第  $n + 2$  行目全ての行転送トランジスタ  $2\ 0\ 0\ 2$  が導通となり、被写体からの光である  $P\ D\ 2\ 0\ 0\ 1$  の電荷が  $F\ D\ 2\ 0\ 0\ 7$  に完全転送される。

#### 【0259】

タイミング  $t_{6\ 1\ 8}$  で、第  $n + 2$  行目全てのトランジスタ  $2\ 0\ 0\ 6$  が導通する。この結果、 $F\ D\ 2\ 0\ 0\ 7$  の電位が低インピーダンス化されて、画素出力  $V\ O\ U\ T\ n + 2$  として、出力回路  $1\ 2\ 0\ 5$  に接続された信号線へ導出される。

10

20

30

40

50

**【0260】**

他の構成及び動作は第1の実施形態と同様である。

**【0261】**

このような第5の実施形態では、第1の行転送トランジスタで構成される導通路、又は列転送トランジスタ及び第2の行転送トランジスタを直列に配した導通路の2種類のうちいずれかの導通タイミングを与えられる。このため、画素毎の露出時間の長短露出制御が可能である。

**【0262】****(第6の実施形態)**

次に、本発明の第6の実施形態について説明する。第6の実施形態は、第5の実施形態の画素回路構成において、長短露光時間の開始時間を揃えるためのものである。なお、本実施形態でも、ライン内の各画素に2種類の行転送パルスと、列転送パルスを送信して長短露光を制御する。この方法について、図23を参照しながら説明する。図23は、第6の実施形態における画素1202の駆動方法及びその特性を示す図である。この図23は、行転送トランジスタ2002、列転送トランジスタ2004、行転送トランジスタ2005、及びリセットトランジスタ2003の導通／非導通を制御する駆動方法を示すタイミングチャートである。なお、 $t_{71} \sim t_{718}$ はタイミングを表す。

10

**【0263】**

先ず、タイミング $t_{71}$ で、第n行目全てのリセットトランジスタ2003及びn行目全ての行転送トランジスタ2002のゲートが導通になる。この結果、第n行目全てのPD2001の電荷がFD2007に完全転送されてリセットされ、第n行目全てのFD2007もリセットトランジスタ2003のドレイン電位にリセットされる。

20

**【0264】**

タイミング $t_{72}$ で、第n行目全ての行転送トランジスタ2002のゲートが非導通になる。この結果、第n行目全てのPD2001への電荷の蓄積が開始される。

**【0265】**

タイミング $t_{73}$ で、第n+1行目全てのリセットトランジスタ2003及び第n+1行目全ての行転送トランジスタ2002のゲートが導通になる。この結果、第n+1行目全てのPD2001の電荷がFD2007に完全転送されてリセットされ、第n+1行目全てのFD2007もリセットトランジスタ2003のドレイン電位にリセットされる。

30

**【0266】**

タイミング $t_{74}$ で、第n+1行目全ての行転送トランジスタ2002のゲートが非導通になる。この結果、第n+1行目全てのPD2001への電荷の蓄積が開始される。

**【0267】**

タイミング $t_{75}$ で、第n+2行目全てのリセットトランジスタ2003及び第n+2行目全ての行転送トランジスタ2002のゲートが導通になる。この結果、第n+2行目全てのPD2001の電荷がFD2007に完全転送されてリセットされ、第n+2行目全てのFD2007もリセットトランジスタ2003のドレイン電位にリセットされる。

**【0268】**

タイミング $t_{76}$ で、第n+2行目全ての行転送トランジスタ2002のゲートが非導通になる。この結果、第n+2行目全てのPD2001への電荷の蓄積が開始される。

40

**【0269】**

タイミング $t_{77}$ で、第n行目全ての行転送トランジスタ2005、及び短秒露光が割り当てられている第m列目の列転送トランジスタ2004のゲートが導通となり、被写体からの光であるPD2001の電荷がFD2007に完全転送される。

**【0270】**

タイミング $t_{78}$ で、トランジスタ2006が導通する。この結果、FD2007の電位が低インピーダンス化されて、画素出力VOUTn\_sとして、出力回路1205に接続された信号線へ導出される。

**【0271】**

50

タイミング t<sub>7</sub>9 で、第 n + 1 行目全ての行転送トランジスタ 2005、及び短秒露光が割り当てられている第 m 列目の列転送トランジスタ 2004 のゲートが導通となり、被写体からの光である PD2001 の電荷が FD2007 に完全転送される。

#### 【0272】

タイミング t<sub>7</sub>10 で、トランジスタ 2006 が導通する。この結果、FD2007 の電位が低インピーダンス化されて、画素出力 VOUT<sub>n+1</sub>\_s として、出力回路 1205 に接続された信号線へ導出される。

#### 【0273】

タイミング t<sub>7</sub>11 で、第 n + 2 行目全ての行転送トランジスタ 2005、及び短秒露光が割り当てられている第 m 列目の列転送トランジスタ 2004 のゲートが導通となり、被写体からの光である PD2001 の電荷が FD2007 に完全転送される。10

#### 【0274】

タイミング t<sub>7</sub>12 で、トランジスタ 2006 が導通する。この結果、FD2007 の電位が低インピーダンス化されて、画素出力 VOUT<sub>n+2</sub>\_s として、出力回路 1205 に接続された信号線へ導出される。

#### 【0275】

タイミング t<sub>7</sub>13 で、第 n 行目全ての行転送トランジスタ 2002 が導通となり、被写体からの光である PD2001 の電荷が FD2007 に完全転送される。

#### 【0276】

タイミング t<sub>7</sub>14 で、第 n 行目全てのトランジスタ 2006 が導通する。この結果、FD2007 の電位が低インピーダンス化されて、画素出力 VOUT<sub>n</sub>\_L として、出力回路 1205 に接続された信号線へ導出される。20

#### 【0277】

タイミング t<sub>7</sub>15 で、第 n + 1 行目全ての行転送トランジスタ 2002 が導通となり、被写体からの光である PD2001 の電荷が FD2007 に完全転送される。

#### 【0278】

タイミング t<sub>7</sub>16 で、第 n + 1 行目全てのトランジスタ 2006 が導通する。この結果、FD2007 の電位が低インピーダンス化されて、画素出力 VOUT<sub>n+1</sub>\_L として、出力回路 1205 に接続された信号線へ導出される。

#### 【0279】

タイミング t<sub>7</sub>17 で、第 n + 2 行目全ての行転送トランジスタ 2002 が導通となり、被写体からの光である PD2001 の電荷が FD2007 に完全転送される。30

#### 【0280】

タイミング t<sub>7</sub>18 で、第 n + 2 行目全てのトランジスタ 2006 が導通すると、FD2007 の電位が低インピーダンス化されて、画素出力 VOUT<sub>n+2</sub>\_L として、出力回路 1205 に接続された信号線へ導出される。

#### 【0281】

他の構成及び動作は第 5 の実施形態と同様である。

#### 【0282】

このような第 6 の実施形態では、第 1 の行転送トランジスタで構成される導通路、又は列転送トランジスタ及び第 2 の行転送トランジスタを直列に配した導通路の 2 種類のうちいずれかの導通タイミングを与える。このため、同一行内の画素毎の露出時間開始時間を揃えることで行内の露光タイミングのずれを軽減することが可能である。40

#### 【0283】

(第 7 の実施形態)

次に、本発明の第 7 の実施形態について説明する。第 7 の実施形態は、第 5 の実施形態の画素回路構成において、同一行内にて複数種類の長短露光時間制御を行うためのものである。図 24 は、第 7 の実施形態における画素 1202 の駆動方法及びその特性を示す図である。この図 24 は、転送ゲートであるトランジスタ 2002、トランジスタ 2004、トランジスタ 2005、及びリセットトランジスタ 2003 の導通 / 非道通を制御する50

駆動方法を示すタイミングチャートである。なお、 $t_{81} \sim t_{824}$ はタイミングを表す。

#### 【0284】

先ず、タイミング  $t_{81}$ で、第  $n$  行目全てのリセットトランジスタ  $2003$ 、及び第  $n$  行目全ての行転送トランジスタ  $2002$  のゲートが導通になる。この結果、第  $n$  行目全ての  $PD2001$  の電荷が  $FD2007$  に完全転送されてリセットされ、第  $n$  行目全ての  $FD2007$  もリセットトランジスタ  $2003$  のドレイン電位にリセットされる。

#### 【0285】

タイミング  $t_{82}$ で、第  $n$  行目全ての行転送トランジスタ  $2002$  のゲートが非導通になる。この結果、第  $n$  行目全ての  $PD2001$  への電荷の蓄積が開始される。

10

#### 【0286】

タイミング  $t_{83}$ で、第  $n+1$  行目全てのリセットトランジスタ  $2003$ 、及び第  $n+1$  行目全ての行転送トランジスタ  $2002$  のゲートが導通になる。この結果、第  $n+1$  行目全ての  $PD2001$  の電荷が  $FD2007$  に完全転送されてリセットされ、第  $n+1$  行目全ての  $FD2007$  もリセットトランジスタ  $2003$  のドレイン電位にリセットされる。

。

#### 【0287】

タイミング  $t_{84}$ で、第  $n+1$  行目全ての行転送トランジスタ  $2002$  のゲートが非導通になる。この結果、第  $n+1$  行目全ての  $PD2001$  への電荷の蓄積が開始される。

#### 【0288】

タイミング  $t_{85}$ で、第  $n+2$  行目全てのリセットトランジスタ  $2003$ 、及び第  $n+2$  行目全ての行転送トランジスタ  $2002$  のゲートが導通になる。この結果、第  $n+2$  行目全ての  $PD2001$  の電荷が  $FD2007$  に完全転送されてリセットされ、第  $n+2$  行目全ての  $FD2007$  もリセットトランジスタ  $2003$  のドレイン電位にリセットされる。

。

#### 【0289】

タイミング  $t_{86}$ で、第  $n+2$  行目全ての行転送トランジスタ  $2002$  のゲートが非導通になる。この結果、第  $n+2$  行目全ての  $PD2001$  への電荷の蓄積が開始される。

20

#### 【0290】

タイミング  $t_{87}$ で、第  $n$  行目全てのリセットトランジスタ  $2003$  及び行転送トランジスタ  $2005$ 、並びに短秒露光が割り当てられている第  $m$  列目の列転送トランジスタ  $2004$  のゲートが導通となる。この結果、被写体からの光である  $PD2001$  の電荷が  $FD2007$  に完全転送されリセットされる。

30

#### 【0291】

タイミング  $t_{88}$ で、第  $n$  行目全てのリセットトランジスタ  $2003$  及び行転送トランジスタ  $2005$ 、並びに短秒露光が割り当てられている第  $m$  列目の列転送トランジスタ  $2004$  のゲートが非導通となる。この結果、 $PD2001$  への電荷の蓄積が再び開始される。

#### 【0292】

タイミング  $t_{89}$ で、第  $n+1$  行目全てのリセットトランジスタ  $2003$  及び行転送トランジスタ  $2005$ 、並びに短秒露光が割り当てられている第  $m$  列目の列転送トランジスタ  $2004$  のゲートが導通となる。この結果、被写体からの光である  $PD2001$  の電荷が  $FD2007$  に完全転送されリセットされる。

40

#### 【0293】

タイミング  $t_{90}$ で、第  $n+1$  行目全てのリセットトランジスタ  $2003$  及び行転送トランジスタ  $2005$ 、並びに短秒露光が割り当てられている第  $m$  列目の列転送トランジスタ  $2004$  のゲートが非導通となる。この結果、 $PD2001$  への電荷の蓄積が再び開始される。

#### 【0294】

タイミング  $t_{91}$ で、第  $n+2$  行目全てのリセットトランジスタ  $2003$  及び行転送

50

トランジスタ2005、並びに短秒露光が割り当てられている第m列目の列転送トランジスタ2004のゲートが導通となる。この結果、被写体からの光であるPD2001の電荷がFD2007に完全転送されリセットされる。

**【0295】**

タイミングt812で、第n+2行目全てのリセットトランジスタ2003及び行転送トランジスタ2005、並びに短秒露光が割り当てられている第m列目の列転送トランジスタ2004のゲートが非導通となる。この結果、PD2001への電荷の蓄積が再び開始される。

**【0296】**

タイミングt813で、第n行目全てのリセットトランジスタ2003及び行転送トランジスタ2005、並びに短秒露光が割り当てられている第m列目の列転送トランジスタ2004のゲートが導通となる。この結果、被写体からの光であるPD2001の電荷がFD2007に完全転送されリセットされる。10

**【0297】**

タイミングt814で、第n行目全てのリセットトランジスタ2003及び行転送トランジスタ2005、並びに短秒露光が割り当てられている第m列目の列転送トランジスタ2004のゲートが非導通となり、PD2001への電荷の蓄積が再び開始される。

**【0298】**

タイミングt815で、第n+1行目全てのリセットトランジスタ2003及び行転送トランジスタ2005、並びに短秒露光が割り当てられている第m列目の列転送トランジスタ2004のゲートが導通となる。この結果、被写体からの光であるPD2001の電荷がFD2007に完全転送されリセットされる。20

**【0299】**

タイミングt816で、第n+1行目全てのリセットトランジスタ2003及び行転送トランジスタ2005、並びに短秒露光が割り当てられている第m列目の列転送トランジスタ2004のゲートが非導通となり、PD2001への電荷の蓄積が再び開始される。

**【0300】**

タイミングt817で、第n+2行目全てのリセットトランジスタ2003及び行転送トランジスタ2005、並びに短秒露光が割り当てられている第m列目の列転送トランジスタ2004のゲートが導通となる。この結果、被写体からの光であるPD2001の電荷がFD2007に完全転送されリセットされる。30

**【0301】**

タイミングt818で、第n+2行目全てのリセットトランジスタ2003及び行転送トランジスタ2005、並びに短秒露光が割り当てられている第m列目の列転送トランジスタ2004のゲートが非導通となり、PD2001への電荷の蓄積が再び開始される。

**【0302】**

タイミングt819で、第n行目全ての行転送トランジスタ2002が導通となり、被写体からの光であるPD2001の電荷がFD2007に完全転送される。

**【0303】**

タイミングt820で、第n行目全てのトランジスタ2006が導通する。この結果、FD2007の電位が低インピーダンス化されて、画素出力VOUTnとして、出力回路1205に接続された信号線へ導出される。40

**【0304】**

タイミングt821で、第n+1行目全ての行転送トランジスタ2002が導通となり、被写体からの光であるPD2001の電荷がFD2007に完全転送される。

**【0305】**

タイミングt822で、第n+1行目全てのトランジスタ2006が導通する。この結果、FD2007の電位が低インピーダンス化されて、画素出力VOUTn+1として、出力回路1205に接続された信号線へ導出される。

**【0306】**

タイミング  $t_{823}$  で、第  $n + 2$  行目全ての行転送トランジスタ  $2002$  が導通となり、被写体からの光である  $PD2001$  の電荷が  $FD2007$  に完全転送される。

#### 【0307】

タイミング  $t_{824}$  で、第  $n + 2$  行目全てのトランジスタ  $2006$  が導通する。この結果、 $FD2007$  の電位が低インピーダンス化されて、画素出力  $VOUT_{n+2}$  として、出力回路  $1205$  に接続された信号線へ導出される。

#### 【0308】

他の構成及び動作は第 5 の実施形態と同様である。

#### 【0309】

このような第 7 の実施形態では、第 1 の行転送トランジスタで構成される導通路、又は列転送トランジスタ並びに第 2 の行転送トランジスタを直列に配した導通路の 2 種類のうちいずれかの導通タイミングを複数種類与える。このため、同一行内の画素毎の複数種類の露出時間の長短露出制御が可能である。10

#### 【0310】

##### (第 8 の実施形態)

次に、本発明の第 8 の実施形態について説明する。第 8 の実施形態は、第 5 の実施形態の画素回路構成において、同一行内にて任意の長短露光時間制御を行うためのものである。図 25 は、第 8 の実施形態における画素  $1202$  の駆動方法及びその特性を示す図である。この図 25 は、転送ゲートであるトランジスタ  $2002$ 、トランジスタ  $2004$ 、トランジスタ  $2005$ 、及びリセットトランジスタ  $2003$  の導通 / 非導通を制御する駆動方法を示すタイミングチャートである。なお、 $t_{91} \sim t_{924}$  はタイミングを表す。20

#### 【0311】

先ず、タイミング  $t_{91}$  で、第  $n$  行目全てのリセットトランジスタ  $2003$ 、及び第  $n$  行目全ての行転送トランジスタ  $2002$  のゲートが導通になる。この結果、第  $n$  行目全ての  $PD2001$  の電荷が  $FD2007$  に完全転送されてリセットされ、第  $n$  行目全ての  $FD2007$  もリセットトランジスタ  $2003$  のドレイン電位にリセットされる。

#### 【0312】

タイミング  $t_{92}$  で、第  $n$  行目全ての行転送トランジスタ  $2002$  のゲートが非導通になる。この結果、第  $n$  行目全ての  $PD2001$  への電荷の蓄積が開始される。

#### 【0313】

タイミング  $t_{93}$  で、第  $n + 1$  行目全てのリセットトランジスタ  $2003$ 、及び第  $n + 1$  行目全ての行転送トランジスタ  $2002$  のゲートが導通になる。この結果、第  $n + 1$  行目全ての  $PD2001$  の電荷が  $FD2007$  に完全転送されてリセットされ、第  $n + 1$  行目全ての  $FD2007$  もリセットトランジスタ  $2003$  のドレイン電位にリセットされる。30

#### 【0314】

タイミング  $t_{94}$  で、第  $n + 1$  行目全ての行転送トランジスタ  $2002$  のゲートが非導通になる。この結果、第  $n + 1$  行目全ての  $PD2001$  への電荷の蓄積が開始される。

#### 【0315】

タイミング  $t_{95}$  で、第  $n + 2$  行目全てのリセットトランジスタ  $2003$ 、及び第  $n + 2$  行目全ての行転送トランジスタ  $2002$  のゲートが導通になる。この結果、第  $n + 2$  行目全ての  $PD2001$  の電荷が  $FD2007$  に完全転送されてリセットされ、第  $n + 2$  行目全ての  $FD2007$  もリセットトランジスタ  $2003$  のドレイン電位にリセットされる。40

#### 【0316】

タイミング  $t_{96}$  で、第  $n + 2$  行目全ての行転送トランジスタ  $2002$  のゲートが非導通になる。この結果、第  $n + 2$  行目全ての  $PD2001$  への電荷の蓄積が開始される。

#### 【0317】

タイミング  $t_{97}$  で、第  $n$  行目全てのリセットトランジスタ  $2003$  及び行転送トランジスタ  $2005$ 、並びに短秒露光が割り当てられている第  $m$  列目の列転送トランジスタ  $2$ 50

004のゲートが導通となる。この結果、被写体からの光であるPD2001の電荷がFD2007に完全転送されリセットされる。

【0318】

タイミングt98で、第n行目全てのリセットトランジスタ2003及び行転送トランジスタ2005、並びに短秒露光が割り当てられている第m列目の列転送トランジスタ2004のゲートが非導通となり、PD2001への電荷の蓄積が再び開始される。

【0319】

タイミングt99で、第n+1行目全てのリセットトランジスタ2003及び行転送トランジスタ2005、並びに短秒露光が割り当てられている第m列目の列転送トランジスタ2004のゲートが導通となる。この結果、被写体からの光であるPD2001の電荷がFD2007に完全転送されリセットされる。

10

【0320】

タイミングt910で、第n+1行目全てのリセットトランジスタ2003及び行転送トランジスタ2005、並びに短秒露光が割り当てられている第m列目の列転送トランジスタ2004のゲートが非導通となり、PD2001への電荷の蓄積が再び開始される。

【0321】

タイミングt911で、第n+2行目全てのリセットトランジスタ2003及び行転送トランジスタ2005、並びに短秒露光が割り当てられている第m列目の列転送トランジスタ2004のゲートが導通となる。この結果、被写体からの光であるPD2001の電荷がFD2007に完全転送されリセットされる。

20

【0322】

タイミングt912で、第n+2行目全てのリセットトランジスタ2003及び行転送トランジスタ2005、並びに短秒露光が割り当てられている第m列目の列転送トランジスタ2004のゲートが非導通となり、PD2001への電荷の蓄積が再び開始される。

【0323】

タイミングt913で、第n行目全ての行転送トランジスタ2005、及び短秒露光が割り当てられている第m列目の列転送トランジスタ2004のゲートが導通となり、被写体からの光であるPD2001の電荷がFD2007に完全転送される。

【0324】

タイミングt914で、トランジスタ2006が導通する。この結果、FD2007の電位が低インピーダンス化されて、画素出力VOUTn\_sとして、出力回路1205に接続された信号線へ導出される。

30

【0325】

タイミングt915で、第n+1行目全ての行転送トランジスタ2005、及び短秒露光が割り当てられている第m列目の列転送トランジスタ2004のゲートが導通となり、被写体からの光であるPD2001の電荷がFD2007に完全転送される。

【0326】

タイミングt916で、トランジスタ2006が導通する。この結果、FD2007の電位が低インピーダンス化されて、画素出力VOUTn+1\_sとして、出力回路1205に接続された信号線へ導出される。

40

【0327】

タイミングt917で、第n+2行目全ての行転送トランジスタ2005、及び短秒露光が割り当てられている第m列目の列転送トランジスタ2004のゲートが導通となり、被写体からの光であるPD2001の電荷がFD2007に完全転送される。

【0328】

タイミングt918で、トランジスタ2006が導通する。この結果、FD2007の電位が低インピーダンス化されて、画素出力VOUTn+2\_sとして、出力回路1205に接続された信号線へ導出される。

【0329】

タイミングt919で、第n行目全ての行転送トランジスタ2002が導通となり、被

50

写体からの光である P D 2 0 0 1 の電荷が F D 2 0 0 7 に完全転送される。

**【 0 3 3 0 】**

タイミング t 9 2 0 で、第 n 行目全てのトランジスタ 2 0 0 6 が導通する。この結果、F D 2 0 0 7 の電位が低インピーダンス化されて、画素出力 V O U T n \_ L として、出力回路 1 2 0 5 に接続された信号線へ導出される。

**【 0 3 3 1 】**

タイミング t 9 2 1 で、第 n + 1 行目全ての行転送トランジスタ 2 0 0 2 が導通となり、被写体からの光である P D 2 0 0 1 の電荷が F D 2 0 0 7 に完全転送される。

**【 0 3 3 2 】**

タイミング t 9 2 2 で、第 n + 1 行目全てのトランジスタ 2 0 0 6 が導通する。この結果、F D 2 0 0 7 の電位が低インピーダンス化されて、画素出力 V O U T n + 1 \_ L として、出力回路 1 2 0 5 に接続された信号線へ導出される。10

**【 0 3 3 3 】**

タイミング t 9 2 3 で、第 n + 2 行目全ての行転送トランジスタ 2 0 0 2 が導通となり、被写体からの光である P D 2 0 0 1 の電荷が F D 2 0 0 7 に完全転送される。

**【 0 3 3 4 】**

タイミング t 9 2 4 で、トランジスタ 2 0 0 6 が導通する。この結果、F D 2 0 0 7 の電位が低インピーダンス化されて、画素出力 V O U T n + 2 \_ L として、出力回路 1 2 0 5 に接続された信号線へ導出される。

**【 0 3 3 5 】**

他の構成及び動作は第 5 の実施形態と同様である。

**【 0 3 3 6 】**

このような第 8 の実施形態では、第 1 の行転送トランジスタで構成される導通路、又は列転送トランジスタ及び第 2 の行転送トランジスタを直列に配した導通路の 2 種類のうちいずれかの導通タイミングを複数種類与える。このため、同一行内の画素毎に任意の複数種類の露出時間の長短露出制御が可能である。

**【 0 3 3 7 】**

なお、上述した実施形態の処理は、各機能を具現化したソフトウェアのプログラムコードを記録した記憶媒体をシステム或いは装置に提供しても実現することができる。そして、そのシステム又は装置のコンピュータ（若しくは C P U 、 M P U ）が記憶媒体に格納されたプログラムコードを読み出し実行することによって、前述した実施形態の機能を実現することができる。この場合、記憶媒体から読み出されたプログラムコード自体が前述した実施形態の機能を実現することになり、そのプログラムコードを記憶した記憶媒体は本発明を構成することになる。このようなプログラムコードを供給するための記憶媒体としては、例えば、フレキシブルディスク、ハードディスク、光ディスク、光磁気ディスク等を用いることができる。また、C D - R O M 、 C D - R 、磁気テープ、不揮発性のメモリカード、R O M 等を用いることもできる。30

**【 0 3 3 8 】**

また、コンピュータが読み出したプログラムコードを実行することにより、前述した各実施の形態の機能が実現されるだけではない。そのプログラムコードの指示に基づき、コンピュータ上で稼動している O S （オペレーティングシステム）などが実際の処理の一部又は全部を行い、その処理によって前述した各実施例の機能が実現される場合も含まれている。40

**【 0 3 3 9 】**

さらに、記憶媒体から読み出されたプログラムコードが、コンピュータに挿入された機能拡張ボードやコンピュータに接続された機能拡張ユニットに備わるメモリに書きこまれてもよい。その後、そのプログラムコードの指示に基づき、その機能拡張ボードや機能拡張ユニットに備わる C P U などが実際の処理の一部又は全部を行い、その処理によって前述した各実施の形態の機能が実現される場合も含むものである。

**【 0 3 4 0 】**

10

20

30

40

50

つまり、本発明の実施形態は、例えばコンピュータがプログラムを実行することによって実現することができる。また、プログラムをコンピュータに供給するための手段、例えばかかるプログラムを記録したCD-ROM等のコンピュータ読み取り可能な記録媒体又はかかるプログラムを伝送するインターネット等の伝送媒体も本発明の実施形態として適用することができる。また、上記の印刷処理用のプログラムも本発明の実施形態として適用することができる。上記のプログラム、記録媒体、伝送媒体及びプログラムプロダクトは、本発明の範疇に含まれる。

【図面の簡単な説明】

【0341】

【図1】第1の実施形態に係る撮像装置の構成を示すブロック図である。

10

【図2】撮像装置1の動作を示すフローチャートである。

【図3】ステップS201において表示される境界輝度パラメータ設定UIのダイアログウィンドウの例を示す図である。

【図4】境界輝度パラメータ設定動作を示す状態遷移図である。

【図5】ピクセル露光量設定部103の一例を示すブロック図である。

【図6】再予備撮像判定動作の詳細を示すフローチャートである。

【図7】撮像条件の記録例を示す図である。

【図8】ピクセル露光量設定動作の詳細を示すフローチャートである。

【図9】露光時間MAP生成処理の詳細を示すフローチャートである。

【図10】露光量時間MAPを示す模式図を示す図である。

20

【図11】第1の実施形態における駆動パルス生成処理の詳細を示すフローチャートである。

【図12】カラー撮像素子部102を構成する各構成要素の配置の一例を示す模式図である。

【図13】第1の実施形態における画素1202の構造の一例を示す回路図である。

【図14A】転送ゲートであるトランジスタ1302及びトランジスタ1304、並びにリセットトランジスタ1303の導通／非導通を制御する駆動方法を示すタイミングチャートである。

【図14B】撮像画素第n行目の第m列～第m+4列までの露光量を示す模式図である。

【図14C】行転送トランジスタ1302、列転送トランジスタ1304及びリセットトランジスタ1303の導通／非導通を制御する駆動方法を示すタイミングチャートである。

30

【図14D】撮像画素第n行～第n+3行目までの行転送トランジスタ1302、列転送トランジスタ1304及びリセットトランジスタ1303の導通／非導通を制御する駆動方法を示すタイミングチャートである。

【図15】ゲイン演算の詳細を示すフローチャートである。

【図16】第2の実施形態における画素1202の駆動方法及びその特性を示す図である。

【図17】第3の実施形態における画素1202の駆動方法及びその特性を示す図である。

40

【図18】第4の実施形態における画素1202の構造の一例を示す回路図である。

【図19】第4の実施形態における画素1202の駆動方法及びその特性を示す図である。

【図20】第5の実施形態における画素1202の構造の一例を示す回路図である。

【図21】第5の実施形態における駆動パルス生成処理の詳細を示すフローチャートである。

【図22】第5の実施形態における画素1202の駆動方法及びその特性を示す図である。

【図23】第6の実施形態における画素1202の駆動方法及びその特性を示す図である。

50

【図24】第7の実施形態における画素1202の駆動方法及びその特性を示す図である。

【図25】第8の実施形態における画素1202の駆動方法及びその特性を示す図である。

【符号の説明】

【0342】

|                      |    |

|----------------------|----|

| 1 : 撮像装置             |    |

| 101 : 光学部            |    |

| 102 : カラー撮像素子部       |    |

| 103 : ピクセル露光量設定部     | 10 |

| 104 : 境界輝度パラメータ保存部   |    |

| 105 : ゲイン演算部         |    |

| 106 : 画素補間部          |    |

| 107 : 画像処理部          |    |

| 108 : メモリ部           |    |

| 109 : 表示部            |    |

| 110 : 画像出力部          |    |

| 501 : 飽和判定部          |    |

| 502 : 予備撮像条件変更部      |    |

| 503 : 撮像条件記録部        | 20 |

| 504 : 輝度算出部          |    |

| 505 : ピクセル露光時間MAP生成部 |    |

| 506 : 露光時間MAP記録部     |    |

| 507 : タイミングジェネレータ部   |    |

| 1201 : 撮像面           |    |

| 1202 : 摄像素子          |    |

| 1203 : 垂直走査回路        |    |

| 1204 : 水平走査回路        |    |

| 1205 : 出力回路          |    |

| 1206 : アンプ           | 30 |

| 1207 : タイミングジェネレータ   |    |

| 1208 : 行信号線          |    |

| 1209 : 列信号線          |    |

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

〔 図 7 〕

| 番号  | 絞り値 | シャッタースピード | ISO感度 | 画素値 |

|-----|-----|-----------|-------|-----|

| 0   | 8.0 | 1／1000    | 100   | 32  |

| 1   | 8.0 | 1／1000    | 100   | 34  |

| 2   | 8.0 | 1／1000    | 100   | 37  |

| 3   | 8.0 | 1／1000    | 100   | 40  |

| ⋮   | ⋮   | ⋮         | ⋮     | ⋮   |

| N   | 8.0 | 1／1000    | 100   | 240 |

| N+1 | 8.0 | 1／2000    | 100   | 128 |

| N+2 | 8.0 | 1／1000    | 100   | 238 |

| ⋮   | ⋮   | ⋮         | ⋮     | ⋮   |

〔 8 〕

【図 9】

【図 10】

【図 11】

【図 12】

【図 1 3】

【図 1 4 A】

【図 1 4 B】

【図 1 4 D】

【図 1 4 C】

【図15】

【図16】

【図17】

【図18】

【図 19】

【図 20】

【図 21】

【図 22】

【図23】

【図24】

【図25】

---

フロントページの続き

(56)参考文献 特開2006-197192(JP,A)

特開2005-223920(JP,A)

特開2007-166238(JP,A)

(58)調査した分野(Int.Cl., DB名)

H 04 N 5 / 335