RÉPUBLIQUE FRANÇAISE

INSTITUT NATIONAL

DE LA PROPRIÉTÉ INDUSTRIELLE

PARIS

(11) N° de publication :

(A n'utiliser que pour les

commandes de reproduction).

**2 507 414**

A1

**DEMANDE

DE BREVET D'INVENTION**

(21)

**N° 81 11311**

(54) Générateur de signaux logiques combinés.

(51) Classification internationale (Int. Cl.<sup>3</sup>). H 03 K 19/173, 19/20 // G 01 R 31/28.

(22) Date de dépôt ..... 9 juin 1981.

(33) (32) (31) Priorité revendiquée :

(41) Date de la mise à la disposition du

public de la demande ..... B.O.P.I. — « Listes » n° 49 du 10-12-1982.

(71) Déposant : COMMISSARIAT A L'ENERGIE ATOMIQUE, établissement de caractère scientifique technique et industriel, résidant en France.

(72) Invention de : André Laviron et Claude Bérard.

(73) Titulaire : *Idem* (71)

(74) Mandataire : Brevatome,

25, rue de Ponthieu, 75008 Paris.

La présente invention concerne un générateur de signaux logiques combinés. Ce générateur permet de former toutes les combinaisons ou un certain nombre de combinaisons de deux signaux logiques à un niveau 1, et de N-2 signaux logiques à un niveau 0,

5 parmi les N sorties ( $QP_1, QP_2, \dots, QP_N$ ) que comporte ce générateur (N étant une constante).

Ce générateur s'applique par exemple, à l'étude des conséquences de défaillance de composants entrant dans le système de sécurité des centrales nucléaires en réalisant, en association avec un simulateur logique, des combinaisons de défaillance des divers composants ; dans cette application où l'on veut pouvoir décrire les combinaisons de composants défaillants qui entraînent la défaillance d'un système global, on simule chaque composant du système par des portes logiques, chacune de ces portes étant reliée à l'une des sorties  $QP_1 \dots QP_N$  du générateur. Suivant l'état de la sortie  $QP_i$  du générateur, la porte correspondante simule l'état passant ou non (bon état ou état défaillant) du composant du système. Pour chacune des combinaisons générée sur deux des sorties du générateur, la réponse du simulateur est analysé afin de savoir s'il s'agit d'une combinaison entraînant défaillance ou non du système global. La liste de ces combinaisons est un résultat qui permet ensuite d'analyser le système global pour des études de fiabilité.

Ce générateur est plus particulièrement destiné à tester des cartes de circuit imprimé présentant un grand nombre de contacts. Pour une carte présentant 1000 contacts par exemple, le générateur permet de passer en revue les 1000 contacts pris deux à deux, en comparant par rapport à une carte de référence, les signaux obtenus en sortie de la carte à tes-

ter, lorsque les contacts sont deux à deux mis successivement à un niveau logique 1, puis au niveau logique 0. De manière connue, ce type de test est généralement réalisé par un calculateur qui effectue, pour une carte comprenant 1000 contacts, environ 500 000 opérations.

Le générateur de l'invention s'applique également à la simulation de tous les systèmes logiques fonctionnant à partir de la réception de signaux logiques aux niveaux 0 ou 1, reçus sur leurs entrées.

On connaît un système qui permet d'obtenir parmi les N sorties qu'il comporte, toutes les combinaisons de deux sorties sur lesquelles sont disponibles des signaux logiques de niveau 1, les N-2 sorties restantes fournissant des signaux logiques de niveau 0. Ce système comprend un compteur binaire à N sorties sur lesquelles on effectue un balayage de toutes les combinaisons possibles ou d'un certain nombre de ces combinaisons. Cependant, pour les fortes valeurs de N, le nombre de combinaisons total à balayer est en général très grand. Généralement, ces combinaisons sont obtenues à partir de systèmes pilotés par ordinateur.

Dans le cas des études de fiabilité d'ensembles logiques, on recherche la liste des éléments défaillants qui entraînent une défaillance totale de l'ensemble. La simulation des systèmes logiques est donc, dans l'état actuel de la technique et avec le système décrit précédemment, une opération compliquée, longue et coûteuse.

L'invention a pour but de remédier à ces inconvénients et notamment de réaliser un générateur de signaux logiques combinés dans lequel la recherche d'une combinaison de signaux n'exige pas l'utilisation d'un ordinateur effectuant un balayage compliqué, long

et coûteux des signaux de sortie de ce générateur.

L'invention a pour objet un générateur de signaux logiques combinés pour former des combinaisons de deux sorties au niveau logique 1 et N-2 sorties au

5 niveau logique 0, parmi N sorties ( $QP_1, \dots, QP_N$ ) du générateur sur lesquelles sont disponibles deux signaux logiques de niveau 1 et N-2 signaux logiques de niveau 0, N étant une constante, caractérisé en ce qu'il comprend :

- 10 - un ensemble (P) de N moyens de mémorisation, ces moyens de mémorisation étant repérés du rang 1 au rang N, les combinaisons des deux sorties au niveau 1 et N-2 sorties au niveau 0 étant fournies sur des sorties ( $QP_1, \dots, QP_N$ ) de ces moyens de mémorisation de rang 1 à N ;

- 15 - des moyens (CH) pour charger dans les N moyens de mémorisation les niveaux logiques correspondant à une combinaison prédéterminée de départ, pour commander des opérations de décalage de contenus des moyens de mémorisation et pour commander, par l'intermédiaire de moyens de transfert (W), des transferts de contenus entre ces moyens de mémorisation ;

- 20 - des moyens de commande (M) pour repérer si la sortie  $QP_1$  de rang 1 des moyens de mémorisation de l'ensemble (P) est au niveau logique 1 et pour actionner les moyens de mémorisation, par l'intermédiaire des moyens de chargement et de décalage (CH) et de transfert (W) de façon :

- 25 . à mettre la sortie  $QP_{i-1}$  à un niveau logique 1 et la sortie  $QP_i$  au niveau logique 0, la sortie  $QP_i$  étant la première sortie qui est à un niveau logique 1, en partant de la sortie de rang 1, cette action n'étant effectuée que si le rang i est supérieur à 1.

- 30 . à mettre la sortie  $QP_1$  à un niveau logique 0 et la sortie  $QP_{r+1}$  à un niveau logique 1, cette ac-

- 35

tion n'étant effectuée que lorsque la première sortie qui est à un niveau logique 1 est la sortie  $QP_1$  de rang  $i=1$ , la sortie  $QP_r$  étant une autre sortie que la sortie  $QP_1$  et étant au niveau logique 1, l'action répétée des moyens de commande (M) fournissant les combinaisons qui suivent la combinaison prédéterminée de départ.

5 - des moyens (A) pour arrêter la génération des combinaisons après une autre combinaison prédéterminée.

10 Selon une autre caractéristique de l'invention, ladite combinaison prédéterminée de départ est, soit la première combinaison pour laquelle les niveaux logiques 1 sont disponibles sur les sorties  $QP_1$  et  $QP_2$  des deux premiers moyens de mémorisation de l'ensemble 15 (P), les sorties  $(QP_3, \dots, QP_N)$  des N-2 moyens de mémorisation suivants étant au niveau logique 0, soit toute autre combinaison prédéterminée de niveaux logiques 1 disponibles sur les sorties de deux des moyens de mémorisation.

20 Selon une autre caractéristique, l'ensemble (P) des N moyens de mémorisation comprend un groupe de deux registres à décalage (J, K), constitués respectivement par N-1 bascules  $(J_1, \dots, J_{N-1}$  et  $K_2, \dots, K_N)$ , le premier registre (J) présentant une entrée de décalage 25 des contenus des bascules de rangs forts vers les bascules de rangs faibles et le deuxième registre (K) présentant une entrée de décalage des contenus des bascules de rangs faibles vers les bascules de rangs forts, les sorties  $(QJ_1, \dots, QJ_{N-1})$  du premier registre 30 (J) étant repérées de 1 à N-1 et les sorties  $(QK_2, \dots, QK_N)$  du deuxième registre (K) étant repérées de 2 à N, la première sortie  $(QP_1)$  des moyens de mémorisation (P) étant constituée par la sortie  $(QJ_1)$  de la première bascule  $(J_1)$  du premier registre (J) et la

dernière sortie ( $QP_N$ ) des moyens de mémorisation (P) étant constituée par la sortie ( $QK_N$ ) de la dernière bascule ( $K_N$ ) du deuxième registre (K), l'ensemble de mémorisation (P) comprenant en outre un ensemble (E)

5 de  $N-2$  portes OU à deux entrées, les deux entrées de ces portes OU étant respectivement connectées aux sorties  $(QJ_2, QK_2) - (QJ_3, QK_3) - \dots - (QJ_{N-1}, QK_{N-1})$  correspondantes des bascules de même rang  $(J_2, K_2) - (J_3, K_3) - \dots - (J_{N-1}, K_{N-1})$  des registres (J, K), les sorties de ces portes OU constituant respectivement les sorties  $(QP_2, \dots, QP_{N-1})$  des moyens de mémorisation (P), les moyens de chargement de commande de décalage et de transfert (CH) appliquant des signaux d'initialisation, de remise à zéro, de décalage ou de

10 transfert de contenus sur des entrées correspondantes des registres (J, K) et sur des entrées des moyens de transfert (W), les moyens (M) de commande étant reliés à la première sortie  $QP_1$  des moyens de mémorisation de l'ensemble (P) pour commander, selon le niveau logique

15 de cette première sortie, la génération des combinaisons, par l'intermédiaire des moyens de chargement (CH), des moyens de transfert (W) et des moyens d'arrêt (A).

Selon une autre caractéristique, les moyens de commande (M) comprennent des moyens de contrôle (X) dont une entrée est reliée à la première sortie ( $QP_1$ ) des moyens de mémorisation, pour repérer si cette sortie est au niveau logique 1, un circuit de validation (VA) des opérations effectuées par les moyens de chargement et de commande de décalage et de transfert (CH) et par les moyens de transfert (W), une sortie de ces moyens de validation (VA) étant reliée à une autre entrée des moyens de contrôle (X), tandis qu'une entrée de ce circuit de validation est reliée à la sortie d'une horloge (H), des moyens (Z) pour indiquer

qu'une combinaison est présente sur les sorties ( $QP_1, \dots, QP_N$ ) des moyens de mémorisation (P) ou pour commander la recherche d'une autre combinaison, ces moyens (Z) d'indication et de commande de recherche de 5 combinaison recevant sur des entrées, des signaux d'initialisation, de validation ou de commande de recherche d'une autre combinaison, une sortie de ces moyens (Z) d'indication et de recherche de combinaison fournissant un signal indicateur de présence d'une 10 combinaison sur les sorties des moyens de mémorisation (P), une autre sortie de ces moyens étant reliée à une autre entrée du circuit de validation (VA) pour permettre les opérations effectuées par les moyens de chargement, de commande de décalage et de transfert 15 (CH) et par les moyens de transfert (W), à partir des impulsions de l'horloge (H), les moyens d'arrêt (A) présentant une sortie qui est reliée à une autre entrée des moyens de validation (VA) pour bloquer ces moyens de validation lorsque les combinaisons désirées 20 ont été obtenues, ces moyens d'arrêt (A) recevant sur des entrées, des signaux de commande de transfert et de commande de décalage, appliqués au premier registre (J) et aux moyens de transfert (W) par les moyens de chargement, de commande de décalage et de transfert 25 (CH).

Selon une autre caractéristique, les moyens de transfert (W) comprennent un premier circuit logique ( $CL_1$ ) dont une entrée est reliée à une sortie de commande des moyens de chargement, de commande de décalage et de transfert (CH), une sortie de ce premier circuit logique ( $CL_1$ ) étant reliée à une entrée de commande de la première bascule ( $J_1$ ) du premier registre à décalage (J) pour mettre à 0 le niveau de la 30 sortie ( $QP_1$ ) de cette bascule si le niveau de celle-ci, repéré par les moyens de contrôle (X) est le ni- 35

veau 1, et un ensemble de seconds circuits logiques ( $CL_2, CL_3, \dots, CL_{N-1}$ ) qui sont repérés du rang 2 au rang N-1 et qui correspondent respectivement aux bascules de même rang des premier et deuxième registres à décalage (J, K), chaque second circuit logique présentant deux entrées reliées respectivement à une sortie de la bascule de même rang du deuxième registre à décalage (K) et à ladite sortie de commande des moyens de chargement et de commande (CH), chaque second circuit logique présentant aussi deux sorties reliées respectivement à deux entrées de commande de la bascule de même rang du premier registre (J), de sorte que :

- lorsque la sortie ( $QP_1$ ) de la première bascule ( $J_1$ ) du premier registre à décalage (J) est au niveau logique 0, les moyens de chargement, de commande de décalage et de transfert (CH) provoquent par une autre sortie de commande reliée à l'entrée de décalage du premier registre (J), un décalage de un rang dans le contenu des bascules du premier registre (J), ce décalage étant effectué des bascules de rangs forts vers les bascules de rangs faibles, ce décalage faisant passer la sortie ( $QP_i$ ) de l'ensemble (P), qui était au niveau logique 1, au niveau logique 0 et la sortie ( $QP_{i-1}$ ) qui était au niveau logique 0, au niveau logique 1, le contenu du second registre (K) restant inchangé ;

- lorsque la sortie ( $QP_1$ ) de la première bascule ( $J_1$ ) du premier registre à décalage (J) est au niveau logique 1, les moyens de chargement, de commande de décalage et de transfert (CH), commandent le premier circuit logique ( $CL_1$ ) pour mettre au niveau logique 0, la sortie ( $QP_1$ ) de la première bascule ( $J_1$ ) du premier registre (J), puis commandent le second circuit logique ( $CL_r$ ) correspondant à une bascule ( $K_r$ ) de rang r, qui est au niveau 1, pour effectuer le

transfert du niveau 1 de la bascule ( $K_r$ ) dans la bascule ( $J_r$ ) du rang  $r$ , la bascule ( $K_r$ ) restant au niveau 1, puis commandent ensuite le décalage du contenu dans la bascule ( $K_r$ ), de un rang, ce décalage étant effectué des bascules de rangs faibles vers les bascules de rangs forts et faisant passer la sortie ( $QP_{r+1}$ ) qui était au niveau 0, au niveau 1.

Selon une autre caractéristique, les moyens (A) d'arrêt de génération de combinaisons comprennent un compteur (CPPO) chargé à l'initialisation du générateur, ce compteur étant activé à chaque opération de décalage ou de transfert, de manière que ces opérations de décalage ou de transfert soient arrêtées lorsque son contenu atteint 0, la sortie de ce compteur étant reliée à l'entrée des moyens de validation (VA) pour bloquer les opérations de décalage lorsque toutes les combinaisons ont été obtenues.

Selon une autre caractéristique, le générateur comprend en outre un circuit logique (ET 20, OU 15) de blocage de génération des combinaisons, à partir d'une combinaison prédéterminée, ce circuit logique présentant des entrées reliées à des sorties des moyens de mémorisation (P) qui correspondent aux sorties fournissant ladite combinaison prédéterminée, et une sortie de commande des moyens de validation (VA).

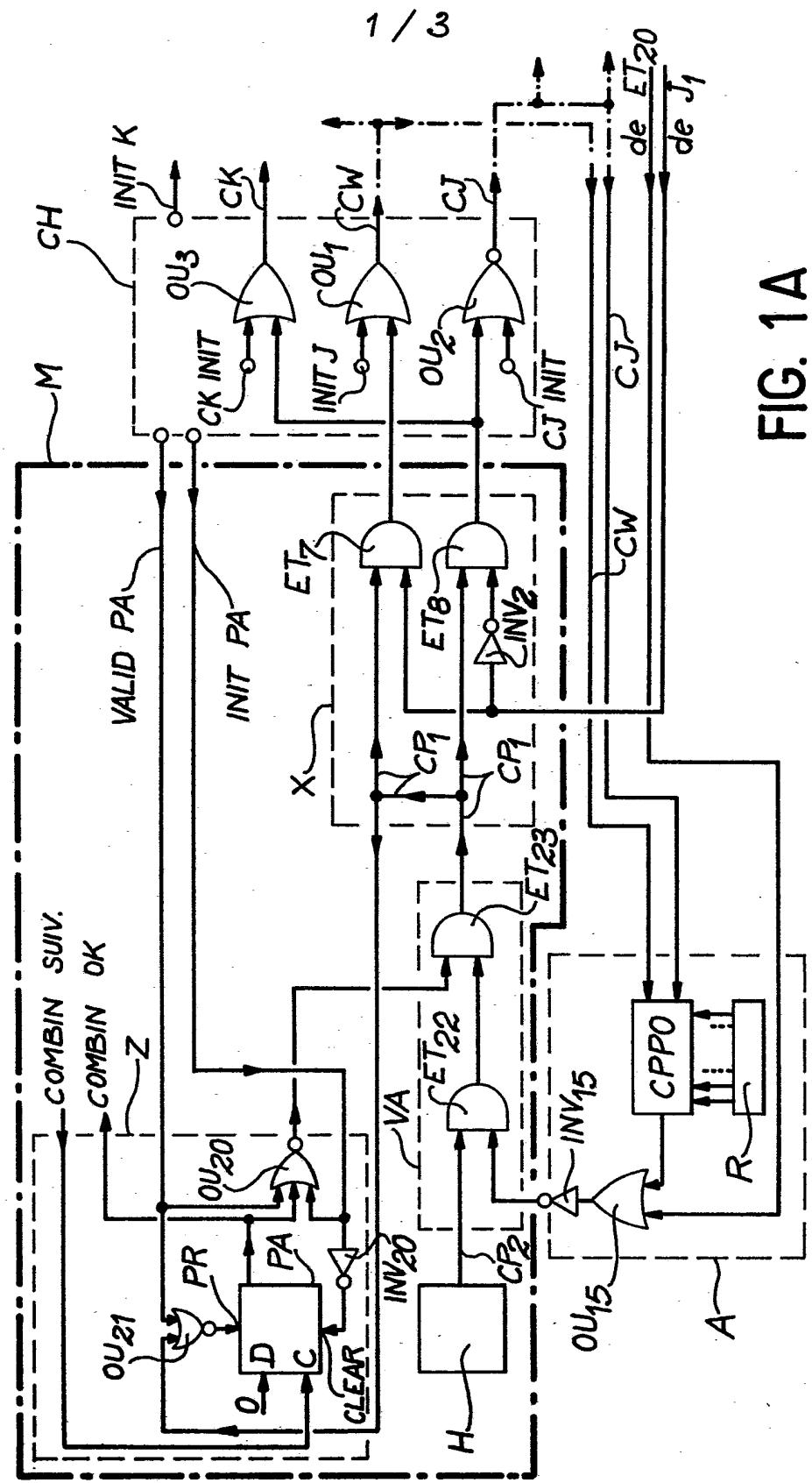

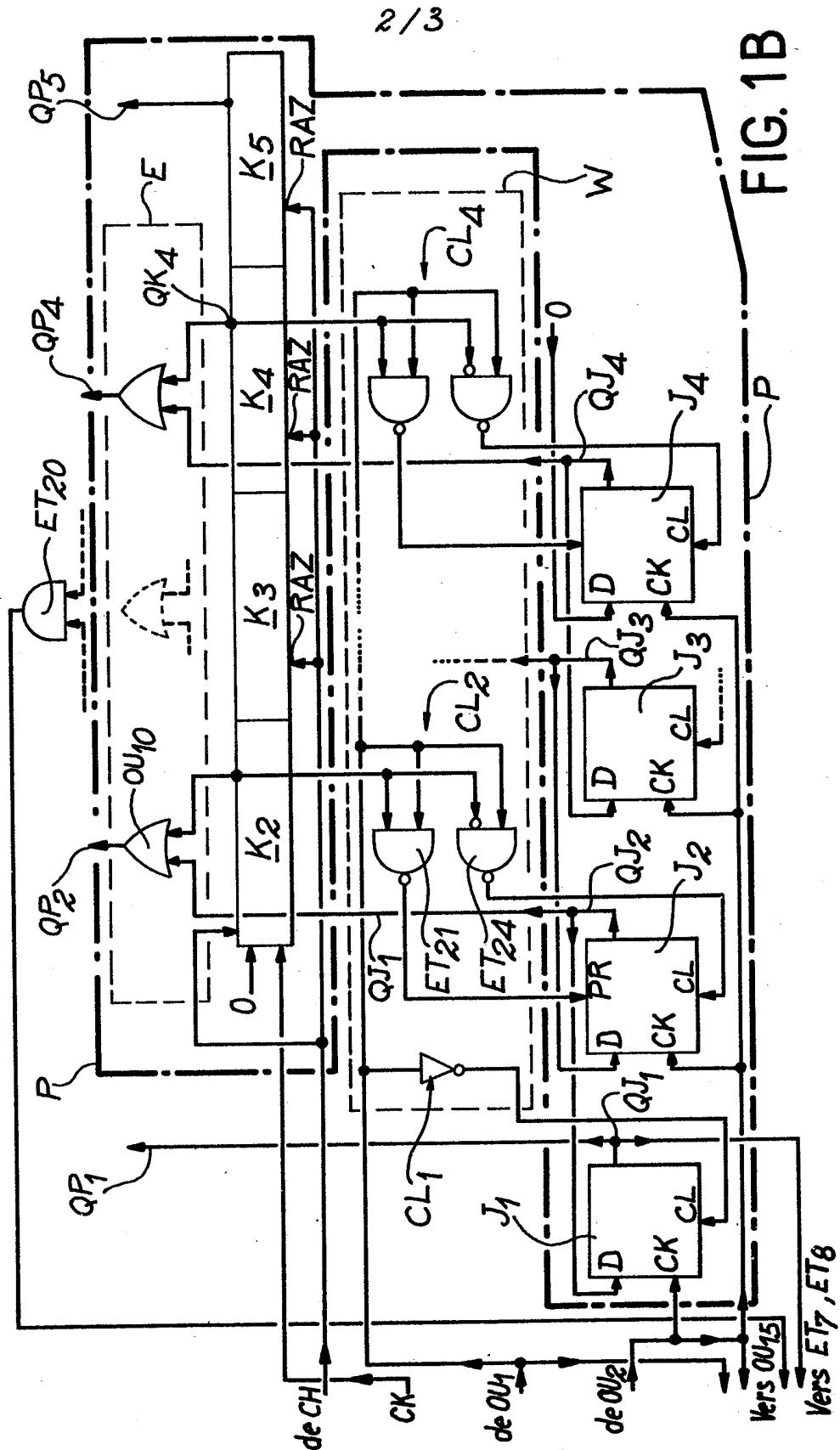

D'autres caractéristiques et avantages de l'invention ressortiront encore de la description qui va suivre, donnée en référence aux dessins annexés dans lesquels :

- 30 - la figure 1 représente schématiquement le générateur conforme à l'invention,

- la figure 2 est un tableau qui donne les niveaux logiques des signaux obtenus successivement sur les sorties du générateur de la figure 1 et qui permet de mieux comprendre le fonctionnement de ce générateur,

- la figure 3 est un tableau plus détaillé, qui donne les niveaux logiques sur les sorties des registres à décalage de l'ensemble de mémorisation du générateur.

- 5        Les figures 1A et 1B représentent schématiquement un générateur de signaux logiques combinés, conforme à l'invention. Ce générateur permet de former toutes les combinaisons de deux sorties au niveau logique 1, et de N-2 sorties au niveau logique 0, parmi

10      10 les N sorties ( $QP_1, QP_2, \dots, QP_N$ ) que comporte le générateur.

Sur la figure et pour des commodités de représentation, on a limité le nombre des sorties du générateur à 5 ; il en résulte que celui-ci possède

15      15 des sorties  $QP_1, QP_2, \dots, QP_5$ . Ce générateur comprend un ensemble P de N moyens de mémorisation qui seront repérés par leurs sorties, du rang 1 au rang N. Les combinaisons de deux sorties au niveau 1 est de N-2 au niveau 0, sont fournies par les sorties  $QP_1, QP_2, \dots, QP_N$ , des moyens de mémorisation de rang 1 à N.

20      Dans l'exemple représenté sur la figure, ces combinaisons apparaissent sur les sorties de rang 1 à 5. Comme on le verra plus loin en détail, l'ensemble P des moyens de mémorisation comprend un groupe de deux registres à décalage J, K, qui sont constitués respectivement par N-1 bascules  $J_1, J_2, \dots, J_{N-1}$  repérées du rang 1 au rang N-1 et par N-1 bascules  $K_2, K_3, \dots, K_N$ , repérées du rang 2 au rang N. Le registre à décalage J est constitué par exemple par des bascules de type D et qui peuvent être par exemple des bascules de la série 74 LS- 74, commercialisées par la Société TEXAS INSTRUMENTS. Les moyens de mémorisation de l'ensemble P sont repérés du rang 1 au rang N (sorties  $QP_1, \dots, QP_N$ ) et sont respectivement constitués par la bascule  $J_1$ , par les ensembles de bascules  $(J_2, K_2), \dots, (J_{N-1}, K_{N-1})$  et par la bascule  $K_N$ .

Le générateur comprend aussi des moyens CH qui seront décrits plus loin en détail et qui permettent de charger dans les N moyens de mémorisation (5 dans l'exemple considéré), des niveaux logiques correspondant à une combinaison prédéterminée de départ ; ces moyens CH permettent également de commander des opérations de décalage dans les contenus des moyens de mémorisation de l'ensemble P, ainsi que des opérations de transfert de contenu entre ces moyens de mémorisation, par l'intermédiaire des moyens de transfert W. Ces différentes opérations de décalage et de transfert, ainsi que les moyens CH et les moyens de transfert W, seront décrits plus loin en détail. Enfin, le générateur comprend des moyens de commande M qui permettent, comme on le verra par la suite, de repérer si la sortie  $QP_1$  de rang 1 est au niveau logique 1 et qui permettent également d'actionner les moyens de mémorisation de l'ensemble P, par l'intermédiaire des moyens de chargement et de décalage CH et des moyens de transfert W de façon :

- à mettre la sortie  $QP_{i-1}$  à un niveau logique 1 et la sortie  $QP_i$  au niveau logique 0, la sortie  $QP_i$  étant la première sortie qui est à un niveau logique 1, en partant de la sortie de rang 1, cette action n'étant effectuée que si le rang i est supérieur à 1 ;

- à mettre la sortie  $QP_1$  à un niveau logique 0 et la sortie  $QP_{r+1}$  à un niveau logique 1, cette action n'étant effectuée que lorsque la première sortie est à un niveau logique 1 et la sortie  $QP_1$  de rang  $i=1$  ;

la sortie  $QP_r$  est une autre sortie que la sortie  $QP_1$ , qui est au niveau logique 1. L'action répétée des moyens de commande M fournit les combinaisons qui suivent la combinaison prédéterminée de départ.

Des moyens A permettent d'arrêter la génération des combinaisons, après une autre combinaison

prédéterminée. Cette combinaison prédéterminée de départ peut être la première combinaison pour laquelle les niveaux logiques 1, sont disponibles sur les sorties  $QP_1$  et  $QP_2$  des deux premiers moyens de mémorisation de l'ensemble P, les sorties  $QP_3, \dots, QP_N$ , des N-2 moyens de mémorisation suivants, étant au niveau logique 0. Cette combinaison prédéterminée de départ peut également être toute autre combinaison prédéterminée, de niveau logique 1, disponible sur deux sorties des moyens de mémorisation de l'ensemble P.

Le tableau de la figure 2 donne les niveaux logiques des signaux obtenus successivement sur les sorties du générateur de la figure 1, ce tableau permet de mieux comprendre le fonctionnement de ce générateur. On suppose que la combinaison prédéterminée de départ est la première combinaison de deux signaux à un niveau logique 1 disponibles sur les deux premières sorties  $QP_1$  et  $QP_2$  du générateur (première ligne du tableau). Comme on l'a indiqué plus haut et comme on le verra plus loin en détail, les moyens M permettent d'actionner les moyens de mémorisation, par l'intermédiaire des moyens de chargement et de décalage CH et de transfert W, de façon que lorsque la sortie  $QP_1$  est à un niveau logique 1, cette sortie soit mise au niveau logique 0. C'est ainsi par exemple que sur la première ligne du tableau, la sortie  $QP_1$  est au niveau logique 1 et que les moyens de commande M permettent de faire passer cette sortie au niveau logique 0. Dans ce cas aussi, l'autre sortie  $QP_r$  du générateur, qui est au niveau logique 1, (sortie  $QP_2$  de rang r=2) reste au niveau logique 1 et la sortie  $QP_{r+1}$  est mise au niveau logique 1. La combinaison obtenue à la suite de ces opérations est celle qui est représentée sur la deuxième ligne du tableau de la figure 2. La sortie  $QP_1$  étant alors au niveau logique 0, les moyens de commande M permettent d'actionner les moyens de mémo-

risation, de manière à mettre à un niveau logique 1, la sortie  $QP_{i-1}$ , la sortie  $QP_i$  étant la première sortie qui est à un niveau logique 1 et à mettre à un niveau logique 0, la sortie  $QP_i$  qui était au niveau logique 1. Dans l'exemple considéré, la première sortie qui est à un niveau logique 1 est la sortie  $QP_2$ , de rang  $i=2$ . Cette sortie qui était au niveau logique 1 est donc mise au niveau logique 0, tandis que la sortie  $QP_1$  de rang  $i-1=1$  est mise au niveau logique 1. L'autre sortie  $QP_3$  qui était au niveau logique 1, ne change pas de niveau. On obtient à la suite de ces opérations, des niveaux logiques 1 sur les sorties  $QP_1$  et  $QP_3$  du générateur, comme indiqué à la ligne 3 du tableau de la figure 2. La sortie  $QP_1$  étant au niveau logique 1, on recherche l'autre sortie  $QP_r$ , de rang  $r$  qui est au niveau logique 1 ; cette sortie est ici la sortie  $QP_3$  de rang  $r=3$ . Dans ce cas, on fait passer comme on l'a indiqué plus haut, la sortie  $QP_1$  au niveau logique 0 et on ne change pas le niveau logique de la sortie  $QP_3$ . On fait ensuite passer la sortie  $QP_{r+1}$ , c'est-à-dire la sortie  $QP_4$ , au niveau logique 1. On obtient alors sur les sorties  $QP_3$  et  $QP_4$  du générateur, des niveaux logiques 1 visibles sur la quatrième ligne du tableau de la figure 2. De la même manière que précédemment, la première sortie qui est alors au niveau logique 0 est la sortie  $QP_i$  de rang  $i=3$  ; la sortie  $QP_1$  étant au niveau logique 0, on fait passer la sortie  $QP_{i-1}$  (c'est-à-dire  $QP_2$ ) au niveau logique 1 et on ne change pas le niveau 1 de la sortie  $QP_4$ . On obtient alors une combinaison de niveaux 1, sur les sorties  $QP_2$  et  $QP_4$  du générateur ; cette combinaison est visible sur la cinquième ligne du tableau de la figure 2. La première sortie qui est alors à un niveau logique 1 est la sortie  $QP_2$  de rang  $i=2$ , alors que la sortie  $QP_1$  est au niveau logique 1 ; dans ce cas, comme précédemment, on fait passer la sortie  $QP_1$  de rang  $i-1$  au niveau logique 1, sans changer le ni-

veau logique de l'autre sortie  $QP_4$  du générateur qui est à un niveau logique 1. La nouvelle combinaison disponible est visible sur la sixième ligne du tableau de la figure 2. Enfin, la première sortie du générateur étant au niveau logique 1, on recherche le rang de l'autre sortie qui est à un niveau logique 1. Cette autre sortie est la sortie  $QP_4$  de rang  $r=4$ . On fait alors passer la sortie  $QP_1$  à 0 et la sortie  $QP_{r+1}$ , c'est-à-dire la sortie  $QP_5$ , au niveau logique 1. On obtient alors une autre combinaison de niveaux logiques 1 disponibles sur les sorties  $QP_4$  et  $QP_5$  du générateur ; cette combinaison est visible sur la septième ligne du tableau de la figure 2 et l'on pourrait poursuivre de façon analogue pour obtenir les autres combinaisons.

L'ensemble de mémorisation P comprend en outre un ensemble E de  $N-2$  portes OU à deux entrées. Les deux entrées de chacune de ces portes sont respectivement connectées aux sorties  $(QJ_2, QK_2)$ ,  $(QJ_3, QK_3), \dots (QJ_{N-1}, QK_{N-1})$ , correspondant à des bascules de même rang  $(J_2, K_2)$ ,  $(J_3, K_3), \dots (J_{N-1}, K_{N-1})$ , des registres J et K. C'est ainsi par exemple que la première porte OU 10 de l'ensemble E présente deux entrées qui sont respectivement reliées aux sorties  $QJ_2$  et  $QK_2$  des registres J et K. La sortie de la première bascule  $J_1$  du registre J et la sortie du dernier registre  $K_N$  du registre K constituent les première et dernière sorties  $(QP_1 \text{ et } QP_N)$  de l'ensemble P de mémorisation. Les sorties des  $N-2$  portes OU de l'ensemble P constituent respectivement les sorties  $QP_2, QP_3, \dots QP_{N-1}$  de cet ensemble. Les moyens de chargement, de commande de décalage et de transfert CH, appliquent des signaux d'initialisation INITJ et INITK aux registres J et K, des signaux de remise à zéro RAZ au registre K et des signaux de décalage CJ, CK, à chacun de ces registres respectivement, ainsi que des

signaux de transfert CW qui sont appliqués aux moyens de transfert W. Les moyens de commande M sont reliés à la première sortie  $QP_1$  des moyens de mémorisation de l'ensemble P pour commander, comme on le verra par la suite, selon le niveau de cette sortie  $QP_1$ , la génération des combinaisons, par l'intermédiaire des moyens de chargement CH, des moyens de transfert W et des moyens d'arrêt A. Ces moyens de commande M comprennent des moyens de contrôle X dont une entrée est reliée à la sortie  $QP_1$  des moyens de mémorisation de l'ensemble P, pour repérer comme on le verra plus loin en détail, si cette sortie est au niveau logique 1. Ces moyens de commande comprennent aussi un circuit de validation VA qui permet de valider les opérations effectuées par les moyens de chargement, de commande de décalage et de transfert CH et de valider les opérations effectuées par les moyens de transfert W. Cette validation s'effectue à partir d'impulsions fournies par une horloge H. Une sortie de ces moyens de validation VA est reliée à une autre entrée des moyens de contrôle X pour leur appliquer un signal  $CP_1$ . Les moyens de commande M comprennent également des moyens Z qui permettent d'indiquer qu'une combinaison de niveaux logiques 1, est présente sur deux des sorties  $QP_1, \dots, QP_N$  des moyens de mémorisation de l'ensemble P. La présence d'une combinaison est indiquée sur une des sorties de ces moyens Z, par la présence d'un signal COMBINOK. Ces moyens Z permettent également de commander la recherche d'une autre combinaison, par l'application sur l'une de leurs entrées, d'un signal COMBINSUIV. Ces moyens Z reçoivent aussi sur d'autres entrées des signaux d'initialisation (INITPA) et de validation (VALIDPA). Une sortie de ces moyens d'indication Z est reliée à une autre entrée du circuit de validation VA, pour que ces moyens commandent les opérations effec-

tuées par les moyens de chargement, de commande de décalages et de transfert CH, et commandent les opérations effectuées par les moyens de transfert W, à partir des impulsions de l'horloge H. Enfin, les moyens d'arrêt A présentent une sortie qui est reliée à une autre entrée des moyens de validation VA. Cette sortie permet de bloquer ces moyens de validation et permet donc de bloquer l'horloge H, lorsque toutes les combinaisons désirées ont été obtenues sur les sorties de moyens de mémorisation de l'ensemble P. Ces moyens d'arrêt A reçoivent sur des entrées, les signaux de commande de transfert CW appliqués aux moyens de transfert W ainsi que les signaux de commande de décalage CJ, appliqués au premier registre J des moyens de mémorisation de l'ensemble P.

Les moyens de transfert W comprennent un premier circuit logique  $CL_1$  constitué par exemple par un amplificateur-inverseur dont une entrée est reliée à une sortie de commande des moyens de chargement et de commande CH qui appliquent à l'entrée de cet amplificateur les signaux de commande de transfert CW. Une sortie de ce premier circuit logique  $CL_1$  est reliée à une entrée de commande CL de la première bascule  $J_1$  du premier registre à décalage J, pour permettre, comme on le verra par la suite, de mettre à un niveau logique 0 la sortie  $QP_1$  de cette bascule, lorsque le niveau de celle-ci, repéré par les moyens de contrôle X, est le niveau 1. Les moyens de transfert W comprennent aussi un ensemble de seconds circuits logiques  $CL_2$ ,  $CL_3, \dots, CL_{N-1}$  qui sont repérés du rang 2 au rang N-1 et qui correspondent respectivement aux bascules de même rang des premier et deuxième registres à décalage J, K. Chaque second circuit logique présente deux entrées qui sont reliées respectivement à une sortie de la bascule de même rang du deuxième registre à décalage K

et à la sortie de commande des moyens de chargement et de commande CH, qui fournissent les signaux de commande de transfert CW. C'est ainsi par exemple que dans l'exemple de réalisation représenté sur la figure, le second circuit logique  $CL_2$  présente une entrée qui est reliée à la sortie  $QK_2$  de la bascule  $K_2$  de même rang du registre à décalage K, et une entrée qui est reliée à la sortie des moyens de commande CH qui fournit les signaux de commande CW. Chacun des seconds circuits logiques de l'ensemble de transfert W présente deux sorties qui sont reliées respectivement à deux entrées de commande de la bascule de même rang du premier registre J. C'est ainsi par exemple que dans le mode de réalisation représenté sur la figure, l'une des sorties du circuit logique  $CL_2$  est reliée à l'entrée PR de la bascule  $J_2$ , tandis que l'autre sortie de ce circuit logique  $CL_2$ , est reliée à une autre entrée de commande de cette bascule. Comme on le verra plus loin en détail, les moyens de commande CH agissent sur les circuits logiques des moyens de transfert W, de manière que :

- lorsque la sortie  $QP_1$  de la première bascule  $J_1$  du premier registre à décalage  $J$  est au niveau logique 0, les moyens  $CH$  provoquent, par une sortie de commande fournissant des signaux de commande de décalage  $CK$  du premier registre  $J$ , un décalage de un rang dans le contenu des bascules du premier registre  $J$  ; ce décalage est effectué des bascules de rangs forts vers les bascules de rangs faibles, par application d'un signal de niveau logique 0 et sur l'entrée  $D$  de la dernière bascule  $J_{N-1}$  du registre  $J$ . Dans l'exemple de réalisation représenté sur la figure, ce décalage est effectué en appliquant un signal de niveau logique 0 sur l'entrée  $D$  de la bascule  $J_4$ . Ce décalage fait passer la sortie  $QP_i$  qui était au ni-

veau logique 1, au niveau logique 0, et la sortie  $QP_{i-1}$  qui était au niveau logique 0, au niveau logique 1.

5 Lorsque la sortie  $QP_1$  de la première bascule  $J_1$  du premier registre à décalage J, est au niveau logique 1, les moyens de chargement et de commande CH commandent le premier circuit logique  $CL_1$  pour mettre au niveau logique 0 la sortie  $QP_1$  de la première bascule  $J_1$ ; ces moyens commandent aussi un autre circuit logique  $CL_r$  correspondant à une bascule  $K_r$  du rang r, qui est au niveau logique 1, pour effectuer le transfert du niveau 1 de la bascule  $K_r$  dans la bascule  $J_r$  de même rang (la bascule  $K_r$  restant au niveau 1).

10 les moyens de chargement et de commande agissent ensuite pour décaler le contenu de la bascule  $K_r$  de un rang, ce décalage étant effectué des bascules de rangs faibles, vers les bascules de rangs forts et faisant passer la sortie  $QP_{r+1}$  qui était au niveau logique 0, au niveau logique 1.

15

20 Les moyens d'arrêt A comprennent un compteur CPPO, chargé par un registre R, à l'initialisation du générateur. Ce compteur est activé à chaque opération de décalage et de transfert, de manière que ces opérations de décalage et de transfert soient arrêtées

25 lorsque le contenu du compteur est égal à 0. La sortie de ce compteur est reliée à l'entrée des moyens de validation VA pour bloquer les opérations de décalage, lorsque toutes les combinaisons ont été obtenues, soit à partir de la première combinaison disponible sur les sorties du générateur, (le compteur étant initialement chargé à la valeur N-2), soit à partir d'une autre combinaison prédéterminée de départ. Ce blocage sur une combinaison prédéterminée est effectué grâce à un circuit logique constitué, comme on le verra par la suite, par les portes ET 20, OU 15, et par l'inverseur

30

35

INV<sub>1</sub>. La porte ET 20 est une porte à deux entrées qui sont reliées respectivement aux sorties de deux des portes OU 10 de l'ensemble E correspondant à la combinaison prédéterminée sur laquelle on décide de bloquer

5 la génération des combinaisons sur les sorties du générateur. La sortie de cette porte ET 20 est reliée à l'une des entrées de la porte OU 15 qui agit sur les moyens de validation VA par l'intermédiaire de l'inverseur INV<sub>1</sub>. Les moyens d'arrêt A comprennent en

10 outre un registre R qui est chargé à la valeur N-2 à chaque initialisation du premier registre J par le signal CW. Le compteur décompte d'une unité à chaque décalage ou transfert du contenu des registres. A cet effet, il reçoit les signaux de sortie CW et CJ provenant des moyens de chargement et de commande CH.

15

La figure 3 est un tableau plus détaillé qui donne les niveaux logiques sur les sorties des registres à décalage J et K de l'ensemble de mémorisation P du générateur. Comme on l'a indiqué plus haut, la sortie QP<sub>1</sub> des moyens de mémorisation de l'ensemble P est constituée par la sortie QJ<sub>1</sub> du premier registre à décalage J, tandis que la dernière sortie QP<sub>N</sub> (QP<sub>5</sub> dans l'exemple décrit) est constituée par la sortie QK<sub>N</sub> (QK<sub>5</sub> dans l'exemple) du deuxième registre K de

20 l'ensemble de mémorisation P. Les sorties QP<sub>2</sub>, ..., QP<sub>N-1</sub> (QP<sub>4</sub> dans l'exemple) sont constituées respectivement par les sorties des portes OU de l'ensemble E qui reçoivent respectivement sur leurs entrées, les signaux des sorties (QJ<sub>2</sub>, QK<sub>2</sub>), ..., (QJ<sub>N-1</sub>, QK<sub>N-1</sub>) des registres à décalage J et K. Comme on l'a indiqué plus haut aussi, les moyens de commande CH agissent sur les circuits logiques des moyens de transfert W, de manière à obtenir sur les sorties du générateur toutes les combinaisons désirées de deux sorties à un niveau logique

25 1. On suppose dans ce tableau que la combinaison pré-

déterminée de départ est la première combinaison disponible sur les sorties du générateur, c'est-à-dire une combinaison qui fournit des niveaux logiques 1 sur les deux premières sorties  $QP_1$  et  $QP_2$ . Dans ce cas, la 5 sortie  $QJ_1$  du premier registre à décalage J est à un niveau logique 1 et la sortie  $QK_2$  du deuxième registre à décalage K est aussi à un niveau logique 1. Les moyens de commande CH agissent alors sur les circuits logiques des moyens de transfert W de la manière suivante : la sortie  $QP_1$  de la bascule  $J_1$  étant au niveau 10 logique 1, les moyens de commande CH agissent sur le circuit logique  $CL_1$  des moyens de transfert W, pour mettre la sortie  $QP_1$  au niveau logique 0. Ce changement de niveau est visible sur la deuxième ligne du tableau relatif au registre J. Les moyens de commande CH agissent alors sur le circuit logique  $CL_2$ , de rang  $r=2$  pour opérer un transfert du niveau logique 1 de la 15 bascule  $K_2$ , dans la bascule  $J_2$ . Cette opération est visible sur la deuxième ligne du tableau relatif au registre J et sur la première ligne du tableau relatif au registre K. Les moyens de commande CH provoquent ensuite un décalage de un rang du niveau logique 1 de la 20 sortie  $QK_2$  de la bascule  $K_2$ , vers les bascules de rangs forts. Ce décalage est visible sur la deuxième ligne du tableau relatif au registre K. La nouvelle 25 combinaison de niveaux logiques 1, est disponible sur les sorties  $QP_2$  et  $QP_3$  de l'ensemble P.

La sortie  $QP_1$  (correspondant à la sortie  $QJ_1$ ) étant au niveau logique 0, les moyens de commande CH provoquent un décalage de un rang vers les rangs faibles, du niveau logique 1 disponible sur l'une des sorties des bascules du registre J. C'est ainsi que dans l'exemple considéré, le niveau logique 1 de la 30 sortie  $QJ_2$  de la bascule  $J_2$ , est décalé de un rang vers les rangs faibles et qu'ainsi, la sortie  $QJ_1$  de 35

la bascule  $J_1$  passe au niveau logique 1. Ce décalage est visible sur la troisième ligne du tableau relatif au registre J. La bascule  $K_3$ , dont la sortie  $QK_3$  était au niveau logique 1, ne change pas d'état. Une nouvelle combinaison est alors disponible sur les sorties  $QP_1$  et  $QP_3$  de l'ensemble de mémorisation P.

De la même manière que précédemment, la sortie  $QP_1$  de la première bascule  $J_1$  étant au niveau logique 1, les moyens de commande CH agissent sur les moyens de mémorisation, de manière à faire passer la 10 sortie  $QJ_1$  de la bascule  $J_1$  au niveau logique 0 (quatrième ligne du tableau relatif au registre J). Ces moyens de mémorisation agissent ensuite sur le circuit 15 logique  $CL_3$  pour commander le transfert vers la bascule  $J_3$  du niveau logique 1 disponible sur la sortie  $QK_3$  de la bascule  $K_3$ . Les moyens de commande CH provoquent ensuite un décalage de un rang vers les rangs forts, du contenu de la bascule  $K_3$ ; il en résulte que la 20 sortie  $QK_4$  de la bascule  $K_4$  passe au niveau logique 1. Ce décalage est visible sur la quatrième ligne du tableau relatif au registre K. Une nouvelle combinaison de deux niveaux logiques 1 est donc disponible sur les 25 sorties  $QP_3$  et  $QP_4$  du générateur. L'obtention des autres combinaisons se fait de la même manière et ne sera pas décrite de façon plus détaillée.

De manière plus détaillée, le générateur de l'invention fonctionne de la manière suivante : il y a un seul niveau logique 1 dans le registre K et un seul niveau logique 1 dans le registre J ; le niveau 1 du 30 registre J se situe dans une bascule qui présente un rang inférieur à celui de la bascule du registre K qui contient un niveau logique 1. Comme on l'a indiqué plus haut, la sortie  $QP_i$  de rang i des moyens de mémorisation est une fonction logique OU entre les sorties 35  $K_i$  et  $J_i$  des registres K et J. D'une manière générale,

les moyens de transfert W permettent de transférer, grâce à des impulsions CW, le niveau logique de la bascule  $K_2$  dans la bascule  $J_2$ , le niveau logique de la bascule  $K_3$  dans la bascule  $J_3$ ..., le niveau logique de la bascule  $K_{N-1}$  dans la bascule  $J_{N-1}$ , ainsi qu'un niveau logique 0 dans la bascule  $J_1$ . Pendant ce transfert, les bascules du registre K conservent leur niveau logique de sortie. Les impulsions CW sont appliquées aux moyens de transfert W, par la sortie d'une porte OU 1 des moyens de commande CH ; cette porte est reliée par l'une de ses entrées, à la sortie d'une porte ET 7 des moyens de contrôle X. L'autre entrée de la porte OU 1 reçoit, à l'initialisation du générateur, un signal INITJ qui permet d'initialiser le registre J. La porte ET 7 présente des entrées qui sont respectivement reliées à une sortie des moyens de validation VA et à la sortie de la porte OU 1. On a supposé, dans l'exemple de réalisation représenté sur la figure, que chaque bascule D du registre J mémorise le niveau logique existant sur l'entrée D, lors du front montant du signal, sur l'entrée CK de cette bascule. Les entrées CL et PR des bascules du registre J sont considérées comme actives, lorsqu'elles reçoivent un signal de niveau logique 0. Dans ce cas d'un signal appliqué sur CL et PR, la sortie de la bascule D passe respectivement à un niveau logique 0 et 1. Dans l'exemple de réalisation représenté sur la figure, on suppose qu'un niveau logique 0 est constamment appliqué sur l'entrée D de la dernière bascule du registre J, pour qu'un décalage s'effectue en entrant des niveaux logiques 0 des rangs forts des bascules de ce registre, vers les rangs faibles de ces bascules, lorsqu'une impulsion CJ est appliquée sur les entrées CK de ces bascules ; cette impulsion CK est fournie par la sortie d'une porte OU 2 des moyens de commande CH ; l'une des entrées de cette porte est reliée à la

sortie d'une porte ET 8 des moyens de contrôle X, tandis qu'une autre entrée de cette porte reçoit, à l'initialisation du générateur, une impulsion CJINIT qui permet d'initialiser l'état des bascules du registre J. La porte ET 8 est reliée d'une part à une sortie des moyens de validation VA et d'autre part, par l'intermédiaire d'un inverseur INV<sub>2</sub>, à la sortie de la première bascule J<sub>1</sub> du registre J, de manière à commander les transferts et les décalages, en fonction de l'état de la sortie de cette première bascule.

Lorsque l'on désire effectuer le transfert du niveau logique de la sortie QK<sub>2</sub> de la bascule K<sub>2</sub> du registre K, vers la bascule J<sub>2</sub> du registre J, on envoie une impulsion CW de niveau 1 sur l'entrée des moyens de transfert W. Si la sortie QK<sub>2</sub> est au niveau logique 1, la porte ET 21 (dont la sortie est inversée) du circuit logique CL<sub>2</sub>, transmet un signal de niveau logique 0 sur l'entrée PR de la bascule J<sub>2</sub> et provoque la mise à 1 du niveau logique de la sortie QJ<sub>2</sub> de cette bascule. Par contre, un signal de niveau logique 1 est transmis sur l'entrée CL de la bascule J<sub>2</sub> par la porte ET 24 (cette porte présente une entrée et une sortie inversée). Le signal de niveau logique 1 appliqué sur l'entrée CL de la bascule J<sub>2</sub> ne modifie pas l'état de cette bascule. Par contre, si la sortie QK<sub>2</sub> de la bascule K<sub>2</sub> est au niveau logique 0, la commande de la bascule J<sub>2</sub> s'effectue par l'intermédiaire de la porte ET 24, qui applique alors un signal de niveau logique 0 sur l'entrée CL de cette bascule. L'application d'une impulsion CW, par l'intermédiaire de l'inverseur INV<sub>1</sub> du circuit logique CL<sub>1</sub>, provoque la remise à zéro de la bascule J<sub>1</sub>. Le fonctionnement du dispositif est alors le suivant : on initialise le registre K par une impulsion INITK provenant des moyens de commande CH ; cette impulsion est appliquée

sur l'entrée PR de la bascule  $K_2$  du registre K et sur les entrées RAZ des autres bascules de ce registre. Cette impulsion permet d'obtenir un niveau logique 1 sur la sortie  $QK_2$  de la bascule  $K_2$  du registre K et des niveaux logique 0 sur toutes les autres sorties, du rang 2 au rang N, de ce registre. On initialise ensuite le registre J par une impulsion INITJ appliquée à la porte OU 1 dont la sortie fournit alors une impulsion CW. Cette impulsion provoque un transfert du niveau logique 1 présent sur la sortie  $QK_2$  du registre K ainsi qu'une remise à zéro de la bascule  $J_1$ . Cette impulsion INITJ est suivie d'une impulsion CJINIT appliquée à la porte OU 2 ; la sortie de cette porte fournit alors une impulsion CJ qui est appliquée sur les entrées CK des bascules du registre J. Par suite de l'application de cette impulsion au registre J, la sortie  $QJ_1$  de la première bascule  $J_1$  du registre J, passe au niveau logique 1, tandis que toutes les sorties des bascules de rang 2 à N-1 du registre J sont au niveau logique 0.

Après ces opérations, les sorties  $QP_1$  et  $QP_2$  des moyens de mémorisation, sont à un niveau logique 1. Les sorties  $QP_j$  de rang j compris entre 3 et N, sont à un niveau logique 0. Cette combinaison de niveaux logiques 1 sur les sorties  $QP_1$  et  $QP_2$ , constitue la première combinaison disponible sur les sorties du générateur.

Pour rechercher la combinaison suivante, une impulsion d'horloge  $CP_1$ , fournie par les moyens de validation VA, est appliquée aux moyens de contrôle X. Ces moyens de validation sont constitués par deux portes ET 22 et ET 23 ; la porte ET 22 présente une entrée qui est reliée à la sortie des moyens d'arrêt A et une autre entrée qui est reliée à la sortie de l'horloge H. La porte ET 23 a une entrée qui est reliée à la

sortie de la porte ET 22 et à la sortie des moyens Z d'indication de combinaison. Les moyens de contrôle X sont conditionnés par la valeur du niveau logique de la sortie  $QJ_1$  de la première bascule de registre J :

5 - si la sortie  $QJ_1$  est à un niveau logique 1, il en résulte, comme on l'a indiqué plus haut, un transfert du contenu de la bascule du registre K dont la sortie est à un niveau logique 1, dans la bascule de même rang du registre J et une remise à zéro de la bascule  $J_1$ . Ce transfert et cette remise à zéro sont effectués grâce à l'application d'une impulsions CW, aux moyens de transfert W ; cette impulsions résulte de l'impulsion  $CP_1$  appliquée à la porte ET 7 conditionnée par l'impulsion CW. On effectue ensuite un décalage du contenu du registre K, par application d'une impulsions CK sur une entrée de décalage de la première bascule du registre K ; cette impulsions CK est fournie par une porte OU 3 des moyens de contrôle CH ; une entrée de cette porte est reliée à la sortie de la porte ET 8 des moyens de contrôle X, tandis qu'une autre entrée de cette porte reçoit, à l'initialisation du générateur, un signal CKINIT. L'impulsion CK résulte de l'impulsion d'horloge  $CP_1$  appliquée à l'entrée de la porte ET 8 conditionnée par l'impulsion  $QJ_1$ . Les différentes portes sont choisies de façon que le décalage du contenu du registre K ne soit efficace qu'après le transfert du contenu de la bascule du registre K dans la bascule de même rang du registre J.

10 20 25 30 35 - si la sortie  $QJ_1$  de la bascule  $J_1$  du registre J est à un niveau logique 0, on effectue un décalage du contenu de ce registre, de un rang, à partir des bascules de rangs forts vers les bascules de rangs faibles. Ce décalage est effectué grâce à l'application permanente d'un niveau logique 0 sur l'entrée D de

la dernière bascule du registre J et par l'application d'une impulsion d'horloge CJ sur les entrées CK des bascules de ce registre. La combinaison qui est alors obtenue est celle qui correspond à la présence de deux niveaux logiques 1 sur les sorties  $QP_2$  et  $QP_3$  des moyens de mémorisation de l'ensemble P. La combinaison suivante est obtenue en décalant le contenu du registre J vers les bascules de rangs faibles de ce registre ; cette autre combinaison correspond à la présence de niveaux logiques 1 sur les sorties  $QP_1$  et  $QP_3$  des moyens de mémorisation de l'ensemble P. Les autres combinaisons sont obtenues de la même manière, en fonction du niveau de la sortie  $QJ_1$ .

Le générateur qui vient d'être décrit peut être initialisé sur une combinaison prédéterminée de départ qui n'est pas la première combinaison disponible (la première combinaison disponible correspondant à  $QP_1 = 1$  et  $QP_2 = 1$ ). Dans ce cas, un niveau 1 est placé dans la première bascule du registre K, grâce à une impulsion INITK appliquée sur l'entrée PR de ce registre. Ce niveau 1 est propagé en position convenable (au niveau 1 de plus fort poids de la combinaison initiale qui est choisie), grâce à des impulsions CKINIT appliquées sur l'entrée de la porte OU 3 des moyens de commande CH. Ces impulsions provoquent des décalages du contenu des bascules du registre K, tout en plaçant les niveaux 0 sur l'entrée de la bascule  $K_2$ , lors de ces décalages.

Cette initialisation du générateur, sur une combinaison particulière, consiste ensuite à placer un niveau 1 dans le registre J, grâce à l'application d'une impulsion INITJ à l'entrée de la porte OU 1 ; de cette impulsion INITJ résulte une impulsion CW sur les entrées de commande des bascules du registre J. Cette

impulsion CW provoque le transfert du niveau 1 présent sur une sortie d'une bascule du registre K, dans la bascule de même rang du registre J et elle provoque également la mise à zéro de la sortie QJ<sub>1</sub> de la première bascule J<sub>1</sub> du registre J (par l'intermédiaire des moyens W). Ce niveau logique 0 est ensuite éventuellement décalé, en position adéquate par une impulsion CJINIT appliquée à la porte OU 2 ; à cette impulsion CJINIT correspond une impulsion CJ qui provoque un décalage du niveau 1 contenu dans l'une des bascules du registre J, vers les bascules de rangs faibles ; à cet effet et comme on l'a indiqué plus haut, un niveau logique 0 est appliqué en permanence sur l'entrée 2 de la dernière bascule du registre J, pendant ces décalages.

De manière encore plus détaillée, le fonctionnement du générateur à partir de la première combinaison qui fournit des niveaux logique 1 sur les sorties QP<sub>1</sub> et QP<sub>2</sub> est le suivant : les moyens de commande CH émettent un signal INITPA qui met à zéro le signal COMBINOK à la sortie des moyens Z d'indication, qui seront décrits plus loin en détail. Le signal COMBINOK permet d'indiquer que la combinaison n'est pas présente sur les sorties des moyens de mémorisation de l'ensemble P. Le signal INITPA est maintenue au niveau 1, de façon à bloquer l'horloge H, par l'intermédiaire de la porte ET 23. Ensuite, les moyens de commande CH émettent l'impulsion INITK, puis l'impulsion INITJ, suivie de CJINIT, comme indiqué plus haut. Enfin, les moyens de commande CH émettent le signal VALIDPA qui met à 1 le signal COMBINOK, pour indiquer que la première combinaison est présente sur les sorties des moyens de mémorisation de l'ensemble P. Le signal INITPA est alors remis à zéro, avant la fin du signal VALIDPA de façon à permettre la mise au niveau

logique 1 de la bascule PA des moyens d'indication Z,

grâce au signal VALIDPA qui bloque l'horloge H et pour

permettre à la bascule PA de basculer entre la fin du

signal INITPA et la fin du signal VALIDPA. Lorsque la

5 bascule PA est passée au niveau logique 1, l'horloge

est alors bloquée et reste bloquée grâce au signal

COMBINOK. L'utilisateur du générateur envoie alors un

10 signal COMBINSUIV pour indiquer qu'il faut procéder à

la recherche de la combinaison suivante : pour la re-

cherche de cette autre combinaison, la bascule PA va-

lide l'horloge par l'intermédiaire des moyens de vali-

dation VA qui fournissent une impulsion CP<sub>1</sub>. Les por-

tes ET 22 et ET 23 sont en fait constituées à partir

15 des circuits synchronisateurs (de type 74120 commer-

cialisés par la Société TEXAS INSTRUMENTS). Ces cir-

cuits synchronisateurs ne laissent passer des impul-

sions complètes que si et seulement si le signal de

validation est à 1 au moment de la transition 0-1 de

20 l'impulsion d'horloge reçue. L'impulsion CP<sub>1</sub> déclen-

che alors, par l'intermédiaire des moyens de contrôle

X, les opérations suivantes :

- soit un transfert du niveau 1 d'une bascule du re-

gistre K dans la bascule de même rang du registre J,

puis la mise à zéro de la bascule J<sub>1</sub>, et enfin un

25 décalage du contenu du registre K, vers les bascules

de rangs forts, si la sortie QJ<sub>1</sub> de la bascule J<sub>1</sub>

est à un niveau 1 ;

- soit un décalage du contenu du registre J vers les

rangs faibles, si la sortie QJ<sub>1</sub> de la bascule J<sub>1</sub> est

30 au niveau logique 0.

35 L'impulsion CP<sub>1</sub> déclenche aussi, avec un

certain temps de retard, la mise au niveau logique 1

du signal COMBINOK, pour indiquer que la combinaison

suivante est présente sur les sorties de l'ensemble de

mémorisation P.

Le processus recommence alors à partir du signal COMBINSUIV.

Les moyens d'arrêt A comprennent d'une part un compteur CPP<sub>0</sub> qui est chargé à partir d'un registre R à la valeur N-2, au moment de la réception du signal CW, à l'initialisation du dispositif. Ce compteur décompte de une unité à chaque fois qu'il reçoit une impulsion CJ provenant de la sortie de la porte OU 2. Lorsque le contenu de ce compteur est égal à zéro, la sortie de ce compteur bloque l'horloge H par l'intermédiaire de la porte ET 22, de la porte OU 15 et de l'inverseur INV 15. Le contenu de ce compteur est égal à zéro lorsque la dernière combinaison est présente sur les sorties des moyens de mémorisation de l'ensemble P.

Lorsque le générateur doit commencer à fonctionner à partir d'une combinaison particulière qui n'est pas la combinaison correspondant à des niveaux 1 sur les sorties QP<sub>1</sub> et QP<sub>2</sub>, le fonctionnement du générateur est le suivant :

Les moyens de commande CH émettent le signal INITPA qui est maintenu au niveau logique 1. Ces moyens de commande émettent ensuite l'impulsion INITK, puis des impulsions CKINIT, pour positionner dans le registre K le niveau 1 à la position correspondant au poids le plus fort à 1, dans la combinaison choisie. Les moyens de commande CH émettent ensuite l'impulsion INITJ, puis des impulsions CJINIT, pour positionner dans le registre J le niveau 1 de poids le plus faible, en position convenable. Enfin, les moyens de commande CH émettent le signal VALIDPA ; le signal INITPA est alors remis à zéro avant le signal VALIDPA. À partir de cette opération, on trouve toutes les combinaisons suivantes, en appliquant à la bascule PA des signaux successifs COMBINSUIV.

Lorsque le générateur qui vient d'être décrit fonctionne à partir de la première combinaison disponible, c'est-à-dire à partir de la combinaison pour laquelle les sorties  $QP_1$  et  $QP_2$  des moyens de mémorisation P sont à un niveau logique 1, alors que toutes les autres sorties  $QP_3 \dots QP_n$  sont à un niveau logique 0, les moyens d'indication et de recherche de combinaisons reçoivent un signal INITPA au niveau logique 1, qui est maintenu pour bloquer l'horloge. Ces moyens d'indication de recherche de combinaison comprennent une bascule PA de type D dont l'entrée D est au niveau logique 0. Le signal INITPA est appliqué à l'entrée CLEAR de la bascule PA, par l'intermédiaire d'un inverseur INV 20 appartenant aux moyens Z. Il en résulte que la bascule PA met à zéro le signal COMBINO<sub>K</sub>, pour indiquer que la combinaison n'est pas présente. Le signal INITPA réalise aussi le blocage de l'horloge H par l'intermédiaire de la porte OU 20 dont le signal de sortie est inversé, avant d'être appliqué à la porte ET 23. La porte OU 20 reçoit également le signal de sortie de la bascule PA et le signal VALIDPA ; ensuite, les moyens de chargement CH fournissent les signaux INITJ et INITK qui permettent d'initialiser les contenus des registres J et K. Enfin, les moyens de chargement CH appliquent le signal VALIDPA et suppriment le signal INITPA pendant la durée du signal VALIDPA, de façon à mettre à 1 le signal COMBINO<sub>K</sub>, pour indiquer que la première combinaison est présente sur les sorties des moyens de mémorisation P. Le signal VALIDPA est appliqué sur l'entrée PR de la bascule PA, par l'intermédiaire d'une porte OU 21 à sortie inversée, appartenant aux moyens Z.

Un signal COMBINSUIV est fourni à la bascule PA pour procéder à la recherche de la combinaison suivante. La bascule PA permet alors de valider l'appli-

cation des impulsions d'horloge  $CP_1$ , aux moyens de contrôle X, par l'intermédiaire de la porte ET 23 des moyens de validation VA. Ces impulsions sont également appliquées à la porte OU 21. Cette impulsion d'horloge 5  $CP_1$  déclenche, par l'intermédiaire des moyens de contrôle X, l'une des opérations suivantes : soit un décalage du contenu du registre J si les moyens de détection D n'ont pas détecté de niveaux 1 sur la bascule  $J_1$ , soit dans le cas contraire, un transfert du registre K dans le registre J et un décalage du registre K. L'impulsion  $CP_1$  déclenche alors avec un certain retard, la mise à 1 du signal COMBINOK pour indiquer qu'une combinaison est présente. Le processus recommence alors de la même manière avec l'application du 10 signal COMBINSUIV. Les moyens d'arrêt A qui comprennent le compteur CPPO chargé à la valeur N-2 par le registre R, au moment où le signal RAZJ lui est appliqué, décomptent à chaque impulsion CJ qu'ils reçoivent. Lorsque le contenu de ce compteur est égal à 0, 15 l'horloge H est bloquée par l'intermédiaire de l'inverseur INV 15 et de la porte ET 22 : la dernière combinaison est présente sur les sorties des moyens de mémorisation P.

20

En résumé, lorsque le générateur de combinaison doit fournir des combinaisons, à partir de la première combinaison, les moyens Z d'indication et de commande de démarrage, interviennent de la manière suivante :

- 25

- Les moyens de chargement CH émettent le signal INITPA qui met à zéro l'information COMBINOK pour indiquer que la combinaison n'est pas présente. INITPA est maintenu au niveau 1 de façon à bloquer l'horloge H par l'intermédiaire de la porte ET 23.

- Les moyens CH fournissent les signaux INITK puis INITJ suivis de CJINIT, comme indiqué précédemment.

- 30

- 35

- Les moyens CH fournissent VALIDPA qui met à 1 l'information COMBINOK, pour indiquer que la 1ère combinaison est présente. INITPA est alors remis à zéro avant la fin de l'impulsion VALIDPA de façon à permettre la mise à 1 de la bascule PA par le signal VALIDPA. VALIDPA bloque l'horloge H pour permettre à la bascule PA de basculer entre la fin de INITPA et la fin de VALIDPA. Lorsque la bascule PA est passée à 1, l'horloge H est alors bloquée et reste bloquée par le signal COMBINOK.

- Le signal COMBINSUIV est alors appliqué à la bascule PA pour indiquer qu'il faut procéder à la recherche de la combinaison suivante.

- La bascule PA valide alors l'horloge H qui émet une impulsion CP<sub>1</sub>. (ET 22 et ET 23 étant des portes de type décrit plus haut).

- Cette impulsion CP<sub>1</sub> déclenche par l'intermédiaire des moyens de contrôle X, la recherche de la combinaison suivante en opérant,

- soit un transfert de K dans J et mise à 0 de J<sub>1</sub> et décalage de K si J<sub>1</sub> = 1,

- soit un décalage de J vers les rangs les plus faibles si J<sub>1</sub> = 0.

- Cette impulsion CP<sub>1</sub> déclenche aussi après un certain retard la mise à 1 du signal COMBINOK pour indiquer que la combinaison est présente.

- Le processus recommence avec le signal COMBINSUIV.

- Lorsque le générateur doit générer des combinaisons, à partir d'une combinaison prédéterminée, son fonctionnement est le suivant : les moyens de contrôle CH appliquent à la bascule PA, le signal INITPA et le maintiennent au niveau 1, puis appliquent aux registres J et K les signaux INITJ et INITK. Ensuite, ces moyens fournissent des impulsions CJINIT et

CKINIT, pour positionner respectivement les niveaux 1 de poids le plus faible et de poids le plus fort dans les bascules correspondantes des registres J et K. Les moyens de contrôle CH appliquent alors le signal

5 VALIDPA à la bascule PA de manière à faire apparaître à la sortie de cette bascule le signal COMBINOK indiquant la présence d'une combinaison. A partir de cet instant, les combinaisons suivantes sont générées à chaque fois que la bascule PA des moyens Z, reçoit un

10 signal COMBINSUIV.

Il est bien évident que le générateur qui vient d'être décrit aurait pu être constitué sous forme modulaire : c'est ainsi que ce générateur pourrait être constitué par un ensemble de registres à décalage

15 J et K et par un ensemble de moyens de transfert W tels que ceux qui viennent d'être décrits, les registres à décalage et les moyens de transfert étant respectivement reliés en série. Dans cette forme modulaire, les moyens de validation VA, les moyens d'arrêt A, les

20 moyens de contrôle X et les moyens de commande CH sont communs aux ensembles de registres J et K ainsi qu'à l'ensemble des moyens de transfert W.

REVENDICATIONS

1. Générateur de signaux logiques combinés pour former des combinaisons de deux sorties au niveau logique 1 et N-2 sorties au niveau logique 0, parmi N sorties ( $QP_1, \dots, QP_N$ ) du générateur sur lesquelles sont disponibles deux signaux logiques de niveau 1 et N-2 signaux logiques de niveau 0, N étant une constante, caractérisé en ce qu'il comprend :

- un ensemble (P) de N moyens de mémorisation, ces moyens de mémorisation étant repérés du rang 1 au rang N, les combinaisons des deux sorties au niveau 1 et N-2 sorties au niveau 0 étant fournies sur des sorties ( $QP_1, \dots, QP_N$ ) de ces moyens de mémorisation de rang 1 à N ;

- des moyens (CH) pour charger dans les N moyens de mémorisation les niveaux logiques correspondant à une combinaison prédéterminée de départ, pour commander des opérations de décalage de contenus des moyens de mémorisation et pour commander, par l'intermédiaire de moyens de transfert (W), des transferts de contenus entre ces moyens de mémorisation ;

- des moyens de commande (M) pour repérer si la sortie  $QP_1$  de rang 1 des moyens de mémorisation de l'ensemble (P) est au niveau logique 1 et pour actionner les moyens de mémorisation, par l'intermédiaire des moyens de chargement et de décalage (CH) et de transfert (W) de façon :

- . à mettre la sortie  $QP_{i-1}$  à un niveau logique 1 et la sortie  $QP_i$  au niveau logique 0, la sortie  $QP_i$  étant la première sortie qui est à un niveau logique 1, en partant de la sortie de rang 1, cette action n'étant effectuée que si le rang i est supérieur à 1.

- . à mettre la sortie  $QP_1$  à un niveau logique 0 et la sortie  $QP_{r+1}$  à un niveau logique 1, cette ac-

tion n'étant effectuée que lorsque la première sortie qui est à un niveau logique 1 est la sortie  $QP_1$  de rang  $i=1$ , la sortie  $QP_r$  étant une autre sortie que la sortie  $QP_1$  et étant au niveau logique 1, l'action répétée des moyens de commande (M) fournissant les combinaisons qui suivent la combinaison prédéterminée de départ.

- des moyens (A) pour arrêter la génération des combinaisons après une autre combinaison prédéterminée.

10 2. Générateur selon la revendication 1, caractérisé en ce que ladite combinaison prédéterminée de départ est, soit la première combinaison pour laquelle les niveaux logiques 1 sont disponibles sur les sorties  $QP_1$  et  $QP_2$  des deux premiers moyens de mémorisation de l'ensemble (P), les sorties ( $QP_3, \dots, QP_N$ ) des N-2 moyens de mémorisation suivants étant au niveau logique 0, soit toute autre combinaison prédéterminée de niveaux logiques 1 disponibles sur les sorties de deux des moyens de mémorisation.

20 3. Générateur selon l'une quelconque des revendications 1 et 2, caractérisé en ce que l'ensemble (P) des N moyens de mémorisation comprend un groupe de deux registres à décalage (J, K) constitués respectivement par N-1 bascules ( $J_1, \dots, J_{N-1}$  et  $K_2, \dots, K_N$ ), le premier registre (J) présentant une entrée de décalage des contenus des bascules de rangs forts vers les bascules de rangs faibles et le deuxième registre (K) présentant une entrée de décalage des contenus des bascules de rangs faibles vers les bascules de rangs forts, les sorties ( $QJ_1, \dots, QJ_{N-1}$ ) du premier registre (J) étant repérées de 1 à N-1 et les sorties ( $QK_2, \dots, QK_N$ ) du deuxième registre (K) étant repérées de 2 à N, la première sortie ( $QP_1$ ) des moyens de mémorisation (P) étant constituée par la sortie ( $QJ_1$ ) de

la première bascule ( $J_1$ ) du premier registre (J) et la dernière sortie ( $Q_{P_N}$ ) des moyens de mémorisation (P) étant constituée par la sortie ( $Q_{K_N}$ ) de la dernière bascule ( $K_N$ ) du deuxième registre (K), l'ensemble de mémorisation (P) comprenant en outre un ensemble (E) de  $N-2$  portes OU à deux entrées, les deux entrées de ces portes OU étant respectivement connectées aux sorties  $(Q_{J_2}, Q_{K_2}) - (Q_{J_3}, Q_{K_3}) - \dots - (Q_{J_{N-1}}, Q_{K_{N-1}})$  correspondantes des bascules de même rang  $(J_2, K_2) - (J_3, K_3) - \dots - (J_{N-1}, K_{N-1})$  des registres (J, K), les sorties de ces portes OU constituant respectivement les sorties  $(Q_{P_2}, \dots, Q_{P_{N-1}})$  des moyens de mémorisation (P), les moyens de chargement de commande, de décalage et de transfert (CH) appliquant des signaux d'initialisation, de remise à zéro, de décalage ou de transfert de contenus sur des entrées correspondantes des registres (J et K) et sur des entrées des moyens de transfert (W), les moyens (M) de commande étant reliés à la première sortie ( $Q_{P_1}$ ) des moyens de mémorisation de l'ensemble (P) pour commander selon le niveau logique de cette première sortie, la génération des combinaisons, par l'intermédiaire des moyens de chargement (CH), des moyens de transfert (W) et des moyens d'arrêt (A).

4. Générateur selon la revendication 3, caractérisé en ce que les moyens de commande (M) comprennent des moyens de contrôle (X) dont une entrée est reliée à la première sortie ( $Q_{P_1}$ ) des moyens de mémorisation, pour repérer si cette sortie est au niveau logique 1, un circuit de validation (VA) des opérations effectuées par les moyens de chargement et de commande de décalage et de transfert (CH) et par les moyens de transfert (W), une sortie de ces moyens de validation (VA) étant reliée à une autre entrée des moyens de contrôle (X), tandis qu'une entrée de ce

circuit de validation est reliée à la sortie d'une horloge (H), des moyens (Z) pour indiquer qu'une combinaison est présente sur les sorties ( $QP_1, \dots, QP_N$ ) des moyens de mémorisation (P) ou pour commander la recherche d'une autre combinaison, ces moyens (Z) d'indication et de commande de recherche de combinaison recevant sur des entrées, des signaux d'initialisation, de validation ou de commande de recherche d'une autre combinaison, une sortie de ces moyens (Z) d'indication et de recherche de combinaison fournissant un signal indicateur de présence d'une combinaison sur les sorties des moyens de mémorisation (P), une autre sortie de ces moyens étant reliée à une autre entrée du circuit de validation (VA) pour permettre les opérations effectuées par les moyens de chargement, de commande de décalage et de transfert (CH) et par les moyens de transfert (W), à partir des impulsions de l'horloge (H), les moyens d'arrêt (A) présentant une sortie qui est reliée à une autre entrée des moyens de validation (VA) pour bloquer ces moyens de validation lorsque les combinaisons désirées ont été obtenues, ces moyens d'arrêt (A) recevant sur des entrées, des signaux de commande de transfert et de commande de décalage, appliqués au premier registre (J) et aux moyens de transfert (W) par les moyens de chargement, de commande de décalage et de transfert (CH).

5. Générateur selon la revendication 4, caractérisé en ce que les moyens de transfert (W) comprennent un premier circuit logique ( $CL_1$ ) dont une entrée est reliée à une sortie de commande des moyens de chargement, de commande de décalage et de transfert (CH), une sortie de ce premier circuit logique ( $CL_1$ ) étant reliée à une entrée de commande de la première bascule ( $J_1$ ) du premier registre à décalage (J) pour mettre à 0 le niveau de la sortie ( $QP_1$ ) de cette bas-

cule si le niveau de celle-ci, repéré par les moyens de contrôle ( $X$ ) est le niveau 1, et un ensemble de seconds circuits logiques ( $CL_2, CL_3, \dots, CL_{N-1}$ ) qui sont repérés du rang 2 au rang  $N-1$  et qui correspondent respectivement aux bascules de même rang des premier et deuxième registres à décalage ( $J, K$ ), chaque second circuit logique présentant deux entrées reliées respectivement à une sortie de la bascule de même rang du deuxième registre à décalage ( $K$ ) et à ladite sortie de commande des moyens de chargement et de commande ( $CH$ ), chaque second circuit logique présentant aussi deux sorties reliées respectivement à deux entrées de commande de la bascule de même rang du premier registre ( $J$ ), de sorte que :

- lorsque la sortie ( $QP_1$ ) de la première bascule ( $J_1$ ) du premier registre à décalage ( $J$ ) est au niveau logique 0, les moyens de chargement, de commande de décalage et de transfert ( $CH$ ) provoquent par une autre sortie de commande reliée à l'entrée de décalage du premier registre ( $J$ ), un décalage de un rang dans le contenu des bascules du premier registre ( $J$ ), ce décalage étant effectué des bascules de rangs forts vers les bascules de rangs faibles, ce décalage faisant passer la sortie ( $QP_i$ ) de l'ensemble ( $P$ ), qui était au niveau logique 1, au niveau logique 0 et la sortie ( $QP_{i-1}$ ) qui était au niveau logique 0, au niveau logique 1, le contenu du second registre ( $K$ ) restant inchangé ;

- lorsque la sortie ( $QP_1$ ) de la première bascule ( $J_1$ ) du premier registre à décalage ( $J$ ) est au niveau logique 1, les moyens de chargement, de commande de décalage et de transfert ( $CH$ ), commandent le premier circuit logique ( $CL_1$ ) pour mettre au niveau logique 0, la sortie ( $QP_1$ ) de la première bascule ( $J_1$ ) du premier registre ( $J$ ), puis commandent le second cir-

cuit logique ( $CL_r$ ) correspondant à une bascule ( $K_r$ ) de rang  $r$ , qui est au niveau 1, pour effectuer le transfert du niveau 1 de la bascule ( $K_r$ ) dans la bascule ( $J_r$ ) du rang  $r$ , la bascule ( $K_r$ ) restant au niveau 1, puis commandent ensuite le décalage du contenu dans la bascule ( $K_r$ ), de un rang, ce décalage étant effectué des bascules de rangs faibles vers les bascules de rangs forts et faisant passer la sortie ( $QP_{r+1}$ ) qui était au niveau 0, au niveau 1.

10 6. Générateur selon l'une quelconque des revendications 4 et 5, caractérisé en ce que les moyens (A) d'arrêt de génération de combinaisons comprennent un compteur (CPPO) chargé à l'initialisation du générateur, ce compteur étant activé à chaque opération de décalage ou de transfert, de manière que ces opérations de décalage ou de transfert soient arrêtées lorsque son contenu atteint 0, la sortie de ce compteur étant reliée à l'entrée des moyens de validation (VA) pour bloquer les opérations de décalage lorsque toutes les combinaisons ont été obtenues.

15 7. Générateur selon l'une quelconque des revendications 4 et 5, caractérisé en ce qu'il comprend en outre un circuit logique (ET 20, OU 15) de blocage de génération des combinaisons, à partir d'une combinaison prédéterminée, ce circuit logique présentant des entrées reliées à des sorties des moyens de mémorisation (P) qui correspondent aux sorties fournissant ladite combinaison prédéterminée, et une sortie de commande des moyens de validation (VA).

3/3

|             | QP <sub>1</sub> | QP <sub>2</sub> | QP <sub>3</sub> | QP <sub>4</sub> | QP <sub>5</sub> |

|-------------|-----------------|-----------------|-----------------|-----------------|-----------------|

| $i=1 \ r=2$ | 1               | 1               | 0               | 0               | 0               |

| $i=2$       | 0               | 1               | 1               | 0               | 0               |

| $i=1 \ r=3$ | 1               | 0               | 1               | 0               | 0               |

| $i=3$       | 0               | 0               | 1               | 1               | 0               |

| $i=2$       | 0               | 1               | 0               | 1               | 0               |

| $i=1 \ r=4$ | 1               | 0               | 0               | 1               | 0               |

|             | 0               | 0               | 0               | 1               | 1               |

FIG. 2

|     | QP <sub>1</sub> | QP <sub>2</sub> | QP <sub>3</sub> | QP <sub>4</sub> | QP <sub>5</sub> |

|-----|-----------------|-----------------|-----------------|-----------------|-----------------|

|     | QJ <sub>1</sub> | QJ <sub>2</sub> | QJ <sub>3</sub> | QJ <sub>4</sub> |                 |

| $J$ | 1               | 0               | 0               | 0               |                 |

|     | 0               | 1               | 0               | 0               |                 |

|     | 1               | 0               | 0               | 0               |                 |

|     | 0               | 0               | 1               | 0               |                 |

|     | 0               | 1               | 0               | 0               |                 |

|     | 1               | 0               | 0               | 0               |                 |

|     | 0               | 0               | 0               | 1               |                 |

|     | QK <sub>2</sub> | QK <sub>3</sub> | QK <sub>4</sub> | QK <sub>5</sub> |

|-----|-----------------|-----------------|-----------------|-----------------|

|     | 1               | 0               | 0               | 0               |

| $K$ | 0               | 1               | 0               | 0               |

|     | 0               | 1               | 0               | 0               |

|     | 0               | 0               | 1               | 0               |

|     | 0               | 0               | 1               | 0               |

|     | 0               | 0               | 1               | 0               |

|     | 0               | 0               | 0               | 1               |

FIG. 3