(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5156203号

(P5156203)

(45) 発行日 平成25年3月6日(2013.3.6)

(24) 登録日 平成24年12月14日(2012.12.14)

(51) Int.Cl.

F 1

|              |           |            |      |

|--------------|-----------|------------|------|

| HO1L 29/786  | (2006.01) | HO1L 29/78 | 616V |

| HO1L 21/28   | (2006.01) | HO1L 29/78 | 616U |

| HO1L 29/417  | (2006.01) | HO1L 29/78 | 618G |

| HO1L 21/3205 | (2006.01) | HO1L 29/78 | 617M |

| HO1L 21/768  | (2006.01) | HO1L 21/28 | 301R |

請求項の数 10 (全 19 頁) 最終頁に続く

(21) 出願番号

特願2006-191725 (P2006-191725)

(22) 出願日

平成18年7月12日 (2006.7.12)

(65) 公開番号

特開2007-27735 (P2007-27735A)

(43) 公開日

平成19年2月1日 (2007.2.1)

審査請求日

平成21年7月10日 (2009.7.10)

(31) 優先権主張番号

10-2005-0062730

(32) 優先日

平成17年7月12日 (2005.7.12)

(33) 優先権主張国

韓国 (KR)

(73) 特許権者

512187343

三星ディスプレイ株式會社

Samsung Display Co., Ltd.

大韓民国京畿道龍仁市器興区三星二路95

95, Samsung 2 Ro, Gih

eung-Gu, Yongin-City

, Gyeonggi-Do, Korea

(74) 代理人

110000408

特許業務法人高橋・林アンドパートナーズ

金湘甲

大韓民国ソウル市江東区明逸洞15番地

三益アパートメント301棟306号

最終頁に続く

(54) 【発明の名称】薄膜トランジスタ表示板及びその製造方法

## (57) 【特許請求の範囲】

## 【請求項 1】

基板と、

前記基板上に形成されているゲート線と、

前記基板上に形成されているゲート絶縁膜と、

前記基板上に形成されている半導体層と、

前記半導体層上に形成されており、ソース電極を含むデータ線と、

前記半導体層上に形成されており、前記ソース電極と対向しているドレイン電極と、

前記ドレイン電極と接続されている画素電極とを含み、

前記データ線は、アルミニウム (A1) を含む導電層、並びに前記アルミニウム (A1) を含む導電層の下部及び上部のうちの少なくとも一つに形成されているモリブデン (Mo) を含む導電層を含み、

前記半導体層は、前記データ線及び前記ドレイン電極と平面形状が実質的に同一な第1部分、及び前記データ線及び前記ドレイン電極で覆われず、前記ソース電極と前記ドレイン電極との間に位置する第2部分を含み、

前記第1部分と前記ソース電極及び前記ドレイン電極との間にのみ、塩素系ガスを含むエッティングガスにより乾式エッティングされる材料からなるオームックコンタクト層が形成され、

前記第2部分のみ、前記エッティングガスに由来する3乃至20at%の塩素原子 (C1) を含むことを特徴とする薄膜トランジスタ表示板。

10

20

**【請求項 2】**

前記モリブデン (M o) を含む導電層は、モリブデン (M o) 、窒化モリブデン (M o N) 、モリブデン - ニオビウム (M o N b) 、モリブデン - バナジウム (M o V) 、モリブデン - チタニウム (M o T i) 、モリブデン - タングステン (M o W) から選択されるいずれか一つであることを特徴とする請求項 1 に記載の薄膜トランジスタ表示板。

**【請求項 3】**

前記アルミニウム (A l) を含む導電層は、アルミニウム - ネオジム (A l N d) であることを特徴とする請求項 1 に記載の薄膜トランジスタ表示板。

**【請求項 4】**

前記データ線は、モリブデン (M o) を含む第 1 導電層、アルミニウム (A l) を含む第 2 導電層、及びモリブデン (M o) を含む第 3 導電層を含むことを特徴とする請求項 1 に記載の薄膜トランジスタ表示板。 10

**【請求項 5】**

前記ゲート線は、アルミニウム (A l) を含む導電層、及びモリブデン (M o) を含む導電層を含むことを特徴とする請求項 1 に記載の薄膜トランジスタ表示板。

**【請求項 6】**

前記アルミニウム (A l) を含む導電層は、アルミニウム - ネオジム (A l N d) であることを特徴とする請求項 5 に記載の薄膜トランジスタ表示板。

**【請求項 7】**

基板上にゲート線を形成し、

20

前記ゲート線上にゲート絶縁膜、半導体層、及びオーミックコンタクト層を形成し、

前記オーミックコンタクト層上にモリブデン (M o) を含む第 1 導電層、アルミニウム (A l) を含む第 2 導電層、及びモリブデン (M o) を含む第 3 導電層を形成し、

前記第 3 導電層上に第 1 感光膜パターンを形成し、

前記第 1 感光膜パターンをエッチングマスクとして用い、前記第 1 導電層、前記第 2 導電層、

前記第 3 導電層、前記オーミックコンタクト層、及び前記半導体層をエッチングし、

前記第 1 感光膜パターンを所定の厚さだけ除去して、第 2 感光膜パターンを形成し、

前記第 2 感光膜パターンをエッチングマスクとして用い、前記第 1 導電層、前記第 2 導電層、及び前記第 3 導電層をエッチングし、前記オーミックコンタクト層の一部を露出し 30

、

前記露出したオーミックコンタクト層を塩素 (C l) 系ガス及びフッ素 (F) 系ガスでエッチングすることを含むことを特徴とする薄膜トランジスタ表示板の製造方法。

**【請求項 8】**

前記塩素系ガスは、C l<sub>2</sub>、H C l、C C l<sub>4</sub>、B C l<sub>3</sub>、及びS i C l<sub>2</sub> H<sub>2</sub> から選択される少なくともいずれか一つであることを特徴とする請求項 7 に記載の薄膜トランジスタ表示板の製造方法。

**【請求項 9】**

前記フッ素系ガスは、S F<sub>6</sub> またはC F<sub>4</sub> であることを特徴とする請求項 7 に記載の薄膜トランジスタ表示板の製造方法。 40

**【請求項 10】**

前記露出したオーミックコンタクト層をエッチングすることは、1 0 0 乃至 8 0 0 m T の圧力下で行うことの特徴とする請求項 7 に記載の薄膜トランジスタ表示板の製造方法。

**【発明の詳細な説明】****【技術分野】****【0 0 0 1】**

本発明は薄膜トランジスタ表示板及びその製造方法に関する。

**【背景技術】****【0 0 0 2】**

50

液晶表示装置 (Liquid Crystal Display) は、現在最も広く使用されている平板表示装置 (Flat Panel Display) のうちの一つである。液晶表示装置は、電極が形成されている二枚の基板、及びその間に挿入されている液晶層からなり、電極に電圧を印加して液晶層の液晶分子を再配向させることによって、透過する光の量を調節する表示装置である。

#### 【0003】

液晶表示装置の中でも、現在主に使用されているものは、電界生成電極が二つの表示板に各々形成されている構造のものである。この中でも、一つの表示板（以下「薄膜トランジスタ表示板」という。）には複数の画素電極が形成され行列形態に配置されており、他の表示板（以下「共通電極表示板」という。）には一つの共通電極が形成され表示板の全面を覆っている構造のものが主流である。このような液晶表示装置における画像の表示は、各画素電極に別々の電圧を印加することによって行われる。このために、画素電極に印加される電圧をスイッチングするための三端子素子である薄膜トランジスタを各画素電極に接続し、この薄膜トランジスタを制御する信号を伝達するゲート線（gate line）、及び画素電極に印加される電圧を伝達するデータ線（data line）を表示板に形成する。10

#### 【0004】

薄膜トランジスタは、ゲート線を通して伝達される走査信号によって、データ線を通して伝達される画像信号を画素電極に伝達または遮断するスイッチング素子としての役割を果たす。このような薄膜トランジスタは、自発光素子である能動型有機発光表示素子（AM-OLED）でも、各発光素子を個別に制御するスイッチング素子としての役割を果たす。20

#### 【0005】

一方、薄膜トランジスタ表示板は、ゲート線及びデータ線を含む導電層、半導体層、及び絶縁層を含む複数の薄膜を含み、各薄膜は、別々のマスクを用いてパターニングされる。

#### 【0006】

しかし、一つのマスクが追加されるたびに、感光膜の塗布、露光、現像、及び洗浄工程を繰返さなければならないので、工程時間及び費用が顕著に増加する。したがって、マスクの数をできる限り減少させることが必要である。

#### 【0007】

そこで、データ金属層及び半導体層を一つのマスクでエッチングする方法が提案された。30

#### 【0008】

しかし、データ金属層及び半導体層を一つのマスクでエッチングする場合には、データ金属層の下部の全面に半導体層が残留することになる。この場合、バックライトのような光源に対して露出する半導体層の面積が広くなり、光リーク電流が急激に増加する。この光リーク電流の増加は、薄膜トランジスタの特性を低下させ、表示装置において残像として視認されることになる。

#### 【発明の開示】

#### 【発明が解決しようとする課題】

#### 【0009】

したがって、本発明が目的とする技術的課題は、このような問題を解決するためのものであって、マスクの数を減少させる場合にも、光リーク電流の急激な増加を防止して、薄膜トランジスタの特性を改善し、且つ、表示装置の残像を改善することにある。40

#### 【課題を解決するための手段】

#### 【0010】

本発明の一実施例による薄膜トランジスタ表示板は、基板と、前記基板上に形成されているゲート線と、前記ゲート線上に形成されているゲート絶縁膜と、前記ゲート絶縁膜上に形成されている半導体層と、前記半導体層上に形成されており、ソース電極を含むデータ線と、前記半導体層上に形成されており、前記ソース電極と対向しているドレイン電極と、前記ドレイン電極と接続されている画素電極とを含み、前記データ線は、アルミニウム50

(A1)を含む導電層、並びに前記アルミニウム(A1)を含む導電層の下部及び上部のうちの少なくとも一つに形成されているモリブデン(Mo)を含む導電層を含み、前記半導体層は、前記データ線及び前記ドレイン電極と平面形状が実質的に同一な第1部分、及び前記データ線及び前記ドレイン電極で覆われず、前記ソース電極と前記ドレイン電極との間に位置する第2部分を含み、前記第2部分は、3乃至20at%の塩素原子(C1)を含む。

#### 【0011】

また、本発明の一実施例による薄膜トランジスタ表示板の製造方法は、基板上にゲート線を形成し、前記ゲート線上にゲート絶縁膜、半導体層、及びオーミックコンタクト層を形成し、前記オーミックコンタクト層上にモリブデン(Mo)を含む第1導電層、アルミニウム(A1)を含む第2導電層、及びモリブデン(Mo)を含む第3導電層を形成し、前記第3導電層上に第1感光膜パターンを形成し、前記第1感光膜パターンをエッティングマスクとし用い、前記第1導電層、前記第2導電層、及び前記第3導電層をエッティングし、前記第1感光膜パターンをエッティングマスクとして用い、前記オーミックコンタクト層及び前記半導体層をエッティングし、前記第1感光膜パターンを所定の厚さだけ除去し、第2感光膜パターンを形成し、前記第2感光膜パターンをエッティングマスクとして用い、前記第1導電層、前記第2導電層、及び前記第3導電層をエッティングして、前記オーミックコンタクト層の一部を露出し、前記露出したオーミックコンタクト層を塩素系ガス及びフッ素系ガスを用いてエッティングすることを含む。

#### 【発明の効果】

#### 【0012】

本発明によれば、データ線をアルミニウム層及びモリブデン層を含む多層膜によって形成し、所定の流量比のエッティングガスを用いてチャネル領域を形成することによって、薄膜トランジスタの特性を改善し、表示装置の残像の発生を防止することができる。

#### 【発明を実施するための最良の形態】

#### 【0013】

以下、添付した図面を参照して、本発明の実施例について、本発明が属する技術分野における通常の知識を有する者が容易に実施することができるように詳細に説明する。しかし、本発明は多様な相異なる形態で実現でき、ここで説明する実施例に限定されるわけではない。

#### 【0014】

図面においては、各層及び領域を明確に表現するために厚さを拡大して示している。明細書全体を通して類似した部分については、同一な図面符号を付けている。層、膜、領域、板などの部分が他の部分の“上”にあるとするとき、これは他の部分の“真上”にある場合だけでなく、その中間に他の部分がある場合も意味する。一方、ある部分が他の部分の“真上”にあるとするとき、これはその中間に他の部分がない場合を意味する。

#### 【0015】

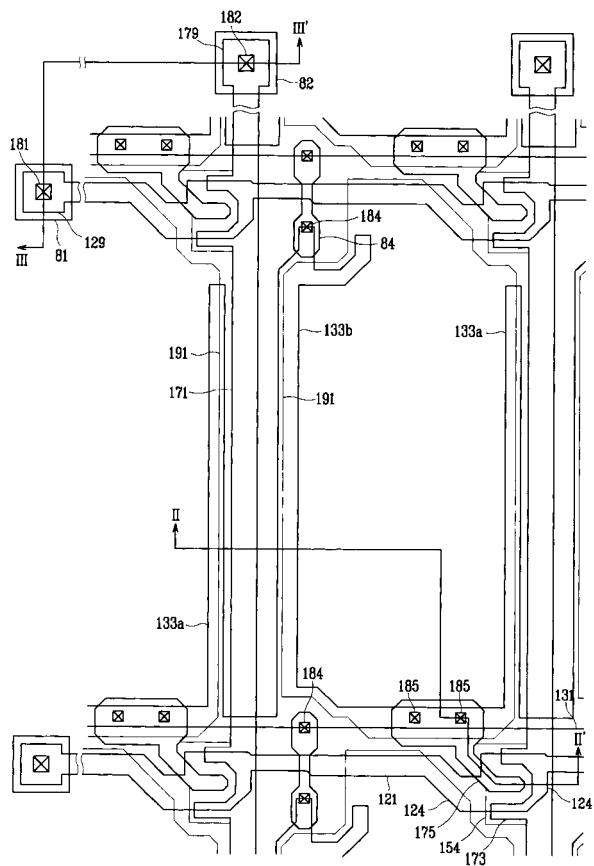

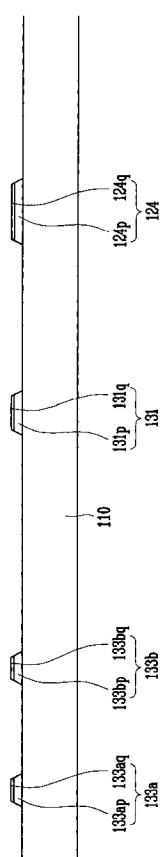

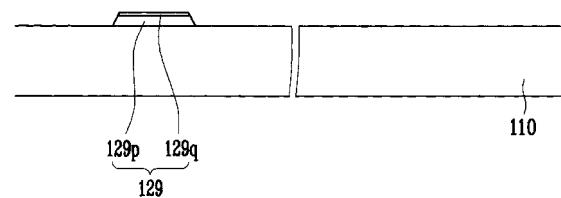

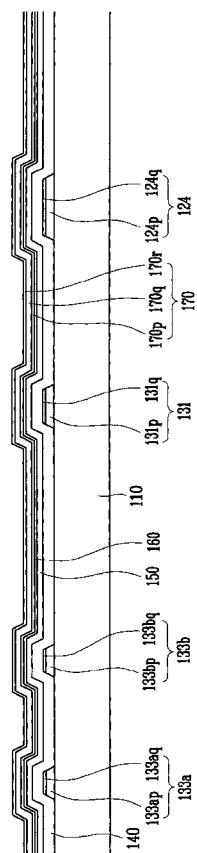

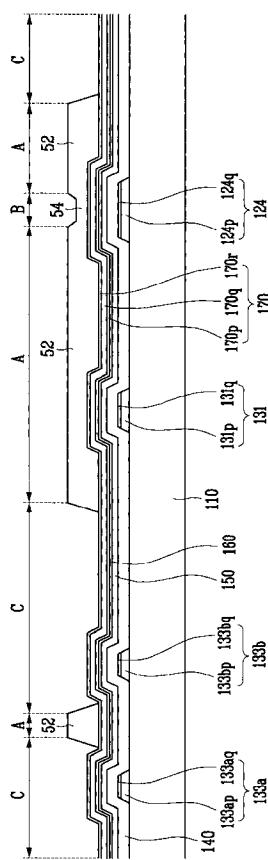

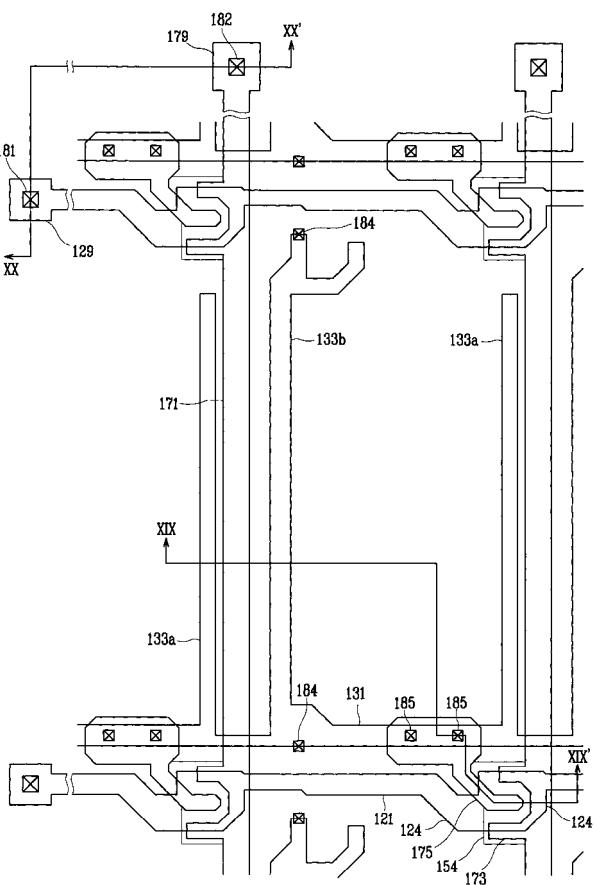

以下、図1乃至図3を参照して、本発明の一実施例による薄膜トランジスタ表示板について詳細に説明する。

#### 【0016】

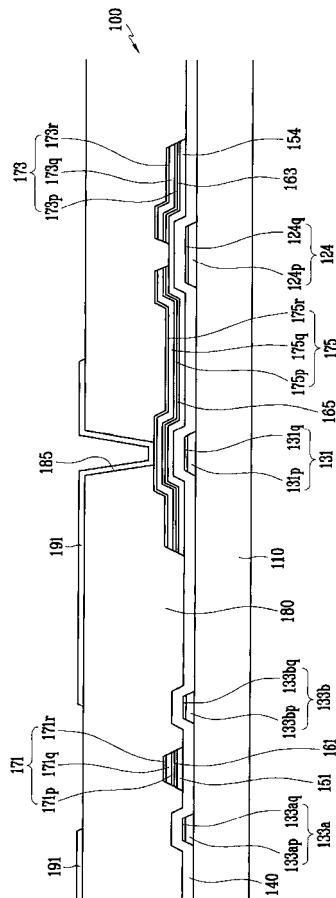

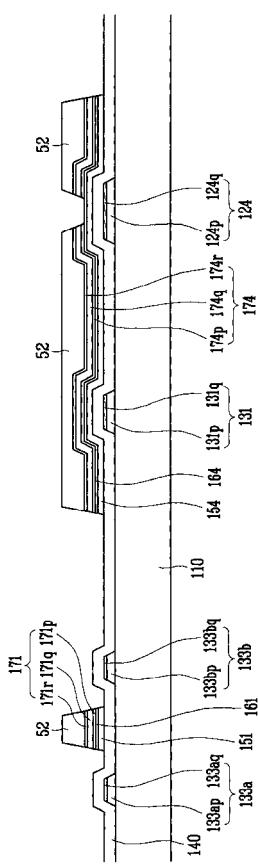

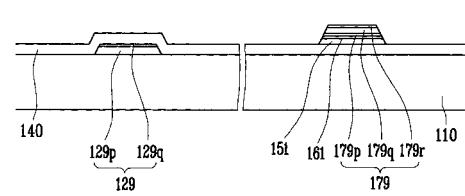

図1は本発明の一実施例による薄膜トランジスタ表示板のレイアウト配置図である。図2及び図3は各々図1の薄膜トランジスタ表示板のI I - I I '線及びI I I - I I I '線による断面図である。

#### 【0017】

透明なガラスまたはプラスチックなどからなる絶縁基板110上に、複数のゲート線(gate line)121及び複数の蓄積電極線(storage electrode line)131が形成されている。

#### 【0018】

ゲート線121は、ゲート信号を伝達し、主に横方向に延びている。各ゲート線121は、下に突出した複数のゲート電極(gate electrode)124、及び他の層

10

20

30

40

50

または外部駆動回路との接続のために面積が広い端部 129 を含む。ゲート信号を生成するゲート駆動回路(図示せず)は、基板 110 上に取り付けられるフレキシブルプリント回路フィルム(flexible printed circuit film)(図示せず)上に設けられたり、基板 110 上に直接設けられたり、基板 110 上に集積されたりする。ゲート駆動回路が基板 110 上に集積されている場合には、ゲート線 121 が延びて、これと直接接続される。

#### 【0019】

蓄積電極線 131 は、所定の電圧の印加を受け、ゲート線 121 とほぼ平行に延びた幹線、及びこれから分かれた複数対の蓄積電極 133a、133b を含む。蓄積電極線 131 の各々は、隣接する二つのゲート線 121 の間に位置し、幹線は二つのゲート線 121 のうちの下側に近く形成されている。蓄積電極 133a、133b の各々は、幹線と接続された固定端、及びその反対側の自由端を含む。ここで、蓄積電極 133b の固定端は面積が広く、自由端は直線部分及び曲線部分の二股に分かれ。しかし、蓄積電極線 131 の形状及び配置は、多様に変更することができる。

#### 【0020】

ゲート線 121 及び蓄積電極線 131 は、アルミニウム(A1)やアルミニウム合金などのアルミニウム系金属を含む下部膜 124p、131p、133ap、133bp、及びモリブデン(Mo)やモリブデン合金などのモリブデン系金属を含む上部膜 124q、131q、133aq、133bq からなる。アルミニウム合金としては、アルミニウムにネオジム(Nd)が所定の量で添加されているアルミニウム-ネオジム(A1Nd)を使用することができる。下部膜 124p、131p、133ap、133bp の厚さは約 100 乃至 500 nm であり、上部膜 124q、131q、133aq、133bq の厚さは約 5 乃至 200 nm である。

#### 【0021】

図 2 及び図 3 で、ゲート電極 124 及び蓄積電極線 131 に対して、下部膜はアルファベット p、上部膜はアルファベット q を図面符号に付け加えて表記した。

#### 【0022】

ゲート線 121 及び蓄積電極線 131 の側面は、基板 110 の面に対して傾いていて、その傾斜角は約 30° 乃至約 80° であるのが好ましい。

#### 【0023】

ゲート線 121 及び蓄積電極線 131 上には、窒化シリコン(SiNx)または酸化シリコン(SiOx)などからなるゲート絶縁膜(gate insulating layer)140 が形成されている。

#### 【0024】

ゲート絶縁膜 140 上には、水素化非晶質シリコン(hydrogenated amorphous silicon)(非晶質シリコンは略して「a-Si」という。)などからなる複数の線状半導体 151 が形成されている。線状半導体 151 は、主に縦方向に延びていて、ゲート電極 124 に向かって延びた複数の突出部(projection)154 を含む。線状半導体 151 は、ゲート線 121 及び蓄積電極線 131 付近で面積が広くなっている。これらを幅広く覆っている。

#### 【0025】

半導体 151 上には、複数の線状及び島型オーミックコンタクト部材(ohmic contact)161、165 が形成されている。オーミックコンタクト部材 161、165 は、リン(P)などのn型不純物が高濃度にドーピングされたn+水素化非晶質シリコンなどからなったり、シリサイド(silicide)からなったりするようにしてよい。線状オーミックコンタクト部材 161 は、複数の突出部 163 を含み、この突出部 163 及び島型オーミックコンタクト部材 165 は、対をなして半導体 151 の突出部 154 上に配置されている。

#### 【0026】

半導体 151 及びオーミックコンタクト部材 161、165 の側面も、基板 110 の面に

10

20

30

40

50

対して傾いていて、その傾斜角は約30°乃至80°である。

**【0027】**

オーミックコンタクト部材161、165上には、複数のデータ線(data line)171及び複数のドレイン電極(drain electrode)175が形成されている。

**【0028】**

データ線171は、データ信号を伝達し、主に縦方向に延びてゲート線121と交差している。各データ線171は、また、蓄積電極線131と交差して、隣接する蓄積電極133a、133bの集合の間に形成される。各データ線171は、ゲート電極124に向かって延びた複数のソース電極(source electrode)173、及び他の層または外部駆動回路との接続のために面積が広い端部179を含む。データ信号を生成するデータ駆動回路(図示せず)は、基板110上に取り付けられるフレキシブルプリント回路フィルム(図示せず)上に設けられたり、基板110上に直接設けられたり、基板110上に集積される。データ駆動回路が基板110上に集積されている場合には、データ線171が延びて、これと直接接続される。

10

**【0029】**

ドレイン電極175は、データ線171と分離されていて、ゲート電極124を中心にソース電極173と対向している。各ドレイン電極175は、面積が広い一側端部、及び棒形状の他側端部を含む。面積が広い端部は蓄積電極線131と重畠し、棒形状の端部は曲がったソース電極173で一部が囲まれている。

20

**【0030】**

一つのゲート電極124、一つのソース電極173、及び一つのドレイン電極175は、半導体151の突出部154と共に一つの薄膜トランジスタ(thin film transistor、TFT)を構成し、薄膜トランジスタのチャネル(channel)領域は、ソース電極173とドレイン電極175との間の突出部154に形成される。

30

**【0031】**

データ線171は、下部膜171p、175p、中間膜171q、175q、及び上部膜171r、175rを含む三重膜構造からなる。下部膜171p、175pは、純粋なモリブデン、または窒化モリブデン(MoN)、モリブデン-ニオビウム(MoNb)、モリブデン-バナジウム(MoV)、モリブデン-チタニウム(MoTi)、モリブデン-タンクス滕(MoW)などのモリブデン合金などのモリブデン系金属からなり、中間膜171q、175qは、比抵抗が低いアルミニウムまたはアルミニウム-ネオジム(AlNd)などのアルミニウム合金からなり、上部膜171r、175rは、ITOやIZOとのコンタクト特性が優れている純粋なモリブデン、または窒化モリブデン(MoN)、モリブデン-ニオビウム(MoNb)、モリブデン-バナジウム(MoV)、モリブデン-チタニウム(MoTi)、モリブデン-タンクス滕(MoW)などのモリブデン合金などのモリブデン系金属からなる。

**【0032】**

図2及び図3で、ソース電極173及び端部179を含むデータ線171、及びドレイン電極175に対して、下部膜はアルファベットp、中間膜はアルファベットq、上部膜はアルファベットrを図面符号に付け加えて表記した。

40

**【0033】**

データ線171及びドレイン電極175の側面も、基板110の面に対して傾いており、その傾斜角は約30°乃至80°であるのが好ましい。

**【0034】**

オーミックコンタクト部材161、165は、その下の半導体151と、その上のデータ線171及びドレイン電極175との間にだけ形成されて、これらの間のコンタクト抵抗を低くする。

**【0035】**

半導体151は、薄膜トランジスタが位置する突出部154を除けば、データ線171、

50

ドレイン電極 175、及びその下部のオーミックコンタクト層 161、163、165と実質的に同一な平面形状である。つまり、線状半導体層 151は、データ線 171及びドレイン電極 175、そしてその下部のオーミックコンタクト層 161、163、165下には全て形成されていて、ソース電極 173とドレイン電極 175との間では露出している。

#### 【0036】

データ線 171、ドレイン電極 175、及び露出した半導体 151部分上には、保護膜 (passivation layer) 180が形成されている。

#### 【0037】

保護膜 180は、窒化シリコンや酸化シリコンなどの無機絶縁物、有機絶縁物、低誘電率絶縁物などからなる。有機絶縁物及び低誘電率絶縁物の誘電率は4.0以下であるのが好みしい。低誘電率絶縁物の例としては、プラズマ化学気相成長 (plasma enhanced chemical vapor deposition、PECVD) によって形成されるa-Si:C:O、a-Si:O:Fなどがある。有機絶縁物のうちの感光性 (photosensitivity) を有するものによって保護膜 180を形成するようにしてもよい。保護膜 180の表面は平坦であり得る。また、保護膜 180は、有機絶縁物の優れた絶縁特性を生かしつつ、露出した半導体 151部分に害を及ぼさないように、下部無機膜及び上部有機膜の二重膜構造からなるようにしてもよい。

10

#### 【0038】

保護膜 180には、データ線 171の端部 179及びドレイン電極 175を各々露出する複数のコンタクトホール (contact hole) 182、185が形成されている。保護膜 180及びゲート絶縁膜 140には、ゲート線 121の端部 129を露出する複数のコンタクトホール 181、及び蓄積電極 133a、133bの固定端付近または自由端の蓄積電極線 131の一部を露出する複数のコンタクトホール 184が形成されている。

20

#### 【0039】

保護膜 180上には、複数の画素電極 (pixel electrode) 191、複数の連結橋 (overpass) 84、及び複数のコンタクト補助部材 (contact assistant) 81、82が形成されている。これらは、ITOまたはIZOなどの透明な導電物質や、アルミニウム、銀、またはその合金などの反射性金属からなることができる。

30

#### 【0040】

画素電極 191は、コンタクトホール 185を通じてドレイン電極 175と物理的、電気的に接続されていて、ドレイン電極 175からデータ電圧の印加を受ける。データ電圧が印加された画素電極 191は、共通電圧 (common voltage) の印加を受ける他の表示板 (図示せず) の共通電極 (common electrode) (図示せず) と共に電場を生成することによって、二つの電極間の液晶層 (図示せず) の液晶分子の配向方向を決定する。画素電極 191及び共通電極は、キャパシタ (以下「液晶キャパシタ (liquid crystal capacitor)」という。) を構成して、薄膜トランジスタがターンオフ (turn-off) された後にも印加された電圧を保持する。

40

#### 【0041】

画素電極 191は、蓄積電極 133a、133bをはじめとする蓄積電極線 131と重畳する。画素電極 191及びこれと電気的に接続されたドレイン電極 175が蓄積電極線 131と重畳して構成するキャパシタをストレージキャパシタ (storage capacitor) といい、ストレージキャパシタは、液晶キャパシタの電圧蓄積能力を強化する。

#### 【0042】

コンタクト補助部材 81、82は、各々コンタクトホール 181、182を通してゲート線 121の端部 129及びデータ線 171の端部 179と接続される。コンタクト補助部

50

材 8 1、8 2 は、データ線 1 7 1 及びゲート線 1 2 1 の端部 1 7 9、1 2 9 と外部装置との接続性を補完して、これらを保護する。

#### 【 0 0 4 3 】

連結橋 8 4 は、ゲート線 1 2 1 を横切って、ゲート線 1 2 1 を間ににおいて反対側に位置する一対のコンタクトホール 1 8 4 を通じて蓄積電極線 1 3 1 の露出した部分及び蓄積電極 1 3 3 b の自由端の露出した端部に接続されている。蓄積電極 1 3 3 a、1 3 3 b をはじめとする蓄積電極線 1 3 1 は、連結橋 8 4 と共に、ゲート線 1 2 1 やデータ線 1 7 1 または薄膜トランジスタの欠陥を修復するのに使用される。

#### 【 0 0 4 4 】

以下、図 1 乃至図 3 に示した薄膜トランジスタ表示板を製造する方法について、図 4 乃至 10 図 2 0 を参照して詳細に説明する。

#### 【 0 0 4 5 】

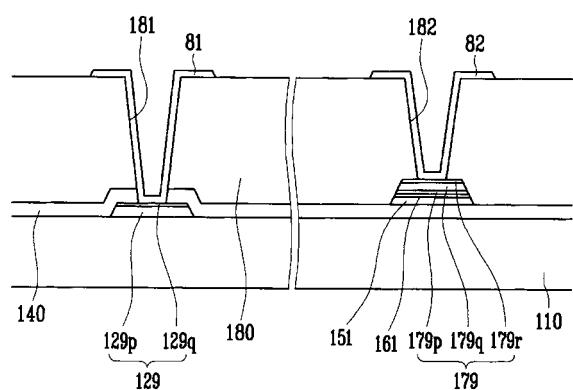

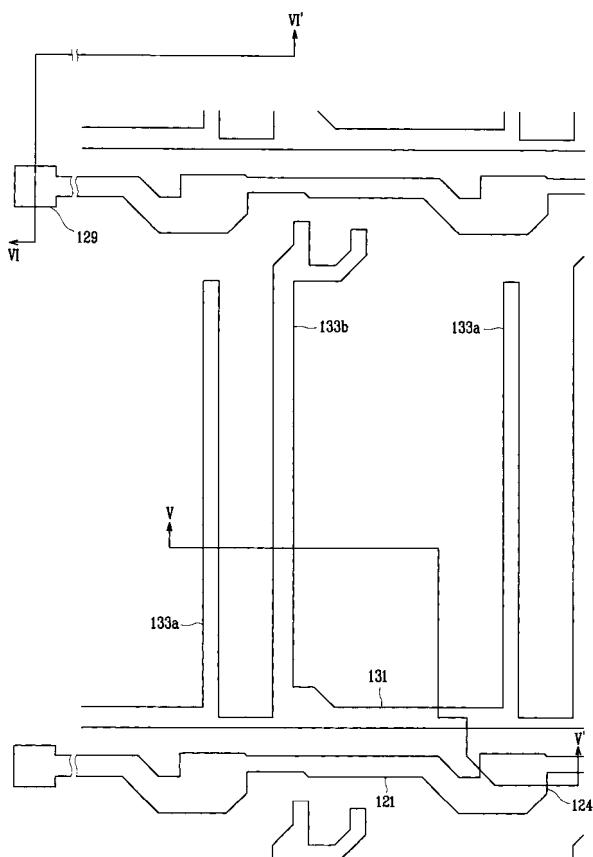

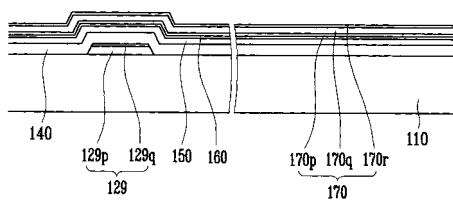

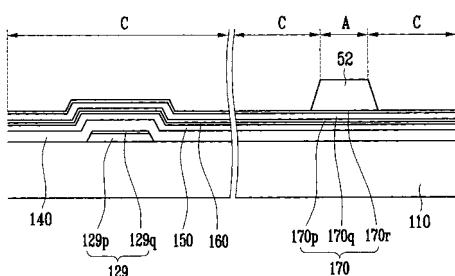

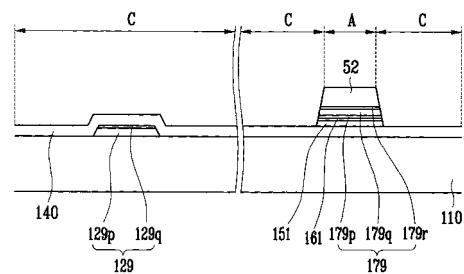

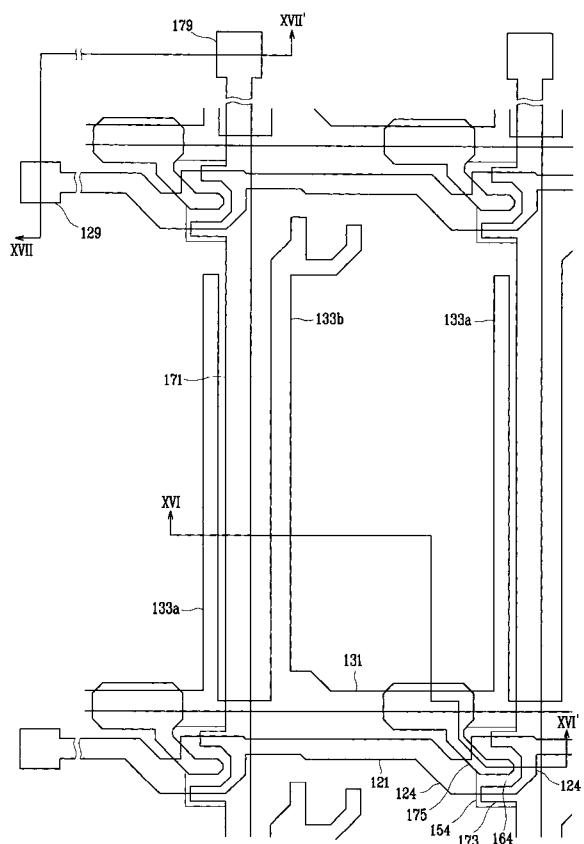

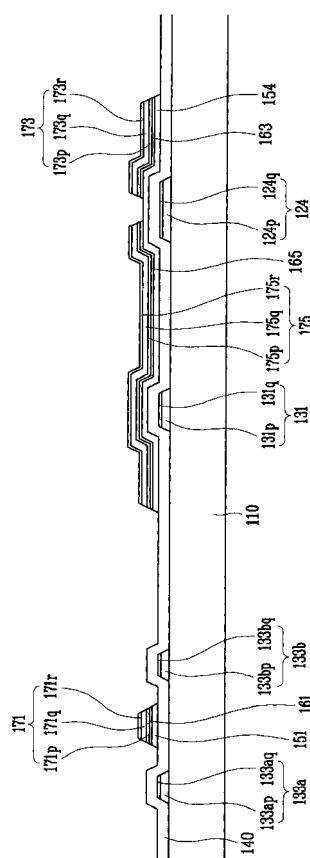

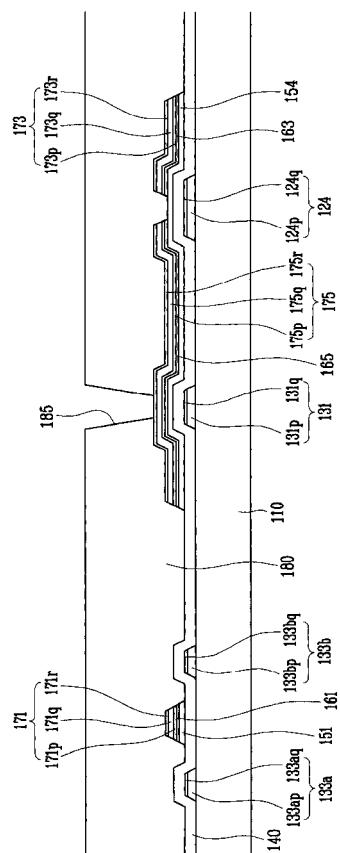

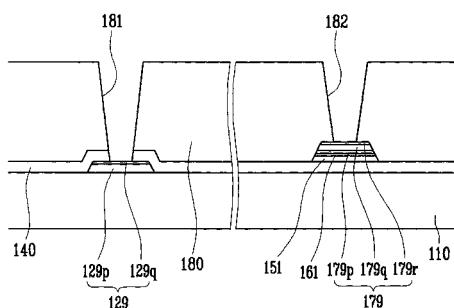

図 4、図 1 5、及び図 1 8 は、本発明の一実施例による薄膜トランジスタ表示板の製造方法を順に示したレイアウト配置図である。図 5 及び図 6 は、図 4 の薄膜トランジスタ表示板の V - V' 線及び V I - V I' 線による断面図である。図 7 乃至図 1 4 は、本発明の一実施例による薄膜トランジスタ表示板の製造方法を順に示した断面図である。図 1 6 及び図 1 7 は、図 1 5 の薄膜トランジスタ表示板の X V I - X V I' 線及び X V I I - X V I I' 線による断面図である。図 1 9 及び図 2 0 は、図 1 8 の薄膜トランジスタ表示板の X I X - X I X' 線及び X X - X X' 線による断面図である。

#### 【 0 0 4 6 】

まず、図 4 乃至図 6 に示したように、透明なガラスまたはプラスチックなどからなる絶縁基板 1 1 0 上に、アルミニウム - ネオジム ( A l N d ) からなる下部膜及びモリブデン ( M o ) 系金属からなる上部膜を順に積層する。

#### 【 0 0 4 7 】

次に、下部膜及び上部膜を湿式エッチング ( w e t e t c h i n g ) し、ゲート電極 1 2 4 及び端部 1 2 9 を含む複数のゲート線 1 2 1 、及び蓄積電極 1 3 3 a、1 3 3 b を含む複数の蓄積電極線 1 3 1 を形成する。

#### 【 0 0 4 8 】

次に、図 7 及び図 8 に示したように、ゲート線 1 2 1 及び蓄積電極線 1 3 1 上に、窒化シリコン ( S i N x ) などからなるゲート絶縁膜 1 4 0 、不純物がドーピングされていない真性非晶質シリコン ( a - S i ) 層 1 5 0 、及び不純物がドーピングされた非晶質シリコン ( n + a - S i ) 1 6 0 層を化学気相成長 ( p l a s m a e n h a n c e d c h e m i c a l v a p o r d e p o s i t i o n 、 P E C V D ) によって形成する。真性非晶質シリコン層 1 5 0 は、水素化非晶質シリコン ( h y d r o g e n a t e d a m o r p h o u s s i l i c o n ) などによって形成し、不純物がドーピングされた非晶質シリコン層 1 6 0 は、リン ( P ) などの n 型不純物が高濃度にドーピングされた非晶質シリコンまたはシリサイドによって形成する。

#### 【 0 0 4 9 】

その後、不純物がドーピングされた非晶質シリコン層 1 6 0 上に、モリブデン系金属からなる下部モリブデン層 1 7 0 p 、アルミニウム系金属からなるアルミニウム層 1 7 0 q 、及びモリブデン系金属からなる上部モリブデン層 1 7 0 r を含むデータ金属層 1 7 0 をスパッタリングによって連続的に順に積層する。

#### 【 0 0 5 0 】

次に、図 9 及び図 1 0 に示したように、上部モリブデン層 1 7 0 r 上に感光膜を形成した後、露光及び現像し、互いに異なる厚さの感光膜パターン 5 2、5 4 を形成する。

#### 【 0 0 5 1 】

ここで、説明の便宜上、配線が形成される部分のデータ金属層 1 7 0 、不純物がドーピングされた非晶質シリコン層 1 6 0 、及び真性非晶質シリコン層 1 5 0 を配線部分 ( A ) とし、ゲート電極 1 2 4 上にチャネルが形成される部分をチャネル部分 ( B ) とし、配線部分 ( A ) 及びチャネル部分 ( B ) を除く領域を残りの部分 ( C ) とする。

10

20

30

40

50

**【0052】**

感光膜パターン52、54のうちで配線部分(A)に位置した第1部分52は、チャネル部分(B)に位置した第2部分54より厚く形成し、残りの部分(C)の感光膜を全て除去する。このとき、第1部分52の厚さと第2部分54の厚さとの比(ratio)は、以下に説明するエッティング工程における工程条件によって異なるようにすべきである。なお、第2部分54の厚さを第1部分52の厚さの1/2以下にするのが好ましい。

**【0053】**

このように、位置によって感光膜の厚さを異なるようにする方法は多様であるが、露光マスクに、透明領域(transparent area)及び遮光領域(light blocking area)を形成するだけでなく、半透明領域(semi-transparent area)を形成することがその一例である。半透明領域には、スリット(slit)パターンが形成されたり、格子パターン(lattice pattern)が形成されたり、また、透過率が中間であったり厚さが中間である薄膜が形成されておりする。スリットパターンを使用する場合には、スリットの幅やスリット間の間隔がフォト工程に使用される露光装置の分解能(resolution)より小さいのが好ましい。他の例としては、リフロー(reflow)が可能な感光膜を使用することができる。つまり、透明領域及び遮光領域だけが形成された通常のマスクに、リフローが可能な感光膜パターンを形成した後でリフローさせ、感光膜が残留しない領域に流れるようにすることによって、薄い部分を形成する。

**【0054】**

次に、図11及び図12に示したように、感光膜パターンの第1部分52を用いて残りの部分(C)に露出しているデータ金属層170を湿式エッティング(wet etching)することにより除去し、一方、(B)部分に対応するデータ金属層174、179を残留させる。

**【0055】**

次に、感光膜パターンの第1部分52を用いて、残りの部分(C)に残留している不純物がドーピングされた非晶質シリコン層160及び真性非晶質シリコン層150を乾式エッティング(dry etching)する。

**【0056】**

次に、エッチバック(etch back)工程によってチャネル部分(B)に残留している感光膜パターンの第2部分54を除去する。この時、感光膜パターンの第1部分52の厚さもある程度薄くなる。

**【0057】**

次に、図13及び図14に示したように、第2部分54が除去された感光膜パターンの第1部分52を用いて湿式エッティングし、データ金属パターン174をソース電極173とドレイン電極175とに分離して、ソース電極173とドレイン電極175との間のチャネル領域に不純物がドーピングされた非晶質シリコンパターン164を露出させる。

**【0058】**

次に、感光膜パターンの第1部分52をエッティングマスクとして用いて、チャネル領域に位置する不純物がドーピングされた非晶質シリコンパターン164を乾式エッティングする。

**【0059】**

この時、乾式エッティングガスとしては、塩素系ガス及びフッ素系ガスを用いる。

**【0060】**

塩素系ガスとしては、 $\text{Cl}_2$ 、 $\text{HCl}$ 、 $\text{BCl}_3$ 、 $\text{CCl}_4$ 、 $\text{SiCl}_2\text{H}_2$ などの塩素原子(Cl)を含むガスを用いてもよい。

**【0061】**

塩素系ガスは、不純物がドーピングされた非晶質シリコンパターン164のエッティング時に所定の量が供給され、下部の半導体154の特性を改善することができる。

**【0062】**

10

20

30

40

50

フッ素系ガスとしては、SF<sub>6</sub> またはCF<sub>4</sub>などのフッ素原子(F)を含むガスを用いてもよい。

【0063】

塩素系ガス及びフッ素系ガスの他に、水素ガス(H<sub>2</sub>)またはヘリウムガス(He)などの不活性ガスが共に供給される。

【0064】

乾式エッチング時のエッチング圧力は、約100乃至800mTで行う。

【0065】

HC1 + SF<sub>6</sub> + Heを使用する場合、SF<sub>6</sub> : HC1の流量比(flow ratio)は1:4乃至1:10であるのが好ましい。Cl<sub>2</sub> + SF<sub>6</sub> + Heを使用する場合、SF<sub>6</sub> : Cl<sub>2</sub>の流量比は1:1乃至1:10であるのが好ましい。前記比率は、薄膜トランジスタの特性の改善効果を示しつつ、エッチングに影響を与えない範囲である。特に、Cl<sub>2</sub>は、HC1より結合解離エネルギー(bond dissociation energy)が小さいので、ラジカル及びイオンの放出に有利で、より少量でも同様の効果を示すことができる。

10

【0066】

上述したように、不純物がドーピングされた非晶質シリコンパターン164のエッチング時に所定の流量の塩素系ガスを供給することによって、薄膜トランジスタの特性の改善効果を示すことができる。

【0067】

20

具体的には、上述したようにデータ金属パターン171、174、179及び真性非晶質シリコン層150を同一な感光膜パターンを用いてエッチングする場合、ソース電極173及び端部179を含むデータ線171と突出部154を含む半導体層151とが実質的に同一な平面形状になる。この場合、バックライト(backlight)のような光源から供給される光に露出される半導体層151の面積が広くなつて、光リーク電流(photo leakage current)が増加する。このような光リーク電流は、データ線171としてアルミニウム層の下部にモリブデン層を形成した多層膜構造を採用了の場合に、より深刻となる。つまり、半導体層151と接触しているモリブデンが半導体内に拡散する問題があり、また、湿式エッチング工程でアルミニウム層から分離されたアルミニウム不純物がチャネル領域などの半導体層を汚染するためである。

30

【0068】

この場合、上述した問題がオフ電流(off-current)及びしきい電圧(threshold voltage)などの薄膜トランジスタの特性に影響を与えることがあり、これは外部、即ち表示板において残像として認識される。

【0069】

そのために、本発明では、ドーピングされた非晶質シリコンパターン164をエッチングする段階、つまりチャネル領域を形成する段階で用いられる塩素系ガス及びフッ素系ガスの流量比を所定の範囲に調節することによって、このような問題を解決することができる。

【0070】

40

チャネル領域を形成する段階で前記範囲の塩素系ガスを用いる場合、エッチング後には突出部154に一部のClが残留する。

【0071】

表1はチャネル領域を形成する段階で用いられた塩素系ガス及びフッ素系ガスの流量比を異なるようにした場合の残像の改善効果を示す実験例である。各実験例において、圧力、電源(power)、及びHeの供給量は、各々170mT、3400W、900sccmと一定である。また、各実験例において、SF<sub>6</sub>の流量を150sccmに固定し、Cl<sub>2</sub>またはHC1の流量をSF<sub>6</sub>の流量に合せて0から所定の比率まで調節して供給した。

【0072】

50

ここで、残像特性は、以下のような方法で実験する。まず、各々の流量比のエッティングガスでチャネル領域を形成した実験用表示板を準備する。実験用表示板には、複数の画素が碁盤の目状に配置されている。実験用表示板にホワイト (white) やブラック (black) でない中間階調のデータ電圧を印加し画面の輝度を測定し、複数の画素が横及び縦方向にブラック及びホワイトを交互に表示するようにした後で、10時間程度放置する。次に、最初に印加した中間階調のデータ電圧を印加し画面の輝度を測定し、残像の程度を確認した。

## 【0073】

【表1】

| 流量比<br>(SF <sub>6</sub> : C<br>Cl <sub>2</sub> ) | 残像改善 | エッティング<br>特性 | 流量比<br>(SF <sub>6</sub> : H<br>Cl) | 残像改善 | エッティング<br>特性 |

|--------------------------------------------------|------|--------------|------------------------------------|------|--------------|

| 1 : 0                                            | ×    | ◎            | 1 : 0                              | ×    | ◎            |

| 1 : 0.3                                          | ×    | ◎            | 1 : 1.12                           | ×    | ◎            |

| 1 : 0.7                                          | ×    | ◎            | 1 : 3                              | ×    | ◎            |

| 1 : 1                                            | ○    | ◎            | 1 : 3.5                            | △    | ◎            |

| 1 : 4                                            | ○    | ◎            | 1 : 4                              | ○    | ◎            |

| 1 : 6                                            | ◎    | ◎            | 1 : 6.5                            | ○    | ◎            |

| 1 : 8.2                                          | ◎    | ◎            | 1 : 9                              | ◎    | ◎            |

| 1 : 9.4                                          | ◎    | ○            | 1 : 9.5                            | ◎    | ○            |

| 1 : 10                                           | ◎    | ○            | 1 : 10                             | ◎    | ○            |

| 1 : 11.2                                         | ◎    | △            | 1 : 11.2                           | ◎    | △            |

| 1 : 13                                           | ◎    | △            | 1 : 13                             | ◎    | △            |

◎：非常に優れている／○：優れている／△：普通／×：不良

## 【0074】

表1に示したように、SF<sub>6</sub> : Cl<sub>2</sub> または SF<sub>6</sub> : HCl の流量比が各々 1 : 1 以上または 1 : 4 以上である場合に、残像の改善効果が明確に現れた。ここで、Cl<sub>2</sub> が HCl より少ない流量比で効果が現れていることは、Cl<sub>2</sub> が HCl に比べて結合解離エネルギー (bond dissociation energy) が小さくて、ラジカル及びイオンの放出に有利であるためである。ただし、SF<sub>6</sub> : Cl<sub>2</sub> または SF<sub>6</sub> : HCl の流量比が 1 : 10 を超える場合には、エッティング特性に影響を与えることが確認された。

## 【0075】

また、前記の範囲内でチャネル領域の半導体に残留する Cl の量を 2 次イオン質量分析 (SIMS: secondary ion mass spectrometry) によって分析した結果、3.0 乃至 20 at% と測定された。

## 【0076】

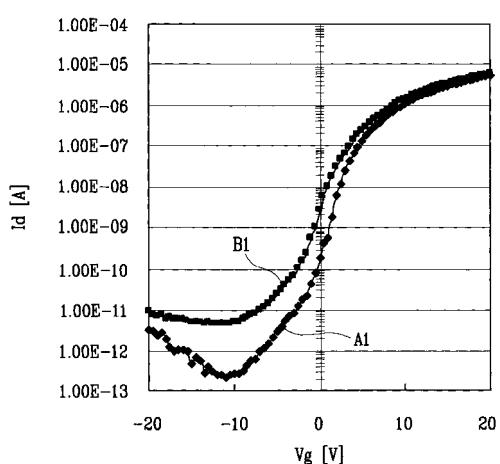

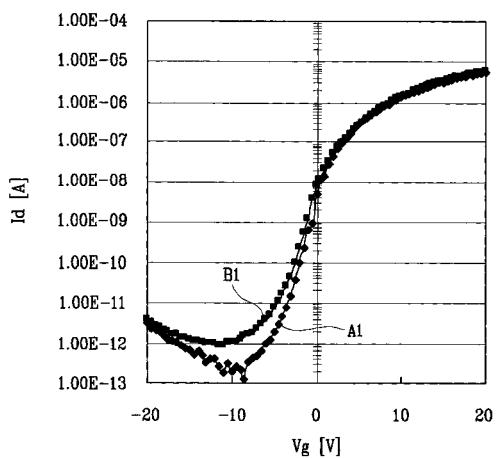

図21A 及び図21B は、Cl の供給量による薄膜トランジスタの特性を示したグラフである。図21A は、SF<sub>6</sub> : HCl を 390 sccm : 470 sccm、つまり 1 : 1.12 の流量比で供給した場合のゲート電圧 (V<sub>g</sub>) によるドレイン電流 (I<sub>d</sub>) の特性を示したグラフである。図21B は、SF<sub>6</sub> : Cl<sub>2</sub> を 150 sccm : 750 sccm、つまり 1 : 5 の流量比で供給した場合のゲート電圧 (V<sub>g</sub>) によるドレイン電流 (I<sub>d</sub>) の特性を示したグラフである。

## 【0077】

ここで、A1 は暗室でドレイン電流 (I<sub>d</sub>) を測定した場合であり、B1 は光が照射される場所でドレイン電流 (I<sub>d</sub>) を測定した場合である。

## 【0078】

これらのグラフに示されているとおり、図21A の場合が図21B に比べて光リーク電流が大きいことが分かる。このような光リーク電流は、ドレイン電圧を降下させ残像を誘発する。

## 【0079】

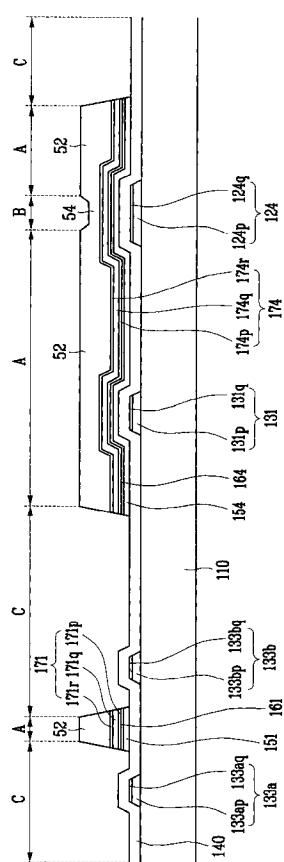

再び図15乃至図17を参照し、残留している感光膜パターン52を除去する。

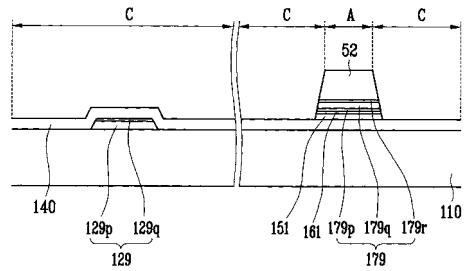

**【0080】**

次に、図18乃至図20に示したように、露出したゲート絶縁膜140、データ線171及びドレイン電極175、及び露出した半導体151の突出部154を覆うように、保護膜180を形成する。

**【0081】**

次に、保護膜180をフォト工程によってエッチングし、複数のコンタクトホール181、182、184、185を形成する。

**【0082】**

最後に、図1乃至図3に示したように、保護膜180上にITOまたはIZOなどの透明な導電物質をスパッタリングによって形成した後にパターニングし、画素電極191、コンタクト補助部材81、82、及び連結橋84を形成する。

10

**【0083】**

以上で、本発明の好ましい実施例について詳細に説明したが、本発明の権利範囲はこれに限定されるわけではなく、請求の範囲で定義している本発明の基本概念を用いた当業者の多様な変形及び改良形態も本発明の権利範囲に属する。

**【図面の簡単な説明】**

**【0084】**

【図1】本発明の一実施例による薄膜トランジスタ表示板の配置図である。

【図2】図1の薄膜トランジスタ表示板のI I - I I'線による断面図である。

20

【図3】図1の薄膜トランジスタ表示板のI I I - I I I'線による断面図である。

【図4】本発明の一実施例による薄膜トランジスタ表示板の製造方法を順に示した配置図である。

【図5】図4の薄膜トランジスタ表示板のV - V'線による断面図である。

【図6】図4の薄膜トランジスタ表示板のV I - V I'線による断面図である。

【図7】本発明の一実施例による薄膜トランジスタ表示板の製造方法を順に示した断面図である。

【図8】本発明の一実施例による薄膜トランジスタ表示板の製造方法を順に示した断面図である。

【図9】本発明の一実施例による薄膜トランジスタ表示板の製造方法を順に示した断面図である。

30

【図10】本発明の一実施例による薄膜トランジスタ表示板の製造方法を順に示した断面図である。

【図11】本発明の一実施例による薄膜トランジスタ表示板の製造方法を順に示した断面図である。

【図12】本発明の一実施例による薄膜トランジスタ表示板の製造方法を順に示した断面図である。

【図13】本発明の一実施例による薄膜トランジスタ表示板の製造方法を順に示した断面図である。

【図14】本発明の一実施例による薄膜トランジスタ表示板の製造方法を順に示した断面図である。

40

【図15】本発明の一実施例による薄膜トランジスタ表示板の製造方法を順に示した配置図である。

【図16】図15の薄膜トランジスタ表示板のX VI - X VII'線による断面図である。

【図17】図15の薄膜トランジスタ表示板のX VII I - X VII I'線による断面図である。

【図18】本発明の一実施例による薄膜トランジスタ表示板の製造方法を順に示した配置図である。

【図19】図18の薄膜トランジスタ表示板のX IX - X IX'線による断面図である。

【図20】図18の薄膜トランジスタ表示板のX X - X X'線による断面図である。

50

【図21A】C1の供給量による薄膜トランジスタの特性の変化を示したグラフである。

【図21B】C1の供給量による薄膜トランジスタの特性の変化を示したグラフである。

【符号の説明】

【0085】

|                 |              |    |

|-----------------|--------------|----|

| 110             | 絶縁基板         |    |

| 121             | ゲート線         |    |

| 124             | ゲート電極        |    |

| 131             | 蓄積電極線        |    |

| 133a、133b       | 蓄積電極         | 10 |

| 140             | ゲート絶縁膜       |    |

| 150             | 真性非晶質シリコン層   |    |

| 151             | 線状半導体        |    |

| 160             | 非晶質シリコン層     |    |

| 161、165         | オーミックコンタクト部材 |    |

| 170             | データ金属層       |    |

| 171             | データ線         |    |

| 173             | ソース電極        |    |

| 175             | ドレイン電極       |    |

| 180             | 保護膜          |    |

| 181、182、184、185 | コンタクトホール     | 20 |

| 191             | 画素電極         |    |

| 52、54           | 感光膜パターン      |    |

| 81、82           | コンタクト補助部材    |    |

| 84              | 連結橋          |    |

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21A】

【図21B】

## フロントページの続き

|                         |                 |

|-------------------------|-----------------|

| (51)Int.Cl.             | F I             |

| H 01 L 23/532 (2006.01) | H 01 L 29/50 M  |

| G 09 F 9/30 (2006.01)   | H 01 L 21/88 R  |

| G 02 F 1/1368 (2006.01) | G 09 F 9/30 338 |

|                         | G 02 F 1/1368   |

(72)発明者 李 禹 根

大韓民国京畿道龍仁市器興邑甫羅里 現代モーニングサイド2次アパートメント102棟504号

(72)発明者 金 時 烈

大韓民国京畿道龍仁市上見洞861番地 晩見マウル8団地斗山ウィップアパートメント806棟1

601号

(72)発明者 周 振 豪

大韓民国ソウル市麻浦区桃花1洞 麻浦三星アパートメント105棟504号

(72)発明者 金 彰 洙

大韓民国京畿道水原市靈通区靈通洞 シンナムシル6団地シンウォンアパートメント643棟17

03号

(72)発明者 皇甫 尚佑

大韓民国ソウル市松坡区蠶室7洞 アジア選手村アパートメント7棟704号

(72)発明者 吳 眇 錫

大韓民国京畿道龍仁市新峰洞 韓一アパートメント102棟202号

(72)発明者 柳 慧 英

大韓民国ソウル市城北区貞陵1洞16-96番地

(72)発明者 秦 洪 基

大韓民国京畿道水原市長安区棗園洞 韓一タウン147棟201号

審査官 井上 弘亘

(56)参考文献 特開平08-242005(JP,A)

特開2004-177946(JP,A)

## (58)調査した分野(Int.Cl., DB名)

|        |               |

|--------|---------------|

| H 01 L | 2 9 / 7 8 6   |

| G 02 F | 1 / 1 3 6 8   |

| G 09 F | 9 / 3 0       |

| H 01 L | 2 1 / 2 8     |

| H 01 L | 2 1 / 3 2 0 5 |

| H 01 L | 2 1 / 7 6 8   |

| H 01 L | 2 3 / 5 3 2   |

| H 01 L | 2 9 / 4 1 7   |