(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5528430号

(P5528430)

(45) 発行日 平成26年6月25日(2014.6.25)

(24) 登録日 平成26年4月25日(2014.4.25)

(51) Int.Cl.

F 1

|                     |                  |             |   |

|---------------------|------------------|-------------|---|

| <b>HO1L 21/316</b>  | <b>(2006.01)</b> | HO1L 21/316 | T |

| <b>HO1L 21/768</b>  | <b>(2006.01)</b> | HO1L 21/90  | P |

| <b>HO1L 21/3205</b> | <b>(2006.01)</b> | HO1L 21/88  | J |

| <b>HO1L 23/522</b>  | <b>(2006.01)</b> |             |   |

請求項の数 6 (全 15 頁)

|               |                               |

|---------------|-------------------------------|

| (21) 出願番号     | 特願2011-506732 (P2011-506732)  |

| (86) (22) 出願日 | 平成21年4月30日 (2009.4.30)        |

| (65) 公表番号     | 特表2011-523202 (P2011-523202A) |

| (43) 公表日      | 平成23年8月4日 (2011.8.4)          |

| (86) 國際出願番号   | PCT/EP2009/055312             |

| (87) 國際公開番号   | W02009/133196                 |

| (87) 國際公開日    | 平成21年11月5日 (2009.11.5)        |

| 審査請求日         | 平成23年12月15日 (2011.12.15)      |

| (31) 優先権主張番号  | 61/050,092                    |

| (32) 優先日      | 平成20年5月2日 (2008.5.2)          |

| (33) 優先権主張国   | 米国(US)                        |

前置審査

|           |                                                                   |

|-----------|-------------------------------------------------------------------|

| (73) 特許権者 | 591060898<br>アイメック<br>I M E C<br>ペルギー、ペー－3001ルーヴアン、カ<br>ペルドリーフ75番 |

| (74) 代理人  | 100101454<br>弁理士 山田 阜二                                            |

| (74) 代理人  | 100081422<br>弁理士 田中 光雄                                            |

| (74) 代理人  | 100100479<br>弁理士 竹内 三喜夫                                           |

| (74) 代理人  | 100112911<br>弁理士 中野 晴夫                                            |

最終頁に続く

(54) 【発明の名称】酸化層の形成方法

## (57) 【特許請求の範囲】

## 【請求項1】

半導体基板の上に酸化層を形成する方法であって、

分離領域を有するデバイス基板、多層の相互結合構造、およびデバイス基板と多層の相互結合構造との間の絶縁層を含む半導体基板を得る工程と、

デバイス基板の裏側から絶縁層まで、デバイス基板中に含まれる分離領域を通って少なくとも1つのホールをエッチングする工程と、

酸性の電解質溶液中で基板を陽極酸化することにより、基板の上に酸化層を形成する工程と、を含み、

基板の上に酸化層を形成する工程は、

電解質溶液中に基板を浸漬する工程と、

電解質溶液中に配置されたカソードと、デバイス基板からなるアノードとの間に10Vと400Vの間の電位を与え、これにより基板を陽極酸化する工程と、で行われ、

陽極酸化する工程は、最初に、所定の時間、固定された電流密度が、基板を通じて得られるように電位を与える工程と、所定の時間が経過した後に、10Vと400Vの間の固定された電位を与える工程との、2工程のプロセスで行われる方法。

## 【請求項2】

酸性の電解質溶液中で基板を陽極酸化する工程は、クエン酸、酢酸、シュウ酸、硫酸、

10

20

リン酸、硝酸、またはそれらの組み合わせを含む電解質溶液中に、基板を浸漬する工程を含む請求項 1 に記載の方法。

【請求項 3】

酸性の電解質溶液中で基板を陽極酸化する工程は、0 % (含有せず) と 20 % の間の酸濃度を有する電解質溶液中に基板を浸漬する工程を含む請求項 1 に記載の方法。

【請求項 4】

基板の上に酸化層を形成する工程は、少なくとも 1 つのホールの側壁に、酸化層を形成する工程を含む請求項 1 に記載の方法。

【請求項 5】

電位を与える工程は、時間の関数として基板を通る電流密度が変化するように、電位を与えて行われる請求項 1 に記載の方法。 10

【請求項 6】

半導体デバイスの製造プロセスにおける、請求項 1 ~ 5 のいずれかに記載の方法の使用。 10

【発明の詳細な説明】

【発明の技術分野】

【0001】

本発明は、半導体プロセスに関する。更に、本発明は、例えば 5 以下のアスペクト比 (高さに対する幅の比) のような高いアスペクト比を有する 3 次元構造の基板上の所定の位置に、酸化層を形成する方法に関する。 20

【発明の背景】

【0002】

シリコン酸化物は、半導体プロセス技術で使用される公知の材料である。シリコン酸化物を堆積または成長するために多くの技術が存在する。シリコン酸化物は、シリコンの熱酸化により形成することができる。代わりに、化学気相堆積 (CVD) がシリコン酸化物の形成に使用されても良い。このプロセスを用いることにより、典型的には 200 から 500 までの範囲の温度で、プロセスチャンバ中の化学反応により、シリコン酸化物が形成される。この目的のために、例えばシラン ( $\text{SiH}_4$ )、TEOS (テトラエチル・オルソシリケイト -  $\text{Si}(\text{OC}_2\text{H}_5)_4$ )、または HMDSO (ヘキサメチルジシロキサン) のような特定の前駆体が一般に使用される。 30

【0003】

形成された酸化物の品質 (電気的特性および機械的特性) は、主に形成中に酸化物中にトラップされた不純物の量に依存し、このように、その形成に使用された技術にも依存する。不純物は、例えば不完全な前駆体の分解の結果である。

【0004】

高品質の酸化膜を低温で得るために、プラズマ誘起化学気相堆積 (PECVD) が使用されて前駆体が効率的に分解される。

【0005】

シリコン酸化物を形成する他の方法は、陽極酸化のようなシリコンの電気化学的酸化による。 40

【0006】

米国特許 5,736,454 には、例えばフィールド酸化層や薄膜トランジスタの酸化層のように、シリコン基板上にシリコン酸化層を形成する方法が開示されている。この方法は、室温で電解反応を行い、アノードとして働くシリコン基板上にシリコン酸化層を形成する工程を含み、電解反応の電解質として純水が使用される。これを得るために、アルミニウム膜がシリコン基板の裏側に蒸着され、陽極酸化のためのアノードコントラクトを形成する。米国特許 5,736,454 の方法は、例えばゲート酸化膜として使用できる高品質のシリコン酸化層を得るためにアシスト技術が必要である。それゆえに、形成された二酸化シリコン層は、更に、不活性ガス雰囲気中で、700 と 1000 との間の温度で、所定の期間、急速熱緻密化が行われ、二酸化シリコンが緻密化される。米国特許 50

, 736, 454に記載された方法の欠点は、取り扱いのためにキャリアに取り付ける必要があり、キャリアは非導電性であるような、薄いウエハには適用できないことである。米国特許5, 736, 454に記載された方法の更なる欠点は、50から88が20分から100分で形成されるという遅いプロセスである。

#### 【0007】

P E C V D堆積は、一般には、200と400の間の温度で行われる。I Cやパッケージの3D集積を覆う、先端のパッケージング応用では、一般的な堆積温度は200より低くする必要があり、好適には、例えば、一般には高温には耐えられないポリマー系樹脂で接着されるキャリアウエハまでの処理ができるように、100より低くする必要がある。P E C V Dを用いた場合、200より低い温度、時には80まで低くして層を堆積することが可能であるが、そのような温度で堆積した酸化物は、例えば低い機械的特性のような劣った特性を示す。層は、低い破壊電界とピンホールの欠点を持つ。また、堆積層の適合性が低く、即ち、深い3D構造では堆積層の膜厚は均一では無い。

10

#### 【0008】

シリコンの酸化は、良好な品質の酸化物を得るには、前処理、追加のアシスト技術、または特別な基板準備が必要な困難なプロセスである。例えば良好な品質の酸化物は、100nA/cm<sup>2</sup>より低い寄生リーク電流を有する。

#### 【0009】

更に、バイア構造が基板上に形成された場合、リソグラフィパターニングに使用するスキヤナの小さな焦点深さおよび/または反射効果によるリソグラフィ限界のために、それらのバイア構造の内側に酸化物を形成することは困難である。

20

#### 【発明の概要】

#### 【0010】

本発明の具体例の目的は、例えばシリコン基板のような半導体基板の上または中の、3次元(3D)構造上のような、半導体基板上に、酸化層を形成する方法を提供することである。

#### 【0011】

本発明の特定の具体例にかかる方法では、酸化層は、例えば半導体基板中のトレンチまたはホールの側壁に、および/または半導体基板の主表面の柱の側壁のような、半導体基板の中または上の3D構造上に形成されても良い。

30

#### 【0012】

本発明の具体例にかかる方法は、例えば室温のような、80より低いような低温で適用される。

#### 【0013】

上記目的は、本発明にかかる方法およびデバイスにより達成される。

#### 【0014】

第1の形態では、本発明は、例えば半導体基板の中または上の3次元構造上のような半導体基板上に酸化層を形成する方法を提供する。この方法は、

半導体基板を得る工程と、

酸性電解質溶液中で基板を陽極酸化することにより、基板上に酸化層を形成する工程と、を含む。

40

#### 【0015】

基板が三次元構造を含むような特別な具体例では、そのような3次元構造は、例として、基板貫通バイア(T S V : through-substrate via)のための円柱またはドーナツ形状のホールでも良い。代わりの具体例では、例えばMEMSデバイスを形成するための、基板の表面上に形成されたあらゆる形状でも良い。3次元構造は、トレンチ、ホール、および/または柱を含む。

#### 【0016】

酸性の電解質溶液中で基板を陽極酸化する工程は、クエン酸、酢酸、シュウ酸、硫酸、リン酸、硝酸、またはそれらの組み合わせのいずれかを含む電解質溶液中に基板を浸漬す

50

る工程を含む。本発明の具体例では、電解質溶液中の酸の濃度は、使用される酸と特定の環境に依存して、0%（含有しない）と20%の間でもよい。

#### 【0017】

酸性電解質溶液では、非酸性の電解質溶液を用いた場合に比較して、陽極酸化の速度が増加することが、本発明の具体例の長所である。このように、より厚い酸化層が、より短時間で形成できる。陽極酸化プロセスの速度は、電解質溶液中の酸の濃度に依存する。

#### 【0018】

本発明の具体例にかかる方法を用いた場合、酸化層は、例えば電解質中に基板が露出した位置のような、所定の位置に形成することができる。そのような所定の位置は、例えば、3次元構造の主表面上、および／またはトレンチやホールやバイアの側壁のようなその側壁のような、3次元構造の部分を含む。10

#### 【0019】

陽極酸化を使用する長所は、陽極酸化電解質に露出した基板表面上の均一な酸化物膜厚と、同時に表面粗れの低減を実現することである。基板中での垂直トレンチやバイアのエッ칭は、一般には粗れた側壁（スカラップス：scallops）となる。基板表面上の鋭い表面形状（例えば、スカラップス）は、局所的に高い静電場となり、それらの位置で陽極酸化プロセスを加速させ、これにより自然な方法で表面を平坦化する。酸化物の平坦な表面、またはこのようにして低減された粗さは、例えば絶縁破壊に対する耐性を改良するような、良好な電気的特性を与える。

#### 【0020】

本発明の具体例にかかる方法の他の特徴は、例えば80より低い温度、更には50より低い温度、例えば室温のような低温で行えることである。20

#### 【0021】

本発明の具体例にかかる方法では、例えば基板貫通バイアのようなバイア、またはMEMSデバイスを形成するために使用できる。

#### 【0022】

本発明の具体例で基板上に酸化層を形成する工程は、

基板を電解質溶液中に浸漬する工程と、

電解質溶液中のカソードと、基板上または基板により形成されたアノードとの間に電位を与える、これにより基板を陽極酸化する工程と、で行われる。基板が3次元構造を含む場合、この構造は基板と一緒に陽極酸化される。電位を与えることにより、電池を通って電流が流れる。陽極層が成長すると、プロセスを行い続けるために、（一定の電流では）より大きな電位が必要となる。所定の電圧に達した場合、所定の酸化物膜厚が達成される。電圧が一定に維持された場合、残りの陽極酸化時間の間に電流が指数関数的に減少し、その間に陽極酸化層中の欠陥が治癒されて酸化物が緻密化される。30

#### 【0023】

本発明の具体例では、形成された酸化層は、基板の表面側に形成される。カソードとアノードとの間に電位を与える工程は、カソードと、基板の表面上に位置するアノードとの間に電位を与える工程を含む。これは、非常に薄い基板を用いる方法で有利である。そのような薄い基板は、取り扱いに便利なように、取り扱いウエハ上に配置する。そのような取り扱いウエハは、大部分の場合、非導電性である。カソードと、基板の表面側のアノードとの間に電位を与えるために、取り扱いの有無や型は陽極酸化プロセスには関係しない。40

#### 【0024】

与えられた電位は、10Vと400Vの間でも良い。電流は、電解質溶液の電気分解を開始するために十分高くなければならない。

#### 【0025】

本発明の具体例では、電解質溶液中に配置されやカソードと、基板の上またはそばに形成されたアノードとの間に電位を与える工程は、時間の関数として基板を通る電流密度を変えるように電位を与える工程でも良い。このように、与えられた電位は、時間の関数と50

して変化しても良い。

**【0026】**

本発明の具体例では、陽極酸化は2工程のプロセスで行われても良い。それらの具体例では、電解質溶液中に配置されやカソードと、基板の上またはそばに形成されたアノードとの間に電位を与える工程は、

最初に、所定の時間、酸化層を形成するために、固定された電流密度が、基板を通って得られ、

所定の時間が経過した後に、固定された電位が、酸化層を治癒するために得られる。

**【0027】**

酸化層の治癒は、ピンホールのような欠陥を除去し、良好な品質の酸化層を得ることを意味する。

**【0028】**

更なる形態では、本発明は、半導体デバイスの製造プロセス中での、本発明の具体例にかかる方法の使用である。

**【0029】**

他の形態では、本発明は、本発明の具体例にかかる方法により形成された酸化層を有する基板を提供することである。

**【0030】**

更なる形態では、本発明は、基板上に、少なくともホールを含む3次元構造を形成するものである。3次元構造は、更に、3次元構造の主表面上の、および／または少なくとも1つのホールの側壁の、酸化層を含み、この酸化層は、本発明の具体例にかかる方法により形成される。例えばトレンチのような高いアスペクト比の3次元構造中で形成された酸化層が等角になることが特に有用である。公知の低温プロセスは、一般には10%より少ないステップカバレッジを有し、ところが本発明の具体例で形成した酸化層はCVD酸化物のように等角であり、低温で形成される。

**【0031】**

本発明の特別で好ましい形態は、添付した独立請求項および従属請求項に表される。従属請求項の特徴は、必要に応じて、独立請求項の特徴や他の従属請求項の特徴と組み合わせても良く、単に請求項に表された通りだけではない。

**【0032】**

本発明の、上記および他の特徴、性質、および優位性は、本発明の原理を例示により示す添付の図面と共に、以下の詳細な記載から明らかになるであろう。この説明は例示のみを目的とし、本発明の範囲を限定するものではない。以下で用いられる参照符号は、添付の図面を引用する。

**【図面の簡単な説明】**

**【0033】**

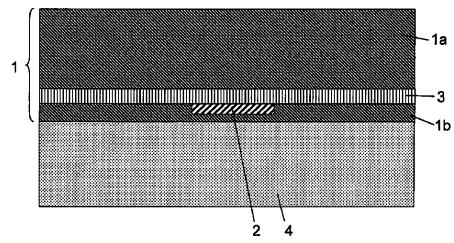

【図1】本発明の具体例にかかる方法の連続した工程を示す。

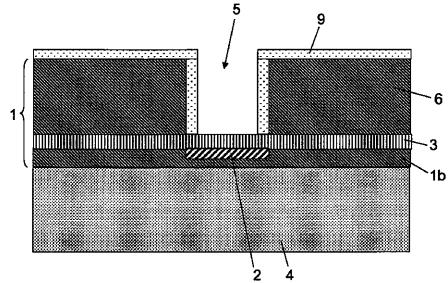

【図2】本発明の具体例にかかる方法の連続した工程を示す。

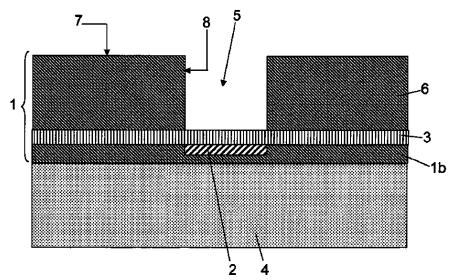

【図3】本発明の具体例にかかる方法の連続した工程を示す。

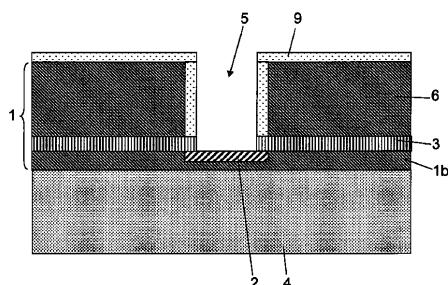

【図4】本発明の具体例にかかる方法の連続した工程を示す。

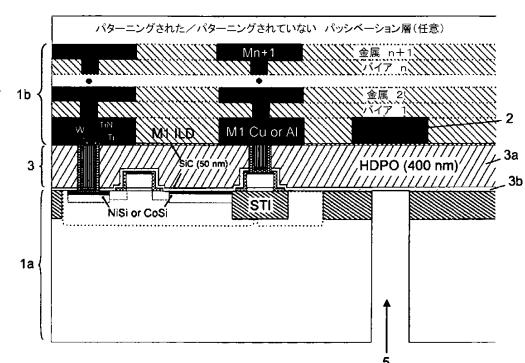

【図5】本発明の具体例にかかる方法を適用できるデバイスの例を示す。

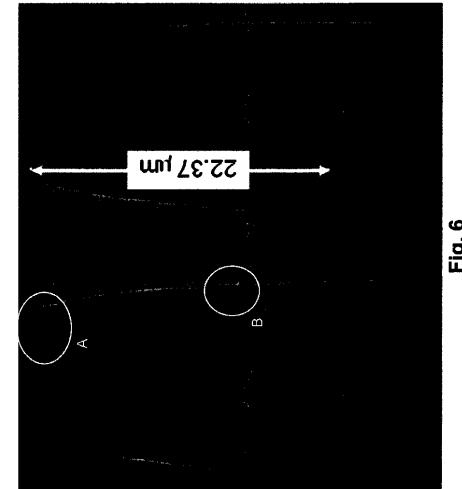

【図6】本発明の具体例にかかる方法により形成された酸化層のSEM写真を示す。

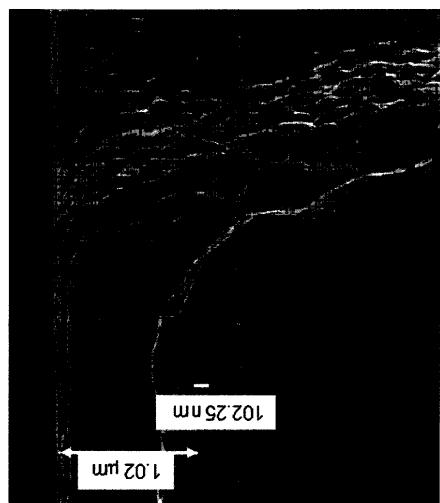

【図7】本発明の具体例にかかる方法により形成された酸化層のSEM写真を示す。

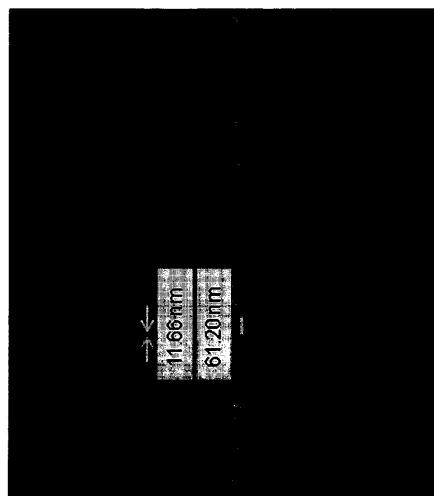

【図8】本発明の具体例にかかる方法により形成された酸化層のSEM写真を示す。

【図9】本発明の具体例にかかる方法により形成された酸化層のSEM写真を示す。

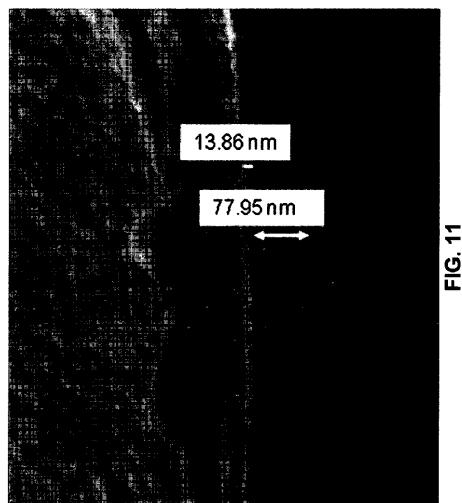

【図10】本発明の具体例にかかる方法により形成された酸化層のSEM写真を示す。

【図11】本発明の具体例にかかる方法により形成された酸化層のSEM写真を示す。

【図12】本発明の具体例とともに使用される電極構造を示す。

**【0034】**

異なる図面において、同一参照番号は、同一または類似の要素を示す。

10

20

30

40

50

**【具体例の説明】****【0035】**

本発明は、特定の具体例に関して、所定の図面を参照しながら説明されるが、本発明はそれらに限定されるものではなく、請求の範囲によってのみ限定されるものである。記載された図面は、単に概略であり限定するものではない。図面において、幾つかの要素の大きさは、図示を目的として拡大され、縮尺通りには記載されない。寸法と、対応する寸法は、本発明の現実の実施化に対応しない。

**【0036】**

更に、説明や請求の範囲中の、第1、第2等の用語は、類似の要素の間で区別するために使用され、時間的、空間的に、ランクや他の方法で順序を表す必要はない。そのように使用される用語は、適当な状況下で入替え可能であり、ここに記載された発明の具体例は、ここの説明や図示されたものと異なる順序によっても操作できることを理解すべきである。10

**【0037】**

また、説明や請求の範囲中の、上、下等の用語は、記載目的のために使用され、相対的な位置を示すものではない。そのように使用される用語は、適当な状況下で入替え可能であり、ここに記載された発明の具体例は、ここに説明や図示されたものと異なる位置でも操作できることを理解すべきである。

**【0038】**

また、請求の範囲で使用される「含む（comprising）」の用語は、それ以降に示される要素に限定して解釈されること排除することであり、他の要素や工程を排除しない。このように、言及された特徴、数字、工程、または成分は、その通りに存在するものと解釈され、1またはそれ以上の他の特徴、数字、工程、または成分、またはこれらの組み合わせの存在または追加を排除してはならない。このように、「手段AおよびBを含むデバイス」の表現の範囲は、構成要素AとBのみを含むデバイスに限定されるべきではない。本発明では、単にデバイスに関連した構成要素がAとBであることを意味する。20

**【0039】**

この明細書を通じて参照される「一の具体例（one embodiment）」または「ある具体例（an embodiment）」は、この具体例に関する記載された特定の長所、構造、または特徴は、本発明の少なくとも1つの具体例に含まれることを意味する。このように、この明細書を通して多くの場所の「一の具体例（one embodiment）」または「ある具体例（an embodiment）」の語句の表現は、同じ具体例を表す必要はなく、表しても構わない。更に、特定の長所、構造、または特徴は、この記載から当業者に明らかのように、1またはそれ以上の具体例中で適当な方法で組み合わせることができる。30

**【0040】**

同様に、本発明の例示の記載中において、能率的に開示し、多くの発明の形態の1またはそれ以上の理解を助ける目的で、本発明の多くの長所は、時には1つの具体例、図面、またはその記載中にまとめられることを評価すべきである。しかしながら、この開示の方法は、請求される発明がそれぞれの請求項に記載されたものより多くの特徴を必要とする意図して表されていると解釈すべきではない。むしろ、以下の請求項が表すように、発明の態様は、1つの記載された具体例の全ての長所より少なくなる。このように詳細な説明に続く請求の範囲は、これにより詳細な説明中に明確に含まれ、それぞれの請求項は、この発明の別々の具体例としてそれ自身で成立する。40

**【0041】**

更に、ここで記載された幾つかの具体例は、他の具体例に含まれる以外の幾つかの特徴を含み、異なった具体例の長所の組み合わせは、本発明の範囲に入ることを意味し、当業者に理解されるように異なった具体例を形成する。例えば、以下の請求の範囲では、請求された具体例のいくつかは、他の組み合わせにおいても使用することができる。

**【0042】**

ここで与えられる記載において、多くの特別な細部が示される。しかしながら、本発明50

の具体例はそれらの特別な細部無しに実施できることを理解すべきである。他の例では、公知の方法、構造、および技術は、この記載の理解をわかりにくくしないために、詳細には示されていない。

#### 【 0 0 4 3 】

本発明は、例えばシリコンプロセスのような半導体プロセスの分野に関し、例えば貫通基板バイアプロセスや半導体ベースのMEMS技術に関する。本発明の特別な具体例では、半導体はシリコンでも良い。

#### 【 0 0 4 4 】

本発明は、例えばホールのような3次元構造を有する基板に関連して詳細に述べられる。しかしながら、これは本発明を限定することを意図するものではない。本発明は、また、柱である3次元構造や柱状の形状を有する3次元構造を有する基板に、他の型の3次元構造を備えた基板に、または平坦な基板に適用することができる。

10

#### 【 0 0 4 5 】

3次元半導体構造上に、特にホールや突出部の垂直な側壁上に等角な酸化層を形成することは、特に大きなアスペクト比（3次元構造の幅寸法を高さ寸法で割った比として定義され、幅寸法は平坦な基板表面で実質的に測定され、高さ寸法は実質的にその垂線として測定される）、例えば5より小さいアスペクト比や、低温プロセス、例えば80より低い温度でのプロセスでは非常に困難である。本発明は、例えばシリコン基板のような3次元半導体の露出した半導体表面領域上に酸化層を形成する方法を提供する。この方法は、平坦に横たわり、3次元構造を含む基板を得る工程であって、3次元構造は、例えばホールやバイアのような、基板の面に対して実質的に垂直な少なくとも1つの面を含む工程と、

20

酸性電解質溶液中で基板を陽極酸化することにより3次元構造の上または中に酸化層を形成する工程と、を含む。

#### 【 0 0 4 6 】

陽極酸化は、表面を電解質溶液中に配置しながら、不活性な材料から形成されたカソード（負電極）とアノード（正電極）との間に電位を与えることにより表面が陽極酸化される電気化学プロセスである。アノードは、処理される部分でも良く、または処理される部分の上に更に提供されても良い。与えられた電位の結果、電解質溶液を通じて直流電流が流れるため、酸化層が続いて成長される。この電流は、カソードにおいて水素を、アノードの表面において酸素を発生させ、これにより酸化層の積層が形成される。

30

#### 【 0 0 4 7 】

陽極酸化では、室温で酸化物が成長できる。陽極酸化を用いることにより、3次元（3D）構造のホールの中や突出部の上に酸化層が形成できる。このように、3D構造のホールの中や突出部の上に酸化層を形成するために陽極酸化を用いることにより、本発明の具体例にかかる方法は、化学気相堆積（CVD）技術のような従来のプロセスの限界を克服し、プロセスを単純化でき、結果としてコストを低減できる。

#### 【 0 0 4 8 】

本発明の具体例では、陽極酸化プロセスは、酸性の電解質溶液中で行われる。電解質溶液は、例えばクエン酸、酢酸、シウ酸、硫酸、リン酸、硝酸、またはそれらの組み合わせのいずれかを含んでも良い。電解質溶液中の酸性成分が、陽極酸化プロセスをスピードアップさせることが見出された。それゆえに、酸性の電解質溶液を用いることにより、同じパラメータ（出発材料、電流、温度等）で、他の酸性でない電解質溶液を用いた陽極酸化プロセスに比較して、一定の時間で、より厚い酸化物が成長できる。より酸性の電解質溶液では、より速く陽極酸化プロセスが起きる。

40

#### 【 0 0 4 9 】

陽極酸化は、陽極酸化電解質に露出した、Siのような半導体表面上で、均一な酸化物膜厚を実現できる。酸化層の膜厚は、陽極酸化電流を決定する、カソードとアノードとの間の陽極酸化電圧で決定される。

#### 【 0 0 5 0 】

50

陽極酸化は、また、同時に表面粗さの低減を行う。例えばSiのような半導体材料中に、垂直なトレンチやバイアをエッティングすると、一般に、粗い側壁(スカラップス)となる。例えばSi表面のような半導体表面上の鋭い表面形状(例えばスカラップス)は、より高い静電場となり、それらの位置において陽極酸化プロセスを加速させ、それにより自然な方法で表面を平坦化する。

#### 【0051】

本発明の具体例は、半導体基板の上または中に形成された3次元構造(3D)構造の上または中に酸化層を形成するための陽極酸化プロセスの使用を提供する。

#### 【0052】

これ以降、本発明の具体例にかかる方法は、例示の方法で、図1～図4を参照しながら説明する。これは説明を容易にするためであり、この例は如何なる方法においても本発明を限定することを意図しないことを理解すべきである。本発明の具体例にかかる方法は、基板および/または3D構造が、金属や半導体材料のような導電性材料を含む限り、基板上に3D構造の酸化層を形成するのに使用できる。10

#### 【0053】

第1の工程では、例えばSi基板のようなデバイス基板1aが提供される。デバイス構造1aの上に、酸化物や窒化物のような誘電体絶縁層3が形成される。誘電体絶縁層3は、単層または複数の層からなっても良い。デバイス基板1aと誘電体絶縁層3との間の界面近傍で、トランジスタ(図示せず)のような能動デバイスが、例えばフロントエンドオブラインのようにデバイス基板1aに形成されても良い。代わりの具体例では、デバイス基板1aは、受動基板である。誘電体絶縁層3の他の側には、例えばデバイスウェハのバックエンドオブラインや半導体挿入(MCM)基板のビルトアップ層のような、絶縁体層と相互結合層とを含む多層の相互結合構造1bが形成される。そのような多層の相互結合構造の1つのコンタクト2が、図1に、模式的に表されて、参考番号2で示される。デバイス基板1aが薄い場合、上述のように複数の層やデバイスで形成された基板は、選択的にキャリア基板4に取り付けられても良い。20

#### 【0054】

基板1は、300μmより小さい膜厚を有してもよく、例えば50μmと300μmの間の膜厚を有しても良い。本発明の具体例では、例えば半導体基板、特にシリコン基板のように、電流を流すことができ、酸化できる限り、如何なる基板でも使用できる。例えば、陽極酸化される部分である基板1、特にそのデバイス基板1aは、低抵抗のシリコンを含んでも良い。低抵抗シリコンは、30μOhm·cm、またはそれより低い抵抗率を有するが、本発明はこれに限定されるものではない。この目的のために、例えばn-またはp-ドープされたシリコンのような、n-またはp-ドープされた半導体材料が用いられても良い。30

#### 【0055】

図2に示すように、適切な半導体技術を用いて、ホール5が、半導体デバイスウェハ1aの裏側から、絶縁層3までエッティングされる。一般的な技術は、斜めまたはまっすぐな側壁8を得るために、ICP-RIEプラズマエッティング技術の使用である。それらのホール5は、円、多角形、リング形状、または幾つかの名前であるトレンチのような、様々な形状を有する。40

#### 【0056】

次に、陽極酸化が行われる。これにより、基板1は酸性の電解質溶液に浸漬され、電解質溶液中に配置されたカソードと、基板1の上または基板のそばに形成されたアノードとの間に電位が与えられる。与えられた電位は、10Vと400Vの間でも良い。本発明の具体例では、基板1の材料、特にデバイス基板1aの材料は、それ自体がアノードとして働いても良い。本発明の他の具体例では、アノードが基板1の上に形成されて、基板1の導電性材料に電気的コンタクトを形成しても良い。後者の場合、10k<sup>2</sup>と100k<sup>2</sup>の間のコンタクトオーミック抵抗が、電極と基板1との間に存在しても良い。このコンタクトは、酸性溶液からコンタクトを保護できる、プラスチックモールド中埋め込まれた電極50

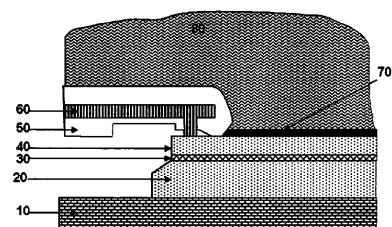

のセットを配置することで実現できる。そのような電極の例を図12に示す。図12に示される電極60は、電極60と取り囲む電解質溶液80との間の直接的な接触を防止するコンタクトシールリング50により覆われて、電極は、酸性の電解質溶液によって汚染されたり破壊されたりしない。コンタクトシールリング50は、電解質溶液の酸性の影響から、電極60を保護するのに適した材料からなる。電極60は、例えば薄い半導体ウエハのような基板40と、その表面側で電気的にコンタクトし、即ち、本発明の具体例にかかる陽極酸化により酸化層70が形成されるのと同じ側にコンタクトする。取り扱いの容易さのために、酸化される基板40は、例えば一時的な接着剤30の手段により、キャリアウエハ20の上に取り付けられても良い。陽極酸化プロセスの間に、選択的にキャリアウエハ20の上に配置され、一時的に取り付けられた基板40は、ホルダーチャック10の上に配置される。

#### 【0057】

デバイス基板1a自身を、配置された電極として使用することは、特に有利である。このように、基板1の裏面にアノードを形成する必要が無く、記載された例では、キャリア基板4の裏に取り付けられる。

#### 【0058】

電解質溶液は、例えば、クエン酸、酢酸、シュウ酸、硫酸、リン酸、硝酸、またはそれらの組み合わせのいずれかを含む。基板1に電圧を与えることにより、電解質溶液を通じて電流が流れ、これにより電解質溶液と接触した導電性材料の陽極酸化を引き起こす。結果として、シリコン酸化層9が、例えば主表面7のような全ての露出したシリコン表面上に形成されるとともに、3D構造の側壁8上にも形成される(図3)。

#### 【0059】

陽極酸化プロセスが、絶縁体3に対して選択的であることがわかる。これは、露出した導電性基板材料にのみ酸化物が形成され、実質的に隣接する非導電体または非導電性材料の上には形成されないことを意味する。

#### 【0060】

主表面7および側壁8の上への例えばシリコン酸化層のような酸化層9の形成は単に一例であり、本発明の他の具体例では、この方法は、少なくとも1つのホール5の側壁8の上ののみに、例えばシリコン酸化層のような酸化層を形成するために使用しても良いことが理解される。これは、例えば最初に3D構造の主表面7に絶縁層を形成し、続いて被覆されていない部分、即ち、少なくとも1つのホール5の側壁8を陽極酸化して、例えばシリコン酸化層のような酸化層9を少なくとも1つのホール5の側壁8の上に形成することを行っても良い。

#### 【0061】

陽極酸化は自己制御性のプロセスであり、これは、陽極酸化のために与えられる電位と、形成される酸化層9の膜厚との間に平衡が存在することを意味する。本発明の具体例では、200nmまでの膜厚の酸化層9の形成が可能である。具体例により、例えばシリコン酸化層のような酸化層9に要求される膜厚に依存して、約10分と10時間との間の時間で陽極酸化が行われる。

#### 【0062】

本発明の具体例では、陽極酸化プロセスは2工程のプロセスでも良い。第1段階では、カソードとアノードとの間に電位が与えられ、酸化層9を形成することができる固定された電流密度が得られる。第2段階では、与えられる電位は、形成された例えばシリコン酸化層のような酸化層9の治癒が可能な、固定された電位である。酸化シリコンのような酸化層9を治癒は、ピンホールのような欠陥を除去して、良好な品質の酸化層を得ることを意味する。特定の具体例では、化学量論的な酸化物が得られ、これは良好な品質的特性を示す。

#### 【0063】

本発明の具体例にかかる方法では、シリコン酸化層のような多孔質酸化層9を形成することも可能である。この場合、電流密度は、陽極酸化中の時間の関数として変化する。

**【0064】**

次の工程では、少なくとも1つのホール5の底の絶縁層3が除去され、下層のコントラクト2を露出させても良い。これは、例えば選択エッティングのような、当業者に知られたいずれかの好ましい技術により行われる。この場合、絶縁層3は、形成された酸化層9に対して選択的にエッティングできることが好ましい。少なくとも1つのホール又はバイア5が、続いて、選択的に、導電性材料により埋められても良い。

**【0065】**

本発明の具体例にかかる方法は、半導体プロセスで使用しても良い。例えば、本発明の具体例にかかる方法は、スルーシリコンバイアのライナー(a liner of a through-silicon-via)、またはバイア分離とも呼ばれる、を形成するのに使用される。例えばシリコン酸化層のような酸化層9の形成は、3D構造の主表面7の上や、少なくとも1つのホールやバイア5の側壁8の上のような例で表される、所定の領域で起きるため、例ではシリコン酸化層のような、形成された酸化層9をパターニングして、例えば少なくとも1つのホールまたはバイア5の底から所定のシリコン酸化層を除去するような、酸化層9の一部を除去するためのパターニング工程は必要でない。

10

**【0066】**

本発明の具体例にかかる方法は、高さに対する幅の比で規定され、例えば5より低いアスペクト比、例えば0.01と5との間のアスペクト比のような高いアスペクト比のバイア5中に、シリコン酸化層のような酸化層9を形成するために使用される。

20

**【0067】**

上述のように、本発明の具体例にかかる方法は、半導体材料の陽極酸化の手段により説明した。金属のような他の導電性材料も、プロセス中に陽極酸化できることを理解すべきである。言い換えれば、本発明の具体例にかかる方法を用いた酸化層の形成は、半導体材料の上または中に形成された、選択的に金属を含む3D構造に適用できる。

**【0068】**

例えばシリコン酸化層のような、本発明の具体例にかかる方法で形成された酸化層9は、通常の化学量論比を有し、即ち、従来の方法で改正した酸化層と同じ化学量論比を有する。シリコン酸化膜が形成される特定の例では、これは、酸化層がSiO<sub>2</sub>からなり、SiOを含まないことを意味する。

30

**【0069】**

本発明の具体例にかかる方法で形成された、例えばシリコン酸化層のような酸化層9は、3D集積に要求される最低限の品質を示す。しかしながら、具体例にかかる方法で形成された、例えばシリコン酸化層のような酸化層9は、ゲート酸化膜として使用するには好ましくない。

**【0070】**

シリコンにおいて、本発明の具体例にかかる方法でSi表面が処理された場合、即ち、本発明の具体例にかかる方法を用いてシリコン酸化層が形成された場合、表面は親水性を有するように形成される。これらの性質は、ウエハ表面上へのリソグラフィ生成物の適用を容易にするために用いられる。

40

**【0071】**

本発明の具体例にかかる方法では、例えばシリコン酸化層のような酸化層が、例えば3次元構造の主表面の中および/または上の、トレンチ又はホール又はバイア5の側壁のような、半導体基板上の3D構造上に形成される。本発明の具体例にかかる方法は、形成された酸化層をパターニングし、これにより酸化物の不要な位置において酸化物を除去する、例えばフォトリソグラフィ工程のような追加の工程を常に必要としない。

**【0072】**

本発明の具体例にかかる方法は、室温で適用でき、これにより、加熱中に、例えば接着層から起るような問題を避けることができる。

**【0073】**

本発明の具体例にかかる方法を用いることにより、連続した等角の酸化層が形成される

50

。

【実施例】

【0074】

シリコン酸化層9がシリコンホールまたはバイア5中に形成される実験が行われた。これにより、シリコンウェハ1が形成された。シリコンウェハ1は、高いアスペクト比0.1(直径が5μmで深さが50μm)を有するスルーリコンバイア5を備えて形成された。シリコンウェハ1は、低コンタクト抵抗を実現するために、HF溶液で洗浄された。

【0075】

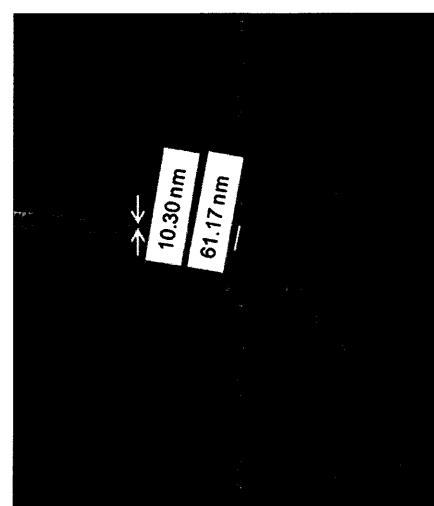

陽極酸化反応のための電解質溶液として、0.1%のクエン酸溶液が使用された。40Vの陽極酸化電位が印加された。5mA/cm<sup>2</sup>の電流密度が達成された。陽極酸化が、10時間行われた。膜厚70nmのシリコン酸化層9が得られた。

【0076】

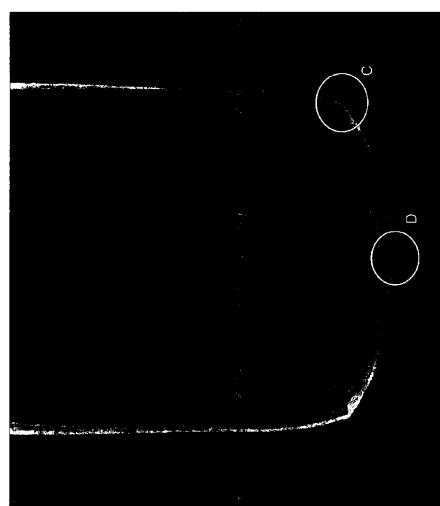

図6から図11は、ホール5の中の結果の酸化層の写真を示す。酸化層が、70nmの膜厚を有した。

【0077】

図7は、詳細に示された図6のAを示す。

【0078】

図8は、詳細に示された図6のBを示す。

【0079】

図9は、ホール5の底を示す。

【0080】

図10は、詳細に示された図9のCを示す

【0081】

図11は、詳細に示された図9のDを示す

【0082】

それらの写真から、均一に成長した膜厚70nmの酸化層が得られることが分かる。酸化物の膜厚は、高いアスペクト比のホール(5μm幅、50μm深さでアスペクト比0.1)に沿ってすべて均一である。

【0083】

写真から分かるように、連続した等角のシリコン酸化層が、このような高いアスペクト比のバイア5で得られた。

【0084】

本発明にかかるデバイスについて、材料とともに、好適な具体例、特定の構造や形状がここで検討されたが、添付の請求の範囲で規定される本発明の範囲から離れることなく、形状や細部において多くの変形や修正が行えることを理解すべきである。

【0085】

そのデバイスの製造プロセスが本発明の具体例にかかる方法を含む一例が、図5に示される。この例では、基板1の部分1aは、当業者にSTI領域として良く知られた分離領域を含む。基板1の部分1bは、コンタクト2を形成する複数のバイア1～バイアnと、複数の金属層M1～Mn+1とを含む。部分1aと部分1bとの間に、絶縁層3が存在する。この例では、絶縁層3は、第1層3aと第2層3bから形成されても良い。第1層3aは、例えば、例示では、400nmの膜厚のHDP(O(高密度プラズマ酸化物))を含む。第2層3bは、例えば、例示では、50nmの膜厚のSiCを含む。図5からわかるように、SiC層3bは、基板1の部分1a中に、少なくとも1つのホールやバイア5をエッチングする場合に、エッチングストップとして働く。本発明の具体例でが、酸化層は、ホールやバイア5中に適用できる。

10

20

30

40

【図1】

FIG. 1

【図3】

FIG. 3

【図2】

FIG. 2

【図4】

FIG. 4

【図5】

【図6】

Fig. 6

【図7】

FIG. 7

【図8】

FIG. 8

【図9】

FIG. 9

【図10】

FIG. 10

【図11】

FIG.11

【図12】

FIG. 12

---

フロントページの続き

(72)発明者 フィリップ・スサン

フランス、エフ - 13009マルセイユ、レジダンス・サン・ゲルマン・バー、アヴニュ・ドゥ・

マザルゲス 693番

(72)発明者 エリック・ペイネ

ベルギー、バー - 3001ルーヴァン、ロツツプールストラート 15番

(72)発明者 フィリップ・ミュレール

フランス、エフ - 92800ピュトー、リュ・サディ・カルノ 56番

審査官 萩原 周治

(56)参考文献 特開平06-350064 (JP, A)

特開平04-065822 (JP, A)

特開2003-086591 (JP, A)

特開2004-241479 (JP, A)

特開2006-261553 (JP, A)

特開平09-312349 (JP, A)

特開平01-287942 (JP, A)

特開平10-125882 (JP, A)

(58)調査した分野(Int.Cl., DB名)

H01L 21/312 - 21/32

H01L 21/3205

H01L 21/768

H01L 23/522 - 23/532