(19) 日本国特許庁(JP)

## (12) 公表特許公報(A)

(11) 特許出願公表番号

特表2015-513782

(P2015-513782A)

(43) 公表日 平成27年5月14日(2015.5.14)

| (51) Int.Cl.           | F 1        |      | テーマコード (参考) |

|------------------------|------------|------|-------------|

| HO1L 21/8234 (2006.01) | HO1L 27/08 | 102A | 5FO38       |

| HO1L 27/088 (2006.01)  | HO1L 29/06 | 601N | 5FO48       |

| HO1L 29/06 (2006.01)   | HO1L 27/06 | 102A | 5F1O2       |

| HO1L 27/06 (2006.01)   | HO1L 27/08 | 311A | 5J055       |

| HO1L 21/8236 (2006.01) | HO1L 29/91 | D    |             |

審査請求 有 予備審査請求 未請求 (全 38 頁) 最終頁に続く

|               |                              |                                 |                                 |

|---------------|------------------------------|---------------------------------|---------------------------------|

| (21) 出願番号     | 特願2014-555189 (P2014-555189) | (71) 出願人                        | 514191586 インフィネオン テクノロジーズ ドレス   |

| (86) (22) 出願日 | 平成25年1月30日 (2013.1.30)       | デン ゲーエムペーハー                     |                                 |

| (85) 翻訳文提出日   | 平成26年9月24日 (2014.9.24)       | ドイツ国 O1099 ドレスデン, ケ             |                                 |

| (86) 國際出願番号   | PCT/EP2013/051827            | ニグスブルッカ シュトラーセ 180              |                                 |

| (87) 國際公開番号   | W02013/113771                | (74) 代理人                        | 110000338 特許業務法人HARAKENZO WORKS |

| (87) 國際公開日    | 平成25年8月8日 (2013.8.8)         | L D P A T E N T & T R A D E M A |                                 |

| (31) 優先権主張番号  | 13/362,038                   | R K                             |                                 |

| (32) 優先日      | 平成24年1月31日 (2012.1.31)       | (72) 発明者                        | ワイス, ロルフ                        |

| (33) 優先権主張国   | 米国(US)                       | ドイツ連邦共和国, O1109 ドレス             |                                 |

|               |                              | デン, アム シュールホルツ 16               |                                 |

|               |                              | (72) 発明者                        | トロイ, ミヒヤエル                      |

|               |                              | オーストリア, アー-9500 フィラッ            |                                 |

|               |                              | ハ, シュライアーガッセ 16                 |                                 |

|               |                              | 最終頁に続く                          |                                 |

(54) 【発明の名称】アクティブドリフトゾーンを有する半導体配置

## (57) 【要約】

半導体素子配置は、負荷経路を有する第1半導体素子と、それぞれが第1負荷端子および第2負荷端子の間の負荷経路と制御端子とを有する、複数の第2半導体素子とを備える。上記複数の第2半導体素子の複数の負荷経路は、直列に接続され、かつ、上記第1半導体素子の上記負荷経路に直列に接続されている。各第2半導体素子の制御端子は、1つの他の上記第2半導体素子の上記負荷端子に接続されており、1つの上記第2半導体素子の制御端子は、第1半導体素子の1つの負荷端子に接続されている。各第2半導体素子は、少なくとも1つの素子特性を有する。少なくとも1つの上記第2半導体素子の少なくとも1つの素子特性は、他の上記第2半導体素子の対応する素子特性とは異なる。

FIG 1

FIG 13

**【特許請求の範囲】****【請求項 1】**

負荷経路を有する第1半導体素子(2)と、

それぞれが第1負荷端子および第2負荷端子( $3_{21}$  -  $3_{2n}$ 、 $3_{31}$  -  $3_{3n}$ )の間の負荷経路と制御端子( $3_{11}$  -  $3_{1n}$ )とを有する、複数の第2半導体素子( $3_1$  -  $3_n$ )とを備え、

上記複数の第2半導体素子( $3_1$  -  $3_n$ )の複数の負荷経路は、直列に接続され、かつ、上記第1半導体素子(2)の上記負荷経路に直列に接続されており、

各第2半導体素子( $3_1$  -  $3_n$ )の制御端子( $3_{11}$  -  $3_{1n}$ )は、1つの他の上記第2半導体素子( $3_1$  -  $3_n$ )の上記第1負荷端子および上記第2負荷端子のうちの1つに接続されており、上記複数の第2半導体素子( $3_1$  -  $3_n$ )のうちの1つの第2半導体素子( $3_1$ )の制御端子( $3_{11}$  -  $3_{1n}$ )は、上記第1半導体素子(2)の1つの負荷端子に接続されており、

各第2半導体素子( $3_1$  -  $3_n$ )は、少なくとも1つの素子特性を有し、

少なくとも1つの上記第2半導体素子( $3_1$  -  $3_n$ )の少なくとも1つの素子特性は、他の上記第2半導体素子の対応する素子特性とは異なることを特徴とする半導体素子配置。

**【請求項 2】**

上記複数の第2半導体素子( $3_1$  -  $3_n$ )は、MOSFET、MISFET、MESFET、FINFET、JFET、HEMT、IGBT、またはナノチューブ素子であり、

上記少なくとも1つの素子特性は、ゲート抵抗、閾値電圧、ゲート-ソース容量、ゲート-ドレイン容量、ドレイン-ソース容量、チャネル幅、ボディ厚さ、チャネル長さ、ゲート酸化膜厚さ、ならびに、ソース領域、ボディ領域およびドレイン領域の1つのドーピング濃度の中から選択されることを特徴とする請求項1に記載の半導体素子配置。

**【請求項 3】**

上記第1半導体素子(2)はトランジスタであることを特徴とする請求項1または2に記載の半導体素子配置。

**【請求項 4】**

上記トランジスタは、ノーマリオフトランジスタであることを特徴とする請求項3に記載の半導体素子配置。

**【請求項 5】**

上記複数の第2半導体素子( $3_1$  -  $3_n$ )は、ノーマリオントランジスタであることを特徴とする請求項1から4のいずれか一項に記載の半導体素子配置。

**【請求項 6】**

上記第1半導体素子(2)の上記負荷経路に負荷経路が直接接続されている1つ( $3_1$ )の上記第2半導体素子( $3_1$  -  $3_n$ )の制御端子( $3_{11}$ )は、上記第1半導体素子(2)の第1負荷端子( $2_2$ )に接続されており、

他の複数の上記第2半導体素子( $3_{21}$  -  $3_{2n}$ )のそれぞれの制御端子( $3_{12}$  -  $3_{1n}$ )は、別の第2半導体素子( $3_1$  -  $3_n$ )の第1負荷端子( $3_{21}$  -  $3_{2n}$ )に接続されていることを特徴とする請求項1から5のいずれか一項に記載の半導体素子配置。

**【請求項 7】**

上記他の複数の上記第2半導体素子( $3_{21}$  -  $3_{2n}$ )のそれぞれの制御端子( $3_{12}$  -  $3_{1n}$ )は、隣接する第2半導体素子の第1負荷端子( $3_{21}$  -  $3_{2n}$ )に接続されていることを特徴とする請求項6に記載の半導体素子配置。

**【請求項 8】**

上記少なくとも1つの第2半導体素子( $3_{1i}$ )の制御端子( $3_{11i}$ )と、別の第2半導体素子( $3_{1i+1}$ )の上記第1負荷端子( $3_{21i+1}$ )との間に、抵抗(41)が接続されていることを特徴とする請求項6に記載の半導体素子配置。

**【請求項 9】**

整流素子(42)が、上記抵抗(41)に並列に接続されていることを特徴とする請求

項 8 に記載の半導体素子配置。

**【請求項 1 0】**

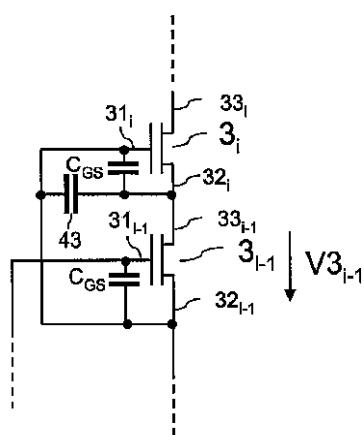

上記少なくとも 1 つの第 2 半導体素子 (3<sub>i</sub>) の上記制御端子 (31<sub>i</sub>) および上記第 1 負荷端子 (32<sub>i</sub>) の間に容量 (43) が接続されており、

上記容量 (43) は、上記少なくとも 1 つの第 2 半導体素子 (3<sub>i</sub>) のゲート - ソース容量 (C<sub>G S</sub>) に対して追加的に存在するものであることを特徴とする請求項 1 から 7 のいずれか一項に記載の半導体素子配置。

**【請求項 1 1】**

上記第 1 半導体素子 (2) は、n チャネルトランジスタまたは p チャネルトランジスタのうちの 1 つであることを特徴とする請求項 1 から 10 のいずれか一項に記載の半導体素子配置。 10

**【請求項 1 2】**

上記複数の第 2 半導体素子 (3<sub>1</sub> - 3<sub>n</sub>) は、n チャネルトランジスタまたは p チャネルトランジスタのうちの 1 つであることを特徴とする請求項 1 から 11 のいずれか一項に記載の半導体素子配置。

**【請求項 1 3】**

上記複数の第 2 半導体素子は FINFET であり、

各第 2 半導体素子は、

少なくとも 1 つの半導体フィン (52) と、

上記少なくとも 1 つの半導体フィン (52) の中に配置されたソース領域 (53)、ボディ領域 (55)、およびドレイン領域 (54) と、 20

上記ボディ領域 (55) に隣接して配置されるゲート電極 (56) とを備え、

上記ボディ領域 (55) は、上記ソース領域 (53) と上記ドレイン領域 (54) との間に配置され、

上記ゲート電極 (56) は、ゲート絶縁体 (57) によって上記ボディ領域 (55) から絶縁されていることを特徴とする請求項 1 から 12 のいずれか一項に記載の半導体素子配置。

**【請求項 1 4】**

半導体素子配置であって、

負荷経路を有する第 1 半導体素子 (2) と、 30

それぞれが第 1 負荷端子および第 2 負荷端子 (32<sub>1</sub> - 32<sub>n</sub>、33<sub>1</sub> - 33<sub>n</sub>) の間の負荷経路と制御端子 (31<sub>1</sub> - 31<sub>n</sub>) とを有する、複数の第 2 半導体素子 (3<sub>1</sub> - 3<sub>n</sub>) とを備え、

上記複数の第 2 半導体素子 (3<sub>1</sub> - 3<sub>n</sub>) の複数の負荷経路は、直列に接続され、かつ、上記第 1 半導体素子 (2) の上記負荷経路に直列に接続されており、

上記第 1 半導体素子および上記複数の第 2 半導体素子 (3<sub>1</sub> - 3<sub>n</sub>) を有する直列回路は、上記半導体素子配置の第 1 負荷端子 (12) および第 2 負荷端子 (13) の間に接続され、

2 つの上記第 2 半導体素子 (3<sub>1</sub> - 3<sub>n</sub>) の上記負荷経路の間に位置する、上記直列回路のタップと、 40

上記タップと連結された第 3 負荷端子 (13') とをさらに備えることを特徴とする半導体素子配置。

**【請求項 1 5】**

上記第 3 負荷端子 (13') と上記タップとの間に接続されたスイッチング素子 (35) を備え、

上記第 3 負荷端子 (13') は、上記第 2 負荷端子 (13) に接続されていることを特徴とする請求項 1 4 に記載の半導体素子配置。

**【請求項 1 6】**

上記スイッチング素子 (35) は、機械的スイッチング素子または半導体スイッチング素子であることを特徴とする請求項 1 5 に記載の半導体素子配置。 50

**【請求項 17】**

上記第3負荷端子(13')と上記タップとの間に接続されたヒューズを備え、

上記第3負荷端子(13')は、上記第2負荷端子(13)に接続されていることを特徴とする請求項14または15に記載の半導体素子配置。

**【請求項 18】**

各第2半導体素子(3<sub>1</sub>-3<sub>n</sub>)の制御端子は、1つの他の上記第2半導体素子(3<sub>1</sub>-3<sub>n</sub>)の上記負荷端子に接続されており、

1つの上記第2半導体素子(3<sub>1</sub>-3<sub>n</sub>)の制御端子は、上記第1半導体素子の複数の上記負荷端子の1つに接続されていることを特徴とする請求項13に記載の半導体素子配置。 10

**【請求項 19】**

並列に接続された少なくとも2つの直列回路(1<sub>1</sub>-1<sub>p</sub>)を備え、

各直列回路(1<sub>1</sub>-1<sub>p</sub>)は、負荷経路と制御端子とを有する第1半導体素子(2)と、複数の第2半導体素子(3<sub>1</sub>-3<sub>n</sub>)とを備え、

各第2半導体素子(3<sub>1</sub>-3<sub>n</sub>)は、第1負荷端子および第2負荷端子の間の負荷経路と制御端子とを有し、

駆動端子(11)と、

1つの直列回路の上記第1半導体素子(2)の上記制御端子(21)と上記駆動端子(11)との間に接続された少なくとも1つの抵抗(R1-Rp)とをさらに備え、

各直列回路の上記複数の第2半導体素子(3<sub>1</sub>-3<sub>n</sub>)の複数の負荷経路は、直列に接続されており、かつ、上記第1半導体素子(2)の上記負荷経路に直列に接続されており、 20

各直列回路(1<sub>1</sub>-1<sub>p</sub>)の各第2半導体素子(3<sub>1</sub>-3<sub>n</sub>)の制御端子は、1つの他の上記第2半導体素子の上記負荷端子に接続されており、

各直列回路(1<sub>1</sub>-1<sub>p</sub>)の1つの上記第2半導体素子(3<sub>1</sub>-3<sub>n</sub>)の制御端子は、上記第1半導体素子(2)の上記負荷端子の1つに接続されていることを特徴とする半導体素子配置。 30

**【請求項 20】**

複数の上記第1半導体素子(2)の各制御端子は、抵抗(R1-Rp)を介して上記駆動端子(11)に連結されており、

これら複数の抵抗(R1-Rp)のうち少なくとも2つは異なることを特徴とする請求項19に記載の半導体素子配置。 30

**【請求項 21】**

上記少なくとも1つの抵抗は、RC素子の一部であることを特徴とする請求項19に記載の半導体素子配置。

**【請求項 22】**

複数の上記第1半導体素子の各制御端子は、RC素子を介して上記駆動端子に連結されており、これら複数のRC素子のうち少なくとも2つは、異なる時定数を有することを特徴とする請求項19に記載の半導体素子配置。 40

**【請求項 23】**

3個、4個、5個、5個より多い、10個より多い、または、20個より多い第2半導体素子(3<sub>1</sub>-3<sub>n</sub>)を備えることを特徴とする請求項1から22のいずれか一項に記載の半導体素子配置。

**【発明の詳細な説明】****【発明の詳細な説明】****【0001】**

本発明の実施形態は、半導体の配置に関し、特に第1半導体素子および直列に接続された複数の第2半導体素子の半導体の配置に関する。

**【0002】**

パワートランジスタまたはパワーダイオードのようなパワー半導体素子の開発における 50

1つの重要な目的は、高い電圧ブロッキング能力を有するにもかかわらず、低いオン抵抗( $R_{ON}$ )および低いスイッチング損失を有する素子を実現することである。

#### 【0003】

パワートランジスタは、通常、ボディ領域およびドレイン領域の間に配置された、ドレイン領域より低くドープされたドリフト領域を備える。従来のパワートランジスタのオン抵抗は、電流が流れる方向におけるドリフト領域の長さおよびドリフト領域のドーピング濃度に依存している。ここで、ドリフト領域の長さが減少すると、または、ドリフト領域のドーピング濃度が増加すると、オン抵抗は低下する。しかしながら、上記領域の長さの減少またはドーピング濃度の増加は、電圧ブロッキング能力を低下させる。

#### 【0004】

所定の電圧ブロッキング能力を有するパワートランジスタのオン抵抗を低下させる1つの考え得る方法は、ドリフト領域の中に複数の補償領域を設けることである。ここで、補償領域は、ドリフト領域に対して相補的にドープされている。他の考え得る方法は、ドリフト領域の中に複数のフィールドプレートを設けることである。フィールドプレートは、ドリフト領域から誘電的に絶縁され、かつ、例えば上記トランジスタのゲートまたはソース端子に接続されている。これらのタイプのパワートランジスタでは、複数の補償領域またはフィールドプレートは、構成部品がオフ状態であるとき、ドリフト領域におけるドーピング電荷を部分的に“補償”する。これにより、電圧ブロッキング能力を低下させることなく、オン抵抗を低下させる、ドリフト領域のより高いドーピングを提供することができる。

10

#### 【0005】

パワーダイオード(ピンダイオード)は、通常、第1ドーピング型の第1エミッタ領域および第2ドーピング型の第2エミッタ領域の間に、低くドープされたドリフトまたはベース領域を備える。パワーダイオードは、第1および第2エミッタ領域の間に第1極性の電圧(ブロッキング電圧)が印加されたときブロックするために組み込まれ、また、第1および第2エミッタ領域の間に第2極性の電圧が印加されたとき電流を導通するために組み込まれる。しかしながら、導通状態において、上記第1型および第2型の電荷キャリア( $p$ 型および $n$ 型電荷キャリア)を有する電荷キャリアプラズマが、ベース領域において生じる。ベース領域に蓄積される電荷キャリアプラズマの量は、ベース領域の長さに依存し、それゆえ、電圧ブロッキング能力に依存する。電圧ブロッキング能力が上昇すると、電荷キャリアプラズマの量は増加する。この電荷キャリアプラズマは、ダイオードがブロッキング電圧の印加をブロックする前に除去されなければならない。

20

#### 【0006】

しかしながら、これらの既知の素子は、オン状態からオフ状態へおよびその逆へ素子の動作状態を変更するときの時間遅延をもたらす高出力容量を有している。それゆえ、問題は、高い電圧ブロッキング能力、低いオン抵抗、および低出力容量を有するパワー半導体素子のように作用する半導体配置を提供することにある。

30

#### 【0007】

この問題は、クレーム1、14、19の半導体配置によって解決される。限定された実施形態は下位のクレームに開示される。

40

#### 【0008】

第1実施形態は、半導体素子配置に関する。上記半導体素子配置は、負荷経路を有する第1半導体素子、および、複数の第2半導体素子を備える。複数の第2半導体素子のそれぞれは、第1および第2負荷端子と、制御端子との間に負荷経路を有する。複数の第2半導体素子の複数の負荷経路は、直列に接続されており、かつ、第1半導体素子の負荷経路に直列に接続されている。複数の第2半導体素子のそれぞれの制御端子は、他の1つの第2半導体素子の負荷端子に接続されており、1つの第2半導体素子の制御端子は、第1半導体素子の複数の負荷端子の1つに接続されている。さらに、第2半導体素子のそれぞれは、少なくとも1つの素子特性を有しており、少なくとも1つの第2半導体素子の少なくとも1つの素子特性は、他の第2半導体素子の対応する素子特性とは異なる。

50

## 【0009】

第2実施形態は、半導体素子配置に関する。上記半導体素子配置は、負荷経路を有する第1半導体素子、および、複数の第2トランジスタを備える。複数の第2トランジスタのそれぞれは、第1負荷端子、第2負荷端子および制御端子の間に負荷経路を有する。複数の第2トランジスタの複数の負荷経路は、直列に接続されており、第1半導体素子の負荷経路に直列に接続されている。第1半導体素子および複数の第2トランジスタを有する直列回路は、上記半導体素子配置の第1負荷端子および第2負荷端子の間に接続される。上記半導体素子配置は、さらに上記直列回路のタップを備える。上記タップは、2つの第2トランジスタの負荷経路の間に位置し、第3負荷端子が上記タップに連結している。

## 【0010】

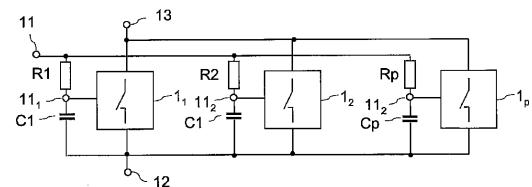

第3実施形態は、半導体素子配置に関する。上記半導体素子配置は、並列に接続された少なくとも2つの直列回路を備える。各直列回路は、負荷経路および制御端子を有する第1半導体素子と、複数の第2半導体素子を備える。複数の第2半導体素子のそれぞれは、第1および第2負荷端子と制御端子との間に負荷経路を有する。上記半導体素子配置は、さらに駆動端子を備える。少なくとも1つの抵抗は、1つの直列回路の第1半導体素子の制御端子と駆動端子との間に接続される。各直列回路の複数の第2半導体素子の複数の負荷経路は、直列に接続され、かつ、第1半導体素子の負荷経路に直列に接続される。各直列回路の各第2半導体素子の制御端子は、他の第2半導体素子の1つの負荷端子に接続されており、各直列回路の1つの第2半導体素子の制御端子は、第1半導体素子の複数の負荷端子のうちの1つに接続されている。

10

20

## 【0011】

当業者は、以下の詳細な説明を読み添付された図面を見ることによって、追加的な特徴および利点を認識するだろう。

## 【0012】

ここで、図面を参照して、実施例を説明する。図面は、基礎原理を理解するために必要な様式のみを説明するように、基礎原理を説明する役割を果たす。図は一定に比例してはいない。図において、同じ参照符号は同様の特徴を示す。

30

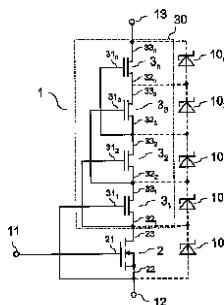

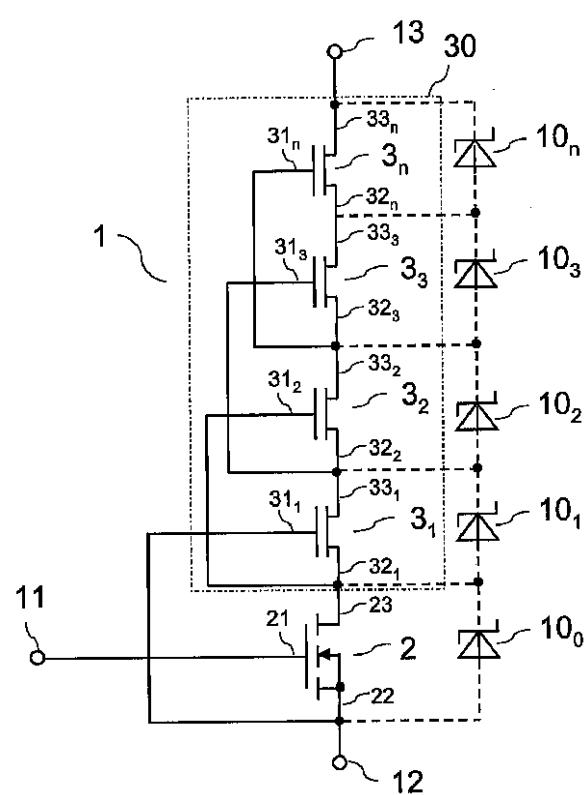

## 【0013】

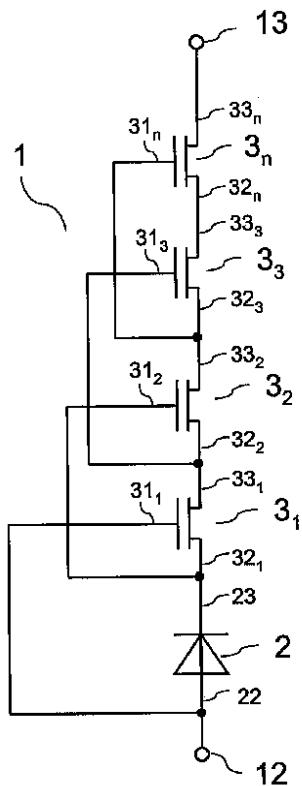

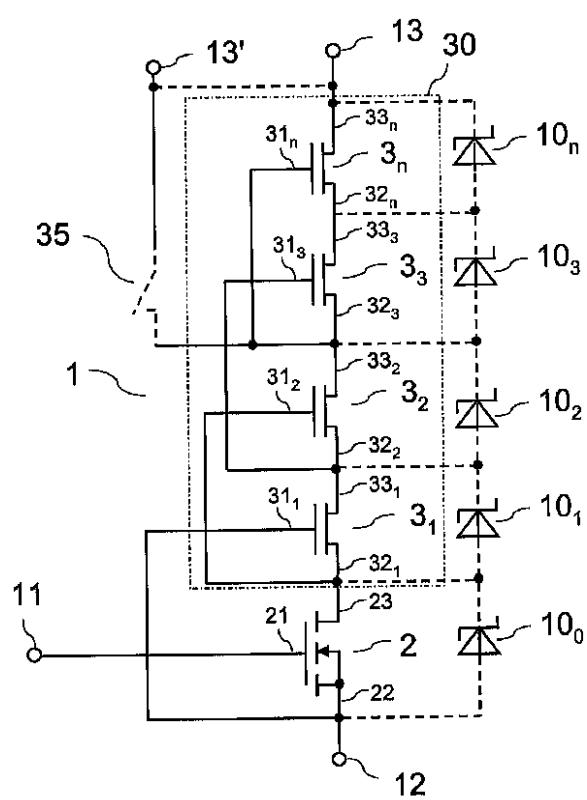

図1は、トランジスタとして実装される第1半導体素子と、互いに直列に接続され、かつ第1半導体素子に直列に接続された複数の第2半導体素子とを有する半導体配置を図示する。

30

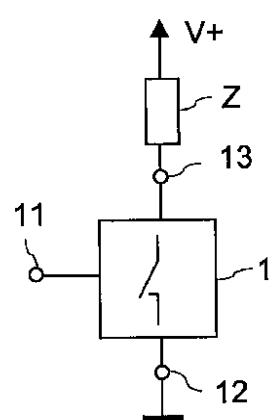

## 【0014】

図2は、負荷をスイッチングする電気スイッチとしての図1の半導体配置の応用を図示する。

## 【0015】

図3は、ダイオードとして実装される第1半導体素子と、互いに直列に接続され、かつ第1半導体素子に直列に接続された複数の第2半導体素子とを有する半導体配置を図示する。

## 【0016】

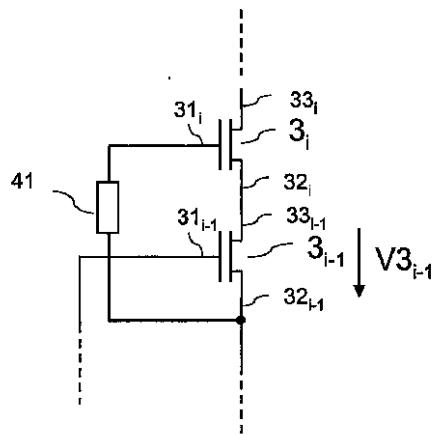

図4は、第1実施形態によるゲート抵抗が異なる2つの第2トランジスタを有する直列回路を図示する。

40

## 【0017】

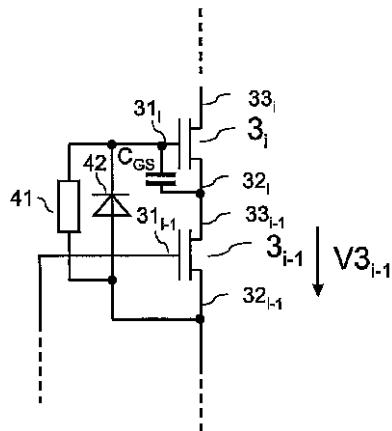

図5は、第2実施形態によるゲート抵抗が異なる2つの第2トランジスタを有する直列回路を図示する。

## 【0018】

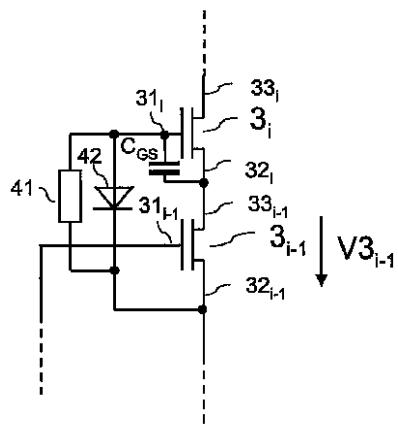

図6は、第3実施形態によるゲート抵抗が異なる2つの第2トランジスタを有する直列回路を図示する。

## 【0019】

図7は、ゲート-ソース容量が異なる2つの第2トランジスタを有する直列回路を図示する。

50

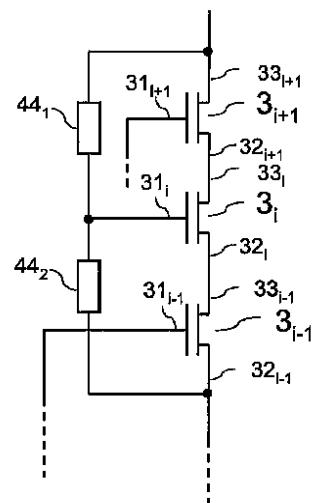

## 【0020】

図8は、数個の第2トランジスタと、抵抗性分圧器を通して駆動される1つの第2トランジスタとを有する直列回路を図示する。

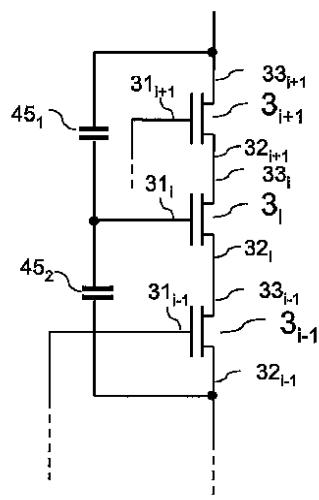

## 【0021】

図9は、数個の第2トランジスタと、容量性分圧器を通して駆動される1つの第2トランジスタとを有する直列回路を図示する。

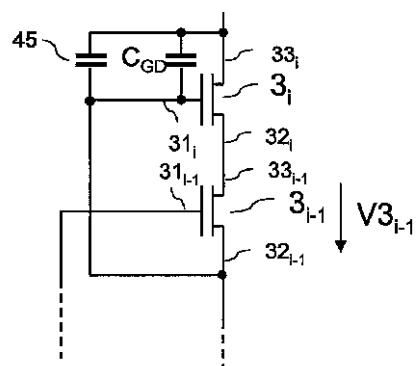

## 【0022】

図10は、ゲート-ドレイン容量が異なる2つの第2トランジスタを有する直列回路を図示する。

## 【0023】

図11は、ドレイン-ソース容量が異なる2つの第2トランジスタを有する直列回路を図示する。

10

## 【0024】

図12は、空乏型MOSFETとしての1つの第2トランジスタの実装の概略を図示する。

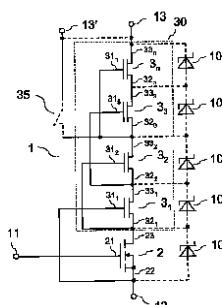

## 【0025】

図13は、図1の回路配置の変形例を図示する。

## 【0026】

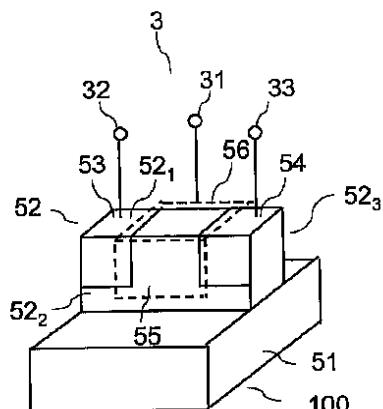

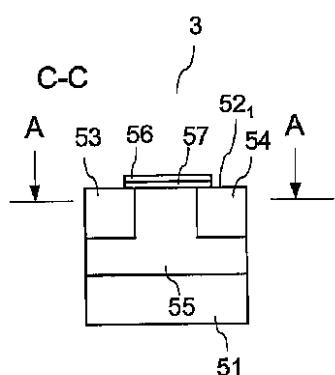

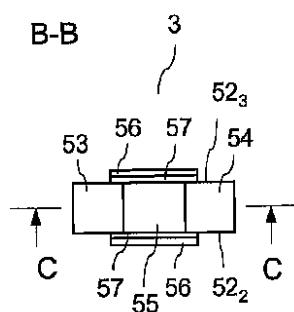

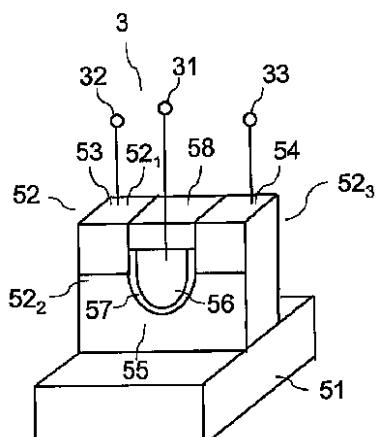

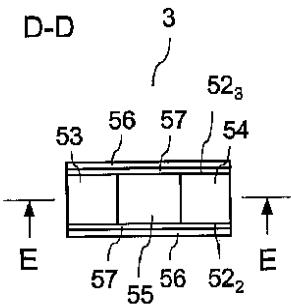

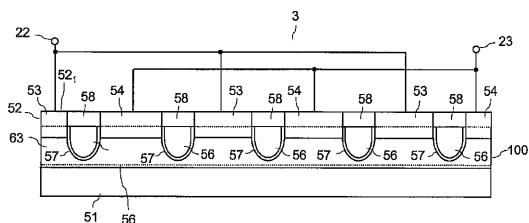

図14は、図14Aから図14Cを含み、FINFETとして実装される1つの第2半導体素子の第1実施形態を図示する。

20

## 【0027】

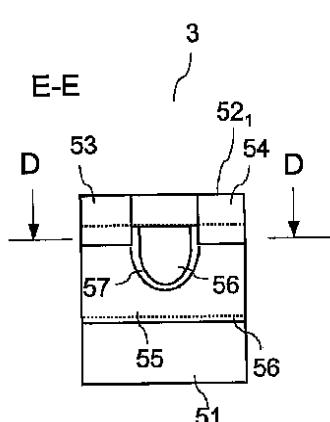

図15は、図15Aから図15Cを含み、FINFETとして実装される1つの第2半導体素子の第2実施形態を図示する。

## 【0028】

図16は、第1半導体素子と複数の第2半導体素子が1つの半導体フィンで実装される第1実施形態による半導体本体の垂直断面図を示す。

## 【0029】

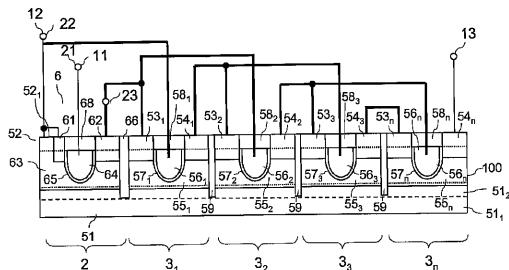

図17は、第1半導体素子と複数の第2半導体素子が1つの半導体フィンで実装される第2実施形態による半導体本体の垂直断面図を示す。

30

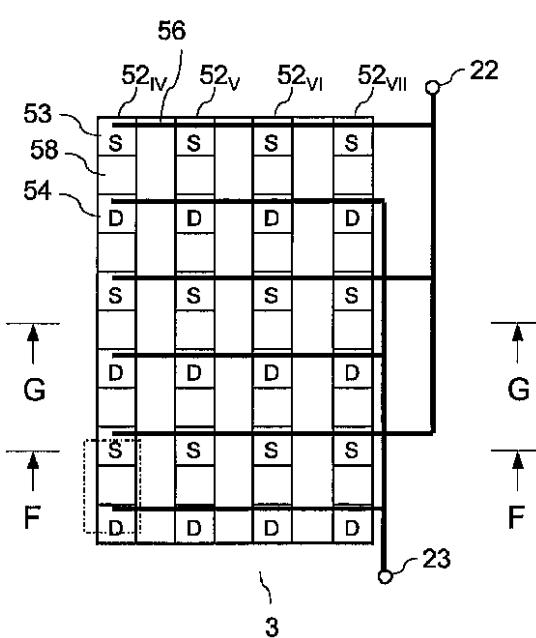

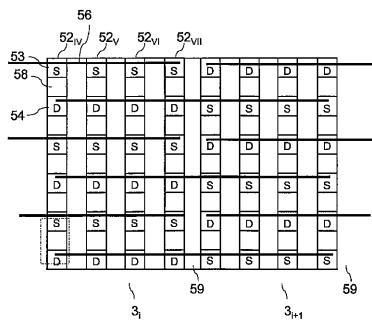

## 【0030】

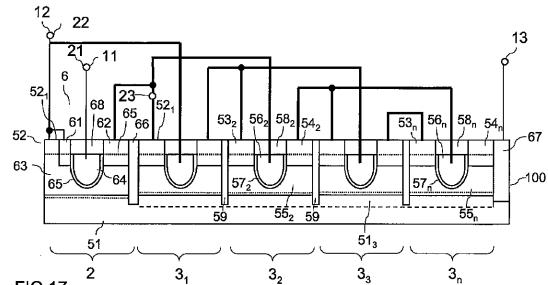

図18は、第1半導体素子と、それぞれが数個のFINFETセルを含む複数の第2半導体素子とが実装される第3実施形態による半導体本体の平面図を示す。

## 【0031】

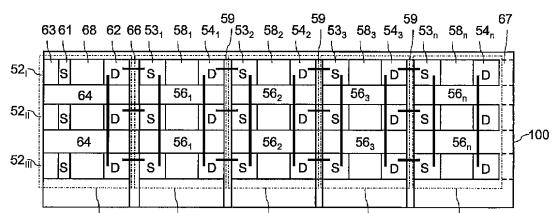

図19は、並列に接続される数個のFINFETセルを含む1つの第2半導体素子の垂直断面図を示す。

## 【0032】

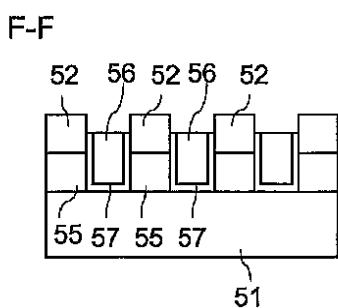

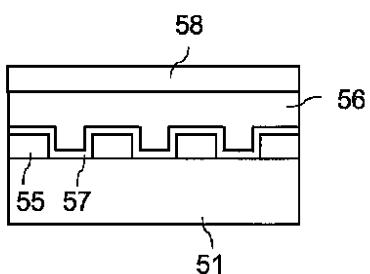

図20は、図20Aから図20Cを含み、並列に接続される数個のFINFETセルを含む1つの第2半導体素子のさらなる実施形態を図示する。

40

## 【0033】

図21は、図20に図示されたタイプの、直列に接続された2つの第2半導体素子を図示する。

## 【0034】

図22は、上記半導体配置のさらなる実施形態を図示する。

## 【0035】

以下の詳細な説明では、参照は添付の図面に付され、その一部を形成し、本発明が実施されうる具体的な複数の実施形態を説明する方法で示される。ここに記載された様々な典型的な実施形態の特徴は、他に特段の記載がない限り、互いに組み合わせてもよいと理解されるべきである。

## 【0036】

図1は、第1半導体素子2および複数の第2半導体素子3<sub>1</sub> - 3<sub>n</sub>を含む半導体配置1

50

の第1実施形態を図示する。第1半導体素子2は、第1負荷端子22および第2負荷端子23との間の負荷経路を有し、上記負荷経路が電流を伝導するオン状態、または、上記負荷経路が遮断するオフ状態を取ることができる。図1による第1半導体素子2は、トランジスタとして実装され、さらに制御端子21を備える。特に、図1による第1半導体素子2は、MOSFETとして実装され、制御端子21はゲート端子であり、第1および第2負荷端子22・23はそれぞれソース端子およびドレイン端子である。

#### 【0037】

以下の図と同様に、図1では、下付添字が付された参照番号“3”は、個々の第2半導体素子を示す。制御端子および負荷端子のような、個々の第2半導体素子の同じ部分は、下付添字が付された同じ参照符号を持つ。例えば、 $3_1$ は、制御端子 $3_{11}$ ならびに第1および第2負荷端子 $3_{21} \cdot 3_{31}$ を有する1番目の1つの第2半導体素子を示す。以下では、参照符号は、複数の第2半導体素子の任意の1つに、または、複数の第2半導体素子に付され、個々の第2半導体素子の間の区別が必要ないとき、添字のない参照番号3、 $3_1$ 、 $3_2$ 、 $3_3$ が複数の第2半導体素子およびそれらの個々の部分を示すものとして使用される。

10

#### 【0038】

第2半導体素子3は、図1に示す実施形態ではトランジスタとして実装され、以下では第2トランジスタとして言及されることもある。複数の第2トランジスタ3のそれぞれは、制御端子 $3_1$ と、第1負荷端子 $3_2$ および第2負荷端子 $3_3$ との間の負荷経路とを有する。1つの第2トランジスタの第1負荷端子が隣接する第2トランジスタの第2負荷端子に接続されるように、複数の第2半導体素子の複数の負荷経路 $3_{21} \cdot 3_{31}$ は、互いに直列に接続されている。さらに、複数の第2トランジスタ3の複数の負荷経路は、第1半導体素子2の負荷経路 $2_2 \cdot 2_3$ と直列に接続され、第1半導体素子2および複数の第2トランジスタ3はカスコードのような回路を形成している。

20

#### 【0039】

図1を参照すると、n個の第2トランジスタ3がある( $n > 1$ である)。これらn個の第2トランジスタ3のうち、1番目の第2トランジスタ $3_1$ は、n個の第2トランジスタ3を有する直列回路において第1半導体素子2の最も近くに配置され、かつ、第1半導体素子2の負荷経路 $2_2 \cdot 2_3$ に直接接続された負荷経路 $3_{21} \cdot 3_{31}$ を有する第2トランジスタである。 $n$ 番目の第2トランジスタ $3_n$ は、n個の第2トランジスタ3を有する直列回路において第1半導体素子2から最も離れて配置された第2トランジスタである。図1に示す実施形態において、 $n = 4$ 個の第2トランジスタ3がある。しかしながら、これは一例であり、第2トランジスタ3の個数nは任意に、つまり、半導体素子配置1の所望の電圧ブロッキング能力に応じて、選択することができる。これについて、以下に詳細に説明する。

30

#### 【0040】

各第2半導体素子3は、その制御端子 $3_1$ を有し、該制御端子 $3_1$ は、別の1つの第2半導体素子3の負荷端子の1つに、または、第1半導体素子2の負荷端子の1つに、接続されている。図1に示す実施形態では、1番目の第2トランジスタ $3_1$ はその制御端子 $3_{11}$ を有し、該制御端子 $3_{11}$ は第1半導体素子2の第1負荷端子 $2_2$ に接続されている。他の第2トランジスタ $3_{21} \cdot 3_{31}$ のそれぞれは、それらの制御端子 $3_{12} \cdot 3_{13}$ を有し、該制御端子 $3_{12} \cdot 3_{13}$ は、直列回路において第1半導体素子2の方向に隣接する第2トランジスタの第1負荷端子 $3_{21} \cdot 3_{23}$ に接続される。説明のために、 $3_i$ が、1番目のトランジスタ $3_1$ 以外の第2トランジスタ $3_{21} \cdot 3_{31}$ の1つであると仮定する。この場合、この第2トランジスタ(上側の第2トランジスタ) $3_i$ の制御端子 $3_{1i}$ は、隣接する第2トランジスタ(下側の第2トランジスタ) $3_{i-1}$ の第1負荷端子 $3_{2i-1}$ に接続される。上側の第2トランジスタ $3_i$ の制御端子が接続される下側の第2トランジスタ $3_{i-1}$ の第1負荷端子 $3_{2i-1}$ は、この上側の第2トランジスタ $3_i$ の負荷端子 $3_{2i} \cdot 3_{3i}$ の1つとは直接接続されていない。さらなる実施形態(図示せず)によれば、1つの第2トランジスタ $3_i$ の制御端子 $3_{1i}$ は、第2トランジスタ $3_i$ に直

40

50

接続される第2トランジスタ $3_{i-1}$ の第1負荷端子 $3_{1i-1}$ に接続されないが、上記トランジスタからさらに遠くの第2トランジスタ $3_{i-k}$ の負荷端子 $3_{2i-k}$ に接続される( $k > 1$ である)。例えば、もし $k = 2$ であれば、第2トランジスタ $3_i$ の制御端子 $3_{1i}$ は、直列回路において第1半導体素子2の方向に上記第2トランジスタ $3_i$ から2つの第2トランジスタ分離れた、第2トランジスタ $3_{i-2}$ の第1負荷端子 $3_{2i-2}$ に接続される。

## 【0041】

図1を参照するに、第1半導体素子2および複数の第2トランジスタ3は、複数のMOSFET(金属酸化膜半導体電界効果トランジスタ)として実装されうる。これら複数のMOSFETのそれぞれは、制御端子 $2_1 \cdot 3_1$ としてのゲート端子、第1負荷端子 $2_2 \cdot 3_2$ としてのソース端子、および第2負荷端子 $2_3 \cdot 3_3$ としてのドレイン端子を有する。複数のMOSFETは、ゲートおよびソース端子(制御端子および第1負荷端子)の間に印加された電圧によって制御することができる電圧制御素子である。それゆえ、図1に示される配置では、1番目の第2トランジスタ $3_1$ は、第1半導体素子2の負荷経路電圧に対応する電圧によって制御される。他の第2トランジスタ $3_i$ は、少なくとも1つの第2トランジスタ $3_{i-1}$ または $3_{i-2}$ の負荷経路電圧によって制御される。1つのMOSFETの“負荷経路”電圧は、このMOSFETの第1および第2負荷端子(ドレインおよびソース端子)の間の電圧である。

10

## 【0042】

図1に示す実施形態では、第1半導体素子2は、ノーマリオフ(エンハンスマント)トランジスタであるが、複数の第2トランジスタ3は、ノーマリオン(ディプレッション)トランジスタである。しかしながら、これは単なる一例である。第1半導体素子2および複数の第2トランジスタ3のそれぞれは、ノーマリオントランジスタとして、またはノーマリオフトランジスタとして実装(実施)されうる。個々のトランジスタは、n型トランジスタとして、またはp型トランジスタとして実装されうる。

20

## 【0043】

MOSFETとして第1半導体素子2および第2トランジスタ3を実装することは単なる一例である。MOSFET、MISFET(金属-絶縁体-半導体電界効果トランジスタ)、MESFET(金属半導体電界効果トランジスタ)、IGBT(絶縁ゲートバイポーラトランジスタ)、JFET(接合ゲート電界効果トランジスタ)、FINFET(フィンFET)、ナノチューブ素子、HEMT(高電子移動度トランジスタ)等のような、任意のタイプのトランジスタを、第1半導体素子2および第2トランジスタ3の実装(実施)に使用することができる。第1半導体素子2および第2半導体素子3の実装に使用される素子のタイプに依存せず、上記直列回路において、複数の第2トランジスタ3のそれぞれは少なくとも1つの他の第2トランジスタ3または第1半導体素子2によって制御されるように、これらの素子は接続される。

30

## 【0044】

トランジスタとして実装される第1半導体素子2、および第2トランジスタ3を有する上記半導体素子配置1は、第1半導体素子2に適切な駆動電圧を印加することにより、従来のトランジスタのように、オンおよびオフを切り替えることができる。第1半導体素子2の制御端子 $2_1$ は、全体の配置1の制御端子 $1_1$ を形成し、第1半導体素子2の第1負荷端子 $2_1$ およびn番目の第2トランジスタ $3_n$ の第2負荷端子は、それぞれ、全体の配置1の第1および第2負荷端子 $1_2 \cdot 1_3$ を形成している。

40

## 【0045】

図2は、負荷Zをスイッチングするための電子スイッチとしての上記半導体素子配置1の使用を図示する。第1および第2負荷端子 $1_2 \cdot 1_3$ の間の経路である上記半導体配置1の負荷経路は、上記負荷と直列に接続されている。上記半導体素子配置1および上記負荷Zを有するこの直列回路は、第1(正)および第2(負)の電源電位V+、GNDのための複数の端子の間に接続される。

## 【0046】

50

半導体配置 1 の動作原理を以下に説明する。単に説明のために、第 1 半導体素子 2 は n 型エンハンスマントMOSFETとして実装されていると仮定し、複数の第 2 トランジスタ 3 は n 型ディプレッショNMOSFETまたはn型JFETとして実装されていると仮定し、個々の素子 2、3 は、図 1 に図示するように相互に接続されていると仮定する。しかしながら、基本的な動作原理は、他のタイプの第 1 および第 2 半導体素子で実装された半導体素子配置にも適用される。

#### 【0047】

第 2 トランジスタ 3 の実装に使用されうるディプレッショNMOSFETまたはJFETは、ほぼ 0 の駆動電圧（ゲート - ソース電圧）が印加されたとき、オン状態である半導体素子であり、一方、素子のピンチオフ電圧より駆動電圧の絶対値が高いとき、MOSFETまたはJFETはオフ状態である。“駆動電圧”は、素子のゲート端子およびソース端子の間の電圧である。n型MOSFETまたはJFETでは、ピンチオフ電圧は負の電圧であり、p型MOSFETまたはJFETではピンチオフ電圧は正の電圧である。

10

#### 【0048】

第 2 および第 1 負荷端子 13・12 の間に（正の）電圧が印加され、かつ、制御端子 1 1 に適切な駆動電位が加えられることによって第 1 半導体素子 2 がオンに切り替えられたとき、1番目の第 2 トランジスタ 3<sub>1</sub> は導通し（オン状態であり）、第 1 半導体素子 2 の負荷経路 22-23 に渡る電圧の絶対値は低すぎて、1番目の第 2 トランジスタ 3<sub>1</sub> をピンチオフできない。その結果、1番目の第 2 トランジスタ 3<sub>1</sub> の負荷経路電圧によって制御される 2 番目の第 2 トランジスタ 3<sub>2</sub> もまた、導通し始める。言い換えると、第 1 半導体素子 2 および各第 2 トランジスタ 3 は、最終的に導通し、半導体配置 1 はオン状態になる。半導体配置 1 がオン状態であり、かつ、半導体素子 2 がオフに切り替えられたとき、第 1 半導体素子 2 の負荷経路に渡る電圧降下は増大し、上記負荷経路の電圧の絶対値が 1 番目の第 2 トランジスタ 3 のピンチオフ電圧に到達したとき、1番目の第 2 トランジスタ 3<sub>1</sub> はオフに切り替わり始める。全体の配置 1 の第 2 負荷端子 13 および第 1 負荷端子 12 の間に正の電圧が印加されたとき、第 1 半導体素子 2 がオフに切り替わると、第 1 半導体素子 2 の第 2 負荷端子 23 および第 1 負荷端子 22 の間の電圧はまた、正の電圧になる。この場合、1番目の第 2 トランジスタ 3<sub>1</sub> のゲート - ソース電圧は、このトランジスタ 3<sub>1</sub> をピンチオフにするのに適した負の電圧になる。

20

#### 【0049】

1番目の第 2 トランジスタ 3<sub>1</sub> がオフに切り替わったとき、その負荷経路に渡る電圧降下は増大するため、2番目の第 2 トランジスタ 3<sub>2</sub> はオフに切り替わる。これにより、各第 2 トランジスタ 3 がオフに切り替わるまで、順に 3 番目の第 2 トランジスタ 3<sub>3</sub> 等がオフに切り替わり、最終的に半導体素子配置 1 は安定したオフ状態になる。第 2 および第 1 端子 13・12 の間に印加される外部電圧は、第 1 半導体素子 2 および第 2 トランジスタ 3 に渡って外部電圧を分配する必要がある数、オン状態からオフ状態になる複数の第 2 トランジスタと同じ数だけ、スイッチングを行う。低い外部電圧が印加されたとき、いくつかの第 2 トランジスタ 3 はオン状態のままであるが、他はオフ状態になる。オフ状態になる第 2 トランジスタ 2 の数は、外部電圧が増加するにつれて増加する。このように、全体の半導体素子配置 1 の電圧ブロッキング能力の範囲における高い外部電圧が印加されたとき、第 1 半導体素子 2 および各第 2 トランジスタ 3 はオフ状態になる。半導体素子配置 1 がオフ状態であり、かつ、第 1 半導体素子 2 がオンに切り替えられたとき、第 1 半導体素子 2 の負荷経路に渡る電圧降下は減少し、それは 1 番目の第 2 トランジスタ 3<sub>1</sub> をオンに切り替え、以下同様に順に 2 番目の第 2 トランジスタ 3<sub>2</sub> 等をオンに切り替える。これは各第 2 トランジスタ 3 を再びオンに切り替えるまで続く。

40

#### 【0050】

第 1 半導体素子 2 に直列に接続された複数の第 2 トランジスタ 3 のスイッチング状態は、第 1 半導体素子 2 のスイッチング状態に依存しており、第 1 半導体素子 2 のスイッチング状態に従う。このように、半導体配置 1 のスイッチング状態は、第 1 半導体素子 2 のスイッチング状態によって定義される。第 1 半導体素子 2 がオン状態の時、半導体配置 1 は

50

オン状態であり、第1半導体素子2がオフ状態の時、半導体配置1はオフ状態である。

#### 【0051】

半導体配置1は、それがオン状態であるとき、第1および第2負荷端子12・13の間に低い抵抗を有し、それがオフ状態であるとき、第1および第2負荷端子12・13の間に高い抵抗を有する。オン状態では、第1および第2負荷端子12・13の間のオーム抵抗は、第1半導体素子2および第2トランジスタ3のオン抵抗 $R_{ON}$ の合計に相当する。半導体配置1がアバランシェ降伏が起きる前のオフ状態であるときの第1および第2負荷端子12・13の間に印加されうる最大電圧である電圧ブロッキング能力は、第1半導体素子2および複数の第2トランジスタ3の電圧ブロッキング能力の合計に相当する。第1半導体素子2および個々の第2トランジスタ3は、3Vから50Vの間の電圧ブロッキング能力のような、比較的低い電圧ブロッキング能力を有してよい。しかしながら、第2トランジスタ3の数に依存して、600Vまたはそれ以上のような、最大で数100Vの、全体として高い電圧ブロッキング能力が得られる。10

#### 【0052】

半導体配置1の電圧ブロッキング能力およびオン抵抗は、それぞれ、第1半導体素子2および複数の第2トランジスタ3の電圧ブロッキング能力、ならびに、第1半導体素子2および複数の第2トランジスタ3のオン抵抗によって定義される。5個以上、10個以上、または20個以上の第2トランジスタ3のように、2つより著しく多い第2トランジスタ3が実装されているとき( $n > 2$ )、半導体配置1の電圧ブロッキング能力およびオン抵抗は、主に複数の第2トランジスタ3を有する配置30によって定義される。全体の半導体配置1は、従来のパワートランジスタのように動作することができる。ここで、従来のパワートランジスタでは、主に統合されたドリフト領域がオン抵抗および電圧ブロッキング能力を定義していた。このように、複数の第2トランジスタ3を有する配置30は、従来のパワートランジスタにおけるドリフト領域と同等の機能を有する。それゆえ、複数の第2トランジスタ3を有する配置30を、ここでは、アクティブドリフト領域(ADR: active drift region)と呼称する。図1の全体の半導体素子配置1は、ADZトランジスタまたはADRトランジスタ(ADZトランジスタ)と呼ぶことができ、あるいは、第1半導体素子2がMOSFETで実装されているときはADRFET(ADZFET)と呼ぶことができる。20

#### 【0053】

半導体素子配置1がオフ状態であるとき、第1および第2負荷端子12・13の間に印加された電圧は分配され、この電圧の一部は、第1半導体素子2の負荷経路22-23に渡って降下し、この電圧の他の部分は、複数の第2トランジスタ3の複数の負荷経路に渡って降下する。しかしながら、複数の第2トランジスタ3へのこの電圧の分配が等しくない場合がある。その代わり、第1半導体素子2により近いそれらの第2トランジスタ3は、第1半導体素子2からより離れたそれらの第2トランジスタ3よりも高い電圧負荷を有してもよい。30

#### 【0054】

複数の第2トランジスタ3に電圧がより均等に分配されるために、半導体配置1は、任意で、複数の第2トランジスタ3の複数の負荷経路に渡って電圧を制限または固定(クランプ)する電圧制限手段 $10_1 - 10_n$ を含む。任意で、クランプ素子 $10_0$ がまた、第1半導体素子2の負荷経路(ソースおよびドレイン端子の間)に並列に接続される。電圧クランプ手段 $10_0 - 10_n$ は、多くの異なる方法で実装(実施)することができる。単に説明のために、図1に図示されるクランプ手段 $10_0 - 10_n$ はツェナーダイオード $10_0 - 10_n$ を含みうる。各ツェナーダイオード $10_0 - 10_n$ は、複数の第2トランジスタ3の1つの負荷経路に、任意で第1半導体素子2の負荷経路に、並列で接続されている。40

#### 【0055】

ツェナーダイオード $10_0 - 10_n$ の代わりに、トンネルダイオード、PINダイオード、アバランシェダイオード等を、同じように使用してもよい。さらなる実施形態(図示50

せず)によれば、個々のクランプ素子 $10_0 - 10_n$ は、例えば、複数の第2トランジスタ3が $n$ 型MOSFETである場合、 $p$ 型MOSFETのようなトランジスタとして実装される。これらのクランプMOSFETのそれぞれは、そのゲート端子がそのドレイン端子に接続され、各MOSFETの負荷経路(ドレイン-ソース経路)は、複数の第2トランジスタ3のうちの1つの負荷経路に並列に接続される。

#### 【0056】

図1に図示されるツエナーダイオード $10_0 - 10_n$ のような、個々のクランプ素子は、第1半導体素子2および複数の第2トランジスタ3と同じ半導体本体(ボディ)の中に統合されうる。しかしながら、これらのクランプ素子は、半導体本体の外側に配置される外部素子として実装されることも可能である。

10

#### 【0057】

図3は、半導体素子配置1のさらなる実施形態を図示する。図3の配置では、第1半導体素子2は、第1負荷端子21を形成するアノード端子と第2負荷端子を形成するカソード端子とを有するダイオードとして実装される。図3の半導体配置1の動作原理は、(図1に係るトランジスタのような)制御端子を介して制御することができないが、第2および第1負荷端子23・22の間に印加される電圧の極性によって制御されるダイオードのオン状態(順方向バイアスされた状態)およびオフ状態(逆バイアスされた状態)の違いはあるが、図1の半導体配置1の動作原理に対応する。複数の第2トランジスタ3として $n$ 型ディプレッションMOSFETまたは $n$ 型JFETを実装(使用)したとき、図3の半導体配置1は、半導体配置1の第1および第2負荷端子13・12の間に正電圧が印加されたとき、オン状態であり、図3の半導体配置1は、半導体配置1の第1および第2負荷端子13・12の間に負電圧が印加されたとき、オフ状態である。図1の半導体配置1に関して説明した他の全てのことは、図3のダイオード2を有する半導体配置1に適宜当てはまる。図3に係るダイオードを有する半導体配置1は、従来の(高電圧の)ダイオードのように使用することができる。

20

#### 【0058】

以下では、第1半導体素子2と複数の第2半導体素子(第2トランジスタ)3との区別が必要ないとき、第1半導体素子2および複数の第2トランジスタ3を簡単に“素子”と呼ぶ。

30

#### 【0059】

第2トランジスタ3のそれぞれは、個々のトランジスタの動作またはスイッチングの挙動を規定または支配する少なくとも1つの素子特性を有する。例えば、第2トランジスタ3がMOSFETとして実装されているとき、考えられる素子特性は、ゲート抵抗、閾値電圧、ゲート-ソース容量、ゲート-ドレイン容量、ドレイン-ソース容量、チャネル幅、ゲート絶縁体の厚さ、あるいは、ソース領域、ボディ領域、またはドレイン領域のドーピング濃度である。これらの素子特性について、以下にさらに詳細に説明する。

#### 【0060】

一実施形態によれば、少なくとも1つの第2半導体素子3の少なくとも1つの素子特性は、他の複数の第2半導体素子3の対応する素子特性とは異なる。個々の第2半導体素子3の素子特性のバリエーションにより、半導体素子配置1全体のスイッチングの挙動は、特定の要求に適合され、または特定の要求を取り入れることができる。

40

#### 【0061】

一実施形態によれば、変えられる少なくとも1つの素子特性はゲート抵抗である。このように、他の複数の第2トランジスタ3のゲート抵抗とは異なるゲート抵抗、特に、他の複数の第2トランジスタ3のゲート抵抗より高いゲート抵抗を有する少なくとも1つの第2トランジスタ3がある。ゲート抵抗に関連して、また以下に説明される他の素子特性にも関連して、“異なる”とは有意に(著しく)異なることを意味し、それゆえ製造工程における通常の変動または揺らぎからくる差は含まれない。一実施形態によれば、1つの半導体素子の素子特性、例えばゲート抵抗は、別の半導体素子の対応する素子特性とは、2つの素子特性の比が少なくとも1.1、少なくとも2、少なくとも5、または少なくとも

50

10であるとき、異なると考えられる。

**【0062】**

MOSFETのゲート抵抗は該MOSFETのスイッチング速度を規定することが一般に知られている。スイッチング速度は、オン状態からオフ状態、またはその逆へ、MOSFETが以下に早く変化できるかの度合いである。MOSFETは、該MOSFETのゲート端子を介して充電または放電される内部ゲート容量（ゲート-ソース容量およびゲート-ドレイン容量）を含むことが一般に知られている。このゲート容量の充電状態は該MOSFETのスイッチング状態（オンまたはオフ）を決定する。MOSFETのゲート抵抗は、MOSFETの駆動電位が利用できる端子とMOSFETのゲート電極との間の電気抵抗である。図1の半導体素子配置1では、個々の第2トランジスタ3のゲート電極に関する駆動電位が利用できる複数の端子は、それぞれ、他の複数の第2トランジスタ3の第1負荷端子（ソース端子）32または第1トランジスタ2の第1負荷端子（ソース端子）21である。高いゲート抵抗があるとき、ゲート容量は、比較的ゆっくりと充電または放電されるだけであり、MOSFETはあるスイッチング状態（オンまたはオフ）から他のスイッチング状態（オフまたはオン）に比較的ゆっくりと切り替わる。このように、他の複数の第2トランジスタ3のゲート抵抗に比べて少なくとも1つの第2トランジスタ3のゲート抵抗を増加させることにより、上記少なくとも1つの第2トランジスタのスイッチング速度を、他の複数の第2トランジスタのスイッチング速度に比べて低下することができる。個々の第2トランジスタ3のスイッチング速度の減少は、異なる用途で有益である。

10

20

30

40

**【0063】**

例えば、半導体素子配置1が、フライバックコンバータのようなスイッチングコンバータにおけるスイッチとして使用されるとき、半導体素子配置1がオフに切り替わるときに電圧オーバーシュートが生じる。半導体素子配置1をオフに切り替える過程において、第1および第2負荷端子12・13の間の電圧は増加する。ここで、上記電圧が増加する割合（速度）は、1番目の第2トランジスタ3<sub>1</sub>で始まり、続いてオン状態からオフ状態に切り替わる個々の第2トランジスタ3のスイッチング速度に依存する。第1および第2負荷端子12・13の間の電圧が既に大きく増加しているとき、オフに切り替わるそれら複数の第2トランジスタ3のスイッチング速度を減少させることによって、電圧オーバーシュートを防止するまたは少なくとも減少させることができる。例えば、最大で520Vの電圧が第1および第2負荷端子12・13の間の間に印加されると仮定する。この最大電圧でオーバーシュートが生じる。この場合、第1および第2負荷端子12・13の間の電圧が約450Vに増加した後、またはさらに一般的に最大電圧の約80%または85%に増加した後でオフに切り替わるそれら複数の第2トランジスタ3のゲート抵抗が、（他の複数の第2トランジスタのゲート抵抗に比べて）増加されているように、半導体素子配置1を実施することができる。説明のため、半導体素子配置1は約620Vの電圧ブロッキング能力を有していると仮定する。この場合、半導体素子配置1は、1つの第1トランジスタ2およびn=30個の第2トランジスタ3を含んでもよい。ここで、半導体素子配置1のオフ状態において、第1トランジスタ2および各第2トランジスタ3が約20Vの負荷経路電圧を有するように、複数の第2トランジスタ3は使用される。この場合、第1および第2負荷端子12・13の間の電圧が450Vに増加したとき、第1トランジスタ2およびn=21個の第2トランジスタ3がオフに切り替わっている。このように、第2トランジスタ3<sub>n-9</sub>から3<sub>n</sub>のスイッチング速度が、前に説明した要件を満たすために、低減されるべきである。

**【0064】**

例えば、400VのDCリンク電圧を生成する力率補正（PFC）回路におけるブーストコンバータのようなブーストコンバータにおけるスイッチング素子として半導体素子配置1が使用されるとき、例えば、第1および第2負荷端子12・13の間の電圧が約350Vまたは最大電圧の約90%に上昇した時にオフに切り替わり始めるそれら複数の第2トランジスタ3のゲート抵抗が増加されているように、半導体素子配置1は実装される。

50

このように、これらのトランジスタのスイッチング速度は低くされる。

#### 【0065】

例えば、400VのDCリンク電圧を受け取るインバータの一部であるハーフブリッジ回路におけるスイッチとして半導体素子配置1が使用されるとき、例えば、第1および第2負荷端子<sub>12·13</sub>の間の電圧が175Vから225Vの間または最大電圧の45%から55%の間であるときにオフに切り替わるそれら複数の第2トランジスタ3は、増加されたゲート抵抗を有するように、半導体素子配置1は実装される。これは、ハーフブリッジの負荷経路電圧の最大傾斜が生じる電圧範囲であり、この電圧範囲でオフに切り替わるそれら第2トランジスタ3のスイッチング速度を遅くすることによって、負荷経路電圧の傾斜を減少させることができる。

10

#### 【0066】

他の複数の第2トランジスタ3とは異なるゲート抵抗を有する上記少なくとも1つの第2トランジスタ3のゲート抵抗は、多くの異なる方法で、調整、特に増加されることができる。ゲート抵抗または他の素子特性の調整に関するいくつかの実施形態は、以下に図を参照して説明される。これらの図では、直列に接続された2つの第2トランジスタ<sub>3i·3i-1</sub>が図示されている。第2トランジスタ<sub>3i</sub>(以下では上側トランジスタと呼ぶ)は、第2トランジスタ<sub>3i-1</sub>(以下では下側トランジスタと呼ぶ)の負荷経路電圧によって制御される。上側トランジスタ<sub>3i</sub>のゲート端子<sub>31i</sub>は、下側トランジスタ<sub>3i-1</sub>のソース端子<sub>32i-1</sub>に接続されている。上側トランジスタ<sub>3i</sub>の少なくとも1つの素子特性は、下側トランジスタ<sub>3i-1</sub>の対応する素子特性とは異なっている。上側および下側トランジスタ<sub>3i·3i-1</sub>は、上記直列回路の中の第2トランジスタ3の任意のペアとすることができる。下側トランジスタ<sub>3i-1</sub>が1番目の第2トランジスタ<sub>31</sub>であるとき、このトランジスタ<sub>31</sub>の第1負荷端子<sub>321</sub>は、別の第2トランジスタの第2負荷端子には接続されていないが、第1半導体素子2の第1負荷端子<sub>23</sub>に接続されている。

20

#### 【0067】

図4は、上側第2トランジスタ<sub>3i</sub>のゲート抵抗を調整する一実施形態を図示する。上側トランジスタ<sub>3i</sub>のゲート抵抗は、上側トランジスタ<sub>3i</sub>の内部ゲート電極(図3には図示せず)と下側トランジスタ<sub>3i-1</sub>の第1負荷端子(ソース端子)<sub>32i-1</sub>との間の電気抵抗である。このゲート抵抗は、図4の抵抗<sub>41</sub>によって下位略的に図示される。ゲート抵抗<sub>41</sub>は、多くの異なる方法で調整することができる。一実施形態によれば、第1負荷端子<sub>32i-1</sub>とゲート端子<sub>31i</sub>との間の接続配線の中で抵抗素子<sub>41</sub>が接続される。この接続配線は、例えば、アルミニウム配線または銅配線のような金属配線である。抵抗素子<sub>41</sub>は、例えば、接続配線より高い抵抗を有するポリシリコン抵抗素子として実装される。さらなる実施形態によれば、ゲート抵抗を増加させるために、ゲート端子<sub>31i</sub>および第2負荷端子<sub>32i-1</sub>である個々の端子と接続配線との接触抵抗は増加せられる。第2負荷端子<sub>32i-1</sub>は、下側トランジスタのソース領域(図4には図示せず)に電気的に接触している。下側トランジスタ<sub>3i-1</sub>のソース領域は、ドーピングされた半導体領域である。通常、MOSFETのソース領域のような、接続端子に接続されるドーピングされた半導体領域は、半導体領域が接触する、より高濃度にドーピングされた接觸領域を含む。接觸領域のドーピング濃度は、例えば $1E20\text{ cm}^{-3}$ 以上である。接觸抵抗を増加させるために、接觸領域のドーピング濃度は低減されうる、または、接觸領域は除外(省略)される。接觸領域が高いドーピング濃度であるとき、接觸端子および接觸領域の間にオーミックコンタクト(オーム接觸)が得られる。より低いドーピング濃度で、上記接觸はショットキー接觸となりうる。このように、一実施形態によれば、下側トランジスタ<sub>3i-1</sub>のソース端子<sub>32i-1</sub>およびソース領域との間の接觸抵抗は、ソース領域における接觸領域のドーピング濃度を低減することによって、低減される。

30

40

#### 【0068】

図4の上側第2トランジスタ<sub>3i</sub>のような1つの第2トランジスタ3のゲート抵抗が、図4の下側第2トランジスタ<sub>3i-1</sub>のような他の複数の第2トランジスタ3のゲート抵

50

抗に比べて上昇されると、上記少なくとも1つのトランジスタ $3_i$ のスイッチング速度は、トランジスタ $3_i$ がオンに切り替わるときもトランジスタ $3_i$ がオフに切り替わるときも遅くなる。

#### 【0069】

図5および図6に図示されるさらなる実施形態によれば、pnダイオードまたはショットキーダイオードのような整流素子42が追加的なゲート抵抗41に並列に接続される。“追加的なゲート抵抗”は、スイッチング速度を操作するために追加されたゲート抵抗の部分である。整流素子の極性に依存して、図5または図6の上側第2トランジスタ $3_i$ のスイッチング速度は、オンに切り替わる間またはオフに切り替わる間、減少する。上側第2トランジスタ $3_i$ がオフに切り替わるとき、図5Aに概略的に示される内部ゲート-ソース容量 $C_{GS}$ は、下側第2トランジスタ $3_{i-1}$ の負荷経路にかかる電圧 $V_{3_{i-1}}$ に充電される。下側第2トランジスタ $3_{i-1}$ がオンに切り替わると、ゲート-ソース容量 $C_{GS}$ は放電される。複数の第2トランジスタがn型ディプレッショントランジスタである本実施形態では、整流素子42の極性が、図5のように、整流素子42のカソードがゲート端子 $3_{1i}$ に接続され、アノードが下側トランジスタ $3_{i-1}$ のソース端子 $3_{2i-1}$ に接続されるようなとき、ゲート-ソース容量 $C_{GS}$ は、追加的なゲート抵抗41を介してのみ充電されうる。この場合、ゲートは負の電位に充電されるという事実のせいで、上側トランジスタ $3_i$ がオフに切り替わる間、ゲート $3_{1i}$ からソース $3_{2i-1}$ に正の電流が流れなければならない。オフに切り替わるときの上側トランジスタ $3_i$ のスイッチング速度は、ダイオードは逆バイアスになるので、抵抗によって低減される。一方、上側トランジスタ $3_i$ をオンに切り替えるため、下側トランジスタ $3_{i-1}$ の負荷経路電圧 $V_{i-1}$ が減少するとき、ゲート-ソース容量 $C_{GS}$ は、整流素子42を介して急速に放電されうる。上側トランジスタ $3_i$ がオンに切り替わる場合、ゲートは放電されなければならない、すなわち、オフ状態に比べて正の電位に充電されなければならない。正の電流がソース $3_{2i-1}$ から $3_{1i}$ に流れる。電流はダイオードを通して流れることができるので、スイッチングオンは高速である。図6に示すように、整流素子42の極性が逆であるとき、ゲート-ソース容量 $C_{GS}$ は、整流素子42を介して急速に充電されうるが、追加的なゲート抵抗を介してのみ放電されうる。この場合、上側第2トランジスタ $3_i$ のスイッチング速度は、トランジスタ $3_i$ がオンに切り替わるときのみ低減される。

#### 【0070】

複数の第2トランジスタのスイッチング速度に影響を与えるさらなる素子特性は、図5および図6において上側第2トランジスタ $3_i$ に関して概略的に図示されている、ゲート-ソース容量 $C_{GS}$ である。上述の説明を参照すると、ゲート-ソース容量 $C_{GS}$ は、上側トランジスタ $3_i$ の所望のスイッチング状態に依存して充電または放電される。

#### 【0071】

図7を参照すると、図7の上側第2トランジスタ $3_i$ のような少なくとも1つの第2トランジスタ3のゲート-ソース容量 $C_{GS}$ は、図7の下側第2トランジスタ $3_{i-1}$ のような他の複数の第2トランジスタのゲート-ソース容量 $C_{GS}$ より高い。それゆえ、上側第2トランジスタ $3_i$ のスイッチング速度は、低減されうる。上側第2トランジスタ $3_i$ のゲート-ソース容量 $C_{GS}$ は、上側トランジスタ $3_i$ の内部ゲート-ソース容量 $C_{GS}$ に並列に追加的な容量43を接続することにより、増加される。下側トランジスタ $3_{i-1}$ のゲート-ソース容量 $C_{GS}$ は内部ゲート-ソース容量 $C_{GS}$ のみを含むが、上側第2トランジスタ $3_i$ のゲート-ソース容量 $C_{GS}$ は、内部ゲート-ソース容量 $C_{GS}$ および追加的な容量43を含む。

#### 【0072】

図8および図9を参照すると、分圧素子を有する分圧器の出力を介して第2トランジスタ $3_i$ のゲート端子 $3_{1i}$ を駆動することによって、他の複数の第2トランジスタ3のスイッチング速度と比べて、例えば図8および図9の第2トランジスタ $3_i$ のような1つの第2トランジスタ3のスイッチング速度は、影響を与えられる。図8を参照すると、分圧器は、例えば、抵抗器として実装される第1および第2抵抗性分圧素子 $4_{41} \cdot 4_{42}$ を

10

20

30

40

50

有する抵抗性の分圧器とすることができる。図9を参照すると、分圧器は、容量 $45_1$ ・ $45_2$ として実装される第1および第2分圧素子を有する容量性の分圧器とすることもできる。分圧器は、例えば、下側トランジスタ $3_{i-1}$ の第1負荷端子 $32_{i-1}$ と第2トランジスタ $3_{i+1}$ の第2負荷端子 $33_{i+1}$ との間に接続され、中央(タップ)は、第2トランジスタ $3_i$ の第1負荷端子 $31_i$ に接続される。

#### 【0073】

個々の第2トランジスタ3のスイッチング速度に影響を与えるために変更されうるさらなる素子特性は、例えば、ゲート-ドレイン容量またはドレン-ソース容量である。これについて、以下に図10および図11を参照して説明する。図10は、再び2つの第1トランジスタ $3_i$ ・ $3_{i-1}$ (上側および下側トランジスタ)を有する直列回路を図示する。各第2トランジスタ3は、内部ゲート-ドレイン容量 $C_{GD}$ を有する。上側第2トランジスタ $3_i$ の内部ゲート-ドレイン容量 $C_{GD}$ は、図10に概略的に図示されている。第2トランジスタ3のスイッチング動作の間、ゲート-ソース容量 $C_{GS}$ (図6および7参照)が充電または放電されるだけでなく、ゲート-ドレイン容量 $C_{GD}$ もまた充電または放電される。ここで、第2トランジスタ3のゲート-ドレイン容量 $C_{GD}$ は、該トランジスタ3がオフに切り替わるときに充電され、該トランジスタがオンになるときにはほとんど放電される。このように、個々の第2トランジスタ3のスイッチング速度は、ゲート-ドレイン容量を変更することによって変化させることができる。全体のゲート-ドレイン容量が増加すると、個々の第2トランジスタ3はゆっくり切り替わる。図10を参照すると、このゲート-ドレイン容量は、内部ゲート-ドレイン容量 $C_{GD}$ に対して並列に追加的な容量 $45$ を接続することによって、増加させることができる。

#### 【0074】

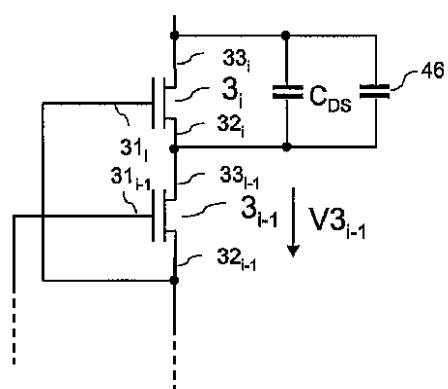

図11を参照すると、上側第2トランジスタ $3_i$ は、ドレン端子 $32_i$ とソース端子 $33_i$ との間にドレン-ソース容量 $C_{DS}$ を有する(図11には下側トランジスタ $3_{i-1}$ の対応するドレン-ソース容量は図示されていない)。上側第2トランジスタ $3_i$ がオフに切り替わると、負荷電圧が増加するように、ドレン-ソース容量 $C_{DS}$ は充電される。上側第2トランジスタ $3_i$ がオフに切り替わると、負荷電圧が減少するように、ドレン-ソース容量 $C_{DS}$ は放電される。上側第2トランジスタ $3_i$ のドレン-ソース容量 $C_{DS}$ はそのスイッチング速度に影響する。上側第2トランジスタ $3_i$ のスイッチング速度は、内部ドレン-ソース容量 $C_{DS}$ に並列に追加的な容量 $46$ を接続することにより減少させることができる。これは、全体のドレン-ソース容量を増加させることを意味する。

#### 【0075】

どのようにしてゲート-ソース容量 $C_{GS}$ 、ゲート-ドレイン容量 $C_{GD}$ 、またはドレン-ソース容量 $C_{DS}$ を増加させることができるのかを説明するために、追加的な容量 $43$ ・ $45$ ・ $46$ が図7、10、11にそれぞれ図示されている。しかしながら、これは単なる説明である。全体のゲート-ソース容量、ゲート-ドレイン容量、またはドレン-ソース容量は、必ずしも並列に接続された2つの容量を含まなくてもよい。その代わり、他の複数の第2トランジスタ3の対応する容量に比べてこれらの容量を増加させるために、複数の異なる手段を適用することができる。

#### 【0076】

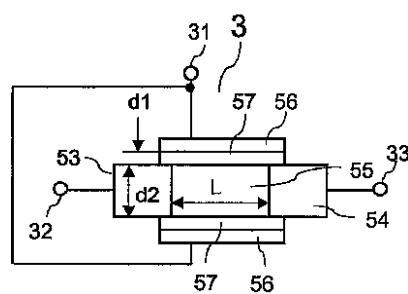

図12は、トランジスタのスイッチングの挙動を操作するために変更されうるさらなる素子特性を説明するため、ディプレッションMOSFETとして使用される第2トランジスタ3の考えられる実装を概略的に図示する。図12を参照すると、第2トランジスタ3は、ソース領域53、ドレン領域54、および、ソース領域53とドレン領域54との間のボディ領域55を含む。ディプレッションMOSFETでは、ソース領域53、ドレン領域54、およびボディ領域55は、同じドーピング型である。n型ディプレッションMOSFETでは、これらの半導体領域はn型にドーピングされている一方、p型ディプレッションMOSFETではこれらの半導体領域はp型にドーピングされている。ディプレッションMOSFETは、さらに、ボディ領域55に隣接し、ゲート絶縁体57に

10

20

30

40

50

よってボディ領域55から絶縁されたゲート電極56を含む。図12に図示される実施形態では、ゲート電極56は、ボディ領域55の向かい合った側面に隣接する。

#### 【0077】

ソース領域53は、ソース端子32（第1負荷端子）に接続され、ドレイン領域54はドレイン端子33（第2負荷端子）に接続され、かつ、ゲート電極56は、ゲート端子31（制御端子）に接続される。これらの端子は、図12において単に概略的に図示される。

#### 【0078】

図12のディプレッショナMOSFETの動作原理は以下のようである。ドレイン端子33およびソース端子32の間に電圧が印加され、ゲート電極56がバイアスされていないとき（これはゲート電極56の電位がソース端子32の電位と一致するときを意味する）、電流はドレイン領域54、ボディ領域55、およびソース領域53を通って、ドレイン端子33およびソース端子32の間を流れる。*n*型トランジスタではソース端子32の電位に対してゲート電極56が負にバイアスされているとき、*p*型トランジスタではソース端子32の電位に対してゲート電極56が正にバイアスされているとき、ゲート絶縁体57に隣接するボディ領域55の中にディプレッション領域が形成される。ディプレッション領域が、ボディ領域55においてソース領域53とドレイン領域54との間の伝導チャネルを完全にピンチオフすると、ディプレッションMOSFETはオフに切り替わる。トランジスタ3がピンチオフするゲート-ソース電圧が、トランジスタ3のピンチオフ電圧である。このピンチオフ電圧は、いくつかのパラメータに依存する。

10

20

30

#### 【0079】

ピンチオフ電圧は、ゲート絶縁体57の厚さd1に依存し、ゲート絶縁体57の厚さが増加すると、ピンチオフ電圧の大きさは増加する。ピンチオフ電圧は、また、ボディ領域55のドーピング濃度に依存し、ボディ領域55のドーピング濃度が増加すると、ピンチオフ電圧の大きさは増加する。

#### 【0080】

さらに、ピンチオフ電圧は、ゲート電極56の2つの向かい合う部分の間のボディ領域55の厚さd2に依存する。以下に図14および図15を参照して説明されるように、第2トランジスタ3がFINFETとして実装されているとき、ボディ領域55の厚さd2は、半導体フィンの厚さに相当する。ボディ領域55の厚さd2が増加すると、ピンチオフ電圧は増加する。

40

#### 【0081】

一実施形態によれば、少なくとも1つの第2トランジスタ3のピンチオフ電圧は、他の複数の第2トランジスタ3のピンチオフ電圧とは異なる。上述の説明を参照すると、ゲート絶縁体57の厚さd1、ボディ領域55の厚さd2、または、ボディ領域55のドーピング濃度を変更することにより、ピンチオフ電圧を変化させることができる。

#### 【0082】

スイッチングトランジスタ3のスイッチングの挙動に影響を与えるために変更されうるさらなるパラメータは、ボディ領域55の長さLおよびボディ領域55の幅Wである。“ボディ領域55の長さL”は、ソース領域53とドレイン領域54との間の距離に対応する。“ボディ領域55の幅W”は、図12に図示された平面に垂直な方向におけるボディ領域の寸法である。幅Wを変更することによって、および/または、長さLを変更することによって、ゲート-ソース容量およびゲート-ドレイン容量を変化させることができる。ここで、これらのパラメータの少なくとも1つが増加すると、これらの容量は増加する。一実施形態によれば、1つの第2トランジスタ3の長さLおよび幅Wのうちの少なくとも1つは、別の第2トランジスタ3の対応するパラメータとは異なる。

50

#### 【0083】

図12のトランジスタ3は、さらにバルク端子を含んでもよい。バルク端子は、ボディ領域55に隣接している半導体領域の端子である。この半導体領域は、半導体基板であってもよい。トランジスタが（図14および図15で図示されるような）FINFETとし

50

て実装されているとき、バルク端子は、トランジスタが実装される基板に接触する端子であってもよく、または、引き出されるように上記ボディ領域55から接続されてもよい。

#### 【0084】

一実施形態によれば、バイアス電圧がバルク端子に印加されてもよい。バルク端子に印加されたバイアス電圧は、ピンチオフ電圧に影響し、バイアス電圧が増加すると、ピンチオフ電圧は減少する。一実施形態によれば、少なくとも1つの第2トランジスタ3のバルク端子バイアス電圧は、他の複数の第2トランジスタ3のバルク端子バイアス電圧とは異なる。

#### 【0085】

上述の説明を参照すると、各第2トランジスタ3のスイッチングの挙動は、上で説明した素子特性の1つを調整することにより、変化させるまたは調整することができる。一実施形態によれば、1番目の第2トランジスタ3<sub>1</sub>およびn番目の第2トランジスタ3<sub>n</sub>は、他の複数の第2トランジスタ3の対応する素子特性とは異なる少なくとも1つの素子特性を有するように実装されてもよい。

10

#### 【0086】

図13は、半導体素子配置1のさらなる実施形態を図示する。図12の半導体素子配置1は、図1の半導体素子配置1に基づいており、さらに、2つの第2トランジスタ（図3の実施形態では3<sub>2</sub>・3<sub>3</sub>）の2つの負荷経路の間のタップに接続される第3負荷端子13'を含む。図2に関して行った説明を参照すると、半導体素子配置1は、半導体素子配置1に直列に接続された負荷のスイッチングのための電子スイッチとして使用することができる。切り替えられる電圧の振幅に依存して、第2負荷端子13または第3負荷端子13'が、半導体素子配置1を電源電位の端子または負荷のそれぞれに接続するために使用されうる。例えば、電源電圧（供給電圧）または負荷電圧が低い電圧であるとき、第3負荷端子13'が使用され、一方、電源電圧が高電圧であるとき第2負荷端子13が使用される。第1の場合では、第2負荷端子13と第3回路ノードが接続されたタップとの間の複数の第2トランジスタ3は、バイパスされる。どれだけ多くの第2トランジスタ3がバイパスされるかは、第3負荷端子13'が複数の第2トランジスタ3を有する配置30のどこに接続されるかに依存している。いくつかの第2トランジスタ3をバイパスすることで、半導体素子配置1の電圧ブロッキング能力は低下する。しかしながら、第1負荷端子12および第3負荷端子13'の間の有効な上記素子のオン抵抗は、第1負荷端子12および第2負荷端子13の間の上記素子のオン抵抗よりも低い。

20

30

#### 【0087】

さらなる実施形態（図13に破線で図示される）によれば、第3負荷端子13'は、第2負荷端子13に恒久的に接続される。これは、第2および第3負荷端子13・13'の代わりに第2負荷端子13のみを有するのと等価である。この実施形態では、スイッチ35が第2負荷端子13（第3負荷端子13'）の間に接続される。このスイッチ35は、低オーム機械的スイッチ（リレー）または半導体スイッチであってもよく、第2負荷端子13に低い電圧が印加されたとき、第2負荷端子13と上記タップとの間で複数の第2トランジスタ3をバイパスする役割をする。

40

#### 【0088】

スイッチ35の電圧ブロッキング能力は、バイパスされた複数の第2トランジスタ3（3<sub>3</sub>・3<sub>n</sub>）の直列回路の電圧ブロッキング能力に対応するが、この直列回路より低いオン抵抗を有してもよい。しかしながら、スイッチ35は、通常は、非常に低い頻度でオンおよびオフに切り替えられるので、スイッチ35は、スイッチング損失、スイッチング速度等について最適化される必要はない。

#### 【0089】

さらなる実施形態によれば、スイッチ35の代わりにヒューズが実装されてもよい。この実施形態では、一度高電圧（ヒューズがとび、第2トランジスタがバイパスされないとき）で動作すると、そのように構成され、さもなくば、低電圧（ヒューズがアクティブでいくつかの第2トランジスタがバイパスされるとき）で動作するよう構成される。

50

## 【0090】

上で説明した図において回路記号で表される第1半導体素子2および第2半導体素子(第2トランジスタ)3は、多くの異なる方法によって実装することができる。第2トランジスタ3の実装に関する説明のためのいくつかの実施形態について、以下に図を参照して説明する。

## 【0091】

図14Aは、1つの第2トランジスタ3の斜視図を示す。図14Bは、この第2トランジスタ3の垂直断面図を示し、図14Cは、この第2トランジスタ3の水平断面図を示す。図14A、14B、14Cは、第2トランジスタ3が実装されている半導体本体100の部分のみを示す。第1半導体素子2のアクティプ領域および隣の第2半導体素子3のアクティプ領域は図示されていない。図14Aから14Cによる第2トランジスタ3は、MOSFET、特にFINFETとして実装されており、フィン状の半導体部分52(以下では“半導体フィン”とも呼ぶ)の中に配置されたソース領域53、ドレイン領域54、およびボディ領域55を含む。半導体フィン52は、基板51上に配置されている。第1の水平方向において、ソースおよびドレイン領域53・54は、第1側壁52<sub>2</sub>から第2側壁52<sub>3</sub>に延びている。第1の水平方向に垂直な第2の水平方向において、ソースおよびドレイン領域53・54は、互いに離れており、ボディ領域55によって分離されている。ゲート電極56(図14Aでは破線で図示されている)は、ゲート絶縁体57によって半導体フィン52から絶縁されており、半導体フィン52の上面52<sub>1</sub>および側壁52<sub>2</sub>・52<sub>3</sub>上でボディ領域55に隣接している。

10

20

## 【0092】

図15Aおよび図15Cは、FINFETとして実装される1つの第2トランジスタ3のさらなる実施形態を図示する。図15Aは斜視図を示し、図15Bは垂直断面E-Eの垂直断面図を示し、図15Cは水平断面D-Dの水平断面図を示す。垂直断面E-Eは、半導体フィン52の上面52<sub>1</sub>に垂直に延び、かつ半導体フィン52の長手方向に延びる。水平断面D-Dは、半導体フィンの上面52<sub>1</sub>に平行に延びる。半導体フィン52の“長手方向”は、第2水平方向に対応し、ソースおよびドレイン領域53・54が互いから離れている方向である。

30

## 【0093】

図15Aから図15Cに係るトランジスタ3は、U形状サラウンドゲートFINFETとして実施されている。このトランジスタでは、ソース領域53およびドレイン領域54は、第1水平方向において、半導体フィン52の第1側壁52<sub>2</sub>から第2側壁52<sub>3</sub>に延びている。第1の水平方向に垂直な第2の水平方向(半導体フィン52の長手方向)において、ソースおよびドレイン領域53・54は、互いに離れている。図15Aおよび図15Bを参照すると、半導体フィン52の上面52<sub>1</sub>からボディ領域55の中に延び、かつ、第1水平方向において側壁52<sub>2</sub>から側壁52<sub>3</sub>に延びる溝によって、ソース領域53およびドレイン領域54は分離されている。ボディ領域55は、半導体フィン52において、ソース領域53、ドレイン領域54および溝の下に配置されている。ゲート電極56は、半導体フィン52の側壁52<sub>2</sub>・52<sub>3</sub>に沿って溝の中でボディ領域55に隣接し、ゲート絶縁体57によってボディ領域55、ソース領域53およびドレイン領域54から絶縁されている。ゲート電極56がボディ領域55に隣接して配置されていない領域である溝の上部領域では、ゲート電極56は、絶縁体または誘電体58によって覆われうる。

40

## 【0094】

図14A～14Cおよび図15A～15Cの第2トランジスタ3は、例えば、n型またはp型ディプレッショントランジスタのような、ディプレッショントランジスタとして実装される。この場合、ソース領域53、ドレイン領域54およびボディ領域55は、同じドーピング型である。ボディ領域55は、通常、ソース領域53およびドレイン領域54よりも低いドーピング濃度である。ボディ領域55のドーピング濃度は、例えば、約2E18cm<sup>-3</sup>である。ソース領域53およびドレイン領域54の間のボディ領域55における伝導チャネルを完全に遮断できるようにするために、半導体フィン52の側壁52<sub>2</sub>

50

・<sub>523</sub>に沿ったゲート電極<sub>56</sub>は、第2水平方向(長手方向)において半導体フィン<sub>52</sub>に沿って十分に延びている。縦方向(垂直方向)において、側壁<sub>522</sub>・<sub>523</sub>に沿ったゲート電極<sub>56</sub>は、ソース領域<sub>53</sub>およびドレイン領域<sub>54</sub>から少なくとも溝より下まで延びている。

#### 【0095】

図14Aおよび図15Aを参照すると、ソース領域<sub>53</sub>は、第1負荷端子(ソース端子)<sub>32</sub>に接続され、ドレイン領域<sub>54</sub>は、第2負荷端子(ドレイン端子)<sub>33</sub>に接続され、ゲート電極<sub>56</sub>は、制御端子(ゲート端子)<sub>31</sub>に接続される。これらの端子は、図14Aおよび図15Aでは概略的にのみ示される。

#### 【0096】

ソース領域<sub>53</sub>およびドレイン領域<sub>54</sub>の間の伝導チャネルを完全に遮断し、第2トランジスタ<sub>3</sub>をオフに切り替えるために、ゲート電極<sub>56</sub>によって制御されるディプレッション領域が側壁<sub>522</sub>から側壁<sub>523</sub>まで延びることができるように、第1水平方向における半導体フィンの寸法である半導体フィン<sub>52</sub>の厚さ、および、ボディ領域<sub>55</sub>のドーピング濃度は、調整される。*n*型ディプレッションMOSFETでは、ゲート電極<sub>56</sub>およびソース領域<sub>53</sub>の間、またはゲート端子<sub>31</sub>およびソース端子<sub>32</sub>の間のそれぞれに、負の制御(駆動)電圧が印加されたとき、ディプレッション領域は、ボディ領域<sub>55</sub>において拡大する。図1を参照した説明を参照すると、この駆動電圧は、第1半導体素子<sub>2</sub>の負荷電圧に依存する、または、別の1つの第2トランジスタ<sub>3</sub>の負荷電圧に依存する。ディプレッション領域が側壁<sub>522</sub>・<sub>523</sub>に垂直にどれだけ拡大しているかは、また、ゲート端子<sub>31</sub>およびソース端子<sub>32</sub>の間に印加される制御電圧の大きさに依存する。それゆえ、半導体フィン<sub>52</sub>の厚さおよびボディ領域<sub>55</sub>のドーピング濃度は、また、半導体素子配置1の動作の間に生じうる制御電圧の大きさに依存して設計される。チャネル(ボディ領域)<sub>55</sub>がU形状であり、かつ、ゲート電極<sub>56</sub>もまた半導体フィン<sub>52</sub>の側壁<sub>522</sub>・<sub>523</sub>および上面<sub>521</sub>に接して配置される、U形状サラウンドゲートFINFETとしての図14A～14Cおよび図15A～15Cに示されるFINFETの実装は、単なる一例である。これらのFINFETは、半導体フィン<sub>52</sub>の上面<sub>521</sub>に接さず、側壁<sub>522</sub>・<sub>523</sub>に接して配置される2つのゲート電極部分を用いるゲート電極<sub>56</sub>を有するように変更(図示せず)されることもできる。このタイプのFINFETは、ダブルゲートFINFETと呼ばれる。上述および後述の各FINFETは、U形状サラウンドゲートFINFETまたはダブルゲートFINFETとして実施することができる。1つの集積回路において、異なるタイプのMOSFETまたはFINFETとして個々の第2トランジスタ<sub>3</sub>を実装することもできる。

#### 【0097】

各第2トランジスタ<sub>3</sub>および第1半導体素子<sub>2</sub>は、FINFETとして実装することができる。これらの個々のFINFETは、半導体配置1を形成する異なる方法で実装される。

#### 【0098】

図16は、第1半導体素子<sub>2</sub>および*n*個の第2トランジスタ<sub>3</sub>のアクティブ領域(ソース、ドレイン、およびボディ領域)が配置される半導体フィン<sub>52</sub>の垂直断面図を示す。この実施形態では、第1半導体素子<sub>2</sub>および複数の第2トランジスタ<sub>3</sub>は、U形状サラウンドゲートFINFETまたはダブルゲートFINFETとして実装されている。図16では、類似の参照符号が、図14A～14Cおよび図15A～15Cと類似の特徴を示すために使用されている。図16では、異なる第2トランジスタ<sub>31</sub>～<sub>3n</sub>の類似の特徴の参照符号は、異なる添字(1、2、3、*n*)を持つ。

#### 【0099】

図16を参照すると、隣接する複数の第2トランジスタ<sub>3</sub>の複数のアクティブ領域は、半導体フィン<sub>52</sub>の縦方向に延びる複数の絶縁層<sub>59</sub>によって互いに絶縁されている。これらの絶縁層<sub>59</sub>は、基板<sub>51</sub>まで、または基板<sub>51</sub>の中にまで延びていてもよい。さらに、絶縁層<sub>59</sub>は、半導体フィン<sub>52</sub>の側壁から側壁まで延びている。しかしながら、こ

10

20

30

40

50

れは図 16 では見えない。第 1 半導体素子 2 の複数のアクティブ領域は、半導体フィン 5 2 の縦方向（垂直方向）に延びるさらなる絶縁層 6 6 によって、1 番目の第 2 トランジスタ 3<sub>1</sub> のアクティブ領域から絶縁されている。第 1 半導体素子 2 では、ソース領域 6 1 およびドレイン領域 6 2 がボディ領域 6 3 によって分離されている。溝の中（および、半導体フィンの側壁に点線で示される位置）に配置されたゲート電極 6 4 は、ソース領域 6 1 からボディ領域 6 3 に沿ってドレイン領域 6 2 まで延びる。ソース領域 6 1 は、半導体配置 1 の第 1 負荷端子 1 2 を形成する第 1 負荷端子 2 2 に接続されている。ドレイン領域 6 2 は、第 2 負荷端子 2 3 に接続されている。ゲート電極 6 4 は、半導体配置 1 の制御端子 1 1 を形成する制御端子 2 1 に接続されている。ボディ領域 6 3 もまた、第 1 負荷端子 2 2 に接続されている。

10

## 【0100】

第 1 半導体素子 2 は、例えば、エンハンスマント M O S F E T として実装される。この場合、ボディ領域 6 3 は、ソース領域 6 1 およびドレイン領域 6 2 に対して相補的にドーピングされている。n 型 M O S F E T では、ソース領域 6 1 およびドレイン領域 6 2 は n 型にドーピングされている一方、ボディ領域 6 3 は、p 型にドーピングされている。p 型 M O S F E T では、ソース領域 6 1 およびドレイン領域 6 2 は p 型にドーピングされている一方、ボディ領域 6 3 は n 型にドーピングされている。

## 【0101】

一実施形態によれば、基板 5 1 は、複数の第 2 トランジスタ 3 の複数のアクティブ領域および第 1 半導体素子 2 のソース領域 6 1 およびドレイン領域 6 2 に対して相補的にドーピングされている。この場合、個々の第 2 トランジスタ 3 の間に接合絶縁がある。さらなる実施形態（破線で示す）によれば、基板 5 1 は、S O I (silicon-on-insulator) 基板であり、半導体基板 5 1<sub>1</sub> および半導体基板 5 1<sub>1</sub> 上の絶縁層 5 1<sub>2</sub> を含む。半導体フィン 5 2 は、絶縁層 5 1<sub>2</sub> 上に配置される。この実施形態では、基板 5 1 において、個々の第 2 トランジスタ 3 の間に絶縁層が存在する。

20

## 【0102】

図 17 に図示されるさらに別の実施形態によれば、基板 5 1 は、複数の第 2 トランジスタ 3 の複数のアクティブ領域と同じ型、かつ、第 1 半導体素子 2 のソース領域 6 1 およびドレイン領域 6 2 と同じ型にドーピングされている。この実施形態では、第 1 半導体素子 2 がオン状態であるときに、ソース領域 6 1 と基板 5 1 との間にボディ領域 6 3 における伝導経路ができるように、第 1 半導体素子 2 のゲート電極 6 4 が基板 5 1 に向かって延びている。さらに基板 5 1 は、基板 5 1 と同じ型にドーピングされた接触領域 6 7 を通して、半導体配置 1 の第 2 負荷端子 1 3 に接続されている。接触領域 6 7 は、基板 5 1 より高くドーピングされており、半導体フィン 5 2 の第 1 面 5 2<sub>1</sub> から基板 5 1 まで延びている。接触領域 6 7 は、n 番目の第 2 トランジスタ 3 のドレイン領域 5 4<sub>n</sub> に隣接してもよい。接触領域 6 7 は、任意である。第 2 負荷端子 1 3 と基板 5 1 との間の接続は、第 2 トランジスタ 3<sub>n</sub> のドレイン領域 5 4<sub>n</sub> およびボディ領域 5 5<sub>n</sub> を通して設けられてもよい。

30

## 【0103】

図 17 の半導体配置では、基板 5 1 は、複数の第 2 トランジスタ 3 を通る電流経路に並列な電流経路、または、A D Z に並列な電流経路を形成する。基板 5 1 は、従来のパワートランジスタにおけるドリフト領域と類似している。この実施形態では、個々の第 2 トランジスタ 3 の複数のボディ領域 5 5 は、ドリフト領域 5 1 と連結している。

40

## 【0104】

さらなる実施形態（図 17 に破線で示される）によれば、基板 5 1 は、基板 5 1 の残りの部分および第 2 トランジスタ 3 のボディ領域 5 5 とは相補的にドーピングされている半導体層 5 1<sub>3</sub> を含む。この層 5 1<sub>3</sub> は、複数の第 2 トランジスタ 3 の複数のボディ領域 5 5 と、ドリフト領域として作用する基板 5 1 の部分との間に配置され、基板 5 1 における個々の第 2 トランジスタ 3 の間の接合絶縁を提供する。

## 【0105】

複数の第 2 トランジスタ 3 と直列に接続されたダイオード 2 を有する図 3 の半導体配置

50

1は、第1半導体素子2の制御端子を第1負荷端子22に接続するか、制御端子21をフロートにするかのいずれかによって、図14および図15に示す配置から容易に得ることができる。この場合、ボディ領域63およびドレイン領域65の間のpn接合によって形成されるダイオードである、MOSFETのボディダイオードのみが、第2半導体素子3の第1および第2負荷端子22・23の間でアクティブになる。

#### 【0106】

第1半導体素子2および複数の第2トランジスタ3（以下では素子と呼ぶ）のそれぞれは、並列に接続される複数の同じセル（トランジスタセル）を含んでもよい。これらのセルのそれぞれは、図14および図15に示される、第1半導体素子2または第2トランジスタ3のそれぞれのように実装することができる。1つの素子に並列に接続される複数のセルを設けることで、流れる電流の容量を増加させ、個々の素子のオン抵抗を低減することを助けることができる。

10

#### 【0107】

図18は、第1半導体素子2および複数の第2トランジスタ3を含む第1実施形態による半導体配置の上面図を示す。これらの素子のそれぞれは、並列に接続された複数（そのうち3つが図示されている）のセルを有する。1つの素子の個々のセルは、異なる半導体フィン52<sub>I</sub>・52<sub>II</sub>・52<sub>III</sub>に実装されている。これらのセルのそれぞれは、図18では追加的に“S”とラベルされたソース領域61・53と、図18では追加的に“D”とラベルされたドレイン領域62・54とを有する。1つの素子の複数のセルは、該1つの素子の複数のソース領域を一緒に接続し、該1つの素子の複数のドレイン領域と一緒に接続することにより、並列に接続される。異なる素子の複数の負荷端子の間の接続と同様に、これらの接続は、図18では太線で概略的に図示される。制御端子（ゲート端子）と異なる素子の負荷端子との間の接続は、図18では図示されていない。複数のセルおよび異なる素子の間の接続は、半導体本体の上に配置され、個々のアクティブ領域（ソース領域およびドレイン領域）を接続する従来の配線配置を用いて実施することができる。この配線配置は一般に知られているので、これについてのさらなる説明は必要ない。1つの素子2・3<sub>1</sub>・3<sub>2</sub>・3<sub>3</sub>・3<sub>n</sub>の個々のセルは、個々の半導体フィンのU形状溝の中および個々のフィンの間の溝の中に配置された共通ゲート電極64・56<sub>1</sub>・56<sub>2</sub>・56<sub>3</sub>・56<sub>n</sub>を有する。これらの“複数のフィンの間の溝”は、フィンに沿った長手方向の溝である。全てのゲート64・56<sub>1</sub>・56<sub>2</sub>・56<sub>3</sub>・56<sub>n</sub>は、絶縁体66・59によって互いに電気的に絶縁されている。

20

#### 【0108】

図19は、複数のトランジスタセルを有する1つの第2トランジスタ3を実装するさらなる実施形態を図示する。この実施形態では、第2トランジスタ3の複数のトランジスタセルは、2つの半導体フィン52において実現される。半導体フィン52の長手方向において、ソース領域53およびドレイン領域54は、ゲート電極56に適合した1つの（U形状の）溝によって分割されたソース領域53および隣接するドレイン領域54が交互に配置される。複数のソース領域53は、第1負荷端子22に接続されており、複数のドレイン領域54は、第2負荷端子23に接続されており、それゆえ個々のトランジスタセルは並列に接続される。ゲート電極56は、個々のトランジスタセルについて共通であり、長手方向において半導体フィン52の側壁に沿って延びる。各ソース領域53および各ドレイン領域54（半導体フィン52の長手の端に配置されるソース領域およびドレイン領域を除き）は、2つの隣接するトランジスタセルで共通である。

30

40

#### 【0109】

図19を参照して説明した1つの半導体フィンの中にいくつかのトランジスタセルを設けるコンセプトは、もちろん、第1半導体素子2の実装にも応用することができる。

#### 【0110】

図20A～20Cを参照すると、1つの第2トランジスタ3は、複数の半導体フィン52<sub>I</sub><sub>V</sub>、52<sub>V</sub>・52<sub>V</sub><sub>I</sub>・52<sub>V</sub><sub>II</sub>を含んでもよく、各半導体フィン52<sub>I</sub><sub>V</sub>・52<sub>V</sub><sub>I</sub>は、複数のトランジスタセル（これらのセルの1つは図20Aにおいて破線および

50

点線の枠で強調されている)を含む。図20Aは、1つの第2トランジスタ3の上面図を示し、図20Bは、異なるフィンの複数のソース領域53を通って切断する断面F-Fにおける垂直断面図を示し、図20Cは、異なるフィンのゲート電極56を有する複数の溝を通って切断する断面G-Gにおける垂直断面図を示す。図20Aを参照すると、個々のトランジスタセルが並列に接続されるように、個々のトランジスタセルのソース領域53は、第1負荷端子22に接続されており、個々のトランジスタセルのドレイン領域54は、第2負荷端子23に接続されている。これらの接続は図20では概略的にのみ示す。

#### 【0111】

図20A～図20Cを参照して説明した、各半導体フィンが複数のトランジスタセルを含むように複数の半導体フィンを設けるコンセプトは、もちろん、第1半導体素子2の実装にも応用することができる。

10

#### 【0112】

図20Aでは20個のトランジスタセル(すなわち、4個の半導体フィン $52_{\text{I}\text{V}} - 52_{\text{V}\text{I}}$ のそれぞれに5個のセルがある)のみが図示されているが、1つの第2トランジスタ3または第1半導体素子2は、並列に接続された、数千個以下のトランジスタセル、または数千万個以下のトランジスタセル、あるいは、数億個以下のトランジスタセルを含んでもよい。個々のトランジスタセルは、並列に接続されたトランジスタセルのマトリクスを形成する。マトリクス状に配列した複数のトランジスタセルを有する素子(第1半導体素子2または第2トランジスタ3)を、以下では、マトリクス素子と呼ぶ。

20

#### 【0113】

図21は、マトリクス素子として実装される複数の第2トランジスタ3が、どのようにして直列に接続されるのかを図示している。説明のために、図21には、2つの第2トランジスタ $3_{\text{i}} \cdot 3_{\text{i}+1}$ のみを示す。直列のこれら2つのトランジスタの接続のために、第2トランジスタ $3_{\text{i}+1}$ の複数のソース領域53は、トランジスタ $3_{\text{i}}$ の複数のドレイン領域54に接続されている。第2トランジスタ $3_{\text{i}}$ の複数のソース領域53は、第2トランジスタ $3_{\text{i}-1}$ (図示せず)の複数のドレイン領域54に接続されており、第2トランジスタ $3_{\text{i}+1}$ の複数のドレイン領域54は、トランジスタ $3_{\text{i}+2}$ (図示せず)の複数のソース領域53に接続されている。

#### 【0114】

以前の説明を参照すると、第1トランジスタ2および複数の第2トランジスタ3を有する直列回路における各トランジスタは、複数のトランジスタセルで実施することができる。一実施形態によれば、それぞれが第1トランジスタおよび複数の第2トランジスタを含むいくつかの直列回路が並列に接続されるように、半導体素子配置は分割される。このように分割された半導体配置は、図22に概略的に図示される。

30

#### 【0115】

図22では、参照符号 $1_1 \cdot 1_2 \cdot 1_p$ は、並列に接続された個々の直列回路を示す。個々の直列回路 $1_1 \cdot 1_2 \cdot 1_p$ の複数の第1トランジスタは、全体の配置の制御端子 $1_1$ (主制御端子)に接続された別個のゲート端子 $1_{11} \cdot 1_{12} \cdot 1_{1p}$ を有する。ゲート抵抗 $R_1 \cdot R_2 \cdot R_p$ は、複数のゲート端子 $1_{11} \cdot 1_{12} \cdot 1_{1p}$ と主制御端子 $1_1$ との間に接続されている。これらのゲート抵抗 $R_1 \cdot R_2 \cdot R_p$ を通して、個々の直列回路の第1トランジスタのスイッチングの開始が調整できる。ここで、1つのトランジスタのスイッチングの開始は、対応する抵抗が増加すると遅れ、逆もまた同様である。一実施形態によれば、個々の直列回路を繋いでオン状態またはオフ状態に切り替えるために、これらのゲート抵抗は異なる。これは、全体の $d_i / d_t$ を低減する、それゆえEMIを低減することに役に立つ。任意で、複数の容量 $C_1 \cdot C_2 \cdot C_p$ が複数のゲート端子 $1_{11} \cdot 1_{12} \cdot 1_{1p}$ と共にソース $1_2$ との間に接続される。これらの容量は、個々の直列回路の中の第1トランジスタのゲート-ソース容量(図示せず)に並列に接続される。これら追加的な容量 $C_1 \cdot C_2 \cdot C_p$ を通して、各直列回路 $1_1 \cdot 1_2 \cdot 1_p$ のスイッチングの開始が調整できる。ここでスイッチングの開始は、対応する容量が増加すると遅れる。一実施形態によれば、個々の容量 $C_1 \cdot C_2 \cdot C_p$ は、互いに異なる。各場合において、

40

50

1つの抵抗  $R_{1 \cdot R_2 \cdot R_p}$  および1つの容量  $C_{1 \cdot C_2 \cdot C_p}$  はRC素子を形成し、複数のゲート端子  $11_1 \cdot 11_2 \cdot 11_p$  が1つのRC素子を介して主制御端子(駆動端子)  $11$  と連結される。複数の抵抗  $R_{1 \cdot R_2 \cdot R_p}$  および複数の容量は、これらのRC素子のうちの少なくとも2つが異なる時定数を有するように設計される。

**【0116】**

さらなる実施形態によれば、複数の抵抗  $R_{1 \cdot R_2 \cdot R_p}$  は省略され、スイッチング速度は、複数の容量  $C_{1 \cdot C_2 \cdot C_p}$  のバリエーションによってのみ変えられる。

**【図面の簡単な説明】**

**【0117】**

【図1】トランジスタとして実装される第1半導体素子と、互いに直列に接続され、かつ第1半導体素子に直列に接続された複数の第2半導体素子とを有する半導体配置を図示する。

10

【図2】負荷をスイッチングする電気スイッチとしての図1の半導体配置の応用を図示する。

【図3】ダイオードとして実装される第1半導体素子と、互いに直列に接続され、かつ第1半導体素子に直列に接続された複数の第2半導体素子とを有する半導体配置を図示する。

。

【図4】第1実施形態によるゲート抵抗が異なる2つの第2トランジスタを有する直列回路を図示する。

【図5】第2実施形態によるゲート抵抗が異なる2つの第2トランジスタを有する直列回路を図示する。

20

【図6】第3実施形態によるゲート抵抗が異なる2つの第2トランジスタを有する直列回路を図示する。

【図7】ゲート-ソース容量が異なる2つの第2トランジスタを有する直列回路を図示する。

【図8】数個の第2トランジスタと、抵抗性分圧器を通して駆動される1つの第2トランジスタとを有する直列回路を図示する。

【図9】数個の第2トランジスタと、容量性分圧器を通して駆動される1つの第2トランジスタとを有する直列回路を図示する。

【図10】ゲート-ドレイン容量が異なる2つの第2トランジスタを有する直列回路を図示する。

30

【図11】ドレイン-ソース容量が異なる2つの第2トランジスタを有する直列回路を図示する。

【図12】空乏型MOSFETとしての1つの第2トランジスタの実装の概略を図示する。

。

**【図13】**図1の回路配置の変形例を図示する。

【図14】FINFETとして実装される1つの第2半導体素子の第1実施形態を図示する。

【図15】FINFETとして実装される1つの第2半導体素子の第2実施形態を図示する。

40

【図16】第1半導体素子と複数の第2半導体素子が1つの半導体フィンで実装される第1実施形態による半導体本体の垂直断面図を示す。

【図17】第1半導体素子と複数の第2半導体素子が1つの半導体フィンで実装される第2実施形態による半導体本体の垂直断面図を示す。

【図18】第1半導体素子と、それぞれが数個のFINFETセルを含む複数の第2半導体素子とが実装される第3実施形態による半導体本体の平面図を示す。

【図19】並列に接続される数個のFINFETセルを含む1つの第2半導体素子の垂直断面図を示す。

【図20】並列に接続される数個のFINFETセルを含む1つの第2半導体素子のさらなる実施形態を図示する。

50

【図21】図20に図示されたタイプの、直列に接続された2つの第2半導体素子を図示する。

【図22】上記半導体配置のさらなる実施形態を図示する。

【図1】

FIG 1

【図2】

FIG 2

【図3】

【図4】

FIG 3

【図5】

【図6】

【図 7】

FIG 7

【図 8】

FIG 8

【図 9】

FIG 9

【図 10】

FIG 10

【図 1 1】

FIG 11

【図 1 2】

FIG 12

【図 1 3】

FIG 13

【図 1 4 A】

FIG 14A

【図 14 B】

FIG 14B

【図 14 C】

FIG 14C

【図 15 A】

FIG 15A

【図 15 B】

FIG 15B

【 図 1 5 C 】

**FIG 15C**

【 図 1 6 】

FIG 16

【 図 17 】

〔図18〕

**FIG 18**       $2$        $3_1$        $3_2$        $3_3$        $3_n$

【 図 1 9 】

FIG 19

【図20A】

FIG 20A

【図 20B】

FIG 20B

【図 20C】

FIG 20C

【図 21】

FIG 21

【図 22】

FIG 22

## 【手続補正書】

【提出日】平成26年9月24日(2014.9.24)

## 【手続補正1】

【補正対象書類名】特許請求の範囲

【補正対象項目名】全文

【補正方法】変更

## 【補正の内容】

【特許請求の範囲】

## 【請求項1】

負荷経路を有する第1半導体素子(2)と、

それぞれが第1負荷端子および第2負荷端子( $3_{2,1}$  -  $3_{2,n}$ 、 $3_{3,1}$  -  $3_{3,n}$ )の間の負荷経路と制御端子( $3_{1,1}$  -  $3_{1,n}$ )とを有する、複数の第2半導体素子( $3_1$  -  $3_n$ )とを備え、

上記複数の第2半導体素子( $3_1$  -  $3_n$ )の複数の負荷経路は、直列に接続され、かつ、上記第1半導体素子(2)の上記負荷経路に直列に接続されており、

各第2半導体素子( $3_1$  -  $3_n$ )の制御端子( $3_{1,1}$  -  $3_{1,n}$ )は、1つの他の上記第2半導体素子( $3_1$  -  $3_n$ )の上記第1負荷端子および上記第2負荷端子のうちの1つ、または、上記第1半導体素子(2)の1つの負荷端子に接続されており、

各第2半導体素子( $3_1$  -  $3_n$ )は、少なくとも1つの素子特性を有し、

少なくとも1つの上記第2半導体素子( $3_1$  -  $3_n$ )の少なくとも1つの素子特性は、他の上記第2半導体素子の対応する素子特性とは異なることを特徴とする半導体素子配置。

## 【請求項2】

上記複数の第2半導体素子( $3_1$  -  $3_n$ )は、MOSFET、MISFET、MESFET、FINFET、JFET、HEMT、IGBT、またはナノチューブ素子であり、

上記少なくとも 1 つの素子特性は、ゲート抵抗、閾値電圧、ゲート - ソース容量、ゲート - ドレイン容量、ドレイン - ソース容量、チャネル幅、ボディ厚さ、チャネル長さ、ゲート酸化膜厚さ、ならびに、ソース領域、ボディ領域およびドレイン領域の 1 つのドーピング濃度の中から選択されることを特徴とする請求項 1 に記載の半導体素子配置。

#### 【請求項 3】

上記第 1 半導体素子 (2) はトランジスタであることを特徴とする請求項 1 または 2 に記載の半導体素子配置。

#### 【請求項 4】

上記トランジスタは、ノーマリオフトランジスタであることを特徴とする請求項 3 に記載の半導体素子配置。

#### 【請求項 5】

上記複数の第 2 半導体素子 ( $3_1$  -  $3_n$ ) は、ノーマリオントランジスタであることを特徴とする請求項 1 から 4 のいずれか一項に記載の半導体素子配置。

#### 【請求項 6】

上記第 1 半導体素子 (2) の上記負荷経路に負荷経路が直接接続されている 1 つ ( $3_1$ ) の上記第 2 半導体素子 ( $3_1$  -  $3_n$ ) の制御端子 ( $3_{11}$ ) は、上記第 1 半導体素子 (2) の第 1 負荷端子 ( $2_2$ ) に接続されており、

他の複数の上記第 2 半導体素子 ( $3_2$  -  $3_n$ ) のそれぞれの制御端子 ( $3_{12}$  -  $3_{1n}$ ) は、別の第 2 半導体素子 ( $3_1$  -  $3_n$ ) の第 1 負荷端子 ( $3_{21}$  -  $3_{2n}$ ) に接続されていることを特徴とする請求項 1 から 5 のいずれか一項に記載の半導体素子配置。

#### 【請求項 7】

上記他の複数の上記第 2 半導体素子 ( $3_2$  -  $3_n$ ) のそれぞれの制御端子 ( $3_{12}$  -  $3_{1n}$ ) は、隣接する第 2 半導体素子の第 1 負荷端子 ( $3_{21}$  -  $3_{2n}$ ) に接続されていることを特徴とする請求項 6 に記載の半導体素子配置。

#### 【請求項 8】

上記少なくとも 1 つの第 2 半導体素子 ( $3_i$ ) の制御端子 ( $3_{1i}$ ) と、別の第 2 半導体素子 ( $3_{i+1}$ ) の上記第 1 負荷端子 ( $3_{2i+1}$ ) との間に、抵抗 (41) が接続されていることを特徴とする請求項 6 に記載の半導体素子配置。

#### 【請求項 9】

整流素子 (42) が、上記抵抗 (41) に並列に接続されていることを特徴とする請求項 8 に記載の半導体素子配置。

#### 【請求項 10】

上記少なくとも 1 つの第 2 半導体素子 ( $3_i$ ) の上記制御端子 ( $3_{1i}$ ) および上記第 1 負荷端子 ( $3_{2i}$ ) の間に容量 (43) が接続されており、

上記容量 (43) は、上記少なくとも 1 つの第 2 半導体素子 ( $3_i$ ) のゲート - ソース容量 ( $C_{GS}$ ) に対して追加的に存在するものであることを特徴とする請求項 1 から 7 のいずれか一項に記載の半導体素子配置。

#### 【請求項 11】

上記第 1 半導体素子 (2) は、n チャネルトランジスタまたは p チャネルトランジスタのうちの 1 つであることを特徴とする請求項 1 から 10 のいずれか一項に記載の半導体素子配置。

#### 【請求項 12】

上記複数の第 2 半導体素子 ( $3_1$  -  $3_n$ ) は、n チャネルトランジスタまたは p チャネルトランジスタのうちの 1 つであることを特徴とする請求項 1 から 11 のいずれか一項に記載の半導体素子配置。

#### 【請求項 13】

上記複数の第 2 半導体素子は FINE であり、

各第 2 半導体素子は、

少なくとも 1 つの半導体フィン (52) と、

上記少なくとも 1 つの半導体フィン (52) の中に配置されたソース領域 (53) 、

ボディ領域(55)、およびドレイン領域(54)と、

上記ボディ領域(55)に隣接して配置されるゲート電極(56)とを備え、

上記ボディ領域(55)は、上記ソース領域(53)と上記ドレイン領域(54)との間に配置され、

上記ゲート電極(56)は、ゲート絶縁体(57)によって上記ボディ領域(55)から絶縁されていることを特徴とする請求項1から12のいずれか一項に記載の半導体素子配置。

#### 【請求項14】

半導体素子配置であって、

負荷経路を有する第1半導体素子(2)と、

それぞれが第1負荷端子および第2負荷端子( $3_{21}$  -  $3_{2n}$ 、 $3_{31}$  -  $3_{3n}$ )の間の負荷経路と制御端子( $3_{11}$  -  $3_{1n}$ )とを有する、複数の第2半導体素子( $3_1$  -  $3_n$ )とを備え、

上記複数の第2半導体素子( $3_1$  -  $3_n$ )の複数の負荷経路は、直列に接続され、かつ、上記第1半導体素子(2)の上記負荷経路に直列に接続されており、

上記第1半導体素子および上記複数の第2半導体素子( $3_1$  -  $3_n$ )を有する直列回路は、上記半導体素子配置の第1負荷端子(12)および第2負荷端子(13)の間に接続され、

各第2半導体素子( $3_1$  -  $3_n$ )の制御端子( $3_{11}$  -  $3_{1n}$ )は、1つの他の上記第2半導体素子( $3_1$  -  $3_n$ )の上記負荷端子、または、上記第1半導体素子(2)の1つの負荷端子(22、23)に接続されており、

上記複数の第2半導体素子( $3_1$  -  $3_n$ )のうちの1つの第2半導体素子( $3_1$ )は、その制御端子( $3_{11}$ )と、その第1負荷端子およびその第2負荷端子( $3_{21}$ 、 $3_{31}$ )のうちの1つとの間の駆動電圧として、上記第1半導体素子(2)の負荷経路電圧を受け、

他の複数の上記第2半導体素子( $3_2$  -  $3_n$ )のそれぞれは、駆動電圧として、少なくとも1つの第2半導体素子の負荷経路電圧を受け、

2つの上記第2半導体素子( $3_1$  -  $3_n$ )の上記負荷経路の間に位置する、上記直列回路のタップと、

上記タップと連結された第3負荷端子(13')とをさらに備えることを特徴とする半導体素子配置。

#### 【請求項15】

上記第3負荷端子(13')と上記タップとの間に接続されたスイッチング素子(35)を備え、

上記第3負荷端子(13')は、上記第2負荷端子(13)に接続されていることを特徴とする請求項14に記載の半導体素子配置。

#### 【請求項16】

上記スイッチング素子(35)は、機械的スイッチング素子または半導体スイッチング素子であることを特徴とする請求項15に記載の半導体素子配置。

#### 【請求項17】

上記第3負荷端子(13')と上記タップとの間に接続されたヒューズを備え、

上記第3負荷端子(13')は、上記第2負荷端子(13)に接続されていることを特徴とする請求項14または15に記載の半導体素子配置。

#### 【請求項18】

各第2半導体素子( $3_1$  -  $3_n$ )の制御端子は、1つの他の上記第2半導体素子( $3_1$  -  $3_n$ )の上記負荷端子に接続されており、

1つの上記第2半導体素子( $3_1$  -  $3_n$ )の制御端子は、上記第1半導体素子の複数の上記負荷端子の1つに接続されていることを特徴とする請求項13に記載の半導体素子配置。

#### 【請求項19】

並列に接続された少なくとも 2 つの直列回路 ( $1_1 - 1_p$ ) を備え、各直列回路 ( $1_1 - 1_p$ ) は、負荷経路と制御端子とを有する第 1 半導体素子 (2) と複数の第 2 半導体素子 ( $3_1 - 3_n$ ) とを備え、

各第 2 半導体素子 ( $3_1 - 3_n$ ) は、第 1 負荷端子および第 2 負荷端子の間の負荷経路と制御端子とを有し、

駆動端子 (11) と、

1 つの直列回路の上記第 1 半導体素子 (2) の上記制御端子 (21) と上記駆動端子 (11) との間に接続された少なくとも 1 つの抵抗 ( $R_1 - R_p$ ) とをさらに備え、

各直列回路の上記複数の第 2 半導体素子 ( $3_1 - 3_n$ ) の複数の負荷経路は、直列に接続されており、かつ、上記第 1 半導体素子 (2) の上記負荷経路に直列に接続されており、

各直列回路 ( $1_1 - 1_p$ ) の各第 2 半導体素子 ( $3_1 - 3_n$ ) の制御端子は、1 つの他の上記第 2 半導体素子の上記負荷端子、または、 上記第 1 半導体素子 (2) の上記負荷端子の 1 つに接続されていることを特徴とする半導体素子配置。

#### 【請求項 20】

複数の上記第 1 半導体素子 (2) の各制御端子は、抵抗 ( $R_1 - R_p$ ) を介して上記駆動端子 (11) に連結されており、

これら複数の抵抗 ( $R_1 - R_p$ ) のうち少なくとも 2 つは異なることを特徴とする請求項 19 に記載の半導体素子配置。

#### 【請求項 21】

上記少なくとも 1 つの抵抗は、RC 素子の一部であることを特徴とする請求項 19 に記載の半導体素子配置。

#### 【請求項 22】

複数の上記第 1 半導体素子の各制御端子は、RC 素子を介して上記駆動端子に連結されており、これら複数の RC 素子のうち少なくとも 2 つは、異なる時定数を有することを特徴とする請求項 19 に記載の半導体素子配置。

#### 【請求項 23】

3 個、4 個、5 個、5 個より多い、10 個より多い、または、20 個より多い第 2 半導体素子 ( $3_1 - 3_n$ ) を備えることを特徴とする請求項 1 から 22 のいずれか一項に記載の半導体素子配置。

## 【国際調査報告】

| INTERNATIONAL SEARCH REPORT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                        |                                                                      |  | International application No<br>PCT/EP2013/051827 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|--|---------------------------------------------------|

| <b>A. CLASSIFICATION OF SUBJECT MATTER</b><br>INV. H01L27/06 H01L27/088 H01L21/84 H01L29/40 H01L29/78<br>H01L27/12 H01L29/06                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                        |                                                                      |  |                                                   |

| <b>ADD.</b><br><small>According to International Patent Classification (IPC) or to both national classification and IPC</small>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                        |                                                                      |  |                                                   |

| <b>B. FIELDS SEARCHED</b><br><small>Minimum documentation searched (classification system followed by classification symbols)</small><br><b>H01L</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                        |                                                                      |  |                                                   |

| <small>Documentation searched other than minimum documentation to the extent that such documents are included in the fields searched</small>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                        |                                                                      |  |                                                   |

| <small>Electronic data base consulted during the international search (name of data base and, where practicable, search terms used)</small><br><b>EPO-Internal, INSPEC, IBM-TDB, WPI Data</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                        |                                                                      |  |                                                   |

| <b>C. DOCUMENTS CONSIDERED TO BE RELEVANT</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                        |                                                                      |  |                                                   |

| Category*                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Citation of document, with indication, where appropriate, of the relevant passages                     | Relevant to claim No.                                                |  |                                                   |

| Y                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | EP 0 140 349 A2 (HITACHI LTD [JP])<br>8 May 1985 (1985-05-08)<br>abstract; claims; figures<br>-----    | 1-13,<br>19-23                                                       |  |                                                   |

| Y                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | US 4 367 421 A (BAKER RICHARD H)<br>4 January 1983 (1983-01-04)<br>abstract; claims; figures<br>-----  | 1-13,<br>19-23                                                       |  |                                                   |

| X                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | DE 33 35 475 A1 (ANT NACHRICHTENTECH [DE])<br>2 May 1985 (1985-05-02)                                  | 14-18                                                                |  |                                                   |

| Y                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | abstract; claims; figures 2,3<br>-----                                                                 | 1-13,<br>19-23                                                       |  |                                                   |

| Y                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | DE 31 00 795 A1 (SIEMENS AG [DE])<br>5 August 1982 (1982-08-05)<br>abstract; claims; figure 1<br>----- | 1-13,<br>19-23                                                       |  |                                                   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | -/-                                                                                                    |                                                                      |  |                                                   |

| <input checked="" type="checkbox"/> Further documents are listed in the continuation of Box C.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                        | <input checked="" type="checkbox"/> See patent family annex.         |  |                                                   |

| <small>* Special categories of cited documents :</small><br>"A" document defining the general state of the art which is not considered to be of particular relevance<br>"E" earlier application or patent but published on or after the international filing date<br>"L" document which may throw doubts on priority claim(s) or which is cited to establish the publication date of another citation or other special reason (as specified)<br>"O" document referring to an oral disclosure, use, exhibition or other means<br>"P" document published prior to the international filing date but later than the priority date claimed                                                                                                          |                                                                                                        |                                                                      |  |                                                   |

| <small>"T" later document published after the international filing date or priority date and not in conflict with the application but cited to understand the principle or theory underlying the invention<br/>           "X" document of particular relevance; the claimed invention cannot be considered novel or cannot be considered to involve an inventive step when the document is taken alone<br/>           "Y" document of particular relevance; the claimed invention cannot be considered to involve an inventive step when the document is combined with one or more other such documents, such combination being obvious to a person skilled in the art<br/>           "&amp;" document member of the same patent family</small> |                                                                                                        |                                                                      |  |                                                   |

| Date of the actual completion of the international search<br><br>25 April 2013                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                        | Date of mailing of the international search report<br><br>07/05/2013 |  |                                                   |

| Name and mailing address of the ISA/<br>European Patent Office, P.B. 5818 Patentlaan 2<br>NL - 2280 HV Rijswijk<br>Tel. (+31-70) 340-2040,<br>Fax: (+31-70) 340-3016                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                        | Authorized officer<br><br>Wirner, Christoph                          |  |                                                   |

## INTERNATIONAL SEARCH REPORT

|                                                   |

|---------------------------------------------------|

| International application No<br>PCT/EP2013/051827 |

|---------------------------------------------------|

C(Continuation). DOCUMENTS CONSIDERED TO BE RELEVANT

| Category* | Citation of document, with indication, where appropriate, of the relevant passages                                                                         | Relevant to claim No. |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

| Y         | US 2010/078694 A1 (WILLMEROTH ARMIN [DE] ET AL) 1 April 2010 (2010-04-01)<br>abstract; claims; figures<br>-----                                            | 19-23                 |

| Y         | US 2003/071320 A1 (KOCON CHRISTOPHER B [US]) 17 April 2003 (2003-04-17)<br>abstract; claims; figures<br>-----                                              | 13                    |

| Y         | US 2010/032671 A1 (MARSHALL ANDREW [US]) 11 February 2010 (2010-02-11)<br>abstract; claims; figures<br>-----                                               | 13                    |

| A         | US 4 487 458 A (JANUTKA WILLIAM J [US]) 11 December 1984 (1984-12-11)<br>abstract; claims; figures<br>-----                                                | 1-23                  |

| A         | US 5 557 127 A (AJIT JANARDHANAN S [US] ET AL) 17 September 1996 (1996-09-17)<br>abstract; claims; figures<br>-----                                        | 1-23                  |

| A         | US 4 893 070 A (MILBERGER WALTER E [US] ET AL) 9 January 1990 (1990-01-09)<br>abstract; claims; figures<br>-----                                           | 1-23                  |

| X,P       | WO 2012/093177 A2 (INFINEON TECHNOLOGIES AUSTRIA [AT]; WEIS ROLF [AT]; HIRLER FRANZ [DE];) 12 July 2012 (2012-07-12)<br>abstract; claims; figures<br>----- | 1,14                  |

| X,P       | EP 2 521 259 A2 (SHARP KK [JP]) 7 November 2012 (2012-11-07)<br>abstract; claims; figures<br>-----                                                         | 1,14                  |

**INTERNATIONAL SEARCH REPORT**

Information on patent family members

|                              |

|------------------------------|

| International application No |

| PCT/EP2013/051827            |

| Patent document cited in search report |    | Publication date |                                                    | Patent family member(s)                                                                                                                 |                                                                                                                            | Publication date |

|----------------------------------------|----|------------------|----------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|------------------|

| EP 0140349                             | A2 | 08-05-1985       | DE<br>EP<br>US                                     | 3485409 D1<br>0140349 A2<br>4692643 A                                                                                                   | 13-02-1992<br>08-05-1985<br>08-09-1987                                                                                     |                  |

| US 4367421                             | A  | 04-01-1983       |                                                    | NONE                                                                                                                                    |                                                                                                                            |                  |

| DE 3335475                             | A1 | 02-05-1985       |                                                    | NONE                                                                                                                                    |                                                                                                                            |                  |

| DE 3100795                             | A1 | 05-08-1982       |                                                    | NONE                                                                                                                                    |                                                                                                                            |                  |