## (19) **日本国特許庁(JP)**

# (12) 公 開 特 許 公 報(A)

(11)特許出願公開番号

特開2004-103637 (P2004-103637A)

(43) 公開日 平成16年4月2日(2004.4.2)

| (51) Int.C1. <sup>7</sup> | FΙ                                                   |             |                       | テーマコード    | (参考)   |

|---------------------------|------------------------------------------------------|-------------|-----------------------|-----------|--------|

| HO1L 29/78                | HO1L                                                 | 29/78 6     | 18F                   | 5F048     |        |

| HO1L 21/823               | 18 HO1L                                              | 29/78 6     | 53D                   | 5 F 1 1 O |        |

| HO1L 27/092               | HO1L                                                 | 29/78 6     | 17T                   |           |        |

| HO1L 29/78                | HO1L                                                 | 29/78 6     | 26A                   |           |        |

|                           | HO1L                                                 | 27/08 3     | 2 1 C                 |           |        |

|                           | 審査請求 未                                               | 請求 請求項の     | D数 27 O L             | (全 30 頁)  | 最終頁に続く |

| (21) 出願番号<br>(22) 出願日     | 特願2002-259767 (P2002-259767)<br>平成14年9月5日 (2002.9.5) | 10-7-0-20-4 | 503121103<br>株式会社ルネサン | ステクノロジ    |        |

東京都千代田区丸の内二丁目4番1号

(74) 代理人 100080001

弁理士 筒井 大和

(72) 発明者 藤岡 美緒

> 東京都小平市上水本町五丁目20番1号 株式会社日立製作所半導体グループ内

(72) 発明者 蒲原 史朗

> 東京都小平市上水本町五丁目20番1号 株式会社日立製作所半導体グループ内

> > 最終頁に続く

## (54) 【発明の名称】半導体装置およびその製造方法

## (57)【要約】

【課題】電界効果トランジスタのゲート絶縁膜に酸化シ リコンより誘電率が高いhigh-k材料を使用した場 合に生ずるキャリアの移動度の低下を抑制または防止す る。

【解決手段】high-k材料で形成されるゲート絶縁 膜7を有するNMISQNとPMISQPにおいて、そ の動作時にチャネルがゲート絶縁膜7とP型半導体層2 aまたはN型半導体層2bとの接触界面よりも深い位置 に形成されるようにする。NMISQNにおいては、ゲ ート電極8Bの直下のP型半導体層2aの表層にN型半 導体層5を形成し、PMISOPにおいては、ゲート電 極80の直下のN型半導体層2bにP型半導体層6を形 成することで埋込チャネルが形成されるようにした。

【選択図】 図 1

## 【特許請求の範囲】

## 【請求項1】

- (a)第1導電型の第1半導体層と、

- (b)前記第1半導体層上に形成され、酸化シリコンより高い誘電率の材料を含むゲート 絶縁膜と、

(2)

- ( c ) 前記ゲート絶縁膜上に形成されたゲート電極と、

- (d)前記ゲート電極直下の前記第1半導体層内に形成され、前記第1導電型とは異なる 第2導電型にされた第2半導体層とを備えることを特徴とする半導体装置。

#### 【請求項2】

- ( a ) 絶縁層と、

- (b)前記絶縁層上に形成された第1導電型の第1半導体層と、

- (c)前記第1半導体層上に形成され、酸化シリコンより高い誘電率の材料を含むゲート 絶縁膜と、

- ( d ) 前記ゲート絶縁膜上に形成されたゲート電極と、

- (e)前記ゲート電極直下の前記第1半導体層内に形成され、前記第1導電型とは異なる 第2導電型にされた第2半導体層とを備えることを特徴とする半導体装置。

### 【請求項3】

- (a) 絶縁層と、

- (b)前記絶縁層上に形成された第1導電型の第1半導体層と、

- (c)前記第1半導体層上に形成され、酸化シリコンより高い誘電率の材料を含むゲート 20 絶縁膜と、

- ( d ) 前記ゲート絶縁膜上に形成されたゲート電極と、

- (e)前記第1半導体層の前記ゲート電極の直下に形成された第1の領域と、

- (f)前記第1半導体層の前記第1の領域の両側に形成された第2の領域とを有する電界効果トランジスタを備え、

- 前記電界効果トランジスタのチャネルが、前記第1の領域において、前記ゲート絶縁膜と前記第1半導体層との界面から離れた位置に形成されるようにしたことを特徴とする半導体装置。

## 【請求項4】

- ( a ) 絶縁層と、

- (b)前記絶縁層上に形成された第1導電型の第1半導体層と、

- (c)前記第1半導体層上に形成され、酸化シリコンより高い誘電率の材料を含むゲート 絶縁膜と、

- ( d ) 前記ゲート絶縁膜上に形成されたゲート電極と、

- ( e ) 前記第1半導体層の前記ゲート電極の直下に形成された第1の領域と、

- (f)前記第1半導体層の前記第1の領域の両側に形成されたソースおよびドレイン用の第2の領域とを有する電界効果トランジスタを備え、

- 前記電界効果トランジスタの動作時に前記第1の領域に埋込チャネルが形成されるようにしたことを特徴とする半導体装置。

## 【請求項5】

- (a) 絶縁層と、

- ( b ) 前記絶縁層上に形成された第1導電型の第1半導体層と、

- (c)前記第1半導体層上に形成され、酸化シリコンより高い誘電率の材料を含むゲート 絶縁膜と、

- ( d ) 前記ゲート絶縁膜上に形成されたゲート電極と、

- (e)前記第1半導体層の前記ゲート電極の直下に形成された第1の領域と、

- (f)前記第1半導体層の前記第1の領域の両側に形成された第2の領域とを有する電界効果トランジスタを備え、

- 前記第1の領域の一部が、前記電界効果トランジスタの非動作時に空乏化していることを 特徴とする半導体装置。

10

40

30

20

30

40

50

#### 【請求項6】

- (a) 絶縁層と、

- (b)前記絶縁層上に形成された第1導電型の第1半導体層と、

- ( c ) 前記第1半導体層上に形成され、酸化シリコンより高い誘電率の材料を含むゲート 絶縁膜と、

- (d)前記ゲート絶縁膜上に形成されたゲート電極と、

- ( e ) 前記第1半導体層の前記ゲート電極の直下に形成された第1の領域と、

- (f)前記第1半導体層の前記第1の領域の両側に形成された第2の領域とを有する電界効果トランジスタを備え、

前記第1の領域の全部が、前記電界効果トランジスタの非動作時に空乏化していることを特徴とする半導体装置。

#### 【請求項7】

- (a)柱状の半導体層と、

- (b)前記柱状の半導体層に形成された第1の領域と、

- ( c ) 前記柱状の半導体層の前記第1の領域の両側に形成された第2の領域と、

- ( d ) 前記柱状の半導体層の外周を覆うように形成された絶縁膜であって、酸化シリコンより高い誘電率の材料を含むゲート絶縁膜と、

- (e)前記柱状の半導体層の前記第1の領域の外周の少なくとも一部を前記ゲート絶縁膜を介して覆うように形成されたゲート電極とを有する電界効果トランジスタを備え、

- 前記電界効果トランジスタのチャネルが、前記第1の領域において、前記ゲート絶縁膜と前記柱状の半導体層との界面から離れた位置に形成されるようにしたことを特徴とする半導体装置。

## 【請求項8】

- (a)柱状の半導体層と、

- (b)前記柱状の半導体層に形成された第1の領域と、

- (c)前記柱状の半導体層の前記第1の領域の両側に形成されたソースおよびドレイン用の第2の領域と、

- (d)前記柱状の半導体層の外周を覆うように形成された絶縁膜であって、酸化シリコンより高い誘電率の材料を含むゲート絶縁膜と、

- (e)前記柱状の半導体層の前記第1の領域の外周の少なくとも一部を前記ゲート絶縁膜を介して覆うように形成されたゲート電極とを有する電界効果トランジスタを備え、

- 前記電界効果トランジスタのチャネルが、前記柱状の半導体層の中心軸側に形成されるようにしたことを特徴とする半導体装置。

## 【請求項9】

請求項7または8に記載された半導体装置において、

前記第1の領域の全部が、前記電界効果トランジスタの非動作時に空乏化していることを特徴とする半導体装置。

## 【請求項10】

請求項1~9のいずれか一項に記載された半導体装置において、前記ゲート絶縁膜は、酸化アルミニウム、酸化ジルコニウム、酸化ハフニウム、酸化チタン、窒化シリコンまたは酸化タンタルのいずれかを含むことを特徴とする半導体装置。

#### 【請求項11】

請求項1~10のいずれか一項に記載された半導体装置において、前記ゲート電極は、N型ポリシリコン、 P型ポリシリコンまたは金属のいずれかを含むことを特徴とする半導体装置。

## 【請求項12】

- ( a ) 第 1 導電型の第 1 半導体層を形成する工程と、

- (b)前記第1半導体層の第1の領域に第1導電型とは異なる第2導電型の第2半導体層を形成する工程と、

- ( c ) 前記第2半導体層上に酸化シリコンより高い誘電率の材料を含むゲート絶縁膜を形

成する工程と、

(d)前記ゲート絶縁膜上にゲート電極を形成する工程とを有することを特徴とする半導体装置の製造方法。

#### 【請求項13】

- ( a ) 絶縁層上に第1導電型の第1半導体層を形成した基板を用意する工程と、

- (b)前記第1半導体層の第1の領域に前記第1導電型と異なる第2導電型の第2半導体層を形成する工程と、

- (c)前記第2半導体層上に、酸化シリコンより高い誘電率の材料を含むゲート絶縁膜を 形成する工程と、

- (d)前記ゲート絶縁膜上にゲート電極を形成する工程とを有することを特徴とする半導体装置の製造方法。

#### 【請求項14】

- ( a ) 絶縁層上に第1導電型の第1半導体層を形成した基板を用意する工程と、

- ( b ) 前記第1半導体層に電界効果トランジスタを形成する工程とを有し、

前記電界効果トランジスタの形成工程は、

- (b1)前記第1半導体層上に、酸化シリコンより高い誘電率の材料を含むゲート絶縁膜を形成する工程と、

- (b2)前記ゲート絶縁膜上にゲート電極を形成する工程と、

- ( b 3 ) 前記第1半導体層の前記ゲート電極の直下の第1の領域の両側に所定の不純物を導入することにより、前記第1導電型とは異なる第2導電型の第2の領域を形成する工程と、

- ( b 4 ) 前記電界効果トランジスタのチャネルが、前記第1の領域において、前記ゲート 絶縁膜と前記第1半導体層との界面から離れた位置に形成されるように前記第1の領域に 不純物を導入する工程とを有することを特徴とする半導体装置の製造方法。

## 【請求項15】

- ( a ) 絶縁層上に第 1 導電型の第 1 半導体層を形成した基板を用意する工程と、

- (b)前記第1半導体層に電界効果トランジスタを形成する工程とを有し、

前記電界効果トランジスタの形成工程は、

- ( b 1 ) 前記第1半導体層上に、酸化シリコンより高い誘電率の材料を含むゲート絶縁膜を形成する工程と、

- (b2)前記ゲート絶縁膜上にゲート電極を形成する工程と、

- ( b 3 ) 前記第1半導体層の前記ゲート電極の直下の第1の領域の両側に所定の不純物を導入することにより、前記第1導電型とは異なる第2導電型の第2の領域を形成する工程と、

- (b4)前記電界効果トランジスタのチャネルが、前記第1の領域において、前記ゲート 絶縁膜と前記第1半導体層との界面から離れた位置に形成されるように前記第1の領域に 不純物を導入する工程とを有し、

- 前記第1半導体層は、前記電界効果トランジスタの非動作時に前記第1の領域の一部が空 乏化されるような厚さに形成されていることを特徴とする半導体装置の製造方法。

#### 【請求項16】

- (a) 絶縁層上に第1導電型の第1半導体層を形成した基板を用意する工程と、

- ( b ) 前記第 1 半導体層に電界効果トランジスタを形成する工程とを有し、

前記電界効果トランジスタの形成工程は、

- (b1)前記第1半導体層上に、酸化シリコンより高い誘電率の材料を含むゲート絶縁膜を形成する工程と、

- (b2)前記ゲート絶縁膜上にゲート電極を形成する工程と、

- ( b 3 ) 前記第1半導体層の前記ゲート電極の直下の第1の領域の両側に所定の不純物を導入することにより、前記第1導電型とは異なる第2導電型の第2の領域を形成する工程と、

- (b4)前記電界効果トランジスタのチャネルが、前記第1の領域において、前記ゲート

20

10

30

40

絶縁膜と前記第1半導体層との界面から離れた位置に形成されるように前記第1の領域に 不純物を導入する工程とを有し、

前記第1半導体層は、前記電界効果トランジスタの非動作時に前記第1の領域の全部が空 乏化されるような厚さに形成されていることを特徴とする半導体装置の製造方法。

絶 縁 層 上 に 形 成 さ れ た 柱 状 の 半 導 体 層 に 電 界 効 果 ト ラ ン ジ ス タ を 形 成 す る 工 程 を 有 し 、 前記電界効果トランジスタの形成工程は、

- (a) 第1の領域の両側に第2の領域を有する前記柱状の半導体層を形成する工程と、

- ( b ) 前記柱状の半導体層の表面に、酸化シリコンより高い誘電率の材料を含むゲート絶 縁膜を形成する工程と、

- ( c ) 前記第 1 の領域の外周の少なくとも一部を覆うように前記ゲート絶縁膜を介してゲ ート電極を形成する工程と、

- ( d ) 前記電界効果トランジスタのチャネルが、前記第 1 の領域において、前記ゲート絶 縁膜と前記半導体層との界面から離れた位置に形成されるように前記第1の領域に不純物 を導入する工程とを有することを特徴とする半導体装置の製造方法。

#### 【請求項18】

- (a) 第1導電型の第1半導体層に形成され、第1導電体型とは異なる第2導電型にされ たソース領域およびドレイン領域と、

- (b)前記第1半導体層に形成され、前記ソース領域と前記ドレイン領域とに挟まれ、且 つ、前記第2導電型にされた第2半導体層と、

- ( c )前記第1半導体層上に形成され、酸化シリコンより高い誘電率を有するゲート絶縁 膜と、

- (d)前記第2半導体層上に、前記ゲート絶縁膜を介して形成されたゲート電極とを備え

前記 ゲート 電 極 へ の 電 圧 印 加 時 に 、 前 記 第 1 半 導 体 層 と 前 記 ゲ ー ト 絶 縁 膜 と の 界 面 領 域 よ り も 先 に 前 記 第 1 半 導 体 層 と 前 記 第 2 半 導 体 層 の 界 面 領 域 に 、 前 記 ソ ー ス 領 域 と 前 記 ド レ イン領域とを導通させるチャネルが形成されることを特徴とする半導体装置。

#### 【請求項19】

- (a) 絶縁層と、

- ( b ) 前記絶縁層上に形成された第1半導体層と、

- ( c ) 前記第1半導体層に形成されたMISFETと、

## を有し、

前記MISFETは、

- ( c 1 ) 前記第 1 半導体層に、前記第 1 半導体層の表面から前記絶縁層にかけて形成され たソース領域およびドレイン領域と、

- ( c 2 ) 前記半導体層の前記ソース領域およびドレイン領域の間に、前記ソース領域およ び ド レ イ ン 領 域 よ り も 低 い 濃 度 で 、 か つ 、 前 記 ソ - ス 領 域 お よ び ド レ イ ン 領 域 と 同 じ 導 電 型にされた半導体層であって、前記第1半導体層の表面から前記絶縁層にかけて形成され た第2半導体層と、

- ( c 3 ) 前記第1半導体層上に形成され、酸化シリコンより高い誘電率を有するゲート絶 縁膜と、

- ( c 4 )前記第 2 半 導体層 上に、前記ゲート絶縁膜を介して形成されたゲート電極とを備 え、

前記ゲート電極への電圧印加時に、前記第2半導体層と前記ゲート絶縁膜との界面領域よ りも先に前記第2半導体層と前記絶縁層の界面領域に、前記ソース領域と前記ドレイン領 域とを導通させるチャネルが形成されることを特徴とした半導体装置。

#### 【請求項20】

請求項19に記載された半導体装置において、

前記第1半導体層の厚さは、50nmよりも薄く形成されていることを特徴とする半導体 装置。

10

20

30

#### 【請求項21】

円柱状に形成された、少なくとも3つの半導体層を有するMISFETであって、前記MISFETは、

- (a)前記半導体層の1層であり、前記半導体層の底面を含むソース領域と、

- (b)前記半導体層の他の1層であり、前記半導体層の他方の底面を含み、且つ、前記ソース領域と同一導電型のドレイン領域と、

- (c)前記半導体層の他の1層であり、前記ソース領域と前記ドレイン領域に挟まれ、前記ソース領域および前記ドレイン領域よりも低い濃度にされ、かつ、前記ソース領域およびドレイン領域と同一導電型の第2半導体層と、

- (d)前記半導体層側面に、前記第2半導体層を囲んで形成され、且つ、酸化シリコンより高い誘電率を有するゲート絶縁膜と、

- ( e ) 前記ゲート絶縁膜を介して形成されたゲート電極とを有し、

前記ゲート電極への電圧印加時に、前記第2半導体層と前記ゲート絶縁膜との界面領域よりも先に前記第2半導体層の中心に、前記ソース領域と前記ドレイン領域とを導通させるチャネルが形成されることを特徴とした半導体装置。

#### 【請求項22】

請求項19,20または21に記載された半導体装置であって、

前記MISFETがOFF状態において、前記第1半導体層は完全空乏化されていることを特徴とする半導体装置。

## 【請求項23】

請求項18~22のいずれか一項に記載された半導体装置において、

前記ソース領域および前記ドレイン領域は、それぞれ、低濃度不純物領域と高濃度不純物領域を有し、

前記低濃度不純物領域は、前記高濃度不純物領域よりも前記ゲート電極に近い位置に形成されていることを特徴とする半導体装置。

#### 【請求項24】

請求項18~23のいずれか一項に記載された半導体装置において、前記ゲート電極は、 N型ポリシリコンまたはP型ポリシリコンで形成されていることを特徴とする半導体装置

### 【請求項25】

請求項18~23のいずれか一項に記載された半導体装置において、

前記ゲート電極は、モリブデン、タングステンまたはコバルトのいずれかを含む膜で形成されていることを特徴とする半導体装置。

## 【請求項26】

請求項1~9のいずれか一項に記載された半導体装置において、前記ゲート絶縁膜は、酸化アルミニウム、酸化ジルコニウム、酸化ハフニウム、酸化チタン、窒化シリコンまたは酸化タンタルのいずれかを含むことを特徴とする半導体装置。

## 【請求項27】

- (a) 絶縁層と、

- (b)前記絶縁層上に形成された半導体層と、

- (c)前記半導体層を、第1導電型の第1半導体層とこれとは反対の導電型の第2導電型の第3半導体層とに分離する素子分離領域と、

- ( d ) 前記第1半導体層に形成された第1 M I S F E T と、

- (e)前記第3半導体層に形成された第2MISFETと、

## を有し、

前記第1MISFETは、

(d1)前記第1半導体層に形成された前記第2導電型の第1ソース領域および第1ドレイン領域と、

(d2)前記第1半導体層において、前記第1ソース領域と前記第1ドレイン領域に挟まれ、且つ、前記第2導電型の第4半導体層と、

20

10

30

40

(d3)前記第1半導体層上に形成され、酸化シリコンより高い誘電率を有するゲート絶縁膜と、

(d4)前記第4半導体層上に、前記ゲート絶縁膜を介して形成された第1ゲート電極と を備え、

前記第2MISFETは、

( e 1 ) 前記第 3 半導体層に形成された前記第 1 導電型の第 2 ソース領域および第 2 ドレイン領域と、

(e2)前記第2半導体層において、前記第2ソース領域と前記第2ドレイン領域に挟まれ、且つ、前記第1導電型の第5半導体層と、

( e 3 )前記第3半導体層上に形成された前記ゲート絶縁膜と、

( e 4 ) 前記第5半導体層上に、前記ゲート絶縁膜を介して形成された第2ゲート電極と を備え、

前記第1ゲート電極への電圧印加時に、前記第4半導体層と前記ゲート絶縁膜との界面領域よりも先に前記第4半導体層と前記第1半導体層の界面領域に、前記第1ソース領域と前記第1ドレイン領域とを導通させる第1チャネルが形成され、

前記第2ゲート電極への電圧印加時に、前記第5半導体層と前記ゲート絶縁膜との界面領域よりも先に前記第5半導体層と前記第3半導体層の界面領域に、前記第2ソース領域と前記第2ドレイン領域とを導通させる第2チャネルが形成されることを特徴とした半導体装置。

## 【発明の詳細な説明】

[ 0 0 0 1 ]

【発明の属する技術分野】

本発明は、半導体装置およびその製造技術に関し、特に、酸化シリコンより高い誘電率の材料をゲート絶縁膜に使用した半導体装置およびその製造技術に適用して有効な技術に関する。

[0002]

【従来の技術】

例えば特開2000-150668号公報に記載されているように、微細なゲート電極の低抵抗化とゲート空乏化率の改善を主な目的として、ゲート電極に不純物を導入したポリシリコンではなく、金属を用いた例がある。そして、ゲート電極に金属を用いた場合における閾値電圧の上昇を防止するため、埋め込みチャネル構造を形成して低い閾値電圧を実現している。

[0003]

また、現在の半導体装置の製造技術においては、MOS(Metal Oxide Semiconductor)型素子のゲート絶縁膜として酸化シリコン膜(SiO<sub>2</sub>)が使用される。近年、半導体装置の高集積化を図るために、MOS型素子の微細化が進められているが、MOS型素子の微細化が進むにつれて、ゲート絶縁膜を薄くする必要がある。

[0004]

しかし、ゲート絶縁膜である酸化シリコン膜を薄くするとトンネル効果により、ゲート電極とチャネル形成領域との間にトンネル電流が発生し、リーク電流が増加する。リーク電流が増加すると、消費電力が増加するという問題点がある。

[0005]

このため、酸化膜より高誘電率を有する材料(以下、high-k材料という)を使用することで、同一キャパシタンスを維持しながら、ゲート絶縁膜を厚くしている。ゲート絶縁膜を厚くすると、ゲート電極とチャネル形成領域との間にトンネル電流が発生しなくなり、上記した問題点を解決することができる。

[0006]

なお、high‐k材料をゲート絶縁膜に使用したMOS型素子の例としては、例えばL.Kang et al., IEDM Tech. Dig., 35(2000)に記載されている。

20

10

30

40

## [0007]

【発明が解決しようとする課題】

しかし、上記したhigh-k材料をゲート絶縁膜に使用した場合、ゲート絶縁膜直下に 形成されるチャネル形成領域を流れる電子の移動度が劣化するという問題点がある。すな わち、high-k材料をゲート絶縁膜に使用した場合、ゲート絶縁膜の表面の平坦性が 大きく低下し、ゲート絶縁膜に隣接するチャネル形成領域を流れる電子が散乱を起す。こ のため、電子の移動度が低下し、チャネル形成領域を流れる電流が減少するという問題点 がある。

[0008]

本発明の目的は、ゲート絶縁膜にhigh-k材料を使用した場合であっても、チャネル 形成領域を流れる電子の移動度の低下を抑制または防止することができる技術を提供する ことにある。

[0009]

本発明の前記ならびにその他の目的と新規な特徴は、本明細書の記述および添付図面から明らかになるであろう。

[0010]

【課題を解決するための手段】

本願において開示される発明のうち、代表的なものの概要を簡単に説明すれば、以下のとおりである。

[0011]

本発明は、high-k材料を含むゲート絶縁膜を有する電界効果トランジスタにおいて、その動作時にゲート絶縁膜と半導体との界面よりも深い位置にチャネルが形成されるようにするものである。

[0012]

また、本発明は、(a)第1導電型の不純物を導入した第1半導体層と、(b)前記第1 半導体層上に形成され、酸化シリコンより高い誘電率の材料を含むゲート絶縁膜と、(c) )前記ゲート絶縁膜上に形成されたゲート電極と、(d)前記ゲート電極直下の前記第1 半導体層内にあるチャネル形成領域に形成された層であって、第1導電型とは異なる導電型の不純物を導入した第2半導体層とを備えるものである。

[ 0 0 1 3 ]

また、本発明は、(a)第1導電型の不純物を導入した第1半導体層を形成する工程と、(b)前記第1半導体層のチャネル形成領域に第1導電型と異なる導電型の不純物を導入することにより第2半導体層を形成する工程と、(c)前記第2半導体層上に酸化シリコンより高い誘電率の材料を含むゲート絶縁膜を形成する工程と、(d)前記ゲート絶縁膜を形成する工程と、(d)前記ゲート絶縁膜上にゲート電極を形成する工程とを備えるものである。

[0014]

【発明の実施の形態】

以下、本発明の実施の形態を図面に基づいて詳細に説明する。また、実施の形態を説明するための全図において同一機能を有するものは同一の符号を付し、その繰り返しの説明は省略する。また、本実施の形態においては、電界効果トランジスタを代表するMIS・FET(Metal Insulator Semiconductor Field Effect Transistor)をMISと略し、Pチャネル型のMIS・FETをPMISと略し、Nチャネル型のMIS・FETをNMISと略す。

[0015]

(実施の形態1)

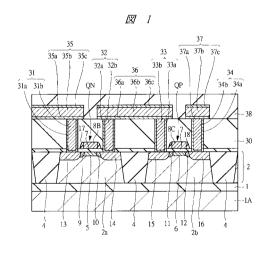

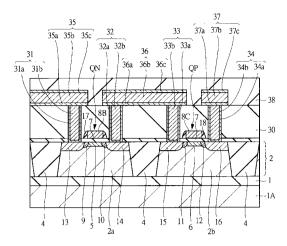

本実施の形態1における半導体装置を、図面を参照しながら説明する。図1は、本実施の 形態1における半導体装置の構成を示した要部断面図である。図1において、本実施の形態1における半導体装置の素子部は、N型のチャネルが形成されるNMISQNとP型の チャネルが形成されるPMISQPを有している。

[0016]

50

20

30

30

40

50

半 導 体 基 板 1 A は 、 例 え ば 単 結 晶 シ リ コ ン ( S i ) か ら な り 、 こ の 半 導 体 基 板 1 A 上 に 絶 縁層1が形成されている。絶縁層1は、例えば酸化シリコンからなり、この絶縁層1上に は、NMISONの構成要素であるP型半導体層2aおよびPMISOPの構成要素であ るN型半導体層2bを含む半導体層(第1半導体層の一例)2が形成されている。半導体 層 2 の厚さは、例えば 1 0 0 n m またはそれ以上である。 P 型半導体層 2 a には、例えば ボロン(B)等のP型不純物が導入されている。N型半導体層2bには、例えばリンまた はヒ素(As)等のようなN型不純物が導入されている。このP型半導体層2aおよびN 型半導体層2bの主面には、それぞれNMISQNおよびPMISQPが形成されている 。このNMISQNと上記PMISQPとは、素子分離層4によって、互いに分離されて いる。 素 子 分 離 層 4 は、 半 導 体 層 2 に 掘 ら れ た 溝 内 に 、 例 え ば 酸 化 シ リ コ ン 等 か ら な る 絶 縁膜が埋め込まれることで形成されている(溝型アイソレーション構造)。この素子分離 層4の下部は上記絶縁層1に達するように形成されており、NMISQNとPMISQP とは完全に分離された構造とされている。このようなSOI(Silicon n s u l a t o r ) 構造をとることにより素子間の完全な絶縁分離を図ることができるの で、素子の集積密度の向上を図ることができる。また、素子間の完全な絶縁分離を図るこ とができるため、半導体基板1Aを介したクロストークやラッチアップ現象などによる誤 動作の防止が可能となる。また、接合容量が低減されるため、高速動作、低消費電力の素 子を形成することが可能となる。

[0017]

次に、NMISQNの構造例を説明すると次の通りである。NMISQNは、P型半導体層2a、N型半導体層5(第2半導体層の一例)、ゲート絶縁膜7、ゲート電極8B、低濃度N型不純物拡散層(第2の領域)9、10、高濃度N型不純物拡散層(第2の領域)13、14、サイドウォール17を有している。このNMISQNは、絶縁層1上に形成されており、SOI(Silicon On Insulator)構造をしている。なお、半導体層2においてソースおよびドレイン用の低濃度N型不純物拡散層(第2の領域)9、10の間のゲート電極8Bの直下のP型半導体層2aにおいて、その表面から絶縁層1に達する領域が第1の領域であり、その一部にNMISQNのチャネルが形成される

[0018]

NMISQNのゲート電極8Bは、例えばN型のポリシリコンからなり、その両側面にはサイドウォール17が形成されている。半導体層2(P型半導体層2a)において、ゲート電極8Bの両側に当たる位置には、NMISQNのソースおよびドレイン用の半導体領域を構成する低濃度N型不純物拡散層9,10および高濃度N型不純物拡散層13,14が形成されている。すなわち、低濃度N型不純物拡散層10および高濃度N型不純物拡散層13,14を含むドレイン領域とが形成されている。低濃度N型不純物拡散層9,10および高濃度N型不純物拡散層14を含むドレイン領域とが形成されている。低濃度N型不純物拡散層9,10および高濃度N型不純物拡散層13,14には、例えばリン(P)または砒素(As)等のようなN型不純物が導入されているが、NMISQNのチャネル形成領域(ゲート電極8Bの直下のP型半導体層2aの動作領域)に近い低濃度N型不純物拡散層9,10は、高濃度N型不純物拡散層13,14よりも不純物濃度が低く設定されており、電界集中の緩和によるホットキャリアの発生を低減する機能を有している。

[0019]

また、P型半導体層2 a において、ゲート電極8 B の直下のチャネル形成領域には、上記 N 型半導体層5 が上記低濃度 N 型不純物拡散層9 ,1 0 に挟まれるように形成されている。 N 型半導体層 5 には、例えばリン(P)や砒素(A s)等のような N 型不純物が導入されている。 N M I S Q N の非動作時(ゲート電極8 B に動作電圧を印加していない時)には、ゲート電極8 B 直下の P 型半導体層 2 a に空乏層が形成されるようになっている。 ただし、この空乏層は絶縁層1 に達するものではなく、空乏層と絶縁層1 との間にはキャリアの多い中性領域(P 型半導体層2 a)が存在する構成となっている(部分空乏型)。 このような部分空乏型の S O I では、基板としてバルクを用いた場合に比べて、例えば以下

の効果が得られる。第1に接合容量を低減できる。このため、負荷容量を低減できるので、高速動作、低消費電力のデバイスを開発できる。また、高周波動作時における信号伝達損失を低減できる。第2に、基板バイアス効果を向上させることができる。第3に、しきい値の設定やソースおよびドレインでのシリサイド層の形成でもバルクと同じプロセスを適用できる。一方、NMISQNの動作時(ゲート電極8Bに所定の動作電圧を印加した時)には、N型半導体層5とP型半導体層2aとの境界付近にチャネルが形成される。すなわち、本実施の形態では、N型半導体層5を設けることにより、電子の通り道であるチャネルを、ゲート絶縁膜7と半導体層2との接触界面ではなく、その接触界面よりも深い位置に形成することができる(埋込チャネル)。これによる効果は後述する。

#### [0020]

ゲート電極 8 B と半導体層 2 ( P 型半導体層 2 a の N 型半導体層 5 )との間には、ゲート 絶縁膜7が形成されている。ゲート絶縁膜7は、例えば酸化アルミニウム(A1,O3) 、 酸 化 ジ ル コ ニ ウ ム ( Z r O ヵ ) 、 酸 化 ハ フ ニ ウ ム ( H f O ヵ ) 、 酸 化 チ タ ン ( T i O ヵ )、室化シリコン(Si3 N4)または酸化タンタル(Ta2 O5)などのようなhig h-k材料より形成されている。このようにゲート絶縁膜7をhigh-k材料より形成 することにより、ゲート絶縁膜7を薄くしなくてもMISの特性を上げるのに必要な容量 を稼ぐことができる。したがって、ゲート絶縁膜7の厚さをある程度確保できるので、ゲ ート電極 8 B とチャネルとの間に生ずるリーク電流を減少させることができる。しかし、 ゲート絶縁膜 7 の材料としてhigh-k材料を使用すると、ゲート絶縁膜 7 の材料とし て酸化シリコンを使用した場合に比べて、ゲート絶縁膜7が接する半導体層2の表面の平 坦性が低下する。このため、NMISONのチャネルがゲート絶縁膜7と半導体層2との 界面に形成されるような、いわゆる表面チャネルが形成されるような構成とすると、チャ ネルを流れる電子は、ゲート絶縁膜7と半導体層2との界面の凹凸によって散乱してしま う結果、電子の移動度が低下し、NMISQNの駆動電流量が低下してしまう。これに対 して、本実施の形態においては、P型半導体層2aのチャネル形成領域にN型半導体層5 を設け、NMISQNのチャネルがゲート絶縁膜7と半導体層2との界面ではなく、その 界面よりも深い位置に形成されるようにしたことにより、キャリアである電子は、ゲート 絶縁膜7と半導体層2との界面の凹凸に邪魔されることなく、散乱してしまうこともなく 、埋込チャネルを移動できる。すなわち、NMISQNのチャネルを流れる電子の散乱を 抑制または防止できるので、その電子の移動度の低下を抑制または防止することができる

## [0021]

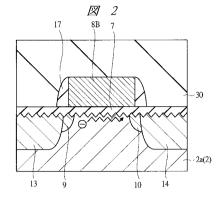

図2は、ゲート絶縁膜7をhigh‐k材料で形成した表面チャネル型のNMISにおいて、表面チャネルに電子が流れる様子を模式的に示している。high‐k材料を使用したゲート絶縁膜7と半導体層2との接触界面は、平坦性が低くなっており、凹凸が形成されている。このNMISにおいては、P型半導体層2aの表面にチャネルが形成されるため、電子がチャネルを移動する際、電子はゲート絶縁膜7とP型半導体層2aの表面に存在する凹凸によって散乱される。したがって、電子の移動度が低下し、電流が減少する問題が発生する。

## [0022]

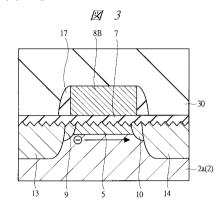

これに対して図3は、本実施の形態1におけるNMISQNにおいて、埋込チャネルに電子が流れる様子を模式的に示している。本実施の形態1におけるNMISQNにおいては、ゲート絶縁膜7直下のチャネル形成領域にN型半導体層5を設けることにより、ゲート電極8Bに電圧を印加したときに、N型半導体層5とP型半導体層2aとの境界付近(界面領域)に埋込チャネルが形成される。すなわち、図2に示したように電子がゲート絶縁膜7直下よりも深い領域に電子が流れる。すなわち、電子は、ゲート絶縁膜7と接しないところを流れるため、ゲート絶縁膜7の表面に存在する凹凸に散乱されることなく、チャネルを流れることができる。このため、本実施の形態1におけるNMISQNによれば、電子の移動度の低下を抑制または防止することができる。

10

20

30

20

30

50

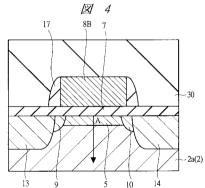

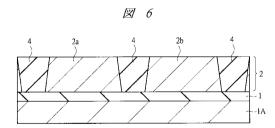

## [0023]

図4は、本実施の形態1におけるNMISQNの要部拡大断面図を示したものであり、図5は、図4中のシリコン表面Aから深さ方向に進んだ所定位置における不純物濃度のプロファイルを示したものである。すなわち、図5は、埋込チャネルを形成するN型半導体層5の不純物濃度分布を示したものである。図5を見て分かるように、表面から0.2μm付近まで、最大で、1.0×10<sup>18</sup>(1/cm³)の不純物濃度を有する砒素(As)が導入されているとともに、表面から0.5μm付近まで、最大で1.0×10<sup>17</sup>(1/cm³)の不純物濃度を有するボロン(B)が導入されていることが分かる。このように不純物を導入することにより、N型半導体層5を形成することができる。

#### [ 0 0 2 4 ]

次に、上記 P M I S Q P の構成について説明する。図 1 に示す P M I S Q P は、N 型半導体層 2 b、P 型半導体層 6 (第 2 半導体層の一例)、ゲート絶縁膜 7 、ゲート電極 8 C、低濃度 P 型不純物拡散層(第 2 の領域) 1 1、1 2、高濃度 P 型不純物拡散層(第 2 の領域) 1 5、1 6、サイドウォール 1 8を有している。なお、半導体層 2 においてソースおよびドレイン用の低濃度 P 型不純物拡散層(第 2 の領域) 1 1、1 2 の間のゲート電極 8 C の直下の N 型半導体層 2 b において、その表面から絶縁層 1 に達する領域が第 1 の領域であり、その一部に P M I S Q P のチャネルが形成される。

## [0025]

PMISQPのゲート電極8Cは、例えばP型のポリシリコンからなり、その両側面にはサイドウォール18が形成されている。半導体層2(N型半導体層2b)において、ゲート電極8Cの両側に当たる位置には、PMISQPのソースおよびドレイン用の半導体領域を構成する低濃度P型不純物拡散層11,12および高濃度P型不純物拡散層15,16が形成されている。すなわち、低濃度P型不純物拡散層11および高濃度P型不純物拡散層15方。16を含むソース領域と、低濃度P型不純物拡散層12および高濃度P型不純物拡散層16を含むドレイン領域とが形成されている。低濃度P型不純物拡散層11,12および高濃度P型不純物拡散層15,16には、例えばホウ素(B)等のようなP型不純物が導入されているが、PMISQPのチャネル形成領域(ゲート電極8Cの直下のN型半導体層2bの動作領域)に近い低濃度P型不純物拡散層11,12は、高濃度P型不純物拡散層15,16よりも不純物濃度が低く設定されており、電界集中の緩和によるホットキャリアの発生を低減する機能を有している。

### [0026]

ま た 、 N 型 半 導 体 層 2 b に お い て 、 ゲ ー ト 電 極 8 B の 直 下 の チ ャ ネ ル 形 成 領 域 に は 、 上 記 P 型 半 導 体 層 6 が 上 記 低 濃 度 P 型 不 純 物 拡 散 層 1 1 , 1 2 に 挟 ま れ る よ う に 形 成 さ れ て い る。P型半導体層6には、例えばホウ素(B)等のようなP型不純物が導入されている。 PMISQPの非動作時(ゲート電極8Cに動作電圧が印加されていない時)には、ゲー ト電極8C直下のチャネル形成領域(N型半導体層2b)に空乏層が形成されるようにな っている。ただし、この空乏層は絶縁層1に達するものではなく、空乏層と絶縁層1との 間にはキャリアの多い中性領域(N型半導体層2b)が存在する構成となっている(部分 空乏型)。このような部分空乏型のSOIでは、基板としてバルクを用いた場合に比べて 、上記した効果が得られる。一方、PMISQPの動作時(ゲート電極8Cに所定の動作 電圧が印加された時)には、P型半導体層6とN型半導体層2bとの境界付近にチャネル が形成される。すなわち、本実施の形態では、P型半導体層6を設けることにより、電子 の通り道であるチャネルを、ゲート絶縁膜7と半導体層2との接触界面ではなく、その接 触界面よりも深い位置に形成することができる(埋込チャネル)。したがって、PMIS QPでも、NMISQNと同様に、ゲート絶縁膜7と半導体層2との接触界面における凹 凸に起因するキャリアの散乱を抑制または防止できるので、キャリアの移動度の低下を抑 制または防止できる。

## [0027]

ゲート電極 8 C と半導体層 2 ( N 型半導体層 2 b の P 型半導体層 6 )との間には、ゲート絶縁膜 7 が形成されている。ゲート絶縁膜 7 の材料は、上記した h i g h - k 材料と同じ

30

40

50

であり、その効果はNMISQNで説明したのと同じなので説明を省略する。また、本実施の形態においては、N型半導体層2bのチャネル形成領域にP型半導体層6を設け、PMISQPの動作時におけるチャネルがゲート絶縁膜7と半導体層2との界面ではなく、その界面よりも深い位置に形成されるようにしたことにより、キャリアである正孔は、ゲート絶縁膜7と半導体層2との界面の凹凸に邪魔されることなく、散乱してしまうこともなく、埋込チャネルを移動できる。すなわち、PMISQPのチャネルを流れる正孔の散乱を抑制または防止できるので、その正孔の移動度の低下を抑制または防止することができる。

## [0028]

次に、本実施の形態 1 における半導体装置の配線部について説明する。なお、配線部の説明は、第 1 配線層までを示し、それ以上の層の説明は省略する。

#### [0029]

図1において、NMISQNおよびPMISQP上には、例えば酸化シリコンよりなる層 間絶縁層30が形成されている。この層間絶縁層30には、NMISQNの高濃度N型不 純物拡散層13、14、PMISQPの高濃度P型不純物拡散層15、16に達する孔が 形成されている。NMISQNのソース層に達する孔には、窒化チタン膜31a、タング ステン膜 3 1 b が埋め込まれてプラグ 3 1が形成されており、NMISQNのドレイン層 に達する孔には、窒化チタン膜32a、タングステン膜32bが埋め込まれてプラグ32 が形成されている。また、PMISQPのソース層に達する孔には、窒化チタン膜33a 、 タングステン膜 3 3 b が埋め込まれてプラグ 3 3 が形成されており、 P M I S Q P のド レイン層に達する孔には、 窒化チタン膜 3 4 a 、 タングステン膜 3 4 b が埋め込まれてプ ラグ 3 4 が形成されている。プラグ 3 1 は、窒化チタン膜 3 5 a 、タングステン膜 3 5 b 、窒化チタン膜35cよりなる第1層配線35に接続されている。また、プラグ32およ びプラグ 3 3 は、窒化チタン膜 3 6 a 、タングステン膜 3 6 b 、窒化チタン膜 3 6 c より なる第1層配線36に接続されている。したがって、NMISQNのドレイン層とPMI SQPのソース層が第1層配線36によって接続されておりCMIS(Compleme ntary MIS)型素子が形成されている。また、プラグ34は、窒化チタン膜37 a、タングステン膜37b、窒化チタン膜37cよりなる第1層配線37に接続されてい る。第1層配線35、第1層配線36、第1層配線37上には、例えば酸化シリコンより なる層間絶縁層38が形成されている。

### [0030]

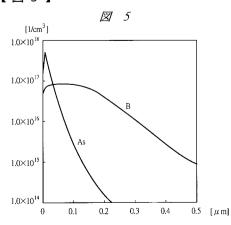

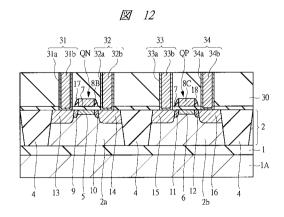

次に、本実施の形態1の半導体装置の製造方法について図6~図12を参照しながら説明する。図6~図12は、本実施の形態1の半導体装置の製造工程中の要部断面図である。

## [0031]

まず、図6に示すように、シリコンよりなる半導体基板1A上に、熱酸化法を使用して酸化シリコンよりなる絶縁層1を形成する。次に、例えばP型不純物であるボロン(B)を含有する半導体基板を、半導体基板1Aの絶縁層1を形成した面に貼り合わせて熱処理をした後、例えばCMP(Chemical Mechanical Polishing)技術により所定の厚さ(例えば100nmまたはそれ以上の厚さ)になるまで研磨することにより、半導体層2(第1半導体層の一例)を形成する。

## [0032]

続いて、半導体層 2 上に C V D 法を使用して窒化シリコン膜を形成した後、フォトリソグラフィ技術およびエッチング技術を使用して、窒化シリコン膜をパターニングする。その後、パターニングした窒化シリコン膜をマスクとして半導体層 2 のエッチングを行い、素子分離溝を形成する。そして、素子分離溝を形成した半導体層 2 上に、 C V D 法を使用して酸化シリコン膜を堆積する。

## [0033]

次に、 C M P 技術を使用して素子分離溝以外に堆積した酸化シリコン膜を除去し、半導体層 2 の領域を分離する素子分離層 4 を形成する。続いて、半導体層 2 および素子分離層 4 上にレジスト膜を塗布し、露光、現像することによりパターニングする。このパターニン

30

40

50

(13)

グでは、PMIS形成領域が露出され、それ以外の領域が覆われるようなレジストパターンを形成する。そして、レジストパターンから露出した領域にイオン注入法を使用して、例えばN型不純物であるリン(P)や砒素(As)を半導体層2に注入することにより、N型半導体層2b(第1半導体層の一例)を形成する。このようにして、いわゆるSOI(Silicon On Insulator)構造を形成することができる。

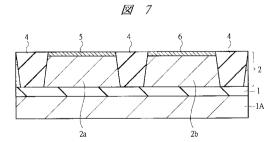

[0034]

次に、図7に示すように、フォトリソグラフィ技術およびイオン注入法を使用してP型半導体層2aにN型不純物である砒素を注入した後、熱処理を施すことによりN型半導体層5(第2半導体層の一例)を形成する。同様に、フォトリソグラフィ技術およびイオン注入法を使用してN型半導体層2bにP型不純物であるボロンを注入した後、熱処理を施すことによりP型半導体層6(第2半導体層の一例)を形成する。

[ 0 0 3 5 ]

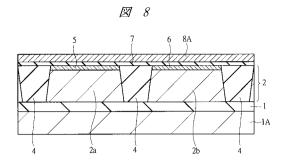

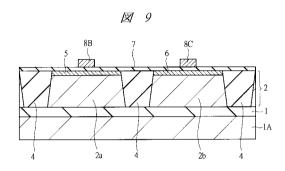

続いて、図8に示すように、CVD法を使用して酸化シリコンより誘電率が高いhigh- k 材料からなるゲート絶縁膜7をCVD法等により形成した後、CVD法を使用して酸化シリコン膜8Aを堆積する。酸化シリコンより誘電率が高いhigh- k 材料とした。 を材料を使用している。なが挙げられる。なお、ゲート絶縁膜7としてhigh- k 材料を使用する例を示ってもよい。でカート絶縁膜7としてhigh- k 材料を使用する例を示ってもよい。でカート絶縁膜7は、high- k 膜と酸化シリコン膜の積層膜であってもよい。そが後、フォトリソグラフィ技術およびイオン注及法を使用して、NMISQN形成領域のポリシリコン膜8AにN型不純物であるリンや砒素などを注入する。同様に、フォトリソグラフィ技術およびイオン注入なる。ポリシリコン膜8Aの不純物は、それを堆積するとで導入しても良い。続いて、フォトリソグラフィ技術およびエッチ技術を使用してりまり、N型不純物を含むゲート電極8Cを形成する。

[0036]

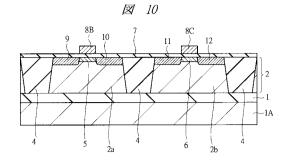

次に、図10に示すように、フォトリソグラフィ技術およびイオン注入法を使用することにより、N型不純物を注入して低濃度N型不純物拡散層9、10を形成した後、同様にフォトリソグラフィ技術およびイオン注入法を使用して、P型不純物を注入した低濃度P型不純物拡散層11、12を形成する。

[0037]

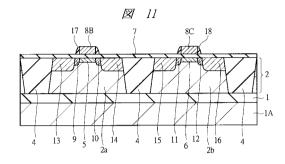

続いて、CVD法を使用してゲート絶縁膜7およびゲート電極8B、8C上に窒化シリコン膜または酸化シリコン膜を堆積した後、異方性エッチングによりエッチバックをすることにより、図11に示すサイドウォール17、18を形成する。そして、フォトリソグラフィ技術およびイオン注入法を使用することにより、N型不純物を注入し高濃度N型不純物拡散層13、14を形成する。同様に、フォトリソグラフィ技術およびイオン注入法を使用することによりP型不純物を注入し高濃度P型不純物拡散層15、16を形成する。

[0038]

次に、図12に示すように、ゲート絶縁膜7およびゲート電極8B、8C上に、CVD法を使用して酸化シリコンよりなる層間絶縁層30を形成後、NMISQNのソース層およびドレイン層に達する貫通孔を形成するとともにPMISQPのソース層およびドレイン層に達する貫通孔を形成する。

[0039]

続いて、形成した貫通孔にスパッタリング法を使用して窒化チタン膜 3 1 a 、 3 2 a 、 3 3 a 、 3 4 a を形成した後、C V D 法を使用してタングステン膜 3 1 b 、 3 2 b 、 3 3 b 、 3 4 b を形成する。その後、C M P 研磨を施すことにより、プラグ 3 1 、 3 2 、 3 3 、 3 4 を形成する。

[0040]

次に、図1に示すように、層間絶縁層30およびプラグ31、32、33、34上にスパッタリング法を使用して窒化チタン膜を形成後、CVD法を使用してタングステン膜を形

20

30

40

50

成し、その後再びスパッタリング法を使用して窒化チタン膜を形成する。続いて、フォトリソグラフィ技術およびエッチング技術を使用して、窒化チタン膜35a、タングステン膜35b、窒化チタン膜35cよりなる第1層配線35、窒化チタン膜36a、タングステン膜36b、窒化チタン膜36cよりなる第1層配線36、窒化チタン膜37a、タングステン膜37b、窒化チタン膜37cよりなる第1層配線37を形成する。その後、第1層配線35、第1層配線36、第1層配線37上に、CVD法を使用して酸化シリコンよりなる層間絶縁層38を形成する。このようにして、本実施の形態1における半導体装置を製造することができる。

## [0041]

(実施の形態2)

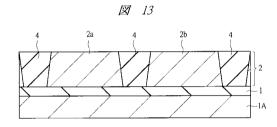

本実施の形態2では、前記実施の形態1における半導体装置を前記実施の形態1で述べた製造方法と異なる方法で製造する場合について説明する。図13~図24は本実施の形態2の半導体装置の製造工程中の要部断面図である。

[0042]

まず、前記実施の形態1で述べた方法と同様にして、図13に示すように半導体基板1A上に絶縁層1を形成し、この絶縁層1上に素子分離層4で分離されたP型半導体層2aおよびN型半導体層2bを形成する。

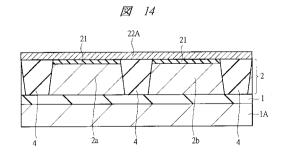

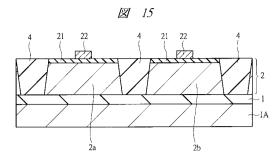

[0043]

次に、図14に示すようにP型半導体層2a、N型半導体層2bおよび素子分離層4上に熱酸化法を使用して酸化シリコン膜よりなるダミーゲート絶縁膜21を形成する。そして、ダミーゲート絶縁膜21上にCVD法を使用してポリシリコン膜22Aを堆積する。その後、フォトリソグラフィ技術およびエッチング技術を使用して、ポリシリコン膜22Aをパターニングすることにより、図15に示すようにダミーゲート電極22を形成する。ここで、ポリシリコン膜22Aの代わりに窒化シリコン膜を堆積させてもよい。

[0044]

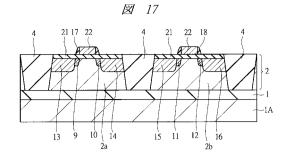

続いて、図16に示すように、フォトリソグラフィ技術およびイオン注入法を使用して例えばN型不純物であるリンや砒素をP型半導体層2aに注入した後、熱処理を施すことにより低濃度N型不純物拡散層9、10を形成する。同様に、フォトリソグラフィ技術およびイオン注入法を使用してP型不純物であるボロンをN型半導体層2bに注入した後、熱処理を施すことにより低濃度P型不純物拡散層11、12を形成する。

[0045]

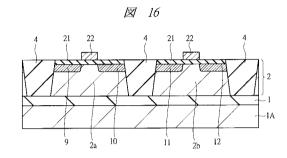

その後、ダミーゲート絶縁膜 2 1 およびダミーゲート電極 2 2 上に C V D 法を使用して窒化シリコン膜を形成し、異方性エッチングを行うことにより図 1 7 に示すサイドウォール 1 7 、 1 8 を形成する。

[0046]

次に、フォトリソグラフィ技術およびイオン注入法を使用することにより、 N 型不純物であるリンや砒素を注入した後に熱処理を施すことにより高濃度 N 型不純物拡散層 1 3 、 1 4 を形成する。同様にフォトリソグラフィ技術およびイオン注入法を使用することにより、 P 型不純物であるボロンを注入した後に熱処理を施すことにより高濃度 P 型不純物拡散層 1 5 、 1 6 を形成する。

[ 0 0 4 7 ]

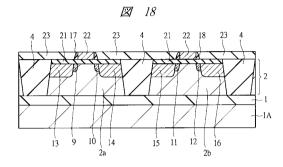

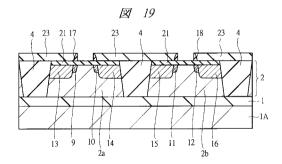

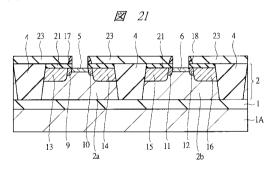

続いて、図18に示すように、半導体層2の素子形成面上にCVD法を使用して酸化シリコン膜23を堆積した後、CMP技術を使用して、ダミーゲート電極22の表面が露出される程度まで酸化シリコン膜23を研磨する。そして、図19に示すように、フォトリソグラフィ技術およびエッチング技術を使用して、ダミーゲート電極22を除去する。その後、図20に示すように、ダミーゲート絶縁膜21および酸化シリコン膜23上にレジスト膜を塗布した後、露光、現像することによりレジスト膜のパターニングを行う。このパターニングでは、NMISQN形成領域にレジスト膜が残らないようにする。次に、イオン注入法を使用して、NMISQN形成領域にN型不純物であるリンや砒素を打ち込む。打ち込まれたリンや砒素は、P型半導体層2aのチャネル形成領域に注入され、その後の

20

30

40

50

熱処理によって埋込チャネルを形成するためのN型半導体層5が形成される。

[0048]

次に、パターニングされたレジスト膜を除去した後、ダミーゲート絶縁膜21 および酸化シリコン膜23上にレジスト膜を塗布した後、露光、現像することによりレジスト膜のパターニングを行う。このパターニングは、PMISQP形成領域にレジスト膜が残らないようにする。次に、イオン注入法を使用して、PMISQP形成領域にP型不純物であるボロンを打ち込む。打ち込まれたボロンは、N型半導体層2bのチャネル形成領域に注入され、その後の熱処理によって埋込チャネルを形成するためのP型半導体層6が形成される。

[0049]

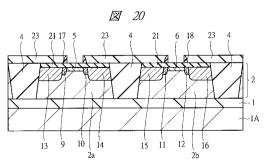

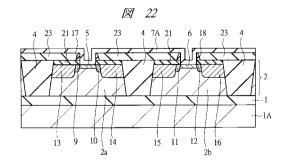

続いて、レジスト膜を除去した後、図 2 1 に示すように、露出しているダミーゲート絶縁膜 2 1 をエッチングにより除去する。そして、図 2 2 に示すように、 C V D 法を使用して酸化シリコンより高い誘電率を有する h i g h - k 膜 7 A を C V D 法等によって堆積する。酸化シリコンより高い誘電率を有する h i g h - k 材料としては、例えば A l  $_2$  O  $_3$  、 Z r O  $_2$  、 H f O  $_2$  、 T i O  $_2$  、 S i  $_3$  N  $_4$  または T a  $_2$  O  $_5$  などが挙げられる。

[0050]

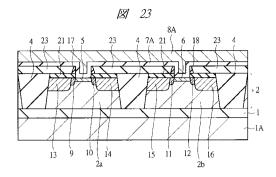

次に、図23に示すように、CVD法を使用してhigh-k膜7A上にポリシリコン膜8Aを堆積した後、フォトリソグラフィ技術およびイオン注入法を使用して、NMISQN形成領域のポリシリコン膜8AにN型不純物であるリンや砒素などを注入する。同様に、フォトリソグラフィ技術およびイオン注入法を使用してPMISQP形成領域のポリシリコン膜8AにP型不純物であるボロンを注入する。

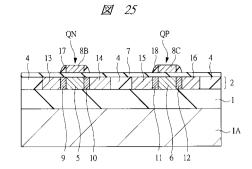

[ 0 0 5 1 ]

続いて、図24に示すように、CMP技術を使用してhigh-k膜7Aおよびポリシリコン膜8Aを研磨することにより、ゲート絶縁膜7、N型不純物が注入されたゲート電極8Bを形成する。ゲート電極8B、8Cとして、ポリシリコンを使用する例を示したが、高い熱処理を伴う拡散層形成後にゲート電極を形成するため、例えばタングステン(W)、モリブデン(Mo)、コバルト(Co)などの金属を使用してもよい。この時、高温の熱処理を必要とする拡散層の形成が終わっているため、ゲート電極8Cに比較的融点の低い金属膜を用いたとしても、金属が融解する等の不良が発生することなく形成することができる。

[0052]

この後の工程は、実施の形態 1 で説明した内容と同じため省略する。このように本実施の 形態 2 における半導体装置の製造方法によっても、前記実施の形態 1 における半導体装置 を製造することができる。

[0053]

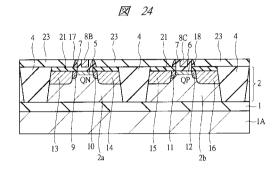

(実施の形態3)

図25は、本実施の形態3における半導体装置の要部断面図である。

[0054]

本実施の形態3では、NMISQNおよびPMISQPの非動作時に、ゲート電極8B,8C直下の半導体層2(N型半導体層5およびP型半導体層6)が完全に空乏化されるようになっている。すなわち、ゲート電極8B,8C直下の半導体層2では、半導体層2の主面から絶縁層1に到るまで完全に空乏化されるようになっている(完全空乏型)。このため、半導体層2は前記実施の形態1よりも薄く形成されており、その厚さは、例えば50nmまたはそれよりも薄く形成されている。このような完全空乏型のSOIでは、基板としてバルクを用いた場合または部分空乏型のSOIに比べて、例えば以下の効果が得られる。第1にバルクを使用した場合に比べて接合容量を低減できる。このため、負荷容量を低減できるので、高速動作、低消費電力のデバイスを開発でき、また、高周波動作時における信号伝達損失を低減できる。第2に、バルクを使用した場合に比べて基板バイアス効果を向上させることができる。第3に、部分空乏型に比べてサブスレッショルド係数を

30

40

50

(16)

小さくすることができる。このため、同一のオフ電流を想定した場合、完全空乏型では、部分空乏型やバルクに比べて、しきい値電圧を 0 . 1 V 程度小さくすることができ、低電圧動作の半導体装置における速度性能の向上を図ることができる。第 4 に、部分空乏型に比べて基板浮遊効果を小さくすることができる。このため、MISの動作安定性を向上させることができるので、回路およびレイアウトの設計を容易にすることができる。

[0055]

また、NMISQNのソースおよびドレイン用の低濃度N型不純物拡散層9、10および高濃度N型不純物拡散層(第2の領域)13、14と、PMISQPのソースおよびドレイン用の低濃度P型不純物拡散層11、12および高濃度P型不純物拡散層(第2の領域)15、16が半導体層2の表面から絶縁層1に達するまでに広がって形成されている。

[0056]

これ以外の構成は、前記実施の形態1,2と同様である。例えば本実施の形態3でも、ゲート絶縁膜7は、前記実施の形態1,2と同様にhigh‐k材料を含む構成とされている。また、本実施の形態3においても、NMISQNおよびPMISQPの動作時には、キャリア(電子または正孔)の通り道であるチャネルが、ゲート絶縁膜7と半導体層2との接触界面ではなく、その接触界面よりも深い位置、ここでは絶縁層1と半導体層2との界面近傍に形成されるようになっている(埋込チャネル)。したがって、本実施の形態3のような完全空乏型のSOI構造を有する半導体装置でも、NMISQNおよびPMISQPのキャリア(電子または正孔)は、ゲート絶縁膜7と半導体層2との界面の凹凸に邪魔されることなく、また散乱してしまうこともなく、埋込チャネルを移動できる。すなわち、NMISQNおよびPMISQPのチャネルを流れるキャリアの散乱を抑制または防止できるので、そのキャリアの移動度の低下を抑制または防止することができる。

[0057]

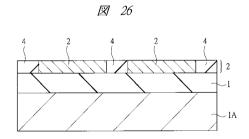

次に、本実施の形態3における半導体装置の製造方法を説明する。

[0058]

まず、前記実施の形態 1 で述べた方法と同様にして、図 2 6 に示すように半導体基板 1 A 上に絶縁層 1 を形成し、この絶縁層 1 上に素子分離層 4 で分離された厚さが約 5 0 n m またはそれより薄い半導体層 2 を形成する。このようにして、いわゆる S O I 構造を形成することができる。

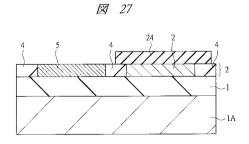

[ 0 0 5 9 ]

次に、図27に示すように、PMIS形成領域をレジスト膜24で覆った後、イオン注入法を使用してP型半導体層2にN型不純物であるリンまたは砒素を注入する。そして、熱処理を施すことにより埋込チャネルが形成されるN型半導体層5を形成する。本実施の形態においてN型半導体層5は、半導体層2の主面から絶縁層1に達するまでに及んで形成されている。ここで、イオン注入法では、深さ方向の厚さに応じて横方向の長さが制御される。すなわち、イオンを注入する深さ方向の厚さが薄ければ、それに応じてイオンが注入される横方向の長さも小さくすることができる。したがって、本実施の形態では、N型半導体層5の厚さが、例えば50nm以下というように薄く形成されているので、イオン注入法によって形成されるN型半導体層5の横方向の長さも短くすることができる。このため、NMISの微細化が可能となる。

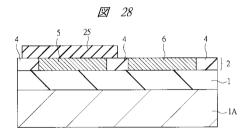

[0060]

続いて、レジスト膜24を除去した後、図28に示すように、NMIS形成領域をレジスト膜25で覆った後、イオン注入法を使用して半導体層2にP型不純物であるボロンを注入する。そして、熱処理を施すことにより埋込チャネルが形成されるP型半導体層6を形成する。本実施の形態においてP型半導体層6は、半導体層2の主面から絶縁層1に達するまでに及んで形成されている。上記NMISと同様PMIS側でも微細化が可能である

[0061]

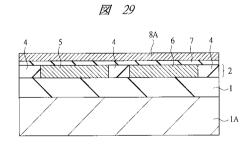

次に、レジスト膜25を除去した後、図29に示すように、N型半導体層5およびP型半導体層6を含む半導体層2および素子分離層4上にCVD法を使用して、酸化シリコンよ

20

30

40

50

り高い誘電率を有するhigh‐k材料からなるゲート絶縁膜7を堆積する。そして、このゲート絶縁膜7上にCVD法を使用して、ポリシリコン膜8Aを形成した後、フォトリソグラフィ技術およびイオン注入法を使用してNMISQN形成領域上に形成されたポリシリコン膜8AにN型不純物であるリンや砒素を注入する。同様に、フォトリソグラフィ技術およびイオン注入法を使用してPMISQP形成領域上に形成されたポリシリコン膜8AにP型不純物であるボロンを注入する。

[0062]

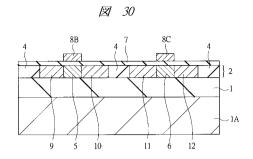

その後、フォトリソグラフィ技術およびエッチング技術を使用してポリシリコン膜 8 A をパターニングして、図 3 0 に示すゲート電極 8 B、 8 C を形成する。続いて、フォトリソグラフィ技術およびイオン注入法を使用して、低濃度 N 型不純物拡散層 9 、 1 0 および低濃度 P 型不純物拡散層 1 1 、 1 2 を形成する。

[0063]

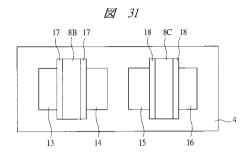

次に、ゲート絶縁膜7上およびゲート電極8B、8C上にCVD法を使用して窒化シリコン膜を形成した後、異方性エッチングをすることにより、図25に示したサイドウォーオった。18を形成する。そして、フォトリソグラフィ技術およびイオン注入法を使用することにより、N型不純物を注入し高濃度N型不純物拡散層13、14を形成する。同様にフォトリソグラフィ技術およびイオン注入法を使用することによりP型不純物を注入し高濃度P型不純物拡散層15、16を形成する。図31に、上記工程を経た本実施の形の高濃度P型不純物拡散層15、16を形成する。図31に、上記工程を経た本実施の形のの間における半導体装置を上部から眺めた要部面図を示す。図31におけて、NMISQ配が付いたゲート電極8Cがあることが分かる。そして、NMISQNとPMISQによるののののののののでは、できる。このようにして本実施の形態3における半導体装置を形成することができる。

[0064]

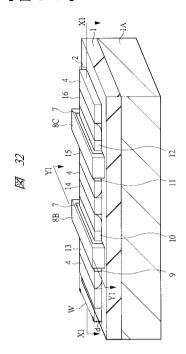

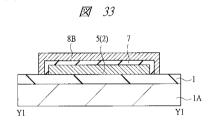

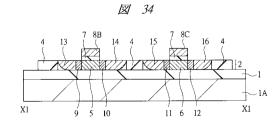

次に、本実施の形態3における半導体装置の変形例について説明する。図32は、変形例における半導体装置の構成を示した要部斜視図である。また、図33は図32のY1-Y1線の断面図を示し、図34は図32のX1-X1線の断面図を示している。半導体基板1A上には、絶縁層1が形成されており、この絶縁層1上には、半導体層2が島状に設けられている。この半導体層2には、NMISQNとPMISQPとが隣接されて形成されている。このNMISQNとPMISQPとの間には、素子分離層4が形成されている。素子分離層4は、半導体層2の主面から絶縁層1に達するように形成されている。このため、NMISQNとPMISQPとは、絶縁層1と素子分離層4とによって完全に分離されている。

[0065]

半導体層2の厚さdは、上記と同様に、例えば50nmまたはそれよりも薄く形成されており、完全空乏型のSOI構造とされている。もちろん前記実施の形態1と同様にSQDのSOI構造とされている。もちに異なっているのは、NMISQDのよびPMISQPのゲート絶縁膜7およびゲート電極8B,8Cは、半導体層2の上の内で、上記と特に異なっているのは、半導体層2の上での側面を覆うように形成されていることである。このため、NMISQPMISQPの大っト幅とのの表すことができる。すなわち、図25で示した構造ののととの和(=W+2d)で表すことができる。すなわち、図25で示した構造ののよびPMISQPのが「トートに流れる電流を図25に示した構造のの、NMISQNおよびPMISQPの動作時に流れる電流を図25に示したが、MISQNおよびPMISQPよりも増大さとができる。ここでは、NMISQNおよびPMISQPの動作速度の向上を図ることができる。ここでは、NMISQNおよびPMISQPの動作を図ることができる。ここでは、NMISQNおよびPMISQPと同じ実効的なゲート幅(W+2d)を得るようにしても良いでおいて

20

30

40

50

も良いし、半導体層2の厚さで稼いでも良し、幅Wと厚さdとを等しくして得ても良い。

## [0066]

このような構造でもNMISQNおよびPMISQPのチャネルは、前記実施の形態1,2 および図25で説明した例と同様に、ゲート絶縁膜7と半導体層2との界面よりも深い位置、半導体層2の側面ではゲート絶縁膜7と半導体層2の界面から離れた位置に形成される。したがって、この場合もNMISQNおよびPMISQPのキャリアの散乱を抑制または防止でき、キャリアの移動度の低下を抑制または防止できる。なお、ゲート電極8B,8C側面のサイドウォールの図示は省略する。

## [0067]

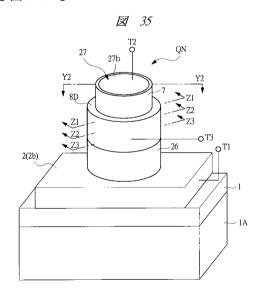

(実施の形態4)

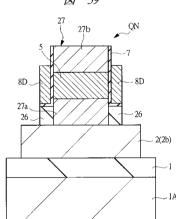

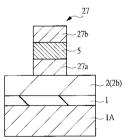

図35は本実施の形態4における半導体装置の要部斜視図、図36は図35のZ1-Z1線の断面図、図37は図35のZ2-Z2線の断面図、図38は図35のZ3-Z3線の断面図、図39は図35のY2-Y2線の断面図を示している。

## [0068]

本実施の形態 4 では、絶縁層 1 上に半導体層 2 (N型半導体層 2 b)を介して円柱状の半導体層 2 7 が設けられており、その円柱状の半導体層 2 7 に、例えば縦型のNMISQNのチャネルが形成される構成を含む半導体装置の一例について説明する。ここではNMISを例示するが、PMISを形成しても良い。また、半導体層 2 7 は、円柱状に限定されるものではなく立方体状でも良い。

## [0069]

半導体層 2 7 は、例えばシリコンからなり、 $N^+$  型半導体層(第 2 の領域) 2 7 a、N 型半導体層(第 2 半導体層、第 1 の領域) 5 および  $N^+$  型半導体層(第 2 の領域) 2 7 b が下層から順に重なるように形成されている。半導体層 2 7 a , 2 7 b は、M I S のソースおよびドレイン用の半導体領域を形成する領域である。半導体層 2 7 a , 2 7 b には、例えばリンまたは砒素等のような N 型不純物が導入されている。このうち、最下層の  $N^+$  型半導体層 2 7 a は、半導体層 2 と電気的に接続されている。半導体層 2 7 b は配線を通じて端子 1 と電気的に接続されている。

## [0070]

半導体層27の基部(半導体層27の底部からN<sup>+</sup>半導体層27aの途中の高さ位置までの部分)には、その外周を覆うように絶縁層26が円筒状に形成されている。絶縁層26は、例えば酸化シリコンからなり、ゲート電極8Dと半導体層2とを離間させる機能を有している。また、半導体層27の基部よりも上方の部分には、その外周(特にN型半導体層5の外周)を覆うようにゲート絶縁膜7が円筒形状に形成されている。ゲート絶縁膜7は、前記実施の形態1~3と同様のhigh-k材料で形成されている。さらに、半導体層27の外周には、その外周(特にN型半導体層5の外周)を覆うように上記ゲート絶縁膜7を介してゲート電極8Dが円筒形状に形成されている。ゲート電極8Dは、例えばN型ポリシリコンからなる。ゲート電極8Dは配線を通じて端子T3と電気的に接続されている。

## [0071]

本実施の形態4においても、NMISQNの非動作時は、半導体層27の中間のN型半導体層5の全体は空乏化されている(完全空乏型)。一方、NMISの動作時(ゲート電極8Dに所定の動作電圧を印加した時)には、NMISQNのチャネルがゲート絶縁膜7と半導体層27との界面ではなく、その界面よりも深い位置、すなわち円柱状の半導体層27の中心軸からその外周に向かって形成されるような状態になる(埋込チャネル)。この場合、NMISQNのキャリアである電子は、円柱状の半導体層27の中心軸に沿うように(図29の上下方向に沿って)流れる。このため、キャリアである電子は、ゲート絶縁膜7と半導体層27との界面の凹凸に邪魔されることなく、また散乱してしまうこともなく、埋込チャネルを移動できる。すなわち、NMISQNのチャネルを流れる電子の散乱を抑制または防止できるので、その電子の移動度の低下を抑制または防止することができ

る。

[0072]

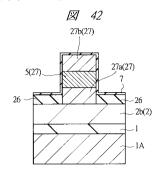

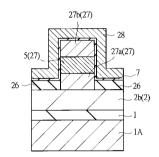

次に、本実施の形態4の半導体装置の製造方法を図40~図43により説明する。なお、図40~図43は、半導体装置の製造工程中の要部断面図である。

[0073]

まず、図40に示すように、シリコンよりなる半導体基板1A上に、熱酸化法を使用して酸化シリコンよりなる絶縁層1を形成する。次に、例えばN型不純物であるリンや砒素を導入した半導体基板を、半導体基板1Aの絶縁層1を形成した面に貼り合わせて熱処理をした後、CMP技術により所定の厚さになるまで研磨し半導体層2(N型半導体層2b)を形成する。

[0074]

続いて、図41に示すように、N型半導体層2b上に、リンまたは砒素などのN型不純物をドープした第1のアモルファスシリコン膜、相対的に不純物濃度が低くなるようにリンまたは砒素などのN型不純物をドープした第2のアモルファスシリコン膜および第1のアモルファスシリコンと同程度のリンまたは砒素などのN型不純物をドープした第3のアモルファスシリコン膜をCVD法等によって下方から順に堆積し、熱処理を行って、これらのアモルファスシリコン膜を結晶化する。アモルファスシリコン膜の結晶化は、後述するゲート絶縁膜の形成工程での熱処理などを利用しても良い。また、第1のアモルファスシリコン膜は、CVD法によって堆積させた後にN型不純物をイオン打ち込み法等によってドープし、その後に熱処理を加えることで形成してもよい。第2、第3のアモルファスシリコン膜についても同様である。

[0075]

続いて、フォトリソグラフィ技術およびエッチングすることにより半導体層27を円柱状にパターニングする。これにより、N<sup>+</sup>型半導体層27a、N型半導体層5およびN<sup>+</sup>型半導体層27bを有する円柱状の半導体層27を形成する。

[0076]

次に、SOI基板上に酸化シリコンよりなる絶縁層26をCVD法によって堆積した後、これをエッチバックすることにより、図42に示すように、半導体層27の基部に絶縁層26を形成する。その後、酸化シリコンより誘電率の高いhigh-k材料からなるゲート絶縁膜7をCVD法等により形成する。続いて、図43に示すようにゲート絶縁膜7を覆うように、N型ポリシリコン膜28をCVD法等により堆積した後、これをフォトリソグラフィ技術およびエッチング技術を使用してパターニングすることにより、図39等に示したようにゲート電極8Dを形成する。続いて、フォトリソグラフィ技術およびエッチング技術を使用して絶縁層26、N型半導体層2bを図39に示した形状にする。このようにして、本実施の形態4における半導体装置を形成することができる。

[0077]

本実施の形態 4 の変形例として半導体基板 1 A の主面に他の素子(例えばMIS)を形成しても良い。例えばSRAMのメモリセルのドライバMISを半導体基板 1 の主面に形成する。SRAMのメモリセルの負荷MISまたは転送用MISを上記縦型のNMISQNで形成する。このドライバMISのソースまたはドレインは、配線を通じて縦型のNMISQNのソースまたはドレインの一方(すなわち、端子T1)と電気的に接続される。縦型のMISQNが転送用MISであれば、そのソースまたはドレインの他方(すなわち、端子T2)はデータ線と電気的に接続される。また、縦型のNMISQNのゲート電極 8 D(すなわち、端子T3)はワード線に電気的に接続される。また、この場合、絶縁層 1 は、配線層間の層間絶縁膜に相当する。

[0078]

以上、本発明者によってなされた発明を前記実施の形態に基づき具体的に説明したが、本発明は前記実施の形態に限定されるものではなく、その要旨を逸脱しない範囲で種々変更可能であることはいうまでもない。

[0079]

10

20

30

40

30

40

50

以上、本願によって開示される実施の形態のうち、代表的なものによって得られる効果を 簡単に説明すれば、以下の通りである。

[0800]

SOI構造をとることにより素子間の完全な絶縁分離を図ることができるので、素子の集積密度の向上を図ることができる。また、素子間の完全な絶縁分離を図ることができるため、半導体基板を介したクロストークやラッチアップ現象などによる誤動作の防止が可能となる。また、接合容量が低減されるため、高速動作、低消費電力の素子を形成することが可能となる。

[0081]

また、ゲート絶縁膜を酸化シリコン膜よりも誘電率の高いhigh-k材料により形成することにより、ゲート絶縁膜を薄くしなくてもMISの特性を上げるのに必要な容量を稼ぐことができる。したがって、ゲート絶縁膜の厚さをある程度確保できるので、ゲート電極とチャネルとの間に生ずるリーク電流を減少させることができる。

[0082]

また、high- k 材料を含むゲート絶縁膜を有する電界効果トランジスタにおいて、本実施の形態のNMISQnによれば、N型半導体層 5 を形成することで、その動作時にゲート絶縁膜と半導体との界面よりも深い位置にチャネルが形成されるようにすることにより、電界効果トランジスタのチャネルを流れる電子の散乱を防止できる。

[0083]

また、SOI構造でゲート下の半導体層を完全空乏とすることで、基板としてバルクを用いた場合または部分空乏型のSOIに比べて、接合容量を低減できる。また、高周波動作時における信号伝達損失を低減できる。また、バルクを使用した場合に比べて基板バイアス効果を向上させることができる。また、部分空乏型に比べてサブスレッショルド係数を小さくすることができる。

[0084]

【発明の効果】

本願によって開示される発明のうち、代表的なものによって得られる効果を簡単に説明すれば、以下の通りである。

[0085]

チャネル形成領域を流れる電子の移動度の低下を抑制または防止することができる。

【図面の簡単な説明】

【図1】本発明の実施の形態1における半導体装置の構成を示した要部断面図である。

【図2】ゲート絶縁膜直下に形成されたチャネルに電子が流れて散乱される様子を模式的に示した要部断面図である。

【図3】本発明の実施の形態1において、埋込チャネルに電子が流れる様子を模式的に示した要部断面図である。

【図4】本発明の実施の形態1における半導体装置の一部を示した要部断面図である。

【 図 5 】シリコン表面から深さ方向に進んだ所定位置における不純物濃度のプロファイル を示したグラフ図である。

【図6】本発明の実施の形態1における半導体装置の製造工程中の要部断面図である。

【図7】本発明の実施の形態1における半導体装置の製造工程中の要部断面図である。

【 図 8 】 本 発 明 の 実 施 の 形 態 1 に お け る 半 導 体 装 置 の 製 造 工 程 中 の 要 部 断 面 図 で あ る 。

【図9】本発明の実施の形態1における半導体装置の製造工程中の要部断面図である。

【図10】本発明の実施の形態1における半導体装置の製造工程中の要部断面図である。

【図11】本発明の実施の形態1における半導体装置の製造工程中の要部断面図である。

【図12】本発明の実施の形態1における半導体装置の製造工程中の要部断面図である。

【図13】本発明の実施の形態2における半導体装置の製造工程中の要部断面図である。

【図14】本発明の実施の形態2における半導体装置の製造工程中の要部断面図である。

【図15】本発明の実施の形態2における半導体装置の製造工程中の要部断面図である。

【図16】本発明の実施の形態2における半導体装置の製造工程中の要部断面図である。

```

【図17】本発明の実施の形態2における半導体装置の製造工程中の要部断面図である。

【図18】本発明の実施の形態2における半導体装置の製造工程中の要部断面図である。

【図19】本発明の実施の形態2における半導体装置の製造工程中の要部断面図である。

【図20】本発明の実施の形態2における半導体装置の製造工程中の要部断面図である。

【図21】本発明の実施の形態2における半導体装置の製造工程中の要部断面図である。

【図22】本発明の実施の形態2における半導体装置の製造工程中の要部断面図である。

【図23】本発明の実施の形態2における半導体装置の製造工程中の要部断面図である。

【図24】本発明の実施の形態2における半導体装置の製造工程中の要部断面図である。

【図25】本発明の実施の形態3における半導体装置の構成を示した要部断面図である。

【 図 2 6 】 本 発 明 の 実 施 の 形 態 3 に お け る 半 導 体 装 置 の 製 造 工 程 中 の 要 部 断 面 図 で あ る 。

10

【図27】本発明の実施の形態3における半導体装置の製造工程中の要部断面図である。

【図28】本発明の実施の形態3における半導体装置の製造工程中の要部断面図である。

【図29】本発明の実施の形態3における半導体装置の製造工程中の要部断面図である。

【図30】本発明の実施の形態3における半導体装置の製造工程中の要部断面図である。

【図31】本発明の実施の形態3における半導体装置を上部から眺めた要部平面図である

【図32】本発明の実施の形態3の変形例における半導体装置の構成を示した要部斜視図

である。

【図33】図32のY1-Y1線の断面図である。

【図34】図32のX1-X1線の断面図である。

20

【図35】本発明の実施の形態4における半導体装置の構成を示した斜視図である。

【図36】図35のZ1-Z1線の断面図である。

【図37】図35のZ2-Z2線の断面図である。

【図38】図35のZ3-Z3線の断面図である。

【 図 3 9 】 図 3 5 の Y 2 - Y 2 線 の 断 面 図 で あ る。

【図40】本発明の実施の形態4における半導体装置の製造工程中の要部断面図である。

【図41】図40に続く半導体装置の製造工程を示す要部断面図である。

【図42】図41に続く半導体装置の製造工程を示す要部断面図である。

【図43】図42に続く半導体装置の製造工程を示す要部断面図である。

【符号の説明】

30

1 A 半導体基板

絶縁層

2

半導体層(第1半導体層)

2 a

P 型 半 導 体 層 ( 第 1 半 導 体 層 )

2 b

N 型 半 導 体 層 ( 第 1 半 導 体 層 )

4

素子分離層

N型半導体層(第2半導体層、第1の領域)

P型半導体層(第2半導体層、第1の領域)

6

7

ゲート絶縁膜

7A high-k膜

40

ゲート電極

8 A

ポリシリコン膜

8 B

ゲート電極

8 C

ゲート電極

8 D

ゲート電極

低濃度N型不純物拡散層(第2の領域)

低濃度N型不純物拡散層(第2の領域)

1 0

低濃度P型不純物拡散層(第2の領域)

1 1

低濃度P型不純物拡散層(第2の領域)

1 2

1 3

高濃度N型不純物拡散層(第2の領域)

50

```

- 1 4 高濃度N型不純物拡散層(第2の領域)

- 1 5 高濃度P型不純物拡散層(第2の領域)

- 高濃度 P 型不純物拡散層(第2の領域) 1 6

- 1 7 サイドウォール

- サイドウォール 1 8

- ダミーゲート絶縁膜 2 1

- ダミーゲート電極 2 2

- 2 2 A ポリシリコン膜

- 2 3 酸化シリコン膜

- 2 4 レジスト膜

- 2 5 レジスト膜

- 2 6 絶縁層

- 2 7 半導体層

- 2 8 N型ポリシリコン膜

- 3 0 層間絶縁層

- プラグ 3 1

- 3 1 a 窒化チタン膜

- 31b タングステン膜

- プラグ 3 2

- 3 2 a 窒化チタン膜

- 32b タングステン膜

- 33 プラグ

- 3 3 a 窒化チタン膜

- 33b タングステン膜

- 3 4 プラグ

- 3 4 a 窒化チタン膜

- 34b タングステン膜

- 3 5 第 1 層 配 線

- 3 5 a 窒化チタン膜

- 3 5 b タングステン膜

- 3 5 c 窒化チタン膜

- 3 6 第 1 層 配 線

- 3 6 a 室化チタン膜

- 36 b タングステン膜

- 3 6 c 室化チタン膜

- 3 7 第 1 層 配 線

- 3 7 a 窒化チタン膜

- 37b タングステン膜

- 3 7 c 室化チタン膜

- 3 8 層間絶縁膜

- QN Nチャネル型のMIS・FET

- P チャネル型のM I S ・ F E T QΡ

20

30

## 【図1】

## 【図2】

【図3】

【図4】

【図6】

【図5】

【図7】

【図8】

【図10】

【図9】

【図11】

【図12】

【図13】

【図14】

【図15】

【図17】

【図16】

【図18】

【図19】

【図21】

【図20】

【図22】

【図23】

【図25】

【図24】

【図26】

【図28】

【図27】

【図29】

## 【図30】

## 【図31】

## 【図32】

## 【図33】

## 【図34】

## 【図35】

## 【図36】

**36**

## 【図37】

**2** 37

## 【図39】

**29** 39

## 【図38】

**38**

## 【図40】

**2** 40

【図41】

**Ø** 41

## 【図42】

## 【図43】

## フロントページの続き

(51) Int.CI.<sup>7</sup> F I テーマコード (参考)

H 0 1 L 29/78 6 1 7 J

F ターム(参考) 5F048 AA08 AB03 AC03 AC04 BA09 BA16 BB06 BB07 BB11 **BB16** BC06 BD04 BD05 BD07 BF07 BF11 BF16 BG07 BG13 BG14 CB07 DA23 DA25 DA27 5F110 AA01 AA02 AA09 BB04 BB05 CC02 CC09 DD05 DD13 EE02 EE04 EE09 EE31 EE45 EE47 FF01 FF02 FF03 FF09 FF29

FF35 GG02 GG12 GG32 GG36 GG52 HJ01 HJ13 HJ23 HL01 HL04 HL11 HL23 HL24 HM15 NN02 NN23 NN35 NN62 QQ17

QQ19