(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5820978号

(P5820978)

(45) 発行日 平成27年11月24日(2015.11.24)

(24) 登録日 平成27年10月16日(2015.10.16)

(51) Int.Cl.

HO2M 3/155 (2006.01)

F 1

HO2M 3/155

U

請求項の数 3 (全 25 頁)

(21) 出願番号 特願2010-265544 (P2010-265544)

(22) 出願日 平成22年11月29日 (2010.11.29)

(65) 公開番号 特開2012-120269 (P2012-120269A)

(43) 公開日 平成24年6月21日 (2012.6.21)

審査請求日 平成25年11月29日 (2013.11.29)

(73) 特許権者 314012076

パナソニックIPマネジメント株式会社

大阪府大阪市中央区城見2丁目1番61号

(74) 代理人 110001933

特許業務法人 佐野特許事務所

(72) 発明者 牧田 祐樹

大阪府守口市京阪本通2丁目5番5号 三

洋電機株式会社内

(72) 発明者 平田 俊之

大阪府守口市京阪本通2丁目5番5号 三

洋電機株式会社内

(72) 発明者 甲野藤 正明

大阪府守口市京阪本通2丁目5番5号 三

洋電機株式会社内

最終頁に続く

(54) 【発明の名称】電力変換回路

## (57) 【特許請求の範囲】

## 【請求項 1】

第1端と第2端との間に、一端とグランドラインにコイルと第1のスイッチング素子とを順に接続し、ダイオードとコンデンサとを他端を介して直列に接続した直列回路を第1のスイッチング素子に並列に接続して成ると共に、前記ダイオードと並列に第2のスイッチング素子を接続して第1のスイッチング素子のみを制御して前記一端に印加される電圧を昇圧して前記他端から出力する昇圧動作と、第2のスイッチング素子のみを制御して前記他端に印加される電圧を降圧して前記一端から出力する降圧動作とを成すチョッパ回路を複数前記一端と前記他端とを順に直列につないで構成し、少なくとも昇圧動作をまたは降圧動作のいずれか一方の動作の一部をバイパスするバイパスラインを備えることを特徴とする電力変換回路。

10

## 【請求項 2】

バイパスラインには当該バイパスラインの開閉を切替えるスイッチを設けることを特徴とする請求項1に記載の電力変換回路。

## 【請求項 3】

第1端に最も近いチョッパ回路は第2のスイッチング素子を備えないことを特徴とする請求項2に記載の電力変換回路。

## 【発明の詳細な説明】

## 【技術分野】

【0001】

20

本発明は、電圧を変換する電力変換回路に関し、特に、双方向に電力を伝送するものに関する。

【背景技術】

【0002】

近年、負荷を蓄電池に接続して利用するケースが増えてきている。例えば、負荷や系統（商用電源を供給するライン）を蓄電池に接続させるケースや、HEV、PHEV、EVで使用される蓄電池を、電動モータに接続させるケースが増えてきている。

【0003】

また蓄電池と負荷側における電圧の違いに対応するため、これらの間には、電圧を変換するコンバータ（電力変換回路）が設けられる。このようなコンバータの一例として、特許文献1には、昇降圧チョッパ回路を用いた昇降圧チョッパ装置が開示されている。

10

【0004】

この昇降圧チョッパ装置によれば、低電圧側から高電圧側へ電力を伝送するときは昇圧がなされ、高電圧側から低電圧側へ電力を伝送するときは降圧がなされる。これにより、双方向への電力伝送が適切に行われるようになっている。なお昇降圧チョッパ回路によれば、昇圧比や降圧比は、スイッチング素子の通流率（デューティ比 = スイッチ（スイッチング素子を含む）ONの時間 / (スイッチONの時間 + スイッチOFFの時間)）を通じて制御することが可能である。

【先行技術文献】

【特許文献】

20

【0005】

【特許文献1】特開2007-267582号公報

【発明の概要】

【発明が解決しようとする課題】

【0006】

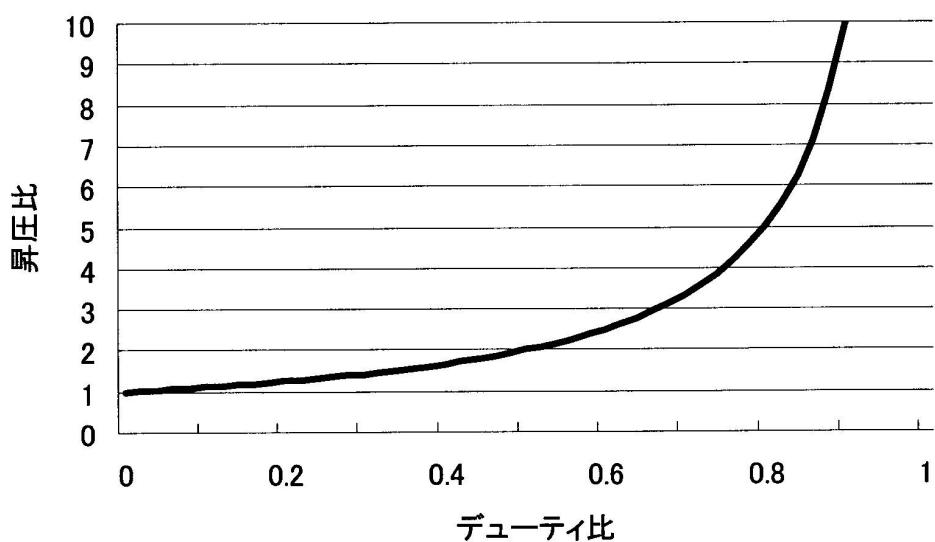

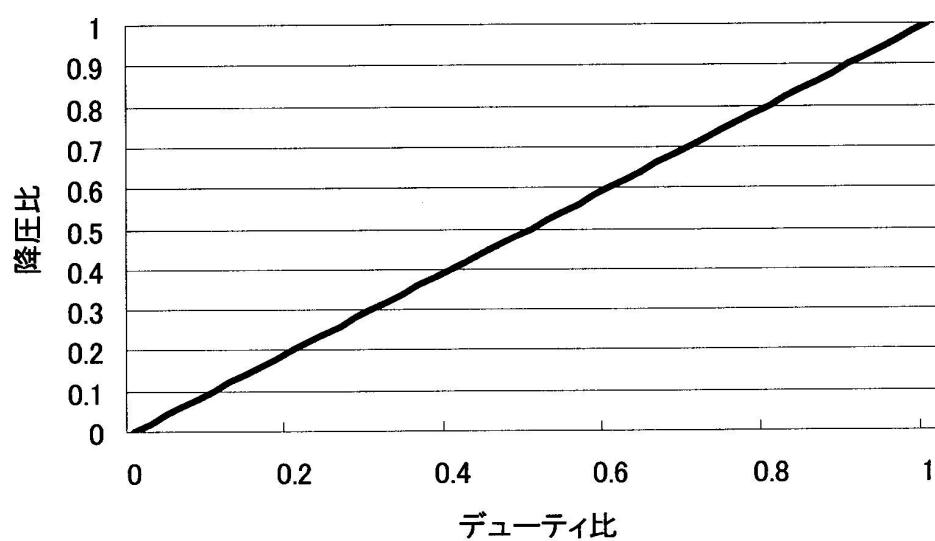

ところで昇降圧チョッパ回路において、昇圧比をR1、降圧比をR2とすると、これらは次の式で表される。

$$R1 = 1 / (1 - \dots)$$

$$R2 =$$

但し は、スイッチング素子のデューティ比を示す。また昇圧時におけるデューティ比と昇圧比の関係を表すグラフ、および降圧時におけるデューティ比と降圧比の関係を表すグラフを、図17に示す。

30

【0007】

上式および図17から明らかな通り、昇圧比R1の増分とデューティ比の増分との比（図17に示したグラフにおける、傾きに相当する）は、デューティ比が大きくなるに連れて著しく増大する。ここで高電圧側と低電圧側との電位差が大きい場合、低電圧側から高電圧側へ電力を伝送するにあたっては、昇圧比を高くする必要がある。しかし昇圧比を高くするために、デューティ比をあまりに大きくすると、例えばデューティ比に対する昇圧比の変動幅が大きくなるため、のズレに対する昇圧比の変動が大きくなり、昇圧動作の制御精度の低下を招くおそれがある。

40

【0008】

なお高い昇圧比を確保するための方策としては、例えば、トランスを用いたフライバック方式、フォワード方式、もしくはプッシュプル方式を採用することが考えられる。しかし何れの場合にも、素子耐圧などの観点から、双方向への電力伝送は容易ではない。

【0009】

そこで高い昇圧比を確保するための別の方策として、昇降圧チョッパ回路に、別の昇圧チョッパ回路を直列に接続したもの（便宜的に、「多段チョッパ回路」と称する）を利用することが考えられる。これにより、複数のチョッパ回路の各々をの小さい領域で動作させることができ、全体として、高い昇圧比での制御において制御精度の改善をする事が出来る。

50

## 【0010】

なお降圧比  $R_2$  の増分とデューティ比 の増分との比については、デューティ比の大きさに関わらずほぼ一定である。そのため、上述した多段チョッパ回路を利用する場合であっても、多くの場合は一部のチョッパ回路に降圧を行わせるだけで、降圧動作の制御精度を良好に維持することが可能である。

## 【0011】

しかし多段チョッパ回路を利用する場合、高電圧側から低電圧側への電力伝送にあたっては、不使用（本願では、降圧チョッパ回路として実質的に動作させないという意）のチョッパ回路をも電力が通ることになり、その分の無駄な電力損失が発生する。電力の伝送効率の観点から、このような電力損失は出来るだけ低減されることが望ましい。

10

## 【0012】

本発明は上述した問題に鑑み、双方向回路での電力損失を低減させることが可能となる電力変換回路の提供を目的とする。

## 【課題を解決するための手段】

## 【0013】

上記目的を達成するため、本発明にかかる電力変換回路は、第1端と第2端との間に、一端とグランドラインにコイルと第1のスイッチング素子とを順に接続し、ダイオードとコンデンサとを他端を介して直列に接続した直列回路を第1のスイッチング素子に並列に接続して成ると共に、前記ダイオードと並列に第2のスイッチング素子を接続して第1のスイッチング素子のみを制御して前記一端に印加される電圧を昇圧して前記他端から出力する昇圧動作と、第2のスイッチング素子のみを制御して前記他端に印加される電圧を降圧して前記一端から出力する降圧動作とを成すチョッパ回路を複数前記一端と前記他端とを順に直列につないで構成し、少なくとも昇圧動作をまたは降圧動作のいずれか一方の動作の一部をバイパスするバイパスラインを備える構成とする。

20

## 【0014】

本構成によれば、第2伝送動作を行うときに、第2回路を降圧回路として実質的に動作させないことで、電力損失を低減させることが可能となる。

## 【発明の効果】

## 【0026】

上述した通り、本発明に係る電力変換回路によれば、双方向回路での電力損失を低減させることが可能となる。

30

## 【図面の簡単な説明】

## 【0027】

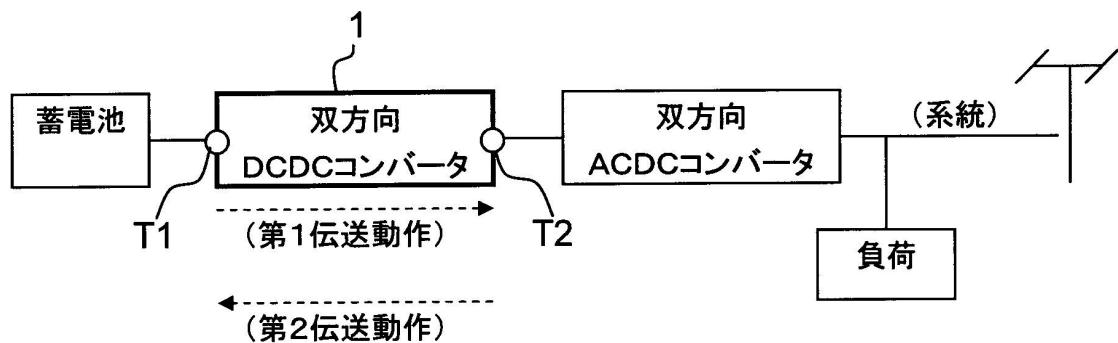

【図1】本発明の実施形態に係る双方向DCDCコンバータについての、使用形態の一例に関する説明図である。

【図2】本発明の第2実施形態に係る双方向DCDCコンバータの構成図である。

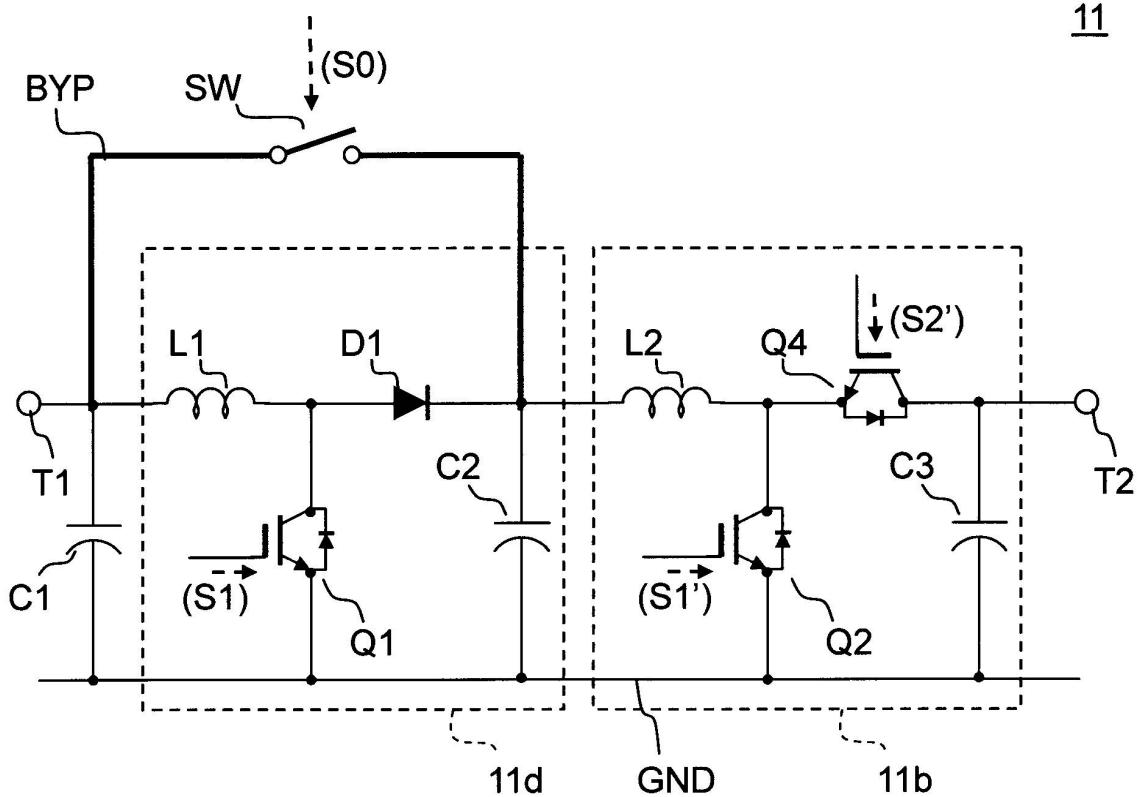

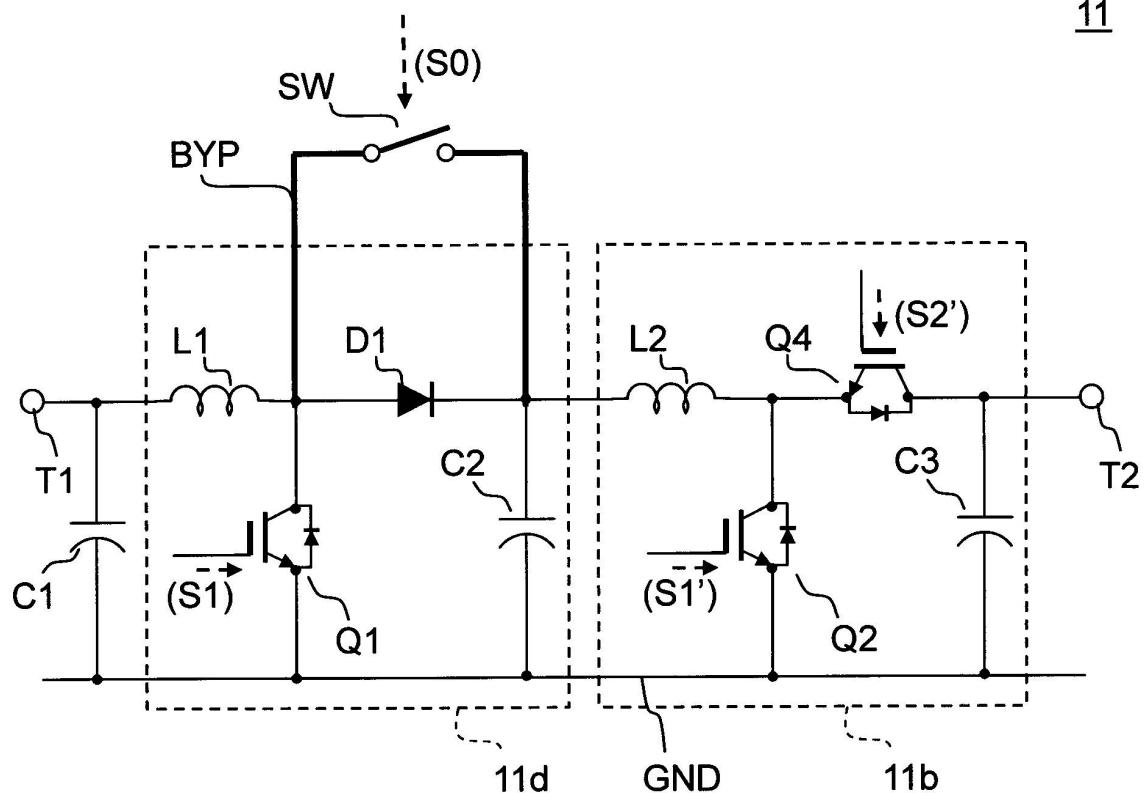

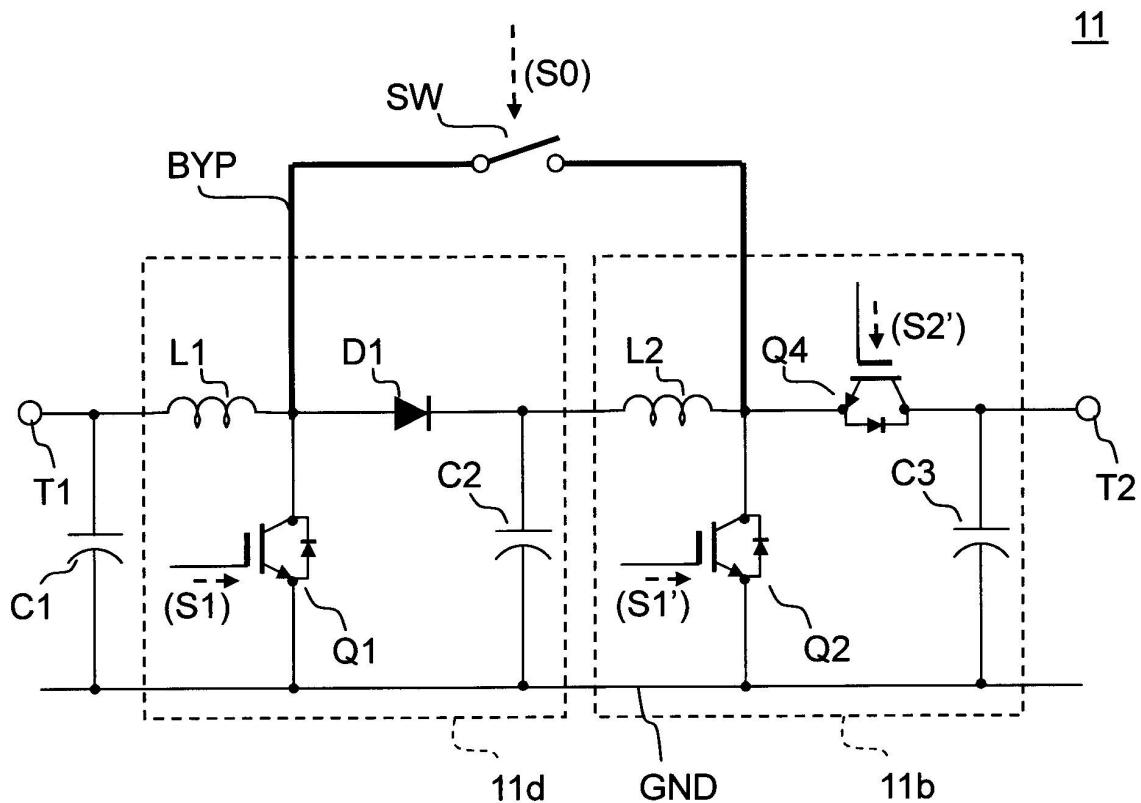

【図3】本発明の第2実施形態に係る電力伝送部の構成図である。

【図4】本発明の第2実施形態に係る各信号のタイミングチャートである。

【図5】パルス信号生成回路の構成図である。

【図6】本発明の第3実施形態に係る双方向DCDCコンバータの構成図である。

40

【図7】本発明の第3実施形態に係る電力伝送部の構成図である。

【図8】本発明の第3実施形態に係る各信号のタイミングチャートである。

【図9】本発明の第4実施形態に係る電力伝送部の構成図である。

【図10】バイパスラインが設けられる形態に関する説明図である。

【図11】バイパスラインが設けられる形態に関する説明図である。

【図12】バイパスラインが設けられる形態に関する説明図である。

【図13】バイパスラインが設けられる形態に関する説明図である。

【図14】バイパスラインが設けられる形態に関する説明図である。

【図15】バイパスラインが設けられる形態に関する説明図である。

【図16】バイパスラインに設けられるスイッチの形態に関する説明図である。

50

【図17】昇降圧チョッパ回路における、デューティ比と昇圧比または降圧比の関係を表すグラフである。

【発明を実施するための形態】

【0028】

本発明の実施形態について、第1実施形態から第4実施形態の各々を例に挙げて、以下に説明する。

【0029】

1. 第1実施形態

まず第1実施形態について、双方向DCDCコンバータ（以下、「コンバータ1」と略記することがある）を挙げて説明する。コンバータ1は、電圧の異なる装置等の間、すなわち低電圧側と高電圧側の間に設けられて使用される。より具体的にはコンバータ1は、端子T1（第1端）と端子T2（第2端）が設けられており、端子T1が低電圧側に接続され、端子T2が高電圧側に接続される。一例としては、図1に示すように、端子T1が蓄電池に接続され、端子T2が、系統に繋がった双方向ACDCコンバータに接続される。

【0030】

またコンバータ1は、より具体的には他の実施形態として詳細に説明するが、次のような構成となっている。コンバータ1は、端子T1と端子T2の間に複数のチョッパ回路を備えており、端子T1に入力された電力を昇圧させた上で端子T2から出力する第1伝送動作、および、端子T2に入力された電力を降圧させた上で端子T1から出力する第2伝送動作、を行う。

【0031】

このように第1伝送動作や第2伝送動作がなされることにより、低電圧側と高電圧側の間で、双方向への電力伝送が適切に行われるようになっている。なおコンバータ1（後述する、主制御部12）は、低電圧側から高電圧側へ電力を伝送すべき期間（第1伝送動作を行うべき期間）の情報、および高電圧側から低電圧側へ電力を伝送すべき期間（第2伝送動作を行うべき期間）の情報を取得するようになっている。

【0032】

また前記複数のチョッパ回路は、端子T1から端子T2へ向かう方向への昇圧動作、および、端子T2から端子T1へ向かう方向への降圧動作をするよう形成された第1回路と、端子T1から端子T2へ向かう方向への昇圧動作をするよう形成された第2回路との各々を少なくとも一つずつ含んでいる。そして第1伝送動作を行うときは、第1回路および第2回路が、第1端から第2端へ向かう方向への前記昇圧動作を行う。また第2伝送動作を行うときは、第1回路および第2回路が第2端から第1端へ向かう方向への前記降圧動作を行い、少なくとも第2回路の一つは、第2回路のみでは実質的に降圧動作を行わない。

【0033】

このような構成となっているため、コンバータ1において、第2回路が双方向で昇降圧動作するように形成されている場合は、第2伝送動作を行うときに、第2回路に実質的に降圧動作を行わせない。そのため、第2回路は降圧動作した場合の出力を出力しないので、当該回路における降圧のためのスイッチング動作等による電力損失が回避され、その結果、コンバータ1は電力損失を低減させることが可能となっている。また、第2回路が端子T1から端子T2への単方向の昇圧動作をするように構成されている場合は、第1伝送動作を行うときに、効率改善が図られる場合がある。

【0034】

第2回路に実質的に降圧動作を行わせないようにする形態の例は、後述する第2から第4実施形態の説明にて明らかとなる。なお第2および第4実施形態では、降圧回路をバイパスすることで降圧回路の入出力をショートさせる形態（形式的な降圧動作（スイッチング動作等）がなされていても、ショートされているために降圧動作とはならない場合を含む）が採用されている。また第3実施形態では、降圧回路のスイッチング素子を常時オン

10

20

30

40

50

とする形態が採用されている。

【0035】

## 2. 第2実施形態

次に本発明の第2実施形態について、以下に説明する。

【0036】

### [ 双方向 D C D C コンバータの構成等について ]

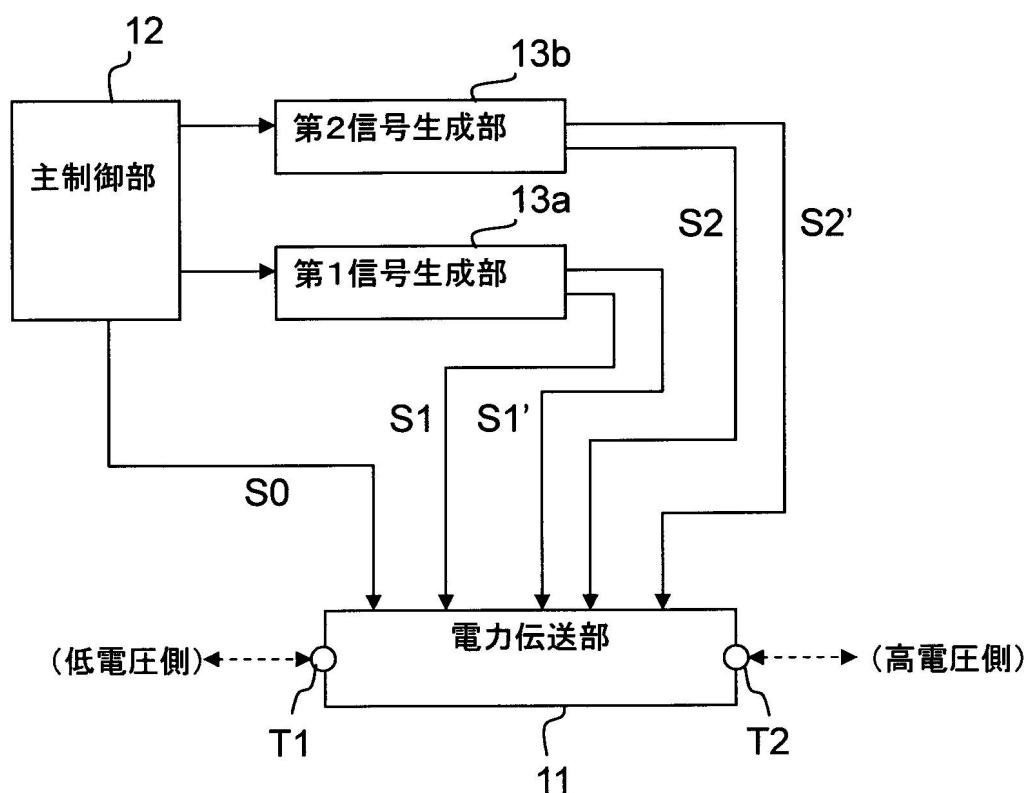

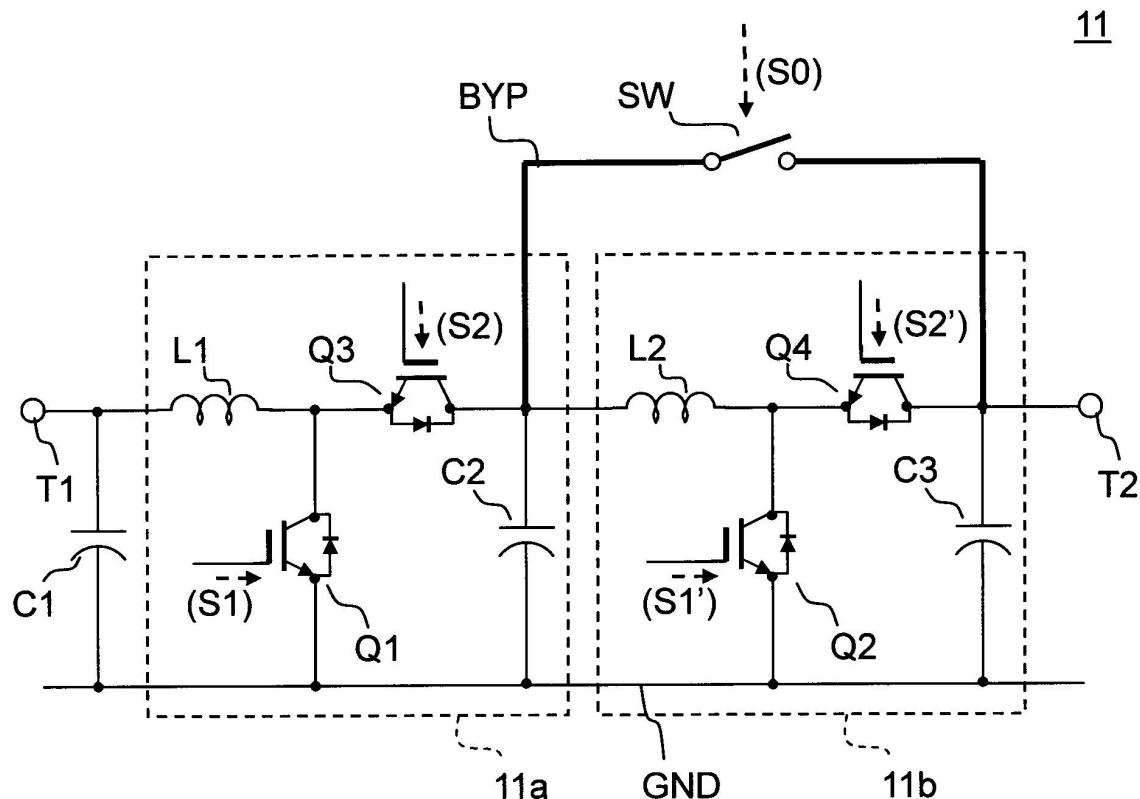

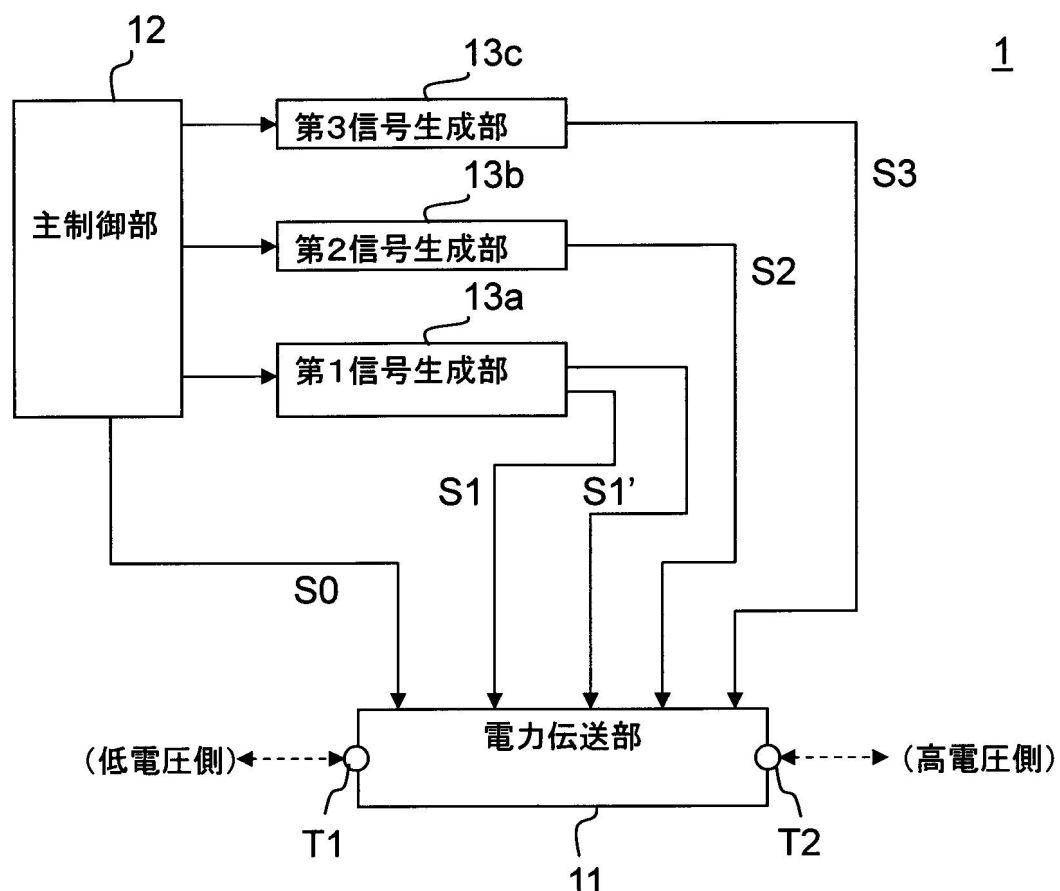

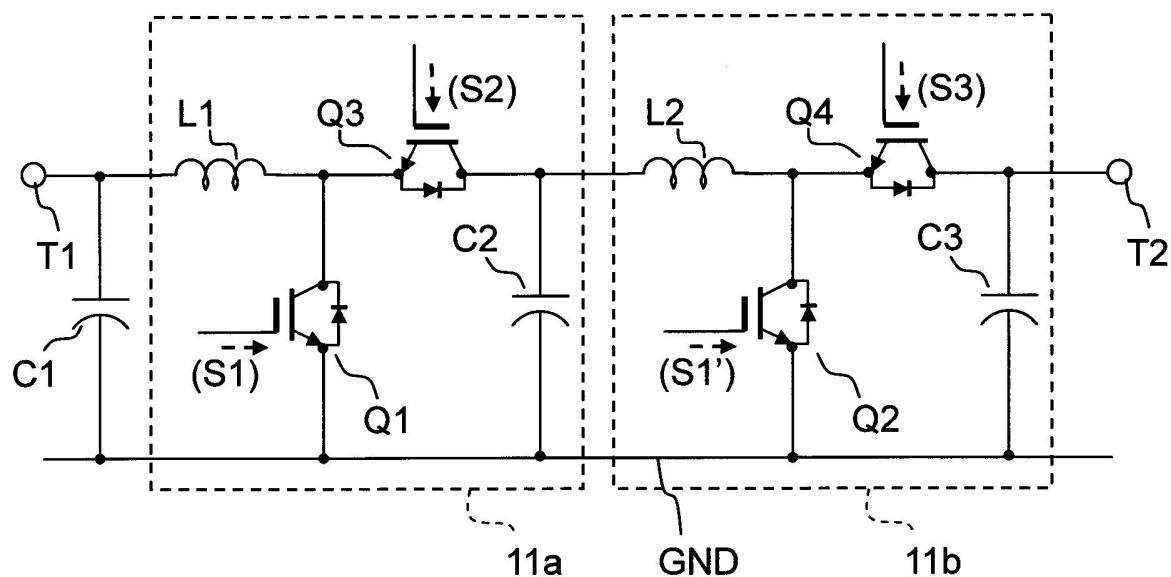

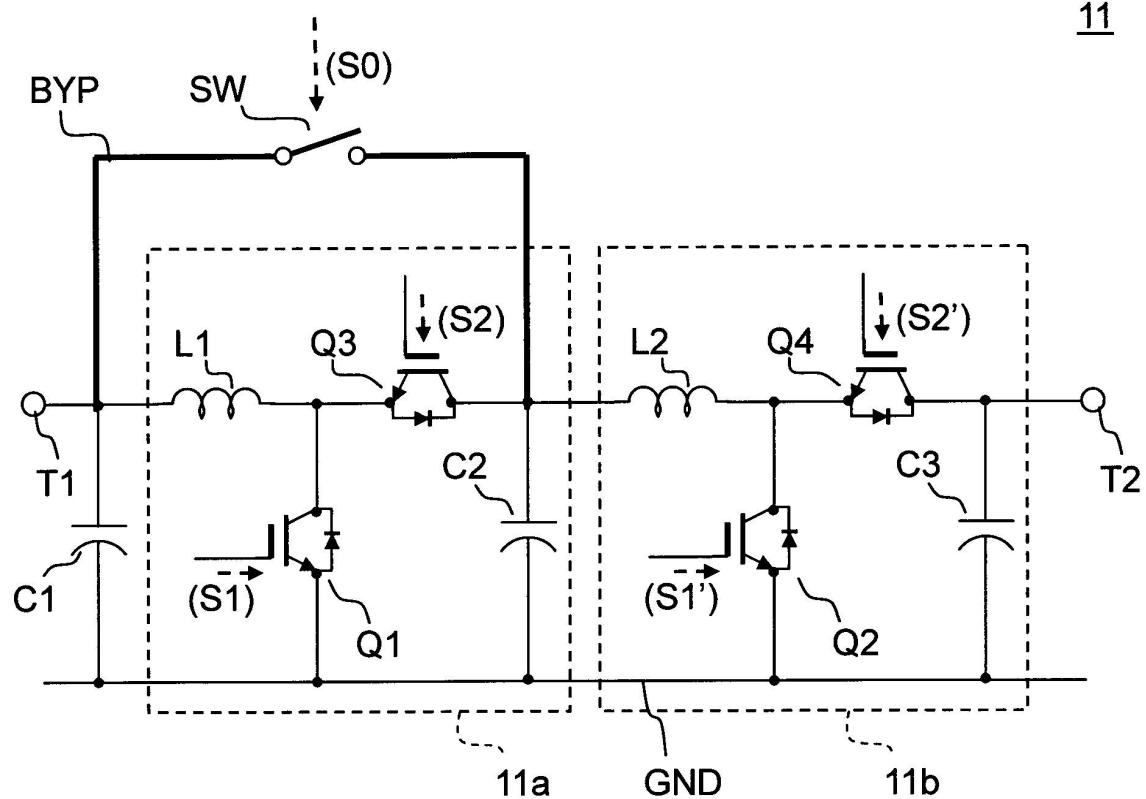

図2は、コンバータ1の構成に関するブロック図である。本図に示すようにコンバータ1は、電力伝送部11、主制御部12、第1信号生成部13a、および第2信号生成部13bを備えている。また図3は、電力伝送部11の構成図(回路図)である。

【0037】

10

電力伝送部11は、低電圧側に接続される端子T1と、高電圧側に接続される端子T2が設けられており、これらの端子間ににおいて、双方向に電力の伝送が可能となっている。また電力伝送部11においては、図3に示すように、複数個(ここでは一例として、2個とする)の昇降圧チョッパ回路(11a、11b)が直列に接続されている。

【0038】

昇降圧チョッパ回路11aは、コイルL1、第1のスイッチング素子に相当するスイッチング素子(IGBT)Q1、第2のスイッチング素子に相当するスイッチング素子(IGBT)Q3、およびコンデンサC2が、それぞれ適切に接続されて形成されている。

【0039】

20

より具体的には、コイルL1の一端は、スイッチング素子Q1のコレクタとスイッチング素子Q3のエミッタに接続されている。またスイッチング素子Q3のコレクタは、コンデンサC2の一端に接続されている。またスイッチング素子Q1のエミッタとコンデンサC2の他端は、グランドラインGND(通常、0Vに設定される)に接続されている。なお各スイッチング素子(Q1、Q3)におけるエミッタとコレクタは、ダイオード(アノードがエミッタ側となっている)を介して接続されている。なお、コイルL1の他端は端子T1に接続されている。

【0040】

またスイッチング素子Q1のON/OFF(コレクタ-エミッタ間における導通と非導通)の切替は、後述する信号S1によって制御される。またスイッチング素子Q3のON/OFFの切替は、後述する信号S2によって制御される。

30

【0041】

昇降圧チョッパ回路11aは、スイッチング素子Q3がOFFにされ、スイッチング素子Q1によるチョッピング(ON/OFFの高速切替による、電力の導通と遮断の繰返し)が行われるとき、コイルL1においてエネルギーの蓄積と放出を繰り返す。その結果、昇降圧チョッパ回路11aは、一端(端子T1の側)に入力された電力を昇圧させた上で、他端(昇降圧チョッパ回路11bの側)から出力する動作(昇圧動作)を行う。

【0042】

40

一方、昇降圧チョッパ回路11aは、スイッチング素子Q1がOFFにされ、スイッチング素子Q3によるチョッピングが行われるとき、コイルL1においてエネルギーの蓄積と放出を繰り返す。その結果、昇降圧チョッパ回路11aは、一端(昇降圧チョッパ回路11bの側)に入力された電力を降圧させた上で、他端(端子T1の側)から出力する動作(降圧動作)を行う。

【0043】

上述の説明から明らかなように、スイッチング素子Q1は昇圧用スイッチング素子に、スイッチング素子Q3は降圧用スイッチング素子に、それぞれ該当している。なお昇降圧チョッパ回路において、昇圧動作および降圧動作が可能であることは公知であるため、この点に関するより詳細な説明については省略する。

【0044】

また昇降圧チョッパ回路11bは、コイルL2、第1のスイッチング素子に相当するスイッチング素子(IGBT)Q2、第2のスイッチング素子に相当するスイッチング素子(

50

I G B T ) Q 4 、およびコンデンサ C 3 が、それぞれ適切に接続されて形成されている。

【 0 0 4 5 】

より具体的には、コイル L 2 の一端は、スイッチング素子 Q 2 のコレクタとスイッチング素子 Q 4 のエミッタに接続されている。またスイッチング素子 Q 4 のコレクタは、コンデンサ C 3 の一端に接続されている。またスイッチング素子 Q 2 のエミッタとコンデンサ C 3 の他端は、グランドライン G N D に接続されている。なお各スイッチング素子 ( Q 2 、 Q 4 ) におけるエミッタとコレクタは、ダイオード ( アノードがエミッタ側となっている ) を介して接続されている。なお、コイル L 2 の他端はスイッチング素子 Q 3 のコレクタに接続され、スイッチング素子 Q 4 のコレクタは端子 T 2 にも接続されている。

【 0 0 4 6 】

なおスイッチング素子 Q 2 の O N / O F F の切替は、後述する信号 S 1 ' によって制御される。またスイッチング素子 Q 4 の O N / O F F の切替は、後述する信号 S 2 ' によって制御される。

【 0 0 4 7 】

昇降圧チョッパ回路 1 1 b は、スイッチング素子 Q 4 が O F F にされ、スイッチング素子 Q 2 によるチョッピングが行われるとき、コイル L 2 においてエネルギーの蓄積と放出を繰り返す。その結果、昇降圧チョッパ回路 1 1 b は、一端 ( 昇降圧チョッパ回路 1 1 a の側 ) に入力された電力を昇圧させた上で、他端 ( 端子 T 2 の側 ) から出力する動作 ( 昇圧動作 ) を行う。上述の説明から明らかのように、スイッチング素子 Q 2 は昇圧用スイッチング素子に該当している。

【 0 0 4 8 】

そして更に、端子 T 1 はコンデンサ C 1 の一端に接続されており、コンデンサ C 1 の他端はグランドライン G N D に接続されている。また端子 T 2 とスイッチング素子 Q 4 との間、およびコイル L 2 とスイッチング素子 Q 3 との間には、それぞれ、バイパスライン B Y P の一端と他端が接続されている。

【 0 0 4 9 】

すなわち昇降圧チョッパ回路 1 1 b と並列になるように、バイパスライン B Y P が設けられている。バイパスライン B Y P は、バイパスライン B Y P の開閉を切替えるスイッチ S W が設けられており、スイッチ S W が閉じられたとき、両端間が導通した状態となる。

【 0 0 5 0 】

なおバイパスライン B Y P は、電力の通過に伴う電力損失が極力小さくなるように配慮されている。バイパスライン B Y P を電力が通過するときの電力損失は、昇降圧チョッパ回路 1 1 b を電力が通過するときの電力損失に比べて、大幅に小さくなっている。なおスイッチ S W の開閉は、後述する信号 S 0 によって制御される。

【 0 0 5 1 】

図 2 に戻り、主制御部 1 2 は、第 1 伝送動作を行うべき期間および第 2 伝送動作を行うべき期間の、何れの期間であるかに応じて、コンバータ 1 の各部を制御する。より具体的には、主制御部 1 2 は、信号 S 0 を出力してスイッチ S W の開閉を制御するとともに、各信号を生成させるように、第 1 信号生成回路 1 3 a および第 2 信号生成回路 1 3 b を制御する。

【 0 0 5 2 】

第 1 信号生成部 1 3 a は、主制御部 1 2 の指示に応じて信号 S 1 および信号 S 1 ' を生成し、スイッチング素子 Q 1 に信号 S 1 を、スイッチング素子 Q 2 に信号 S 1 ' を、それぞれ出力する。また第 2 信号生成部 1 3 b は、主制御部 1 2 の指示に応じて信号 S 2 および信号 S 2 ' を生成し、スイッチング素子 Q 3 に信号 S 2 を、スイッチング素子 Q 4 に信号 S 2 ' を、それぞれ出力する。各信号の状態については、改めて説明する。なお信号 S 1 ' は信号 S 1 と同じであっても良い。また信号 S 2 ' は信号 S 2 と同じであっても良い。

【 0 0 5 3 】

[ 双方向 D C D C コンバータの動作等について ]

10

20

30

40

50

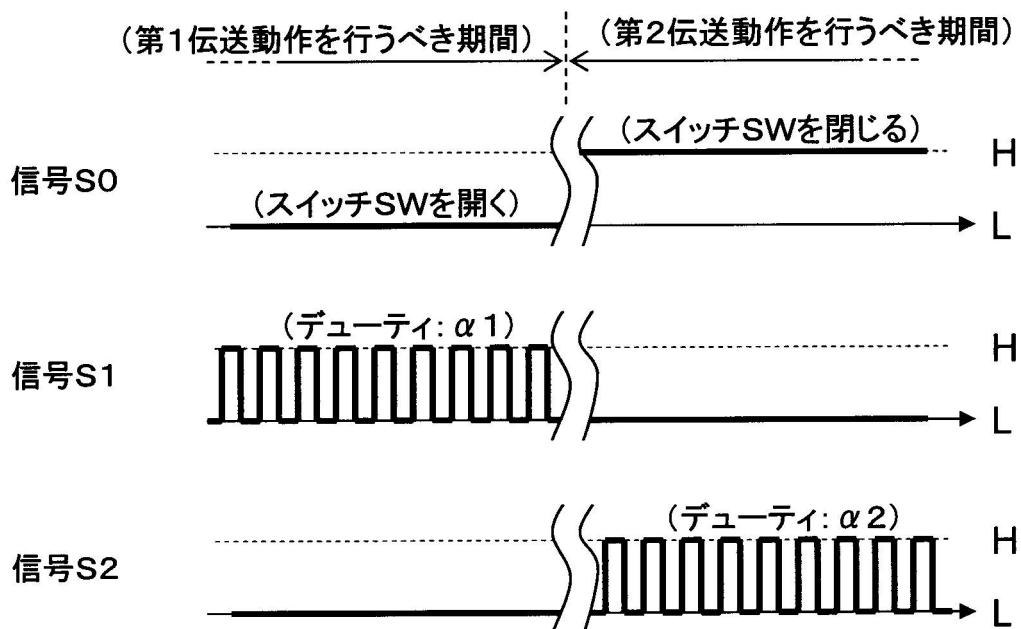

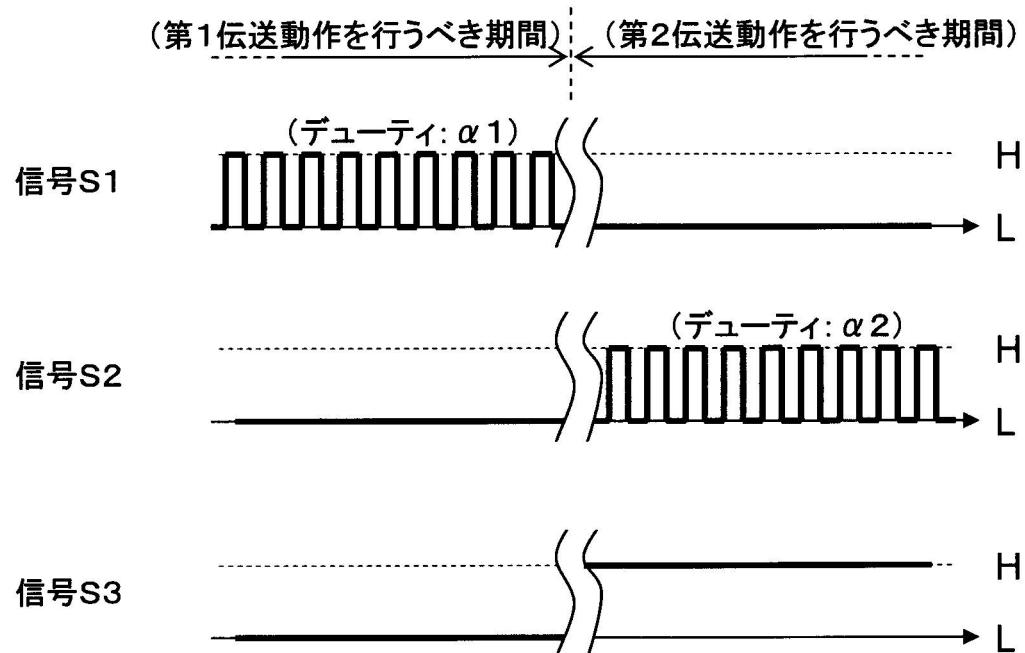

次に、コンバータ 1 の動作についてより詳細に説明する。図 4 は、信号 S 0 、信号 S 1 および信号 S 2 のタイミングチャートを表している。なお当該タイミングチャート（図 8 のものも同様）において、縦軸は電圧を表し、横軸は時間を表している。また信号 S 1 、および信号 S 2 ' のタイミングチャートについては、それぞれ信号 S 1 および信号 S 2 のものと同等（デューティ比等は異なっていても構わない）であるため、ここでは省略する。本図に示すように第 1 信号生成部 1 3 a は、第 1 伝送動作を行うべき期間において、H レベルの期間を ON 期間（スイッチング素子を ON にする期間）としたパルス信号を、信号 S 1 （デューティ比を 1 とする）および信号 S 1 ' （デューティ比を 1 ' とする）として生成する。また第 1 信号生成部 1 3 a は、第 2 伝送動作を行うべき期間において、L レベルに固定された信号を、信号 S 1 および信号 S 1 ' として生成する。

10

#### 【 0 0 5 4 】

一方、第 2 信号生成部 1 3 b は、第 1 伝送動作を行うべき期間において、L レベルに固定された信号を、信号 S 2 および信号 S 2 ' として生成する。また第 2 信号生成部 1 3 b は、第 2 伝送動作を行うべき期間において、H レベルの期間を ON 期間としたパルス信号を、信号 S 2 （デューティ比を 2 とする）および信号 S 2 ' （デューティ比を 2 ' とする）として生成する。

#### 【 0 0 5 5 】

また主制御部 1 2 は、第 1 伝送動作を行うべき期間においてはスイッチ SW が開くように、第 2 伝送動作を行うべき期間においてはスイッチ SW が閉じるように、信号 S 0 を生成する。このように生成された各信号（S 0 、 S 1 、 S 1 ' 、 S 2 、 S 2 ' ）を受け、電力伝送部 1 1 は次のように動作する。

20

#### 【 0 0 5 6 】

まず第 1 伝送動作を行うべき期間において、昇降圧チョッパ回路 1 1 a は、端子 T 1 に入力された電力を昇降圧チョッパ回路 1 1 b へ伝送する昇圧動作を行う。また昇降圧チョッパ回路 1 1 b は、昇降圧チョッパ回路 1 1 a から入力された電力を端子 T 2 へ伝送する昇圧動作を行う。なおこのとき、スイッチ SW は開いているため、電力はバイパスライン B Y P を通らない。これらの昇圧動作が並行してなされる結果、第 1 伝送動作が達成される。

#### 【 0 0 5 7 】

第 1 伝送動作における昇圧比は、各昇降圧チョッパ回路（1 1 a 、 1 1 b ）の昇圧動作における昇圧比の積で表される。なお第 1 伝送動作の実行時においては、端子 T 2 から出力される出力電圧が目標電圧（例えば、系統の標準電圧）に近づくように、デューティ比 1 および 1 ' （昇圧比を決める要素）が調節される。

30

#### 【 0 0 5 8 】

次に第 2 伝送動作を行うべき期間において、バイパスライン B Y P は導通状態となるため、端子 T 2 に入力された電力は、バイパスライン B Y P を通って、昇降圧チョッパ回路 1 1 a へ伝送される。その結果、端子 T 2 から昇降圧チョッパ回路 1 1 a へ電力を伝送するにあたり、当該電力が昇降圧チョッパ回路 1 1 b を通ると仮定した場合に比べ、電力の損失は大幅に低減される。

40

#### 【 0 0 5 9 】

また昇降圧チョッパ回路 1 1 a は、バイパスライン B Y P から入力された電力を端子 T 1 へ伝送する降圧動作を行う。その結果、第 2 伝送動作が達成される。第 2 伝送動作の実行時においては、端子 T 1 から出力する出力電圧が目標電圧（例えば、蓄電池の標準電圧）に近づくように、デューティ比 2 （降圧比を決める要素）が調節される。

#### 【 0 0 6 0 】

なお、出力電圧が目標電圧に近づくようにデューティ比を調節する手段としては、種々の手段が採用され得る。一例としては、図 5 に示すようなパルス信号生成回路 2 0 を設けることによって、上述したデューティ比の調整が可能となる。

#### 【 0 0 6 1 】

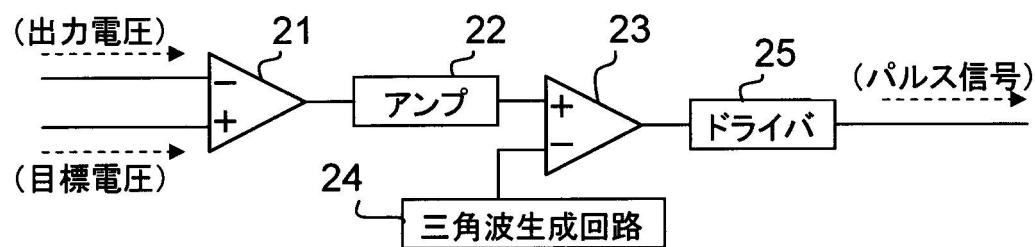

図 5 に示すように、パルス信号生成回路 2 0 は、減算回路 2 1 、アンプ 2 2 、コンパレ

50

ータ 2 3、三角波生成回路 2 4、およびドライバ 2 5 を備えている。減算回路 2 1 は、出力電圧が反転入力端子に、目標電圧が非反転入力端子に、それぞれ入力されるようになっている。

【 0 0 6 2 】

減算回路 2 1 から出力された信号はアンプ 2 2 によって増幅され、コンパレータ 2 3 の非反転入力端子に入力される。またコンパレータ 2 3 の反転入力端子には、三角波生成回路 2 4 によって生成された三角波が入力される。ドライバ 2 5 は、コンパレータ 2 3 から出力された信号に応じて、スイッチング素子を駆動するパルス信号を生成して出力する。

【 0 0 6 3 】

パルス信号生成回路 2 0 によれば、出力電圧が目標電圧より小さいときはデューティ比を増やすように、出力電圧が目標電圧より大きいときはデューティ比を減らすように、パルス信号が生成される。その結果、第 1 伝送動作の実行時（昇圧動作がなされるとき）、および第 2 伝送動作の実行時（降圧動作がなされるとき）において、出力電圧が目標電圧に近づくようにデューティ比を調節することが可能となる。

【 0 0 6 4 】

なおデューティ比の調整手法としては、その他の様々な形態を採用することが可能であり、例えば、三角波の代わりに鋸波が使用されるようにしても構わない。

【 0 0 6 5 】

【 各チョッパ回路の役割について 】

上述したように電力伝送部 1 1 には、チョッパ回路として、昇降圧チョッパ回路 1 1 a および昇降圧チョッパ回路 1 1 b が用いられている。そして昇降圧チョッパ回路 1 1 a は、第 1 実施形態の説明において言及した第 1 回路としての役割を果している。一方、昇降圧チョッパ回路 1 1 b は、第 1 実施形態の説明において言及した第 2 回路としての役割を果している。

【 0 0 6 6 】

コンバータ 1 は、第 1 伝送動作の実行時には、第 1 回路と第 2 回路の両方に昇圧動作を行わせる。そのためコンバータ 1 によれば、全体として高い昇圧比を確保しつつも、各回路のデューティ比の増大が出来るだけ抑えられ、昇圧動作の制御精度を良好に維持することが可能となっている。

【 0 0 6 7 】

またコンバータ 1 は、第 2 伝送動作の実行時には、電力が第 2 回路と並列であるバイパスライン B Y P を通るようにしつつ、第 1 回路に降圧動作を行わせる。そのためコンバータ 1 によれば、第 2 回路をショートさせて電力の損失を低減させることが可能となっている。

【 0 0 6 8 】

また第 1 回路および第 2 回路の何れについても昇降圧チョッパ回路を用いる場合、コンバータ 1 の製造に際して、第 1 回路と第 2 回路の部品を共通化することが可能であり、製造効率の観点から有利となる。但し、第 2 回路として、降圧動作の機能を有していない一般的な昇圧チョッパ回路を用いても構わない。

【 0 0 6 9 】

3 . 第 3 実施形態

次に、本発明の第 3 実施形態について説明する。なお第 3 実施形態の説明にあたっては、第 2 実施形態と異なる点に重点を置き、第 2 実施形態と同等の点については、説明を省略することがある。

【 0 0 7 0 】

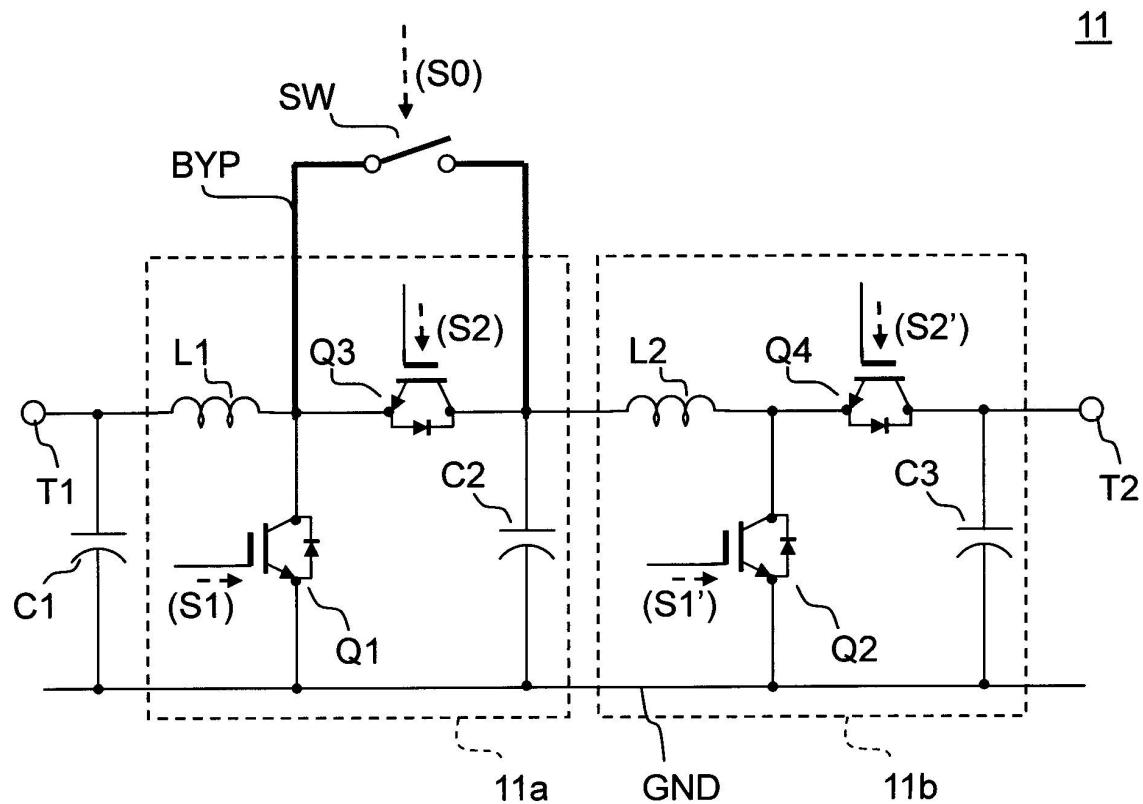

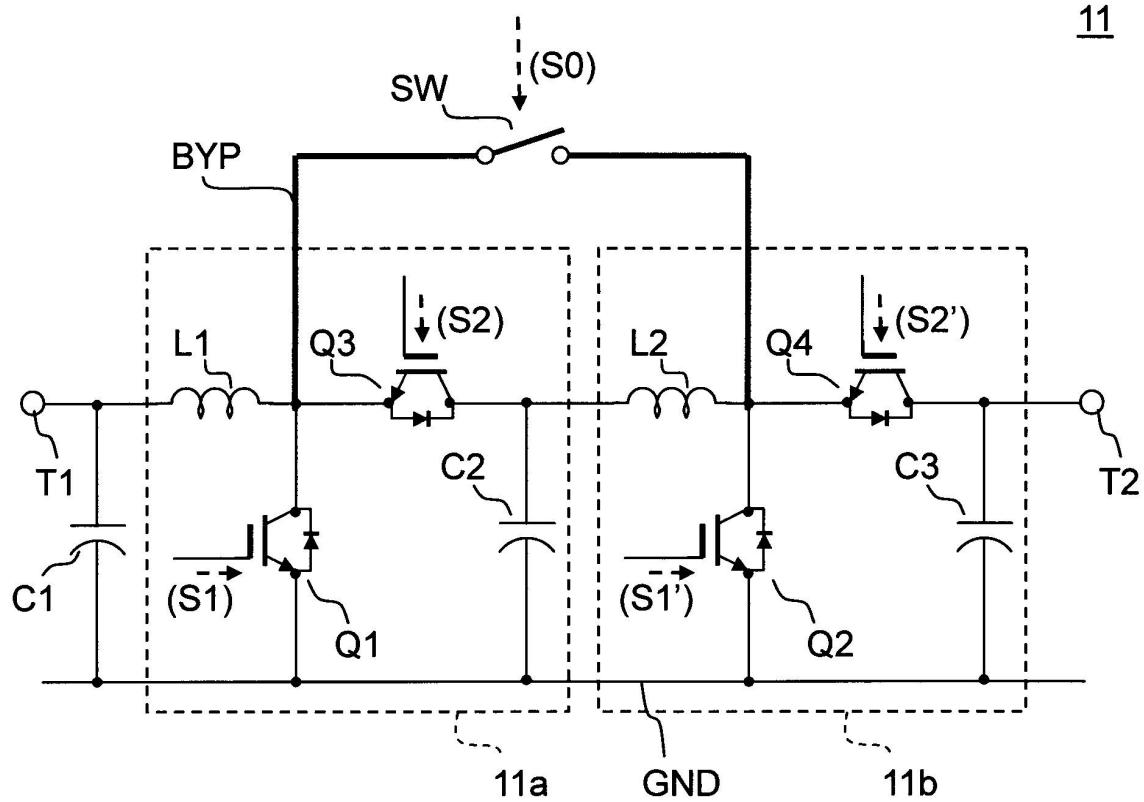

図 6 は、コンバータ 1 の構成に関するブロック図である。本図に示すようにコンバータ 1 は、電力伝送部 1 1 、主制御部 1 2 、第 1 信号生成部 1 3 a 、第 2 信号生成部 1 3 b 、および第 3 信号生成部 1 3 c を備えている。また図 7 は、電力伝送部 1 1 の構成図である。

【 0 0 7 1 】

10

20

30

40

50

電力伝送部 11 は、低電圧側に設けられた端子 T1 と、高電圧側に設けられた端子 T2 が設けられており、これらの端子間において、双方向に電力の伝送が可能となっている。また電力伝送部 11 においては、複数個（ここでは一例として、2 個とする）の昇降圧チョッパ回路（11a、11b）が直列に接続されている。これらの点は、第 2 実施形態の場合と同様である。但し本実施形態では、スイッチング素子 Q4 の ON/OFF の切替は、後述する信号 S3 によって制御される。また第 2 実施形態では設けられていたバイパスライン BYP は、本実施形態では設けられていない。

#### 【0072】

主制御部 12 は、第 1 伝送動作を行うべき期間および第 2 伝送動作を行うべき期間の何れの期間であるかに応じて、各信号を生成させるように、第 1 信号生成回路 13a、第 2 信号生成回路 13b、および第 3 信号生成回路 13c を制御する。

10

#### 【0073】

第 1 信号生成部 13a は、主制御部 12 の指示に応じて信号 S1 および信号 S1' を生成し、信号 S1 をスイッチング素子 Q1 に、信号 S1' をスイッチング素子 Q2 にそれぞれ出力する。また第 2 信号生成部 13b は、主制御部 12 の指示に応じて信号 S2 を生成し、スイッチング素子 Q3 に出力する。また第 3 信号生成部 13c は、主制御部 12 の指示に応じて信号 S3 を生成し、スイッチング素子 Q4 に出力する。

#### 【0074】

次に、コンバータ 1 の動作についてより詳細に説明する。図 8 は、信号 S1（信号 S1' も同様）、信号 S2 および信号 S3 のタイミングチャートを表している。本図に示すように第 1 信号生成部 13a は、第 1 伝送動作を行うべき期間において、H レベルの期間を ON 期間としたパルス信号を、信号 S1（デューティ比を 1 とする）および信号 S1'（デューティ比を 1' とする）として生成する。また第 1 信号生成部 13a は、第 2 伝送動作を行うべき期間において、L レベルに固定された信号を、信号 S1 および信号 S1' として生成する。

20

#### 【0075】

第 2 信号生成部 13b は、第 1 伝送動作を行うべき期間において、L レベルに固定された信号を、信号 S2 として生成する。また第 2 信号生成部 13b は、第 2 伝送動作を行うべき期間において、H レベルの期間を ON 期間としたパルス信号（デューティ比を 2 とする）を、信号 S2 として生成する。

30

#### 【0076】

第 3 信号生成部 13c は、第 1 伝送動作を行うべき期間において、L レベルに固定された信号を、信号 S3 として生成する。また第 3 信号生成部 13c は、第 2 伝送動作を行うべき期間において、H レベルに固定された信号を、信号 S3 として生成する。このように生成された各信号（S1、S1'、S2、S3）を受け、電力伝送部 11 は次のように動作する。

#### 【0077】

まず第 1 伝送動作を行うべき期間において、昇降圧チョッパ回路 11a は、端子 T1 に入力された電力を昇降圧チョッパ回路 11b へ伝送する昇圧動作を行う。また昇降圧チョッパ回路 11b は、昇降圧チョッパ回路 11a から入力された電力を端子 T2 へ伝送する昇圧動作を行う。これらの昇圧動作が並行してなされる結果、第 1 伝送動作が達成される。

40

#### 【0078】

第 1 伝送動作における昇圧比は、各昇降圧チョッパ回路（11a、11b）の昇圧動作における昇圧比の積で表される。なお第 1 伝送動作の実行時においては、端子 T2 から出力する出力電圧が目標電圧に近づくように、デューティ比 1 および 1' が調節される。

#### 【0079】

次に第 2 伝送動作を行うべき期間において、信号 S3 は H レベルに固定されるため、スイッチング素子 Q4 は ON に固定される。この状態では、端子 T2 に入力された電力は、

50

スイッチング素子 Q 4 とコイル L 2 を通って、昇降圧チョッパ回路 11 a へ伝送される。

【 0 0 8 0 】

なおこのとき、スイッチング素子 Q 4 は ON に固定されるため、スイッチング損失による電力損失は発生しない。そのため、端子 T 2 から昇降圧チョッパ回路 11 a へ電力を伝送するにあたり、スイッチング素子 Q 4 がスイッチングを行うと仮定した場合に比べ、電力の損失は低減される。

【 0 0 8 1 】

また昇降圧チョッパ回路 11 a は、昇降圧チョッパ回路 11 b から入力された電力を端子 T 1 へ伝送する降圧動作を行う。その結果、第 2 伝送動作が達成される。第 2 伝送動作の実行時においては、端子 T 1 から出力する出力電圧が目標電圧に近づくように、デューティ比 2 が調節される。

10

【 0 0 8 2 】

また以上の説明から明らかなように、本実施形態においては、昇降圧チョッパ回路 11 a が第 1 回路としての役割を果しており、昇降圧チョッパ回路 11 b が第 2 回路としての役割を果している。また本実施形態のコンバータ 1 は、第 2 伝送動作の実行時において、第 2 回路の降圧用スイッチング素子を ON に固定しつつ、第 1 回路に降圧動作を行わせる。そのため、第 2 回路のスイッチング動作に伴う電力の損失を低減させることができるとなっている。

【 0 0 8 3 】

なお本実施形態のコンバータ 1 は、第 2 実施形態のものに比べ、バイパスライン B Y P を設ける必要が無いために、より簡潔な構成とすることが可能である。また必要に応じて信号 S 2 と信号 S 3 の出力先を変更することにより、昇降圧チョッパ回路 11 a を第 2 回路に変更することや、昇降圧チョッパ回路 11 b を第 1 回路に変更することも可能である。

20

【 0 0 8 4 】

4. 第 4 実施形態

次に、本発明の第 4 実施形態について説明する。なお第 4 実施形態の説明にあたっては、第 2 実施形態と異なる点に重点を置き、第 2 実施形態と同等の点については、説明を省略することがある。

【 0 0 8 5 】

30

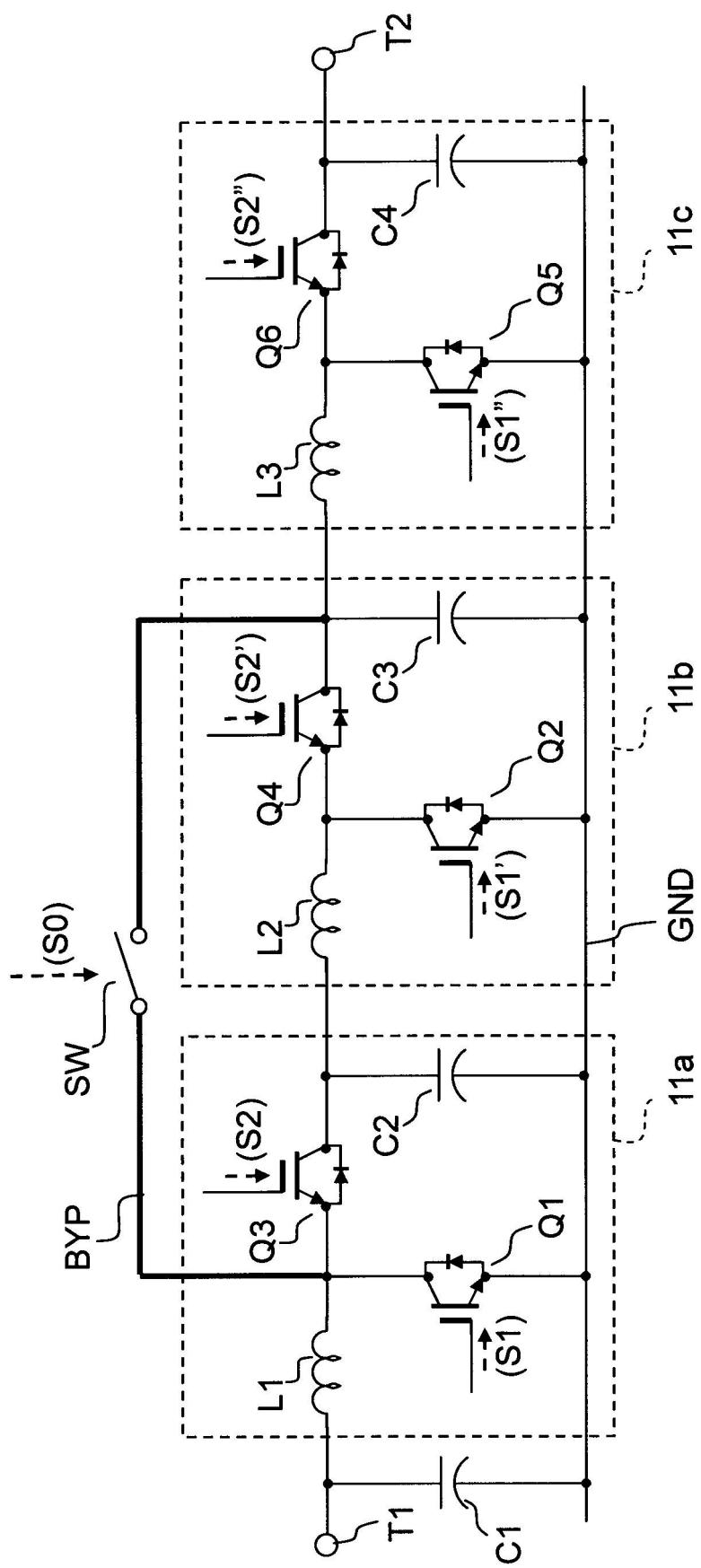

図 9 は、電力伝送部 11 の構成図である。本図に示すように電力伝送部 11 においては、複数個（ここでは一例として 3 個とするが、2 個または 4 個以上であってもよい）の昇降圧チョッパ回路（11 a、11 b、11 c）が直列に接続されている。なお昇降圧チョッパ回路（11 a、11 b）の構成については、第 2 実施形態の場合と同等である。但し本実施形態では、昇降圧チョッパ回路（11 a、11 b）は第 2 回路としての役割を果たす。

【 0 0 8 6 】

昇降圧チョッパ回路 11 c は、コイル L 3、スイッチング素子（IGBT）Q 5、スイッチング素子（IGBT）Q 6、およびコンデンサ C 4 が、それぞれ適切に接続されて形成されている。

40

【 0 0 8 7 】

より具体的には、コイル L 3 の一端は、スイッチング素子 Q 5 のコレクタとスイッチング素子 Q 6 のエミッタに接続されている。またスイッチング素子 Q 6 のコレクタは、コンデンサ C 4 の一端に接続されている。またスイッチング素子 Q 5 のエミッタとコンデンサ C 4 の他端は、グランドライン GND に接続されている。なお各スイッチング素子（Q 5、Q 6）におけるエミッタとコレクタは、ダイオード（アノードがエミッタ側となっている）を介して接続されている。なお、コイル L 3 の他端はスイッチング素子 Q 4 のコレクタに接続され、スイッチング素子 Q 6 のコレクタは端子 T 2 にも接続されている。

【 0 0 8 8 】

なおスイッチング素子 Q 5 の ON / OFF の切替は、信号 S 1" によって制御される。

50

またスイッチング素子Q 6のON / OFFの切替は、信号S 2"によって制御される。信号S 1"は、信号S 1と同じにして生成される信号であり、信号S 2"は、信号S 2と同じにして生成される信号である。

【0089】

昇降圧チョッパ回路11cは、スイッチング素子Q 6がOFFにされ、スイッチング素子Q 5によるチョッピングが行われるとき、コイルL 3においてエネルギーの蓄積と放出を繰り返す。その結果、昇降圧チョッパ回路11cは、一端（昇降圧チョッパ回路11bの側）に入力された電力を昇圧させた上で、他端（端子T 2の側）から出力する動作（昇圧動作）を行う。

【0090】

一方、昇降圧チョッパ回路11cは、スイッチング素子Q 5がOFFにされ、スイッチング素子Q 6によるチョッピングが行われるとき、コイルL 3においてエネルギーの蓄積と放出を繰り返す。その結果、昇降圧チョッパ回路11cは、一端（端子T 2の側）に入力された電力を降圧させた上で、他端（昇降圧チョッパ回路11bの側）から出力する動作（降圧動作）を行う。

【0091】

上述の説明から明らかなように、スイッチング素子Q 5は昇圧用スイッチング素子に、スイッチング素子Q 6は降圧用スイッチング素子に、それぞれ該当している。

【0092】

また第2実施形態とは異なり、バイパスラインBYPの一端と他端は、スイッチング素子Q 4のコレクタとコイルL 3との間、およびスイッチング素子Q 3のエミッタとコイルL 1との間に、それぞれ接続されている。すなわち昇降圧チョッパ回路11bおよび昇降圧チョッパ回路11a（コイルL 1の部分は除く）と並列になるように、バイパスラインBYPが設けられている。なおバイパスラインBYPは、コイルL 1とは直列になっている。

【0093】

バイパスラインBYPは、バイパスラインBYPの開閉を切替えるスイッチSWが設けられており、スイッチSWが閉じられたとき、両端間が導通した導通状態となる。スイッチSWの開閉は、信号S 0によって制御される。

【0094】

主制御部12は、第1伝送動作を行うべき期間においてはスイッチSWが開くように、第2伝送動作を行うべき期間においてはスイッチSWが閉じるように、信号S 0を生成する。第1信号生成部13aは、主制御部12の指示に応じて信号S 1、信号S 1'および信号S 1"を生成し、スイッチング素子Q 1に信号S 1を、スイッチング素子Q 2に信号S 1'を、スイッチング素子Q 5に信号S 1"を、それぞれ出力する。また第2信号生成部13bは、主制御部12の指示に応じて信号S 2、信号S 2'および信号S 2"を生成し、スイッチング素子Q 3に信号S 2を、スイッチング素子Q 4に信号S 2'を、スイッチング素子Q 6に信号S 2"を、それぞれ出力する。信号S 1"および信号S 2"のタイミングチャートは、図4に示す信号S 1および信号S 2のものと同等（デューティ比等は異なっていても構わない）である。このように生成された各信号（S 0 ~ S 2、S 1' S 2'、S 1"、S 2"）を受け、電力伝送部11は次のように動作する。

【0095】

まず第1伝送動作を行うべき期間において、昇降圧チョッパ回路11aは、端子T 1に入力された電力を昇降圧チョッパ回路11bへ伝送する昇圧動作を行う。また昇降圧チョッパ回路11bは、昇降圧チョッパ回路11aから入力された電力を昇降圧チョッパ回路11cへ伝送する昇圧動作を行う。また昇降圧チョッパ回路11cは、昇降圧チョッパ回路11bから入力された電力を端子T 2へ伝送する昇圧動作を行う。これらの昇圧動作が並行してなされる結果、第1伝送動作が達成される。

【0096】

第1伝送動作における昇圧比は、各昇降圧チョッパ回路（11a ~ 11c）の昇圧動作

10

20

30

40

50

における、それぞれの昇圧比の積で表される。なお第1伝送動作の実行時においては、端子T2から出力する出力電圧が目標電圧に近づくように、信号S1、信号S1'および信号S1''のデューティ比が調節される。

【0097】

また第2伝送動作を行うべき期間において、昇降圧チョッパ回路11cは、端子T2に入力された電力を昇降圧チョッパ回路11bの側へ伝送する降圧動作を行う。なおこのとき、バイパスラインBYPは導通状態となっている。そのため、昇降圧チョッパ回路11cによる降圧動作のなされた電力は、バイパスラインBYPを通って、スイッチング素子Q3のコレクタとコイルL1との間へ伝送される。

【0098】

その結果、昇降圧チョッパ回路11cからスイッチング素子Q3のコレクタとコイルL1との間へ電力を伝送するにあたり、昇降圧チョッパ回路11bとスイッチング素子Q3を当該電力が通ると仮定した場合に比べ、電力の損失は大幅に低減される。

【0099】

バイパスラインBYPを通ってきた電力は、更にコイルL1を通って、端子T1へ伝送される。その結果、第2伝送動作が達成される。第2伝送動作の実行時においては、端子T1から出力する出力電圧が目標電圧に近づくように、信号S2''のデューティ比が調節される。

【0100】

また以上の説明から明らかなように、本実施形態においては、昇降圧チョッパ回路11cが第1回路としての役割を果しており、昇降圧チョッパ回路11aと昇降圧チョッパ回路11bは第2回路としての役割を果している。

【0101】

またコンバータ1は、第2伝送動作の実行時には、第2回路（但し、コイルL1の部分を除く）と並列であるバイパスラインBYPを電力が通るようにしつつ、第1回路に降圧動作を行わせる。そのためコンバータ1によれば、第2回路のスイッチング動作に伴う電力の損失を低減させることができとなっている。

【0102】

またバイパスラインBYPは、昇降圧チョッパ回路11aについて、スイッチング素子Q3（降圧用スイッチング素子）とは並列であるが、コイルL1とは直列に設けられている。そのため第2伝送動作の実行時において、コイルL1は電力の伝送経路に含まれることになる。

【0103】

その結果、本実施形態のコンバータ1によれば、第2伝送動作の実行時において、一つのスイッチング素子Q6の使用に対して、コイルL1とコイルL3の二つのコイルが使用される。これにより、一つのコイルのみが使用される場合（第2実施形態を参照）に比べて、出力電流のリップルを抑制することが可能となっている。

【0104】

5. その他

上述した通り各実施形態のコンバータ1は、端子T1（第1端）と端子T2（第2端）の間に複数のチョッパ回路を備えており、端子T1に入力された電力を昇圧させた上で端子T2から出力する第1伝送動作、および、端子T2に入力された電力を降圧させた上で端子T1から出力する第2伝送動作、を行うようになっている。

【0105】

なお複数のチョッパ回路は、第1端から第2端へ向かう方向への昇圧動作、および、第2端から第1端へ向かう方向への降圧動作をするよう形成された第1回路と、第1端から第2端へ向かう方向への昇圧動作をするよう形成された第2回路と、の各々を少なくとも一つずつ含んでいる。そして第1伝送動作を行うときは、第1回路および第2回路が、端子T1から端子T2へ向かう方向への前記昇圧動作を行い、第2伝送動作を行うときは、第1回路および第2回路が端子T2から端子T1へ向かう方向への降圧動作を行い、少な

10

20

30

40

50

くとも第2回路の一つは、第2回路のみでは実質的に降圧動作を行わないようになっている。

【0106】

なお第2実施形態および第4実施形態のコンバータ1は、複数のチョッパ回路における第2回路からなる回路の部分の全部または一部と並列に設けられたバイパスラインBYP(バイパス)を備え、第2伝送動作を行うときに、電力がバイパスラインBYPを通るようにして、第2回路が実質的に降圧動作を行わないようになっている。

【0107】

なお、バイパスラインBYPが、第2回路からなる回路の部分の全部または一部と並列に設けられる形態としては、既に図3や図9に示したものその他、様々な形態が考えられる。例えは当該形態には、図10から図15に示すものも含まれる。

【0108】

なお図10に示す回路は、第2実施形態のコンバータ1(図3を参照)において、昇降圧チョッパ回路11bを第1回路とし、昇降圧チョッパ回路11aを第2回路とし、バイパスラインBYPが第2回路と並列になるように改変したものである。すなわち当該回路は、第1回路と第2回路の位置を入れ替わった点を除き、図3に示す回路と同等の回路である。また図11に示す回路は、図10に示す回路において、バイパスラインBYPが第2回路のコイルと直列になるように改変したものである。また図12に示す回路は、図11に示す回路において、バイパスラインBYPが第1回路のコイルと並列になるように改変したものである。

【0109】

また図13～図15に示す回路は、それぞれ、図10～図12に示した回路において、第2回路を降圧機能を有しない昇圧チョッパ回路11d(昇降圧チョッパ回路11aについて、スイッチング素子Q3を省略したものに相当)に改変したものである。図13～図15に示す回路では、バイパスラインBYPは、第2回路が有しているダイオードD1(昇圧動作時に整流を行う、昇圧用整流素子)と並列になっている。図10～図15の何れの回路においても、昇降圧チョッパ回路11bが第1回路であり、昇降圧チョッパ回路11a(または昇圧チョッパ回路11d)が第2回路である点は変わらない。

【0110】

図3、図10、および図13に示した回路は、バイパスラインBYPが、全ての第2回路からなる回路の全部と並列に設けられた例といえる。また図9、図11、図12、図14、および図15に示した回路は、バイパスラインBYPが、全ての第2回路からなる回路の一部と並列に設けられた例といえる。なお図9、図11、図12、図14、および図15に示した回路における第2回路(図9での昇降圧チョッパ回路11bを除く)は、第2伝送動作の実行時において、第1回路のスイッチング動作に付随して降圧動作を行う(特にコイルが降圧動作に寄与する)が、第2回路のみでは実質的に降圧動作を行わない。

【0111】

また第2実施形態および第4実施形態のコンバータ1(図10～図12に示した回路を有するものも同様)は、第2回路は昇降圧チョッパ回路として形成されており、バイパスラインBYPは、第2回路の降圧用スイッチング素子と並列に設けられている。特に第4実施形態のコンバータ(図11および図12に示した回路を有するものも同様)では、バイパスラインBYPは、このバイパスラインBYPが降圧用スイッチング素子と並列に設けられている第2回路について、コイルとは直列に設けられている。

【0112】

またバイパスラインBYPと並列な第2回路は、コンバータ1が有する複数のチョッパ回路の一部として、任意の位置に任意の個数だけ設けることが可能である。そしてこのような第2回路を複数設ける場合、これらの第2回路は連続(隣り合う状態)であっても良く、非連続であっても良い。なお非連続とする場合、スイッチSWを有するバイパスラインBYPは複数存在することになる。

10

20

30

40

50

## 【0113】

また第3実施形態のコンバータにおいては、第2回路は昇降圧チョッパ回路として形成されており、第2伝送動作を行うときに、第2回路の降圧用スイッチング素子を導通状態に固定することで、第2回路に実質的に降圧動作を行わせないようにしている。

## 【0114】

また第3実施形態では、導通状態に固定する降圧用スイッチング素子として、スイッチング素子Q4を選択しているが、これは一例であって、他のスイッチング素子を選択することも可能である。

## 【0115】

また降圧用スイッチング素子を導通状態に固定する第2回路は、コンバータ1が有する複数のチョッパ回路の一部として、任意の位置に任意の個数だけ設けることが可能である。そしてこのような第2回路を複数設ける場合、これらの第2回路は連続（隣り合う状態）であっても良く、非連続であっても良い。またこのような第2回路を複数設ける場合は、導通状態に固定される降圧用スイッチング素子は複数存在することになる。

10

## 【0116】

また本発明の実施形態について以上の通り説明したが、上述したものはその一例に過ぎない。本発明はその主旨を逸脱しない範囲において、様々な形態で実施され得る。当該実施形態に関する変形例としては、例えば次のようなものが挙げられる。

## 【0117】

電力伝送部11において直列に接続される複数のチョッパ回路において、第1回路や第2回路の個数（直列数）については、特に限定されない。コンバータ1の設計方針などに応じて、任意の個数とすることが可能である。

20

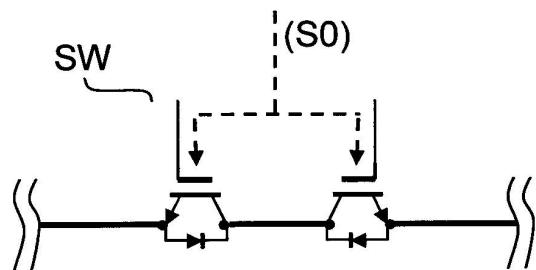

## 【0118】

また、バイパスラインBYPに設けられるスイッチSWは、種々の形態とすることが可能である。例えばスイッチSWとしては、リレースイッチを用いても良く、IGBTやFETといった半導体素子を用いても良い。但し半導体素子を用いる場合は、第1伝送動作が阻害されないよう、例えば図16に示すように、複数の半導体素子を向きを変えて接続する必要がある。また各スイッチング素子（Q1～Q6）について、IGBTの代わりにFETなどが用いられても構わない。

## 【0119】

30

また電力伝送部11において直列に接続される複数のチョッパ回路において、第1回路および第2回路をどの位置に（どのような順番で）配置するかについても、特に限定されない。但し、コンバータ1の設計方針によっては、以下に示す形態を採用することが考えられる。

## 【0120】

まず各コイル（L1～L3）については、一般的に、低電圧側に近いほど、定格電流の大きなものが用いられる（逆に言えば、高電圧側に近いほど定格電流の小さなものが用いられる）ことになる。また例えば第2実施形態では、第2回路のコイルは、第2伝送動作の実行時においてバイパスされるため、電力を通さずに済む。そのため、大きな電力を伝送可能とすることを重視する場合は、複数のチョッパ回路のうち、少なくとも端子T2に最も近いものを第2回路とするのが望ましい。これにより、定格電流の比較的小さいコイルが用いられないようにし、伝送可能な電力の上限値が小さくならないようにすることが可能となる。

40

## 【0121】

また例えば第3実施形態では、仮に昇降圧チョッパ回路11a（端子T1に近い方）を第2回路とすると、コイルL1とコイルL2の両方を、降圧の動作に利用することが可能となる。そのため、昇降圧チョッパ回路11bを第2回路とした場合（コイルL1のみが降圧の動作に利用される）に比べ、出力電流のリップルを低減させることが可能となる。このようなことから、リップルの低減を重視する場合は、複数のチョッパ回路のうち、少なくとも端子T1に最も近いものを第2回路とするのが望ましい。

50

## 【0122】

なお、第2回路に実質的に降圧動作を行わせないため、バイパスラインBYPを用いる実施形態において、少なくとも端子T1に最も近いものを第2回路とする場合、バイパスラインBYPは、少なくとも端子T1に最も近い第2回路と並列に設けられる。また少なくとも端子T2に最も近いものを第2回路とする場合、バイパスラインBYPは、少なくとも端子T2に最も近い第2回路と並列に設けられる。

## 【0123】

また、第2回路に実質的に降圧動作を行わせないため、降圧用スイッチング素子を導通状態に固定する実施形態において、少なくとも端子T1に最も近いものを第2回路とする場合、少なくとも端子T1に最も近い第2回路の降圧用スイッチング素子が、導通状態に固定される。また少なくとも端子T2に最も近いものを第2回路とする場合、少なくとも端子T2に最も近い第2回路の降圧用スイッチング素子が、導通状態に固定される。

10

## 【0124】

また本発明の利用分野は、これまでに挙げた実施形態には限定されない。本発明は、電圧を変換して双方向に電力を伝送する、様々な用途に利用することが可能である。特に、電圧の異なる装置や部品間において双方向に電力を伝送するための回路として、本発明は好適に利用される。

## 【産業上の利用可能性】

## 【0125】

本発明は、電圧を変換する電力変換回路に利用することができる。

20

## 【符号の説明】

## 【0126】

|               |                      |    |

|---------------|----------------------|----|

| 1             | 双方向DCDCコンバータ（電力変換回路） |    |

| 1 1           | 電力伝送部                |    |

| 1 1 a ~ 1 1 c | 昇降圧チョッパ回路            |    |

| 1 1 d         | 昇圧チョッパ回路             |    |

| 1 2           | 主制御部                 |    |

| 1 3 a         | 第1信号生成部              |    |

| 1 3 b         | 第2信号生成部              |    |

| 1 3 c         | 第3信号生成部              | 30 |

| BYP           | バイパスライン              |    |

| C 1 ~ C 4     | コンデンサ                |    |

| D 1           | ダイオード（昇圧用整流素子）       |    |

| GND           | グラウンドライン             |    |

| L 1 ~ L 3     | コイル                  |    |

| Q 1 ~ Q 6     | スイッチング素子             |    |

| S 0 ~ S 2     | 、S 1'、S 2'、S 1"、S 2" | 信号 |

| SW            | スイッチ                 |    |

| T 1           | 第1端（端子）              |    |

| T 2           | 第2端（端子）              | 40 |

【図1】

【図2】

1

【図3】

【図4】

【 图 5 】

20

【 四 6 】

【図7】

11

【図8】

【図9】

11

【図10】

11

【図11】

11

【図12】

11

【図13】

11

【図14】

11

【図15】

11

【図16】

【図17】

### 昇圧時におけるデューティ比と昇圧比の関係

### 降圧時におけるデューティ比と降圧比の関係

---

フロントページの続き

審査官 今井 貞雄

(56)参考文献 特開2010-200519 (JP, A)

特開平01-157265 (JP, A)

特開2008-206317 (JP, A)

特開2008-140038 (JP, A)

(58)調査した分野(Int.Cl., DB名)

H02M 3/155