(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2005-222581

(P2005-222581A)

(43) 公開日 平成17年8月18日(2005.8.18)

(51) Int.C1.<sup>7</sup>

F 1

テーマコード(参考)

G 11 C 11/403

G 11 C 11/34

3 7 1 J

5 M 0 2 4

G 11 C 11/401

G 11 C 11/34

3 6 2 S

G 11 C 11/406

G 11 C 11/34

3 6 3 K

G 11 C 11/407

G 11 C 11/34

3 7 1 K

審査請求 未請求 請求項の数 23 O L (全 68 頁)

(21) 出願番号

特願2004-26999 (P2004-26999)

(22) 出願日

平成16年2月3日(2004.2.3)

(71) 出願人

503121103

株式会社ルネサステクノロジ

東京都千代田区丸の内二丁目4番1号

(74) 代理人

100064746

弁理士 深見 久郎

(74) 代理人

100085132

弁理士 森田 俊雄

(74) 代理人

100083703

弁理士 仲村 義平

(74) 代理人

100096781

弁理士 堀井 豊

(74) 代理人

100098316

弁理士 野田 久登

(74) 代理人

100109162

弁理士 酒井 将行

最終頁に続く

(54) 【発明の名称】半導体記憶装置

## (57) 【要約】

【課題】 適切なタイミングで内部でレイテンシを設定する半導体記憶装置を提供する。

【解決手段】 トリガ生成回路104は、トリガ信号を出力する。遅延回路110は、トリガ信号を受けて、トリガ信号を遅延させた遅延信号を出力する。クロックカウンタ106は、クロックを受け、トリガ信号が受けてから遅延信号を受けるまでの間、受けたクロックの数をカウントし、カウント結果を出力する。判定回路107は、クロックの数とレイテンシとの対応関係を記憶し、クロックカウンタから出力されるカウント結果に対応するレイテンシを判定する。レイテンシ用レジスタ108は、判定されたレイテンシを保持する。WAIT制御回路109は、レイテンシ用レジスタ108に保持されたレイテンシに基づき、外部にWAIT信号を出力する。

【選択図】

図1

## 【特許請求の範囲】

## 【請求項 1】

クロックに同期して動作する半導体記憶装置であって、

行列状に配置された複数のメモリセルを有するメモリアレイと、

トリガ信号を出力するトリガ生成回路と、

前記トリガ信号を受けて、前記トリガ信号を遅延させた遅延信号を出力する遅延回路と、

前記クロックを受け、前記トリガ信号を受けてから前記遅延信号を受けるまでの間、受けたクロックの数をカウントし、カウント結果を出力するクロックカウンタと、

クロックの数とレイテンシとの対応関係を記憶し、前記クロックカウンタから出力されるカウント結果に対応するレイテンシを判定する判定回路と、

前記判定されたレイテンシを保持するレジスタと、

前記レジスタに保持されたレイテンシに基づき、外部にウエイト信号を出力するウエイト制御回路とを備えた半導体記憶装置。

## 【請求項 2】

前記トリガ生成回路は、

外部信号をラッチしてラッチ信号を生成する回路と、

前記ラッチ信号の組合せに応じて、読み出し信号または書き込み信号とともに前記トリガ信号を出力する論理回路とを備えた請求項 1 記載の半導体記憶装置。

## 【請求項 3】

行列状に配置された複数のダイナミックランダムアクセスメモリのメモリセルを有し、一度のリフレッシュの単位となるバンクを複数個有するメモリアレイと、

リフレッシュのトリガを出力する回路と、

前記リフレッシュトリガを受けたときに、外部から指示された動作を実行中のときに、前記動作を実行中のバンクと異なるバンクを選択して、前記選択したバンクのアドレスを出力するバンク選択回路と、

前記受けたアドレスのバンクのリフレッシュを実行するリフレッシュ制御回路とを備え、

前記バンク選択回路は、

リフレッシュが実施済みのバンクのアドレスを保持し、すべてのバンクのアドレスが保持されると、保持されているすべてのアドレスが消去されるレジスタと、

前記リフレッシュトリガを受けたときに、前記レジスタを参照してリフレッシュが未実施のバンクのアドレスを特定する特定回路と、

前記未実施のバンクアドレスと、前記動作を実行中のバンクアドレスとを比較し、異なる場合に、前記未実施のバンクアドレスを出力する比較回路とを含む半導体記憶装置。

## 【請求項 4】

行列状に配置された複数のダイナミックランダムアクセスメモリのメモリセルを有するメモリアレイと、

リフレッシュのタイミングを規定する第 1 の信号を生成する第 1 の回路と、

前記第 1 の信号を出力する出力端子と、

外部からリフレッシュのタイミングを規定する第 2 の信号を受ける入力端子と、

前記第 1 の信号および前記第 2 の信号を受けて、いずれかの信号を出力するスイッチと、

前記スイッチから出力される信号を受けて、当該信号に基づきリフレッシュ制御を行なう第 2 の回路とを備えた半導体記憶装置。

## 【請求項 5】

前記半導体記憶装置は、さらに、

前記第 2 の回路でリフレッシュ制御が実行されている間、外部にウエイト信号を出力するウエイト制御回路を備えた請求項 4 記載の半導体記憶装置。

## 【請求項 6】

10

20

30

40

50

前記第1の回路は、前記第1の信号として一定周期の信号を出力するタイマである、請求項5記載の半導体記憶装置。

【請求項7】

クロックに同期して動作し、バーストモードでのアクセスを行ない、読み出し信号または書き込み信号が生成されるのに先立って、ロウアドレスおよびコラムアドレスを取得する半導体記憶装置であって、

行列上に配置された複数のメモリセルを有するメモリアレイと、

外部から受けた制御信号によって読み出し信号または書き込み信号が生成された第1のクロックに同期して、選択されたロウのロウアクセス処理と、先頭から1個以上かつバーストレングス以下である第1の個数のコラムのコラムアクセス処理を行ない、

レイテンシで規定される第2のクロック以降のクロックに同期して、バーストモードアクセスの残りの第2の個数のコラムのコラムアクセス処理を行なうように制御する制御回路とを備えた半導体記憶装置。

【請求項8】

前記半導体記憶装置は、

前記メモリセルに接続されたビット線対の電位を増幅するセンスアンプ回路と、

前記コラムを選択するコラムデコーダとを含み、

前記制御回路は、

前記センスアンプ回路を活性化させる信号が生成された後のタイミングで、前記第1のクロックに同期して活性化されるロウ活性化信号に応じてコラムイネーブル信号を生成する第1の制御回路と、

前記コラムイネーブル信号に応じて、前記第1の個数のコラムを活性化させる第1の指示信号を前記コラムデコーダに出力し、前記第2のクロック以降のクロックに同期して前記第2の個数のコラムを活性化させる第2の指示信号を前記コラムデコーダに出力する第2の制御回路とを備える、請求項7記載の半導体記憶装置。

【請求項9】

前記制御回路は、前記第1のクロックに同期してコラムアクセス処理が行なわれて出力される先頭のデータのタイミングを外部に通知する信号を生成する回路を含む、請求項8記載の半導体記憶装置。

【請求項10】

前記制御回路は、前記第2のクロック以降のクロックに同期してコラムアクセス処理が行なわれて出力される先頭のデータのタイミングを外部に通知する信号を生成する回路を含む、請求項8記載の半導体記憶装置。

【請求項11】

リフレッシュ動作、読み出し動作、または書き込み動作を実行中に、前記読み出しあり書き込み要求信号が生成されたときには、前記動作の実行終了後の次のクロックを前記第1のクロックとして動作させるためのシフト回路とを備えた請求項8記載の半導体記憶装置。

【請求項12】

外部信号の組合せによって、複数の動作モードのいずれかのモードに設定される半導体記憶装置であって、

行列上に配置された複数のメモリセルを有するメモリアレイと、

前記メモリセルに各々接続されたビット線対と、

前記ビット線対の電位を増幅する第1の増幅回路と、

複数の前記ビット線対に接続されたI/O線対と、

前記各モードに応じていずれかが活性化され、前記I/O線対の電位を増幅する2種類以上の第2の増幅回路とを備えた半導体記憶装置。

【請求項13】

前記複数の動作モードは、外部から入力されるクロックに同期した同期動作モードと、クロックに同期しない非同期動作モードであり、

前記第2の増幅回路は、

10

20

30

40

50

同期動作モードに対応した第1の種類の増幅回路と、

非同期動作モードに対応した第2の種類の増幅回路とである、請求項12記載の半導体記憶装置。

【請求項14】

前記半導体記憶装置は、

同期モードに設定されたときに、前記第1の種類の増幅回路を活性化するとともに、前記第2の種類の増幅回路を非活性化し、

非同期モードに設定されたときに、前記第1の種類の増幅回路を非活性化するとともに、前記第2の種類の増幅回路を活性化させる制御回路と、

前記第1の種類の増幅回路の出力、および前記第2の種類の増幅回路の出力と接続され、前記第1の種類の増幅回路の出力または前記第2の種類の増幅回路の出力のいずれかをデータバスへ出力するデータバスドライバとを備えた請求項13記載の半導体記憶装置。 10

【請求項15】

前記第1の種類の増幅回路は、クロックに同期した信号に基づき、前記I/O線対と当該第1の種類の増幅回路内の増幅部との間の接続を切断するスイッチ部を備え、

前記第2の種類のプリアンプは、前記I/O線対と当該第2の種類の増幅回路内の増幅部との間の接続を切断するスイッチ部を有しない、請求項14記載の半導体記憶装置。 20

【請求項16】

前記I/O線と接続する前記第1の種類の増幅回路および前記第2の種類の増幅回路は、コラム方向に並んで配置され、

前記I/O線対は、分岐を有せずに、前記第1の種類の増幅回路および前記第2の種類の増幅回路と接続する、請求項13記載の半導体記憶装置。 20

【請求項17】

クロックに同期して動作する半導体記憶装置であって、

行列状に配置された複数のメモリセルを有するメモリアレイと、

外部からバイトマスク信号を受けて、前記バイトマスク信号に基づきバイトマスク処理を制御するバイトマスク制御回路と、

前記メモリセルから出力されたデータを受けて、前記バイトマスク制御回路による指示に従って、前記メモリセルから出力されたデータの前記バイトマスク信号に対応するバイトの出力を行なわない出力回路とを備え、 30

前記バイトマスク制御回路は、連続読出しありは連続書き込みが第1の口ウと第2の口ウの2つの口ウに渡る場合、途中で第1の口ウの最後のコラムに達したため第2の口ウへの移行のためロウアクセス処理を行なっている間に、外部からバイトマスク信号を受けたときに、前記バイトマスク信号に対応するバイトのマスク処理を、前記ロウアクセスが終了し、次のビットのデータが出力されるタイミングまで延長する、半導体記憶装置。

【請求項18】

前記半導体記憶装置は、さらに、

前記次のロウへの移行のためロウアクセス処理を行なっている間、データが出力されるまで待つことを外部に知らせるウエイト信号を出力するウエイト制御回路を備え、

前記バイトマスク制御回路は、各バイトごとに、

前記バイトマスク信号が前記連続読出しありは書き込みの先頭のビット以外のビットのバイトマスクを行なうことを示す場合において、前記次のロウへの移行のためロウアクセス処理を行なわないとした場合に前記ビットが前記出力回路から出力されるタイミングに前記ウエイト信号が出力されているときに、前記バイトに対応する出力イネーブル信号をディセーブルにせずに、前記バイトマスク信号に基づいて生成された信号を出力する第1回路と、

前記バイトマスク信号に基づいて生成された信号を受けて保持し、前記ウエイト信号が解除されたタイミングに、前記バイトに対応する出力イネーブル信号をディセーブルにする第2回路とを含み、 40

前記バイトマスク信号に基づいて生成された信号を受けて保持し、前記ウエイト信号が解除されたタイミングに、前記バイトに対応する出力イネーブル信号をディセーブルにする第2回路とを含み、

前記出力回路は、前記出力イネーブル信号がディセーブルを示すときに、前記メモリセ 50

ルから出力されたデータの前記ディセーブルの出力イネーブル信号に対応するバイトの出力を行なわない、請求項17記載の半導体記憶装置。

【請求項19】

クロックに同期して動作する半導体記憶装置であって、

行列状に配置された複数のメモリセルを有するメモリアレイと、

前記メモリセルに接続されたピット線対と、

コラム選択信号を受けて、バーストアクセスの最後のカラムを選択する選択信号が活性化された後の次のクロックでバーストレングスリセット信号を出力するバーストレングスカウンタと、

前記バーストレングスリセット信号を受けて、前記ピット線対をプリチャージする制御回路とを備えた半導体記憶装置。

【請求項20】

前記制御回路は、前記バーストレングスリセット信号を受けて、プリチャージ信号を活性化して、前記プリチャージ信号の活性化によって前記ピット線対をプリチャージする、請求項19記載の半導体記憶装置。

【請求項21】

クロックに同期して動作する同期モードと、非同期で動作する非同期モードとを有する半導体記憶装置であって、

行列状に配置された複数のメモリセルを有するメモリアレイと、

同期固定モードと、非同期固定モードと、同期および非同期の混載モードのいずれかに設定可能な設定回路と、

前記混載モード時に、外部チップイネーブル信号がアサートされてから、外部クロックの立ち上がりまでの時間が所定値以上か否かを調べ、前記所定値以上のときに、非同期固定モードに移行する非同期移行回路と、

同期固定モードまたは混載モードに設定されたときに同期動作を制御する同期制御回路と、

非同期固定モード若しくは混載モードに設定されたとき、または非同期固定モードに移行したときに、非同期動作を制御する非同期制御回路とを備え、

前記非同期移行回路は、前記設定回路の出力に応じて非活性化される、半導体記憶装置。

【請求項22】

前記設定回路は、バスコンフィギュレーションレジスタの所定の2個のピットであり、

前記非同期移行回路は、前記ピットの値が同期固定モードまたは非同期固定モードを示すときには、前記移行動作の処理を停止する、請求項21記載の半導体記憶装置。

【請求項23】

クロックに同期して動作する半導体記憶装置であって、

行列状に配置された複数のメモリセルを有するメモリアレイと、

外部チップイネーブル信号を受けて内部チップイネーブル信号を生成するチップイネーブルバッファと、

外部クロックを受けて内部クロックを生成するクロックバッファと、

外部アドレス信号を受けて内部アドレス信号を生成するアドレスバッファと、

外部チップイネーブル信号以外の外部制御信号を受けて内部制御信号を生成する制御バッファとを備え、

前記クロックバッファ、前記アドレスバッファ、および前記制御バッファは、前記内部チップイネーブル信号を受けて、前記内部チップイネーブル信号がチップの非活性を示すときに、その動作を停止し、

前記クロックバッファ、前記アドレスバッファ、および前記制御バッファは、前記内部チップイネーブル信号が活性化を示すときに、動作を実行し、

前記制御バッファは、外部アドレス取込信号を受けて、内部アドレス取込信号を生成し、

10

20

30

40

50

前記半導体記憶装置は、さらに、

前記内部アドレス取込信号を所定の遅延量だけ遅延させる遅延回路と、

前記遅延回路の出力と前記内部クロックとを受けるクロックドインバータと、

前記クロックドインバータの出力と前記内部クロックとの論理積信号を出力する論理回路と、

前記論理積信号の先頭のパルスに基づき、ロウアドレスストローブ信号を活性化する回路とを備え、

前記論理積信号の先頭のパルスが、前記外部アドレス取込み信号が活性化されている間に立ち上がる外部クロックパルスから生成された内部クロックパルスとなるように、前記遅延回路の所定の遅延量が定められている、半導体記憶装置。 10

#### 【発明の詳細な説明】

#### 【技術分野】

#### 【0001】

本発明は、半導体記憶装置に関し、特に、携帯端末への搭載に適した半導体記憶装置に関する。 20

#### 【背景技術】

#### 【0002】

携帯電話などの携帯端末において用いられる半導体記憶装置は、大容量および制御の簡易性を実現するために、擬似SRAMが用いられている。擬似SRAM(Static Random Access Memory)では、内部のメモリセルとしてはDRAM(Dynamic Random Access Memory)セルが用いられ、入力される制御信号およびアドレス信号などを規定する外部インターフェースとしては、SRAMと類似のクロックに同期しない非同期のインターフェースが用いられている。そして、リフレッシュ動作は、外部からの信号によって制御されるのではなく、内部で自動的に行なわれる(たとえば、特許文献1を参照)。 20

#### 【0003】

さらに、より高速化を実現するために、たとえば、非特許文献1に記載されているCellular RAM(R)のように、擬似SRAMに、同期式のインターフェースを追加した同期式擬似SRAMが実用化されている。この同期式擬似SRAMでは、SRAM類似のクロックに同期しない非同期式のインターフェースに加えて、クロックに同期した同期式のインターフェースを備える。 30

#### 【0004】

ところで、同期式の擬似SRAMでは、読み出しありは書き込み要求を受けてから、データが出力されるまでのクロック数であるコマンドレイテンシCLが経過するまでと、セルフリフレッシュを行なっている間には、外部からアクセスすることができないことをWAIT信号により通知する。従来コマンドレイテンシCLは、外部から与えられるが、同期式の擬似SRAMでは、内部からWAIT信号によりアクセス不可能な旨を通知することができるので、外部から与える必要がないといえる。むしろ、同期式擬似SRAMの内部で、そのときの状態に応じてコマンドレイテンシCLを設定した方が、外部から設定するよりも適切な値に設定することができるといえる。 40

#### 【0005】

これに対して、特許文献2には、クロック周波数によってレイテンシ調整が可能なレイテンシ決定回路が開示されている。このレイテンシ決定回路は、クロック信号に同期してレイテンシ決定を始めるレイテンシ決定開始信号の活性化に応答して内部開始信号を発するレイテンシ決定指示入力部と、レイテンシ決定開始信号に応答してクロック信号のエッジごとに所定のレイテンシ決定区間信号を発するレイテンシ区間定義回路と、内部開始信号を所定時間遅延させてレイテンシを調整するように遅延信号を発する遅延部と、遅延信号の活性化時点でレイテンシ決定開始信号およびレイテンシ決定区間信号に応答してレイテンシ数を決定するレイテンシ指示回路を具備する。このようなレイテンシ決定回路によって、レイテンシを外部からの指示によらずに、内部で決定することができる。 50

#### 【0006】

また、たとえば、特許文献3には、擬似SRAMが複数個のバンクを有する場合には、セルフリフレッシュと読出しありは書き込みとを同時実行する方法が開示されている。すなわち、特許文献3の段落[0020]には、第1乃至第4ロードアドレスラッチ回路及びバッファ80～83は、第1乃至第4セルバンク10～13の内のある一つのセルバンクがリフレッシュモードにあるとしても、残りの3つのセルバンク側にロードアドレスラッチ回路70によりラッチされた第2ロードアドレス信号A<sub>0</sub>～A<sub>n-2</sub>を伝送してリフレッシュモード中にもデータのアクセスを可能にすることができます。

【特許文献1】特開2002-352577号公報

【特許文献2】特開2001-155484号公報

【特許文献3】特開平7-226077号公報

10

【非特許文献1】Cellular RAMTM Memory、インターネット<URL:

<http://www.micron.com/products/psram/cellularram/>>

【発明の開示】

【発明が解決しようとする課題】

【0007】

しかしながら、上述の特許文献および非特許文献に記載の方法では、以下のような問題がある。

【0008】

まず、特許文献2には、内部でレイテンシを設定する方法について記載されているものの、レイテンシを設定するタイミングについては記載されていない。

【0009】

また、特許文献3には、リフレッシュするバンクと読出しありは書き込みを行なうバンクが異なるときに、リフレッシュと読出しありは書き込みとを同時に行なう方法について記載されているものの、読出しありは書き込みを行なうバンクと重ならないように、リフレッシュするバンクを決める方法については記載されていない。

【0010】

また、複数個の擬似SRAMを1つのパッケージに収容したときに、各々が異なるタイミングでリフレッシュを行なうので、各々が outputするWAIT信号が競合するという問題がある。

【0011】

また、コマンドレイテンシCLで規定されるタイミングよりも早いタイミングでデータを出力することができないという問題がある。

【0012】

また、同期モードと非同期式モードなどのように複数のモードを有し、1つのモードを選択して動作する場合には、あるモードでは適切に動作するプリアンプであっても、他のモードでは適切に動作せず、増幅が正常に行なわれない場合がある。

【0013】

また、連續読出しありは書き込みの途中に、次のロウに移行する場合において、外部からは、WAIT信号によって、次のロウに移行するための処理（移行前のワード線の非活性化、移行後のワード線の活性化、およびセンスアンプによる増幅など）が終了されたことを知ってから、バイトマスク信号を与えなければならないという問題がある。

【0014】

また、ビット線対をプリチャージさせるために、外部からチップイネーブル信号を非活性にしなければならず、外部からの制御を要するという問題がある。

【0015】

また、Cellular RAM(R)のような半導体記憶装置では、低周波数のクロックで、かつ同期式で動作させることができないという問題がある。

【0016】

また、スタンバイ状態、または他のチップにアクセス中で、非活性になっているチップにおいて、入出力バッファが動作し続け、無駄に電流を消費するという問題がある。

50

## 【0017】

それゆえに、本発明の目的は、適切なタイミングで内部でレイテンシを設定する半導体記憶装置を提供することである。

## 【0018】

また、本発明の他の目的は、読み出しちゃは書き込みを行なうバンクと重ならないように、リフレッシュするバンクを適切に決める半導体記憶装置を提供することである。

## 【0019】

また、本発明のさらに他の目的は、複数個の擬似 S R A M を 1 つのパッケージに収容したときに、同一のタイミングでリフレッシュを行なうことができる半導体記憶装置を提供することである。

10

## 【0020】

また、本発明のさらに他の目的は、コマンドレイテンシ C L で規定されるタイミングよりも早いタイミングでデータを出力することができる半導体記憶装置を提供することである。

## 【0021】

また、本発明のさらに他の目的は、複数のモードを有し、1つのモードを選択して動作する場合には、すべてのモードでプリアンプが適切に動作するような半導体記憶装置を提供することである。

## 【0022】

また、本発明のさらに他の目的は、連続読み出しちゃは書き込みの途中に、次のロウに移行する場合においても、外部からは、次のロウに移行しない場合と同様にしてバイトマスク信号を与えることができる半導体記憶装置を提供することである。

20

## 【0023】

また、本発明のさらに他の目的は、外部からの制御を要することなく、内部の制御のみでピット線対をプリチャージさせることのできる半導体記憶装置を提供することである。

## 【0024】

また、本発明のさらに他の目的は、低周波数のクロックで、かつ同期式で動作させることができる半導体記憶装置を提供することである。

## 【0025】

また、本発明のさらに他の目的は、非活性になっているチップにおいて、入出力バッファが動作し続け、無駄に電流を消費することを防止した半導体記憶装置を提供することである。

30

## 【課題を解決するための手段】

## 【0026】

上記課題を解決するために、この発明のある局面による半導体記憶装置は、クロックに同期して動作する半導体記憶装置であって、行列状に配置された複数のメモリセルを有するメモリアレイと、トリガ信号を出力するトリガ生成回路と、トリガ信号を受けて、トリガ信号を遅延させた遅延信号を出力する遅延回路と、クロックを受け、トリガ信号を受けてから遅延信号を受けるまでの間、受けたクロックの数をカウントし、カウント結果を出力するクロックカウンタと、クロックの数とレイテンシとの対応関係を記憶し、クロックカウンタから出力されるカウント結果に対応するレイテンシを判定する判定回路と、判定されたレイテンシを保持するレジスタと、レジスタに保持されたレイテンシに基づき、外部にウエイト信号を出力するウエイト制御回路とを備える。

40

## 【0027】

この発明の別の局面による半導体記憶装置は、行列状に配置された複数のダイナミックランダムアクセスメモリのメモリセルを有し、1度のリフレッシュの単位となるバンクを複数個有するメモリアレイと、リフレッシュのトリガを出力する回路と、リフレッシュトリガを受けたときに、外部から指示された動作を実行中のときに、動作を実行中のバンクと異なるバンクを選択して、選択したバンクのアドレスを出力するバンク選択回路と、受けたアドレスのバンクのリフレッシュを実行するリフレッシュ制御回路とを備え、バンク

50

選択回路は、リフレッシュが実施済みのバンクのアドレスを保持し、すべてのバンクのアドレスが保持されると、保持されているすべてのアドレスが消去されるレジスタと、リフレッシュトリガを受けたときに、レジスタを参照してリフレッシュが未実施のバンクのアドレスを特定する特定回路と、未実施のバンクアドレスと、動作を実行中のバンクアドレスとを比較し、異なる場合に、未実施のバンクアドレスを出力する比較回路とを含む。

【0028】

この発明のさらに別の局面による半導体記憶装置は、行列状に配置された複数のダイナミックランダムアクセスメモリのメモリセルを有するメモリアレイと、リフレッシュのタイミングを規定する第1の信号を生成する第1の回路と、第1の信号を出力する出力端子と、外部からリフレッシュのタイミングを規定する第2の信号を受ける入力端子と、第1の信号および第2の信号を受けて、いずれかの信号を出力するスイッチと、スイッチから出力される信号を受けて、当該信号に基づきリフレッシュ制御を行なう第2の回路とを備える。

【0029】

この発明のさらに別の局面による半導体記憶装置は、クロックに同期して動作し、バーストモードでのアクセスを行ない、読み出し信号または書き込み信号が生成されるのに先立つて、ロウアドレスおよびコラムアドレスを取得する半導体記憶装置であって、行列上に配置された複数のメモリセルを有するメモリアレイと、外部から受けた制御信号によって読み出し信号または書き込み信号が生成された第1のクロックに同期して、選択されたロウのロウアクセス処理と、先頭から1個以上かつバーストレングス以下である第1の個数のコラムのコラムアクセス処理を行ない、レイテンシで規定される第2のクロック以降のクロックに同期して、バーストモードアクセスの残りの第2の個数のコラムのコラムアクセス処理を行なうように制御する制御回路とを備える。

【0030】

この発明のさらに別の局面による半導体記憶装置は、外部信号の組合せによって、複数の動作モードのいずれかのモードに設定される半導体記憶装置であって、行列上に配置された複数のメモリセルを有するメモリアレイと、メモリセルに各々接続されたビット線対と、ビット線対の電位を増幅する第1の増幅回路と、複数のビット線対に接続されたI/O線対と、各モードに応じていずれかが活性化され、I/O線対の電位を増幅する2種類以上の第2の増幅回路とを備える。

【0031】

この発明のさらに別の局面による半導体記憶装置は、クロックに同期して動作する半導体記憶装置であって、行列状に配置された複数のメモリセルを有するメモリアレイと、外部からバイトマスク信号を受けて、バイトマスク信号に基づきバイトマスク処理を制御するバイトマスク制御回路と、メモリセルから出力されたデータを受けて、バイトマスク制御回路による指示に従って、メモリセルから出力されたデータのバイトマスク信号に対応するバイトの出力を行なわない出力回路とを備え、バイトマスク制御回路は、連続読み出しありは連続書き込みが第1のロウと第2のロウの2つのロウに渡る場合、途中で第1のロウの最後のコラムに達したため第2のロウへの移行のためロウアクセス処理を行なっている間に、外部からバイトマスク信号を受けたときに、バイトマスク信号に対応するバイトのマスク処理を、ロウアクセスが終了し、次のビットのデータが出力されるタイミングまで延長する。

【0032】

この発明のさらに別の局面による半導体記憶装置は、クロックに同期して動作する半導体記憶装置であって、行列状に配置された複数のメモリセルを有するメモリアレイと、メモリセルに接続されたビット線対と、コラム選択信号を受けて、バーストアクセスの最後のカラムを選択する選択信号が活性化された後の次のクロックでバーストレングスリセット信号を出力するバーストレングスカウンタと、バーストレングスリセット信号を受けて、ビット線対をプリチャージする制御回路とを備える。

【0033】

10

20

30

40

50

この発明のさらに別の局面による半導体記憶装置は、クロックに同期して動作する同期モードと、非同期で動作する非同期モードとを有する半導体記憶装置であって、行列状に配置された複数のメモリセルを有するメモリアレイと、同期固定モードと、非同期固定モードと、同期および非同期の混載モードのいずれかに設定可能な設定回路と、混載モード時に、外部チップイネーブル信号がアサートされてから、外部クロックの立ち上がりまでの時間が所定値以上か否かを調べ、所定値以上のときに、非同期固定モードに移行する非同期移行回路と、同期固定モードまたは混載モードに設定されたときに同期動作を制御する同期制御回路と、非同期固定モード若しくは混載モードに設定されたとき、または非同期固定モードに移行したときに、非同期動作を制御する非同期制御回路とを備え、非同期移行回路は、設定回路の出力に応じて非活性化される。

10

#### 【0034】

この発明のさらに別の局面による半導体記憶装置は、クロックに同期して動作する半導体記憶装置であって、行列状に配置された複数のメモリセルを有するメモリアレイと、外部チップイネーブル信号を受けて内部チップイネーブル信号を生成するチップイネーブルバッファと、外部クロックを受けて内部クロックを生成するクロックバッファと、外部アドレス信号を受けて内部アドレス信号を生成するアドレスバッファと、外部チップイネーブル信号以外の外部制御信号を受けて内部制御信号を生成する制御バッファとを備え、クロックバッファ、アドレスバッファ、および制御バッファは、内部チップイネーブル信号を受けて、内部チップイネーブル信号がチップの非活性を示すときに、その動作を停止し、クロックバッファ、アドレスバッファ、および制御バッファは、内部チップイネーブル信号が活性化を示すときに、動作を実行し、制御バッファは、外部アドレス取込信号を受けて、内部アドレス取込信号を生成し、半導体記憶装置は、さらに、内部アドレス取込信号を所定の遅延量だけ遅延させる遅延回路と、遅延回路の出力と内部クロックとを受けるクロックドインバータと、クロックドインバータの出力と内部クロックとの論理積信号を出力する論理回路と、論理積信号の先頭のパルスに基づき、ロウアドレスストローブ信号を活性化する回路とを備え、論理積信号の先頭のパルスが、外部アドレス取込み信号が活性化されている間に立ち上がる外部クロックパルスから生成された内部クロックパルスとなるように、遅延回路の所定の遅延量が定められている。

20

#### 【発明の効果】

#### 【0035】

本発明のある局面による半導体記憶装置によれば適切なタイミングで内部でレイテンシを設定することができる。

30

#### 【0036】

また、本発明の別の局面による半導体記憶装置によれば、読出しありは書き込みを行なうバンクと重ならないように、リフレッシュするバンクを適切に決めることができる。

#### 【0037】

また、本発明のさらに別の局面による半導体記憶装置によれば、複数個の擬似S R A Mを1つのパッケージに収容したときに、同一のタイミングでリフレッシュを行なうことができる。

40

#### 【0038】

また、本発明のさらに別の局面による半導体記憶装置によれば、コマンドレイテンシで規定されるタイミングよりも早いタイミングでデータを出力することができる。

#### 【0039】

また、本発明のさらに別の局面による半導体記憶装置によれば、複数のモードを有し、1つのモードを選択して動作する場合には、すべてのモードでプリアンプが適切に動作するようにすることができる。

#### 【0040】

また、本発明のさらに別の局面による半導体記憶装置によれば、連続読出しありは書き込みの途中に、次のロウに移行する場合においても、外部からは、次のロウに移行しない場合と同様にしてバイトマスク信号を与えることができる。

50

## 【0041】

また、本発明のさらに別の局面による半導体記憶装置によれば、外部からの制御を要することなく、内部の制御のみでビット線対プリチャージさせることができる。

## 【0042】

また、本発明のさらに別の局面による半導体記憶装置によれば、低周波数のクロックで、かつ同期式で動作させることができる。

## 【0043】

また、本発明のさらに別の局面による半導体記憶装置によれば、非活性になっているチップにおいて、入出力バッファが動作し続け、無駄に電流を消費することを防止することができる。

10

## 【発明を実施するための最良の形態】

## 【0044】

以下、本発明の実施の形態について、図面を用いて説明する。

## 【0045】

## [第1の実施形態]

本実施の形態は、レイテンシを適切なタイミングで内部で自動的に適切な値に設定する同期式擬似S R A Mに関する。

## (構成)

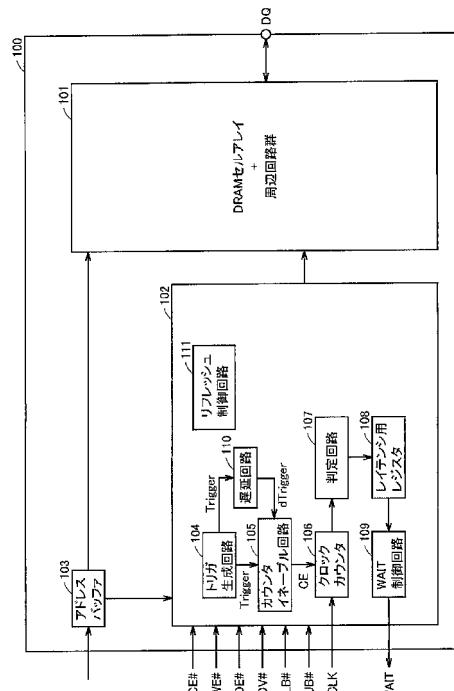

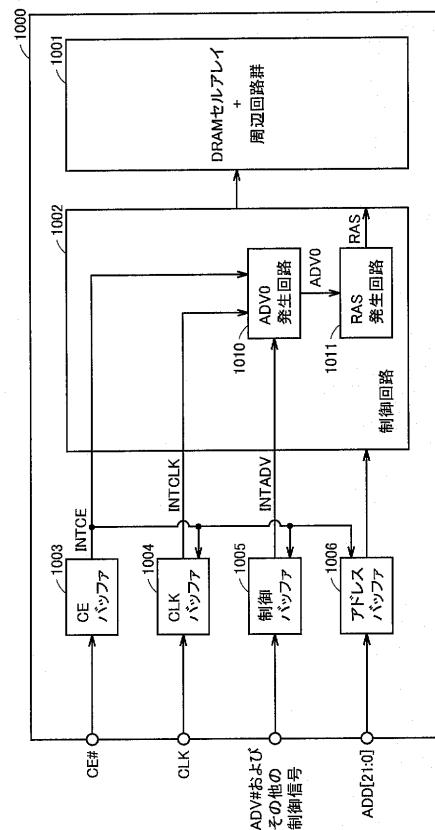

図1は、本実施の形態に係る同期式擬似S R A M 1 0 0の構成を示す。同図を参照して、この同期式擬似S R A M 1 0 0は、D R A Mセルアレイ+周辺回路群1 0 1と、アドレスバッファ1 0 3と、制御回路1 0 2とを含む。

20

## 【0046】

D R A Mセルアレイ+周辺回路群1 0 1のD R A Mセルアレイは、ダイナミックランダムアクセスメモリ(D R A M)のセルで構成されるメモリアレイである。周辺回路群1 0 1は、グローバル入出力線対G I O P(G I Oおよび/G I O)と、各列に対応して設けられた列選択線と、列選択ゲートと、センスアンプと、プリアンプと、ライトドライバと、ロウデコーダ、コラムデコーダなどを含む。

## 【0047】

アドレスバッファ1 0 3は、外部アドレス信号A D D[2 1 : 0]を受けて、内部アドレス信号を生成する。

30

## 【0048】

制御回路1 0 2は、トリガ生成回路1 0 4と、カウンタイネーブル回路1 0 5と、クロックカウンタ1 0 6と、判定回路1 0 7と、レイテンシ用レジスタ1 0 8と、W A I T制御回路1 0 9と、遅延回路1 1 0と、リフレッシュ制御回路1 1 1とを含む。

## 【0049】

リフレッシュ制御回路1 1 1は、図示しない内部のリフレッシュタイムに基づいて、D R A Mセルアレイのセルフリフレッシュ動作を制御する。

## 【0050】

トリガ生成回路1 0 4は、レイテンシの設定のトリガとなるトリガ信号T r i g g e rを出力する。

40

## 【0051】

遅延回路1 1 0は、複数段のインバータからなり、トリガ信号T r i g g e rを受けて、遅延トリガ信号d T r i g g e rを出力する。

## 【0052】

カウンタイネーブル回路1 0 5は、トリガ信号T r i g g e rが入力されてから、遅延トリガ信号d T r i g g e rが入力されるまでの間、カウンタイネーブル信号C Eを「H」にする。

## 【0053】

クロックカウンタ1 0 6は、カウンタイネーブル信号C Eが「H」の間、入力される外部クロックC L Kの数をカウントする。カウント数は、入力される外部C L Kの数と、力

50

ウントイネーブル信号 C E が「 H 」の期間、つまり遅延回路 110 でのトリガ信号 T r i g g e r の遅延量に依存する。遅延回路 110 での遅延量は、温度などの周囲環境に依存する。

【 0054 】

判定回路 107 は、クロックのカウント数と、そのカウント数で動作可能な最小のレイテンシとの対応関係を記憶する。対応関係は、クロックのカウント数が多いほど、最小のレイテンシが大きくなるように定められる。判定回路 107 は、この対応関係に基づいて、クロックカウンタ 106 から出力されるカウント数に応じた最小のレイテンシを判定し、レイテンシ用レジスタ 108 に出力する。

【 0055 】

レイテンシ用レジスタ 108 は、判定回路 107 から送られる最小のレイテンシを保存する。

【 0056 】

W A I T 制御回路 109 は、レイテンシ用レジスタ 108 に保存されている最小のレイテンシに応じた期間だけ、W A I T 信号を「 L 」にする。

【 0057 】

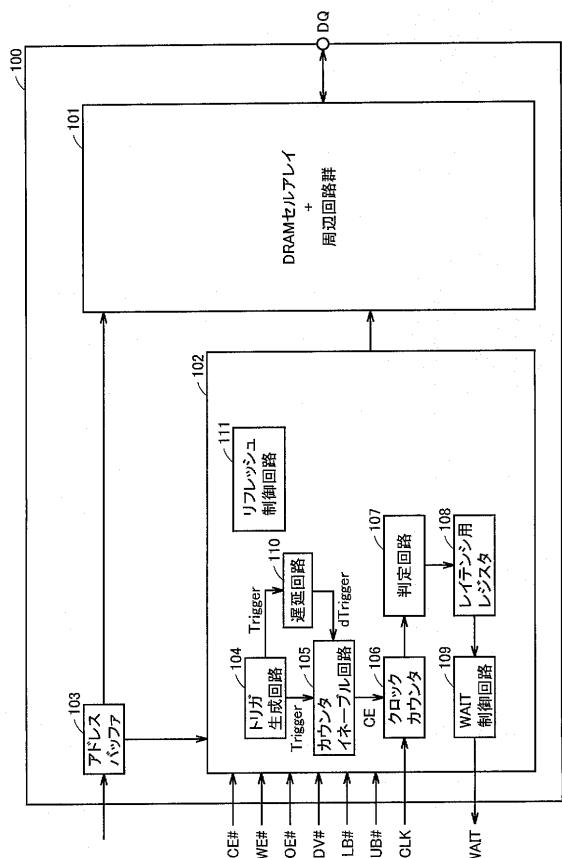

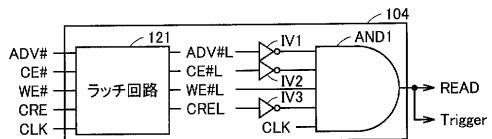

図 2 は、トリガ生成回路 104 の詳細な構成を示す。同図に示すように、トリガ生成回路 104 は、ラッチ回路 121 と、インバータ I V 1 , I V 2 , I V 3 と、論理積回路 A N D 1 とからなる。

【 0058 】

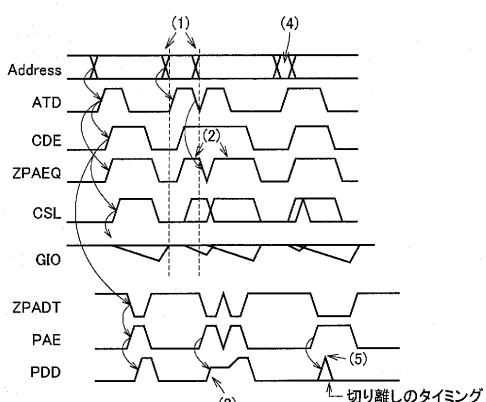

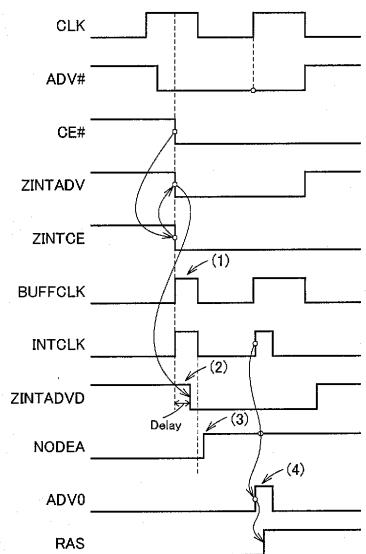

図 3 は、トリガ生成回路 104 で生成される信号のタイミングチャートである。同図を参照して、ラッチ回路 121 は、外部アドレス取込信号 A D V # をラッチして、アドレス取込ラッチ信号 A D V # L を出力する。ラッチ回路 121 は、外部チップイネーブル信号 C E # をラッチして、チップイネーブルラッチ信号 C E # L を出力する。ラッチ回路 121 は、外部ライトイネーブル信号 W E # をラッチして、ライトイネーブルラッチ信号 W E # L を出力する。ラッチ回路 121 は、外部コンフィギュレーションレジスタイネーブル信号 C R E # をラッチして、コンフィギュレーションレジスタイネーブルラッチ信号 C R E L を出力する。A N D 回路 1 は、アドレス取込ラッチ信号 A D V # L が「 L 」、チップイネーブルラッチ信号 C E # L が「 L 」、書き込みラッチ信号 W E # L が「 H 」、コンフィギュレーションレジスタイネーブルラッチ信号 C R E L が「 L 」、かつ外部クロック C L K が「 H 」のときに、読み出し信号 R E A D を「 H 」に活性化するとともに、トリガ信号 T r i g g e r を「 H 」にする。

【 0059 】

このようなトリガ信号生成回路 104 により、外部信号の論理値の組合せによって読み出し信号 R E A D が生成されて読み出しが行なわれるときに、トリガ信号 T r i g g e r も同時に生成され、レイテンシの設定が行なわれる。

【 0060 】

以上のように、本実施の形態に係る同期式擬似 S R A M によれば、読み出し信号 R E A D が生成されて、実際に読み出し処理のためにコマンドレイテンシが必要となるタイミングで、入力される外部クロック C L K の周波数および温度などの周囲環境の下で動作可能な最小の値にレイテンシを設定することができる。

【 0061 】

なお、本実施の形態では、遅延回路 101 は、複数個のインバータで構成されるものとしたが、これに限定するものではなく、たとえば、特定の回路を模擬的に再現したレプリカ回路などを用いてもよい。また、クロックカウンタ 106 は、外部クロック C L K を受けるのではなく、内部クロックを受けるものとしてもよい。

【 0062 】

また、本実施の形態は、同期式擬似 S R A M に限定して適用されるものではなく、クロックに同期して動作する半導体記憶装置であればどのようなものにも適用することができる。

10

20

30

40

50

## 【0063】

## [第1の実施形態の変形例]

第1の実施形態において、トリガ生成回路104は、読み出し信号READが生成されたことを検知して、トリガ信号triggerを生成したが、これに限定するものではない。たとえば、以下のような場合に、トリガ信号triggerを生成するものとしてもよい。

## 【0064】

(1) 書込み信号WRITEなどの他の動作指示信号が入力されたことを検知して、トリガ信号triggerを生成する。

## 【0065】

(2) 電源投入検知回路により電源が投入されたことを検知したときに、トリガ信号triggerを生成する。

## 【0066】

(3) 動作モード設定コマンド判定回路により外部信号によりレイテンシ、バースト長などのモード設定が行なわれたことを判定したときに、trigger信号を生成する。

## 【0067】

(4) 温度変化検知回路により温度変化を検知したときに、トリガ信号triggerを生成する。

## 【0068】

(5) 内部発信回路により、一定周期でトリガ信号triggerを生成する。

## 【0069】

## [第2の実施形態]

本実施の形態は、セルフリフレッシュするバンクを適切に切替えて、WAIT期間を短くした同期式擬似SRAMに関する。

## 【0070】

## (構成)

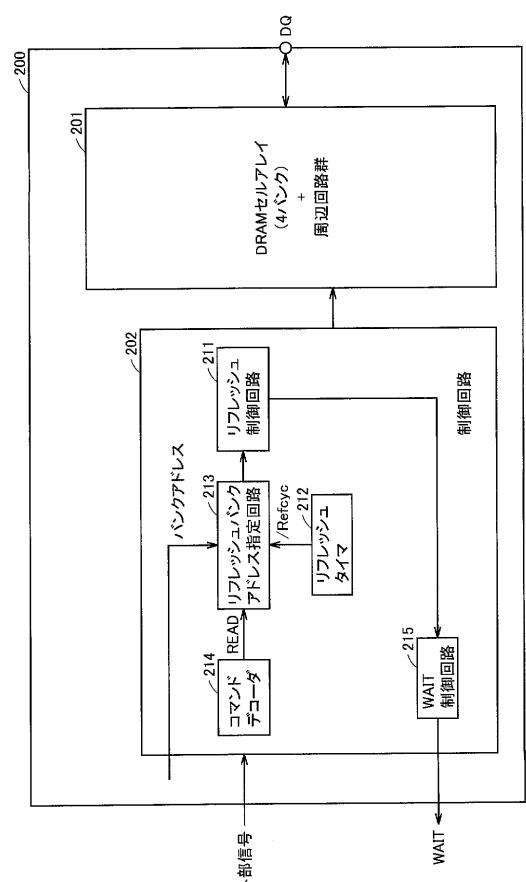

図4は、本実施の形態に係る同期式擬似SRAM200の構成を示す。同図を参照して、この同期式擬似SRAM200は、DRAMセルアレイ+周辺回路群201と、制御回路202とを備える。

## 【0071】

DRAMセルアレイ+周辺回路群201のDRAMセルアレイは、ダイナミックランダムアクセスメモリ(DRAM)のセルで構成されるメモリアレイであり、4個のバンクを有する。バンクは、DRAMセルアレイを分割したメモリセル群であって、1度のリフレッシュ動作の単位となる。つまり、1度のリフレッシュでは、1個のバンクがリフレッシュされる。

## 【0072】

周辺回路群は、グローバル入出力線対GIOP(GIOおよび/GIO)と、各列に対応して設けられた列選択線と、列選択ゲートと、センスアンプと、プリアンプと、ライトドライバと、ロウデコーダ、コラムデコーダなどを含む。

## 【0073】

制御回路202は、コマンドデコーダ214と、リフレッシュバンクアドレス指定回路213と、リフレッシュタイマ212と、リフレッシュ制御回路211と、WAIT制御回路215とを備える。

## 【0074】

コマンドデコーダ214は、外部制御信号より生成された内部制御信号の論理レベルの組合せに従って、ロウ活性化信号ACT、読み出し信号READ、および書き込み信号WRITEを生成する。

## 【0075】

リフレッシュタイマ212は、リング発振器で構成され周期的に活性化されたリフレッ

10

20

30

40

50

シュサイクル信号 /  $Ref_{yc}$  を出力する。

【0076】

リフレッシュバンクアドレス指定回路 213 は、リフレッシュサイクル信号 /  $Ref_{yc}$  と、読み出し信号 READ または書き込み信号 WRITE と、バンクアドレスとを受けて、リフレッシュするバンクのアドレスおよびそのリフレッシュのタイミングを指定する。

【0077】

リフレッシュ制御回路 211 は、リフレッシュバンクアドレス指定回路 213 からバンクアドレスのみを受けると、即座にそのアドレスのバンクのリフレッシュ動作を制御する。また、リフレッシュ制御回路 211 は、リフレッシュバンクアドレス指定回路 213 からバンクアドレスとともに、そのバンクアドレスのバンクの読み出し動作終了後にリフレッシュを行なう旨の指令を受けると、所定の時間経過した後、そのバンクのリフレッシュ動作を制御する。

【0078】

WAIT 制御回路 215 は、リフレッシュ制御回路 211 がリフレッシュ動作を制御している間、WAIT 信号のレベル「L」とする。

【0079】

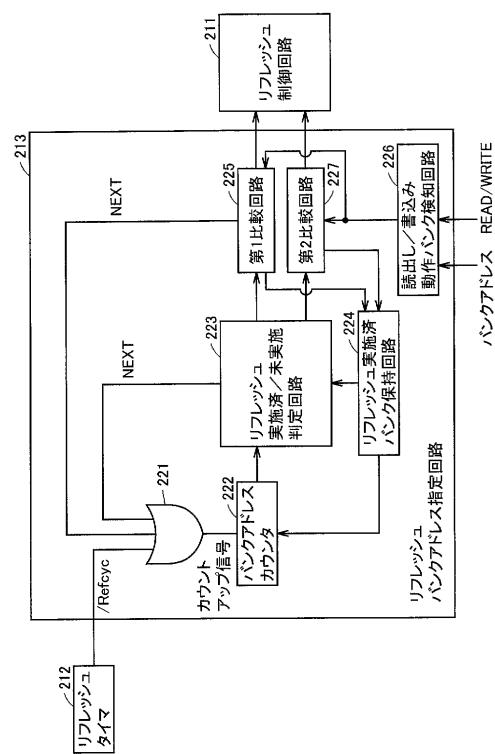

図 5 は、リフレッシュバンクアドレス指定回路 213 の詳細な構成を示す。同図を参照して、リフレッシュバンクアドレス指定回路 213 は、OR 回路 221 と、バンクアドレスカウンタ 222 と、リフレッシュ実施済 / 未実施判定回路 223 と、リフレッシュ実施済バンク保持回路 224 と、第 1 比較回路 225 と、第 2 比較回路 227 と、読み出し / 書込み動作バンク検知回路 226 とを備える。

【0080】

OR 回路 221 は、リフレッシュタイム 212 からリフレッシュサイクル信号 /  $Ref_{yc}$ 、リフレッシュ実施済 / 未実施判定回路 223 から次のバンクを指示する信号 NEXT、または第 1 比較回路 225 から次のバンク指示する信号 NEXT を受けると、カウントアップ信号を出力する。

【0081】

バンクアドレスカウンタ 222 は、カウントアップ信号を受けると、「1」～「4」の範囲でカウントをアップする。ただし。カウント値の初期値は、「0」とし、カウント「4」の次は、カウント「1」とする。

【0082】

リフレッシュ実施済バンク保持回路 224 は、リフレッシュを実施済みのバンクアドレスを保持する。リフレッシュ実施済バンク保持回路 224 は、「1」～「4」のバンクアドレスがすべて保持されたときには、保持しているバンクアドレスをすべて消去とともに、バンクアドレスカウンタ 222 のカウント値を「0」にリセットさせる。したがって、4 回のリフレッシュで、バンク 1 ～ バンク 4 のすべてのリフレッシュが完了される。

【0083】

リフレッシュ実施済 / 未実施判定回路 223 は、バンクアドレスカウンタ 222 のカウンタ値のバンクアドレスが、リフレッシュ実施済バンク保持回路 224 に保持されているか否かを調べる。リフレッシュ実施済 / 未実施判定回路 223 は、カウンタ値のバンクアドレスが保持されていない場合には、未実施と判定し、そのバンクアドレスを第 1 比較回路 225 または第 2 比較回路 227 のいずれかに出力する。ここで、リフレッシュ実施済 / 未実施判定回路 223 は、出力するバンクアドレスがリフレッシュ実施済バンク保持回路 224 に保持されていない、最後の 1 つのバンクアドレスのときには、第 2 比較回路 227 にそのバンクアドレスを出力する。リフレッシュ実施済 / 未実施判定回路 223 は、上記以外のときには、第 1 比較回路 225 にそのバンクアドレスを出力する。

【0084】

リフレッシュ実施済 / 未実施判定回路 223 は、カウンタ値のバンクアドレスが保持されている場合には、実施済みと判定し、次のバンクアドレスを指示する信号 NEXT を出力する。

10

20

30

40

50

## 【0085】

読み出し／書き込み動作バンク検知回路226は、読み出し信号READまたは書き込み信号WRITEを受けたときに、入力されるバンクアドレス（読み出しまだ書き込みを行なっているバンクのアドレス）を第1比較回路225および第2比較回路227に出力する。

## 【0086】

第1比較回路225は、読み出し／書き込み動作バンク検知回路226およびリフレッシュ実施済／未実施判定回路223から受けた2つのバンクアドレスが同一か否かを調べる。第1比較回路225は、2つのバンクアドレスが異なるときには、リフレッシュ実施済／未実施判定回路223から受けたバンクアドレスをリフレッシュ制御回路211に送るとともに、リフレッシュ実施済みバンク保持回路224にそのバンクアドレスを出力し保持させる。第1比較回路225は、2つのバンクアドレスが同一のときには、次のバンクアドレスを指示する信号NEXTを出力する。

## 【0087】

第2比較回路227は、読み出し／書き込み動作バンク検知回路226およびリフレッシュ実施済／未実施判定回路223から受けた2つのバンクアドレスが同一か否かを調べる。第2比較回路227は、2つのバンクアドレスが異なるときには、リフレッシュ実施済／未実施判定回路223から受けたバンクアドレスをリフレッシュ制御回路211に送るとともに、リフレッシュ実施済みバンク保持回路224にそのバンクアドレスを出力し保持させる。第2比較回路227は、2つのバンクアドレスが同一のときには、リフレッシュ実施済／未実施判定回路223から受けたバンクアドレスと、そのバンクアドレスのバンクの読み出し動作終了後にリフレッシュを行なう旨の指令とをリフレッシュ制御回路211に送る。

## 【0088】

（従来の同期式擬似SRAMの動作例）

まず、本実施の形態に係る同期式擬似SRAM200の動作の比較のため、従来の同期式擬似SRAMの動作を説明する。

## 【0089】

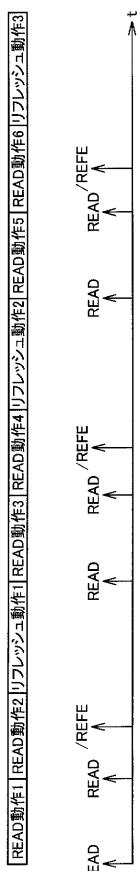

図6は、従来の同期式擬似SRAMの動作を説明するための図である。同図に示すように、外部指示による読み出し信号READに基づき、読み出し動作が行なわれている途中に、リフレッシュタイムが、リフレッシュサイクル信号/Refcycを出力したときには、リフレッシュ制御回路は、実行中の読み出し動作の終了後に、リフレッシュ動作の制御を開始する。また、WAIT制御回路は、リフレッシュ動作を実行中には外部にWAIT信号を出力する。

## 【0090】

したがって、従来の同期式擬似SRAMでは、読み出し動作のタイミングとセルフリフレッシュのタイミングとが重なった場合に、セルフリフレッシュのタイミングが遅れるとともに、外部からは、セルフリフレッシュが終了まで、読み出し指示を出すことができない。

## 【0091】

（本実施の形態の同期式擬似SRAM200の動作例1）

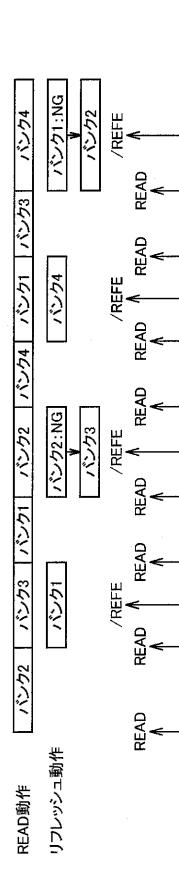

図7は、本実施の形態に係る同期式擬似SRAM200の動作例を説明するための図である。

## 【0092】

まず、外部からのバンク2を指定した読み出し信号READに基づき、バンク2の読み出し動作が行なわれる。

## 【0093】

次に、外部からのバンク3を指定した読み出し信号READに基づき、バンク3の読み出し動作が行なわれる。バンク3の読み出し動作中に、リフレッシュタイム212は、リフレッシュサイクル信号/Refcycを出力する。リフレッシュバンクアドレス指定回路213内のOR回路221は、リフレッシュサイクル信号/Refcycを受けるとカウントアップ信号を出力する。バンクアドレスカウンタ222は、バンクアドレスのカウント値

10

20

30

40

50

を「1」とする。リフレッシュ実施済／未実施判定回路223は、リフレッシュ実施済バンク保持回路224に未だ何も保持されていないので、未実施と判定し、バンクアドレス「1」を第1比較回路225に出力する。読み出し／書き込み動作バンク検知回路226は、読み出し信号READおよびバンクアドレス「3」を受けて、バンクアドレス「3」を第1比較回路225および第2比較回路227に出力する。第1比較回路225は、受けた2つのバンクアドレスが異なるので、リフレッシュ実施済／未実施判定回路223から受けたバンクアドレス「1」をリフレッシュ制御回路211に送るとともに、リフレッシュ実施済みバンク保持回路224にバンクアドレス「1」を出力し保持させる。リフレッシュ制御回路211は、バンクアドレス「1」を受けるとバンク1のリフレッシュ動作を制御する。

10

#### 【0094】

次に、外部からのバンク1を指定した読み出し信号READに基づき、バンク1の読み出し動作が行なわれる。

#### 【0095】

次に、外部からのバンク2を指定した読み出し信号READに基づき、バンク2の読み出し動作が行なわれる。バンク2の読み出し動作中に、リフレッシュタイム212は、リフレッシュサイクル信号/Refcycを出力する。リフレッシュバンクアドレス指定回路213内のOR回路221は、リフレッシュサイクル信号/Refcycを受けるとカウントアップ信号を出力する。バンクアドレスカウンタ222は、バンクアドレスのカウント値を「2」とする。リフレッシュ実施済バンク保持回路224には、バンクアドレス「1」のみが保持され、バンクアドレス「2」が保持されていないので、リフレッシュ実施済／未実施判定回路223は、未実施と判定し、バンクアドレス「2」を第1比較回路225に出力する。読み出し／書き込み動作バンク検知回路226には、読み出し信号READおよびバンクアドレス「2」を受けて、バンクアドレス「2」を第1比較回路225および第2比較回路227に出力する。第1比較回路225は、受けた2つのバンクアドレスが同一なので、次のバンク指示する信号NEXTを出力する。

20

#### 【0096】

OR回路221は、次のバンク指示する信号NEXTを受けるとカウントアップ信号を出力する。バンクアドレスカウンタ222は、バンクアドレスのカウント値を「3」とする。リフレッシュ実施済バンク保持回路224には、バンクアドレス「1」のみが保持され、バンクアドレス「3」が保持されていないので、リフレッシュ実施済／未実施判定回路223は、未実施と判定し、バンクアドレス「3」を第1比較回路225に出力する。読み出し／書き込み動作バンク検知回路226には、読み出し信号READおよびバンクアドレス「2」を受けて、バンクアドレス「2」を第1比較回路225および第2比較回路227に出力する。第1比較回路225は、受けた2つのバンクアドレスが異なるので、リフレッシュ実施済／未実施判定回路223から受けたバンクアドレス「3」をリフレッシュ制御回路211に送るとともに、リフレッシュ実施済みバンク保持回路224にバンクアドレス「3」を出力し保持させる。リフレッシュ制御回路211は、バンクアドレス「3」を受けるとバンク3のリフレッシュ動作を制御する。

30

#### 【0097】

次に、外部からのバンク4を指定した読み出し信号READに基づき、バンク4の読み出し動作が行なわれる。

40

#### 【0098】

次に、外部からのバンク1を指定した読み出し信号READに基づき、バンク1の読み出し動作が行なわれる。バンク1の読み出し動作中に、リフレッシュタイム212は、リフレッシュサイクル信号/Refcycを出力する。リフレッシュバンクアドレス指定回路213内のOR回路221は、リフレッシュサイクル信号/Refcycを受けるとカウントアップ信号を出力する。バンクアドレスカウンタ222は、バンクアドレスのカウント値を「4」とする。リフレッシュ実施済バンク保持回路224には、バンクアドレス「1」および「3」のみが保持され、バンクアドレス「4」が保持されていないので、リフレッシュ制御回路211に送るとともに、リフレッシュ実施済みバンク保持回路224にバンクアドレス「4」を出力し保持させる。リフレッシュ制御回路211は、バンクアドレス「4」を受けるとバンク4のリフレッシュ動作を制御する。

50

シユ実施済／未実施判定回路 223 は、未実施と判定し、バンクアドレス「4」を第1比較回路 225 に出力する。読み出し／書き込み動作バンク検知回路 226 には、読み出し信号 READ およびバンクアドレス「1」を受けて、バンクアドレス「1」を第1比較回路 225 および第2比較回路 227 に出力する。第1比較回路 225 は、受けた2つのバンクアドレスが異なるので、リフレッシュ実施済／未実施判定回路 223 から受けたバンクアドレス「4」をリフレッシュ制御回路 211 に送るとともに、リフレッシュ実施済みバンク保持回路 224 にバンクアドレス「4」を出力し保持させる。リフレッシュ制御回路 211 は、バンクアドレス「4」を受けるとバンク 4 のリフレッシュ動作を制御する。

#### 【0099】

次に、外部からのバンク 3 を指定した読み出し信号 READ に基づき、バンク 3 の読み出し動作が行なわれる。 10

#### 【0100】

次に、外部からのバンク 4 を指定した読み出し信号 READ に基づき、バンク 4 の読み出し動作が行なわれる。バンク 4 の読み出し動作中に、リフレッシュタイムマ 212 は、リフレッシュサイクル信号 / Refreshcyc を出力する。リフレッシュバンクアドレス指定回路 213 内の OR 回路 221 は、リフレッシュサイクル信号 / Refreshcyc を受けるとカウントアップ信号を出力する。バンクアドレスカウンタ 222 は、バンクアドレスのカウント値を「1」（循環的に更新）とする。リフレッシュ実施済バンク保持回路 224 には、バンクアドレス「1」、「3」および「4」が保持されているので、リフレッシュ実施済／未実施判定回路 223 は、実施と判定し、次のバンクを指示する信号 NEXT を出力する。 20

#### 【0101】

OR 回路 221 は、次のバンク指示する信号 NEXT を受けるとカウントアップ信号を出力する。バンクアドレスカウンタ 222 は、バンクアドレスのカウント値を「2」とする。リフレッシュ実施済バンク保持回路 224 には、バンクアドレス「1」、「3」、「4」が保持され、バンクアドレス「2」が保持されていないので、リフレッシュ実施済／未実施判定回路 223 は、未実施と判定し、バンクアドレス「2」を第2比較回路 227 に出力する。ここで、バンクアドレス「2」を第1比較回路 225 でなく、第2比較回路 227 に出力したのは、バンクアドレス「1」～「4」のうち、このバンクアドレス「2」が未実施の最後のバンクだからである。読み出し／書き込み動作バンク検知回路 226 には、読み出し信号 READ およびバンクアドレス「4」を受けて、バンクアドレス「4」を第1比較回路 225 および第2比較回路 227 に出力する。第2比較回路 227 は、受けた2つのバンクアドレスが異なるので、リフレッシュ実施済／未実施判定回路 223 から受けたバンクアドレス「2」をリフレッシュ制御回路 211 に送るとともに、リフレッシュ実施済みバンク保持回路 224 にバンクアドレス「2」を出力し保持させる。リフレッシュ制御回路 211 は、バンクアドレス「2」を受けるとバンク 2 のリフレッシュ動作を制御する。 30

#### 【0102】

リフレッシュ実施済バンク保持回路 224 は、すべてのバンクアドレス「1」～「4」を保持すると、保持しているバンクアドレスを消去するとともに、バンクアドレスカウンタ 222 に、バンクアドレスのカウント値を「0」にリセットさせる。 40

#### 【0103】

（リフレッシュバンクアドレス指令回路の動作例 2）

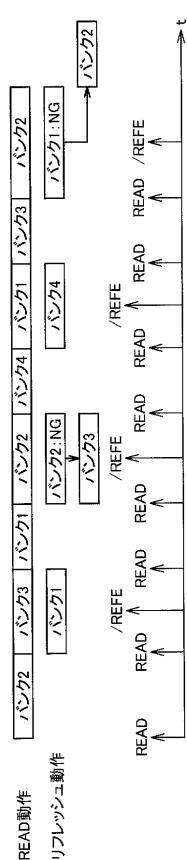

図 8 は、本実施の形態に係る同期式擬似 SRAM 200 の別の動作例を説明するための図である。

#### 【0104】

動作例 1 の最後の段階で、外部からのバンク 4 を指定した読み出し信号 READ の代りに、バンク 2 を指定した読み出し信号 READ が入力されたときの処理について説明する。

#### 【0105】

外部からのバンク 2 を指定した読み出し信号 READ に基づき、バンク 2 の読み出し動作が行なわれる。バンク 2 の読み出し動作中に、リフレッシュタイムマ 212 は、リフレッシュサ 50

イクル信号 / R e f c y c を出力する。リフレッシュバンクアドレス指定回路 213 内の OR 回路 221 は、リフレッシュサイクル信号 / R e f c y c を受けるとカウントアップ信号を出力する。バンクアドレスカウンタ 222 は、バンクアドレスのカウント値を「1」（循環的に更新）とする。リフレッシュ実施済バンク保持回路 224 には、バンクアドレス「1」、「3」および「4」が保持されているので、リフレッシュ実施済 / 未実施判定回路 223 は、実施と判定し、次のバンクを指示する信号 N E X T を出力する。

#### 【0106】

OR 回路 221 は、次のバンク指示する信号 N E X T を受けるとカウントアップ信号を出力する。バンクアドレスカウンタ 222 は、バンクアドレスのカウント値を「2」とする。リフレッシュ実施済バンク保持回路 224 には、バンクアドレス「1」、「3」、「4」が保持され、バンクアドレス「2」が保持されていないので、リフレッシュ実施済 / 未実施判定回路 223 は、未実施と判定し、バンクアドレス「2」を第 2 比較回路 227 に出力する。

#### 【0107】

ここで、バンクアドレス「2」を第 1 比較回路 225 でなく、第 2 比較回路 227 に出力したのは、バンクアドレス「1」～「4」のうち、このバンクアドレス「2」が未実施の最後のバンクだからである。読み出し / 書込み動作バンク検知回路 226 には、読み出し信号 R E A D およびバンクアドレス「2」を受けて、バンクアドレス「2」を第 1 比較回路 225 および第 2 比較回路 227 に出力する。第 2 比較回路 227 は、受けた 2 つのバンクアドレスが同一なので、リフレッシュ実施済 / 未実施判定回路 223 から受けたバンクアドレス「2」と、バンク 2 の読み出し動作終了後にリフレッシュを行なう旨の指令とをリフレッシュ制御回路 211 に送るとともに、リフレッシュ実施済みバンク保持回路 224 にバンクアドレス「2」を出力し保持させる。リフレッシュ制御回路 211 は、バンクアドレス「2」と、バンク 2 の読み出し動作終了後にリフレッシュを行なう旨の指令を受けると、所定の時間経過した後、バンク 2 のリフレッシュ動作を制御する。

#### 【0108】

リフレッシュ実施済バンク保持回路 224 は、すべてのバンクアドレス「1」～「4」を保持すると、保持しているバンクアドレスを消去するとともに、バンクアドレスカウンタ 222 に、バンクアドレスのカウント値を「0」にリセットさせる。

#### 【0109】

以上のように、本実施の形態に係る同期式擬似 S R A M によれば、読み出しまだ書込みを行なうバンクと重ならず、かつリフレッシュが未実施のバンクがリフレッシュするバンクが決められるので、セルフリフレッシュのタイミングが遅れることなく、かつ公平な頻度でリフレッシュを行なうことができる。

#### 【0110】

なお、本実施の形態では、1 回～4 回、および 5 回～8 回などの各 4 回のセルフリフレッシュにおいて、4 個のバンクすべてのリフレッシュを完了するものとしたが、これに限定するものではない。たとえば、8 回のセルフリフレッシュごとに 4 個すべてのリフレッシュを完了するものとしてもよい。この場合には、動作例 2 では、4 回目のバンク 2 のセルフリフレッシュのタイミングを遅らせないようにすることができる。また、外部のシステム側が読み出し信号 R E A D に先立って、読み出すバンクアドレスのスケジュールを指定できるものとしてもよい。この場合には、スケジュール指定されたバンクアドレスの読み出しと重ならず、かつリフレッシュ回数がすべてのバンクで均等になるように、リフレッシュするバンクアドレスのスケジュールを設定することができる。

#### 【0111】

また、本実施の形態の動作例では、読み出し動作中にリフレッシュ要求が発生する場合について説明したが、書込み動作中にリフレッシュ要求が発生する場合についても、同様にして処理される。

#### 【0112】

また、本実施の形態は、同期式擬似 S R A M に限定して適用されるものではなく、クロ

10

20

30

40

50

ックに同期して動作しない擬似 S R A M にも適用可能である。

【 0 1 1 3 】

[ 第 3 の 実 施 形 態 ]

本実施の形態は、複数個の同期式擬似 S R A M を 1 つ の パッケージ に 収容 し、複数個の同期式擬似 S R A M の リフレッシュ の タイミング を 同一 に する 構成 に 関する。

【 0 1 1 4 】

( 構 成 )

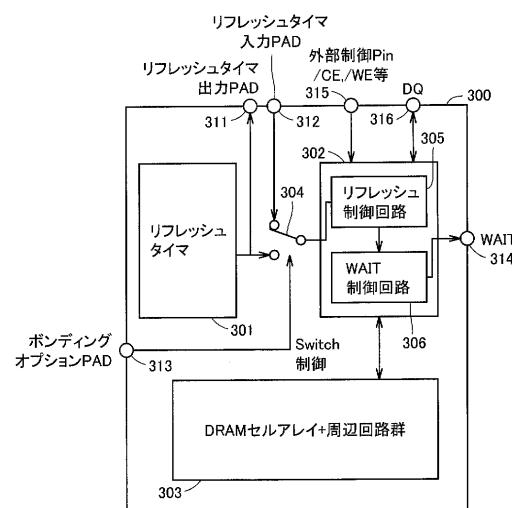

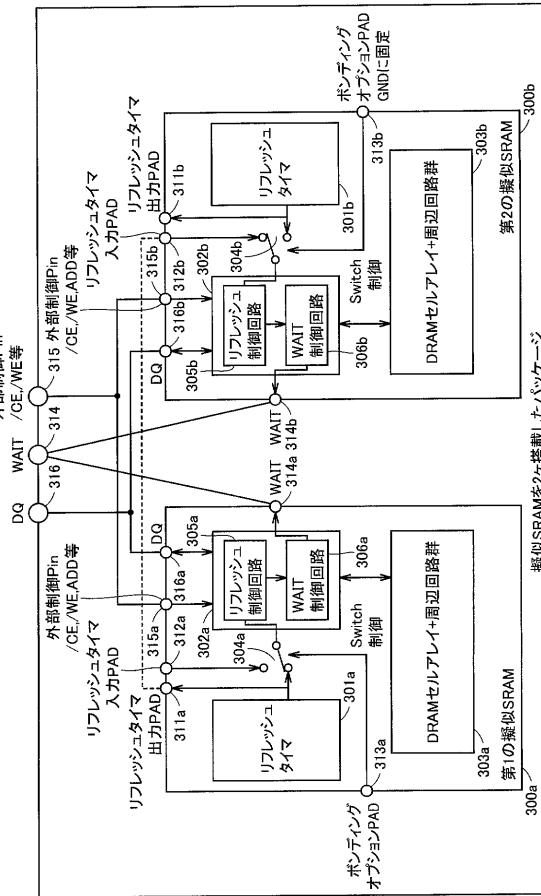

図 9 は、本実施の形態に係る 1 つ の パッケージ に 収容 される 各 同期式 擬似 S R A M 3 0 0 の 構成 を 示す。この 同期式 擬似 S R A M 3 0 0 は、リフレッシュ タイマ 3 0 1 と、制御回路 3 0 2 と、D R A M セルアレイ + 周辺回路群 3 0 3 と、スイッチ 3 0 4 と を 含む。

10

【 0 1 1 5 】

D R A M セルアレイ + 周辺回路群 3 0 3 の D R A M セルアレイ は、ダイナミックランダムアクセスメモリ ( D R A M ) の セル で 構成 さ れる メモリアレイ である。周辺回路群 は、グローバル入出力線対 G I O P ( G I O および / G I O ) と、各列に 対応 して 設けられた 列選択線と、列選択ゲートと、センスアンプと、プリアンプと、ライトドライバと、ロウデコーダ、コラムデコーダなどを 含む。

【 0 1 1 6 】

制御回路 3 0 2 は、制御信号端子 3 1 5 を介して 外部制御信号 を 受ける とともに、データ入出力端子 3 1 6 を介して D R A M セルアレイへの 書込みデータ を 受け て、これらに 基づいて、この 同期式 擬似 S R A M 3 0 0 全体の 处理 を 制御 す る とともに、データ入出力端子 3 1 6 を介して、D R A M セルアレイからの 読出しデータ を 出力 す る。また、制御回路 3 0 2 は、リフレッシュ制御回路 3 0 5 と、W A I T 制御回路 3 0 6 と を 含む。

20

【 0 1 1 7 】

リフレッシュ タイマ 3 0 1 は、 リング発振器 で 構成 さ れ 周期 的 に 活性 化 さ れた リフレッシュ サイクル 信号 / R e f c y c を スイッチ 3 0 4 お よび リフレッシュ タイマ 出力 P A D 3 1 1 に 出力 す る。リフレッシュ タイマ 出力 P A D 3 1 1 に 与え られ た リフレッシュ サイクル 信号 / R e f c y c は、他の 同期式 擬似 S R A M に 送 られる。

【 0 1 1 8 】

リフレッシュ タイマ 入力 P A D 3 1 2 は、他の 同期式 擬似 S R A M の リフレッシュ タイマ から の リフレッシュ サイクル 信号 / R e f c y c を 受け す。

30

【 0 1 1 9 】

ボンディングオプション P A D 3 1 3 は、印可された 電位 に 応じて スイッチ 3 0 4 を 制御 す る。

【 0 1 2 0 】

スイッチ 3 0 4 は、リフレッシュ タイマ 3 0 1 から の リフレッシュ サイクル 信号 / R e f c y c お よび リフレッシュ タイマ 入力 P A D 3 1 2 から の リフレッシュ サイクル 信号 / R e f c y c を 受け す。2 つ の リフレッシュ サイクル 信号 / R e f c y c は、周 期 は 同一 である が、 タイミング が 異なる。

【 0 1 2 1 】

スイッチ 3 0 4 は、ボンディングオプション P A D 3 1 3 の 印可電位 に 応じて、受けた リフレッシュ サイクル 信号 / R e f c y c の い ずれ か を リフレッシュ 制御回路 3 0 5 に 出力 す る。すなわち、スイッチ 3 0 4 は、ボンディングオプション P A D 3 1 3 に 接地電位 が 印可 さ れた とき に、リフレッシュ タイマ 入力 P A D 3 1 2 から の リフレッシュ サイクル 信号 / R e f c y c を 出力 し、接地電位 以外 の 電位 が 印可 さ れた とき に、リフレッシュ タイマ 3 0 1 から の リフレッシュ サイクル 信号 / R e f c y c を 出力 す。

40

【 0 1 2 2 】

リフレッシュ 制御回路 3 0 5 は、セルフ リフレッシュ の 制御 を 行なう。

【 0 1 2 3 】

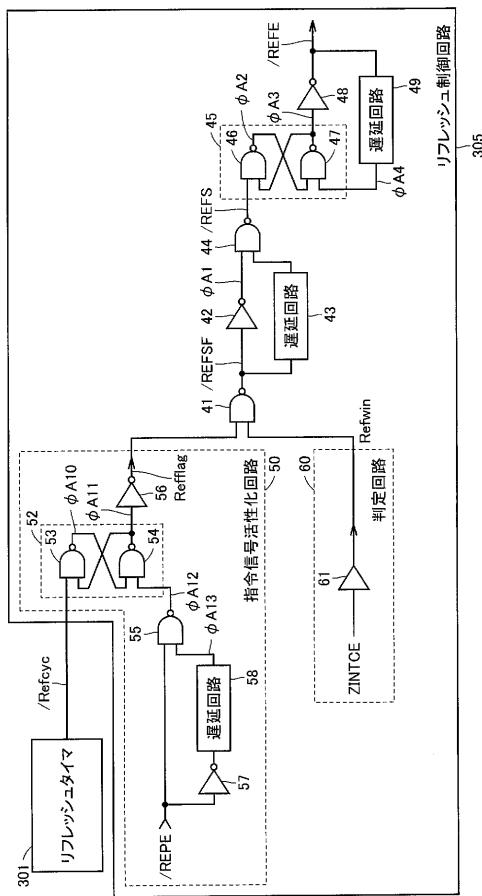

図 1 0 は、リフレッシュ 制御回路 3 0 5 の 詳細 な 構成 を 示す。同図を 参照 して、リフレッシュ 制御回路 3 0 5 は、指令信号活性 化回路 5 0 と、判定回路 6 0 と、N A N D ゲート

50

41, 44と、インバータ42と、バッファ48と、遅延回路43, 49と、フリップフロップ45とを含む。

【0124】

指令信号活性化回路50はリフレッシュ指令信号/R E F Eを活性化させるためにリフレッシュフラッグ信号R e f f l a gを出力する。判定回路60は、リフレッシュフラッグ信号R e f f l a gにより活性化されたリフレッシュ指令信号/R E F Eを出力するか否かを判定するために判定信号R e f w i nを出力する。

【0125】

N A N Dゲート41は、リフレッシュフラッグ信号R e f f l a gと判定信号R e f w i nとを受け、リフレッシュフラッグ信号R e f f l a gと判定信号R e f w i nとの論理積を演算し、その演算結果を反転した信号を反転論理積信号/R E F S Fとして出力する。

【0126】

インバータ42はN A N Dゲート41から出力された信号/R E F S Fを受けて反転した信号A1を出力する。また、遅延回路43は反転論理積信号/R E F S Fを受けて一定時間遅延させる。

【0127】

N A N Dゲート44はインバータ42の出力信号A1と遅延回路43の出力信号とを受け、信号A1と遅延回路43の出力信号との論理積を演算し、その演算結果を反転した信号/R E F Sを出力する。

【0128】

フリップフロップ45はN A N Dゲート46および47で構成される。N A N Dゲート46は信号/R E F SとN A N Dゲート47から出力された出力信号A3とを受け、信号/R E F Sと信号A3との論理積を演算し、その演算結果を反転した信号A2を出力する。N A N Dゲート47はN A N Dゲート46から出力された信号A2と遅延回路49から出力された信号A4とを受け、信号A2と信号A4との論理積を演算し、その演算結果を反転した信号をリフレッシュ指令信号/R E F Eとして出力する。リフレッシュ指令信号/R E F Eの活性化に応じて、リフレッシュ動作が行なわれる。

【0129】

遅延回路49は、フリップフロップ45から出力されたリフレッシュ指令信号/R E F Eを受けて一定時間遅延させた信号A4を出力する。

【0130】

バッファ48は信号A3を受けてリフレッシュ指令信号/R E F Eを出力する。

【0131】

指令信号活性化回路50は、フリップフロップ52と、N A N Dゲート55と、インバータ56および57と、遅延回路58とを含む。

【0132】

フリップフロップ52は、N A N Dゲート53および54で構成される。N A N Dゲート53はリフレッシュサイクル信号/R e f c y cとN A N Dゲート54の出力信号A11とを受け、リフレッシュサイクル信号/R e f c y cと信号A11との論理積を演算し、その演算結果を反転した信号A10を出力する。また、N A N Dゲート54は、N A N Dゲート53から出力された出力信号A10と、N A N Dゲート55から出力された出力信号A12とを受け、信号A10と信号A12との論理積を演算し、その演算結果を反転した信号A11を出力する。

【0133】

インバータ56は、フリップフロップ52から出力された信号A11を受け、反転し、反転した信号をリフレッシュフラッグ信号R e f f l a gとして出力する。

【0134】

インバータ57は、リフレッシュ指令信号/R E F Eを受け、反転する。また、遅延回路58は、インバータ57により反転されたリフレッシュ指令信号/R E F Eを受け、反

10

20

30

40

50

転されたリフレッシュ指令信号 / R E F F E を一定時間遅延させた信号 A 1 3 を出力する。

【 0 1 3 5 】

N A N D ゲート 5 5 は、リフレッシュ指令信号 / R E F F E と遅延回路 5 8 から出力された信号 A 1 3 とを受け、リフレッシュ指令信号 / R E F F E と信号 A 1 3 との論理積を演算し、その演算結果を反転した信号 A 1 2 を出力する。

【 0 1 3 6 】

判定回路 6 0 はバッファ回路 6 1 で構成される。バッファ回路 6 1 は内部チップイネーブル信号 Z I N T C E を受け、判定信号 R e f w i n を出力する。

【 0 1 3 7 】

再び、図 9 を参照して、W A I T 制御回路 3 0 6 は、リフレッシュ制御回路 3 0 5 の制御によりリフレッシュ制御が行なわれている間、W A I T 端子 3 1 4 を介して出力するW A I T 信号のレベルを「 L 」とする。

【 0 1 3 8 】

( パッケージ )

図 1 1 は、本実施の形態に係る 2 個の同期式擬似 S R A M を収納したパッケージの構成を示す。同図を参照して、第 1 の同期式擬似 S R A M 3 0 0 a および第 2 の同期式擬似 S R A M 3 0 0 b は、それぞれ、図 9 の同期式擬似 S R A M と同様の構成である。第 1 の同期式擬似 S R A M 3 0 0 a のボンディングオプション P A D 3 1 3 a は、開放されており、スイッチ 3 0 4 a は、リフレッシュタイム 3 0 1 a から出力されたリフレッシュサイクル信号 / R e f c y c をリフレッシュ制御回路 3 0 5 a に送る。

【 0 1 3 9 】

一方、第 2 の同期式擬似 S R A M 3 0 0 b のボンディングオプション P A D 3 1 3 b は、接地電位が与えられ、スイッチ 3 0 4 b は、リフレッシュタイム入力 P A D 3 1 2 b を通じて受けた第 1 の同期式擬似 S R A M 3 0 0 a のリフレッシュタイム 3 0 1 a から出力されたリフレッシュサイクル信号 / R e f c y c をリフレッシュ制御回路 3 0 5 b に送る。これにより、リフレッシュ制御回路 3 0 5 a および 3 0 5 b は、いずれもリフレッシュタイム 3 0 1 a のリフレッシュサイクル信号 / R e f c y c により動作するので、第 1 の同期式擬似 S R A M 3 0 0 a および 3 0 0 b のリフレッシュのタイミングが同一となる。

W A I T 制御回路 3 0 6 a は、W A I T 端子 3 1 4 a および 3 1 4 を通じてW A I T 信号を出力し、W A I T 制御回路 3 0 6 b は、W A I T 端子 3 1 4 b および 3 1 4 を通じてW A I T 信号を出力する。リフレッシュ制御回路 3 0 5 a および 3 0 5 b のリフレッシュのタイミングが同一となるので、各W A I T 信号が「 L 」に変化するタイミングも同一となる。

【 0 1 4 0 】

以上のように、複数個の同期式擬似 S R A M において、リフレッシュ中により、外部から指示された動作を受け付けることができない旨を知らせるW A I T のレベル変化のタイミングを同一にすることができる。

【 0 1 4 1 】

なお、本実施の形態では、2 個の同期式擬似 S R A M を搭載したパッケージを例にして説明したが、2 個以上の任意の個数の同期式擬似 S R A M を搭載させるものとしてもよい。

【 0 1 4 2 】

また、本実施の形態では、複数の同期式擬似 S R A M で、リフレッシュサイクル信号 / R e f c y c を共用することとし、リフレッシュタイム出力 P A D を通じて自己のリフレッシュサイクル信号 / R e f c y c を出力し、リフレッシュタイム入力 P A D を通じて、他の同期式擬似 S R A M のリフレッシュサイクル信号 / R e f c y c を受けたが、これに限定するものではない。たとえば、複数の同期式擬似 S R A M でリフレッシュフラッグ信号 R e f f 1 a g 、反転論理積信号 / R E F S F 、またはリフレッシュ指令信号 / R E F E を共用することとし、リフレッシュタイム出力 P A D およびリフレッシュタイム入力 P

10

20

30

40

50

A Dを通じて、これらの信号の授受を行なうこととしてもよい。

【0143】

さらに、本実施の形態では、複数の同期式擬似 S R A M がそれぞれの W A I T 信号を出力したが、これに限定するものではない。たとえば、W A I T 制御回路 3 0 6 a と W A I T 端子 3 1 4 a の間、および W A I T 制御回路 3 0 6 b と W A I T 端子 3 1 4 b の間に、それぞれボンディングオプション P A D で制御できるスイッチを設け、一方のスイッチのみ、W A I T 端子と W A I T 制御回路とが接続するように制御することによって、1 つの同期式擬似 S R A M からのみ W A I T 信号を出力するものとしてもよい。

【0144】

さらに、複数個の同期式擬似 S R A M が W A I T 信号を出力しない場合、つまり、セルフリフレッシュのタイミングと、外部からの読み出し信号 R E A D または書き込み信号 W R I T E のタイミングとが重なったときに、読み出し信号 R E A D または書き込み信号 W R I T E を保持しておき、セルフリフレッシュ終了後に、読み出し動作または書き込み動作を行なう場合においては、リフレッシュサイクル信号 / R e f c y c のみを共用するものとしてもよい。つまり、W A I T の制御は行なわない。この場合においても、複数個の同期式擬似 S R A M が同時にリフレッシュを行なうので、信号の干渉が起こりにくいという一定の効果がある。

【0145】

また、本実施の形態は、同期式擬似 S R A M に限定して適用されるものではなく、クロックに同期して動作しない擬似 S R A M にも適用可能である。

【0146】

〔第4の実施形態〕

本実施の形態は、バースト読み出し／書き込みにおいて、読み出しありは書き込み信号が生成された第1のクロックに従って先頭から数個のビットの読み出し／書き込みを行ない、コマンドレイテンシ C L で規定される第2のクロック以降のクロックに従って、残りのビットの読み出し／書き込みを行なう同期式擬似 S R A M に関する。

【0147】

(構成)

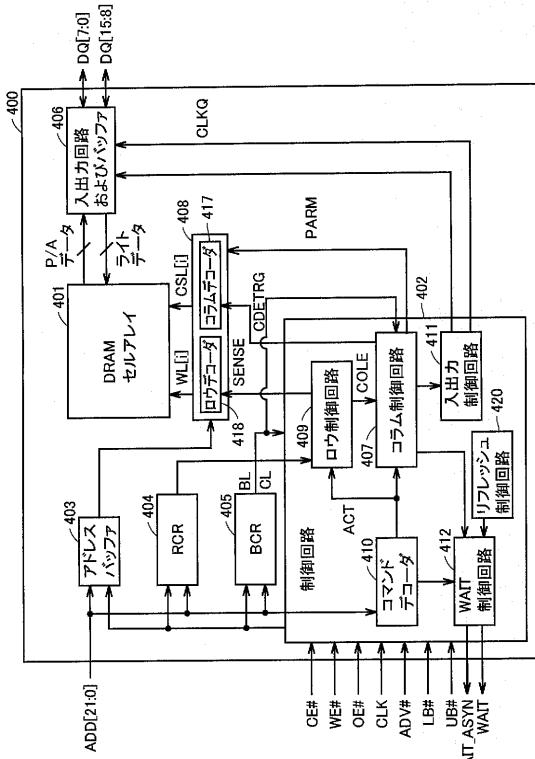

図 12 は、本実施の形態に係る同期式擬似 S R A M 4 0 0 の構成を示す。同図を参照して、この同期式擬似 S R A M 4 0 0 は、D R A M セルアレイ 4 0 1 と、制御回路 4 0 2 と、アドレスバッファ 4 0 3 と、R C R (Refresh Configuration Register) 4 0 4 と、B C R 4 0 5 (Bus Configuration Register) と、入出力回路およびバッファ 4 0 6 とを備える。

【0148】

D R A M セルアレイ 4 0 1 は、ダイナミックランダムアクセスメモリ (D R A M) のセルで構成されるメモリアレイである。

【0149】

入出力回路およびバッファ 4 0 6 は、データ入出力端子 D Q を通じて、外部のシステム側との間でデータの入出力を行なう。入出力回路およびバッファ 4 0 6 は、入出力制御回路 4 1 1 から与えられるクロック信号 C L K Q に同期して、D R A M セルから出力されたデータを出力する。

【0150】

R C R 4 0 4 は、セルフリフレッシュの方法を規定する。

【0151】

B C R 4 0 5 は、外部のシステムとのインターフェース、たとえば、バーストレングス B L 、およびコマンドレイテンシ C L などを記憶する。

【0152】

アドレスバッファ 4 0 3 は、外部アドレス信号 A D D [ 2 1 : 0 ] を受けて、内部アドレス信号を生成する。同期式擬似 S R A M では、アドレスバッファ 4 0 3 は、外部アドレス取込み信号 A D V # が「 L 」のときに、外部アドレス信号 A D D [ 2 1 : 0 ] を取込む

10

20

30

40

50

。外部アドレス取込信号 A D V # が「 L 」となるタイミングは、読み出し信号 R E A D または書き込み信号 W R I T E が生成されるタイミングよりも早い。そして、このとき与えられる外部アドレス信号 A D D [ 2 1 : 0 ] は、ロウアドレスだけでなくコラムアドレスも含む。したがって、ロウアドレスおよびコラムアドレスは、読み出し信号 R E A D または書き込み信号 W E I T E が生成されるよりも先立って、取得される。

#### 【 0 1 5 3 】

このように、ロウアドレスだけでなくコラムアドレスも、読み出し信号 R E A D または書き込み信号が生成されるのに先立った取得できるので、ロウアクセスの後、コマンドレイテンシ C L で規定されるクロックが入力されるまで待たずに、コラムアクセスを開始することができる。本実施の形態では、このような特徴を利用して、読み出し信号 R E A D または書き込み信号が生成されたときのクロック（第 1 のクロックという）に従って、バーストアクセスの先頭のコラムのデータを読み出すためのコラムアクセス処理を行なう。そして、コマンドレイテンシ C L で規定されるクロック（第 2 のクロックという）に従って、バーストアクセスの残りのコラムのデータを読み出すためのコラムアクセス処理を行なう。

10

#### 【 0 1 5 4 】

制御回路 4 0 2 は、コマンドデコーダ 4 1 0 と、入出力制御回路 4 1 1 と、ロウ制御回路 4 0 9 と、コラム制御回路 4 0 7 と、W A I T 制御回路 4 1 2 と、リフレッシュ制御回路 4 2 0 とを含む。

20

#### 【 0 1 5 5 】

コマンドデコーダ 4 1 0 は、外部制御信号より生成された内部制御信号の論理レベルの組合せに従って、ロウ活性化信号 A C T 、読み出し信号 R E A D 、および書き込み信号 W R I T E を生成する。

20

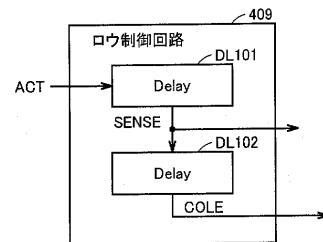

#### 【 0 1 5 6 】

ロウ制御回路 4 0 9 は、コラムイネーブル信号 C O L E 、メモリセルとグローバルビット線対 G I O , Z G I O との間に設けられたビット線対 B L , Z B L に接続されたセンスアンプを活性化させるセンスアンプ活性化信号 S E N S E を生成する。図 1 3 は、ロウ制御回路 4 0 9 の構成を示す。同図を参照して、遅延回路 ( D e l a y ) D L 1 0 1 は、読み出し信号 R E A D または書き込み信号 W R I T E が生成されたクロックである第 1 クロック C L K 0 の立ち上がりに応じて活性化されるロウ活性化信号 A C T を受ける。遅延回路 ( D e l a y ) D L 1 0 1 は、ロウ活性化信号 A C T を遅延させたセンスアンプ活性化信号 S E N S E を出力する。遅延回路 ( D e l a y ) D L 1 0 2 は、センスアンプ活性化信号 S E N S E を受けて、センスアンプ活性化信号 S E N S E を遅延させたコラムイネーブル信号 C O L E を生成する。

30

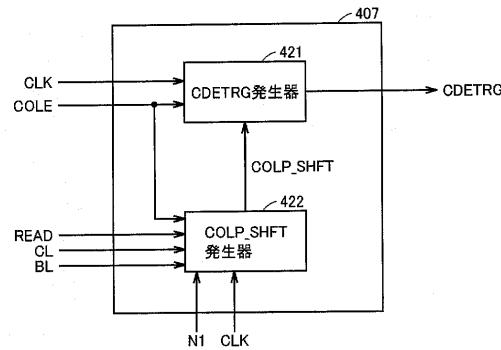

#### 【 0 1 5 7 】

コラム制御回路 4 0 7 は、グローバルビット線対 G I O , Z G I O に接続されたプリアンプを活性化させるプリアンプ活性化信号 P A R M と、コラムデコーダ活性化トリガ信号 C D E T R G を生成する。図 1 4 は、コラム制御回路 4 0 7 の構成の一部を示す。同図を参照して、コラム制御回路 4 0 7 は、 C O L P \_ S H F T 発生器 4 2 2 と、 C D E T R G 発生器 4 2 1 とを備える。

40

#### 【 0 1 5 8 】

C O L P \_ S H F T 発生器 4 2 2 は、外部クロック C L K 、読み出し信号 R E A D ( または書き込み信号 W R I T E ) 、コマンドレイテンシ C L 、読み出し信号 R E A D ( または書き込み信号 W R I T E ) が生成されたときのクロックである第 1 のクロック C L K 0 で読み出すビット数 N 1 ( 本実施の形態では「 1 」である ) 、およびバーストレングス B L に基づいて、コラムシフト信号 C O L P \_ S H F T を生成する。すなわち、 C O L P \_ S H F T 発生器 4 2 2 は、読み出し信号 R E A D ( または書き込み信号 W R I T E ) が生成されたときのクロックの後の、 ( C L - N 1 ) 個目のクロック C L K の立ち下りに応じて、コラムシフト信号 C O L P \_ S H F T を活性化し、バーストレングスカウンタのカウンタ値がバーストレングス B L になったことに応じて、コラムシフト信号 C O L P \_ S H F T を非活性化する。

50

## 【0159】

C D E T R G 発生器 421 は、コラムシフト信号 C O L P \_ S H F T 、外部クロック C L K 、およびコラムイネーブル信号 C O L E に基づいて、コラムデコーダ活性化トリガ信号 C D E T R G を生成する。

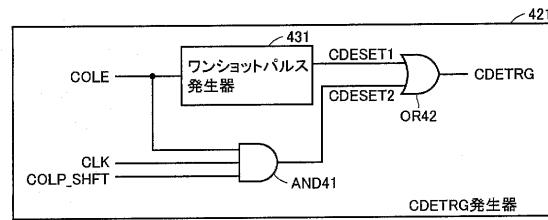

## 【0160】

図15は、C D E T R G 発生器 421 の詳細な構成を示す。同図を参照して、C D E T R G 発生器 421 は、ワンショットパルス発生器 431 と、論理積回路 A N D 41 と、論理和回路 O R 42 とを備える。ワンショットパルス発生器 431 は、コラムイネーブル信号 C O L E の立ち上がりで、レベルが「H」のワンショットパルスを生成する。このワンショットパルスは、第1のクロック C L K 0 に同期してアクセスされる第1番目のコラムを活性化させる信号となる。

10

## 【0161】

論理積回路 A N D 41 は、コラムイネーブル信号 C O E が「H」であり、C O L P \_ S H F T が「H」のときに、レベルが「H」のクロックパルスを出力する。このクロックパルスが、第2のクロック C L K 2 以降のクロックに同期してアクセスされる第2番目～第4番目のコラムを活性化させる信号となる。

20

## 【0162】

論理和回路 O R 42 は、ワンショットパルス発生器 431 から出力されるワンショットパルス、および論理積回路 A N D 41 から出力されるクロックパルスを合成する。合成されたパルスがコラムデコーダ活性化トリガ信号 C D E T R G のパルスとなる。

20

## 【0163】

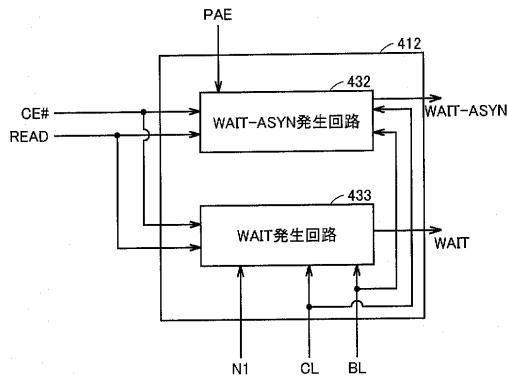

図16は、W A I T 制御回路 412 の構成を示す。同図を参照して、このW A I T 制御回路 412 は、W A I T \_ A S Y N 発生回路 432 と、W A I T 発生回路 433 とを備える。

30

## 【0164】

W A I T \_ A S Y N 発生回路 432 は、コマンドデコーダ 410 から読み出し信号 R E A D または書き込み信号 W R I T E が入力され、かつ外部チップイネーブル信号 C E # が「L」に活性化されていることに応じて、W A I T \_ A S Y N 信号を「L」にする。その後、W A I T \_ A S Y N 発生回路 432 は、プリアンプ活性化信号 P A E を受けた後、先頭のビットのデータ D 0 がデータ出力端子 D Q から出力されるのに要する所定時間の経過後、W A I T \_ A S Y N 信号を「H」にする。その後、W A I T \_ A S Y N 発生回路 432 は、外部チップイネーブル信号 C E # が「H」に非活性化されたことに応じて、W A I T \_ A S Y N 信号を H i - Z にする。

30

## 【0165】

W A I T 発生回路 433 は、コマンドデコーダ 410 から読み出し信号 R E A D または書き込み信号 W R I T E が入力され、かつ、外部チップイネーブル信号 C E # が「L」に活性化されていることに応じて、W A I T 信号を「L」にする。その後、W A I T 発生回路 433 は、( C L - 1 ) + ( 読出し信号 R E A D または書き込み信号 W R I T E が生成されたときのクロックである第1のクロック C L K 0 で読み出すビット数 N 1 ) の個数のクロックを受けた後、W A I T 信号を「H」に活性化する。その後、W A I T 発生回路 433 は、外部チップイネーブル信号 C E # が「H」に非活性化されたことに応じて、W A I T 信号を H i - Z にする。

40

## 【0166】

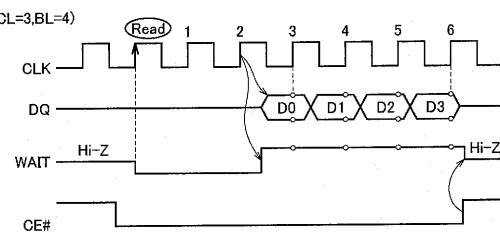

( 従来の同期式擬似 S R A M の W A I T 信号のタイミング )

図17は、従来の同期式擬似 S R A M の W A I T 信号のタイミングを表す図である。同図に示すように、読み出し信号 R E A D が入力され、かつ、外部チップイネーブル信号 C E # が「L」に活性化されていることに応じて、W A I T 信号は、「L」になる。その後、( C L - 1 ) ( C L = 3 ) の個数のクロックを受けた後、W A I T 信号が「H」になる。その後、外部チップイネーブル信号 C E # が「H」に非活性化されたことに応じて、W A I T 信号は、H i - Z になる。

50

## 【0167】

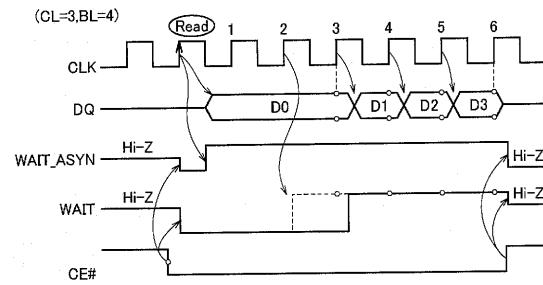

(本実施の形態の同期式擬似S R A M 4 0 0のW A I T \_ A S Y N信号およびW A I T信号のタイミング)

図18は、本実施の形態の同期式擬似S R A M 4 0 0のW A I T \_ A S Y N信号およびW A I T信号のタイミングを表す図である。同図に示すように、読み出し信号R E A Dが入力され、かつ、外部チップイネーブル信号C E #が「L」に活性化されていることに応じて、W A I T \_ A S Y N信号は、「L」になる。その後、プリアンプ活性化信号P A Eを受けた後、先頭のビットのデータD 0がデータ出力端子D Qから出力されるのに要する所定時間の経過後、W A I T \_ A S Y N信号は、「H」になる。これにより、クロックC L K 0に従ってコラムアクセスが行なわれる先頭のビットのデータD 0が出力されるタイミングを外部のシステム側に通知することができる。その後、外部チップイネーブル信号C E #が「H」に非活性化されたことに応じて、W A I T \_ A S Y N信号はH i - Zになる。

## 【0168】

また、同図に示すように、読み出し信号R E A Dが入力され、かつ、外部チップイネーブル信号C E #が「L」に活性化されていることに応じて、W A I T信号は、「L」になる。その後、(C L - 1 + N 1)(C L = 3、N 1 = 1)の個数のクロックを受けた後、W A I T信号が「H」になる。これにより、コマンドレイテンシC Lに基づいて定められるクロックに同期してコラムアクセスが行なわれる先頭のビットのデータD 1が出力されるタイミングを外部のシステム側に通知することができる。その後、外部チップイネーブル信号C E #が「H」に非活性化されたことに応じて、W A I T信号は、H i - Zになる。

## 【0169】

再び、図12を参照して、周辺回路群408は、ロウデコーダ418と、コラムデコーダ417と、図示しないセンスアンプと、図示しないプリアンプとを含む。

## 【0170】

ロウデコーダ418は、選択されたワード線を活性化する。

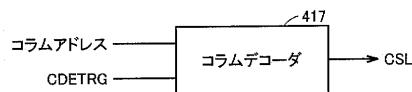

## 【0171】

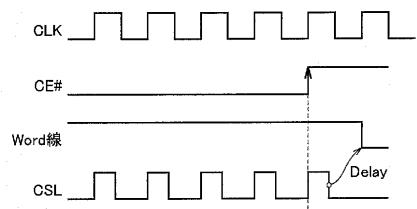

図19は、コラムデコーダ417の構成を示す。同図に示すように、コラムデコーダ活性化トリガ信号C D E T R Gが活性化されたときに、入力されたコラムアドレスに対応するコラム選択信号C S Lを活性化する。

## 【0172】

図示しないセンスアンプは、第1の増幅回路であり、ビット線対B L, Z B Lの間の電位差を増幅する。

## 【0173】

図示しないプリアンプは、第2の増幅回路であり、複数のビット線対B L, Z B Lに接続されたグローバルビット線対G I O, Z G I Oの間の電位差を拡大する。

## 【0174】

図12のリフレッシュ制御回路420は、図示しない内部のリフレッシュタイマに基づいて、D R A Mセルアレイのセルフリフレッシュ動作を制御する。

## 【0175】

(本実施の形態の同期式擬似S R A Mの動作)

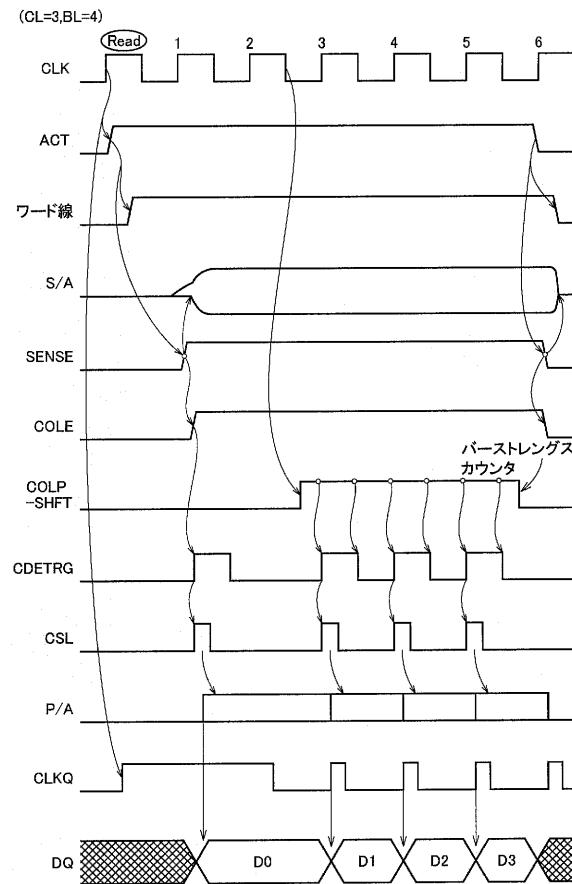

図20は、本実施の形態の同期式擬似S R A M 4 0 0の動作を示すタイミングチャートである。同図を参照して、まず、読み出し信号R E A Dが生成されたクロックC L K 0(第1のクロック)の立ち上がりに同期して、以下のようにロウアクセス処理が行なわれる。

## 【0176】

コマンドデコーダ410は、クロックC L K 0に同期して活性化されたロウ活性化信号を出力する。

## 【0177】

ロウデコーダ418は、アドレスバッファ403から送られるロウアドレスに基づいて、ワード線を選択して、選択したワード線を活性化する。

10

20

30

40

50

## 【0178】

口ウ制御回路409は、口ウ活性化信号ACTを遅延させてセンスアンプイネーブル信号SENSEが活性化する。これにより、周辺回路群408内の図示しないセンスアンプがビット線対の増幅を行なう。

## 【0179】

口ウ制御回路409は、センスアンプイネーブル信号SENSEを遅延させて、コラムイネーブル信号COLEを活性化する。

## 【0180】

次に、第1のクロックCLK0の立ち上がりに同期して、第1番目のコラムのコラムアクセス処理が行なわれる。

10

## 【0181】

CDETRG発生器421は、コラムイネーブル信号COLEの立ち上がりから、ワンショットパルスを生成する。これがコラムデコーダ活性化トリガ信号CDETRGの第1番目のパルスとなる。

## 【0182】

コラムデコーダ417は、コラムデコーダ活性化トリガ信号CDETRGの第1番目のパルスに応じて、入力された第1番目のコラムのコラムアドレスに対応するコラム選択信号CSLを活性化する。

20

## 【0183】

コラム選択信号CSLで選択された第1番目のコラムのビット線対の電位が周辺回路群408内の図示しないプリアンプに送られて、増幅が行なわれる。

## 【0184】

プリアンプで増幅された第1番目のコラムのデータは、入出力回路およびバッファ406に送られる。一方、入出力制御回路411は、外部クロックCLKを受けて内部クロック信号CLKQを出力する。ここで、第1のクロックCLK0の立ち上がりに応じて、先頭のクロック信号CLKQのパルスが生成される。

## 【0185】

入出力回路およびバッファ406は、クロック信号CLKQに同期して、第1番目のコラムから出力されたデータD0をデータ出力端子DQを通じて外部へ出力する。

30

## 【0186】

次に、第1のクロックCLK0から(CL - N1) = 2個目のクロックCLK2(第2のクロック)以降のクロックに同期して、第2番目～第4番目のコラムのコラムアクセス処理が行なわれる。

## 【0187】

COLP\_SHT発生器422は、クロックCLK2(第2のクロック)の立ち下りに応じて、コラムシフト信号COLP\_SHTを活性化し、バーストレングスカウンタのカウンタ値がバーストレングスBLになったことに応じて、コラムシフト信号COLP\_SHTを非活性化する。

## 【0188】

CDETRG発生器421は、コラムシフト信号COLP\_SHTが「H」の期間に含まれる3個のクロックパルスを抽出する。それらがコラムデコーダ活性化トリガ信号CDETRGの第2番目～第4番目のパルスとなる。

40

## 【0189】

コラムデコーダ417は、コラムデコーダ活性化トリガ信号CDETRGの第2番目～第4番目のパルスに応じて、入力された第2番目～第4番目のコラムのコラムアドレスに対応するコラム選択信号CSLを活性化する。

## 【0190】

コラム選択信号CSLで選択された第2番目～第4番目のコラムのビット線対の電位が周辺回路群408内の図示しないプリアンプに送られて、増幅が行なわれる。

## 【0191】

50

プリアンプで増幅された第2番目～第4番目のコラムのデータは、入出力回路およびバッファ406に送られる。一方、入出力制御回路411は、外部からクロック信号CLKを受けて内部クロック信号CLKQを出力する。クロック信号CLKQの第2番目～第4番目のパルスのタイミングは、通常通りのタイミングである。

【0192】

入出力回路およびバッファ406は、クロック信号CLKQの第2番目～第4番目のパルスに同期して、第2番目～第4番目のコラムから出力されたデータD1～D3をデータ出力端子DQを通じて外部へ出力する。

【0193】

以上のように、本実施の形態に係る同期式擬似SRAMによれば、コマンドラインテンシCLKで規定されるタイミングよりも早期にデータを出力するので、システム側では、データを早く受け取ることができ、処理を早く開始することができる。また、バスが不確定な時間を短くできる。

【0194】

本実施の形態では、第1のクロックCLK0に同期して1個のデータを出力したが、これに限定するものではなく、2個または3個のデータを出力するものとしてもよい。第1のクロックCLK0に同期して出力するデータの個数は、システム側の都合で決めればよい。

【0195】

なお、本実施の形態では、外部チップイネーブル信号CE#が「H」に非活性化されたことに応じて、WAIT\_ASYN信号はHi-Zになるものとしたが、これに限定されるものではない。たとえば、WAIT信号が「H」になったことに応じて、WAIT\_ASYN信号はHi-Zになるものとしてもよい。

【0196】

また、第1のクロックCLK0で読出すビット数N1は、固定値であっても、外部信号によってレジスタに値が設定されるものであってもよい。

【0197】

また、本実施の形態では、第1のクロックCLK0で読出すビット数N1が「1」のため、ワンショットパルス発生器431を用いて、第1のクロックCLK0に同期してアクセスされる1個のコラムを活性化させる信号を生成したが、N1が2以上の場合には、生成したワンショットパルスを1サイクルごとにシフトしたパルスをN1個出力する回路を追加すればよい。

【0198】

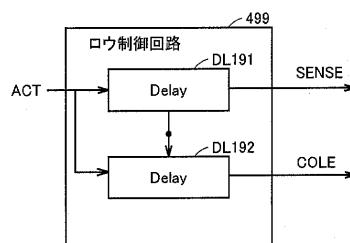

また、ロウ制御回路は、図13に示すものに限定されるものではなく、たとえば、図21に示すようなものであってもよい。図21を参照して、遅延回路(Delay)DL191および遅延回路(Delay)DL192は、読出し信号READまたは書き込み信号WRITEが生成されたクロックである第1クロックCLK0の立ち上がりに応じて活性化されるロウ活性化信号ACTを受ける。遅延回路(Delay)DL191は、ロウ活性化信号ACTを遅延させたセンスアンプ活性化信号SENSEを出力する。遅延回路(Delay)DL192は、ロウ活性化信号ACTを遅延させたコラムイネーブル信号COLを生成する。

【0199】

また、本実施の形態は、同期式擬似SRAMに限定して適用されるものではなく、フラッシュメモリなどのようなのでもよく、クロックに同期して動作する半導体記憶装置であればどのようなものにも適用することができる。特に、高集積、高速が要求の高い同期式擬似SRAMへの応用が適している。

【0200】

なお、本実施の形態の動作例では、外部信号によって読出し信号READが生成されたときの動作を説明したが、外部信号によって書き込み信号WRITEが生成されたときも同様に動作する。

10

20

30

40

50

## 【0201】

## [第4の実施形態の変形例]

本変形例は、リフレッシュ動作中に読み出し信号READまたは書き込み信号WRITEが生成されたときにおいても、第4の実施形態と同様に、バースト読み出し/書き込みにおいて、第1のクロックに従って先頭から数個のビットを読み出し/書き込みし、コマンドレイテンシCLで規定される第2のクロック以降のクロックに従って、残りのビットを読み出し/書き込みする同期式擬似SRAMに関する。

## 【0202】

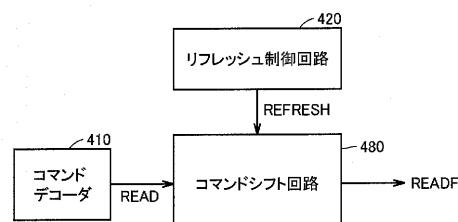

本変形例は、リフレッシュ動作中に読み出し信号READまたは書き込み信号WRITEが生成されたときにおいても対応できるように、第4の実施形態の制御回路402にコマンドシフト回路480を追加する。

## 【0203】

図22は、コマンドシフト回路480の入出力信号を表す図である。コマンドシフト回路408には、コマンドデコーダ410から読み出し信号READと、リフレッシュ制御回路420からリフレッシュ動作信号REFRESHとが入力されて、修正読み出し信号READFを出力する。この修正読み出し信号READFは、読み出し信号READが送られている回路に、読み出し信号READに代わって送られる。

## 【0204】

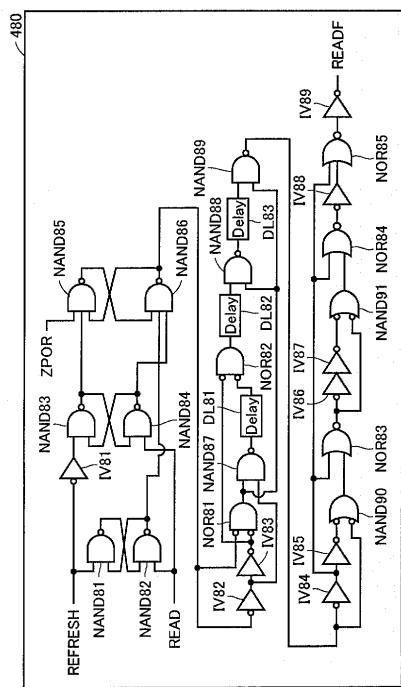

図23は、コマンドシフト回路480の詳細な構成を示す。同図を参照して、リフレッシュ動作信号REFRESHを受ける反転論理積回路NAND81と、読み出し信号READを受ける反転論理積回路NAND82とは、フリップフロップを構成する。インバータINV81は、リフレッシュ動作信号REFRESHを反転する。

## 【0205】

インバータINV81の出力を受ける反転論理積回路NAND83と、読み出し信号READを受ける反転論理積回路NAND84とは、フリップフロップを構成する。

## 【0206】

反転論理積回路NAND83の出力およびリセット信号ZPORを受ける反転論理積回路NAND85と、反転論理積回路NAND82の出力および反転論理積回路NAND84の出力とを受ける反転論理積回路NAND86とは、フリップフロップを構成する。リセット信号ZPORは、電源がオンにされると「H」に活性化される。

## 【0207】

インバータINV82は、反転論理積回路NAND86の出力を受ける。インバータINV83は、インバータINV82の出力を受ける。反転論理和回路NOR81は、反転論理積回路NAND86の出力とインバータINV83の出力とを受ける。

## 【0208】

反転論理積回路NAND87は、反転論理和回路NOR81の出力とインバータINV82の出力とを受ける。遅延回路DL81は、反転論理積回路NAND87の出力を遅延させる。反転論理和回路NOR82は、インバータINV83の出力と遅延回路DL81の出力とを受ける。遅延回路DL82は、反転論理和回路NOR82の出力を遅延させる。

## 【0209】

反転論理積回路NAND88は、遅延回路DL82の出力と反転論理和回路NOR81の出力とを受ける。遅延回路DL83は、反転論理積回路NAND88の出力を遅延させる。反転論理積回路NAND89は、遅延回路DL83の出力と反転論理和回路NOR81の出力とを受ける。

## 【0210】

インバータINV84は、反転論理積回路NAND89の出力を受ける。インバータINV85は、インバータINV84の出力を受ける。反転論理積回路NAND90は、インバータINV85の出力と反転論理積回路NAND89の出力とを受ける。反転論理和回路NOR83は、反転論理積回路NAND90の出力とインバータINV84の出力とを受ける。インバータINV86は、反転論理和回路NOR83の出力を反転する。インバータINV8

10

20

30

40

50

7は、インバータIV86の出力を反転する。

【0211】

反転論理積回路NAND91は、反転論理和回路NOR83の出力とインバータIV87の出力を受ける。反転論理和回路NOR84は、反転論理積回路NAND91の出力とインバータIV84の出力を受ける。インバータIV88は、反転論理和回路NOR84の出力を反転する。反転論理和回路NAND85は、インバータIV84の出力とインバータIV88の出力を受ける。インバータIV89は、反転論理和回路NAND85の出力を反転して修正読出し信号READFを出力する。

【0212】

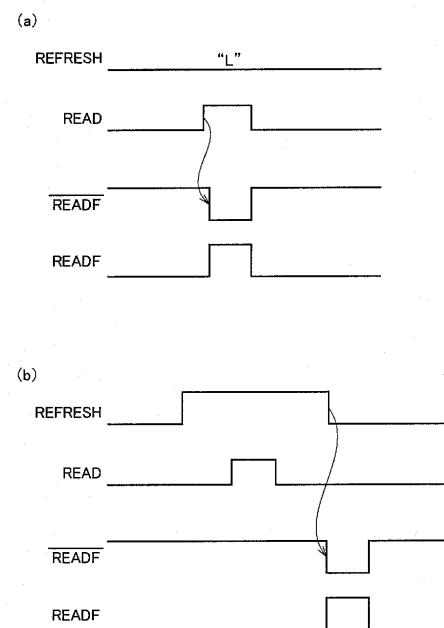

図24(a)は、リフレッシュ動作が行なわれていないときに読出し信号READが入力されたときの修正読出し信号READFを表す図である。同図に示すように、リフレッシュ動作が行なわれていないとき、リフレッシュ動作信号REFRESHは、「L」である。コマンドシフト回路480で生成された修正読出し信号READFが活性化されるタイミングは、読出し信号READが活性化されるタイミングとほぼ同一である。したがって、この修正読出し信号READFを読出し信号READの代りに用いても、第4の実施形態と同様の動作を行なうことができる。

【0213】

図24(b)は、リフレッシュ動作中に読出し信号READが入力されたときの修正読出し信号READFを表す図である。同図に示すように、リフレッシュ動作が行なわれているときに、リフレッシュ動作信号REFRESHは、「H」であるが、リフレッシュ動作が終了すると「L」となる。コマンドシフト回路480で生成された修正読出し信号READFが活性化されるタイミングは、リフレッシュ動作信号REFRESHの立ち下り、リフレッシュの終了直後となる。したがって、この修正読出し信号READFを読出し信号READの代りに用いれば、リフレッシュ終了後から直ちに第4の実施形態と同様の動作を行なうことができる。つまり、図20では、読出し信号READが生成されたときのクロックCLK0を起点として一連の処理が行なわれたが、本変形例は、修正読出し信号READFが入力されたときのクロックを起点として一連の処理が行なわれることになる。

【0214】

なお、本変形例では、リフレッシュ動作中に読出し信号READまたは書き込み信号WRITEが生成された場合について説明したが、読出しさまたは書き込み動作などの実行中に、新たな読出し信号READまたは書き込み信号WRITEが生成された場合についても、同様に適用することができる。特に、この新たな読出しさまたは書き込みを行なうワード線が、その前の読出しさまたは書き込みを行なっていたワード線と異なるときは、もとのワード線の非活性化、新たなワード線の活性化、およびセンスアンプによる増幅などの処理が必要なことから、本変形は、有効であるといえる。

【0215】

なお、本変形例では、コマンドシフト回路480は、読出し信号READによって修正読出し信号READを生成するものとしたが、これに限定するものではなく、書き込み信号WRITEによって修正書き込み信号WRITEFを生成するものであってもよい。

【0216】

[第5の実施形態]

本実施の形態は、同期モードと、非同期モードの両方のモードを有し、それぞれのモードに適した第2の増幅回路であるプリアンプを有する同期式擬似SRAMに関する。なお、第1の増幅回路であるセンスアンプは、ビット線対BL, ZBLの電位を増幅するものであり、第2の増幅回路であるプリアンプは、複数のビット線対BL, ZBLに接続されたグローバルビット線対GIO, ZGIOの電位を増幅するものである。

【0217】

(構成)

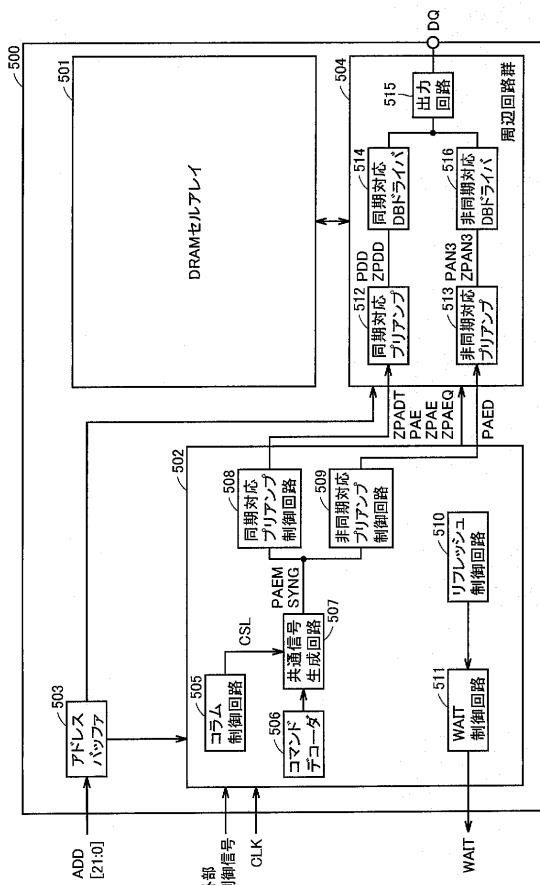

図25は、本実施の形態に係る同期式擬似SRAM500の構成を示す。同図を参照し

10

20

30

40

50

て、この同期式擬似 S R A M 5 0 0 は、D R A M セルアレイ 5 0 1 と、制御回路 5 0 2 と、周辺回路群 5 0 4 と、アドレスバッファ 5 0 3 とを含む。

【 0 2 1 8 】

D R A M セルアレイ 5 0 1 は、ダイナミックランダムアクセスメモリ ( D R A M ) のセルで構成されるメモリアレイである。

【 0 2 1 9 】

アドレスバッファ 503 は、外部アドレス信号 ADD [ 21 : 0 ] を受けて、内部アドレス信号を生成する。

【 0 2 2 0 】

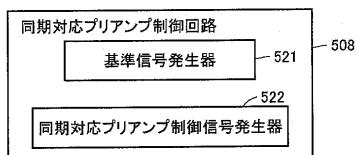

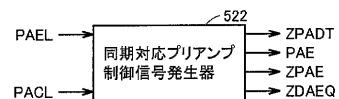

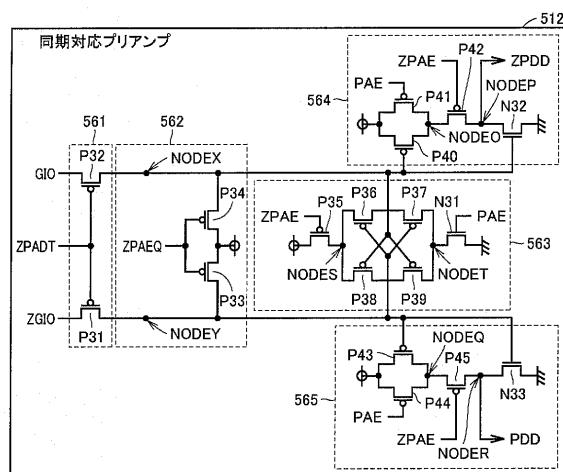

制御回路 502 は、コラム制御回路 505 と、コマンドデコーダ 506 と、共通信号生成回路 507 と、同期対応プリアンプ制御回路 508 と、非同期対応プリアンプ制御回路 509 と、リフレッシュ制御回路 510 と、WAIT制御回路 511 とを備える。

【 0 2 2 1 】

コラム制御回路 505 は、入力されるアドレスに基づいて、コラム選択信号 C S L を出力する。

【 0 2 2 2 】

リフレッシュ制御回路 510 は、図示しない内部のリフレッシュタイムに基づいて、DRAM セルアレイのセルフリフレッシュ動作を制御する。

【 0 2 2 3 】

W A I T 制御回路 511 は、リフレッシュ制御回路 510 の制御によりリフレッシュ制御が行なわれている間、W A I T 端子を介して出力するW A I T 信号のレベルを「L」とする。

【 0 2 2 4 】

コマンドデコーダ 506 は、外部制御信号より生成された内部制御信号の論理レベルの組合せに従って、ロウ活性化信号 ACT、読み出し信号 READ、および書き込み信号 WRITE を生成する。

【 0 2 2 5 】

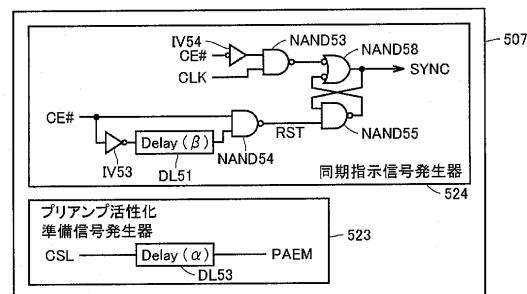

図26は、共通信号生成回路507の構成を示す。同図を参照して、共通信号生成回路507は、プリアンプ活性化準備信号発生器523と、同期指示信号発生器524とを含む。同図に示すように、プリアンプ活性化準備信号PATEMは、コラム制御回路505から送られたコラム選択信号CSLを遅延回路(Delay)DL53で時間だけ遅延させて生成される。プリアンプ活性化準備信号PATEMは、同期対応プリアンプ制御回路508と、非同期対応プリアンプ制御回路509とに送られる。

【 0 2 2 6 】

同期指示信号発生器 524 は、外部チップイネーブル信号 C E # を受けるインバータ I V 54 と、インバータ I V 54 の出力と外部クロック C L K とを受ける反転論理積回路 N A N D 53 と、外部チップイネーブル信号 C E # を受けるインバータ I V 53 と、インバータ I V 53 の出力を 時間だけ遅延させる遅延回路 ( D e l a y ) D L 51 と、外部チップイネーブル信号 C E # と遅延回路 ( D e l a y ) D L 51 の出力とを受ける反転論理積回路 N A N D 54 と、反転論理積回路 N A N D 53 の出力と反転論理積回路 N A N D 55 の出力とを受ける反転論理積回路 N A N D 58 と、反転論理積回路 N A N D 54 の出力と反転論理積回路 N A N D 58 の出力とを受ける反転論理積回路 N A N D 55 とを備える。

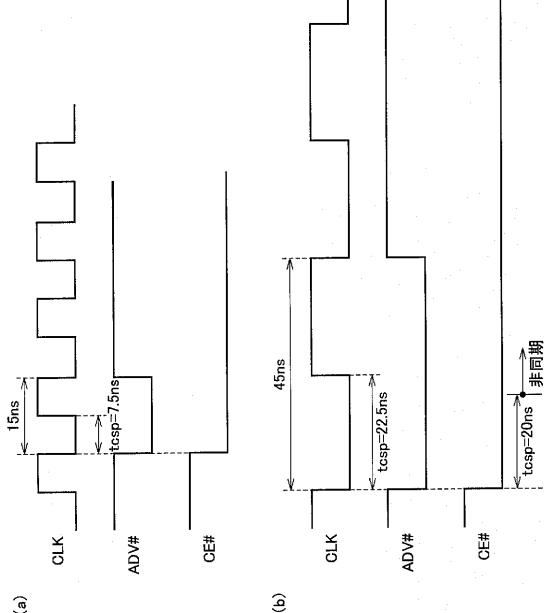

( 0 2 2 7 )

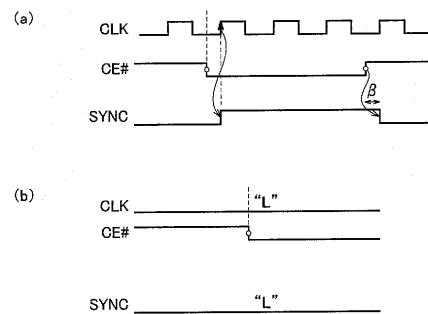

図27(a)および(b)は、同期指示信号SYNCが生成されるタイミングチャートを示す。

〔 0 2 2 8 〕

図27(a)を参照して、外部クロックCLKが入力されているときには、同期指示信号SYNCは、外部チップイネーブル信号CE#が「L」に活性化された後、最初のクロックCLKの立ち上がりで同期モードを示す「H」となり、その後、外部チップイネーブル信号CE#が「H」に活性化された後、最初のクロックCLKの立ち上がりで同期モードを示す「L」となります。

ル信号 C E # が「 H 」に非活性化されて遅延回路 ( Delay ) D L 5 1 による 時間だけ遅延後に「 L 」となる。

【 0 2 2 9 】

図 2 7 ( b ) を参照して、外部クロック C L K が入力されないときに、同期指示信号 S Y N C は、非同期モードを示す「 L 」となる。

【 0 2 3 0 】

同期指示信号 S Y N C は、同期対応プリアンプ制御回路 5 0 8 と、非同期対応プリアンプ制御回路 5 0 9 とに送られる。

【 0 2 3 1 】

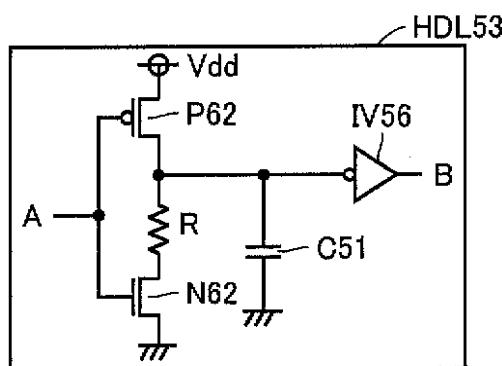

図 2 8 は、同期対応プリアンプ制御回路 5 0 8 の構成を示す。同図に示すように、同期対応プリアンプ制御回路 5 0 8 は、基準信号発生器 5 2 1 と、同期式動作用プリアンプ制御信号発生器 5 2 2 とを含む。

【 0 2 3 2 】

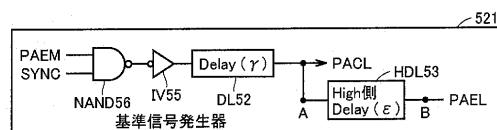

図 2 9 は、基準信号発生器 5 2 1 の構成を示す。同図に示すように、基準信号発生器 5 2 1 は、プリアンプ活性化準備信号 P A E M および同期指示信号 S Y N C を受ける反転論理積回路 N A N D 5 6 と、反転論理積回路 N A N D 5 6 の出力を受けるインバータ I V 5 5 と、インバータ I V 5 5 の出力を 時間だけ遅延させる遅延回路 ( Delay ) D L 5 2 と、遅延回路 ( Delay ) D L 5 2 の出力の「 H 」レベル側を 時間だけ遅延させる遅延回路 ( High 側 Delay ) H D L 5 3 とを備える。遅延回路 ( Delay ) D L 5 2 の出力が第 1 の基準信号 P A C L であり、遅延回路 ( High 側 Delay ) H D L 5 3 の出力が第 2 の基準信号 P A E L である。

【 0 2 3 3 】

図 3 0 は、 H i g h 側 Delay の一例を示す図である。 H i g h 側 Delay は、 P チャネル M O S トランジスタ P 6 2 と、 N チャネル M O S トランジスタ N 6 2 と、抵抗 R と、コンデンサ C 5 1 と、インバータ I V 5 6 とを備える。 H i g h 側 Delay のノード B が「 L 」から「 H 」に変化するタイミングは、ノード A が「 L 」から「 H 」に変化するタイミングよりも遅れるが、ノード B が「 H 」から「 L 」に変化するタイミングは、ノード A が「 H 」から「 L 」に変化するタイミングと同一となる。

【 0 2 3 4 】

図 3 1 は、同期対応プリアンプ制御信号発生器 5 2 2 の構成を示す。同図に示すように、同期対応プリアンプ制御信号発生器 5 2 2 は、第 1 の基準信号 P A E L および第 2 の基準信号 P A C L を受けて、反転プリアンプ接続信号 Z P A D T 、プリアンプ活性化信号 P A E 、反転プリアンプ活性化信号 Z P A E 、反転プリアンプイコライズ信号 Z P A E Q を生成する。

【 0 2 3 5 】

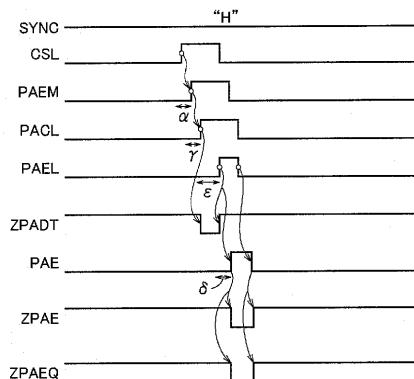

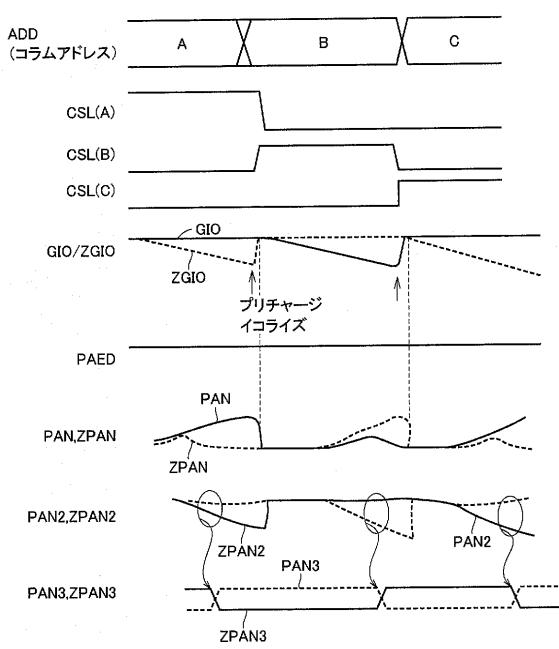

図 3 2 は、同期対応プリアンプ 5 1 2 に関連する信号が生成されるタイミングを示す。同図を参照して、同期モードを指示するときには、図 2 7 ( a ) で説明したように、同期指示信号 S Y N C が「 H 」となる。コラム選択信号 C S L は、適切なタイミングで「 H 」に活性化される。

【 0 2 3 6 】

プリアンプ活性化準備信号 P A E M は、コラム選択信号 C S L を 時間だけ遅延させて生成される。

【 0 2 3 7 】

プリアンプ活性化準備信号 P A E M および同期指示信号 S Y N C が同期活性化信号発生器 5 2 1 の反転論理積回路 N A N D 5 6 に入力されて、プリアンプ活性化準備信号 P A E M から 時間だけ遅延した第 1 の基準信号 P A C L が生成される。

【 0 2 3 8 】

さらに、この第 1 の基準信号 P A C L のパルスの先頭が 時間だけ遅延した第 2 の基準信号 P A E L が生成される。

【 0 2 3 9 】

10

20

30

40

50

同期対応プリアンプ制御信号発生器 522 は、第1の基準信号 P A C L が「H」、かつ第2の基準信号 P A E L が「L」の時に、反転プリアンプ接続信号 Z P A D T を「L」に活性化する。また、同期対応プリアンプ制御信号発生器 522 は、第2の基準信号 P A E L を 時間だけ遅延させて、プリアンプ活性化信号 P A E を生成する。また、同期対応プリアンプ制御信号発生器 522 は、プリアンプ活性化信号 P A E を反転させて、反転プリアンプ活性化信号 Z P A E および反転プリアンプイコライズ信号 Z P A E Q を生成する。

#### 【0240】

一方、同期指示信号 S Y N C が非同期モードを示す「L」のときには、第1の基準信号 P A C L および第2の基準信号 P A E L が活性化されず、その結果、反転プリアンプ接続信号 Z P A D T 、プリアンプ活性化信号 P A E 、反転プリアンプ活性化信号 Z P A E 、および反転プリアンプイコライズ信号 Z P A E Q が活性化されない。

#### 【0241】

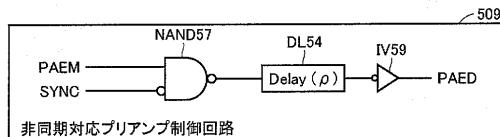

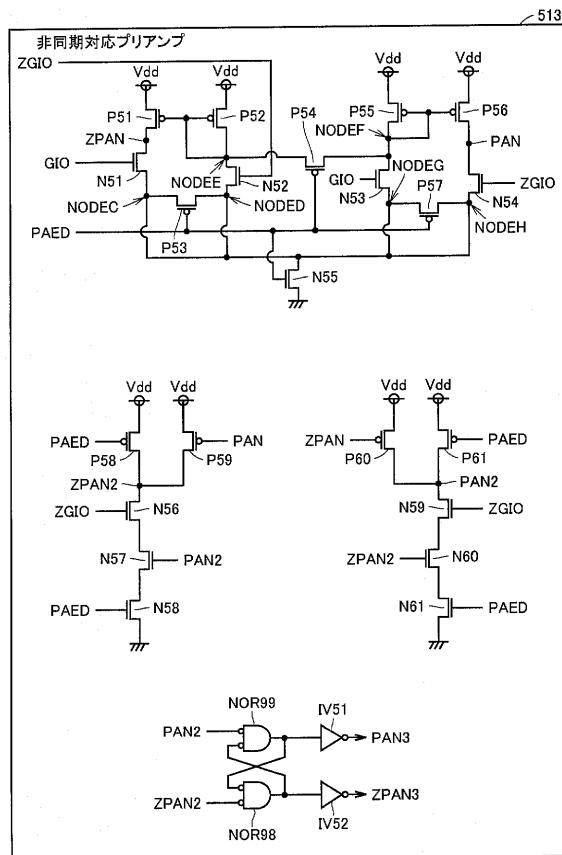

図 33 は、非同期対応プリアンプ制御回路 509 の構成を示す。同図に示すように、非同期対応プリアンプ制御回路 509 は、プリアンプ活性化準備信号 P A E M および同期指示信号 S Y N C の反転を受ける反転論理積回路 N A N D 57 と、反転論理積回路 N A N D 57 の出力を 時間だけ遅延させる遅延回路 ( D e l a y ) D L 54 と、遅延回路 ( D e l a y ) D L 54 の出力を受けるインバータ I V 59 とを備える。インバータ I V 59 の出力がプリアンプ活性化信号 P A E D である。

#### 【0242】

図 34 は、非同期対応プリアンプ 513 に関連する信号が生成されるタイミングを示す。同図を参照して、非同期モードを指示するときには、図 27 (b) で説明したように、同期指示信号 S Y N C が「L」となる。コラム選択信号 C S L は、適切なタイミングで「H」に活性化される。

#### 【0243】

プリアンプ活性化準備信号 P A E M は、コラム選択信号 C S L を 時間だけ遅延させて生成される。

#### 【0244】

プリアンプ活性化準備信号 P A E M および同期指示信号 S Y N C が非同期対応プリアンプ制御回路 509 に送られて、プリアンプ活性化準備信号 P A E M が 時間だけ遅延したプリアンプ活性化信号 P A E D が生成される。

#### 【0245】

一方、同期指示信号 S Y N C が同期モードを示す「H」のときには、プリアンプ活性化信号 P A E D は、活性化されない。

#### 【0246】

再び、図 25 を参照して、周辺回路群 504 は、同期対応プリアンプ 512 と、非同期対応プリアンプ 513 と、同期対応 D B ドライバ 514 と、非同期対応 D B ドライバ 516 と、出力回路 515 とを含む。

#### 【0247】

( 同期対応プリアンプ 512 )

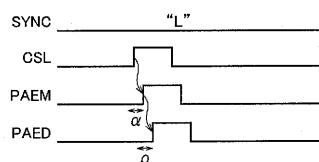

図 35 は、同期対応プリアンプ 512 の構成を示す。同図に示すように、この同期対応プリアンプ 512 は、反転プリアンプ接続信号 Z P A D T で制御されるスイッチ部 561 と、反転プリアンプイコライズ信号 Z P A E Q で制御されるイコライズ部 562 と、プリアンプ活性化信号 P A E および反転プリアンプ活性化信号 Z P A E で制御される増幅部 563 と、プリアンプ活性化信号 P A E および反転プリアンプ活性化信号 Z P A E で制御されるバッファ部 564, 565 とを備える。

#### 【0248】

スイッチ部 561 は、P チャネル M O S トランジスタ P 32 と、P チャネル M O S トランジスタ P 31 とを含む。P チャネル M O S トランジスタ P 32 は、グローバル入出力線 G I O と N O D E X との間に配置される。P チャネル M O S トランジスタ P 31 は、反転グローバル入出力線 Z G I O と N O D E Y との間に配置される。P チャネル M O S トラン

10

20

30

40

50

ジスタP32およびPチャネルMOSトランジスタP31のゲートには、反転プリアンプ接続信号ZPADTが印加される。

【0249】

イコライズ部562は、PチャネルMOSトランジスタP34と、PチャネルMOSトランジスタP33とを含む。PチャネルMOSトランジスタP34は、NODEXと電源との間に配置される。PチャネルMOSトランジスタP33は、NODEYと電源との間に配置される。PチャネルMOSトランジスタP34およびPチャネルMOSトランジスタP33のゲートには、反転プリアンプイコライズ信号ZPAEQが印加される。

【0250】

増幅部563は、PチャネルMOSトランジスタP35～P39と、NチャネルMOSトランジスタN31とを含む。NODESとNODETとの間には、直列に接続されたPチャネルMOSトランジスタP36およびPチャネルMOSトランジスタP37が置かれ、これと並列に、直列に接続されたPチャネルMOSトランジスタP38およびPチャネルMOSトランジスタP39が配置される。PチャネルMOSトランジスタP36およびP37のゲートは、NODEYと接続する。PチャネルMOSトランジスタP38およびP39のゲートは、NODEXと接続する。PチャネルMOSトランジスタP35は、電源とNODESとの間に配置される。NチャネルMOSトランジスタN31は、NODETとグランドとの間に配置される。PチャネルMOSトランジスタP35のゲートには、反転プリアンプ活性化信号ZPAEが印加され、NチャネルMOSトランジスタN31のゲートには、プリアンプ活性化信号PAEが印加される。

10

20

30

40

【0251】

バッファ564は、PチャネルMOSトランジスタP40～P42と、NチャネルMOSトランジスタN32とを含む。PチャネルMOSトランジスタP40およびPチャネルMOSトランジスタP41は、電源とNODEOとの間に配置される。PチャネルMOSトランジスタP40のゲートは、NODEXと接続する。PチャネルMOSトランジスタP41のゲートは、プリアンプ活性化信号PAEが印加される。PチャネルMOSトランジスタP42は、NODEOとNODEPとの間に配置される。PチャネルMOSトランジスタP42のゲートには、反転プリアンプ活性化信号ZPAEが印加される。NチャネルMOSトランジスタN32は、NODEPとグランドとの間に配置される。NチャネルMOSトランジスタN32のゲートは、NODEXと接続する。NODEXから反転プリアンプ出力データZPDDが出力される。

【0252】

バッファ565は、PチャネルMOSトランジスタP43～P45と、NチャネルMOSトランジスタN33とを含む。PチャネルMOSトランジスタP43およびPチャネルMOSトランジスタP44は、電源とNODEQとの間に配置される。PチャネルMOSトランジスタP43のゲートは、NODEYと接続する。PチャネルMOSトランジスタP44のゲートは、プリアンプ活性化信号PAEが印加される。PチャネルMOSトランジスタP45は、NODEQとNODERとの間に配置される。PチャネルMOSトランジスタP45のゲートには、反転プリアンプ活性化信号ZPAEが印加される。NチャネルMOSトランジスタN33は、NODERとグランドとの間に配置される。NチャネルMOSトランジスタN33のゲートは、NODEYと接続する。NODEYからプリアンプ出力データPDDが出力される。

【0253】

この同期対応プリアンプ512は、スイッチ部561を有するため、反転プリアンプ接続信号ZPADTにより適当なタイミングでグローバル入出力対GIO, ZGIOを増幅部523から切り離すことができる。これにより、増幅部523は、グローバル入出力対GIO, ZGIOの電位を一度取り込んだら、その後の変化に左右されることなく増幅を行なうという、いわゆる閉じ込め式の増幅が可能となり、増幅が高速化できる。また、グローバル入出力対GIO, ZGIOが増幅部523から切り離されるので、増幅部523での増幅と同時に、イコライズ部562でプリチャージ処理を行なうことができ、プリア

50

ンプ全体の処理も高速化できる。

【0254】

また、特に、クロックに同期した読み出し処理が行なわれるときには、一定のタイミングでアドレスが変化し、ランダムなタイミングではアドレスは変化しないので、アドレスが変化しないタイミングでスイッチ部561による切り離しを行なえば、グローバル入出力線対GIO, ZGIOのデータを取りのがすことがない。

【0255】

以上より、この同期対応プリアンプ512は、クロックに同期した読み出し動作に適しているといえる。

【0256】

一方、この同期対応プリアンプ512は、以下に示すように、クロックに同期しない、非同期の読み出し動作には適していない。

【0257】

図36は、同期対応プリアンプ512が非同期読み出しには適さないことを説明するための図である。同図に示すように、非同期読み出しでは、アドレスの変化に応じて、読み出し処理が行なわれる。

【0258】

同図の(1)に示すように、コラムアドレスが変化した後、さらに短期間にコラムアドレスが変化したときには、それぞれの変化に対応して、反転プリアンプイコライズ信号ZPAQが活性化されるが、同図の(2)に示すように、それらの活性化されるタイミングが接近する。その結果、プリチャージが十分に行なわれない。そして、プリチャージが行なわれないまま、増幅が行なわれるため、同図の(3)に示すように、プリアンプの出力データPDDにゆがみが生じる。このような問題を回避するためには、プリチャージ期間を十分に設けた後、次のコラムのアクセスを行なう必要があり、同期対応プリアンプ512による処理が遅くなる。

【0259】

また、同図の(4)の示すように、ノイズなどの影響でイリーガルなアドレス変化が生じた場合において、グローバル入出力線対GIO, ZGIOには、イリーガルなコラムアドレス変化のコラムのデータが出力された後、正しいコラムアドレス変化のコラムデータが出力される。この場合、グローバル入出力線対GIO, ZGIOと増幅部563との切り離しのタイミングが早いと、同図の(5)に示すように、イリーガルなデータを増幅し、正しいデータを増幅しない。このような問題を回避するためには、グローバル入出力線対GIO, ZGIOと増幅部563との切り離しのタイミングを遅くする必要があり、同期対応プリアンプ512による処理が遅くなる。

【0260】

以上のように、この同期対応プリアンプ512を非同期の読み出しに用いた場合、処理が遅くなり、適切でないといえる。

【0261】

(非同期対応プリアンプ513)

図37は、非同期対応プリアンプ513の構成を示す。同図に示すように、この非同期対応プリアンプ513は、差動式のカレントミラータイプの増幅器である。

【0262】

図37を参照して、PチャネルMOSトランジスタP51およびP52は、カレントミラー回路を構成する。NチャネルMOSトランジスタN51は、ノードZPANとNODECとの間に配置される。NチャネルMOSトランジスタN52は、NODEEとNODEDとの間に配置される。NチャネルMOSトランジスタN51のゲートは、グローバル入出力線GIOと接続する。NチャネルMOSトランジスタN52のゲートは、反転グローバル入出力線ZGIOと接続する。PチャネルMOSトランジスタP53は、NODECとNODEDとの間に配置される。PチャネルMOSトランジスタP53のゲートには、プリアンプ活性化信号PAEDが印加される。

10

20

30

40

50

## 【0263】

PチャネルMOSトランジスタP55およびP56は、カレントミラー回路を構成する。NチャネルMOSトランジスタN54は、ノードPANとNODEHとの間に配置される。NチャネルMOSトランジスタN53は、NODEFとNODEGとの間に配置される。NチャネルMOSトランジスタN54のゲートは、反転グローバル入出力線ZGIOと接続する。NチャネルMOSトランジスタN53のゲートは、グローバル入出力線GIOと接続する。PチャネルMOSトランジスタP57は、NODEGとNODEHとの間に配置される。PチャネルMOSトランジスタP57のゲートには、プリアンプ活性化信号PAEDが印加される。

## 【0264】

NチャネルMOSトランジスタN55は、NODEDとグランドとの間に配置される。NチャネルMOSトランジスタN55のゲートには、プリアンプ活性化信号PAEDが印加される。PチャネルMOSトランジスタP54は、NODEEとNODEFとの間に配置される。PチャネルMOSトランジスタP54のゲートには、プリアンプ活性化信号PAEDが印加される。

## 【0265】

さらに、電源とノードZPAN2との間にPチャネルMOSトランジスタP58とPチャネルNOSトランジスタP59とが並列に配置される、PチャネルMOSトランジスタP58のゲートには、プリアンプ活性化信号PAEDが入力され、PチャネルMOSトランジスタP59のゲートは、ノードPANと接続する。

## 【0266】

ノードZPAN2とグランドとの間に、NチャネルMOSトランジスタN56、NチャネルMOSトランジスタ57、およびNチャネルMOSトランジスタN58が直列に接続する。NチャネルMOSトランジスタN56のゲートは、反転グローバル入出力線ZGIOと接続する。NチャネルMOSトランジスタN57のゲートは、ノードPAN2と接続する。NチャネルMOSトランジスタN58のゲートには、プリアンプ活性化信号PAEDが入力される。

## 【0267】

さらに、電源とノードPAN2との間にPチャネルMOSトランジスタP60とPチャネルNOSトランジスタP61とが並列に配置される、PチャネルMOSトランジスタP61のゲートには、プリアンプ活性化信号PAEDが入力され、PチャネルMOSトランジスタP60のゲートは、ノードZPANと接続する。

## 【0268】

ノードPAN2とグランドとの間に、NチャネルMOSトランジスタN59、NチャネルMOSトランジスタ60、およびNチャネルMOSトランジスタN61が直列に接続する。NチャネルMOSトランジスタN59のゲートは、反転グローバル入出力線ZGIOと接続する。NチャネルMOSトランジスタN60のゲートは、ノードZPAN2と接続する。NチャネルMOSトランジスタN61のゲートには、プリアンプ活性化信号PAEDが入力される。

## 【0269】

さらに、ノードPAN2と接続する反転論理回路NOR99と、ノードZPAN2と接続する反転論理回路NOR98とは、フリップフロップを構成する。インバータIV51は、反転論理回路NOR99の出力を反転してプリアンプ出力信号PAN3を出力する。インバータIV52は、反転論理回路NOR98の出力を反転して反転プリアンプ出力信号ZPAN3を出力する。

## 【0270】

図38は、非同期対応プリアンプ513の各ノードの電位の時間変化を示す図である。

## 【0271】

この非同期対応プリアンプ513は、同期対応プリアンプ512のようなスイッチ部を有しない、いわゆる非閉じ込め式のプリアンプである。したがって、非同期対応プリアン

10

20

30

40

50

513は、増幅中に、グローバル入出力線GIO, ZGIOと切り離されないので、アドレス変化に応じて読み出しが行われる非同期の読み出しに適している。

【0272】

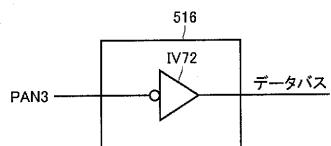

再び、図25を参照して、同期対応DBドライバ514は、受けた電位をデータバスDBに出力する。図39は、同期対応DBドライバ514の構成を示す。同図に示すように、この同期対応DBドライバ514は、同期対応プリアンプ512の出力PDDを受けて、それを反転してデータバスDBへ出力するインバータIV74で構成される。

【0273】

非同期対応DBドライバ516は、受けた電位をデータバスDBに出力する。図40は、非同期対応DBドライバ516の構成を示す。この非同期対応DBドライバ516は、非同期対応プリアンプ513の出力PAN3を受けて、それを反転してデータバスDBへ出力するインバータIV72で構成される。

10

【0274】

図25の出力回路515は、データバスDBのデータを受けてデータ出力端子DQを通じて外部へ出力する。

【0275】

以上のように、本実施の形態に係る同期式擬似SRAMによれば、同期モードにおいて適切に動作するプリアンプと、非同期モードで適切に動作するプリアンプとを有するので、すべてのモードで正常にグローバル入出力線GIO, ZGIOの電位差を増幅を行なうことができる。

20

【0276】

なお、本実施の形態では、同期動作用のプリアンプと、非同期対応のプリアンプとに分けたが、これに限定するものではなく、バーストモード用のプリアンプとランダムアクセスモード用のプリアンプを設けてもよい。この場合には、半導体記憶装置は、同期モードと非同期モードを有するものではなく、バーストモードとランダムアクセスモードを有するものとなる。バーストモード用としては、先読み動作およびパイプライン動作を効率的に実行できるように、プリアンプ512のような閉じ込め式の増幅が可能なプリアンプが適している。

【0277】

本実施の形態は、同期指示信号SYNCによって、同期モードと非同期モードが切り替わるものとしたが、これに限定するものではなく、ボンディングオプションPADを有し、それに印可する電位によって、同期モードと非同期モードとを切替えるものとしてもよい。

30

【0278】

また、本実施の形態では、同期対応DBドライバ514と非同期対応DBドライバ516を有するものとしたが、同期と非同期に対応したDBドライバを用いるものとしてもよい。

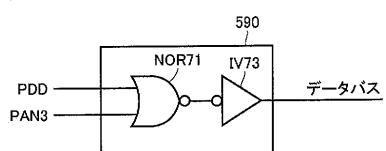

【0279】

図41は、同期対応DBドライバ514と、非同期対応DBドライバ516とを兼ねる共用DBドライバ590の構成を示す。同図に示すように、この共用DBドライバ590は、一方のバッファ部525の出力を受けて、それをデータバスDBへ出力するインバータIV74で構成される。同期対応プリアンプ512の出力PDDと非同期対応プリアンプ513の出力PAN3とを受ける反転論理回路NOR71と、反転論理回路NOR71の出力を反転してデータバスDBへ出力するインバータIV73で構成される。

40

【0280】

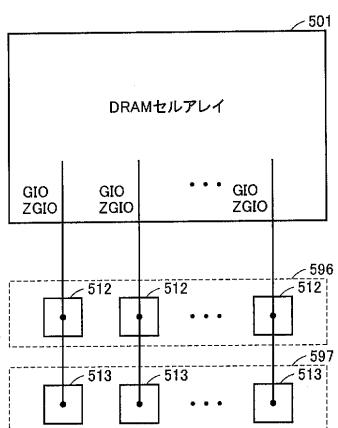

図42は、同期対応プリアンプ512および非同期対応プリアンプ513のレイアウトを表す図である。同図に示すように、同期対応プリアンプ配置領域596には同期対応プリアンプ512が置かれ、非同期対応プリアンプ配置領域597には非同期対応プリアンプ513が配置されている。

【0281】

50

各グローバル入出力線対 G I O , Z G I O と接続する同期対応プリアンプ 512 と非同期対応プリアンプ 513 とは、コラム方向に並んで配置される。グローバル入出力線対 G I O , Z G I O の配置層とプリアンプの配置層とが異なり、グローバル入出力線対 G I O , Z G I O は、分岐を有せずに、同期対応プリアンプ 512 および非同期対応プリアンプ 513 と接続する。

【 0282 】

以上のように、図 42 に示すレイアウトでは、グローバル入出力線対 G I O , Z G I O を分岐させる必要がなく、グローバル入出力線対 G I O , Z G I O の配線が容易である。また、このレイアウトは、コラム方向に同期式擬似 S R A M 500 のサイズが大きくとれるような場合に適している。

10

【 0283 】

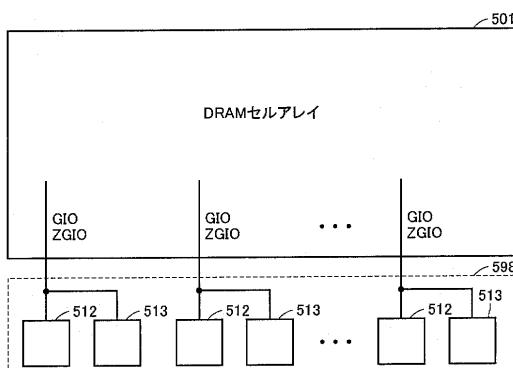

図 43 は、同期対応プリアンプ 512 および非同期対応プリアンプ 513 の別のレイアウトを表す図である。同図に示すように、同期 / 非同期対応プリアンプ配置領域 598 には同期対応プリアンプ 512 と非同期対応プリアンプ 513 とが配置されている。

【 0284 】

各グローバル入出力線対 G I O , Z G I O と接続する同期対応プリアンプ 512 と非同期対応プリアンプ 513 とは、ロウ方向に並んで配置される。グローバル入出力線対 G I O , Z G I O は、分岐を有し、分岐した一方が同期対応プリアンプ 512 に接続し、分岐した他方が非同期対応プリアンプ 513 と接続する。

20

【 0285 】

以上のように、図 43 に示すレイアウトでは、グローバル入出力線対 G I O , Z G I O を分岐させる必要があり。また、このレイアウトは、ロウ方向に同期式擬似 S R A M 500 のサイズが大きくとれるような場合に適している。

【 0286 】

〔 第 6 の実施形態 〕

本実施の形態は、バイトマスク機能を有する同期式擬似 S R A M に関する。同期式擬似 S R A M には、上位バイトまたは下位バイトのマスクを行なうことで、メモリセルから読み出したデータを外部へ出力させないようにすることができる。ところで、バーストモードにおいて、ノーラップモードというものがある。ノーラップモードでは、バースト読出しましたは書込みの途中に最後のコラムに達すると、次のロウへ移行する。この場合、選択していたワード線の不活性化、新たに選択するワード線の活性化、およびセンスアンプによる增幅処理などのロウアクセス処理が必要となる。ロウアクセス処理が行なわれている間、外部に対して W A I T 信号が出力される。外部のシステム側は、この W A I T 信号が解除されてから、バイトマスク信号を与えればよいが、外部のシステムにとっては、このような次のロウへ移行するためのロウアクセス処理の有無に係らず、同一の方法でバイトマスクの設定ができた方が望ましい。本実施の形態は、バースト読出しましたはバースト書込みが第 1 のロウと第 2 のロウの 2 つのロウに渡り、途中で第 1 のロウの最後のコラムに達したため第 2 のロウへ移行する場合においても、外部からは 2 つのロウに渡らない場合と同様にしてバイトマスク信号を与えることを可能とする同期式擬似 S R A M に関する。提供する。

30

【 0287 】

( 構成 )

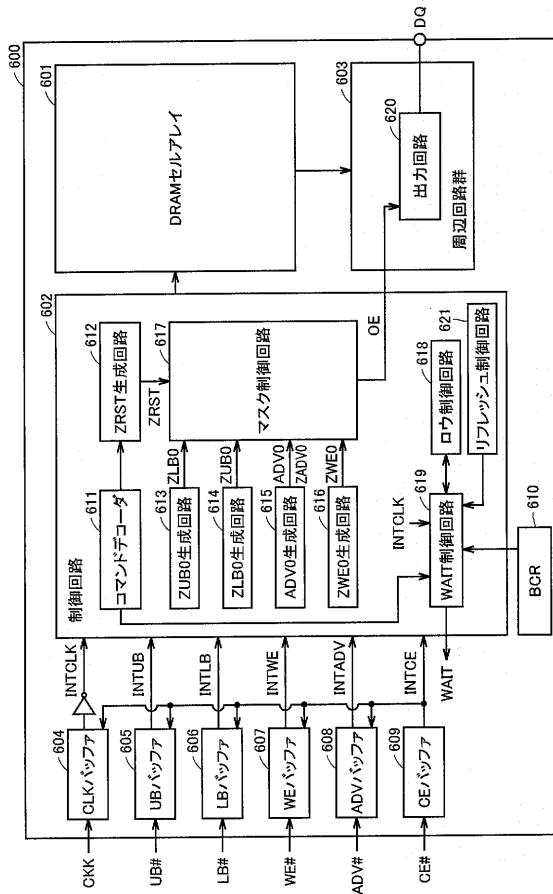

図 44 は、本実施の形態に係る同期式擬似 S R A M 600 の構成を示す。同図を参照して、この同期式擬似 S R A M 600 は、D R A M セルアレイ 601 と、C L K バッファ 604 と、U B バッファ 605 と、L B バッファ 606 と、W E バッファ 607 と、A D V バッファ 608 と、制御回路 602 と、周辺回路群 603 と、B C R (Bus Configuration Register) 610 とを備える。

40

【 0288 】

D R A M セルアレイ 601 は、ダイナミックランダムアクセスメモリ ( D R A M ) のセルで構成されるメモリアレイである。

50

## 【0289】

周辺回路群603は、図示しないグローバル入出力線対G I O P (G I O および / G I O )と、各列に対応して設けられた列選択線と、列選択ゲートと、センスアンプと、プリアンプと、ライトドライバと、ロウデコーダ、コラムデコーダなどを含む。周辺回路群603は、さらに出力回路620を含む。

## 【0290】

出力回路620は、D R A M セルアレイ601から出力されたデータを保持する。出力回路620は、上位バイトおよび下位バイトごとに出力イネーブル信号O E を受ける。出力回路620は、上位バイトの出力イネーブル信号O E がイネーブル「H」を示すときに、保持しているデータの上位バイトをデータ入出力端子D Q を通じて外部に出力する。出力回路620は、下位バイトの出力イネーブル信号O E がイネーブル「H」を示すときに、保持しているデータの下位バイトをデータ入出力端子D Q を通じて外部に出力する。

10

## 【0291】

B C R 610は、外部のシステムとのインターフェース、たとえば、バーストレンジスB L 、およびコマンドレイテンシC Lなどを記憶する。

## 【0292】

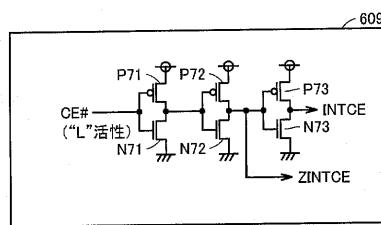

図45は、C E バッファ609の詳細な構成を示す。同図を参照して、C E バッファ608は、外部チップイネーブル信号C E # が入力される、PチャネルM O S トランジスタP71およびNチャネルM O S トランジスタN71で構成されるインバータ1と、そのインバータ1に接続される、PチャネルM O S トランジスタP72およびNチャネルM O S トランジスタN72で構成されるインバータ2と、そのインバータ2に接続される、PチャネルM O S トランジスタP73およびNチャネルM O S トランジスタN73で構成されるインバータ3とを含む。インバータ2の出力が反転内部チップイネーブル信号Z I N T C E であり、インバータ3の出力が内部チップイネーブル信号I N T C E である。

20

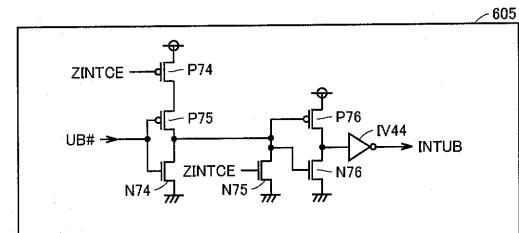

## 【0293】

図46は、U B バッファ605の詳細な構成を示す。同図を参照して、U B バッファ605は、外部上位バイトマスク信号U B # が入力される、PチャネルM O S トランジスタP75およびNチャネルM O S トランジスタN74で構成されるインバータ1と、そのインバータ1に接続される、PチャネルM O S トランジスタP76およびNチャネルM O S トランジスタN76で構成されるインバータ2と、そのインバータ2に接続される、インバータI V 4 4とを含む。インバータI V 4 4の出力が内部上位バイトマスク信号I N T U B となる。さらに、電源とPチャネルM O S トランジスタP75との間にPチャネルM O S トランジスタP74を配置する。インバータ1とインバータ2の接続ノードとグランドとの間に、NチャネルM O S トランジスタN75を配置する。

30

## 【0294】

PチャネルM O S トランジスタP74のゲートおよびNチャネルM O S トランジスタN75のゲートには、反転内部チップイネーブル信号Z I N T C E が入力される。チップが活性化されているとき、反転チップイネーブル信号Z I N T C E が「L」となる。このときには、PチャネルM O S トランジスタP75が電源と接続するとともに、インバータ1とインバータ2の接続ノードが接地されない。したがって、通常の動作が行なわれる。

40

## 【0295】

一方、チップが非活性化されているとき、反転チップイネーブル信号Z I N T C E が「H」となる。このときには、PチャネルM O S トランジスタP75が電源と切断されるとともに、インバータ1とインバータ2の接続ノードが接地される。したがって、内部上位バイトマスク信号I N T U B は、常に「L」のままとなる。

## 【0296】

その他の入力バッファC L K バッファ604、L B バッファ606、W E バッファ607、A D V バッファ608の構成は、U B バッファ605の構成と同一なので、説明は繰返さない。

## 【0297】

50

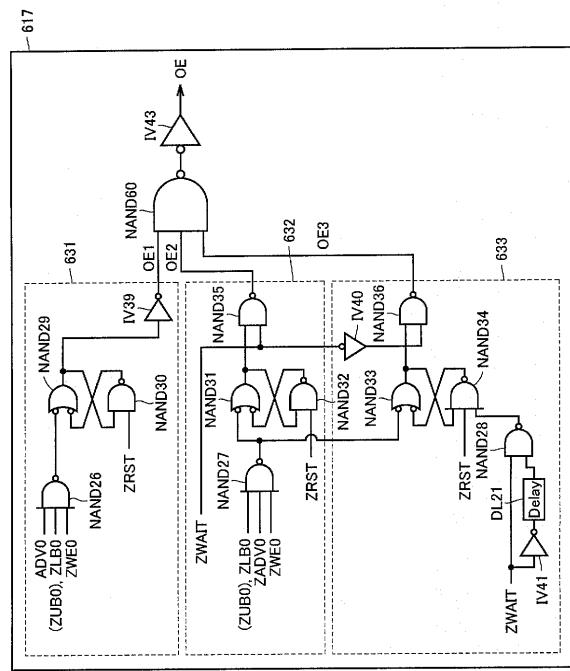

再び、図44を参照して、制御回路602は、コマンドデコーダ611と、ZRS T生成回路612と、ZUB0生成回路613と、ZLB0生成回路614と、ADV0生成回路615と、ZWE0生成回路616と、マスク制御回路617と、ロウ制御回路618と、WAIT制御回路619と、リフレッシュ制御回路621とを備える。

【0298】

コマンドデコーダ611は、外部制御信号より生成された内部制御信号の論理レベルの組合せに従って、ロウ活性化信号ACT、および読み出し信号READを生成する。

【0299】

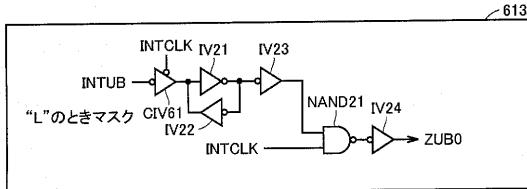

図47は、ZUB0生成回路613の詳細な構成を示す。同図を参照して、クロックドインバータCIV61には、内部上位バイトマスク信号INTUBを受ける。クロックドインバータCIV61の出力がインバータIV21とインバータIV22とからなる双安定回路に送られる。双安定回路の出力がインバータIV23に送られる。インバータIV23の出力および内部クロックINTCLKが反転論理積回路NAND21に送られる。反転論理積回路NAND21の出力がインバータIV24に送られ、インバータIV24の出力がZUB0となる。

【0300】

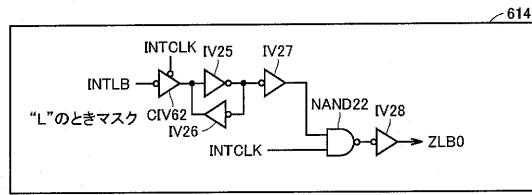

図48は、ZLB0生成回路614の詳細な構成を示す。同図を参照して、クロックドインバータCIV62には、内部下位バイトマスク信号INTLBを受ける。クロックドインバータCIV62の出力がインバータIV25とインバータIV26とからなる双安定回路に送られる。双安定回路の出力がインバータIV27に送られる。インバータIV27の出力および内部クロックINTCLKが反転論理積回路NAND22に送られる。反転論理積回路NAND22の出力がインバータIV28に送られ、インバータIV28の出力がZLB0となる。

【0301】

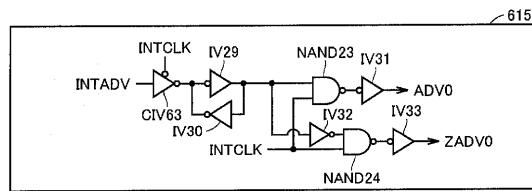

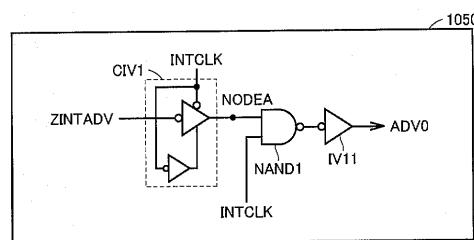

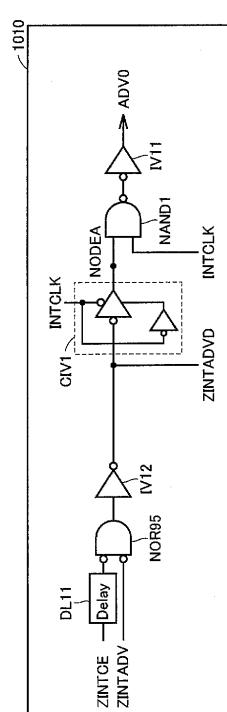

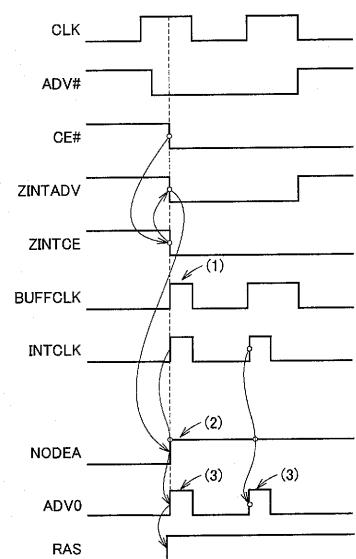

図49は、ADV0生成回路615の詳細な構成を示す。同図を参照して、クロックドインバータCIV63には、内部アドレス取込信号INTADVを受ける。クロックドインバータCIV63の出力がインバータIV29とインバータIV30とからなる双安定回路に送られる。双安定回路の出力および内部クロックINTCLKが反転論理積回路NAND23に送られる。反転論理積回路NAND23の出力がインバータIV31に送られ、インバータIV31の出力がADV0となる。一方、双安定回路の出力がインバータIV32に送られる。インバータIV32の出力および内部クロックINTCLKが反転論理積回路NAND24に送られる。反転論理積回路NAND24の出力がインバータIV33に送られ、インバータIV33の出力がZADV0となる。

【0302】

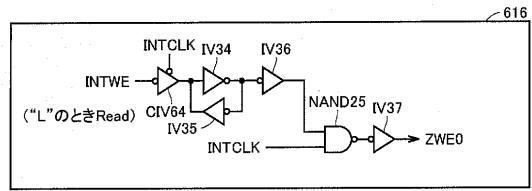

図50は、ZWE0生成回路616の詳細な構成を示す。同図を参照して、クロックドインバータCIV64には、内部ライトイネーブル信号INTWEを受ける。クロックドインバータCIV64の出力がインバータIV34とインバータIV35とからなる双安定回路に送られる。双安定回路の出力がインバータIV36に送られる。インバータIV36の出力および内部クロックINTCLKが反転論理積回路NAND25に送られる。反転論理積回路NAND25の出力がインバータIV37に送られ、インバータIV37の出力がZWE0となる。

【0303】

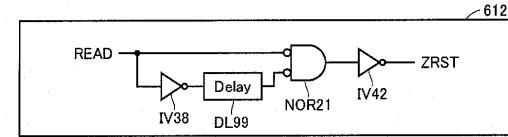

図51は、ZRS T生成回路612の詳細な構成を示す。同図を参照して、インバータIV38は、読み出し信号READを受ける。遅延回路(Delay)DL99は、インバータIV99の出力を遅延させる。反転論理和回路NOR21は、読み出し信号READと遅延回路(Delay)DL99の出力を受ける。インバータIV42は、反転論理和回路NOR21の出力を受ける。インバータIV42の出力が反転リセット信号ZRS Tとなる。

【0304】

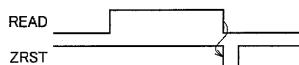

図52は、反転リセット信号ZRS Tが生成されるタイミングを表す図である。同図に

10

20

30

40

50

示すように、反転リセット信号Z R S Tは、読み出し信号R E A Dが「L」に非活性化されるときに、活性化されて「L」レベルのパルスとなる。

【0305】

図53は、マスク制御回路617の詳細な構成を示す。同図は、下位側(L B)のみを示しているが、上位側(U B)も、これと同様である。図53を参照して、第1制御回路631において、反転論理積回路N A N D 2 6は、A D V 0、Z L B 0、およびZ W E 0を受ける。反転論理積回路N A N D 2 9および反転論理積回路N A N D 3 0は、フリップフロップを構成する。反転論理積回路N A N D 2 9は、反転論理積回路N A N D 2 6の出力を受ける。反転論理積回路N A N D 3 0は、反転リセット信号Z R S Tを受ける。インバータI V 3 9は、反転論理積回路N A N D 2 9の出力を受ける。インバータI V 3 9の出力は、第1出力イネーブル信号O E 1となる。このような構成により、第1の制御回路631は、外部バイトマスク信号L B #がバーストアクセスの先頭のビットのバイトマスクを行なうことを示す時には、外部バイトマスク信号L B #が「H」となったクロックC L Kから、出力回路620から先頭のビットが出力されるタイミングを含む時点まで、第1の出力イネーブル信号O E 1を「L」にする。

10

【0306】

第2制御回路632において、反転論理積回路N A N D 2 7は、Z A D V 0、Z L B 0、およびZ W E 0を受ける。反転論理積回路N A N D 3 1および反転論理積回路N A N D 3 2は、フリップフロップを構成する。反転論理積回路N A N D 3 1は、反転論理積回路N A N D 2 7の出力を受ける。反転論理積回路N A N D 3 1は、反転リセット信号Z R S Tを受ける。反転論理積回路N A N D 3 5は、Z W A I T信号および反転論理積回路N A N D 3 1の出力とを受ける。反転論理積回路N A N D 3 5の出力は、第2出力イネーブル信号O E 2となる。このような構成により、第2制御回路632は、外部バイトマスク信号L B #が、先頭のビット以外のビットのバイトマスクを行なうことを示す時に、次のロウへの移行のためのロウアクセス処理が行なわれなかつとした場合にそのビットが出力回路620出力されるタイミングにW A I T信号が「H」のときに、通常通り第2の出力イネーブル信号O E 2を「L」にし、そのタイミングにW A I T信号が「L」のときに、第2の出力イネーブル信号O E 2を「L」にせず、バイトマスク信号に基づいて生成された信号(すなわち、反転論理積回路N A N D 2 7の出力)を第3制御回路633に出力する。

20

30

【0307】

第3制御回路633において、インバータI V 4 1は、Z W A I T信号を受ける。遅延回路(D e l a y)D L 2 1は、インバータI V 4 1の出力を遅延させる。反転論理積回路N A N D 2 8は、Z W A I T信号と遅延回路(D e l a y)D L 2 1の出力を受ける。反転論理積回路N A N D 3 3および反転論理積回路N A N D 3 4は、フリップフロップを構成する。反転論理積回路N A N D 3 3は、反転論理積回路N A N D 2 7の出力を受ける。反転論理積回路N A N D 3 4、反転リセット信号Z R S Tおよび反転論理積回路N A N D 2 8の出力を受ける。インバータI V 4 0は、Z W A I T信号を受ける。反転論理積回路N A N D 3 6は、インバータI V 4 0の出力と、反転論理積回路N A N D 3 3の出力を受ける。反転論理積回路N A N D 3 6の出力は、第3出力イネーブル信号O E 3となる。このような構成により、第3制御回路633は、バイトマスク信号に基づいて生成された信号を受けて保持し、W A I T信号が「L」から「H」になったタイミングに、第3の出力イネーブル信号O E 3を「L」にする。

40

【0308】

反転論理積回路N A N D 6 0は、第1の出力イネーブル信号O E 1、第2の出力イネーブル信号O E 2、および第3の出力イネーブル信号O E 3を受ける。インバータI V 4 3は、反転論理積回路N A N D 6 0の出力を受けて、出力イネーブル信号O Eを出力する。反転論理積回路N A N D 6 0およびインバータI V 4 3によって、第1の出力イネーブル信号O E 1、第2の出力イネーブル信号O E 2、および第3の出力イネーブル信号O E 3のうちの少なくとも1つが「L」のときに、出力イネーブル信号O Eは「L」となる。

50

## 【0309】

再び、図44を参照して、ロウ制御回路618は、ロウアクセス処理（ワード線の活性化、センスアンプによる増幅など）を制御する。

## 【0310】

リフレッシュ制御回路621は、図示しない内部のリフレッシュタイマに基づいて、DRAMセルアレイのセルフリフレッシュ動作を制御する。

## 【0311】

WAIT制御回路619は、リフレッシュ制御回路621の制御によりリフレッシュ制御が行なわれている間、およびノーラップモードでバースト読出しの途中で最後のコラムに達したため、次のロウへの移行のためのロウアクセス処理（もとのロウのワード線の非活性化、新たなロウのワード線の活性化、およびセンスアンプによる増幅など）を行なっている間に、WAIT端子介して出力するWAIT信号のレベルを「L」とする。つまり、WAIT信号が「L」によって、データが出力されるまで待つことを外部に知らせる。

10

## 【0312】

（次のロウへの移行を伴わないときのアクセス動作）

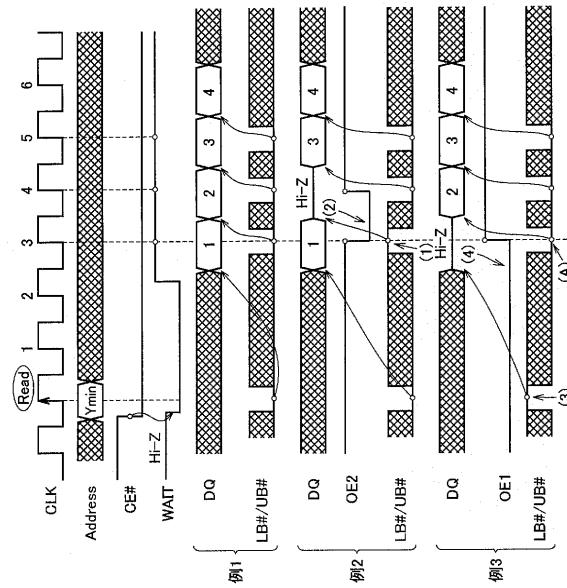

図54は、本実施の形態の同期式擬似SRAM600におけるバースト読出し時に次のロウへの移行を伴わないときの信号の変化を表すタイミングチャートである。同図を参照して、例1～例3の動作を説明する。

20

## 【0313】

（例1）マスクなしのとき

外部バイトマスク信号LB#、UB#は、「H」となることがない。この場合には、第1出力イネーブル信号OE1、第2出力イネーブル信号OE2、および第3出力イネーブル信号OE3は、全期間「H」となる。

30

## 【0314】

（例2）第2ビットをマスクするとき

外部バイトマスク信号LB#、UB#は、同図の（1）において、「H」となる。この場合には、第1出力イネーブル信号OE1および第3出力イネーブル信号OE3は、全期間「H」となる。一方、第2出力イネーブル信号OE2は、同図の（2）に示すように、第2ビットが出力回路620から出力されるタイミング（クロックCLK3の立ち上がりからクロックCLK4の立ち上がりまで）において「L」となる。

30

## 【0315】

（例3）第1ビットをマスクするとき

外部バイトマスク信号LB#、UB#は、同図の（3）において、「H」となる。この場合には、第2出力イネーブル信号OE2および第3出力イネーブル信号OE3は、全期間「H」となる。第1出力イネーブル信号OE1は、同図の（4）に示すように、外部バイトマスク信号LB#、UB#が「H」となったクロックCLKから、第1ビットが出力回路620から出力されるタイミングを含む時点まで（クロックCLK0の立ち上がりからクロックCLK3の立ち上がりまで）、「L」となる。

40

## 【0316】

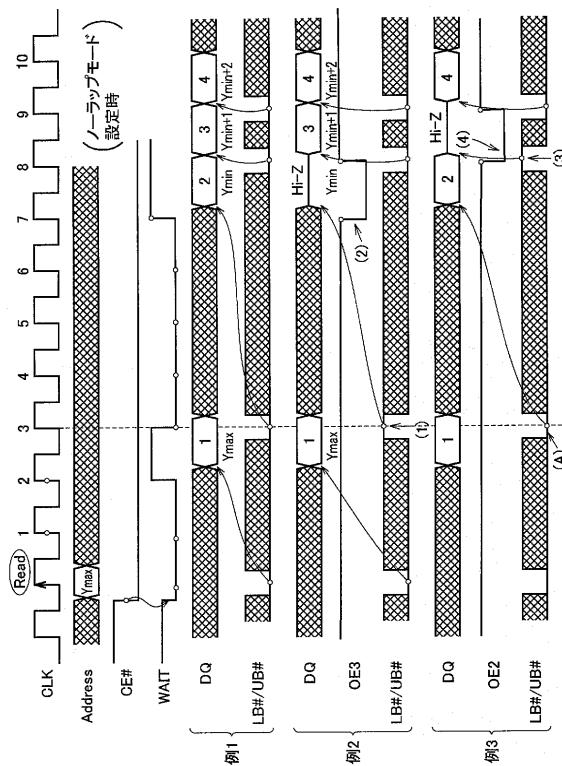

（ノーラップモードにおいて、次のロウへの移行を伴うときのアクセス動作）

図55は、本実施の形態の同期式擬似SRAM600におけるノーラップモード設定時に、バースト読出し時に次のロウへの移行を伴うときの変化を表すタイミングチャートである。同図を参照して、例1～例3の動作を説明する。

## 【0317】

（例1）マスクなしのとき

外部バイトマスク信号LB#、UB#は、「H」となることがない。第1出力イネーブル信号OE1、第2出力イネーブル信号OE2、および第3出力イネーブル信号OE3は、全期間「H」となる。

50

## 【0318】

（例2）第2ビットをマスクするとき（次のロウへの移行処理を伴う）

外部バイトマスク信号 L B #, U B # は、同図の(1)において、「H」となる。この場合には、第1出力イネーブル信号 O E 1 および第2出力イネーブル信号 O E 2 は、全期間「H」となる。第3出力イネーブル信号 O E 3 は、同図の(3)に示すように、W A I T 信号が「H」となったときのタイミング(クロック C L K 7 の立ち上がりからクロック C L K 8 の立ち上がりまで)において「L」となる。

### 【0319】

これにより、第2ビットのマスク処理は、次のロウのロウアクセス処理が終了して W A I T 信号が「H」となる時点まで延長される。

### 【0320】

(例3) 第3ビットをマスクするとき

外部バイトマスク信号 L B #, U B # は、同図の(3)において、「H」となる。この場合、第1出力イネーブル信号 O E 1 および第3出力イネーブル信号 O E 3 は、全期間「H」となる。第2出力イネーブル信号 O E 2 は、同図の(4)に示すように、第3ビットが出力回路 6 2 0 から出力されるタイミング(クロック C L K 8 の立ち上がりからクロック C L K 9 の立ち上がりまで)において「L」となる。

### 【0321】

(例4) 第1ビットをマスクするとき

図示しないが、図54の(例3)のとき同一である。

### 【0322】

以上の説明から明らかなように、第2ビットのバイトマスク信号の設定タイミング、すなわち、外部バイトマスク信号 L B #, U B # を与えるタイミングは、図54および図55のいずれの(A)で示されるタイミングである。したがって、バースト読出しありバースト書き込みの途中に、次のロウに移行する場合においても、外部からは、次のロウに移行しない場合と同様にしてバイトマスク信号を与えることができる。

### 【0323】

なお、本実施の形態は、ノーラップモードにのみ適用できるものではなく、チップイネーブル信号が非活性になるまで連続して読出し/書き込みを行なうコンティニュアスモードにおいても有効である。

### 【0324】

また、本実施の形態は、同期式擬似 S R A M に限定して適用されるものではなく、クロックに同期して動作する半導体記憶装置であればどのようなものにも適用することができる。

### 【0325】

[第7の実施形態]

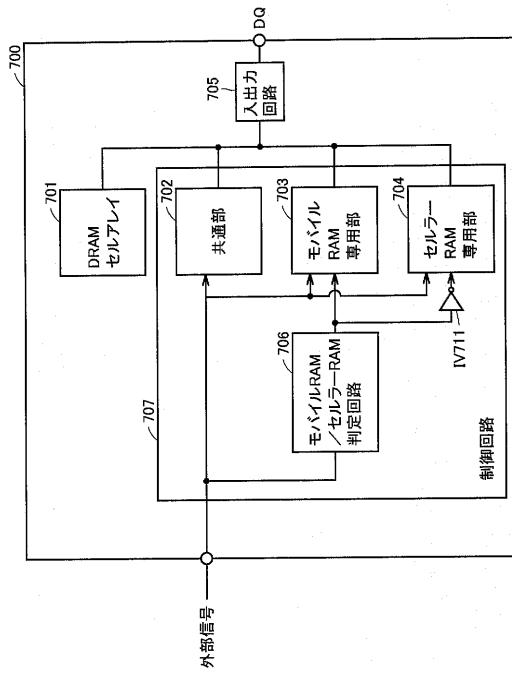

本実施の形態は、モバイル R A M と、セルラー R A M の両方の機能を備えたモバイル/セルラー兼用 R A M に関する。ここで、セルラー R A M とは、非特許文献1に記載されている同期型の擬似 S R A M である。モバイル R A M は、携帯電話用の特有の機能を備えた擬似 S R A M である。

### 【0326】

(構成)

図56は、本実施の形態のモバイル/セルラー兼用 R A M 7 0 0 の構成を示す。同図を参照して、このモバイル/セルラー兼用 R A M 7 0 0 は、D R A M セルアレイ 7 0 1 と、制御回路 7 0 7 と、入出力回路 7 0 5 とを備える。

### 【0327】

D R A M セルアレイ 7 0 7 は、ダイナミックランダムアクセスメモリ(D R A M)のセルで構成されるメモリアレイである。

### 【0328】

入出力回路 7 0 5 は、データ出力端子 D Q を通じて外部からデータを受けるとともに、外部にデータを出力する。

### 【0329】

10

20

30

40

50

制御回路 707 は、共通部 702 と、モバイル RAM 専用部 703 と、セルラー RAM 専用部 704 と、モバイル RAM / セルラー RAM 判定回路 706 とを含む。

【0330】

モバイル RAM / セルラー RAM 判定回路 706 は、外部信号に応じて、共通部 702 、モバイル RAM 専用部 703 、およびセルラー RAM 専用部 704 のいずれを動作させるかを判定して、動作させる。

【0331】

共通部 702 は、モバイル RAM とセルラー RAM に共通の機能を実行する。

【0332】

モバイル RAM 専用部 703 は、モバイル RAM のみが有する機能を実行する。

10

【0333】

セルラー RAM 専用部 704 は、セルラー RAM のみが有する機能を実行する。

【0334】

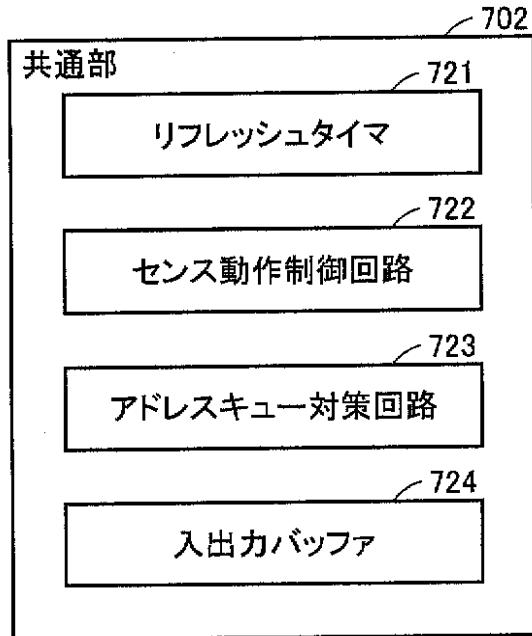

図 57 は、共通部 702 の構成を示す。同図に示すように、共通部 702 は、リフレッシュタイム 721 と、センス動作制御回路 722 と、アドレスキー対策回路 723 と、入出力バッファ 724 とを備える。

【0335】

リフレッシュタイム 721 は、セルフリフレッシュを行なうタイミング信号を出力する。

【0336】

センス動作制御回路 722 は、センスアンプの動作を制御する。

20

【0337】

アドレスキー対策回路 723 は、アドレスキーが発生しないように制御する回路である。

【0338】

入出力バッファ 724 は、外部制御信号、外部アドレス信号、外部クロックなどを受けて保持し、内部制御信号、内部アドレス信号、内部クロックなどを生成するとともに、外部へ出力するデータを保持する。

【0339】

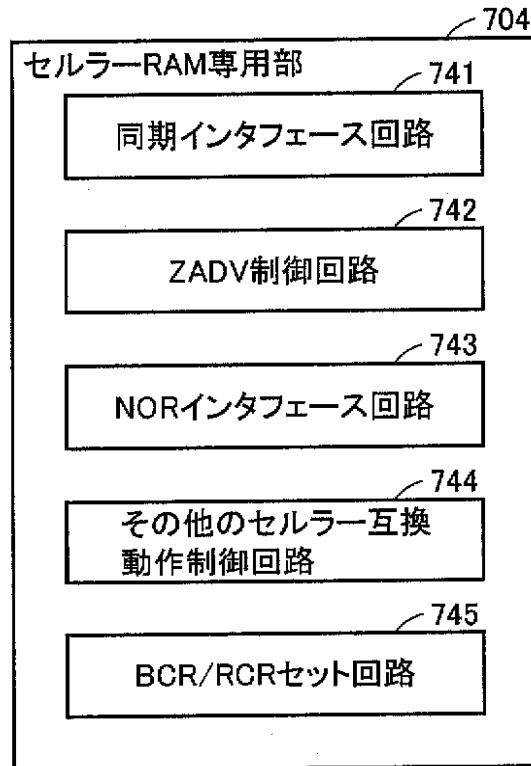

図 58 は、セルラー RAM 専用部 704 の構成を示す。同図に示すように、セルラー RAM 専用部 704 は、同期インターフェース回路 741 と、ZADV 制御回路 742 と、NOR インタフェース回路 743 と、その他のセルラー互換動作制御回路 744 と、BCR / RCR セット回路 745 とを備える。

30

【0340】

同期インターフェース回路 741 は、クロックに同期した動作を制御する。

【0341】

ZADV 制御回路 742 は、外部アドレス取込信号 ADV # に基づき、外部アドレスの取込みを制御する。

【0342】

NOR インタフェース回路 743 は、NOR 型フラッシュメモリとのインターフェースを制御する。

40

【0343】

その他のセルラー互換動作制御回路 744 は、たとえば、SRAM 互換のインターフェースを制御する。

【0344】

BCR / RCR セット回路 745 は、BCR 、およびRCR をセットする。

【0345】

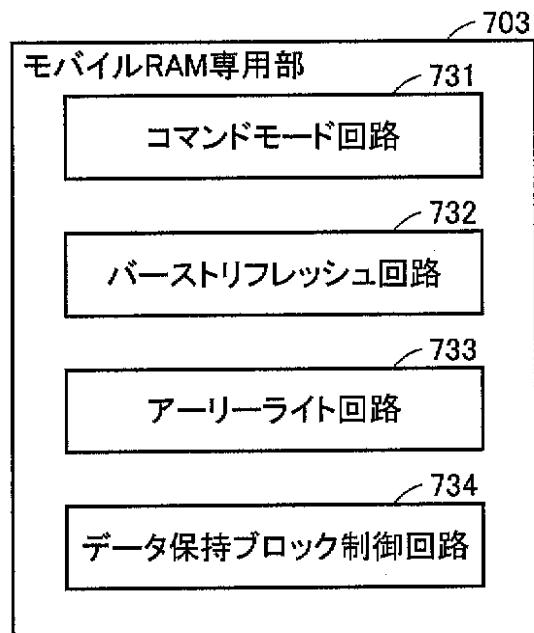

図 59 は、モバイル RAM 専用部 703 の構成を示す。同図に示すように、モバイル RAM 専用部 703 は、コマンドモード回路 731 と、バーストリフレッシュ回路 732 と、アーリーライト回路 733 と、データ保持ブロック制御回路 734 とを備える。

50

## 【0346】

コマンドモード回路731は、外部の信号の組合せによって、内部のレジスタのセットおよびリセットを行なう。

## 【0347】

バーストリフレッシュ回路732は、リフレッシュ要求を内部カウンタに保持しておき、ある一定のタイミングが入力された時に、連続してリフレッシュ動作を行なう。

## 【0348】

アーリーライト回路733は、ライト動作のタイミングを早くしたアーリーライト動作を制御する。

## 【0349】

データ保持ブロック制御回路734は、選択したブロックのみリフレッシュを行なうように制御することで、選択したブロックのデータのみ保持する。

## 【0350】

以上のように、本実施の形態に係るRAMによれば、セルラーRAMとモバイルRAMの両方の機能を効率よく実現するように構成したので、生産管理を効率化でき、製品切替え時期における在庫の低減を防止し、さらに開発コストを削減できる。

## 【0351】

## [第8の実施形態]

本実施の形態は、バーストレングスカウンタを用いてプリチャージを実行する同期式擬似SRAMに関する。

## 【0352】

## (構成)

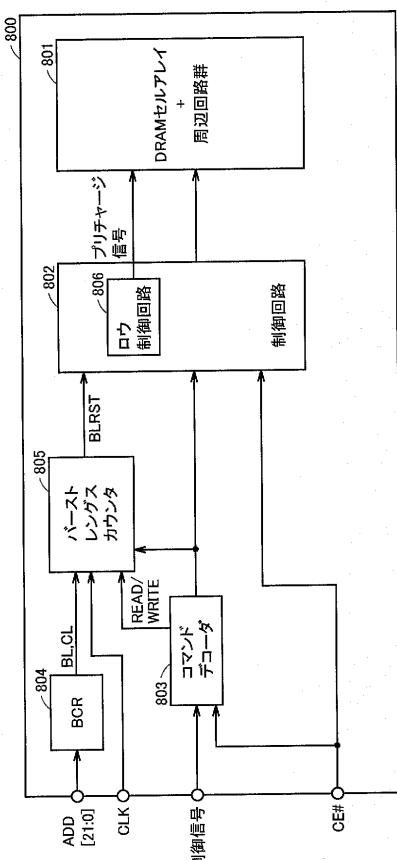

図60は、本実施の形態に係る同期式擬似SRAM800の構成を示す。同図を参照して、この同期式擬似SRAM800は、DRAMセルアレイ+周辺回路群801と、制御回路802と、コマンドデコーダ803と、BCR(Burst Configuration Register)804と、バーストレングスカウンタ805とを備える。

## 【0353】

DRAMセルアレイ+周辺回路群801のDRAMセルアレイは、ダイナミックランダムアクセスメモリ(DRAM)のセルで構成されるメモリアレイである。周辺回路群は、グローバル入出力線対GIO(GIOおよび/GIO)と、各列に対応して設けられた列選択線と、列選択ゲートと、センスアンプと、プリアンプと、ライトドライバと、ロウデコーダ、コラムデコーダなどを含む。

## 【0354】

コマンドデコーダ803は、外部制御信号より生成された内部制御信号の論理レベルの組合せに従って、ロウ活性化信号ACT、読み出し信号READ、および書き込み信号WRITEを生成する。

## 【0355】

BCR804は、外部のシステムとのインターフェース、たとえば、バーストレングスBL、およびコマンドレイテンシCLなどを記憶する。

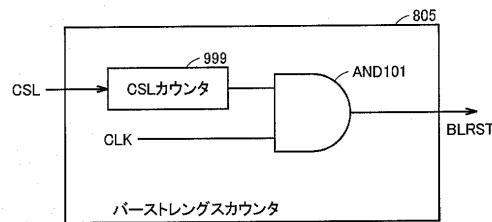

## 【0356】

図61は、バーストレングスカウンタ805の詳細な構成を示す。同図を参照して、バーストレングスカウンタ805は、CSLカウンタ999と、論理積回路AND101とを含む。CSLカウンタ999は、コラム選択信号CSLを受ける。CSLカウンタ999は、バーストレングスBL個のコラム選択信号CSLのパルスをカウントすると、「H」を出力する。論理積回路AND101は、外部クロックCLKおよびCSLカウンタ999の出力を受けて、CSLカウンタ999の出力が「H」となった後の最初のクロックCLKが入力されたタイミングで、バーストレングスリセット信号BL\_RSTを「H」に活性化する。

## 【0357】

制御回路802は、ロウ制御回路806を含む。ロウ制御回路806は、バーストレン

10

20

30

40

50

グスリセット信号 B L R S T を受けると、プリチャージ信号 P R C を活性化する。このプリチャージ信号 P R C によって、ワード線が非活性化され、ビット線対がプリチャージされる。

【 0 3 5 8 】

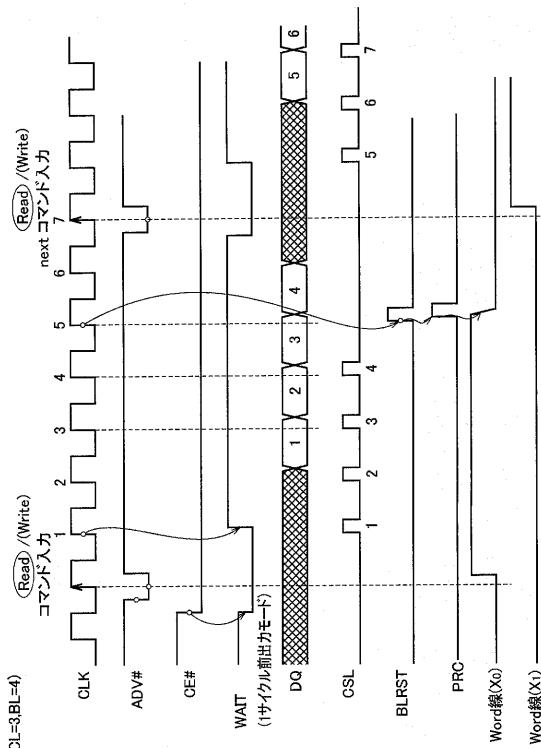

( 動作 )

図 6 2 は、ワード線が非活性化されるタイミングチャートを示す。同図に示すように、読み出し信号 R E A D または書込み信号 W R I T E を受けたクロックのタイミングをクロック C L K 0 とした時に、コマンドレイテンシ C L = 2 、バーストレングス B L = 4 より、バーストアクセスの最後のコラムの選択のためのコラム選択信号 C S L がクロック C L K 4 のタイミングで活性化される。バーストレングスカウンタ 8 0 5 は、 C L K 0 から、( C L + B L - 1 ) = 5 個後のクロックであるクロック C L K 5 のタイミングで、バーストレングスリセット信号 B L R S T を「 H 」に活性化する。そして、このバーストレングスリセット信号 B L R S T に基づいて、プリチャージ信号 P R C が活性化され、選択されていたワード線 ( X 0 ) が非活性化され、ビット線対がプリチャージされる。

【 0 3 5 9 】

以上のように、本実施の形態に係る同期式擬似 S R A M によれば、バーストレングスカウンタ 8 0 5 は、バーストレングス B L 個のコラム選択信号 C S L のパルスをカウントすると、バーストレングスリセット信号 B L R S T を活性化するので、外部チップイネーブル信号 C E # を「 H 」にもどさなくても、ワード線を非活性化することができる。

【 0 3 6 0 】

以上のように、本実施の形態に係る同期式擬似 S R A M によれば、外部制御によって、ワード線を非活性化するのではなく、内部制御でワード線を非活性化するので、制御が簡易になる。

【 0 3 6 1 】

なお、外部アドレス取込み信号 A D V # の立ち下りを起点にリセット信号を発生させて、このリセット信号によってプリチャージ信号 P R C を発生するようにしてもよい。

【 0 3 6 2 】

なお、本実施の形態では、バーストレングスリセット信号 B L R S T に基づき、ワード線の非活性化を行なったが、これに限定するものではなく、たとえば、読みしも書き込みも行なわれていないスタンバイ状態にするものとしてもよい。

【 0 3 6 3 】

また、本実施の形態は、同期式擬似 S R A M に限定して適用されるものではなく、クロックに同期して動作する半導体記憶装置であればどのようなものにも適用することができる。

【 0 3 6 4 】

[ 第 9 の 実施 形態 ]

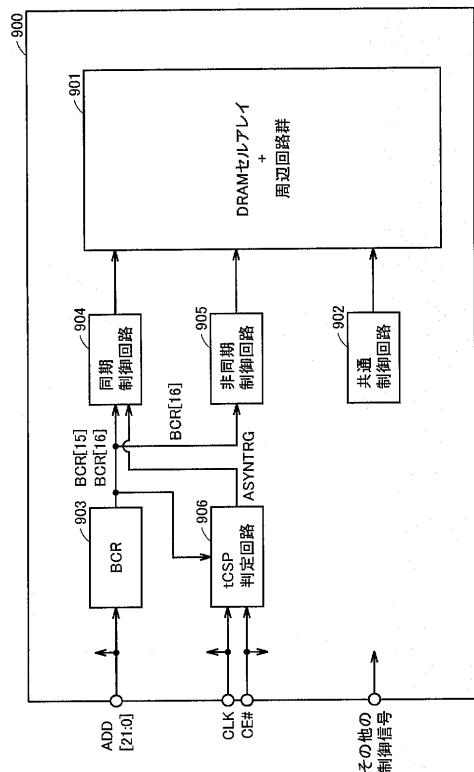

本実施の形態は、同期モード固定のモードを有する同期式擬似 S R A M に関する。

【 0 3 6 5 】

( 従来の同期モード / 非同期モードの設定 )