(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4014048号

(P4014048)

(45) 発行日 平成19年11月28日(2007.11.28)

(24) 登録日 平成19年9月21日(2007.9.21)

(51) Int.C1.

F 1

|             |           |             |   |

|-------------|-----------|-------------|---|

| HO3K 17/16  | (2006.01) | HO3K 17/16  | H |

| HO3K 17/695 | (2006.01) | HO3K 17/16  | L |

| HO3K 17/687 | (2006.01) | HO3K 17/687 | B |

|             |           | HO3K 17/687 | F |

請求項の数 3 (全 10 頁)

|           |                               |

|-----------|-------------------------------|

| (21) 出願番号 | 特願2004-164291 (P2004-164291)  |

| (22) 出願日  | 平成16年6月2日 (2004.6.2)          |

| (65) 公開番号 | 特開2005-348019 (P2005-348019A) |

| (43) 公開日  | 平成17年12月15日 (2005.12.15)      |

| 審査請求日     | 平成17年3月10日 (2005.3.10)        |

|           |                                            |

|-----------|--------------------------------------------|

| (73) 特許権者 | 000116024<br>ローム株式会社<br>京都府京都市右京区西院溝崎町21番地 |

| (74) 代理人  | 100121337<br>弁理士 藤河 恒生                     |

| (72) 発明者  | 大久保 利郎<br>京都府京都市右京区西院溝崎町21番地<br>ローム株式会社内   |

審査官 白井 亮

最終頁に続く

(54) 【発明の名称】コイル負荷駆動出力回路

## (57) 【特許請求の範囲】

## 【請求項 1】

電源電位と接地電位との間に直列に接続され、中点から電源側駆動トランジスタ制御電圧を出力する第1及び第2の制御トランジスタと、

第1及び第2の制御トランジスタに流れる電流をそれぞれ制限する第1及び第2の電流制限インピーダンス素子と、

電源電位と接地電位との間に直列に接続され、中点から接地側駆動トランジスタ制御電圧を出力する第3及び第4の制御トランジスタと、

第3及び第4の制御トランジスタに流れる電流をそれぞれ制限する第3及び第4の電流制限インピーダンス素子と、

電源電位と接地電位との間に直列に接続され、それが電源側駆動トランジスタ制御電圧又は接地側駆動トランジスタ制御電圧により制御され、中点からコイル負荷を駆動するための駆動電圧を出力する電源側駆動トランジスタ及び接地側駆動トランジスタと、

電源側駆動トランジスタ制御電圧により制御され、オンしていると強制的に接地側駆動トランジスタをオフする電源側検出トランジスタと、

接地側駆動トランジスタ制御電圧により制御され、オンしていると強制的に電源側駆動トランジスタをオフする接地側検出トランジスタと、を備え、

電源側駆動トランジスタはP型MOSトランジスタ、接地側駆動トランジスタはN型MOSトランジスタであり、

電源側駆動トランジスタがオフするとき、前記駆動電圧がコイル負荷によって急激に降

10

20

下しないように第1の電流制限インピーダンス素子により電源側駆動トランジスタのゲート電圧を徐々に上昇させ、その後接地側駆動トランジスタがオンするとき、第3の電流制限インピーダンス素子を第1の電流制限インピーダンス素子の抵抗値よりも大きくすることによって電源側駆動トランジスタから接地側駆動トランジスタに貫通して電流が流れないように接地側駆動トランジスタのゲート電圧を徐々に上昇させ、

接地側駆動トランジスタがオフするとき、前記駆動電圧がコイル負荷によって急激に上昇しないように第4の電流制限インピーダンス素子により接地側駆動トランジスタのゲート電圧を徐々に下降させ、その後電源側駆動トランジスタがオンするとき、第2の電流制限インピーダンス素子を第4の電流制限インピーダンス素子の抵抗値よりも大きくすることによって電源側駆動トランジスタから接地側駆動トランジスタに貫通して電流が流れないように電源側駆動トランジスタのゲート電圧を徐々に下降させることを特徴とするコイル負荷駆動出力回路。

### 【請求項2】

電源電位と接地電位との間に直列に接続され、中点から電源側駆動トランジスタ制御電圧を出力する第1及び第2の制御トランジスタと、

第1及び第2の制御トランジスタに流れる電流をそれぞれ制限する第1及び第2の電流制限インピーダンス素子と、

電源電位と接地電位との間に直列に接続され、中点から接地側駆動トランジスタ制御電圧を出力する第3及び第4の制御トランジスタと、

第3及び第4の制御トランジスタに流れる電流をそれぞれ制限する第3及び第4の電流制限インピーダンス素子と、

電源電位と接地電位との間に直列に接続され、それぞれが電源側駆動トランジスタ制御電圧又は接地側駆動トランジスタ制御電圧により制御され、中点からコイル負荷を駆動するための駆動電圧を出力する電源側駆動トランジスタ及び接地側駆動トランジスタと、

電源側駆動トランジスタ制御電圧により制御され、オンしていると強制的に接地側駆動トランジスタをオフする電源側検出トランジスタと、

接地側駆動トランジスタ制御電圧により制御され、オンしていると強制的に電源側駆動トランジスタをオフする接地側検出トランジスタと、を備え、

電源側駆動トランジスタ及び接地側駆動トランジスタは共にN型MOSトランジスタであり、

電源側駆動トランジスタがオフするとき、前記駆動電圧がコイル負荷によって急激に下降しないように第2の電流制限インピーダンス素子により電源側駆動トランジスタのゲート電圧を徐々に下降させ、その後接地側駆動トランジスタがオンするとき、第3の電流制限インピーダンス素子を第2の電流制限インピーダンス素子の抵抗値よりも大きくすることによって電源側駆動トランジスタから接地側駆動トランジスタに貫通して電流が流れないように接地側駆動トランジスタのゲート電圧を徐々に上昇させ、

接地側駆動トランジスタがオフするとき、前記駆動電圧がコイル負荷によって急激に上昇しないように第4の電流制限インピーダンス素子により接地側駆動トランジスタのゲート電圧を徐々に下降させ、その後電源側駆動トランジスタがオンするとき、第1の電流制限インピーダンス素子を第4の電流制限インピーダンス素子の抵抗値よりも大きくすることによって電源側駆動トランジスタから接地側駆動トランジスタに貫通して電流が流れないように電源側駆動トランジスタのゲート電圧を徐々に上昇させることを特徴とするコイル負荷駆動出力回路。

### 【請求項3】

請求項1又は2に記載のコイル負荷駆動出力回路において、

電源側検出トランジスタのゲートには電源側駆動トランジスタ制御電圧が入力され、接地側検出トランジスタのゲートには接地側駆動トランジスタ制御電圧が入力されていることを特徴とするコイル負荷駆動出力回路。

### 【発明の詳細な説明】

### 【技術分野】

**【0001】**

本発明は、モータやアクチュエータなどのコイル負荷を駆動するためのコイル負荷駆動出力回路に関するものである。

**【背景技術】****【0002】**

通常、コイル負荷を駆動するのにパルス幅変調（P W M）パルスを用いた装置では、そのスイッチングにより発生する輻射ノイズが多いため、他の信号へのクロストーク等の影響などが問題となる。特に、コイル負荷の駆動電圧を出力するコイル負荷駆動出力回路の駆動トランジスタは電流出力能力が大きいため、そのスイッチングによる輻射ノイズは大きい。

10

**【0003】**

一方、一般的の出力回路でのスイッチングによるノイズ低減対策としては例えば特許文献1、2に示されるような提案がなされている。すなわち、これらの出力回路は、電源側駆動トランジスタ又は接地側駆動トランジスタを徐々にオンさせることで、ノイズ低減を図っている。また、それにより同時に電源側駆動トランジスタと接地側駆動トランジスタにおける貫通電流の防止も図っている。

**【0004】**

【特許文献1】特開平6-152374号公報

【特許文献2】特開平11-317653号公報

**【発明の開示】**

20

**【発明が解決しようとする課題】****【0005】**

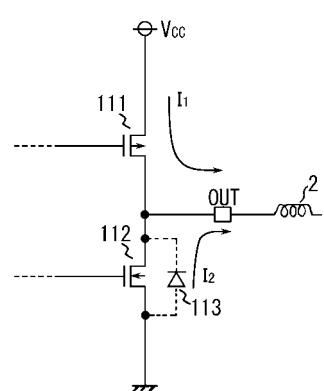

ところが、この出力回路が駆動する負荷がコイル負荷の場合、すなわち、出力回路がコイル負荷駆動出力回路である場合、コイル負荷の誘導性の性質により特別な現象が起きる。例えば、図4に示すように、コイル負荷2に出力端子OUTから電流I<sub>1</sub>の供給をしている電源側駆動トランジスタ111がスイッチングによりオフになったとき、コイル負荷2の誘導性の性質により電流は流れ続けようとするため、回生電流I<sub>2</sub>が接地側駆動トランジスタ112と並列に存在する寄生ダイオード113を通ってコイル負荷2に流れる。従って、このとき、出力端子OUTの電圧は電源電位V<sub>cc</sub>から接地電位以下に急激に下降して輻射ノイズを発生する。

30

**【0006】**

この輻射ノイズは、通常、コンデンサなどのノイズ対策部品を必要とする箇所に実装することで対処が可能であるが、輻射ノイズ自体を低減させることは性能やコストの面から重要である。

**【0007】**

本発明は、係る事由に鑑みてなされたものであり、その目的は、スイッチングによる輻射ノイズを低減することができるコイル負荷駆動出力回路を提供することにある。

**【課題を解決するための手段】****【0008】**

上記目的を達成するために、請求項1に記載のコイル負荷駆動出力回路は、電源電位と接地電位との間に直列に接続され、中点から電源側駆動トランジスタ制御電圧を出力する第1及び第2の制御トランジスタと、第1及び第2の制御トランジスタに流れる電流をそれぞれ制限する第1及び第2の電流制限インピーダンス素子と、電源電位と接地電位との間に直列に接続され、中点から接地側駆動トランジスタ制御電圧を出力する第3及び第4の制御トランジスタと、第3及び第4の制御トランジスタに流れる電流をそれぞれ制限する第3及び第4の電流制限インピーダンス素子と、電源電位と接地電位との間に直列に接続され、それぞれが電源側駆動トランジスタ制御電圧又は接地側駆動トランジスタ制御電圧により制御され、中点からコイル負荷を駆動するための駆動電圧を出力する電源側駆動トランジスタ及び接地側駆動トランジスタと、電源側駆動トランジスタ制御電圧により制御され、オンしていると強制的に接地側駆動トランジスタをオフする電源側検出トランジ

40

50

スタと、接地側駆動トランジスタ制御電圧により制御され、オンしていると強制的に電源側駆動トランジスタをオフする接地側検出トランジスタと、を備え、電源側駆動トランジスタはP型MOSトランジスタ、接地側駆動トランジスタはN型MOSトランジスタであり、電源側駆動トランジスタがオフするとき、前記駆動電圧がコイル負荷によって急激に下降しないように第1の電流制限インピーダンス素子により電源側駆動トランジスタのゲート電圧を徐々に上昇させ、その後接地側駆動トランジスタがオンするとき、第3の電流制限インピーダンス素子を第1の電流制限インピーダンス素子の抵抗値よりも大きくすることによって電源側駆動トランジスタから接地側駆動トランジスタに貫通して電流が流れないように接地側駆動トランジスタのゲート電圧を徐々に上昇させ、接地側駆動トランジスタがオフするとき、前記駆動電圧がコイル負荷によって急激に上昇しないように第4の電流制限インピーダンス素子により接地側駆動トランジスタのゲート電圧を徐々に下降させ、その後電源側駆動トランジスタがオンするとき、第2の電流制限インピーダンス素子を第4の電流制限インピーダンス素子の抵抗値よりも大きくすることによって電源側駆動トランジスタから接地側駆動トランジスタに貫通して電流が流れないように電源側駆動トランジスタのゲート電圧を徐々に下降させることを特徴とする。

#### 【0009】

請求項2に記載のコイル負荷駆動出力回路は、電源電位と接地電位との間に直列に接続され、中点から電源側駆動トランジスタ制御電圧を出力する第1及び第2の制御トランジスタと、第1及び第2の制御トランジスタに流れる電流をそれぞれ制限する第1及び第2の電流制限インピーダンス素子と、電源電位と接地電位との間に直列に接続され、中点から接地側駆動トランジスタ制御電圧を出力する第3及び第4の制御トランジスタと、第3及び第4の制御トランジスタに流れる電流をそれぞれ制限する第3及び第4の電流制限インピーダンス素子と、電源電位と接地電位との間に直列に接続され、それぞれが電源側駆動トランジスタ制御電圧又は接地側駆動トランジスタ制御電圧により制御され、中点からコイル負荷を駆動するための駆動電圧を出力する電源側駆動トランジスタ及び接地側駆動トランジスタと、電源側駆動トランジスタ制御電圧により制御され、オンしていると強制的に接地側駆動トランジスタをオフする電源側検出トランジスタと、接地側駆動トランジスタ制御電圧により制御され、オンしていると強制的に電源側駆動トランジスタをオフする接地側検出トランジスタと、を備え、電源側駆動トランジスタ及び接地側駆動トランジスタは共にN型MOSトランジスタであり、電源側駆動トランジスタがオフするとき、前記駆動電圧がコイル負荷によって急激に下降しないように第2の電流制限インピーダンス素子により電源側駆動トランジスタのゲート電圧を徐々に下降させ、その後接地側駆動トランジスタがオンするとき、第3の電流制限インピーダンス素子を第2の電流制限インピーダンス素子の抵抗値よりも大きくすることによって電源側駆動トランジスタから接地側駆動トランジスタに貫通して電流が流れないように接地側駆動トランジスタのゲート電圧を徐々に上昇させ、接地側駆動トランジスタがオフするとき、前記駆動電圧がコイル負荷によって急激に上昇しないように第4の電流制限インピーダンス素子により接地側駆動トランジスタのゲート電圧を徐々に下降させ、その後電源側駆動トランジスタがオンするとき、第1の電流制限インピーダンス素子を第4の電流制限インピーダンス素子の抵抗値よりも大きくすることによって電源側駆動トランジスタから接地側駆動トランジスタに貫通して電流が流れないように電源側駆動トランジスタのゲート電圧を徐々に上昇させることを特徴とする。

#### 【0010】

請求項3に記載のコイル負荷駆動出力回路は、請求項1又は2に記載のコイル負荷駆動出力回路において、電源側検出トランジスタのゲートには電源側駆動トランジスタ制御電圧が入力され、接地側検出トランジスタのゲートには接地側駆動トランジスタ制御電圧が入力されていることを特徴とする。

#### 【発明の効果】

#### 【0011】

本発明のコイル負荷駆動出力回路は、各制御トランジスタに流れる電流をそれぞれ制限

10

20

30

40

50

する電流制限インピーダンス素子を設けているので、電源側駆動トランジスタ及び接地側駆動トランジスタを徐々にオフ及びオンさせることができてスイッチングによる輻射ノイズを低減することができる。

【発明を実施するための最良の形態】

【0012】

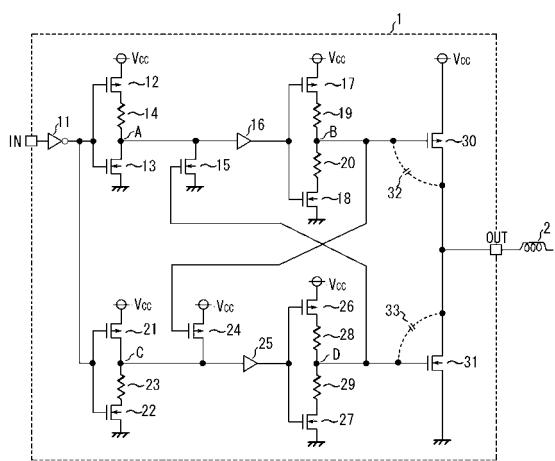

以下、本願発明を実施するための最良の形態であるコイル負荷駆動出力回路を説明する。図1にコイル負荷駆動出力回路1を示す。11はインバータであり、このインバータ11は、図外モータ制御回路又はアクチュエータ制御回路から入力端子INに入力されるハイ又はローレベルの入力信号(PWM信号)を反転出力する。12、13はP型MOSトランジスタ、N型MOSトランジスタであり、これらP型MOSトランジスタ12及びN型MOSトランジスタ13は、電源電位V<sub>cc</sub>と接地電位との間に直列に接続され、インバータ11の出力信号を入力して中点、すなわち節点Aから反転出力する。14は電流制限インピーダンス素子であり、この電流制限インピーダンス素子14はP型MOSトランジスタ12に流れる電流を制限する。15はN型MOSトランジスタである接地側検出トランジスタであり、この接地側検出トランジスタ15は、節点Aに接続され、後述の節点Dの電圧、すなわち接地側駆動トランジスタ制御電圧により制御される。16はバッファであり、このバッファ16は節点Aの電圧波形を整形する。17、18はP型MOSトランジスタである第1の制御トランジスタ、N型MOSトランジスタである第2の制御トランジスタであり、これら第1の制御トランジスタ17及び第2の制御トランジスタ18は、電源電位V<sub>cc</sub>と接地電位との間に直列に接続され、バッファ16の出力信号を入力して中点、すなわち節点Bから電源側駆動トランジスタ制御電圧を出力する。19、20は第1及び第2の電流制限インピーダンス素子であり、これら第1及び第2の電流制限インピーダンス素子19、20は第1及び第2の制御トランジスタ17、18に流れる電流をそれぞれ制限する。

【0013】

更に、21、22はP型MOSトランジスタ、N型MOSトランジスタであり、これらP型MOSトランジスタ21及びN型MOSトランジスタ22は、電源電位V<sub>cc</sub>と接地電位との間に直列に接続され、インバータ11の出力信号を入力して中点、すなわち節点Cから反転出力する。23は電流制限インピーダンス素子であり、この電流制限インピーダンス素子23はN型MOSトランジスタ22に流れる電流を制限する。24はP型MOSトランジスタである電源側検出トランジスタであり、この電源側検出トランジスタ24は、節点Cに接続され、節点Bの電圧、すなわち電源側駆動トランジスタ制御電圧により制御される。25はバッファであり、このバッファ25は節点Cの電圧波形を整形する。26、27はP型MOSトランジスタである第3の制御トランジスタ、N型MOSトランジスタである第4の制御トランジスタであり、これら第3の制御トランジスタ26及び第4の制御トランジスタ27は、電源電位V<sub>cc</sub>と接地電位との間に直列に接続され、バッファ25の出力信号を入力して中点、すなわち節点Dから接地側駆動トランジスタ制御電圧を出力する。28、29は第3及び第4の電流制限インピーダンス素子であり、これら第3及び第4の電流制限インピーダンス素子28、29は、第3及び第4の制御トランジスタ26、27に流れる電流をそれぞれ制限する。

【0014】

更に、30、31はP型MOSトランジスタである電源側駆動トランジスタ、N型MOSトランジスタである接地側駆動トランジスタであり、これら電源側駆動トランジスタ30及び接地側駆動トランジスタ31は、電源電位V<sub>cc</sub>と接地電位との間に直列に接続され、それそれが電源側駆動トランジスタ制御電圧又は接地側駆動トランジスタ制御電圧により制御され、中点から出力端子OUTを介してコイル負荷2を駆動するための駆動電圧を出力する。なお、図1においては、理解を容易にするために、電源側駆動トランジスタ30のドレイン・ゲート間の寄生容量32と、接地側駆動トランジスタ31のドレイン・ゲート間の寄生容量33と、を示している。また、コイル負荷2の図示しない片側にはコイル負荷駆動出力回路1と同様の回路が設けられる。

10

20

30

40

50

## 【0015】

ここで、電流制限インピーダンス素子14、19、20、23、28、29は抵抗である。電流制限インピーダンス素子14は、接地側検出トランジスタ15がオンしていると、P型MOSトランジスタ12がオンしていても節点Aの電圧をローレベルに保つことができる程度の抵抗値である。電流制限インピーダンス素子23は、電源側検出トランジスタ24がオンしていると、N型MOSトランジスタ22がオンしていても節点Cの電圧をハイレベルに保つことができる程度の抵抗値である。第1の電流制限インピーダンス素子19と第4の電流制限インピーダンス素子29の抵抗値は同一又は略同一であり（例えば1K乃至2K）、第2の電流制限インピーダンス素子20と第3の電流制限インピーダンス素子28の抵抗値（例えば10K乃至30K）よりも小さい。

10

## 【0016】

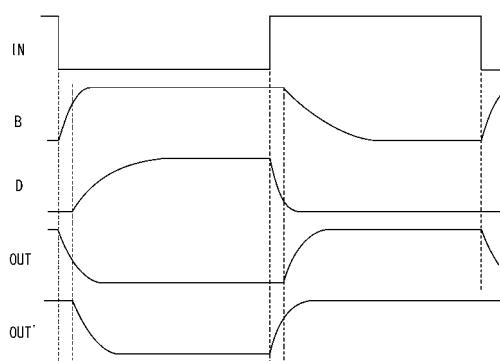

このコイル負荷駆動出力回路1の動作を図2の波形図に基づいて説明する。先ず、出力端子OUTからコイル負荷2の方向に電流が流れている場合を説明する。なお、同図において、OUTの波形はこの場合の出力端子OUTの電圧波形を示し、OUT'は後述のコイル負荷2から出力端子OUTの方向に電流が流れている場合の出力端子OUTの電圧波形を示す。入力端子INからの入力信号がハイレベルからローレベルに変化すると、節点Aはローレベルとなり、節点Bの電圧は、第1の制御トランジスタ17がオンするので、インピーダンス素子19の抵抗値と寄生容量32の容量値で決まる時定数で上昇する。節点Bの電圧変化に従って電源側駆動トランジスタ30のオン抵抗は徐々に高くなり、コイル負荷2は誘導性の性質により電流を流し続けようとするため、出力端子OUTの電圧は徐々に降下する。従って、出力端子OUTの電圧は急激には降下しないので、輻射ノイズが低減される。

20

## 【0017】

なお、このとき、電源側検出トランジスタ24はオンしているので、節点Cはハイレベルに、節点Dはローレベルに保たれ、従って、接地側駆動トランジスタ31は入力端子INからの入力信号に係わらず強制的にオフされている。そして、節点Bの電圧が更に上昇して電源側駆動トランジスタ30のゲート・ソース間電圧がしきい値（スレショールド）よりも小さくなると、電源側駆動トランジスタ30はいわゆるサブスレショールド領域となりオン抵抗は急激に高くなつてオフし始める。そうすると、同時に電源側検出トランジスタ24もオフし始めるので節点Cはローレベルとなる。節点Dの電圧は、第3の制御トランジスタ26がオンするので、インピーダンス素子28の抵抗値と寄生容量33の容量値で決まる時定数で上昇する。

30

## 【0018】

ここで、インピーダンス素子28はインピーダンス素子19の抵抗値よりも大きいので、節点Dの電圧は節点Bの電圧よりも緩やかに上昇する。これにより、サブスレショールド領域であつても少量の電流が流れる電源側駆動トランジスタ30が完全にオフしてから接地側駆動トランジスタ31に電流が流れることになり、これら2個のトランジスタ30、31における貫通電流を抑制する。この貫通電流抑制のためには、節点Bの電圧は比較的早く電源電位Vccまで上昇させる必要があるので、インピーダンス素子19は前述のようにインピーダンス素子28の抵抗値よりも小さくしてあるのである。

40

## 【0019】

入力端子INからの入力信号がローレベルからハイレベルに変化すると、節点Cはハイレベルとなり、節点Dの電圧は、第4の制御トランジスタ27がオンするので、インピーダンス素子29の抵抗値と寄生容量33の容量値で決まる時定数で降下する。節点Dの電圧変化に従って接地側駆動トランジスタ31のオン抵抗は徐々に高くなり、コイル負荷2は誘導性の性質により電流を流し続けようとするため、出力端子OUTの電圧は僅かに降下するが、接地側駆動トランジスタ31と並列に存在する寄生ダイオード（図示せず）によりクランプされる。なお、このとき、接地側検出トランジスタ15はオンしているので、節点Aはローレベルに、節点Bはハイレベルに保たれ、従って、電源側駆動トランジスタ30は入力端子INからの入力信号に係わらず強制的にオフされている。そして、節点

50

Dの電圧が更に下降して接地側駆動トランジスタ31のゲート・ソース間電圧がしきい値(スレショールド)よりも小さくなると、接地側駆動トランジスタ31はサブスレショールド領域となりオン抵抗は急激に高くなつてオフし始める。そうすると、同時に接地側検出トランジスタ15もオフし始めるので節点Aはハイレベルとなる。節点Bの電圧は、第2の制御トランジスタ18がオンするので、インピーダンス素子20の抵抗値と寄生容量32の容量値で決まる時定数で緩やかに降下する。この節点Bの電圧に従い出力端子OUTの電圧は徐々に上昇する。従つて、輻射ノイズは低減される。

#### 【0020】

次に、コイル負荷2から出力端子OUTの方向に電流が流れている場合を説明する。出力端子OUT(図2の波形OUT')以外の各部は前述と同様の動作を示す。入力端子INからの入力信号がハイレベルからローレベル又はローレベルからハイレベルに変化すると、出力端子OUTの電圧は、節点Dの電圧に従つて徐々に降下又は上昇する。つまり、出力端子OUTの電圧は、接地側駆動トランジスタ31がオンし始めてから降下し始め、接地側駆動トランジスタ31がオフし始めてから上昇し始める。この場合も同様に輻射ノイズは低減される。

#### 【0021】

次に、本発明の別の実施形態であるコイル負荷駆動出力回路を説明する。このコイル負荷駆動出力回路51は、図3に示すように、コイル負荷駆動出力回路1におけるP型MOSトランジスタである電源側駆動トランジスタ30をN型MOSトランジスタである電源側駆動トランジスタ56に置き換えたものである。これに伴い、P型MOSトランジスタである電源側検出トランジスタ24をN型MOSトランジスタである電源側検出トランジスタ55に、バッファ16を反転バッファ52に、第1の電流制限インピーダンス素子19を抵抗値が比較的大きい(例えば10K乃至30Kの)第1の電流制限インピーダンス素子53に、第2の電流制限インピーダンス素子20を抵抗値が比較的小さい(例えば1K乃至2Kの)第2の電流制限インピーダンス素子54に、それぞれ置き換えられている。このコイル負荷駆動出力回路51は、前述の図2において節点Bの電圧波形が上下逆になるが、コイル負荷駆動出力回路1と同様な動作を行い、輻射ノイズが低減される。

#### 【0022】

なお、コイル負荷駆動出力回路1又は51は、接地側検出トランジスタ15及び電源側検出トランジスタ24又は55などを設けることにより、電源側駆動トランジスタ30又は56がオンしていれば接地側駆動トランジスタ31は強制的にオフされ、接地側駆動トランジスタ31がオンしていれば電源側駆動トランジスタ30は強制的にオフされるようにして、電源側駆動トランジスタ30又は56と接地側駆動トランジスタ31における貫通電流を自動的に抑制しているが、第1乃至第4の制御トランジスタ17、18、26、27のゲートを個別に制御して貫通電流を抑制することも可能である。

#### 【0023】

以上、本発明の実施形態であるコイル負荷駆動出力回路について説明したが、本発明は、実施形態に記載したものに限られることなく、特許請求の範囲に記載した事項の範囲内でのさまざまな設計変更が可能である。例えば、電流制限インピーダンス素子14、19(又は53)、20(又は54)、23、28、29は抵抗であるが、これを定電流源とすることも可能である。また、寄生容量32、33の他に積極的に容量を付加することも可能である。

#### 【図面の簡単な説明】

#### 【0024】

【図1】本発明の実施形態に係るコイル負荷駆動出力回路の回路図。

【図2】同上の各部に生じる波形を示した波形図。

【図3】本発明の別の実施形態に係るコイル負荷駆動出力回路の回路図。

【図4】スイッチング時の現象を説明する回路図。

#### 【符号の説明】

#### 【0025】

10

20

30

40

50

- 1、5 1 コイル負荷駆動出力回路

2 コイル負荷

1 5 接地側検出トランジスタ

1 7 第1の制御トランジスタ

1 8 第2の制御トランジスタ

1 9、5 3 第1の電流制限インピーダンス素子

2 0、5 4 第2の電流制限インピーダンス素子

2 4、5 5 電源側検出トランジスタ

2 6 第3の制御トランジスタ

2 7 第4の制御トランジスタ

2 8 第3の電流制限インピーダンス素子

2 9 第4の電流制限インピーダンス素子

3 0、5 6 電源側駆動トランジスタ

3 1 接地側駆動トランジスタ

10

【図1】

【図2】

【図3】

【図4】

---

フロントページの続き

(56)参考文献 特開平01-176117(JP,A)

特開2003-189683(JP,A)

特開平01-196915(JP,A)

特開平01-309413(JP,A)

特開平05-252011(JP,A)

特開平08-223014(JP,A)

特開平03-034622(JP,A)

特開平01-240013(JP,A)

特開平09-047015(JP,A)

(58)調査した分野(Int.Cl., DB名)

H03K 17/00 - 17/70

H03K 19/00

19/01 - 19/082

19/094 - 19/096